Modeling structure of GPU texture mapping non-blocking memory Cache

A technology of texture mapping and texture storage, which is applied in processor architecture/configuration, image data processing, image memory management, etc. It can solve problems such as limited data bandwidth and data processing speed, graphics elements, and texture data cannot be fully loaded, and achieve Avoid circuit signal design and avoid cumbersome effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

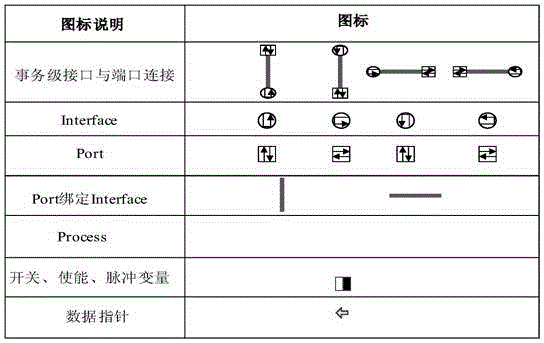

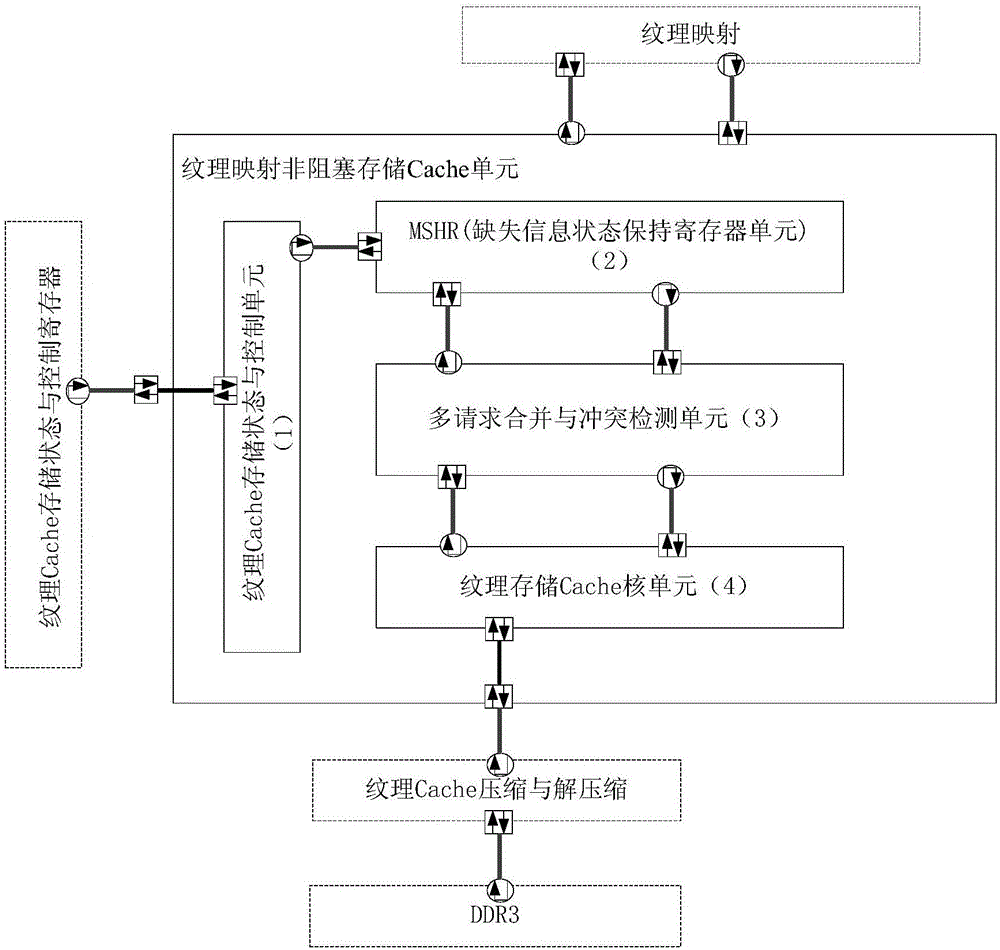

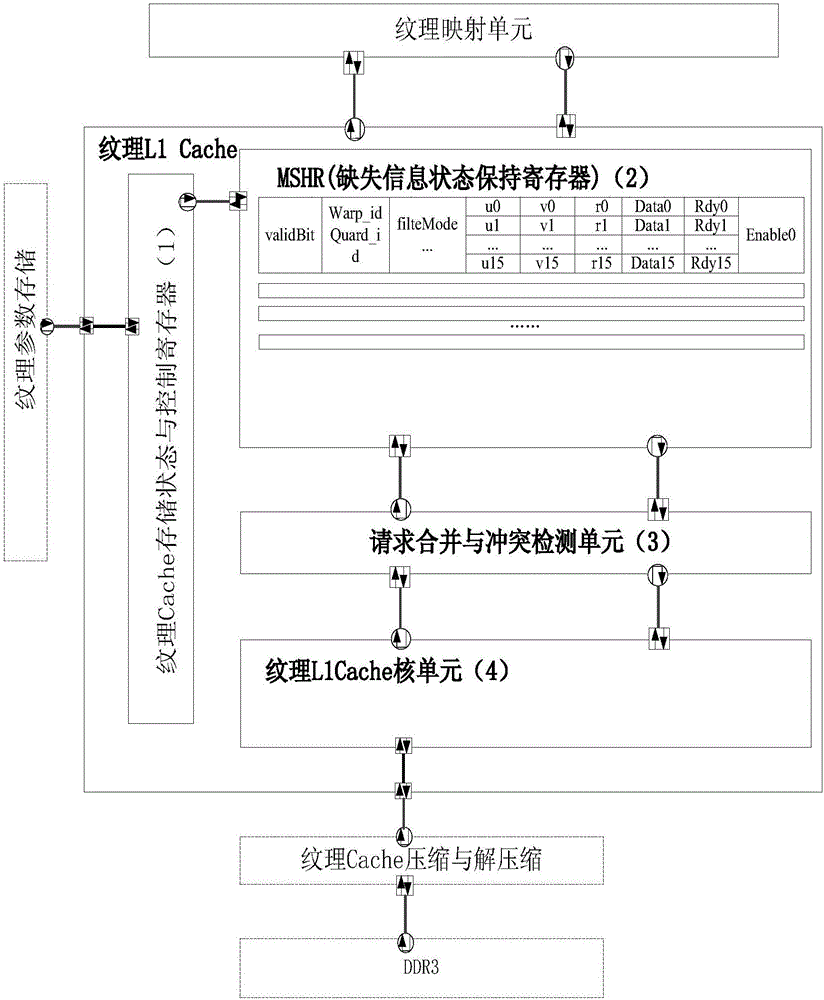

[0042] The technical solutions of the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

[0043] Such as figure 1 , figure 2 and image 3 As shown, a GPU texture mapping non-blocking rate storage Cache modeling structure uses SystemC language and Transaction Level Modeling (TLM, transaction level modeling) method to perform cycle-accurate hardware modeling on the texture storage Cache access process. The texture mapping unit includes 4 functional modules. These 4 functional unit models adopt the multi-process method of input request conflict detection, request merging and division, multi-port, multi-Bank, and non-blocking pipeline to realize parallel processing of texture access request data.

[0044] The texture mapping non-blocking storage Cache unit includes a texture Cache storage state and control unit (1), a missing information state holding register storage unit (MSHR) (2), a multi-requ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More