Hybrid PUF circuit

A hybrid and circuit technology, applied in logic circuits, electrical components, pulse technology, etc., can solve the problems of general model attack effect, general machine learning attack effect, PUF circuit reliability and randomness, etc., to achieve high reliability Randomness, strong defense against model attacks and machine learning attacks, and strong capabilities

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

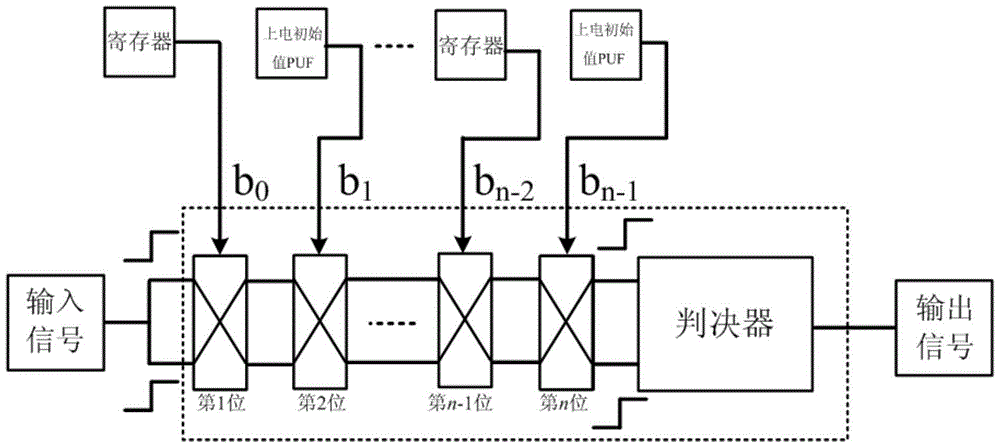

[0031] Embodiment one: if figure 1 As shown, a hybrid PUF circuit includes a basic PUF circuit and a control PUF circuit, and the basic PUF circuit is a decision-type PUF circuit;

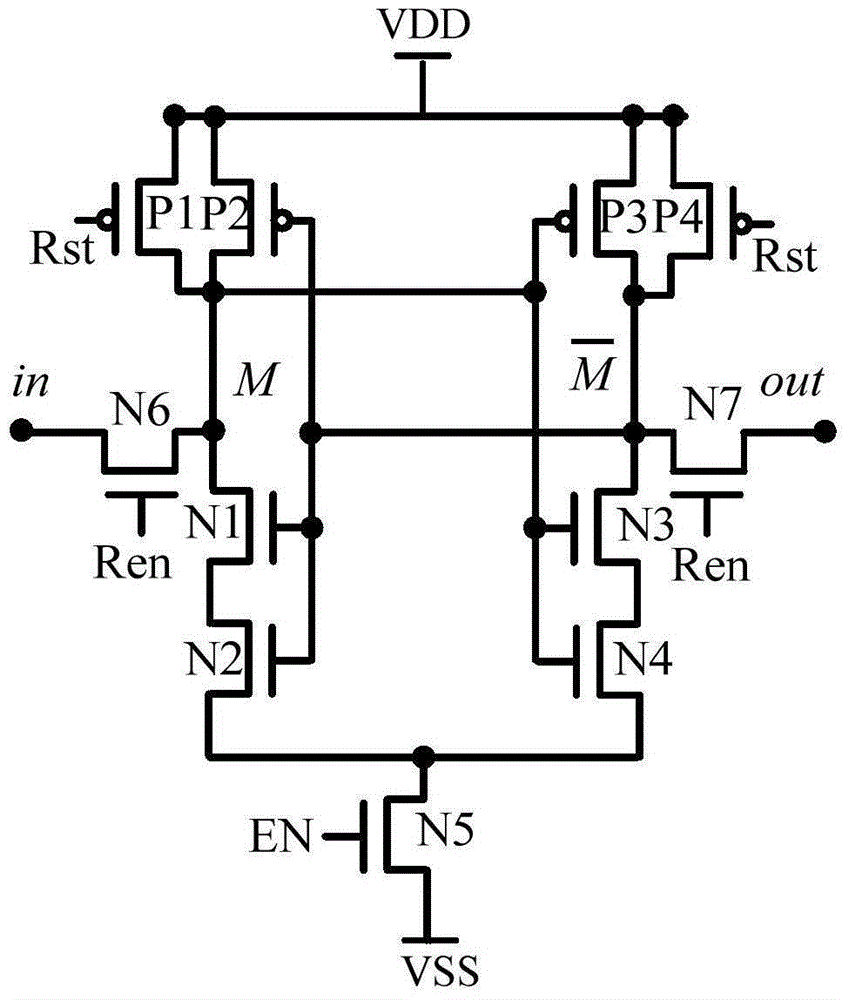

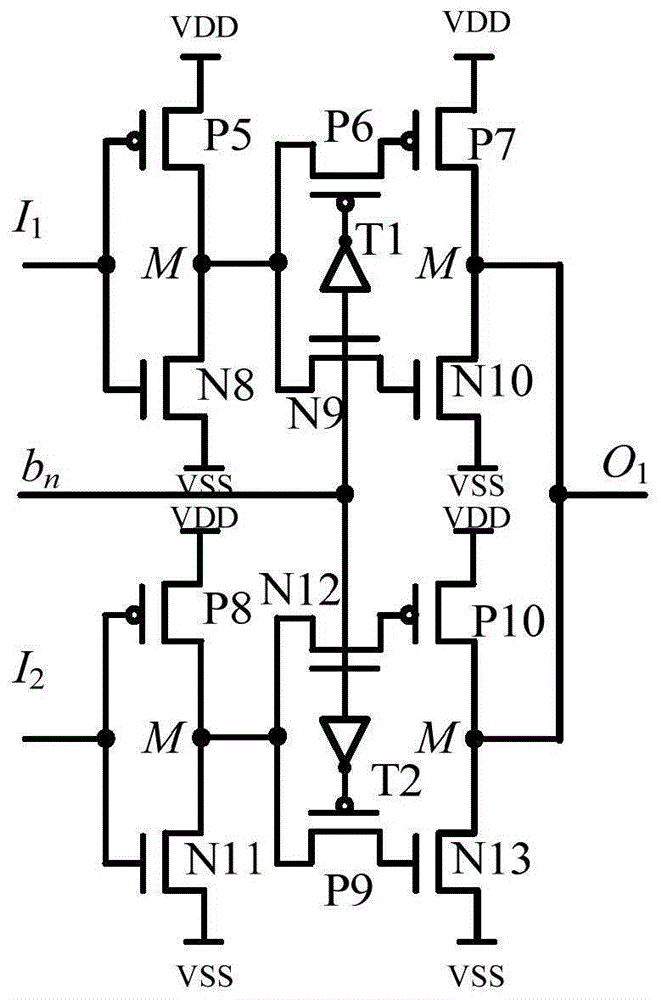

[0032] The basic PUF circuit includes a decision device and an n-bit delay circuit, the decision device has a first input terminal, a second input terminal and an output terminal, the delay circuit is composed of two delay circuit units, and the delay circuit unit has a first input terminal, a second input terminal Terminal, output terminal and enabling terminal, two delay circuit units are respectively the first delay circuit unit and the second delay circuit unit, the first input terminal of the first delay circuit unit and the first input terminal of the second delay circuit unit in the delay circuit The input end is connected and its connection end is the first input end of the delay circuit, and the second input end of the first delay circuit unit in the delay circuit is connected with the sec...

Embodiment 2

[0037] Embodiment two: if Figure 1-Figure 7 As shown, a hybrid PUF circuit includes a basic PUF circuit and a control PUF circuit, and the basic PUF circuit is a decision-type PUF circuit;

[0038] The basic PUF circuit includes a decision device and an n-bit delay circuit, the decision device has a first input terminal, a second input terminal and an output terminal, the delay circuit is composed of two delay circuit units, and the delay circuit unit has a first input terminal, a second input terminal Terminal, output terminal and enabling terminal, two delay circuit units are respectively the first delay circuit unit and the second delay circuit unit, the first input terminal of the first delay circuit unit and the first input terminal of the second delay circuit unit in the delay circuit The input end is connected and its connection end is the first input end of the delay circuit, and the second input end of the first delay circuit unit in the delay circuit is connected wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More