Patents

Literature

2542 results about "Program instruction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

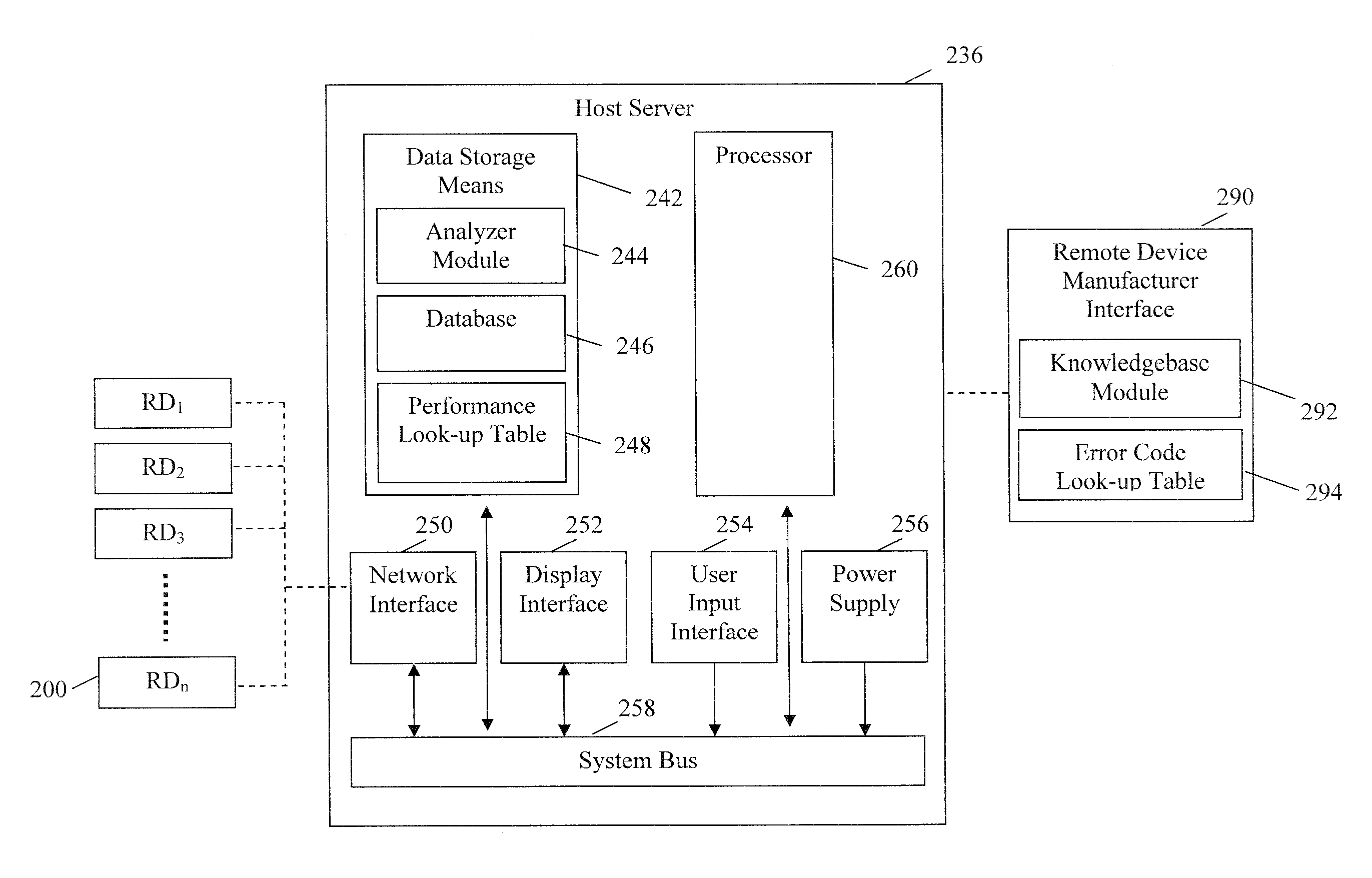

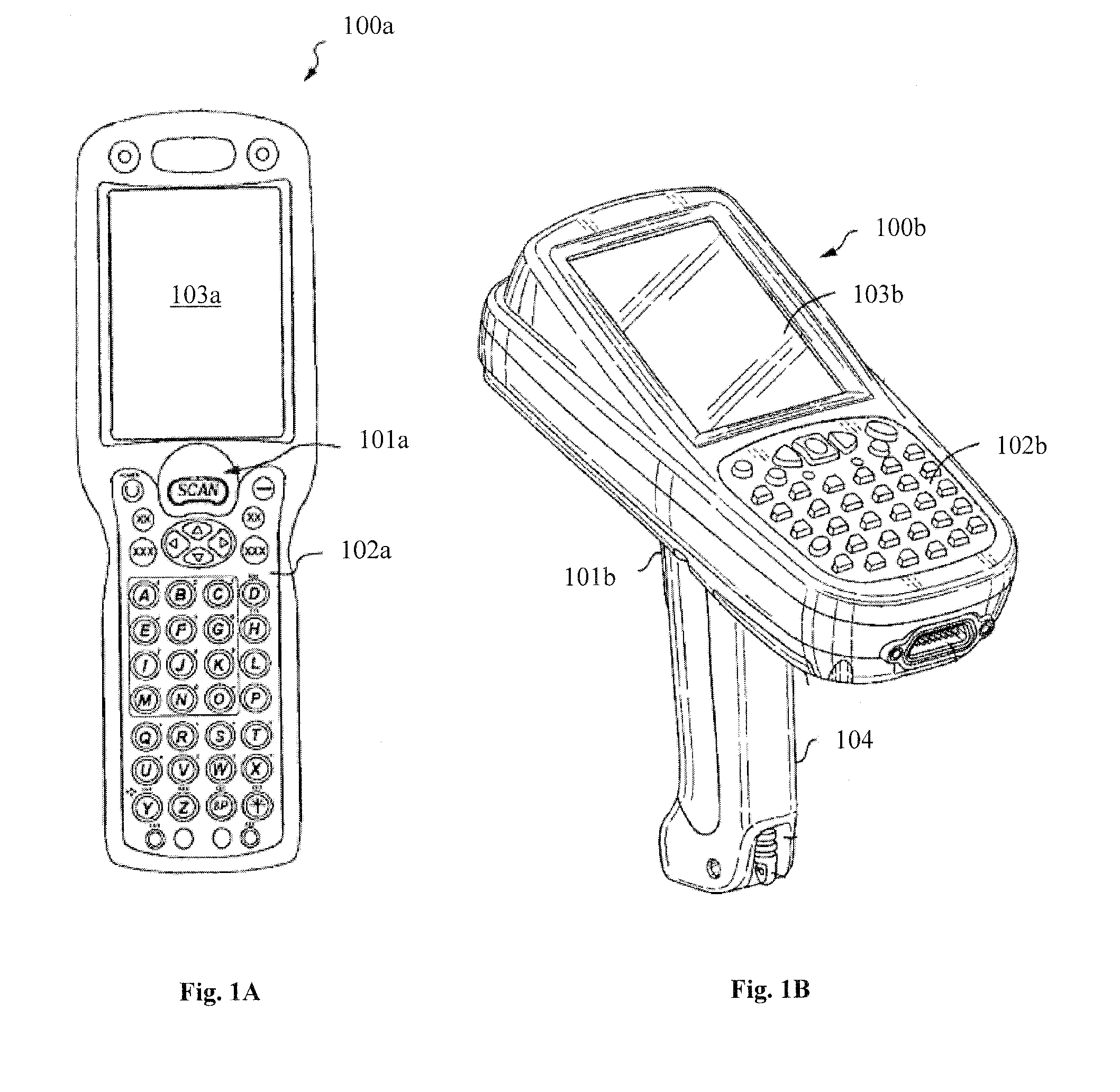

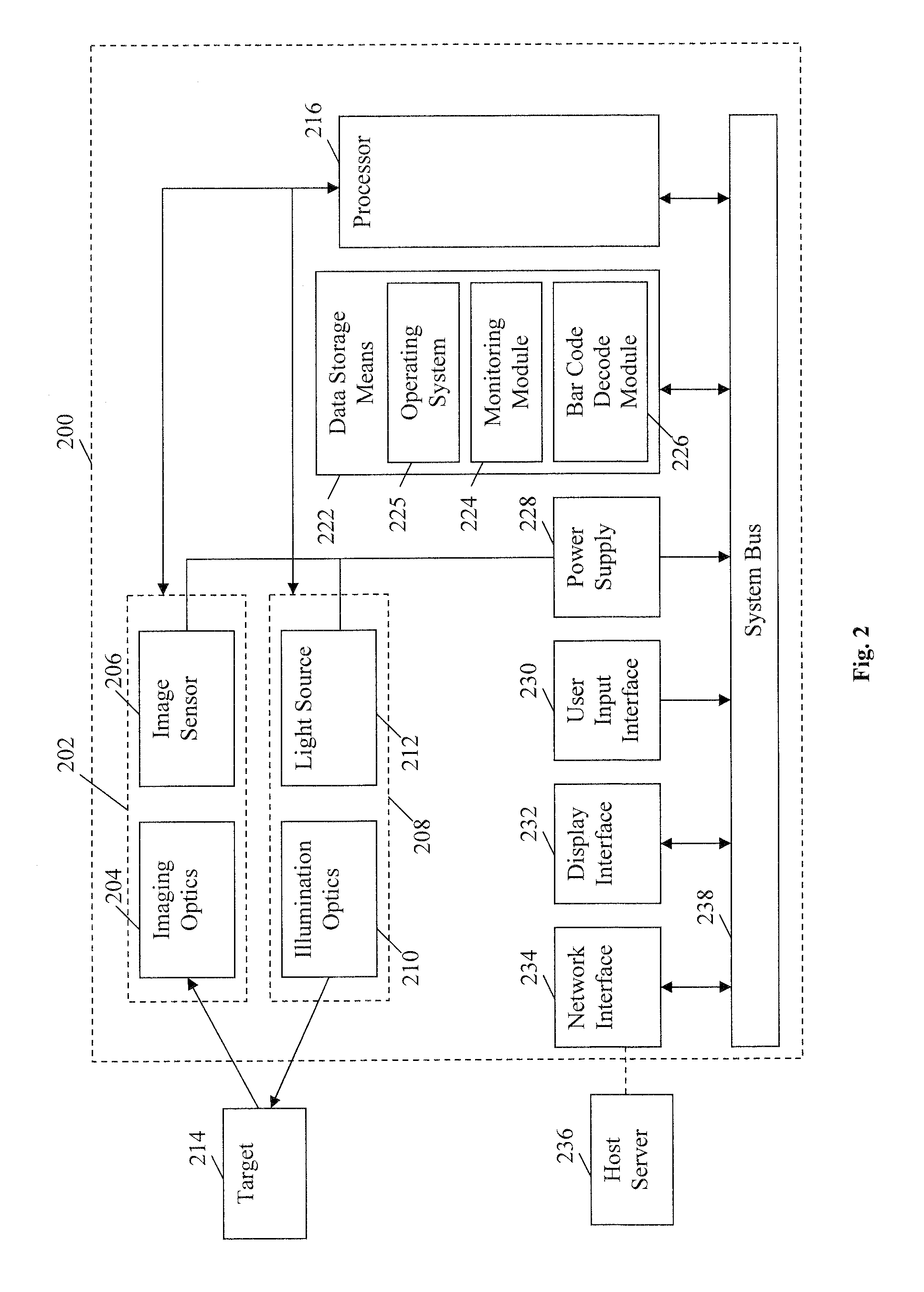

Remote device management system and method

A remote device monitoring system including a host server including at least a processor, system bus, user input interface configured to communicate with a user input device, display interface configured to communicate with a display, network interface configured to communicate with at least one remote device and at least one data storage means including a database, a performance look-up table and at least one analyzer module including program instructions that, when implemented by the processor, receive at least one performance parameter value from at least one remote device and query the performance look-up table.

Owner:HAND HELD PRODS

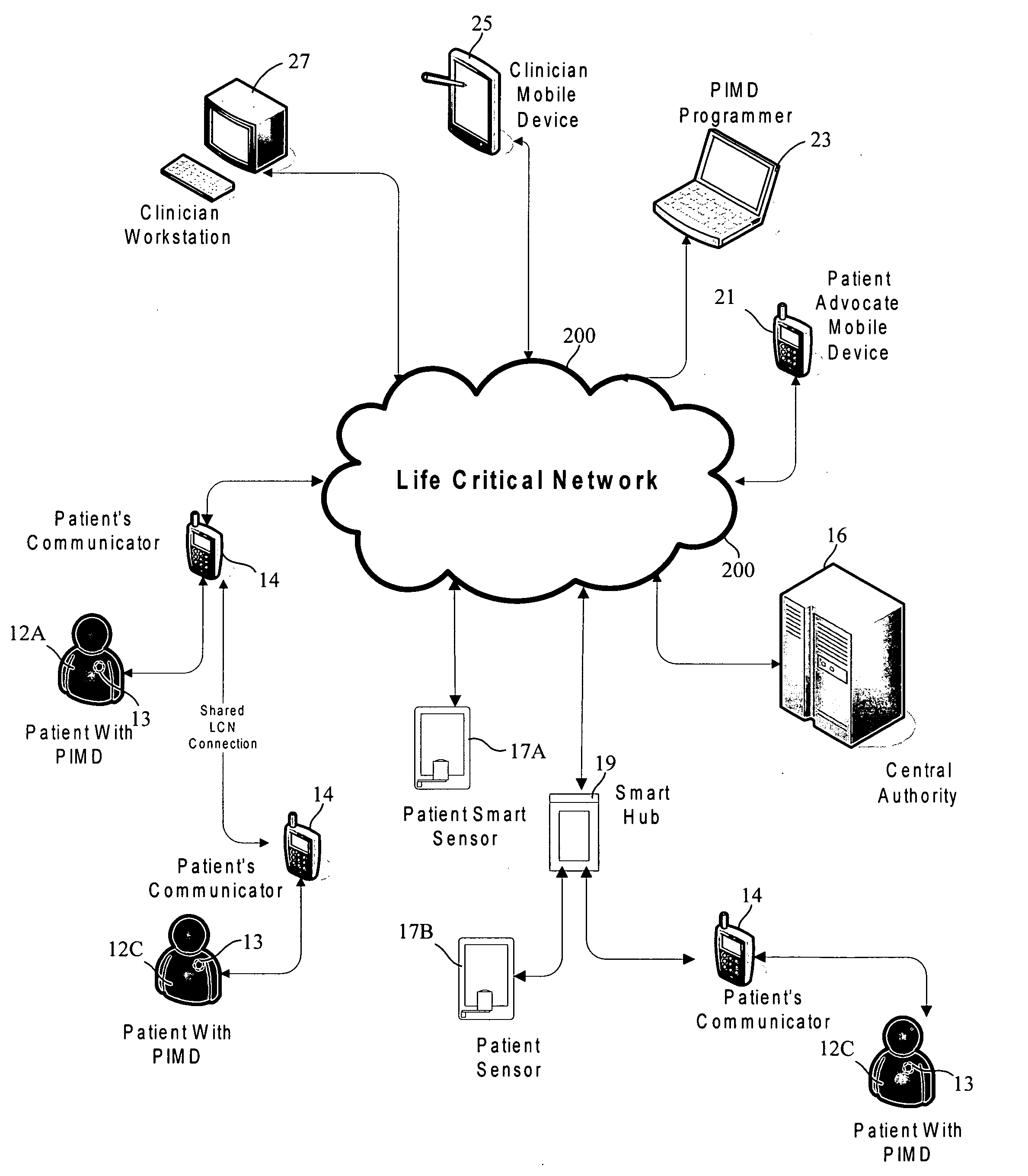

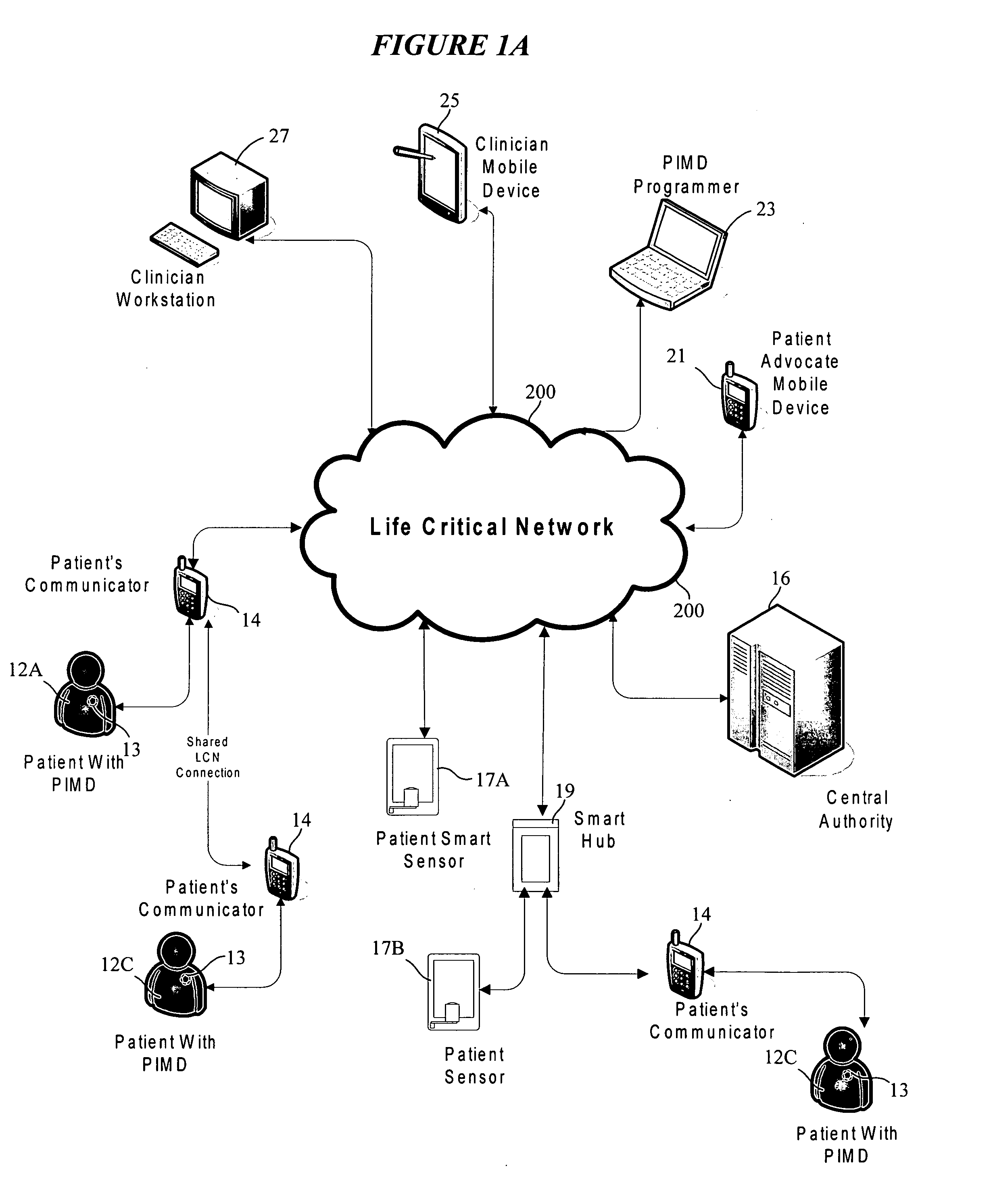

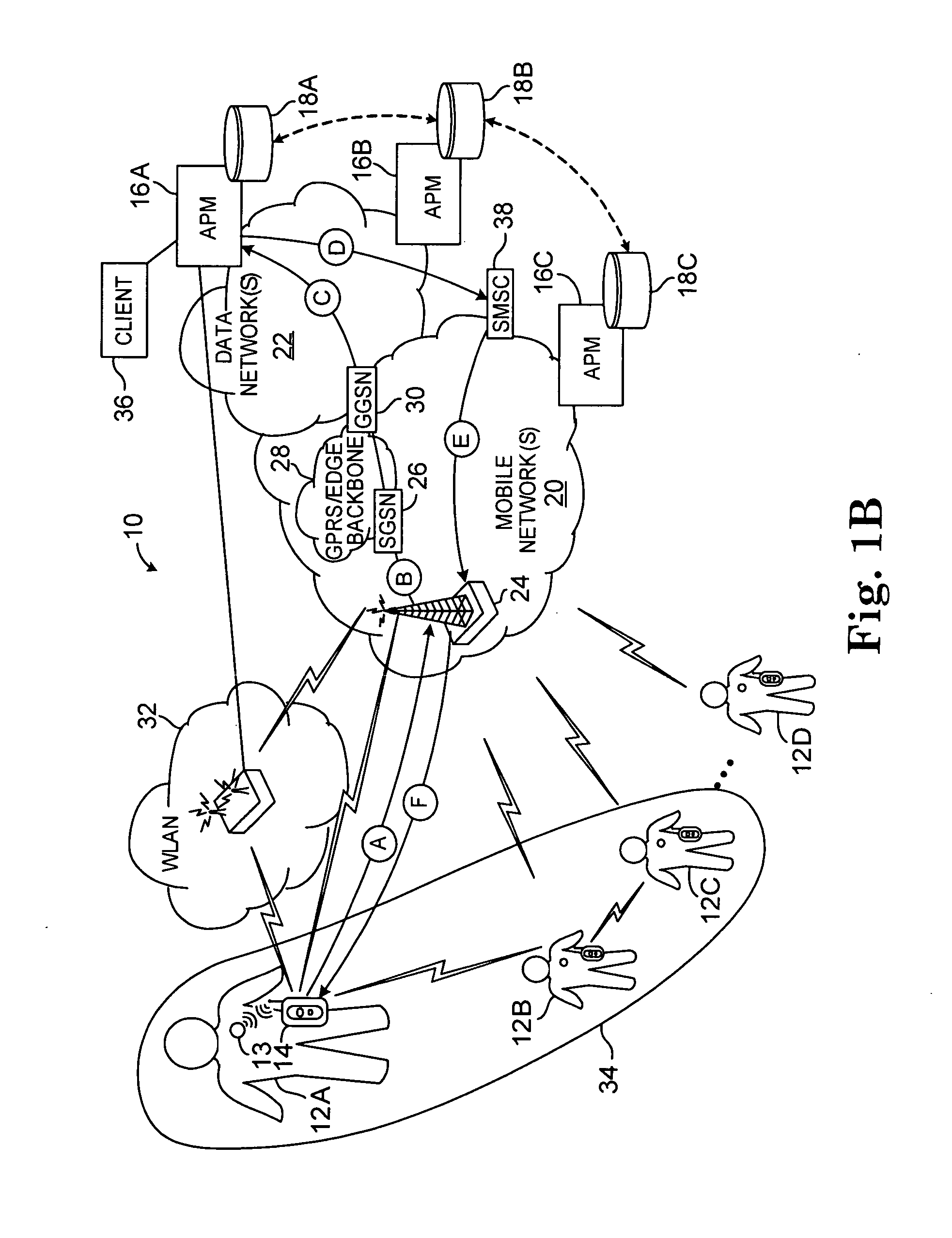

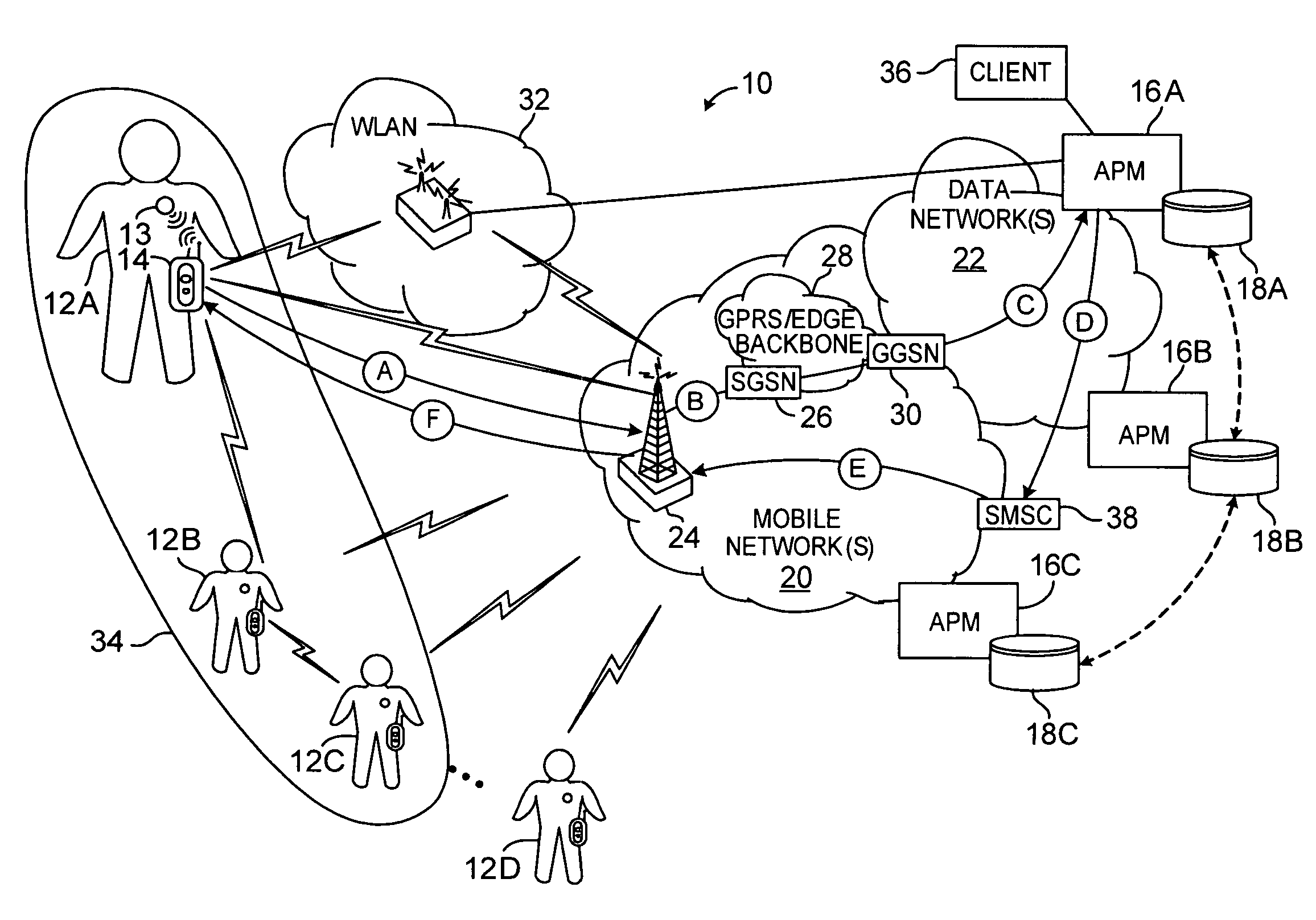

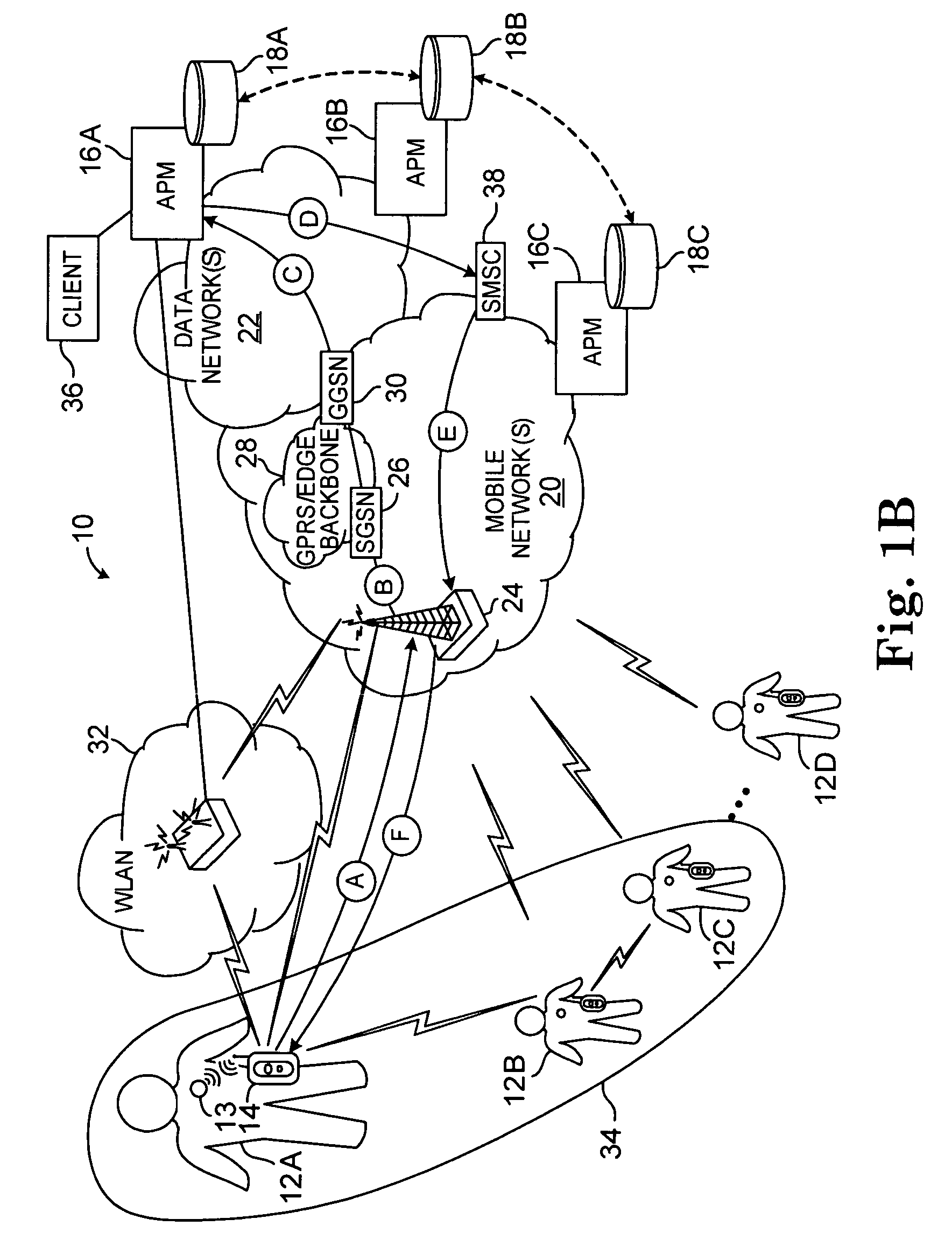

Medical data transport over wireless life critical network

ActiveUS20090058635A1Facilitate communicationElectrotherapyDiagnostic recording/measuringMedical equipmentProgram instruction

A portable patient communicator (PPC) includes a portable housing that supports a processor coupled to memory for storing medical firmware and wireless radio firmware, first and second radios, a processor, and a power source. Communications between a patient implantable medical device (PIMD) and the first radio of the PPC are effected in accordance with program instructions of the medical firmware, and communications between the second radio of the PPC and the wireless network are effected in accordance with program instructions of the wireless radio firmware. Data from the PIMD is received via the first radio to which a priority level is assigned, such as in a tiered manner. A data transport mechanism is selected among disparate data transport mechanisms based at least in part on the priority level. PIMD data is transmitted to the wireless network using the selected transport mechanism via the second radio.

Owner:CARDIAC PACEMAKERS INC

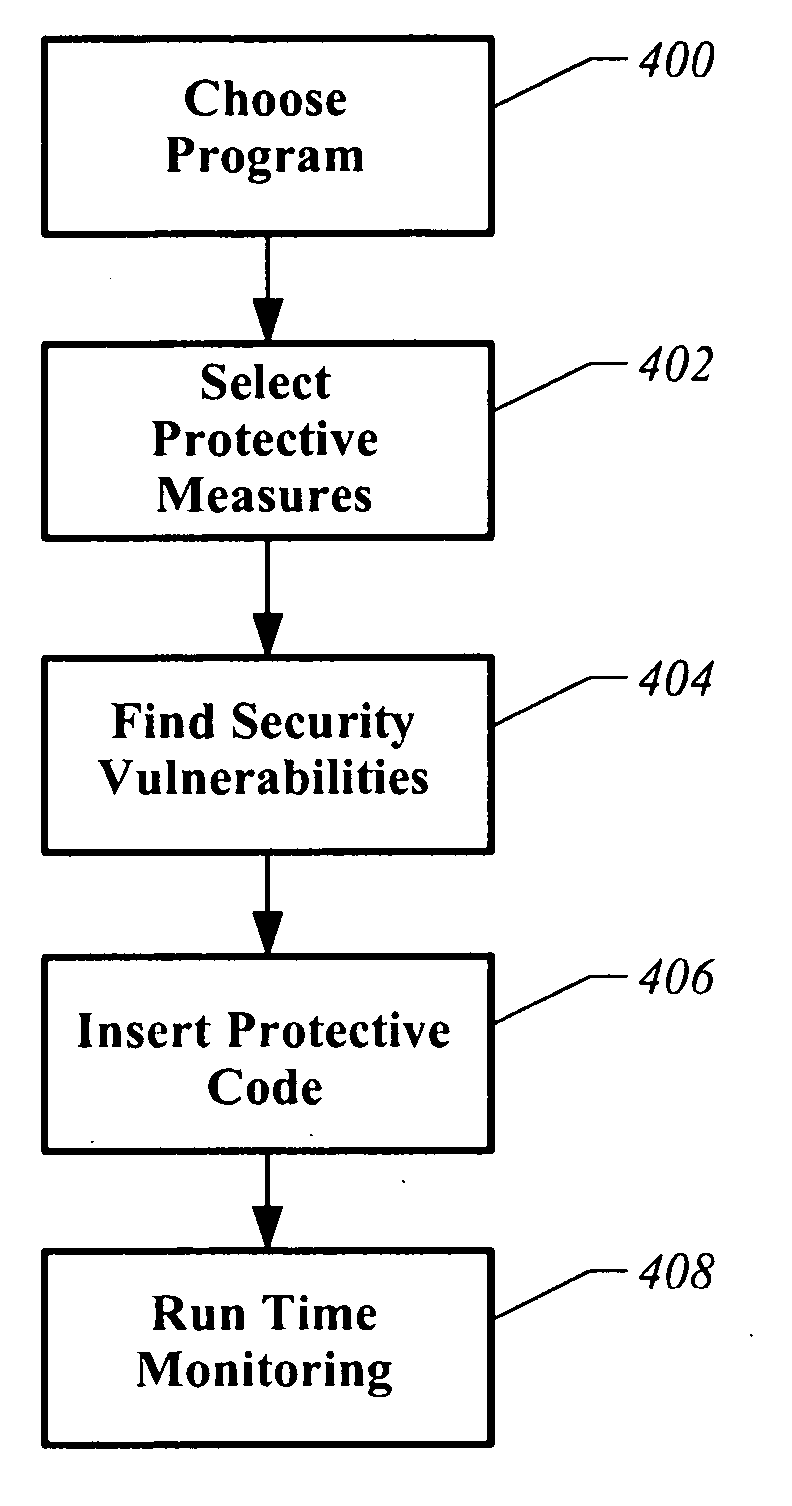

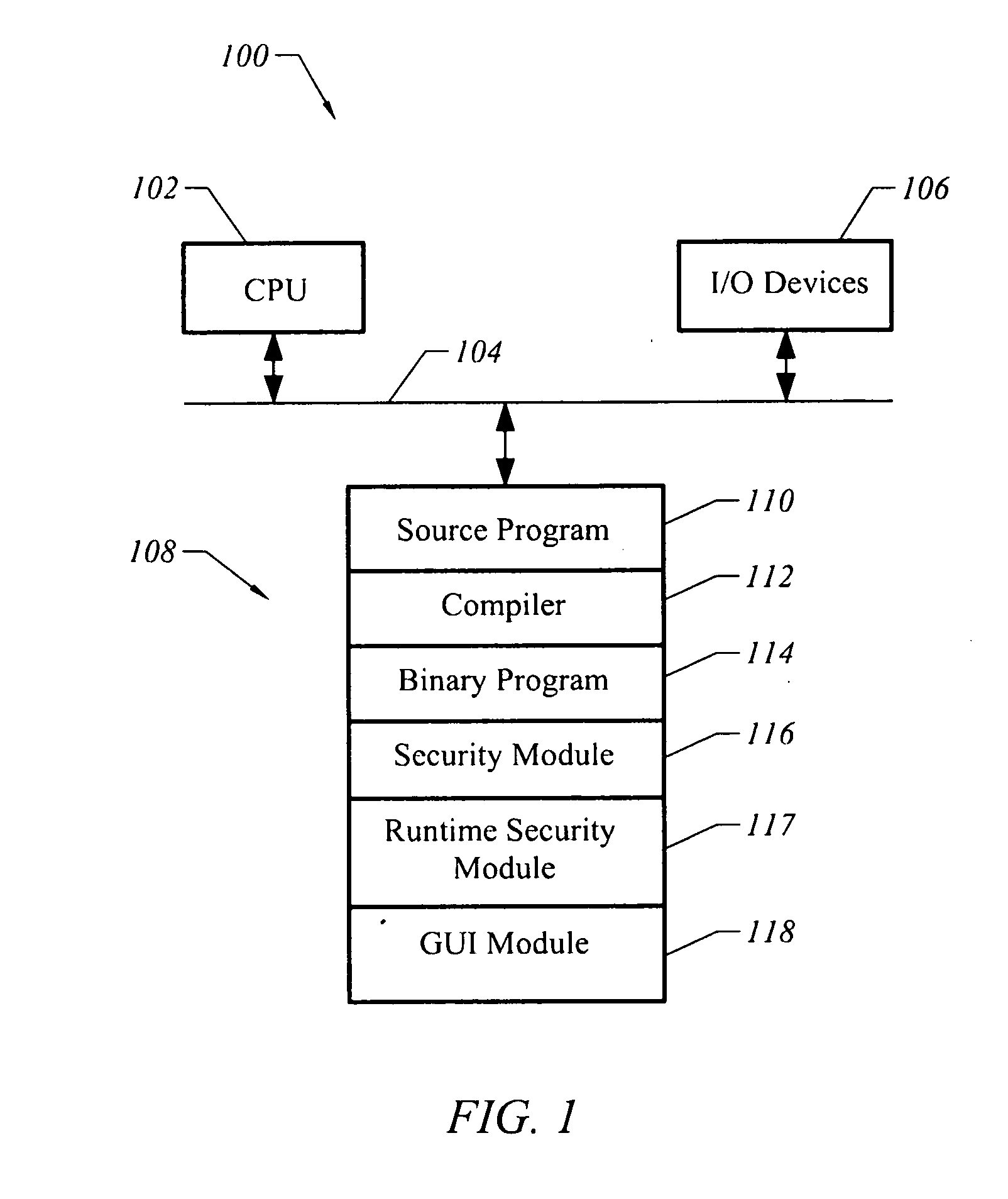

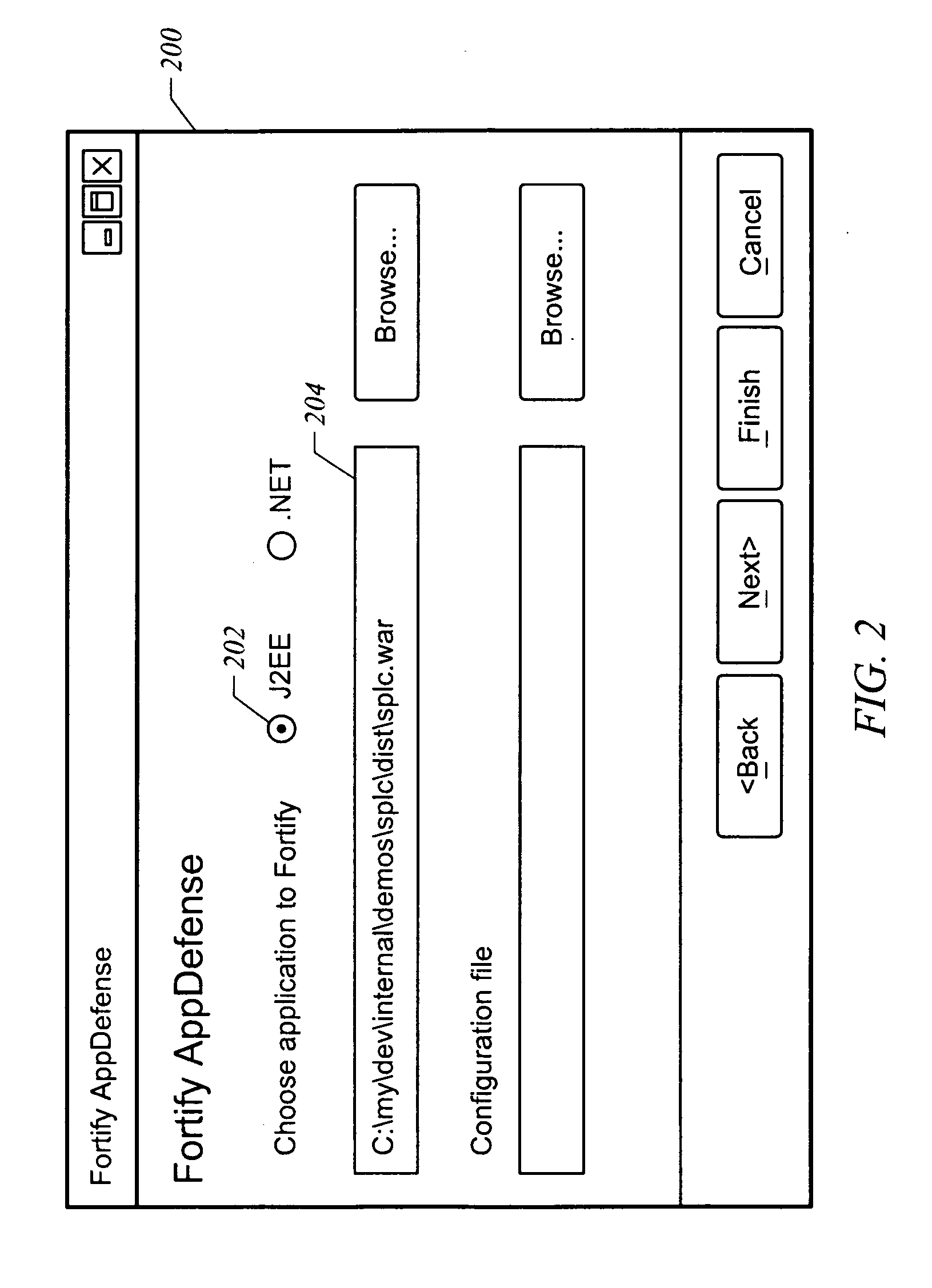

Apparatus and method for analyzing and supplementing a program to provide security

ActiveUS20070074169A1Memory loss protectionError detection/correctionProgramming languageProgram instruction

A computer readable storage medium has executable instructions to perform an automated analysis of program instructions. The automated analysis includes at least two analyses selected from an automated analysis of injection vulnerabilities, an automated analysis of potential repetitive attacks, an automated analysis of sensitive information, and an automated analysis of specific HTTP attributes. Protective instructions are inserted into the program instructions. The protective instructions are utilized to detect and respond to attacks during execution of the program instructions.

Owner:MICRO FOCUS LLC

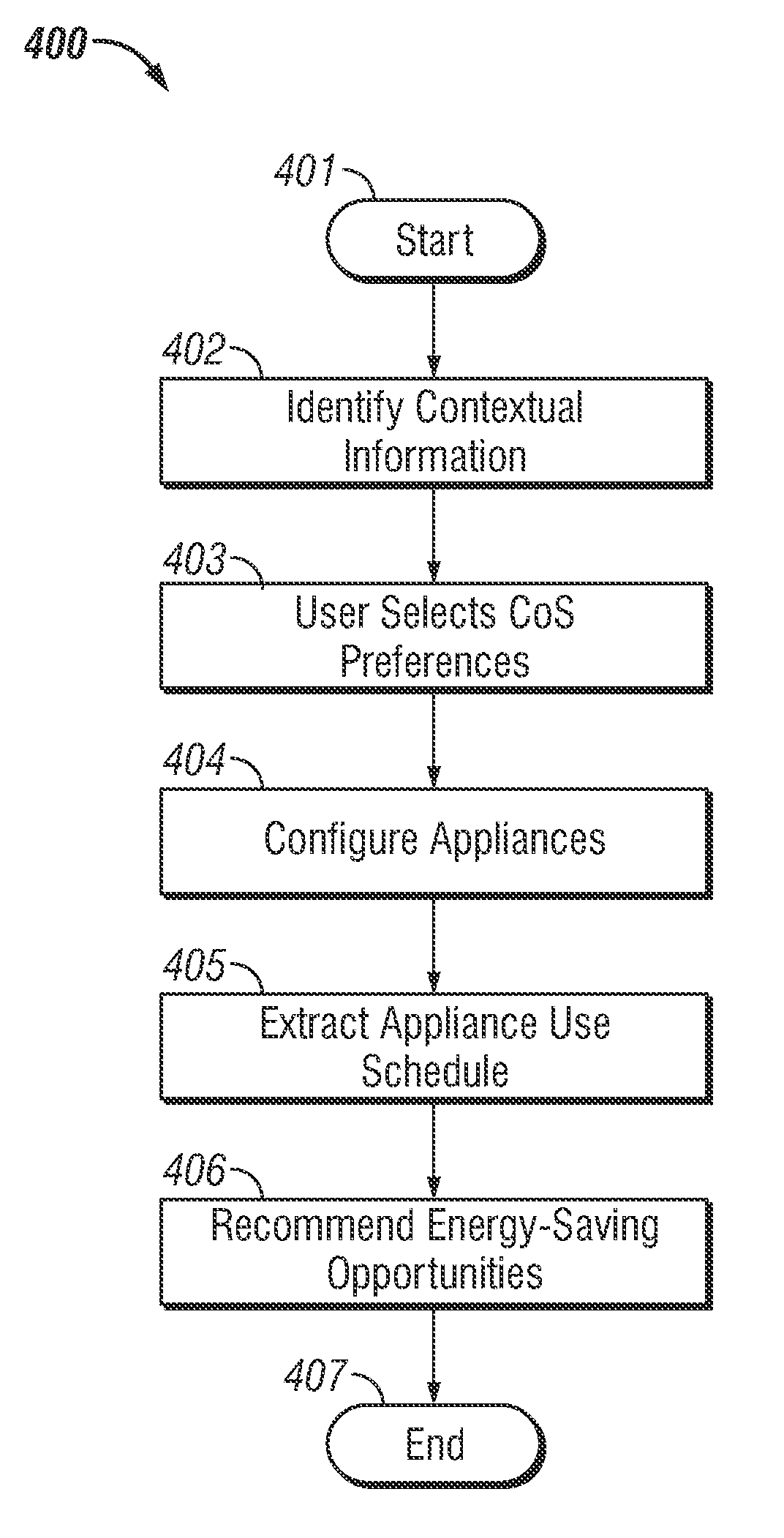

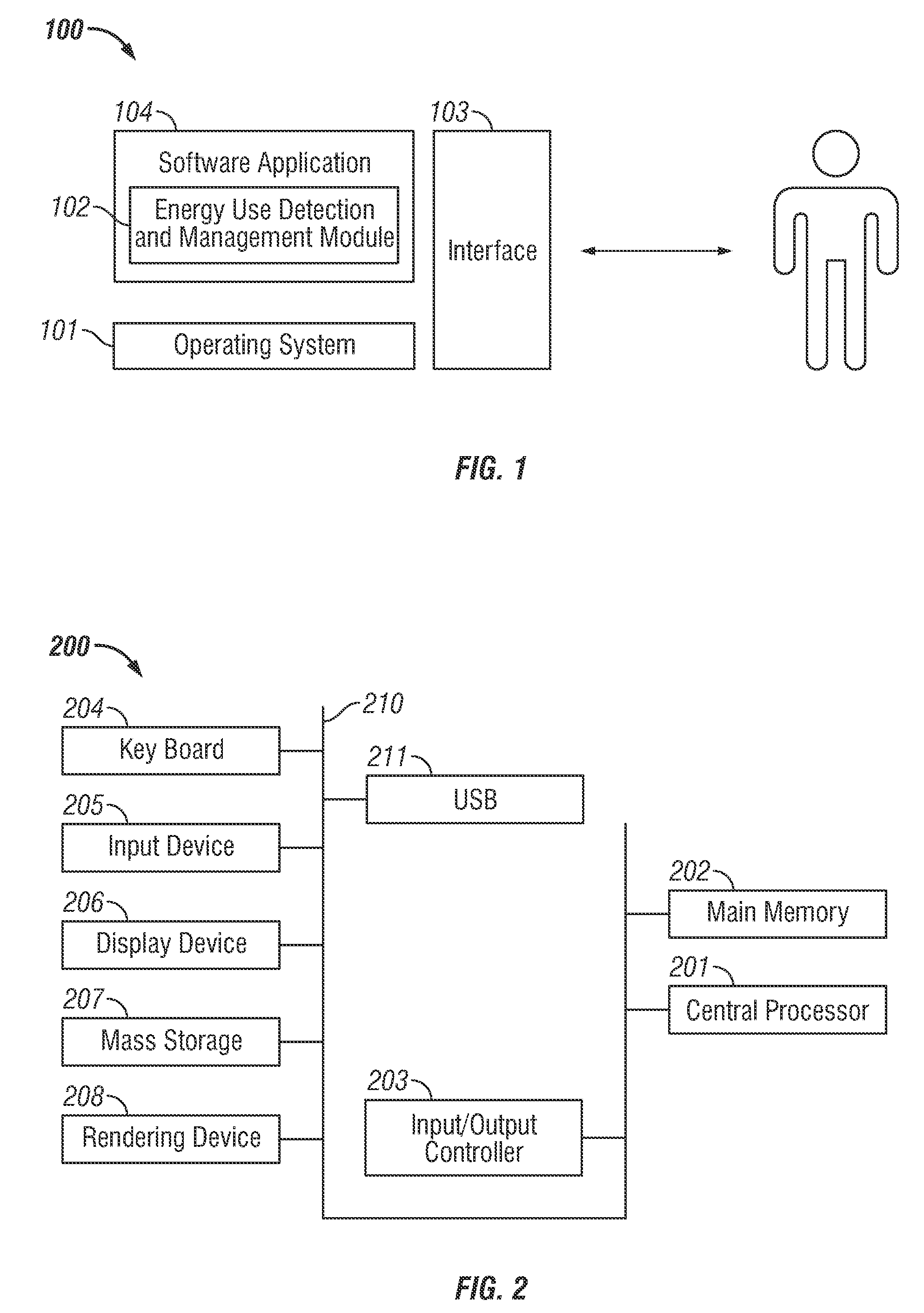

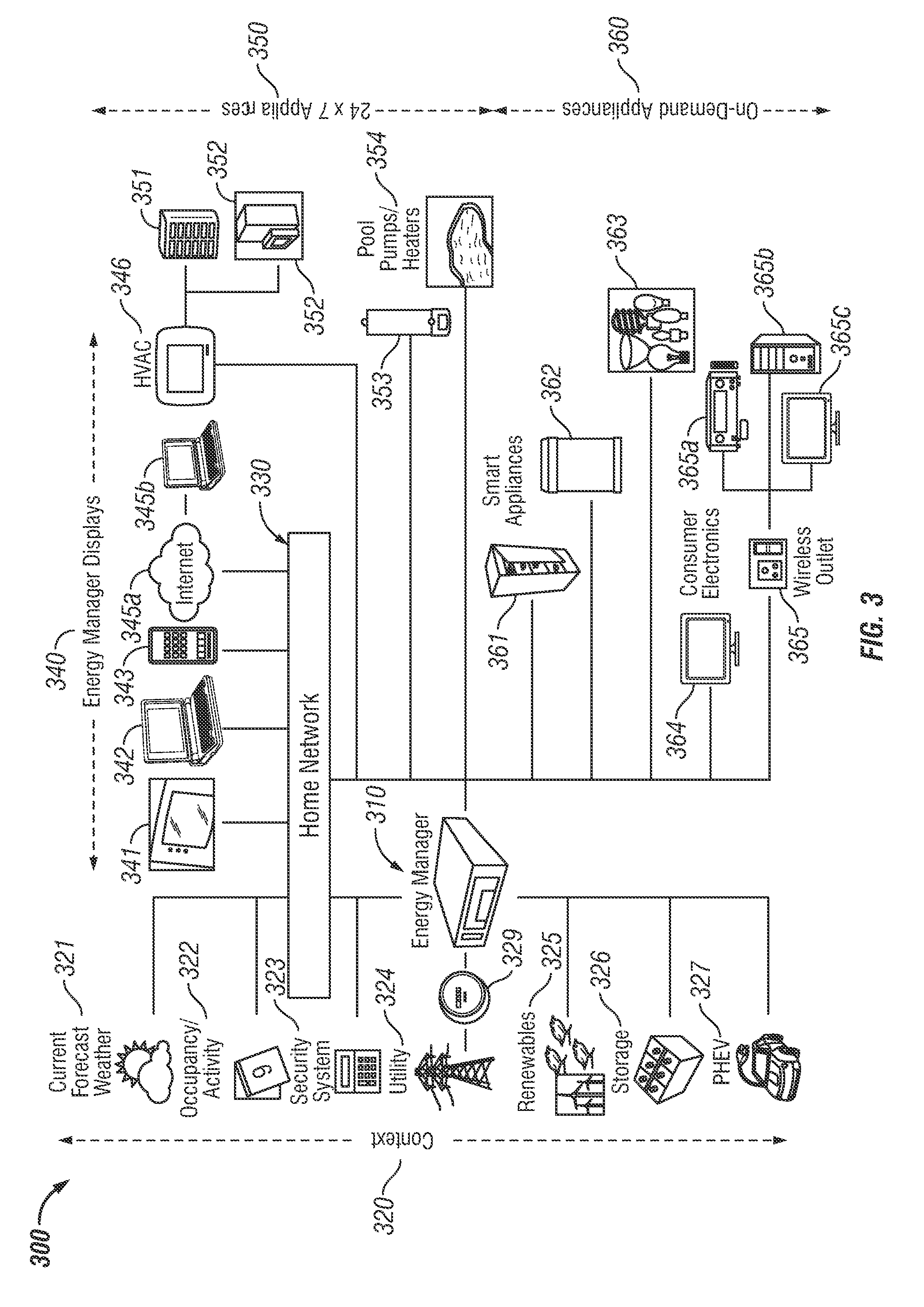

Context-aware smart home energy manager

InactiveUS20110046805A1Programme controlMechanical power/torque controlProgram instructionEngineering

A context-aware smart home energy management (CASHEM) system and method is disclosed. CASHEM dynamically schedules household energy use to reduce energy consumption by identifying contextual information within said household, selecting a comfort of service preference, wherein said comfort of service preference is based on different said contextual information, and extracting an appliance use schedule for maximum energy savings based on said contextual information in light of said comfort of service preferences, by executing a program instruction in a data processing apparatus. CASHEM correlates said contextual information with energy consumption levels to dynamically schedule said appliance based on an energy-saving condition and a user's comfort. Comfort of service preferences are gathered by CASHEM by monitoring occupant activity levels and use of said appliance. CASHEM can also recommend potential energy savings for a user to modify comfort of service preferences.

Owner:HONEYWELL INT INC

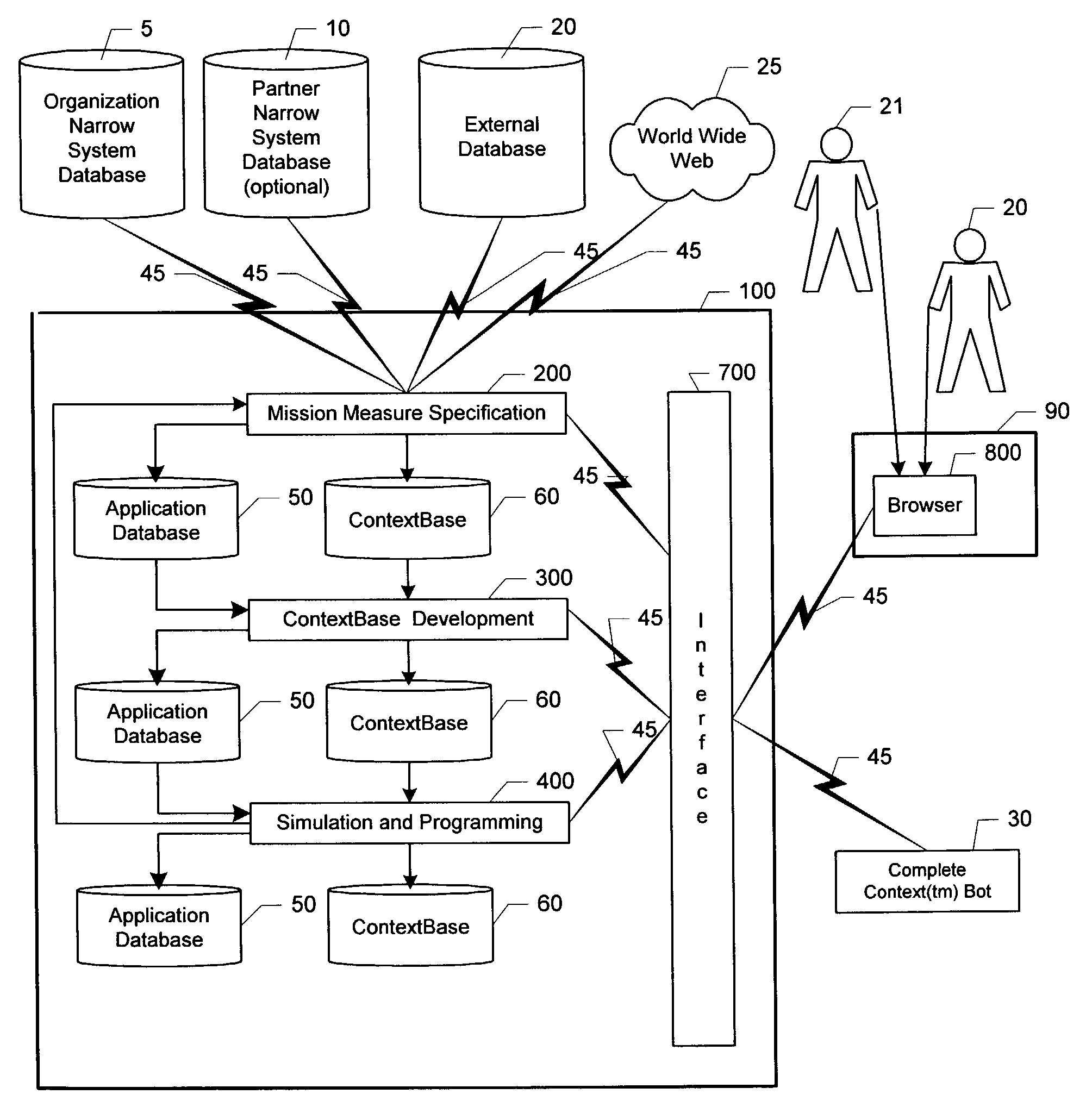

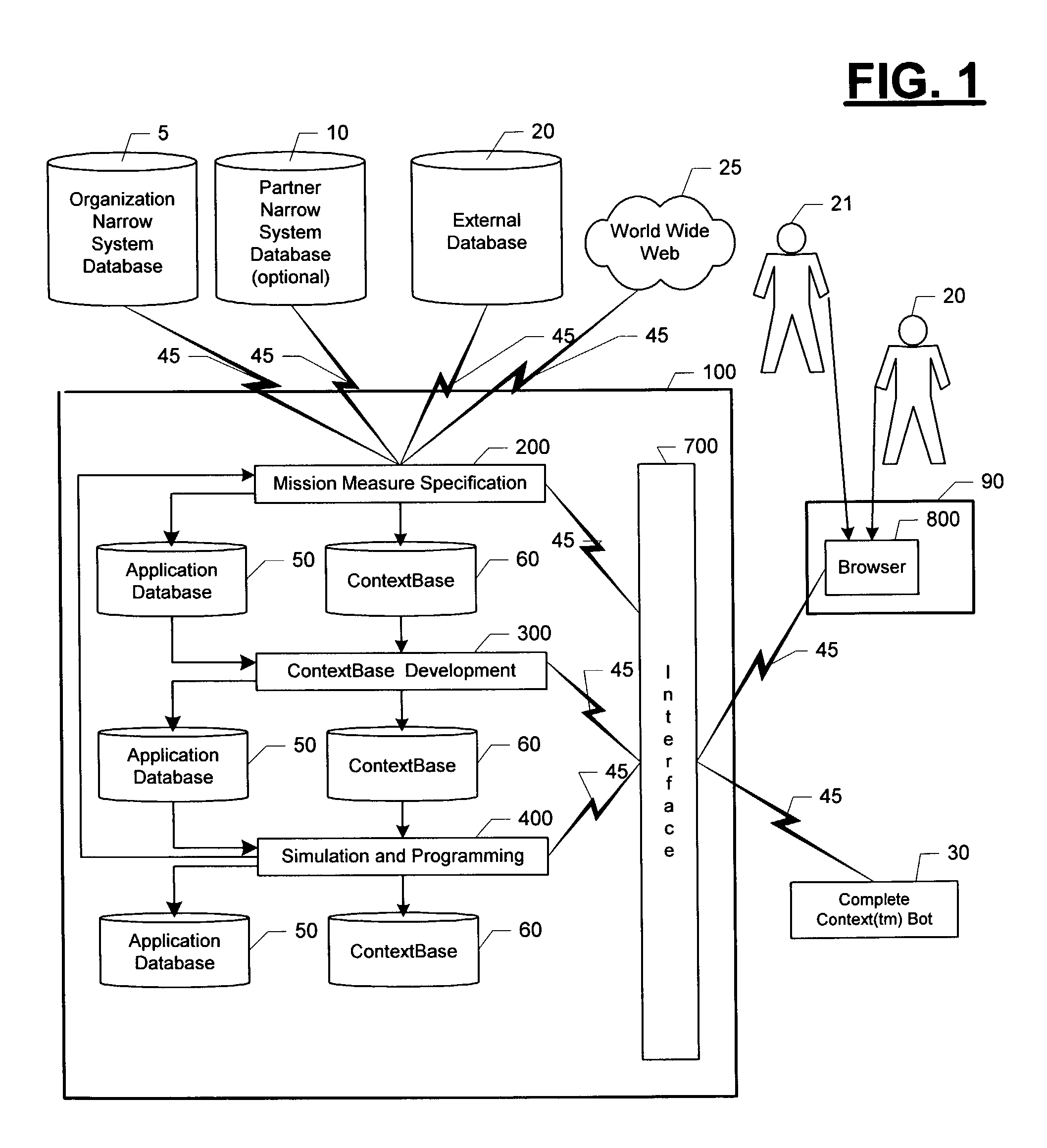

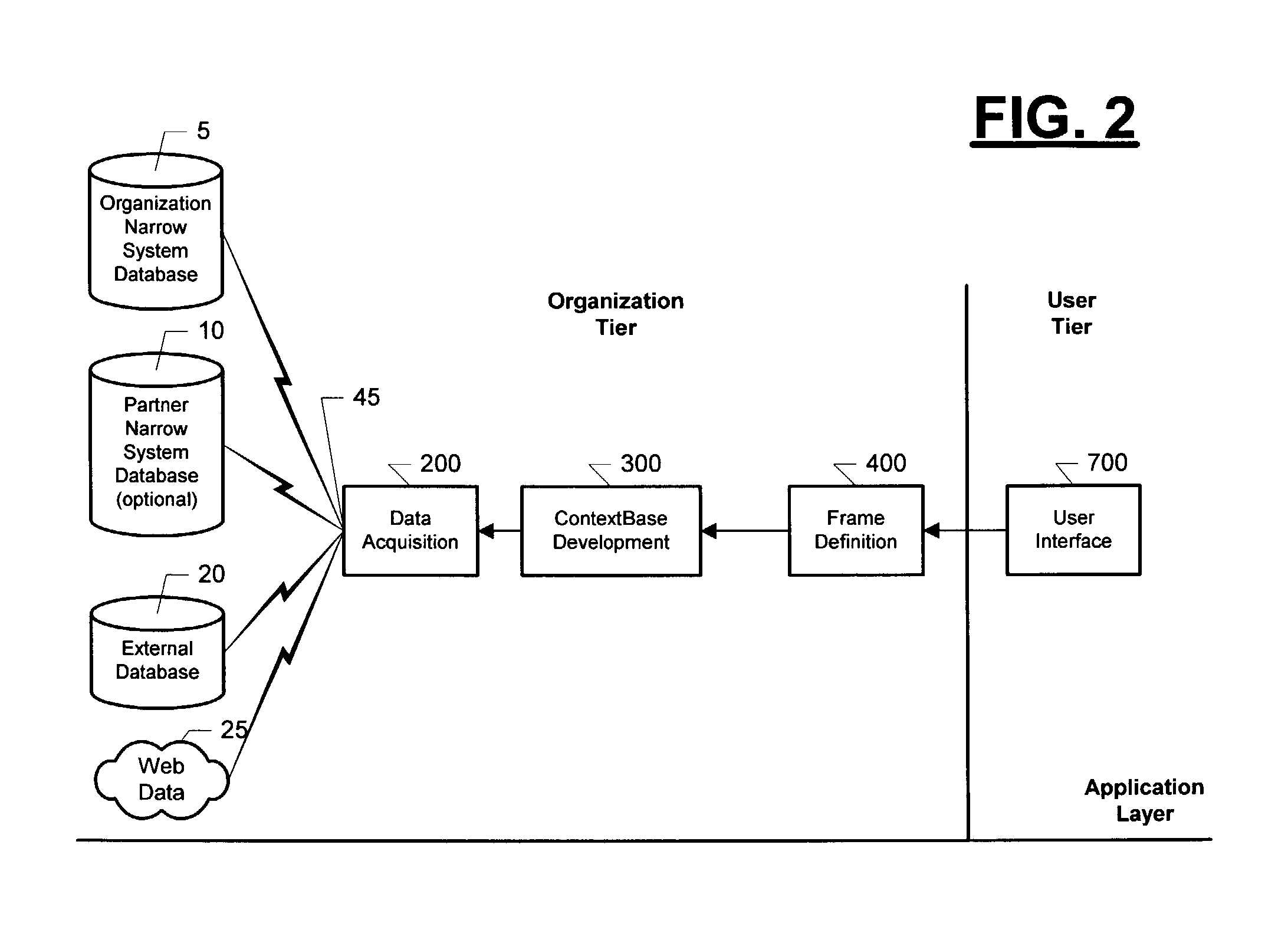

Automated bot development system

ActiveUS7039654B1Increases scale and scopeProlong lifeResourcesSpecial data processing applicationsAnalog robotProgram instruction

An automated system (100) and method for developing Complete Context™ Bots (30) for an organization. After extracting data from existing narrowly focused systems, mission measures and organization levels are defined for one or more organizations. The elements, factors and risks that contribute to mission measure performance by organization level and organization are systematically defined and stored in a ContextBase (60) using up to six context layers. ContextBase (60) information is extracted for specified combinations of context layers, organization levels and organizations as required to produce complete context frames that are used to support simulations of bot performance under a variety of scenarios. The program instructions that will maximize bot performance under the forecast scenarios are identified. After this programming is transferred to the Complete Context™ Bot (30), it is activated.

Owner:XENOGENIC DEV LLC

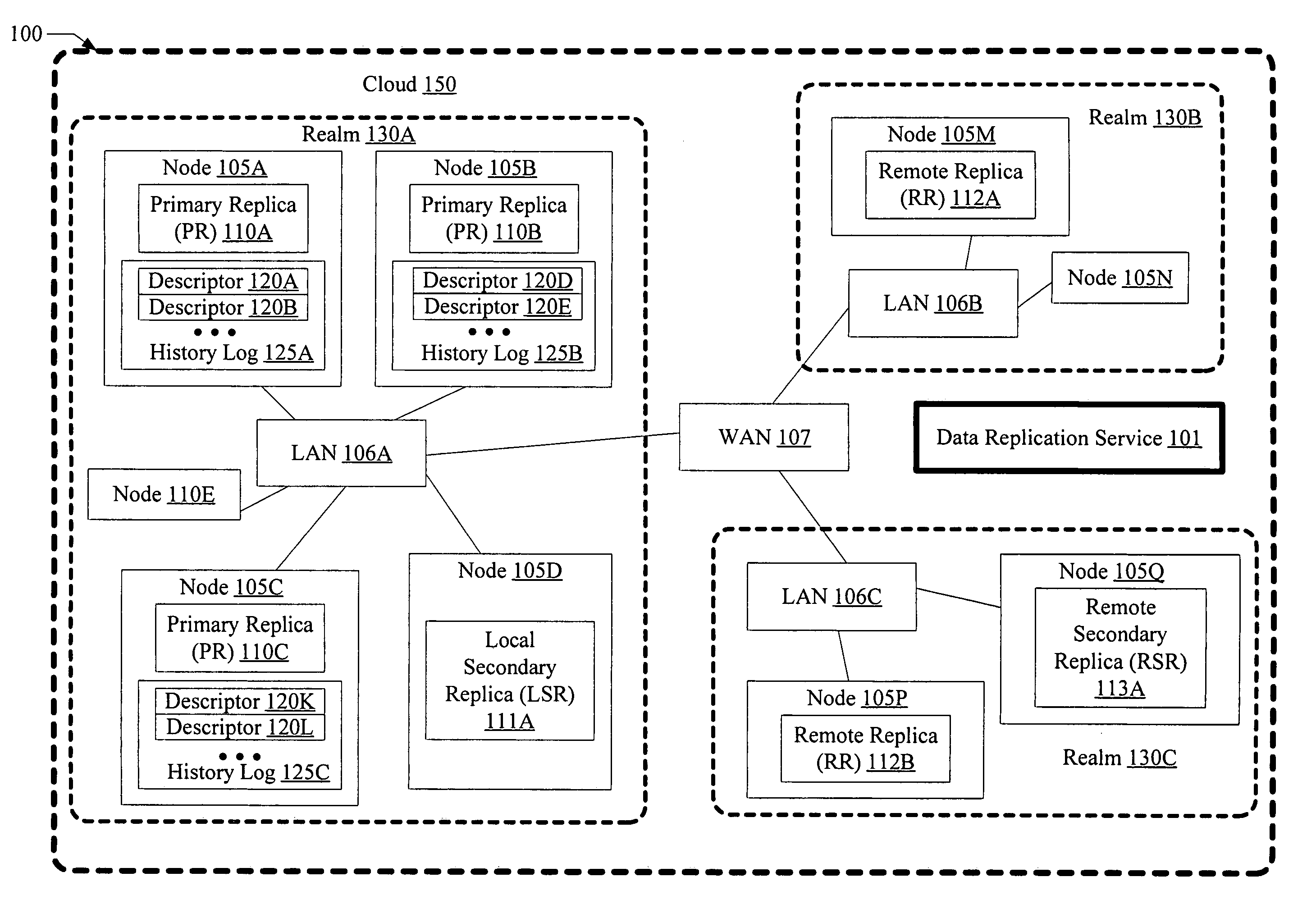

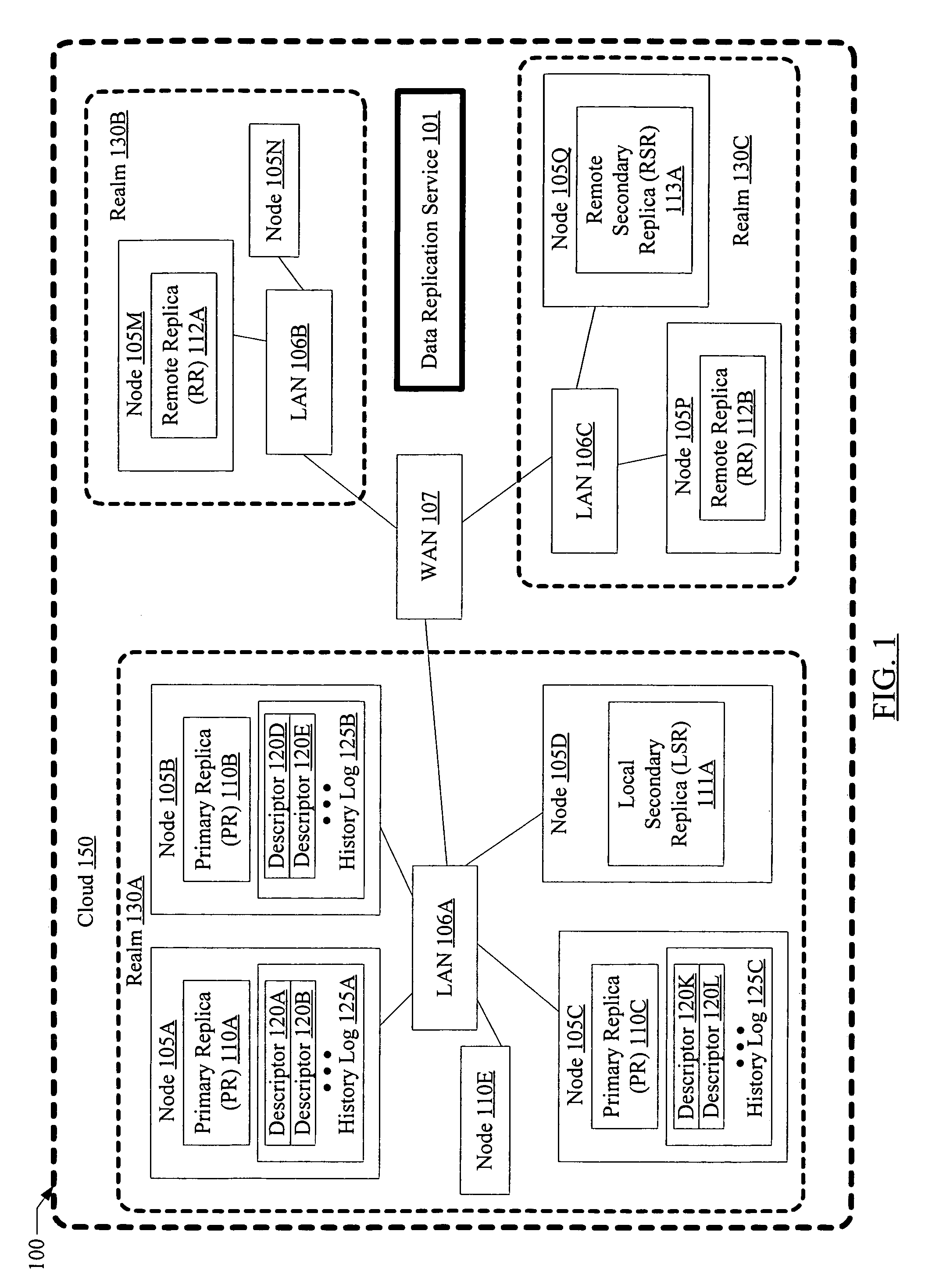

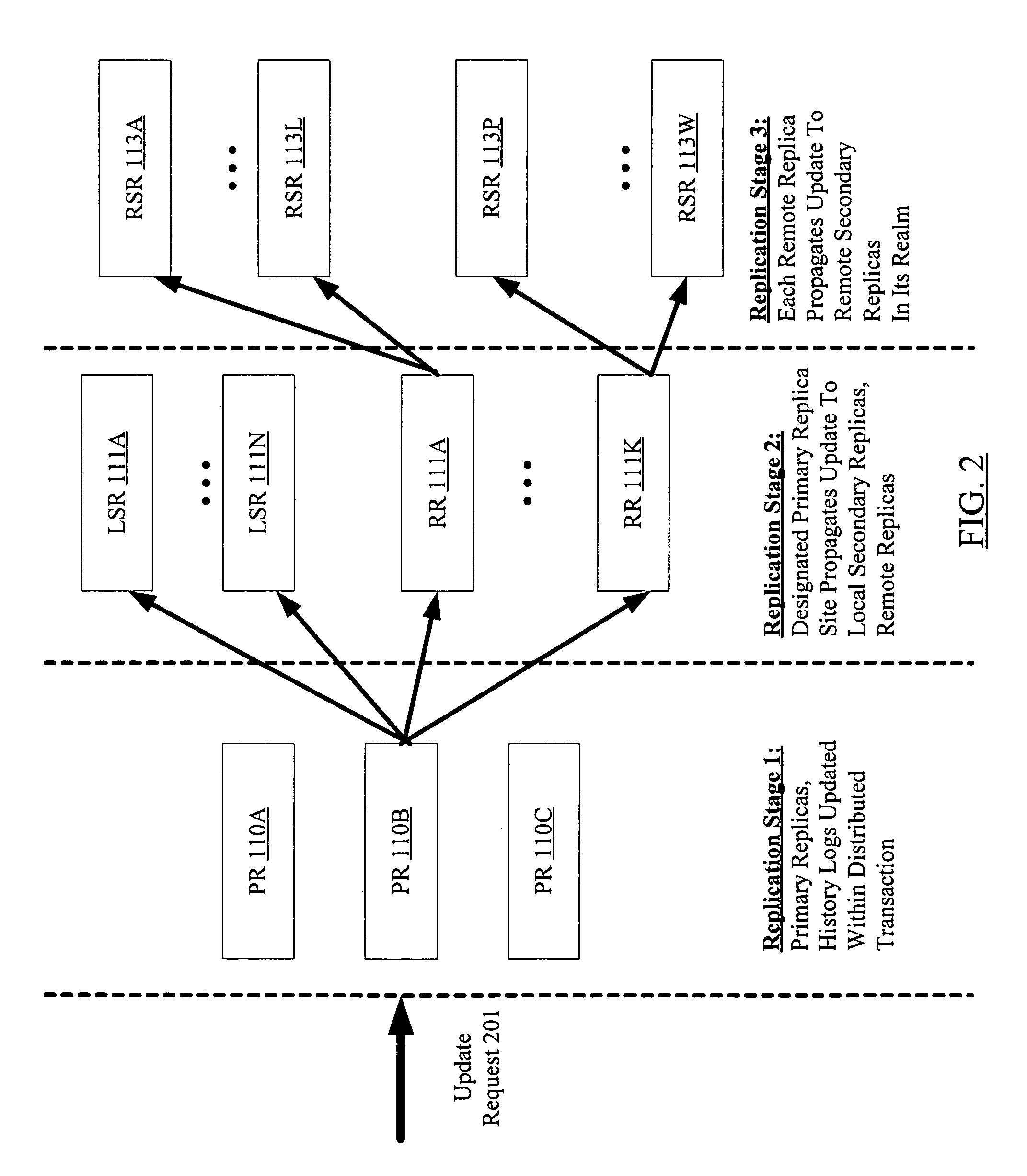

Fault tolerant multi-stage data replication with relaxed coherency guarantees

InactiveUS7653668B1Reduce trafficEasy accessDigital data information retrievalDigital data processing detailsProgram instructionMetadata description

A system for fault tolerant multi-stage data replication with relaxed coherency comprises one or more processors and memory coupled to the processors, where the memory stores program instructions executable by the processors to implement a data replication service. In response to an update request directed at a data object, in a first stage of replication, the data replication service is configured to update respective primary replicas at a plurality of primary replica sites for the data object, and to store metadata descriptors at each of the plurality of primary replica sites. The data replication service is configured to determine whether a notification of the update is to be sent to any other replica sites. In response to identifying such other replica sites, an update notification including contents of a metadata descriptor may be sent to the other replica sites in one or more additional replication stages.

Owner:SYMANTEC OPERATING CORP

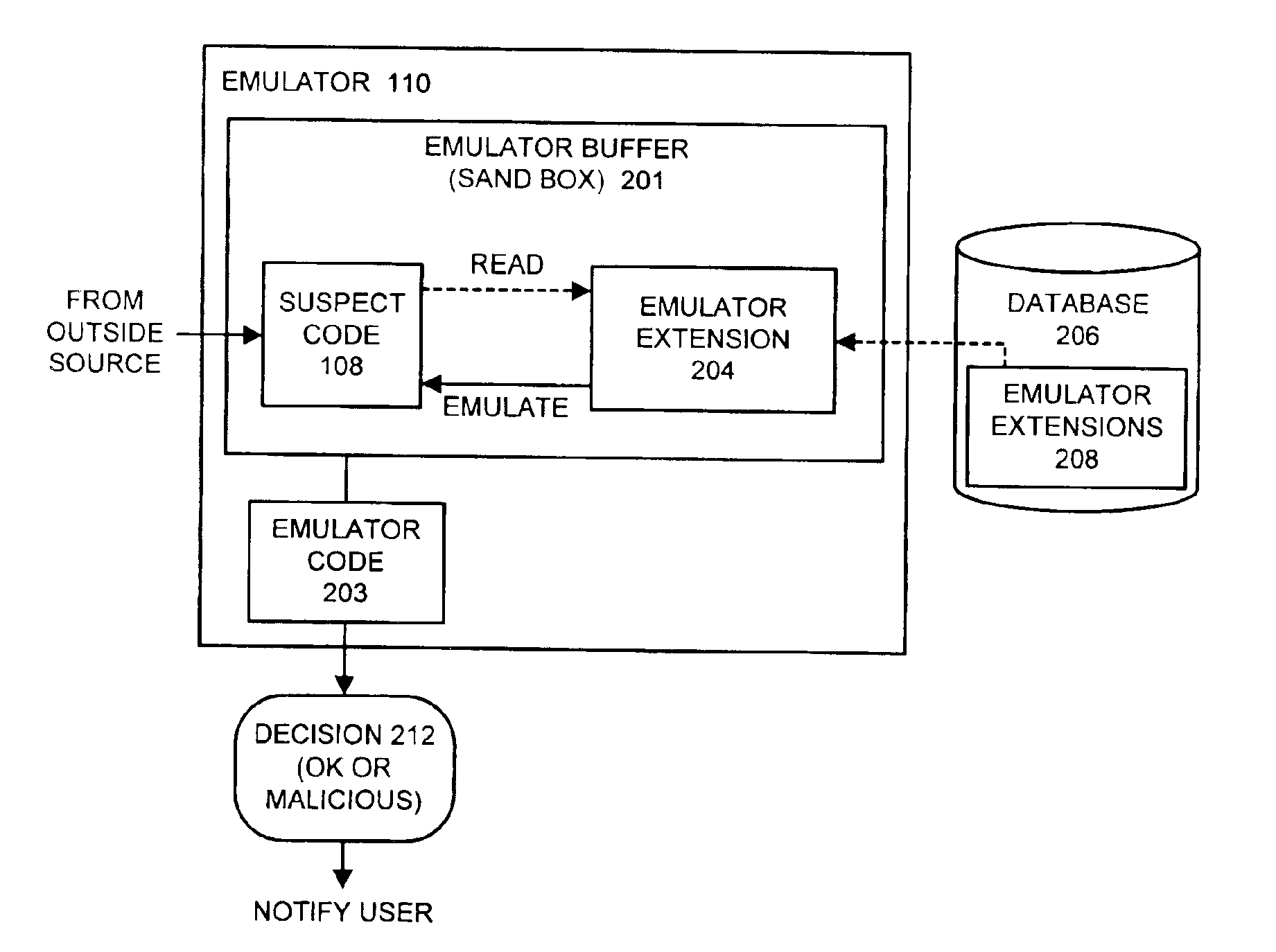

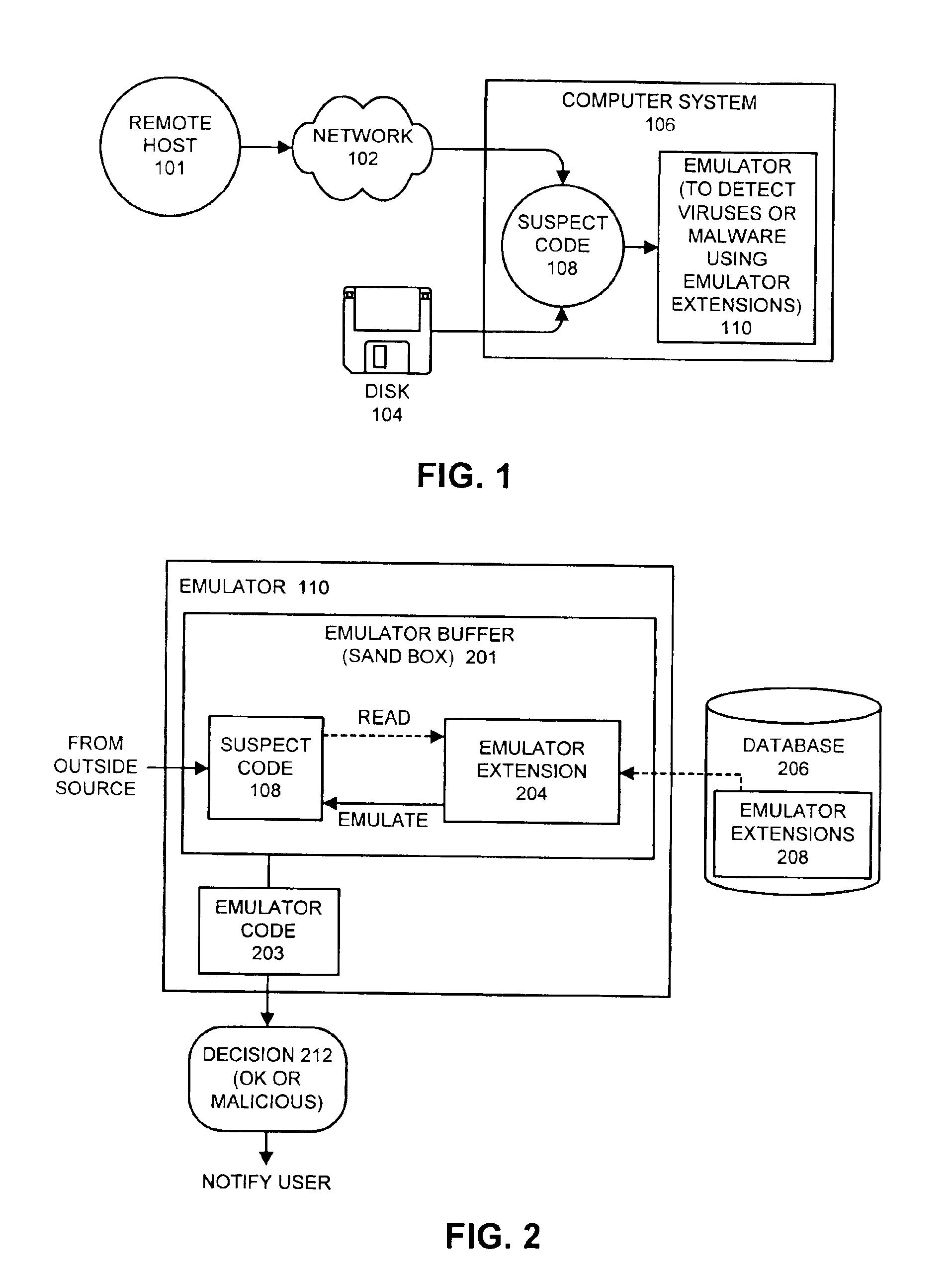

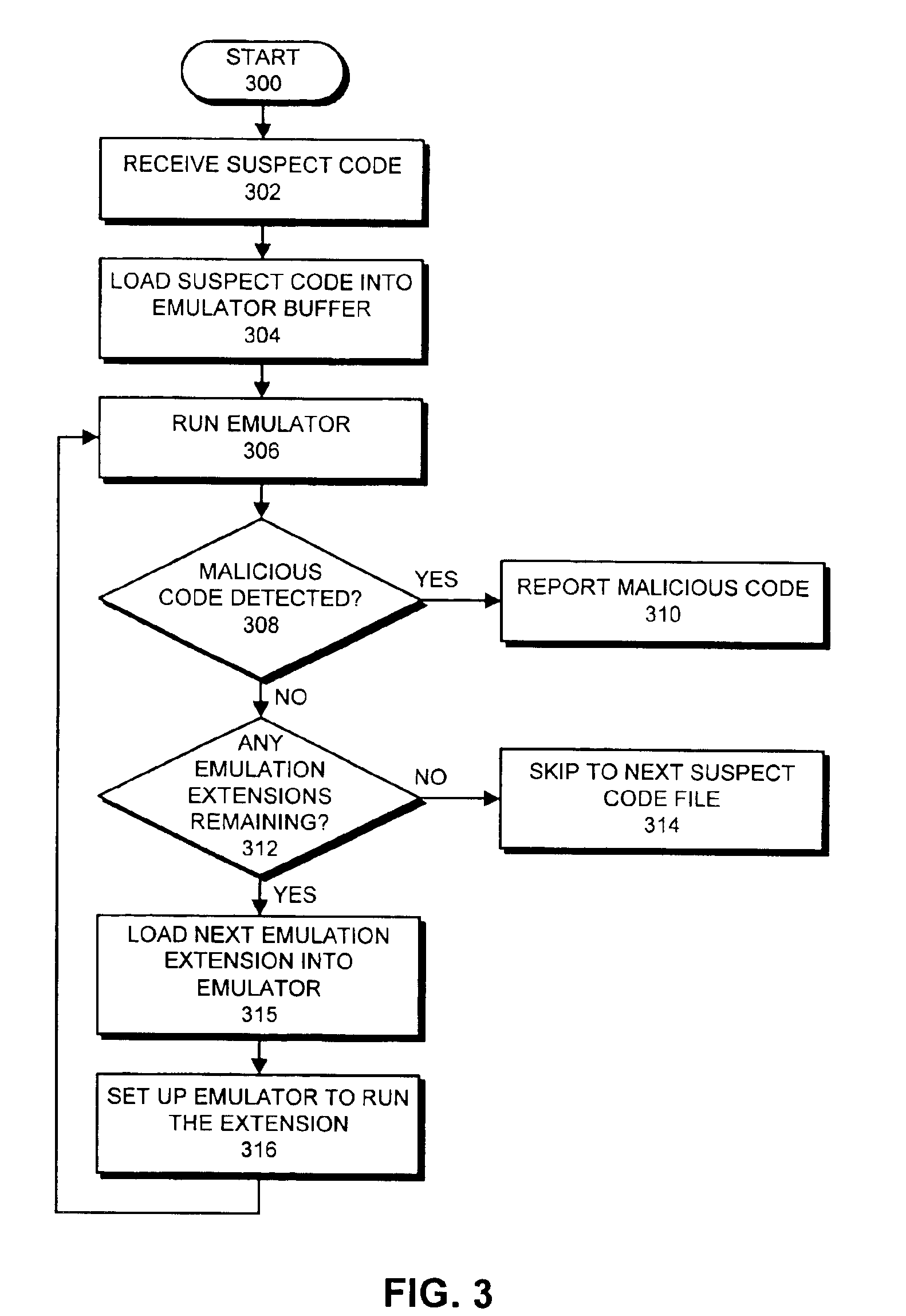

Detecting computer viruses or malicious software by patching instructions into an emulator

InactiveUS6907396B1High simulationPlatform integrity maintainanceTransmissionProgram instructionAnalog computer

One embodiment of the present invention provides a system for emulating computer viruses and / or malicious software that operates by patching additional program instructions into an emulator in order to aid in detecting a computer virus and / or malicious software within suspect code. During operation, the system loads a first emulator extension into the emulator. This first emulator extension includes program instructions that aid in the process of emulating the suspect code in order to detect a computer virus and / or malicious software. The system also loads the suspect code into an emulator buffer. Next, the system performs an emulation using the first emulator extension and the suspect code. This emulation is performed within an insulated environment in a computer system so that the computer system is insulated from malicious actions of the suspect code. During this emulation, the system determines whether the suspect code is likely to exhibit malicious behavior. In one embodiment of the present invention, loading the first emulator extension into the emulator involves loading the first emulator extension into the emulator buffer within the emulator. In this embodiment, performing the emulation involves emulating the program instructions that comprise the first emulator extension.

Owner:MCAFEE LLC

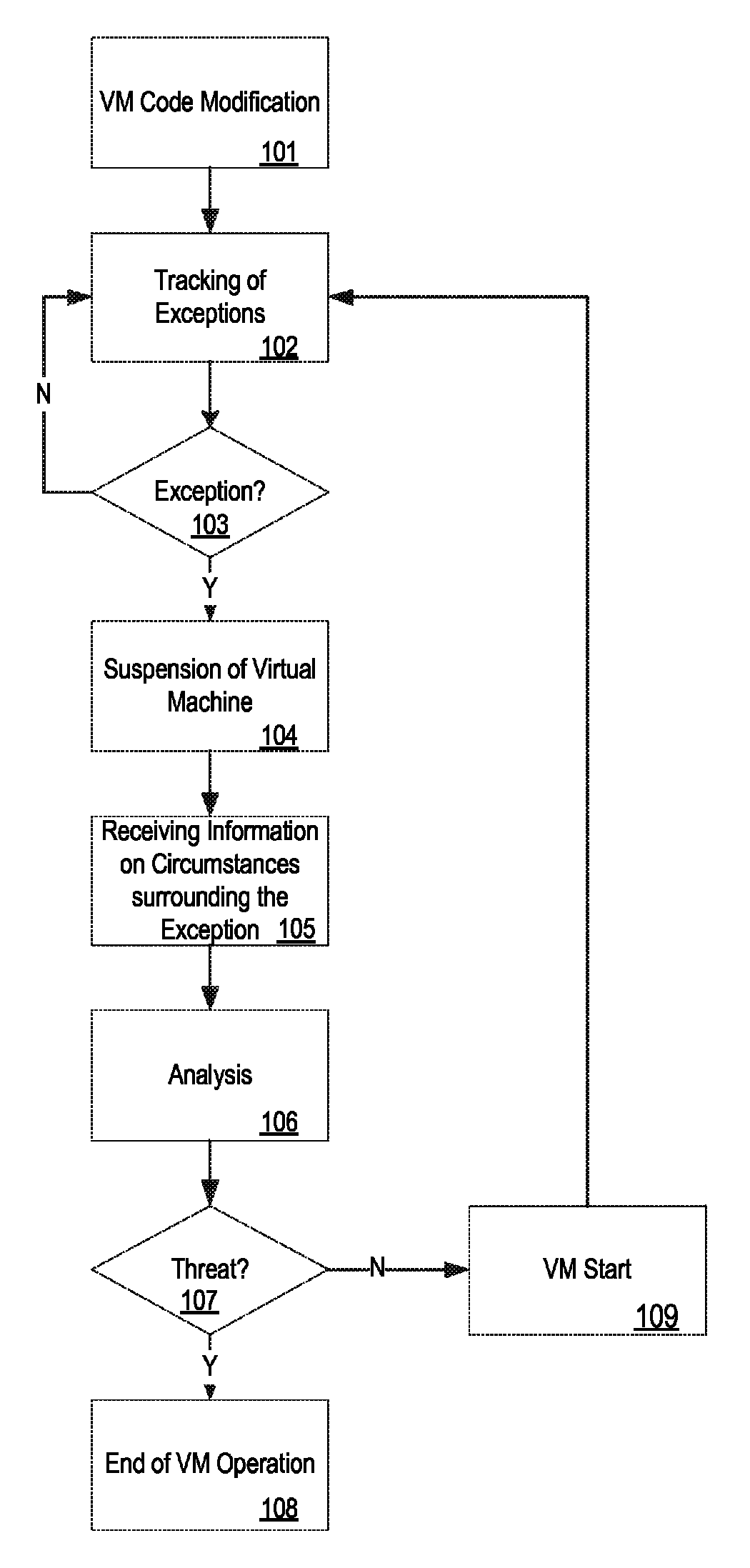

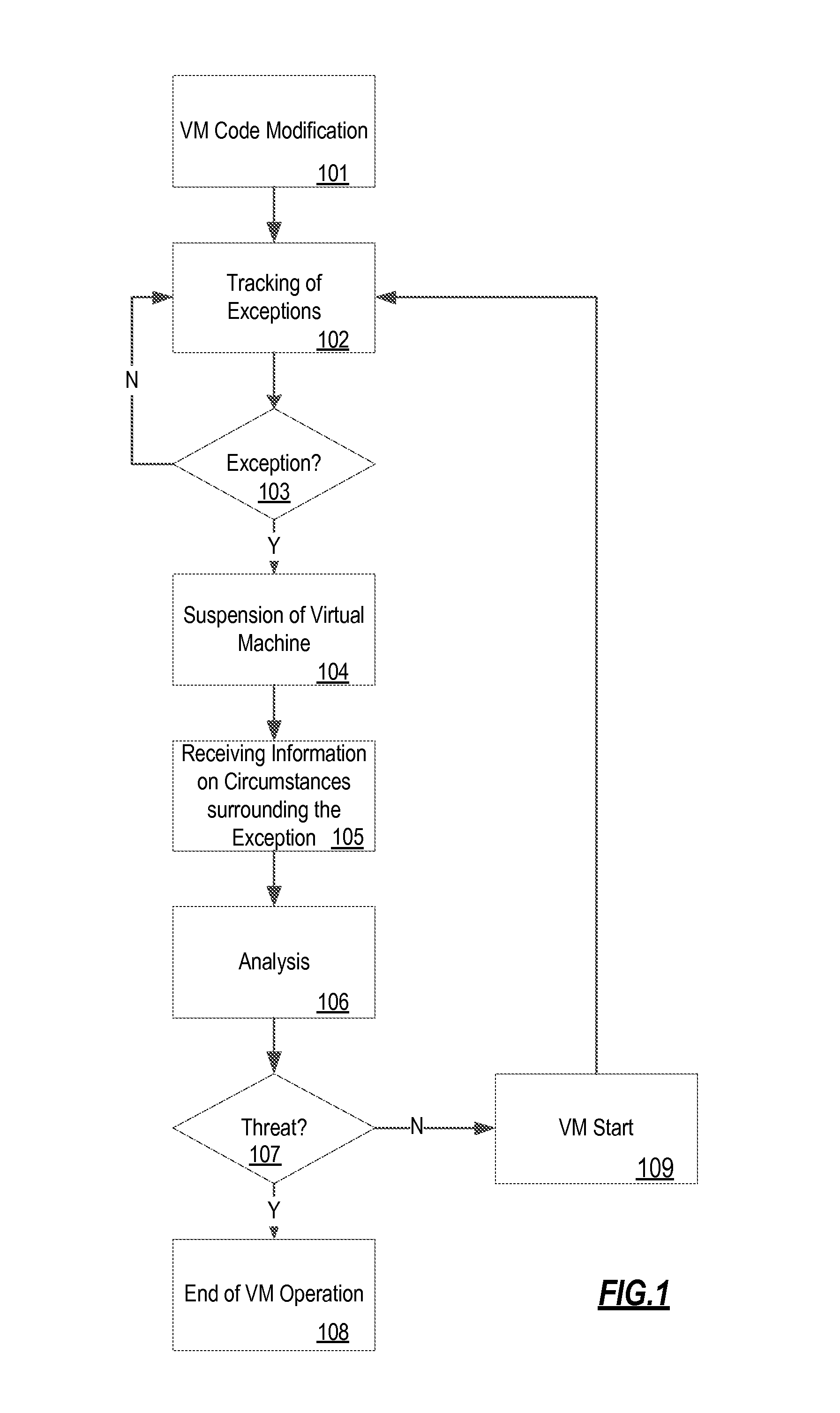

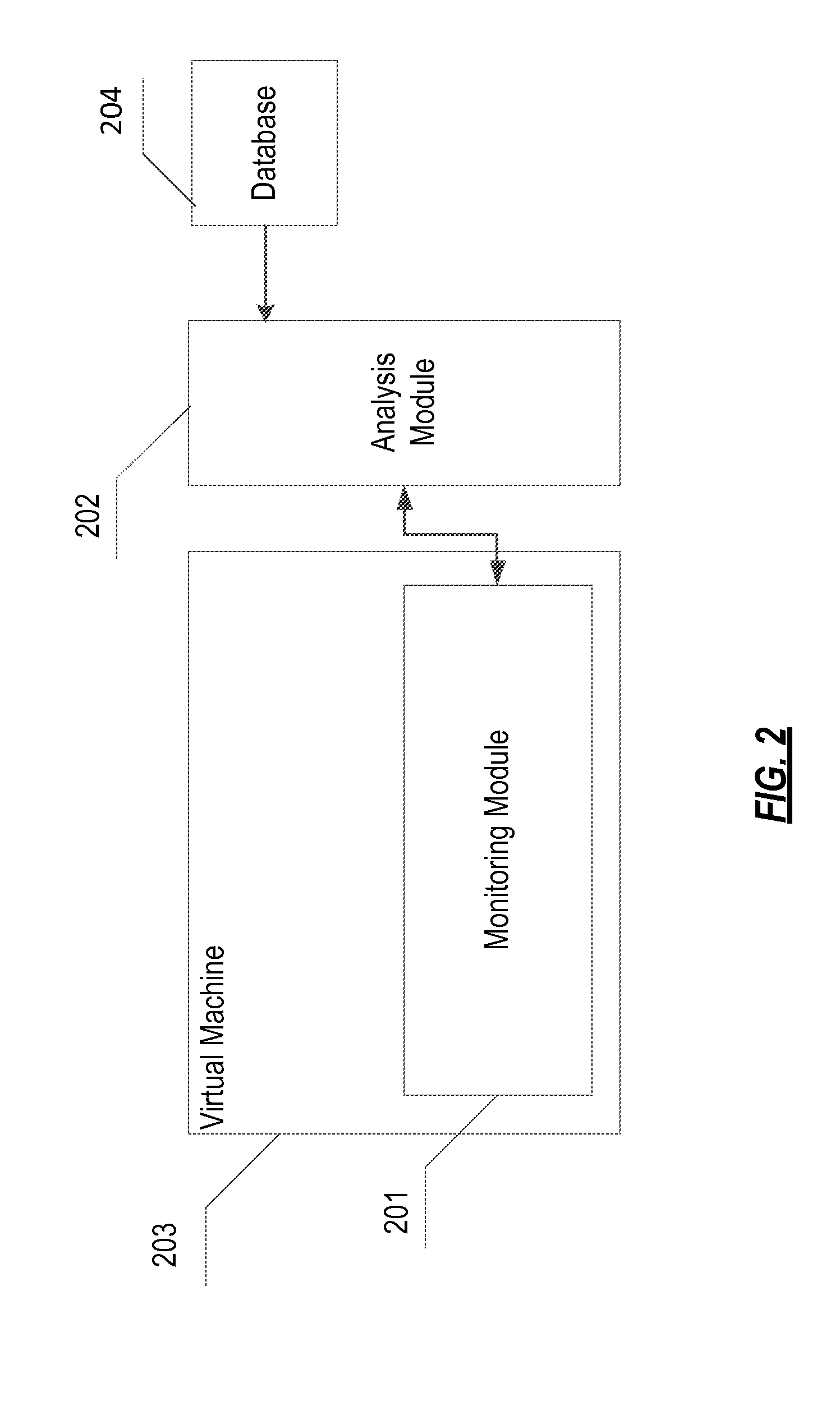

System and method for detecting malicious code executed by virtual machine

Protection against a malicious set of program instructions (e.g., a malicious program) executable by a process virtual machine. The program instructions of process virtual machine are augmented to establish an exception monitoring module within the process virtual machine. When the process virtual machine executes a subject set of program instructions, the exception monitoring module detects a security policy violation exception occurring as a result. In response thereto, the exception monitoring module gathers context information representing circumstances surrounding the occurrence of the exception, and provides the context information for analysis of a presence of malicious code. The exception monitoring module determines, based on a result of the analysis, whether to permit further execution of the subject set of program instructions by the process virtual machine.

Owner:AO KASPERSKY LAB

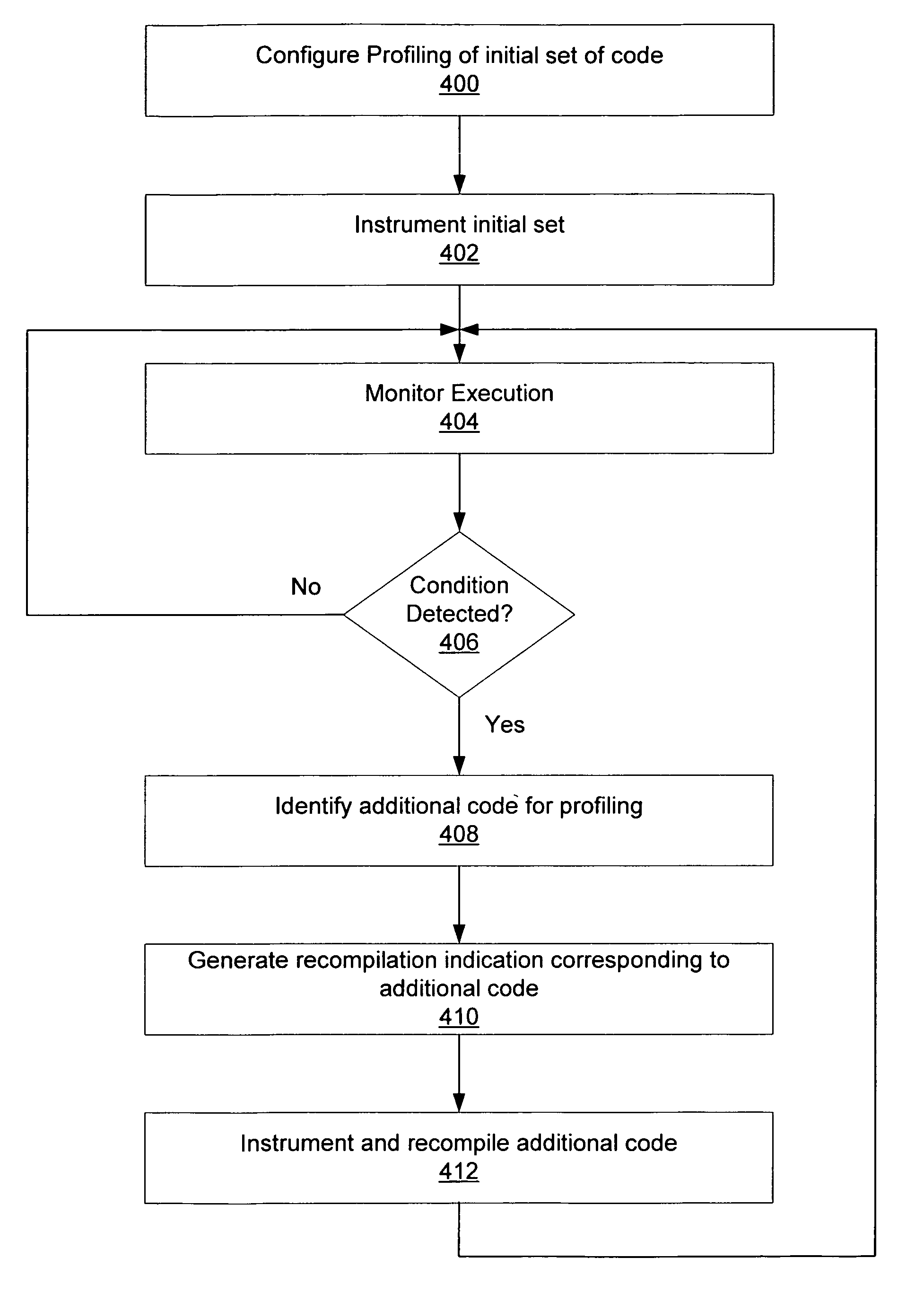

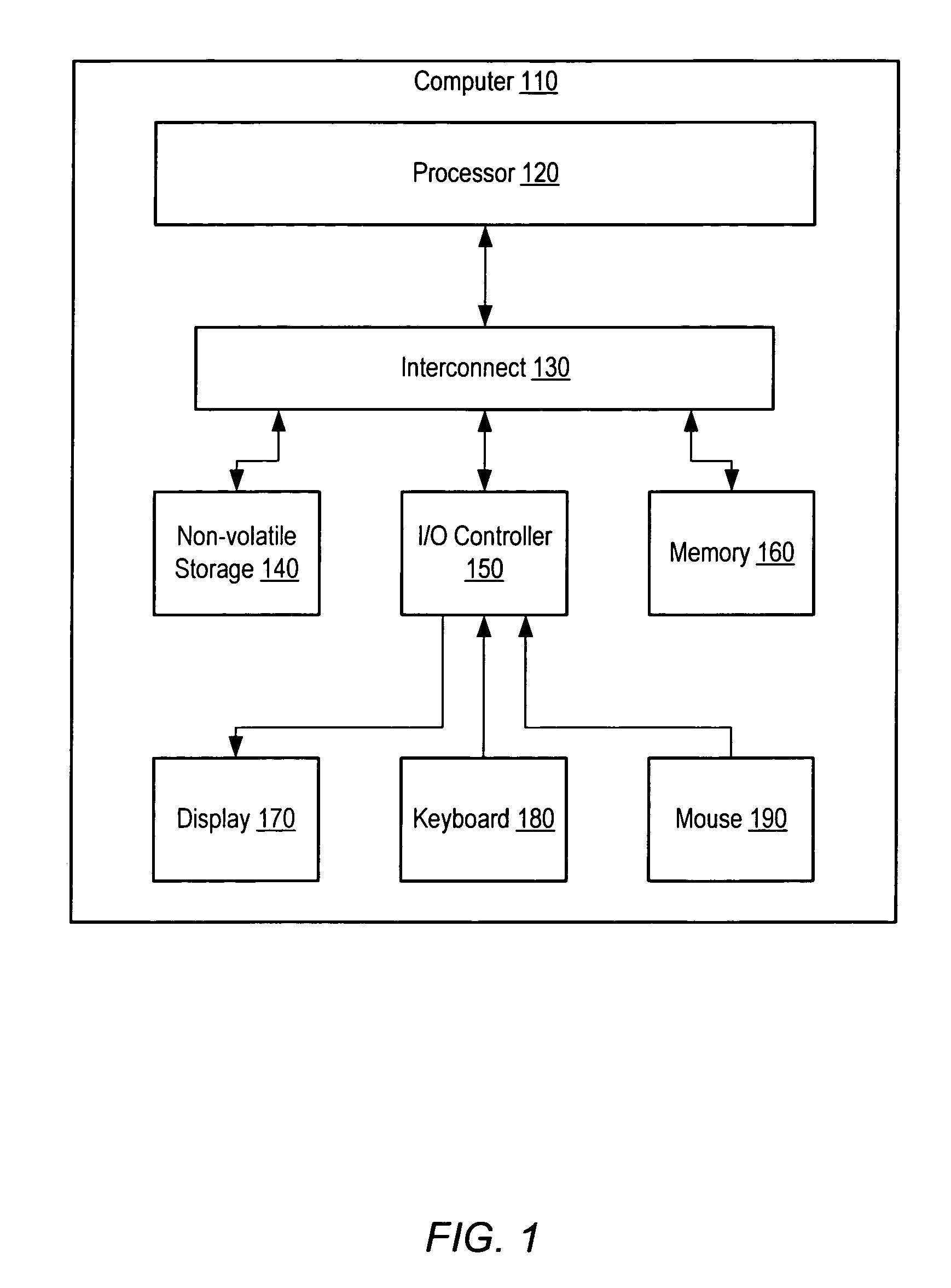

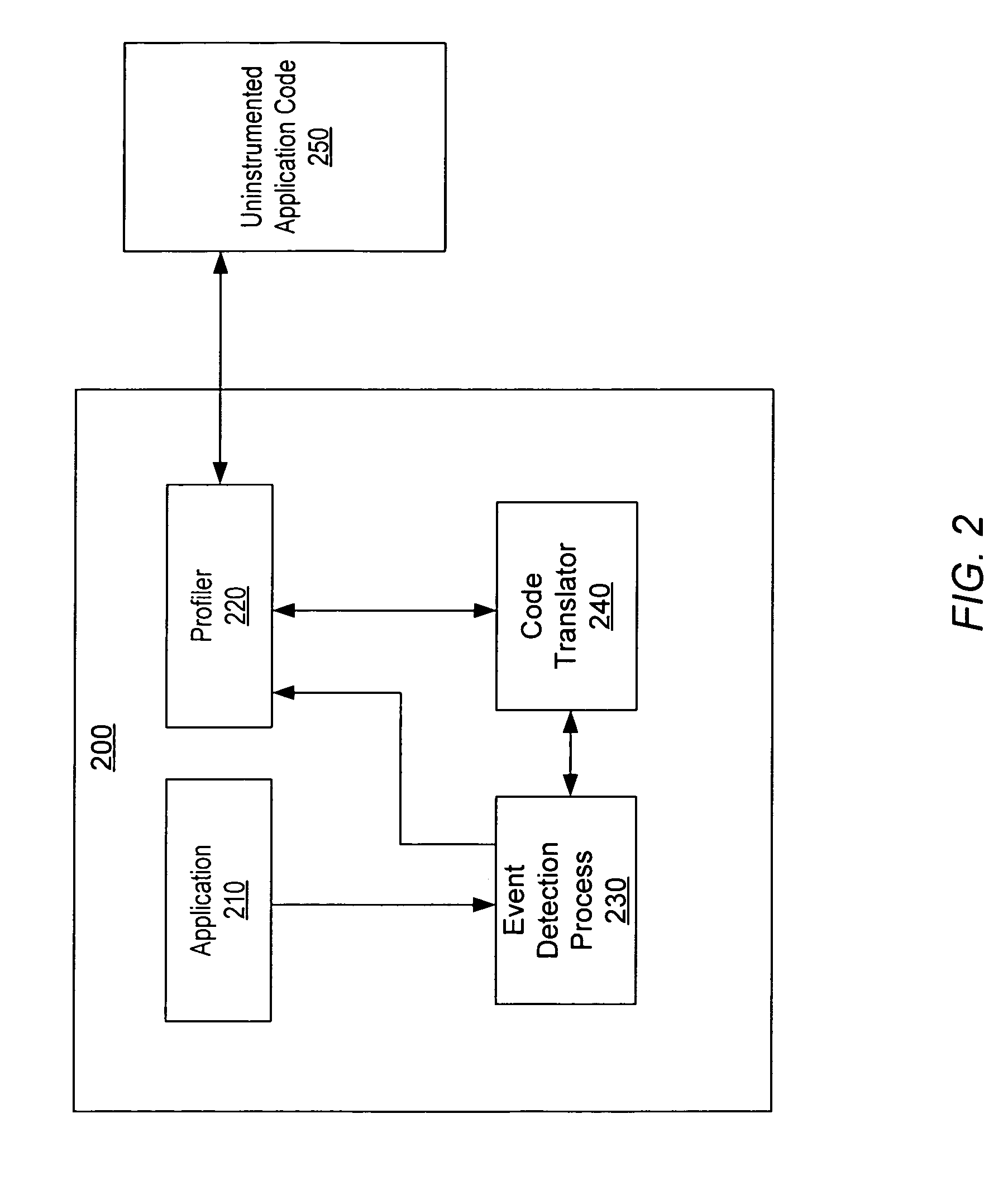

Adaptive instrumentation through dynamic recompilation

ActiveUS8176480B1Long performance latencySoftware engineeringSpecific program execution arrangementsProgram instructionParallel computing

A system and method for instrumenting program instructions. A processing system includes a compiler and a profiler. The profiler is configured to instrument an application by inserting one or more instrumentation instructions in the application. During execution of the application, execution is monitored and a particular condition is detected. Responsive to the condition, a portion of the code which corresponds to the detected condition is identified. A request is conveyed for recompilation of code which corresponds to code. Prior to recompilation of the code, the profiler instruments the portion of code. Execution and monitoring of the execution continue, and instrumentation / recompilation may be repeated. Initially, relatively little of the application code may be instrumented. As execution and monitoring continues, more and more of the application code may be dynamically instrumented during execution.

Owner:SYMANTEC OPERATING CORP

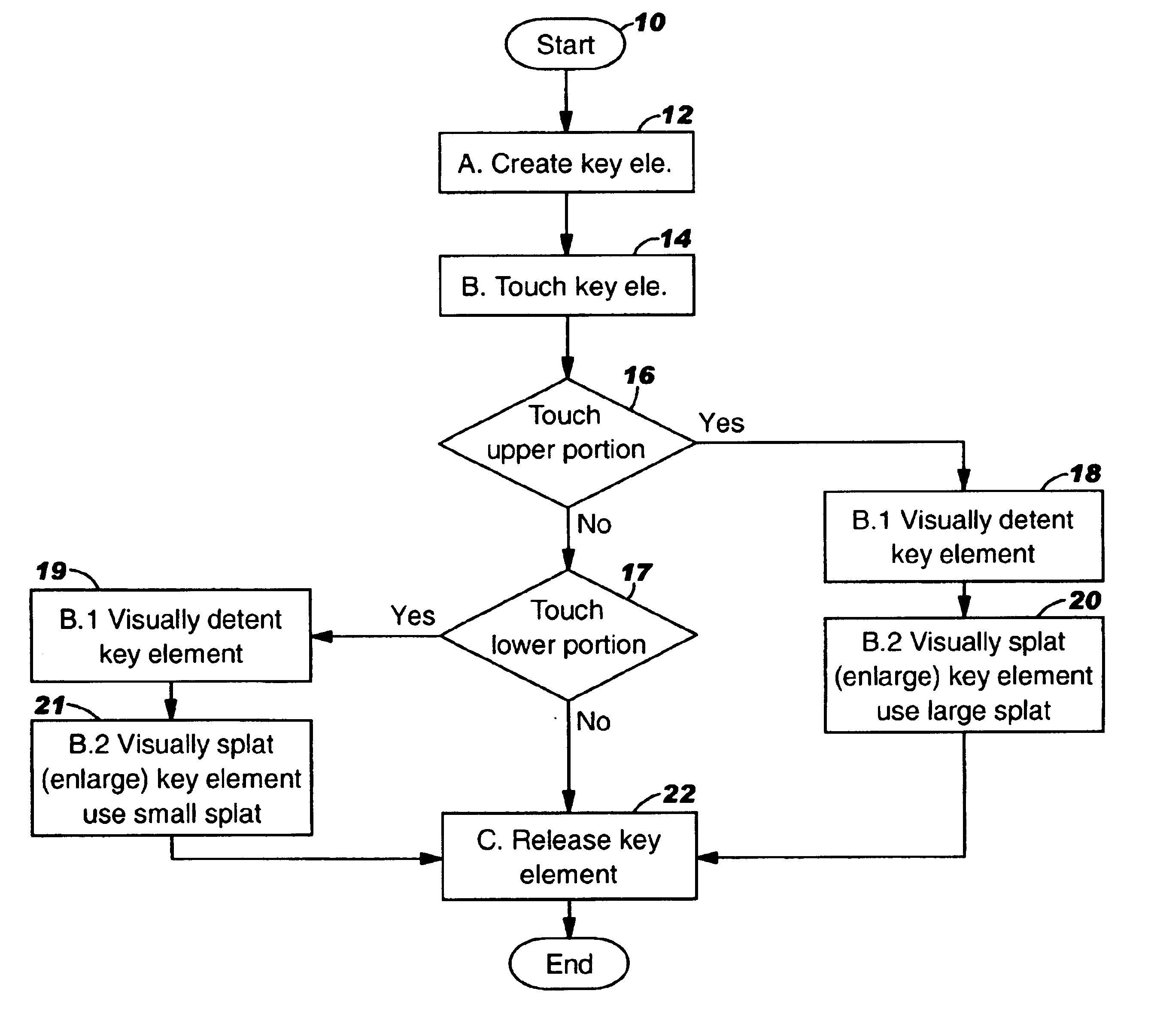

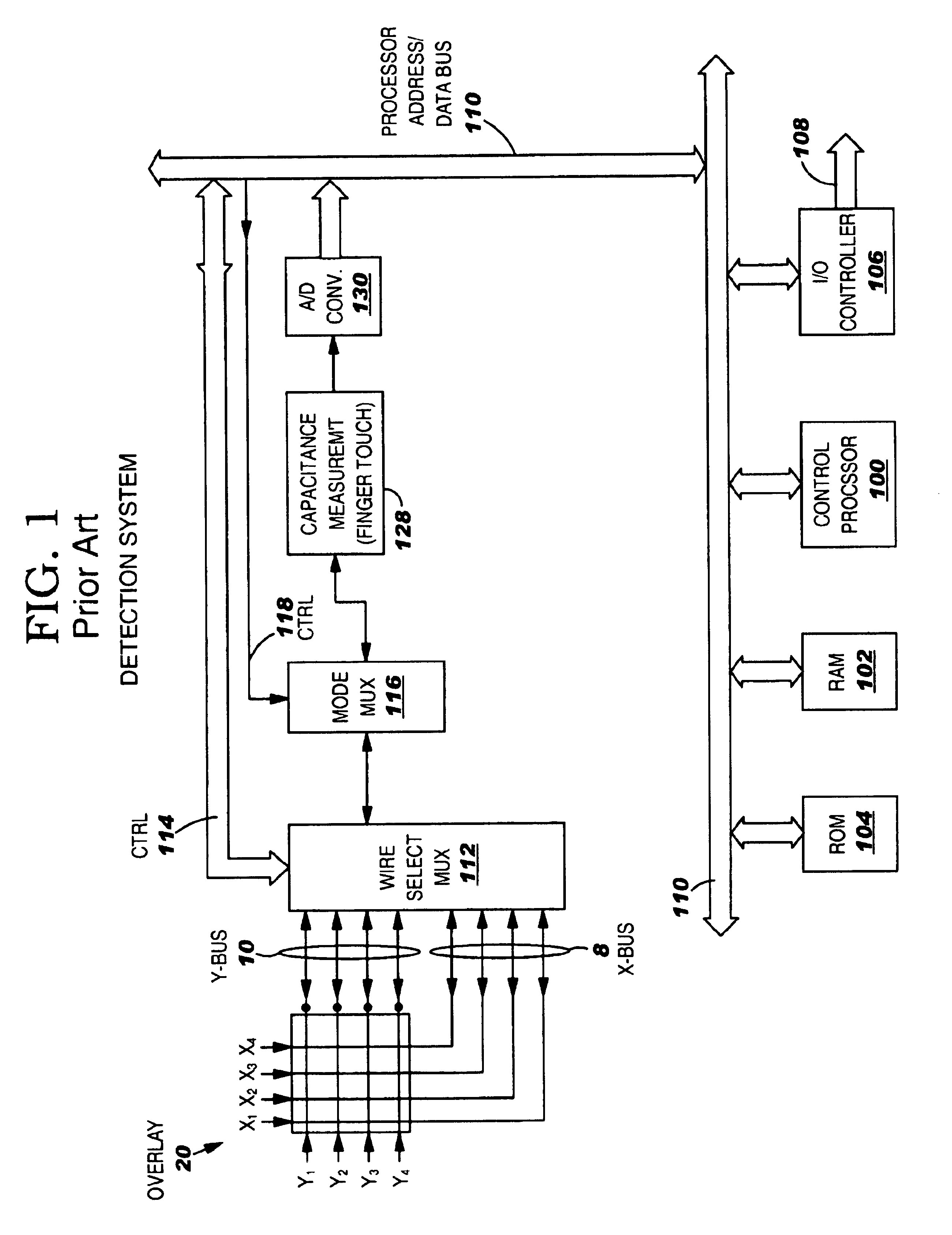

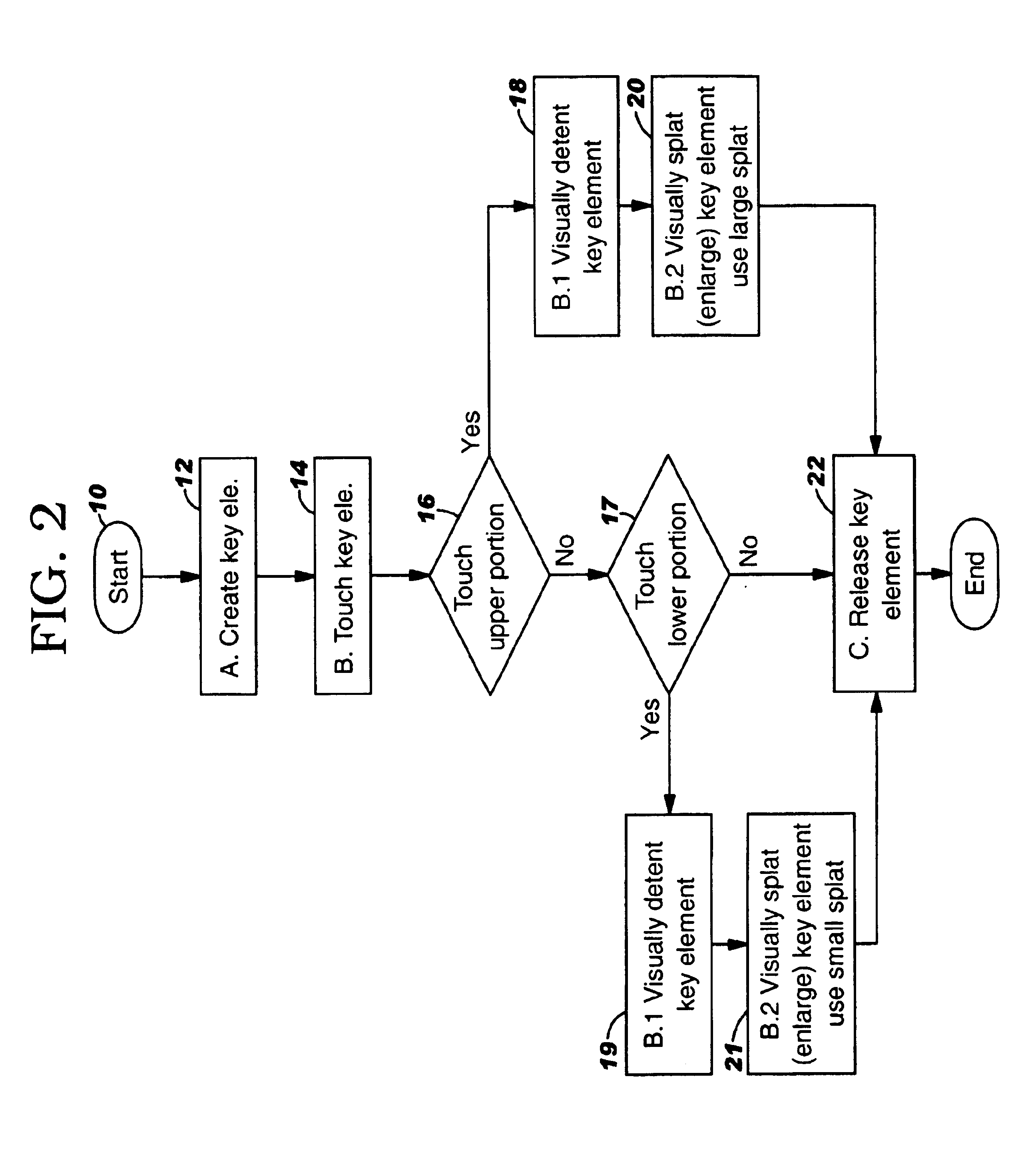

Touch sensitive apparatus and method for improved visual feedback

InactiveUS6803905B1Easy to FeedbackImprove perceptionInput/output for user-computer interactionCathode-ray tube indicatorsGraphicsTouch Perception

A touch sensitive apparatus and method of operation to improve visual feedback and visual perception of tactile input to an operator. The apparatus includes a touch screen device or display having a touch overlay, a processor and stored program instructions in a memory in which a three-dimensional graphical image, such as a key element, is created in the apparatus and shown on the display as an input device or keypad to the processor. Each key element includes a beveled surface surrounding a flat surface. When a displayed key element is touched by a probe, such as a finger, the screen area about the displayed key element and the finger, visually enlarges or "splats" confirming the selection of the particular key. Concomitantly or simultaneously, the key element detents or depresses within the key pad, changes color and bevel size further verifying the key selection to the operator thereby creating a sense of key movement and visual perception of tactile input to the operator aiding in the operation of the key pad. The simultaneous visual key enlargement, visual detenting and change in key color and bevel size upon key selection in a touch sensitive apparatus improves the feedback to the operator in the selection and confirmation of a key element actuated by the operator.

Owner:IBM CORP

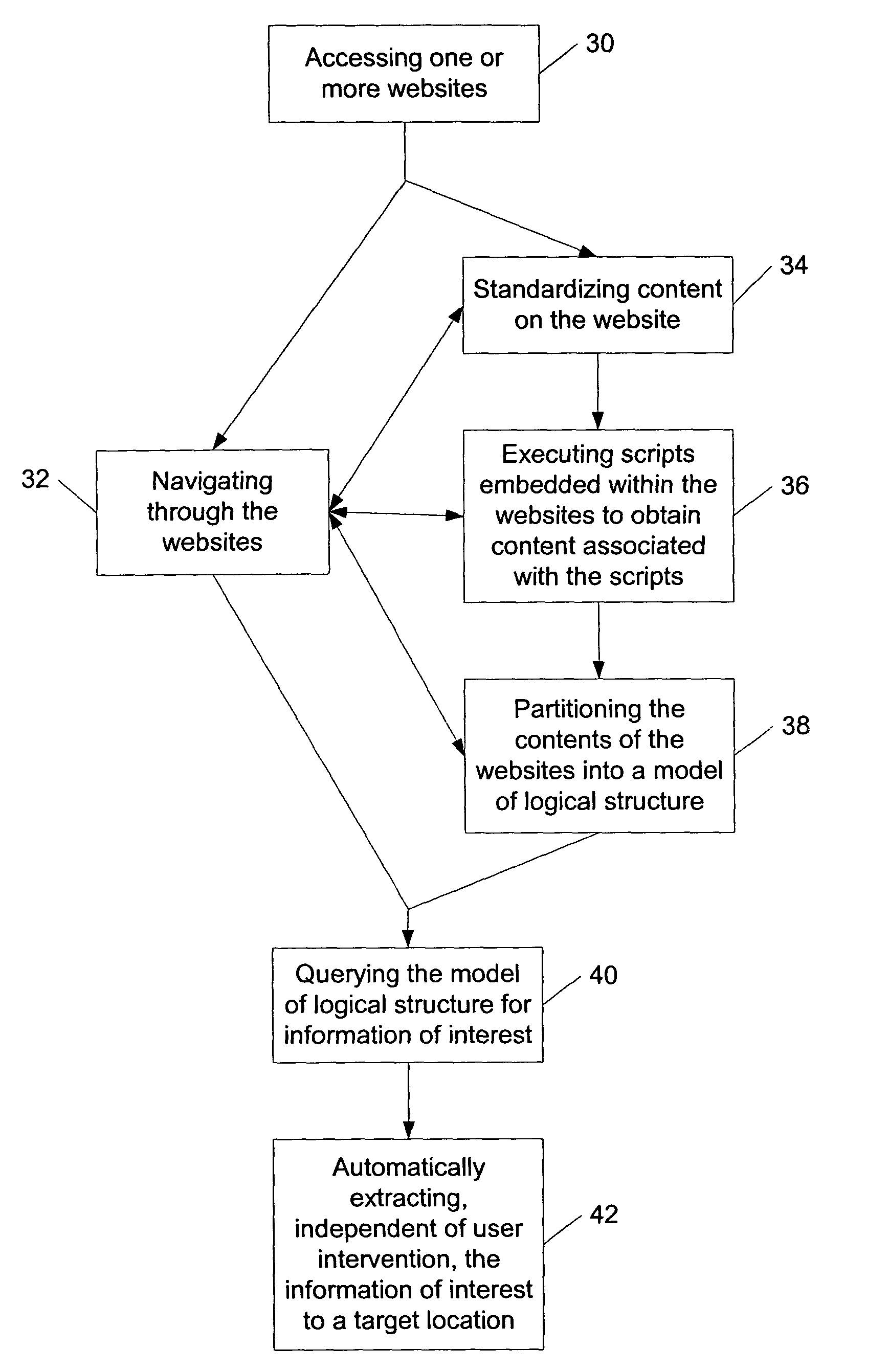

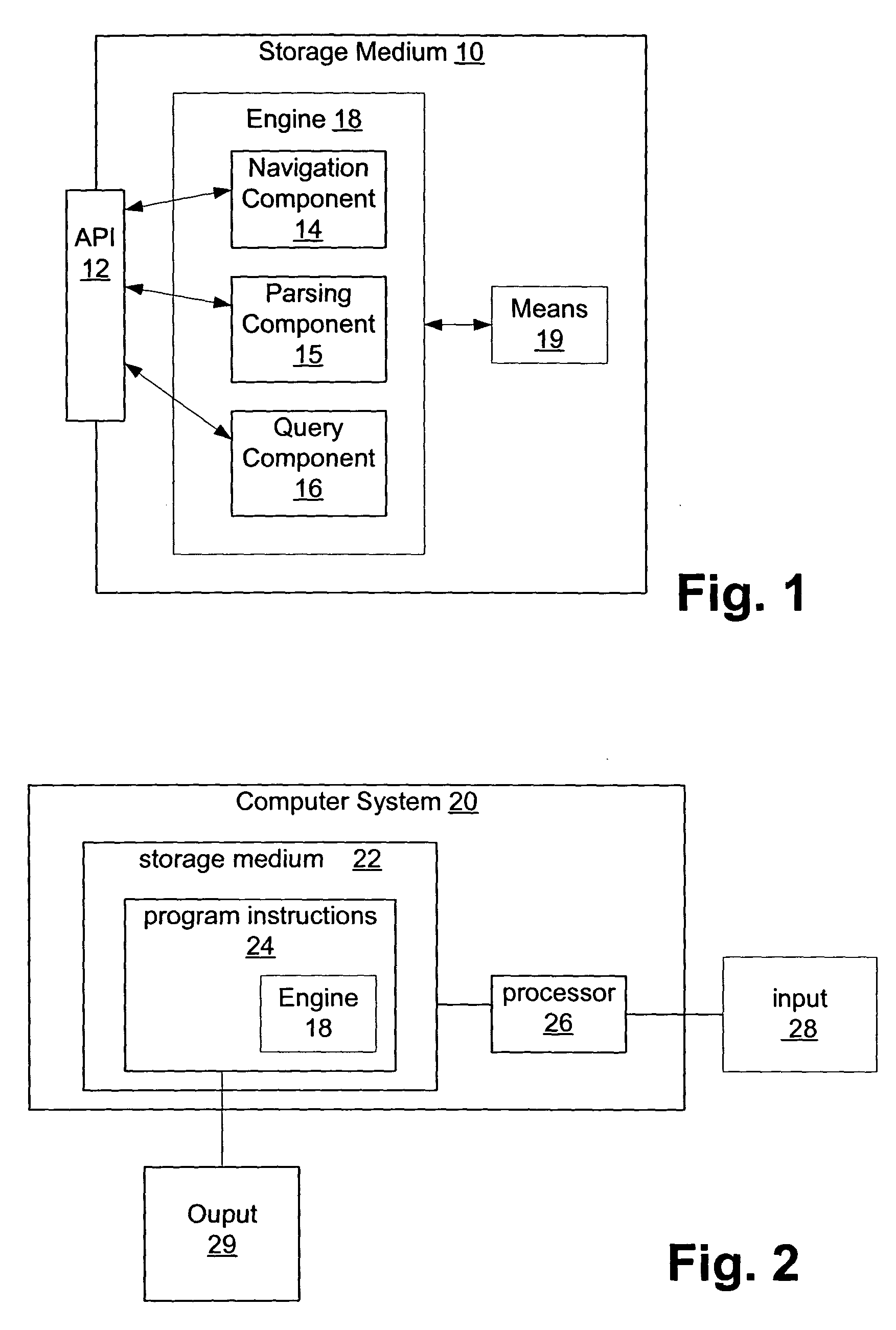

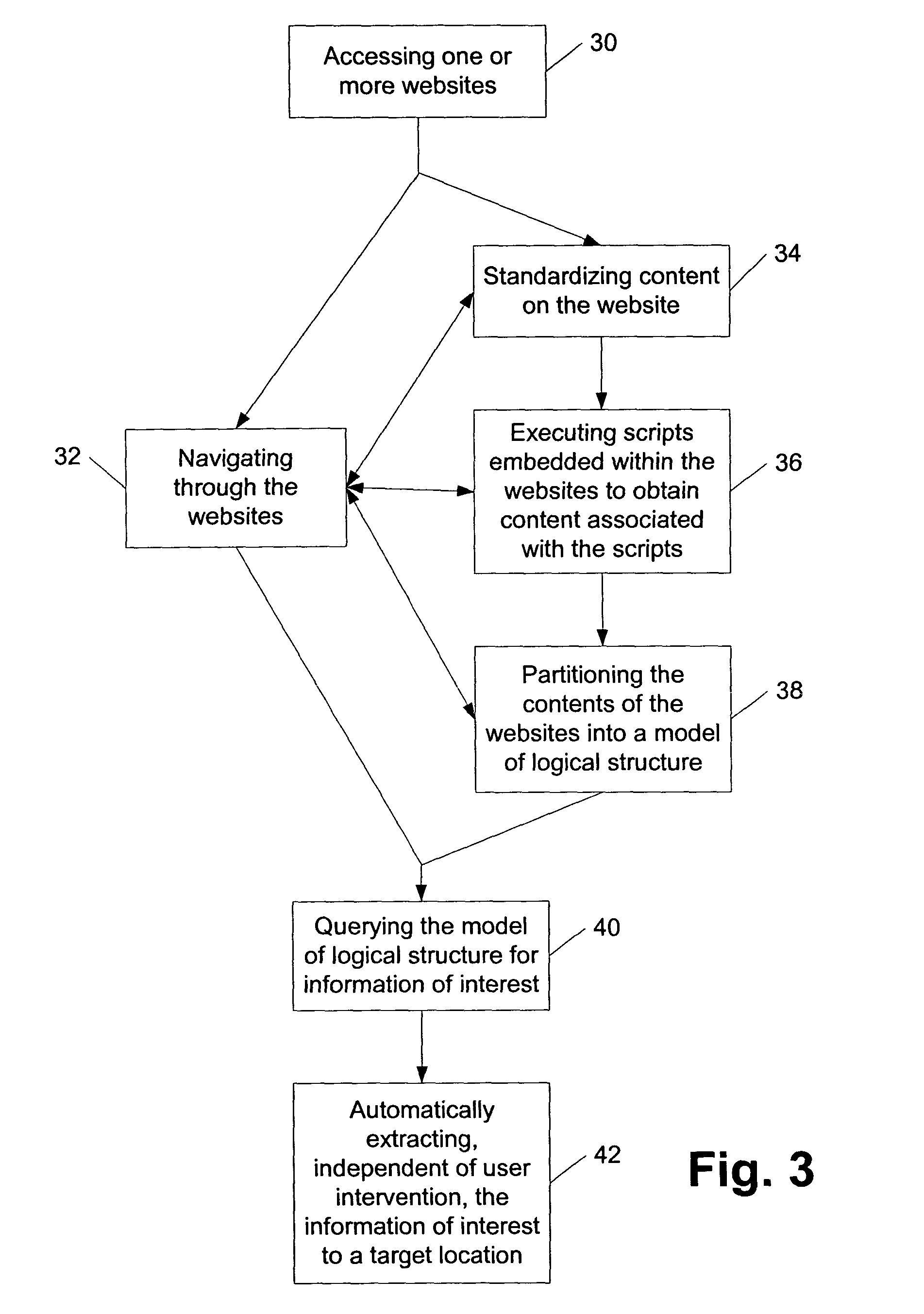

Automated world wide web navigation and content extraction

ActiveUS7725875B2Quick searchInformation wideDigital data processing detailsMultiple digital computer combinationsWeb siteWeb navigation

Storage mediums and a computer-implemented method for automating web navigation and content extraction are provided. In particular, a storage medium with program components which are executable through a common application program interface and are utilizable by a developer to write programming instructions is provided. In some cases, the storage medium may include a program component for adaptively navigating through one or more websites and another program component for extracting scripted content from the one or more websites. In addition or alternatively, the storage medium may include a program component for standardizing content on a web page. In some cases, the storage medium may be configured to allow a user to include XPath query language in program instructions written from the storage medium. A storage medium comprising program instructions executable using a processor for performing such functions and a computer-implemented method employing such processes are also provided herein.

Owner:ACTIAN CORP

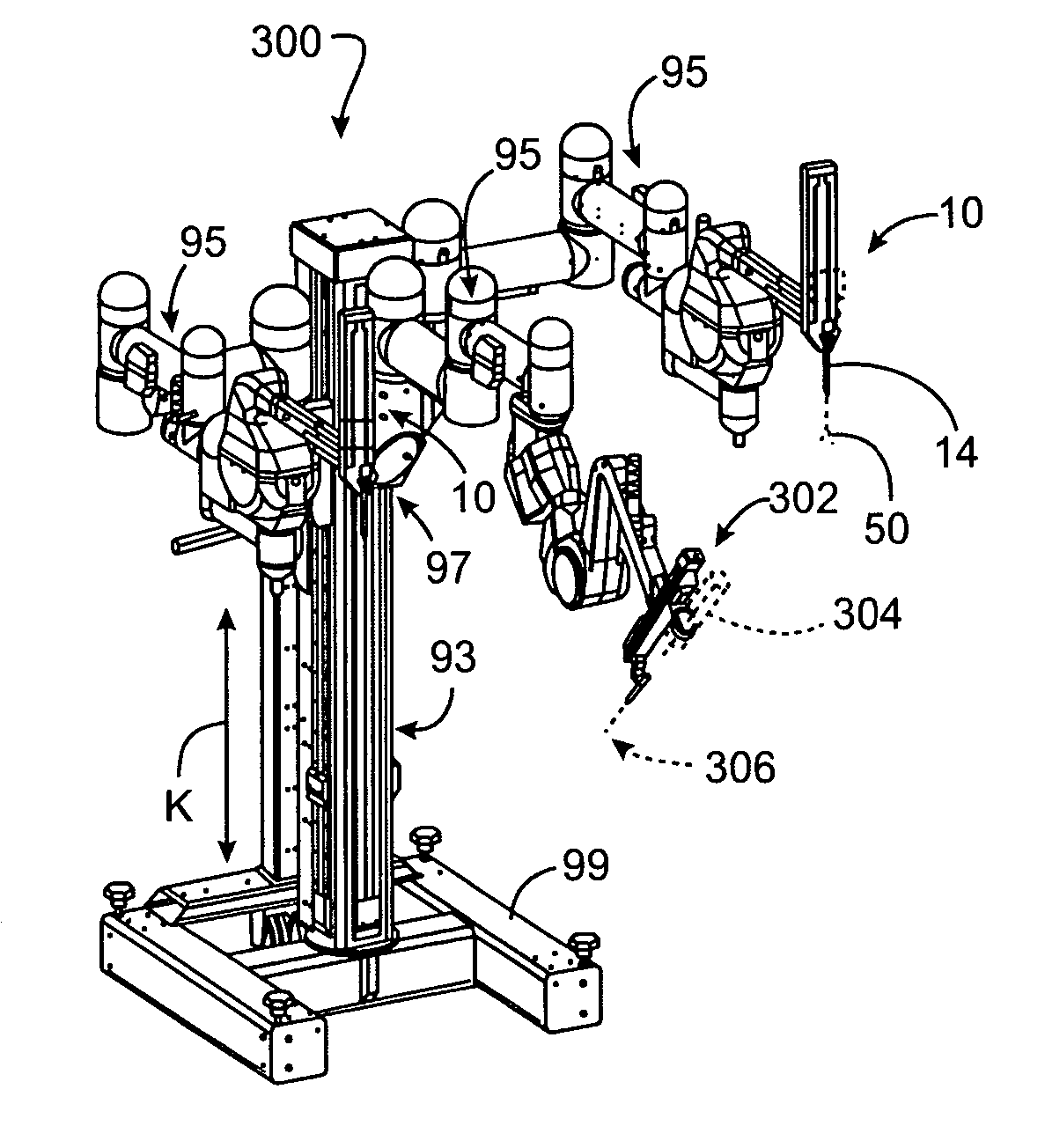

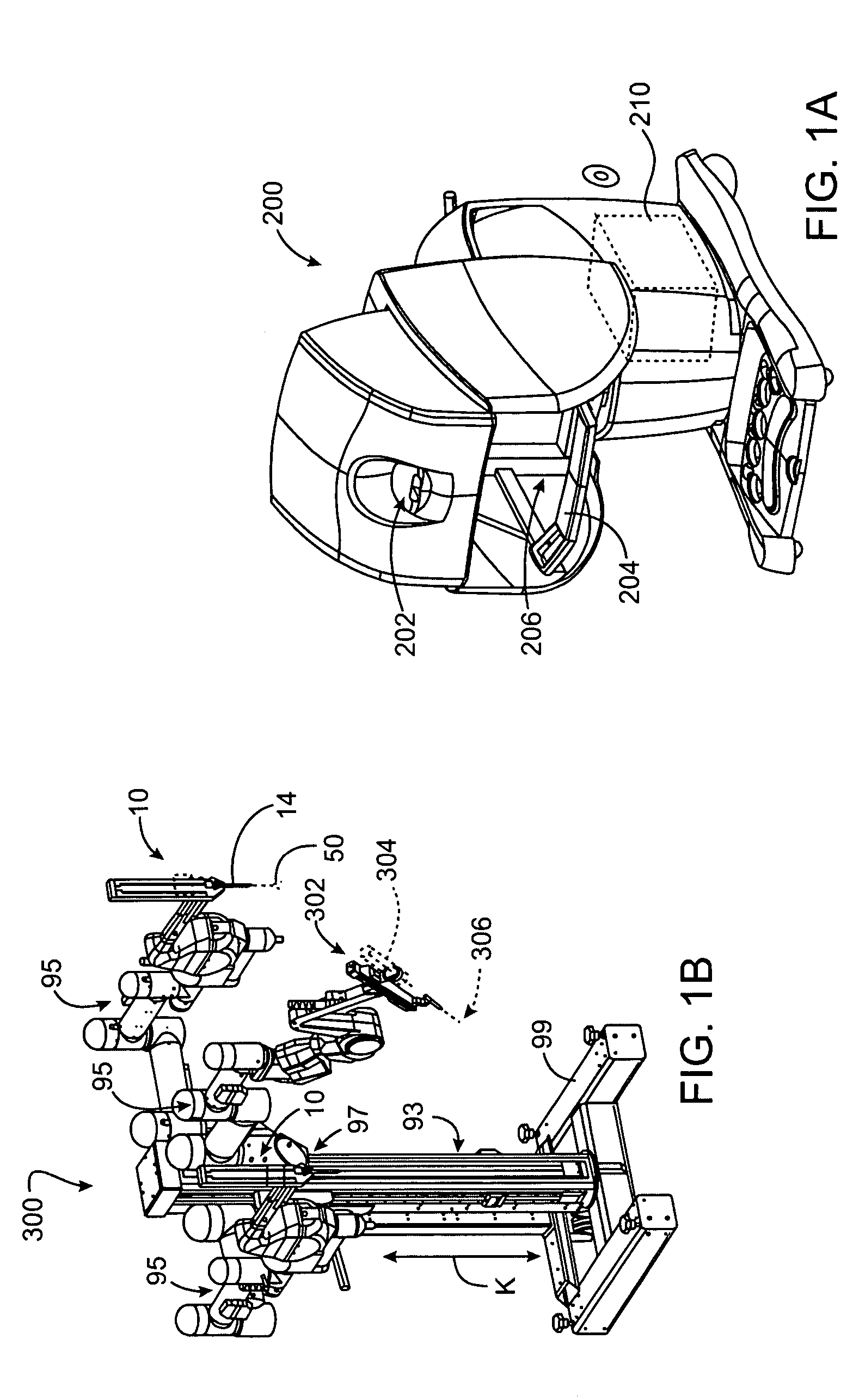

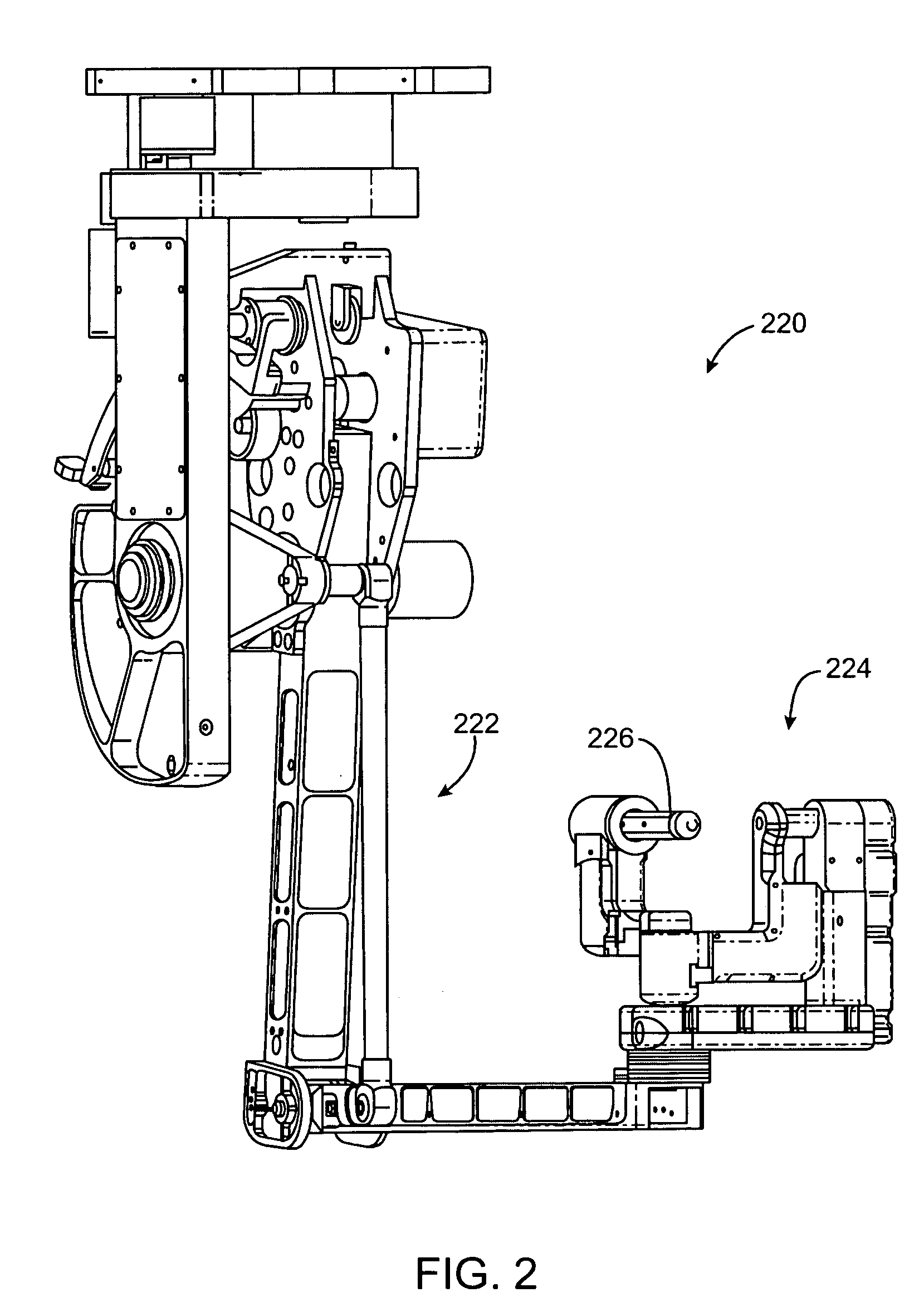

Tool memory-based software upgrades for robotic surgery

Robotic devices, systems, and methods for use in robotic surgery and other robotic applications, and / or medical instrument devices, systems, and methods includes both a reusable processor and a limited-use robotic tool or medical treatment probe. A memory the limited-use component includes machine readable code with data and / or programming instructions to be implemented by the processor. Programming of the processor can be updated by shipping of new data once downloaded by the processor from a component, subsequent components can take advantage of the updated processor without repeated downloading.

Owner:INTUITIVE SURGICAL OPERATIONS INC

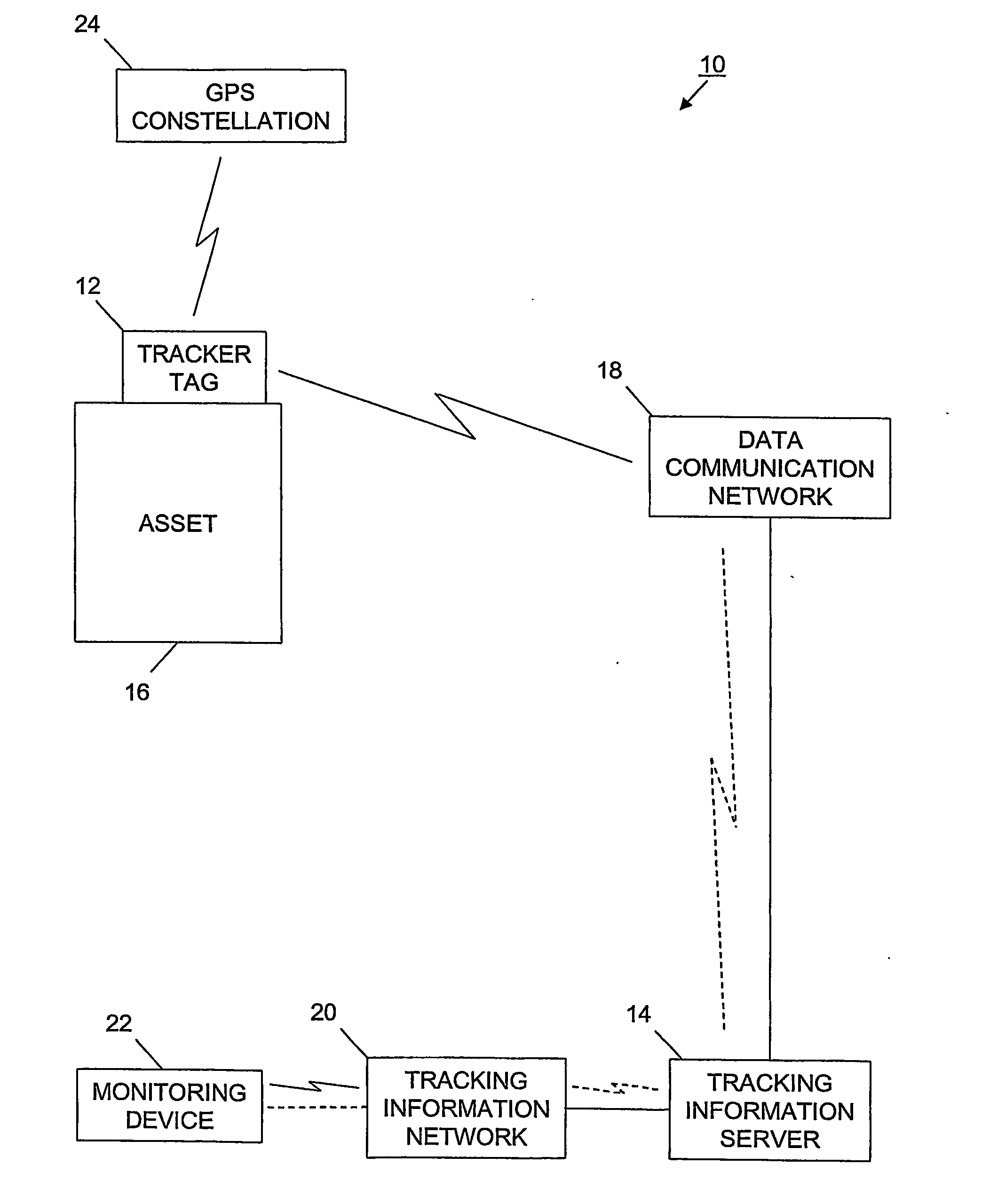

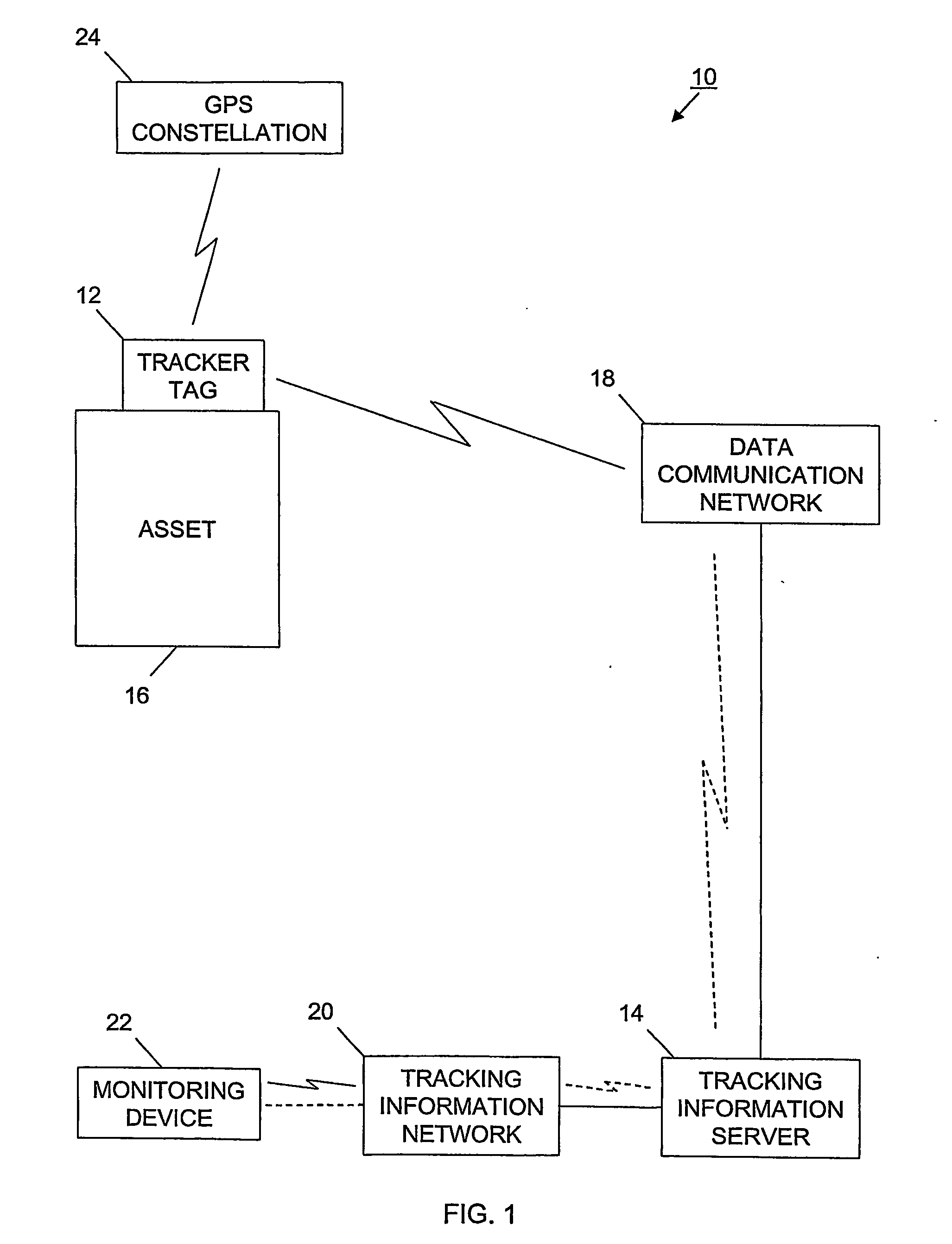

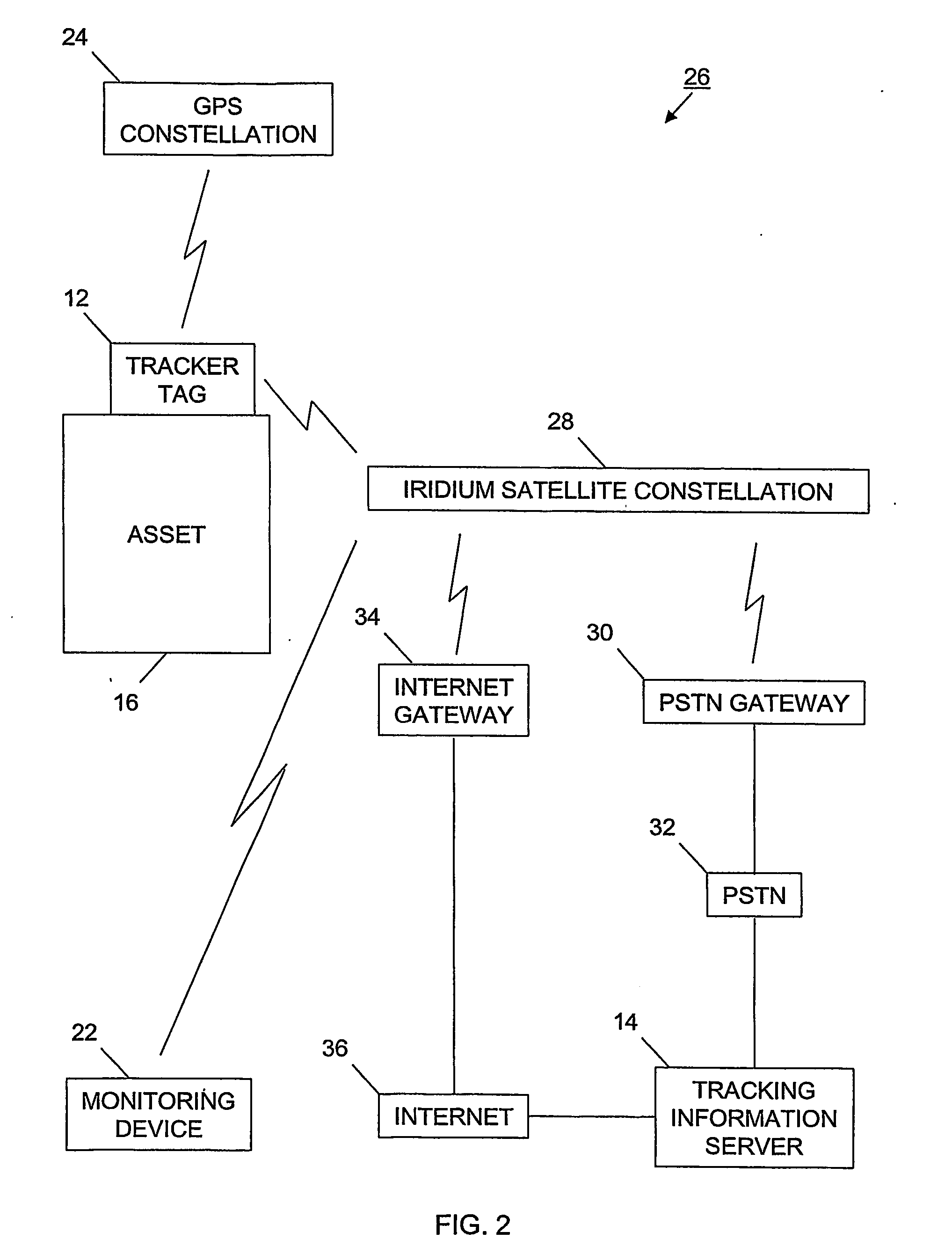

Tracking system and associated method

InactiveUS20060187026A1Easy to receiveVehicle testingRegistering/indicating working of vehiclesProgram instructionIridium satellite constellation

A tracking system (10) for tracking movable assets (16) and several methods for using the system are provided. The tracking system includes a monitoring device (22), a tracking information network (20), a data communication network (18), a tracker tag (12), and a tracking information server (14). The tracker tag uses GPS technology. The tracking information server provides programmed instructions to the tracker tag in messages via a messaging system. The tracker tag selectively retrieves the messages from the messaging system. The tracking information server provides tracking information and related information to a subscriber. In one embodiment, the tracker tag is in communication with an Iridium satellite constellation (28) and tracking information is displayed to the subscriber when the asset is substantially anywhere in the world. In another embodiment, the monitoring device is in communication with the Iridium satellite constellation and tracking information is displayed to the subscriber when the subscriber is substantially anywhere in the world, preferably via the Internet (36).

Owner:ARGO TECH CORP

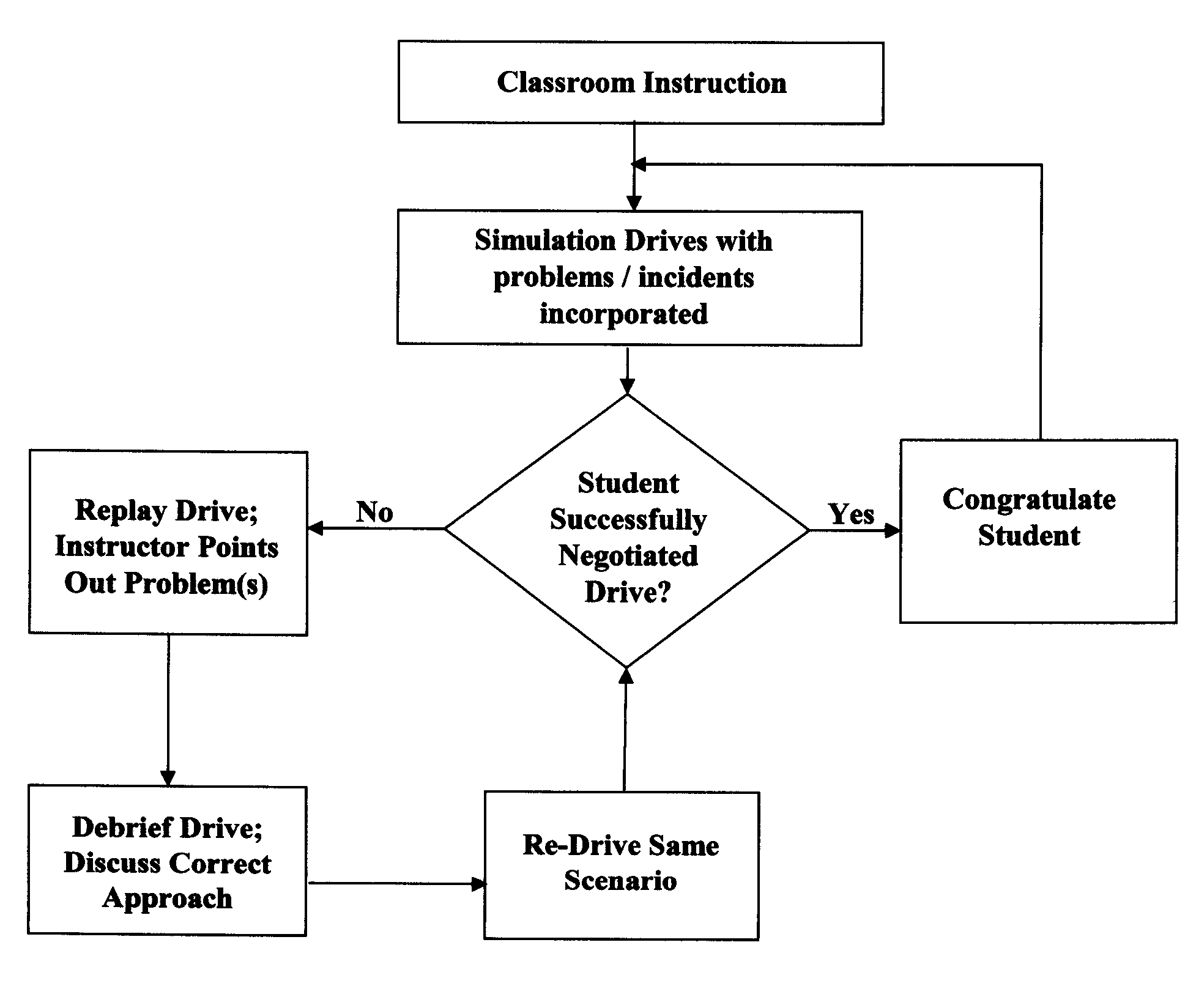

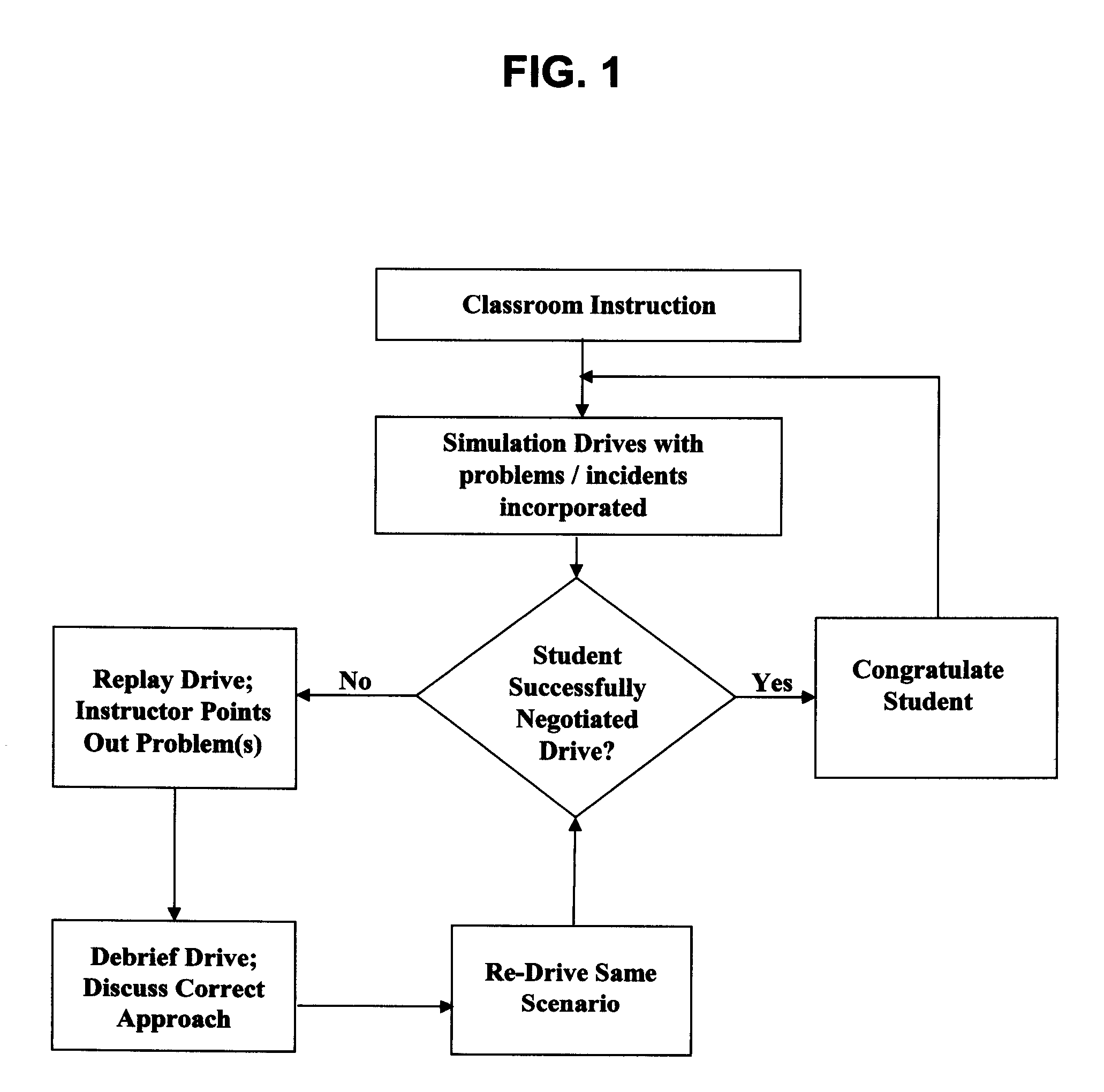

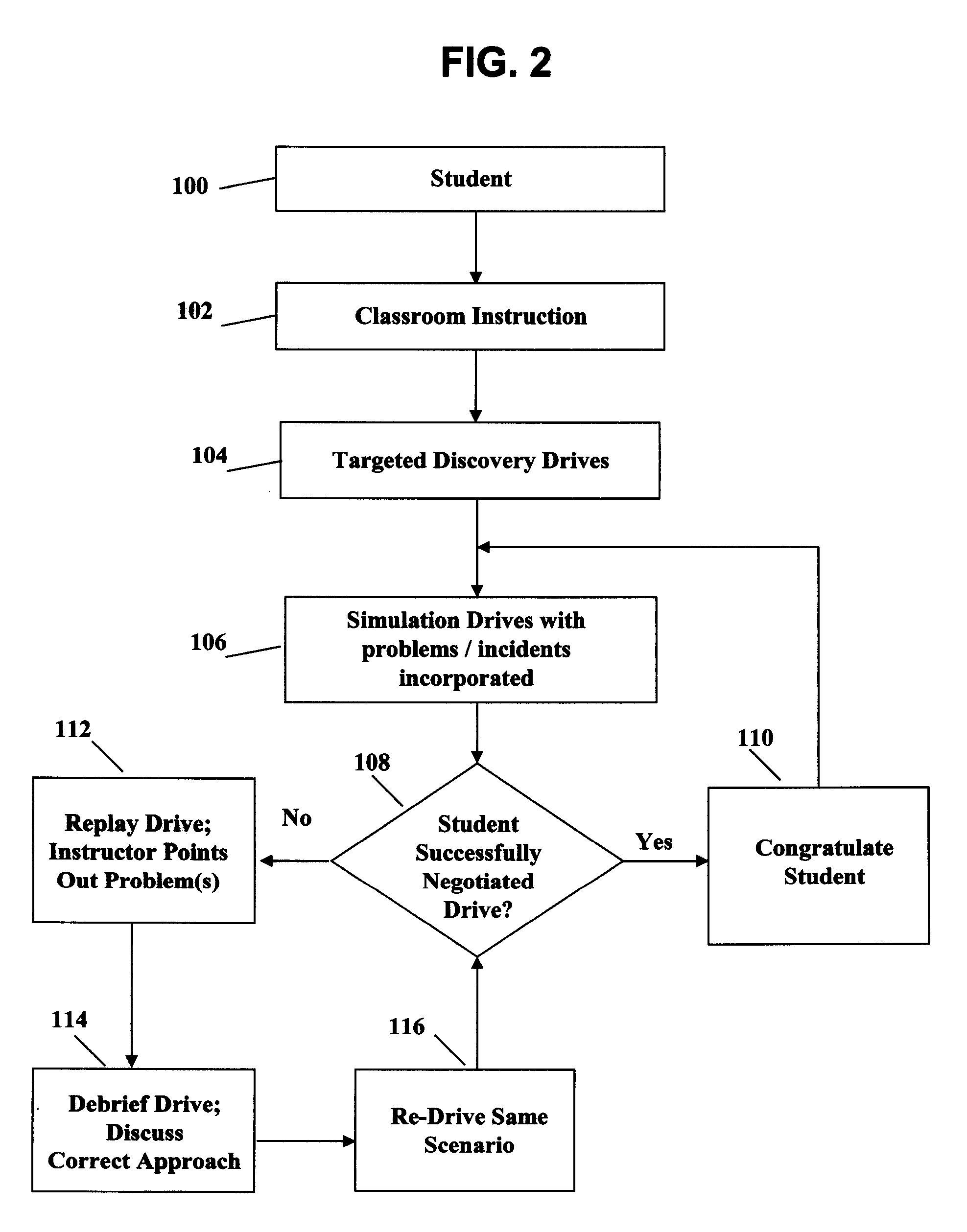

Simulation-based novice driver instruction system and method

InactiveUS20080064014A1Cosmonautic condition simulationsSimulatorsDriver/operatorProgram instruction

The present invention provides for a simulation-based system and method for driver instruction using a highly sophisticated physical and computer-based simulation system combined with a novel simulation-based instruction methodology that allows a novice driver to learn driving fundamentals and advanced defensive driving skills in the safety of the simulator environment. The novelty of the present invention lies in the driving simulation aspect of the driver instruction disclosed herein combined with the novel method of instruction disclosed herein. The simulation-based system and method provides numerous advantages over any other driving instruction system or method currently in use or known in the art.

Owner:DRIVINGMBA

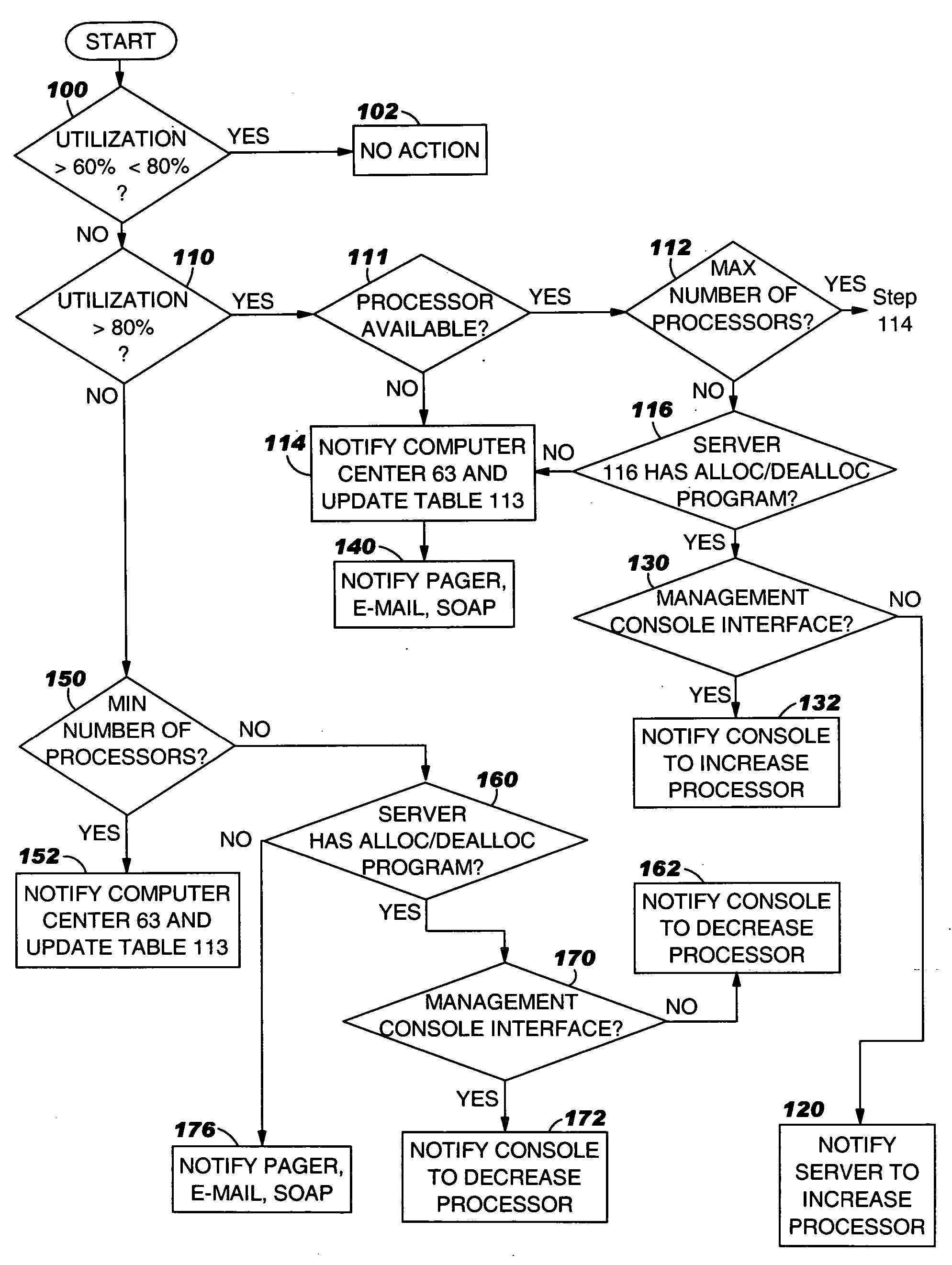

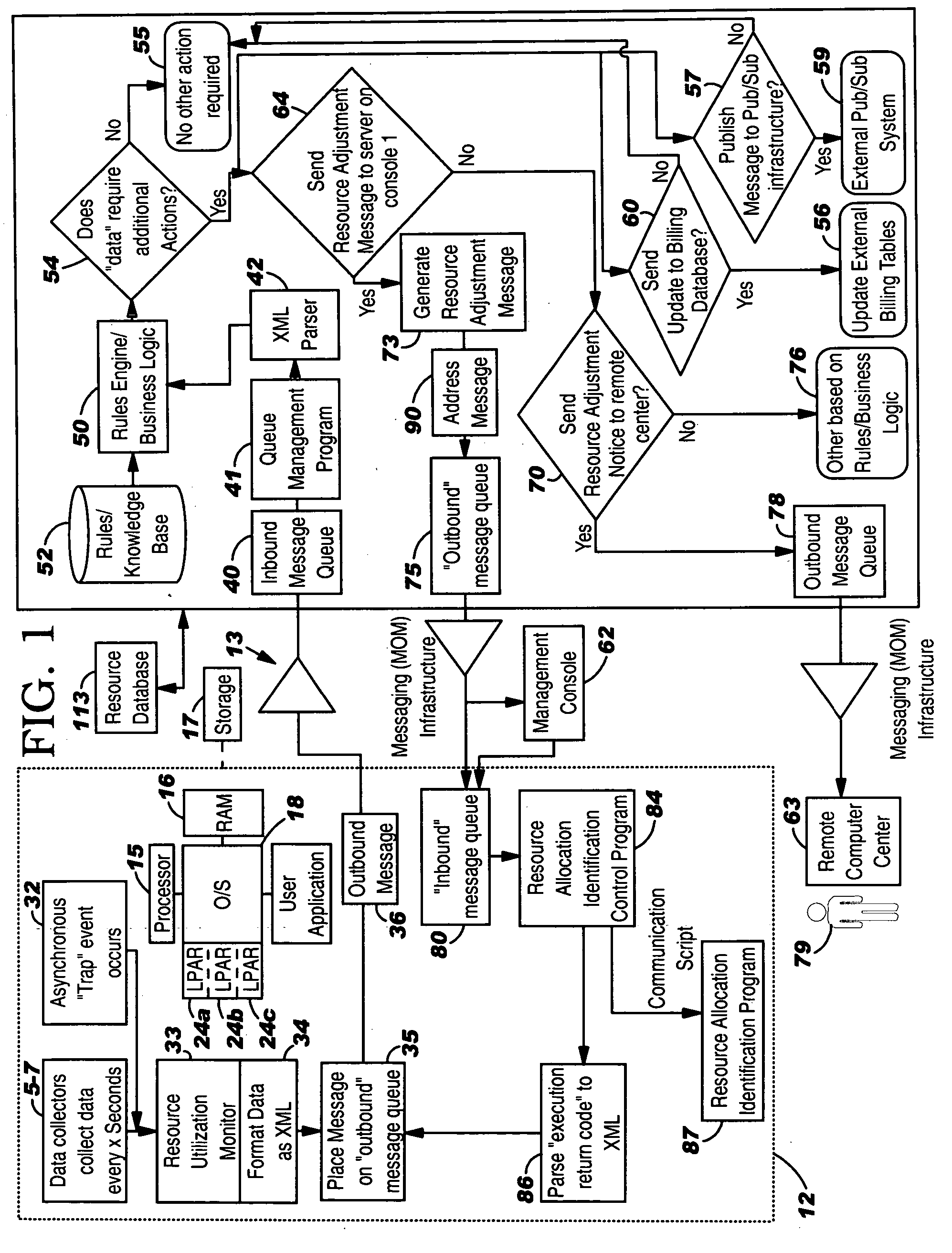

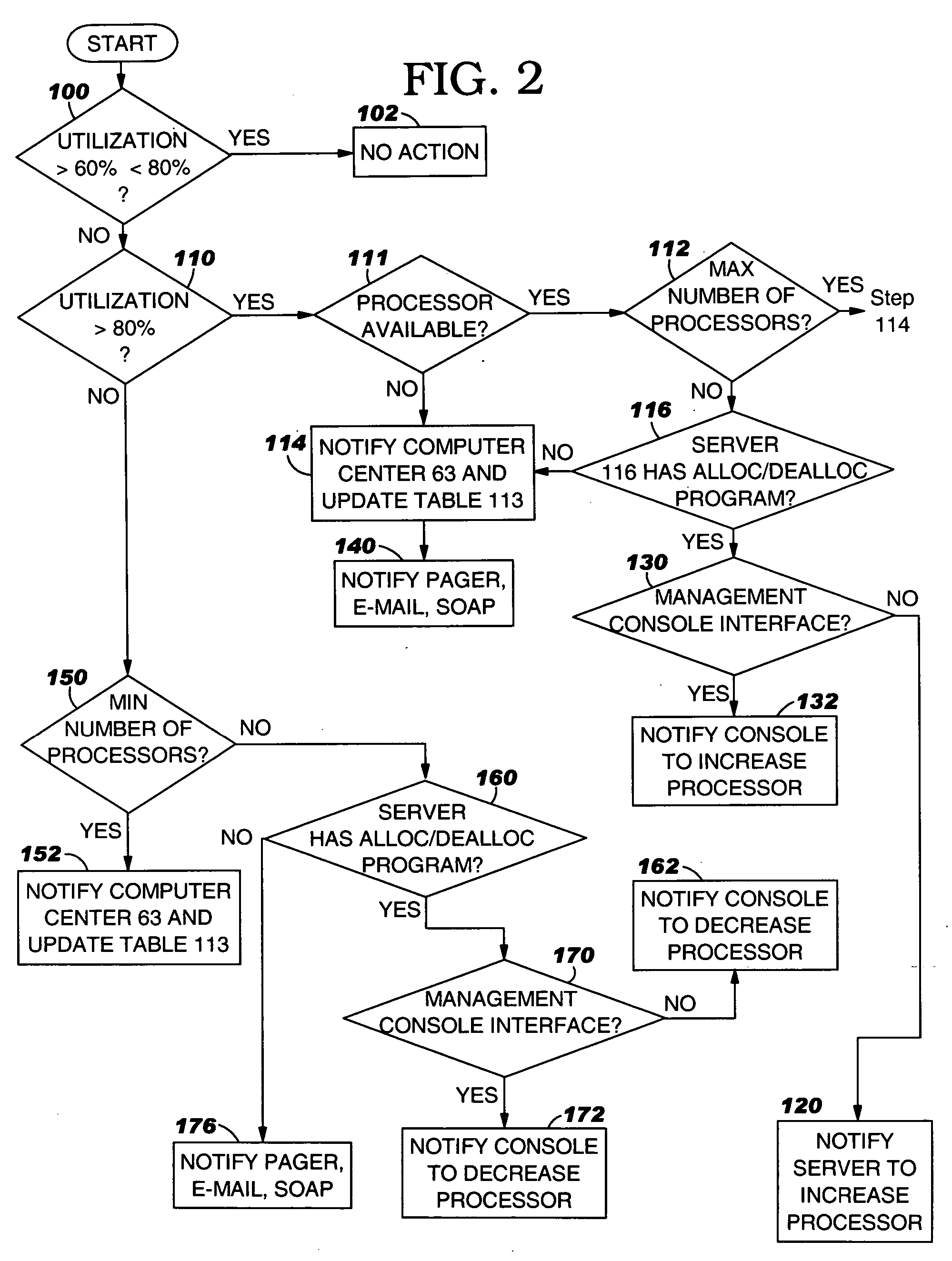

System, method and program to automatically adjust allocation of computer resources

InactiveUS20060136761A1Volume/mass flow measurementDigital computer detailsComputer resourcesProgram instruction

System and computer program product for automatically adjusting allocation of processing power in a server. The server includes means for monitoring utilization of the processing power in the server and reporting the utilization of the processing power to the system, or means for monitoring availability of the processing power in the server and reporting the availability of the processing power to the system. The system comprises means or program instructions, responsive to a report that the processor utilization is above a first predetermined upper threshold or the processor availability is below a first predetermined lower threshold, for determining if the server can accommodate allocation of additional processing power, and if so, generating a request to allocate additional processing power to the server. The system also comprises other means or program instructions, responsive to a report that the processor utilization is below a second predetermined lower threshold or the processor availability is above a second predetermined upper threshold, for determining if the server can accommodate a de allocation of processing power, and if so, generating a request to de allocate some of the currently allocated processing power from the server. The system and program product also automatically adjust allocation of memory in the server.

Owner:IBM CORP

Medical data transport over wireless life critical network

ActiveUS7978062B2ElectrotherapyDiagnostic recording/measuringNetworked Transport of RTCM via Internet ProtocolProgram instruction

A portable patient communicator (PPC) includes a portable housing that supports a processor coupled to memory for storing medical firmware and wireless radio firmware, first and second radios, a processor, and a power source. Communications between a patient implantable medical device (PIMD) and the first radio of the PPC are effected in accordance with program instructions of the medical firmware, and communications between the second radio of the PPC and the wireless network are effected in accordance with program instructions of the wireless radio firmware. Data from the PIMD is received via the first radio to which a priority level is assigned, such as in a tiered manner. A data transport mechanism is selected among disparate data transport mechanisms based at least in part on the priority level. PIMD data is transmitted to the wireless network using the selected transport mechanism via the second radio.

Owner:CARDIAC PACEMAKERS INC

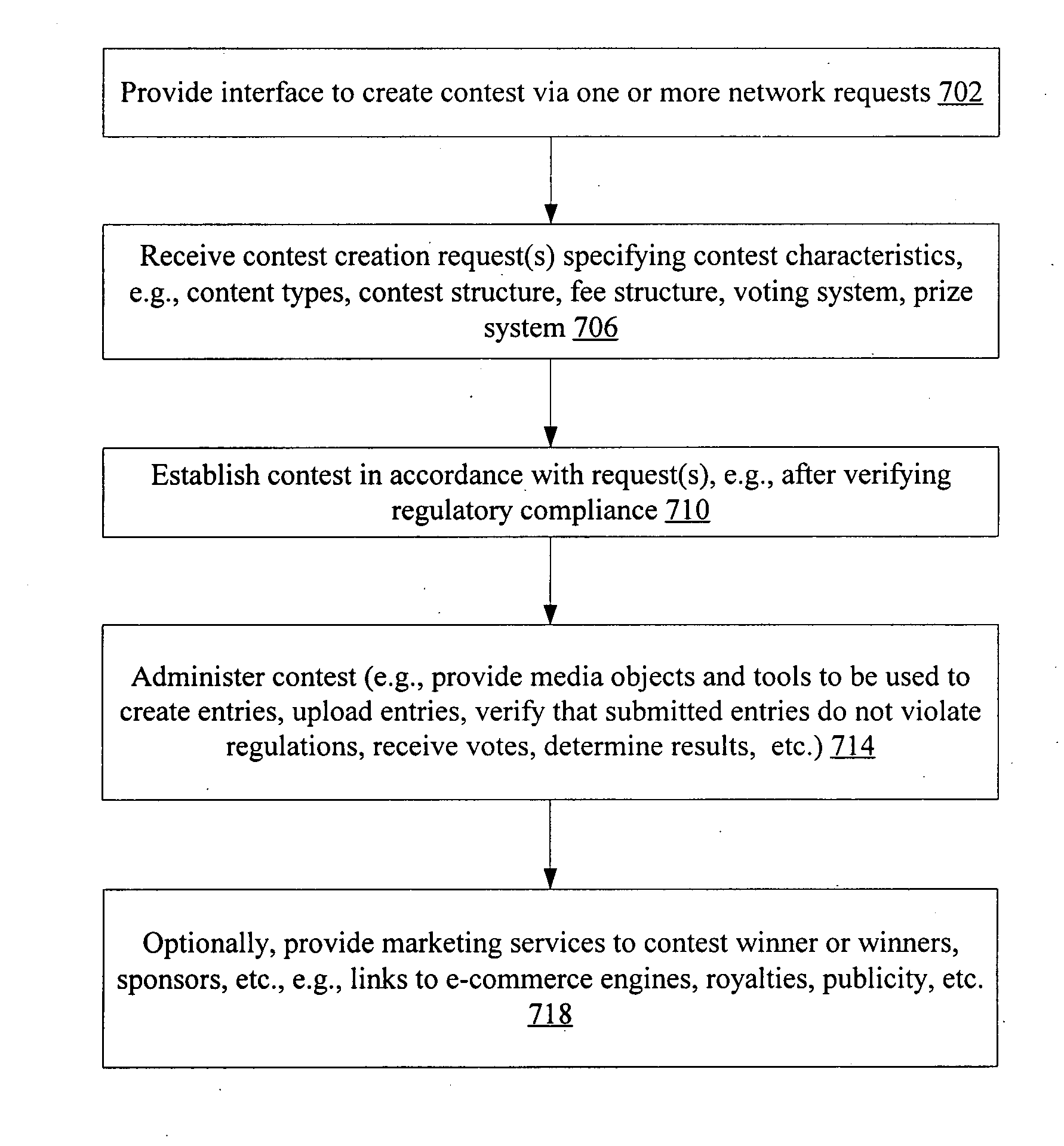

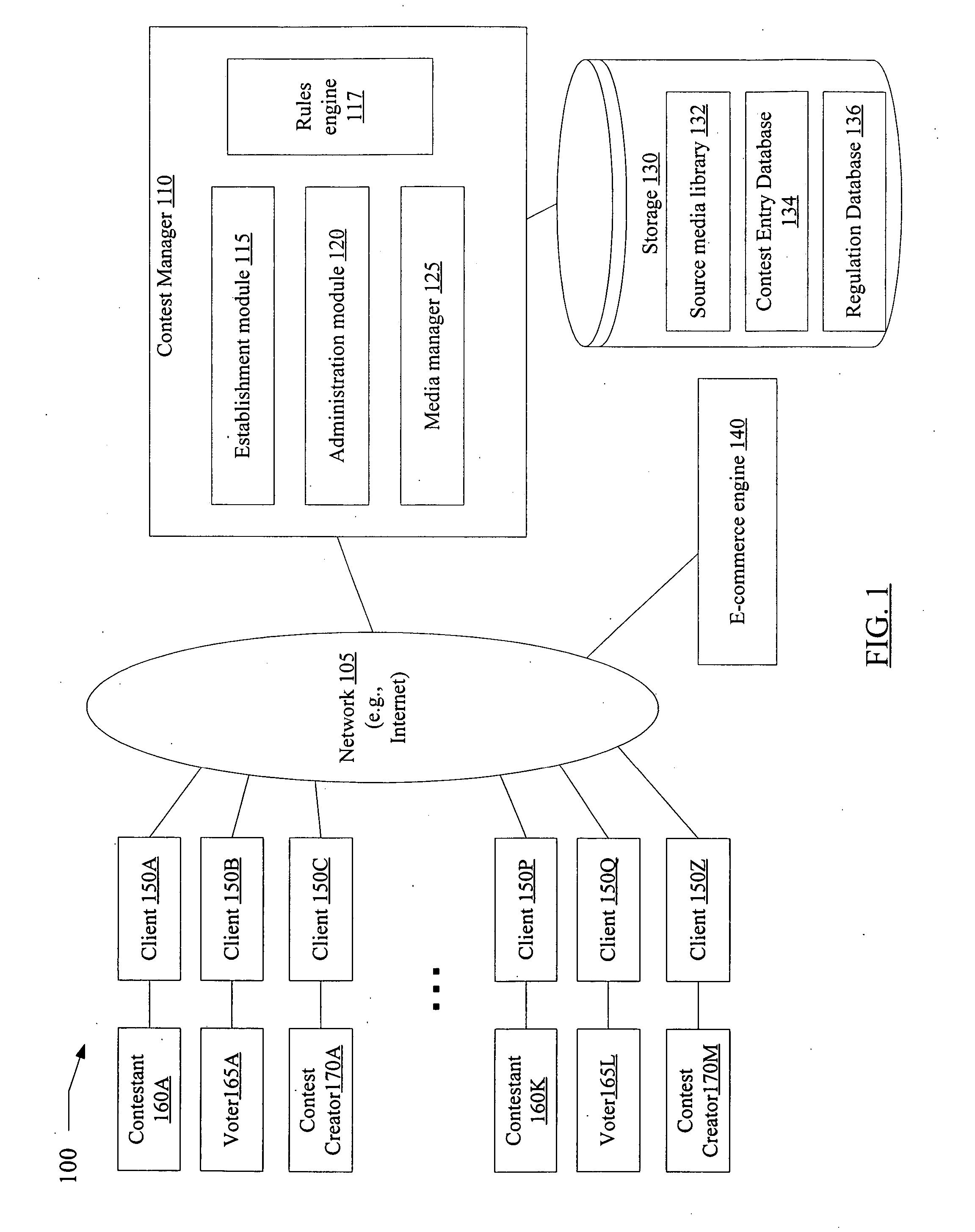

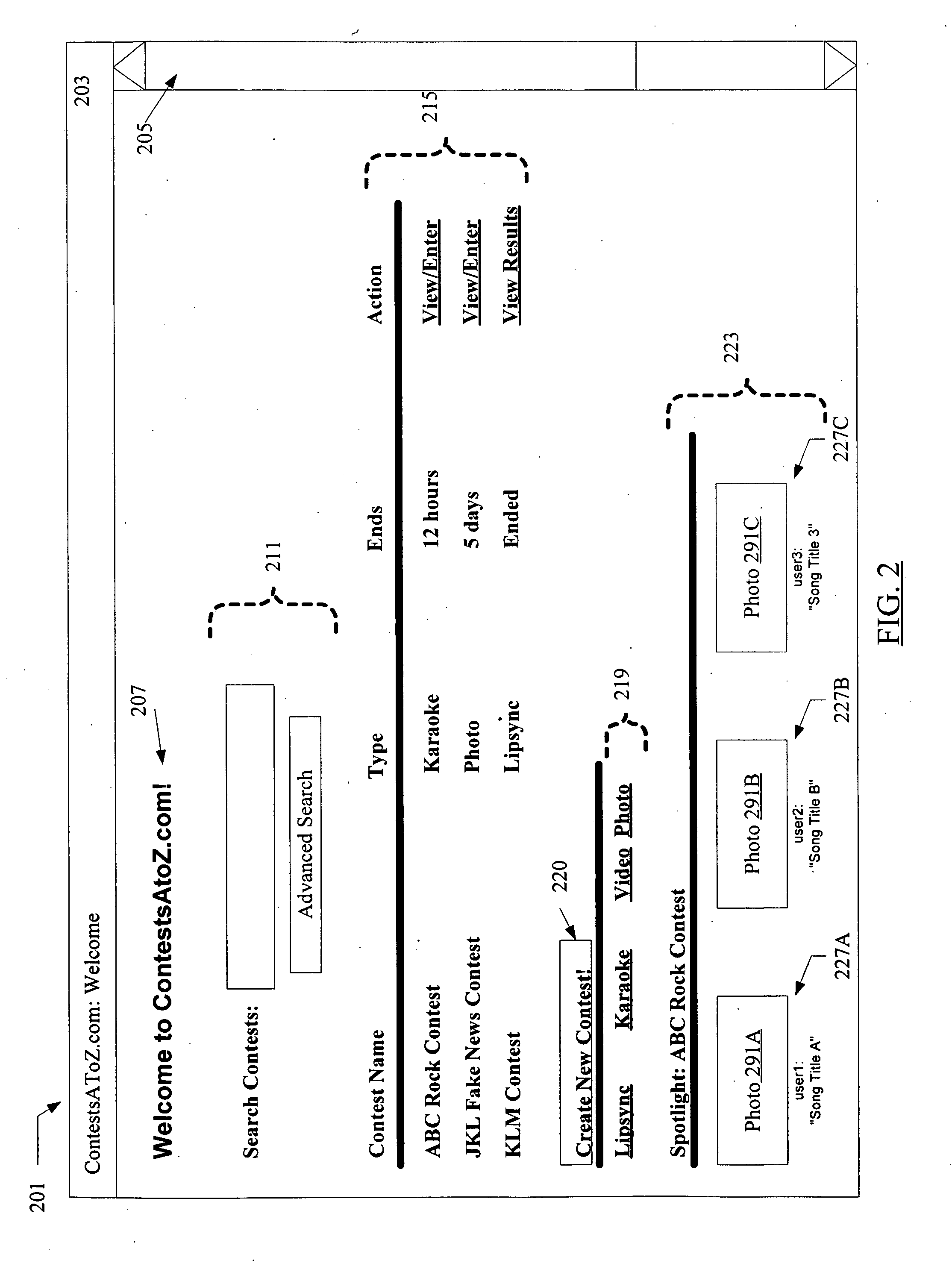

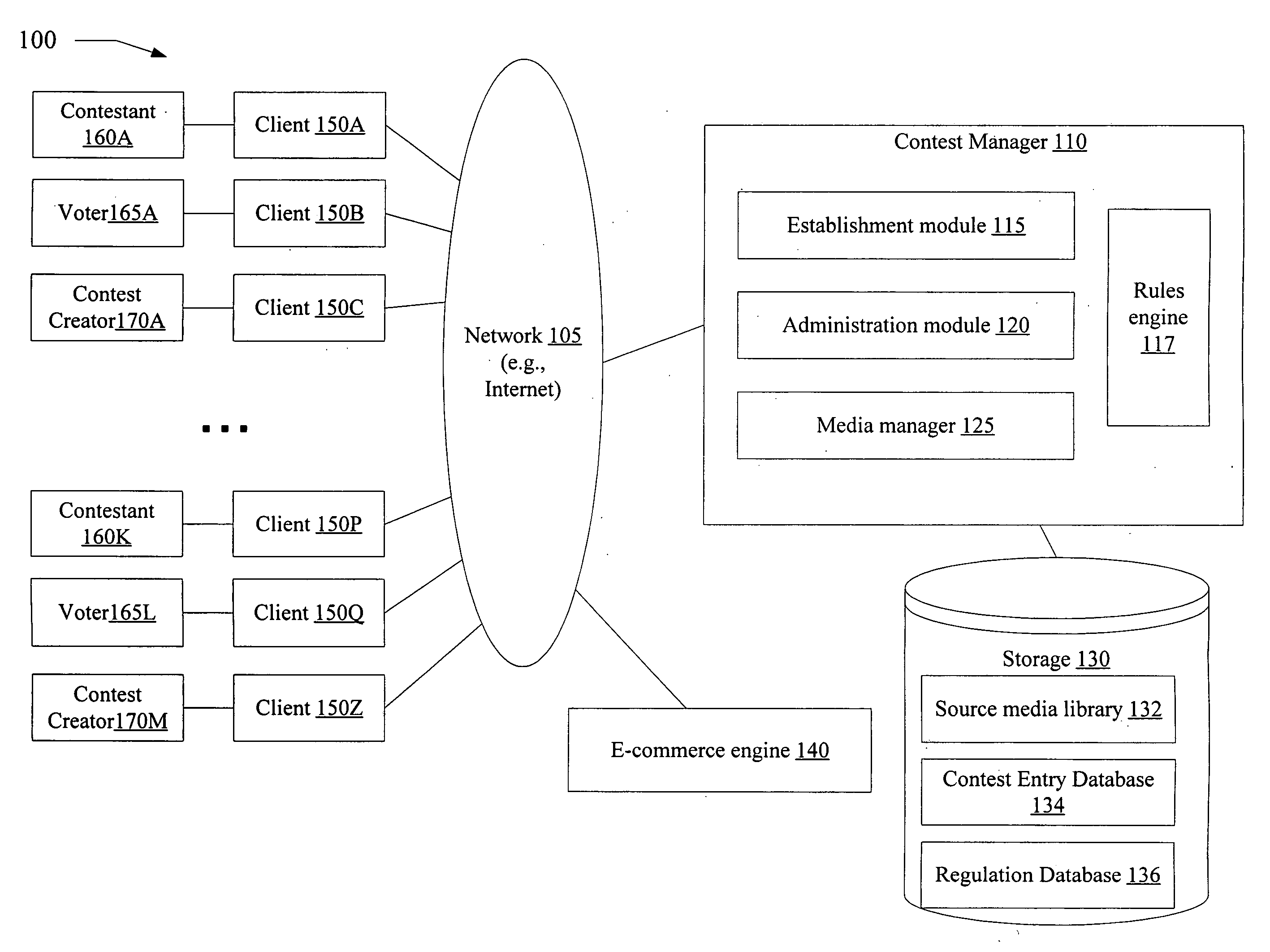

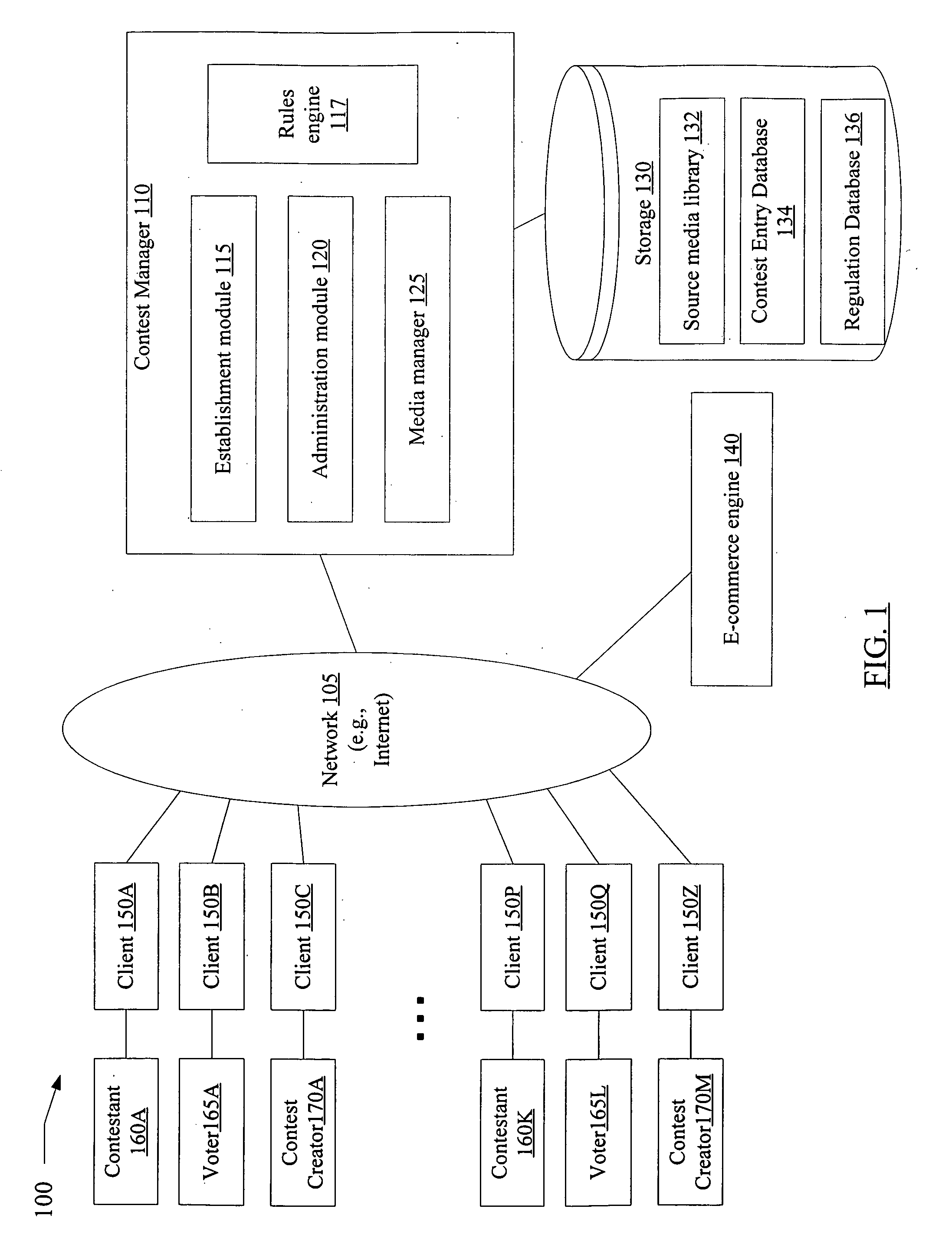

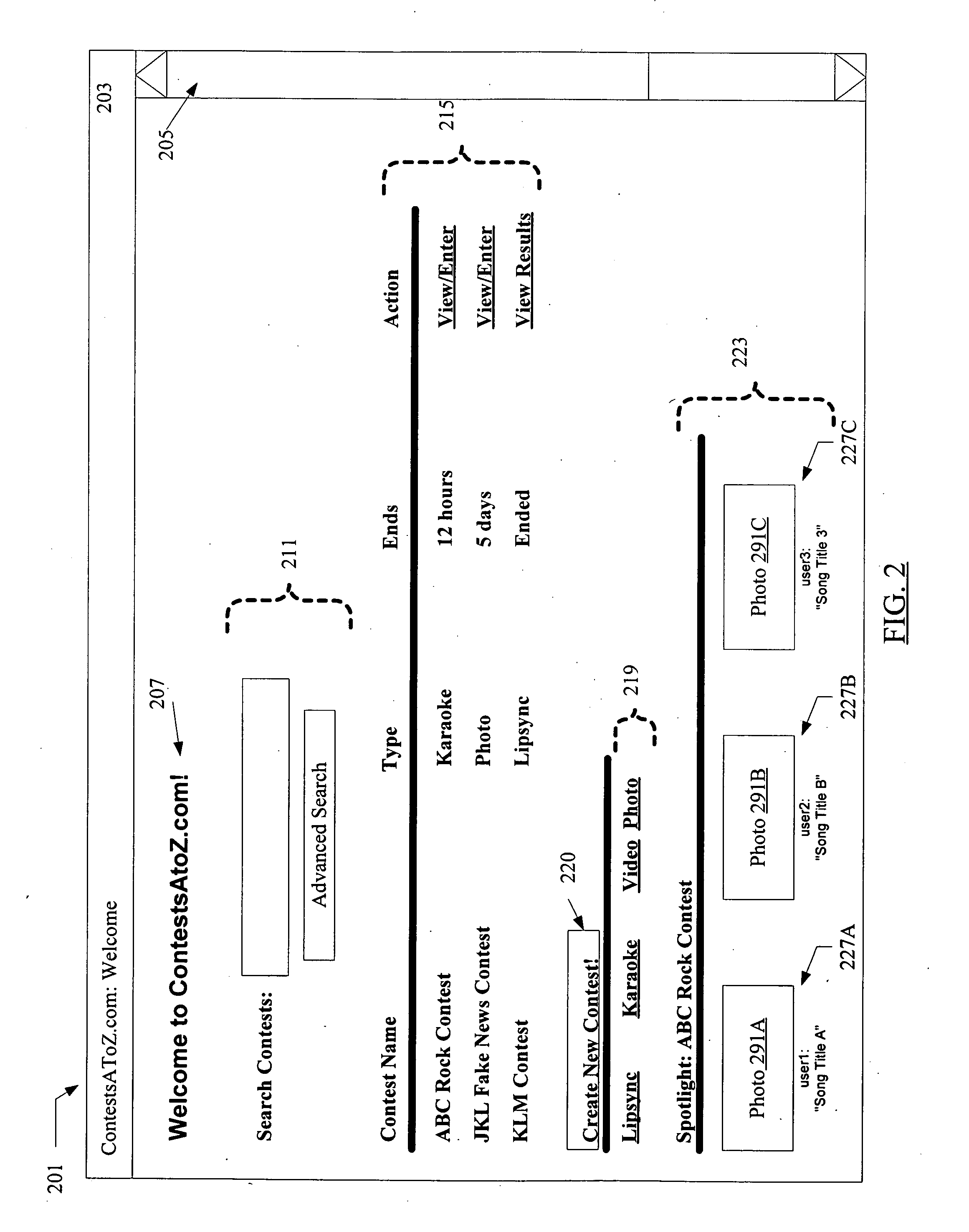

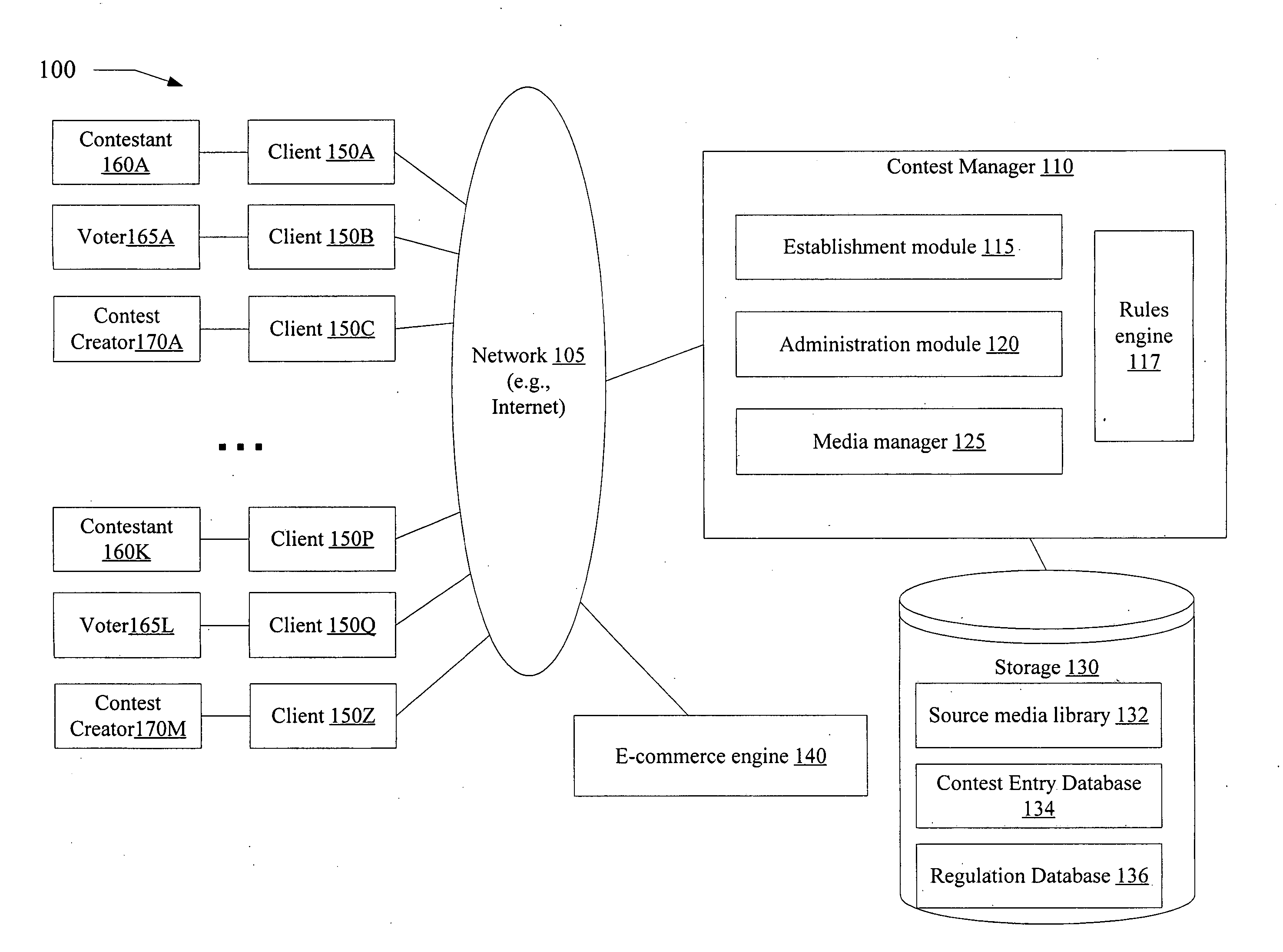

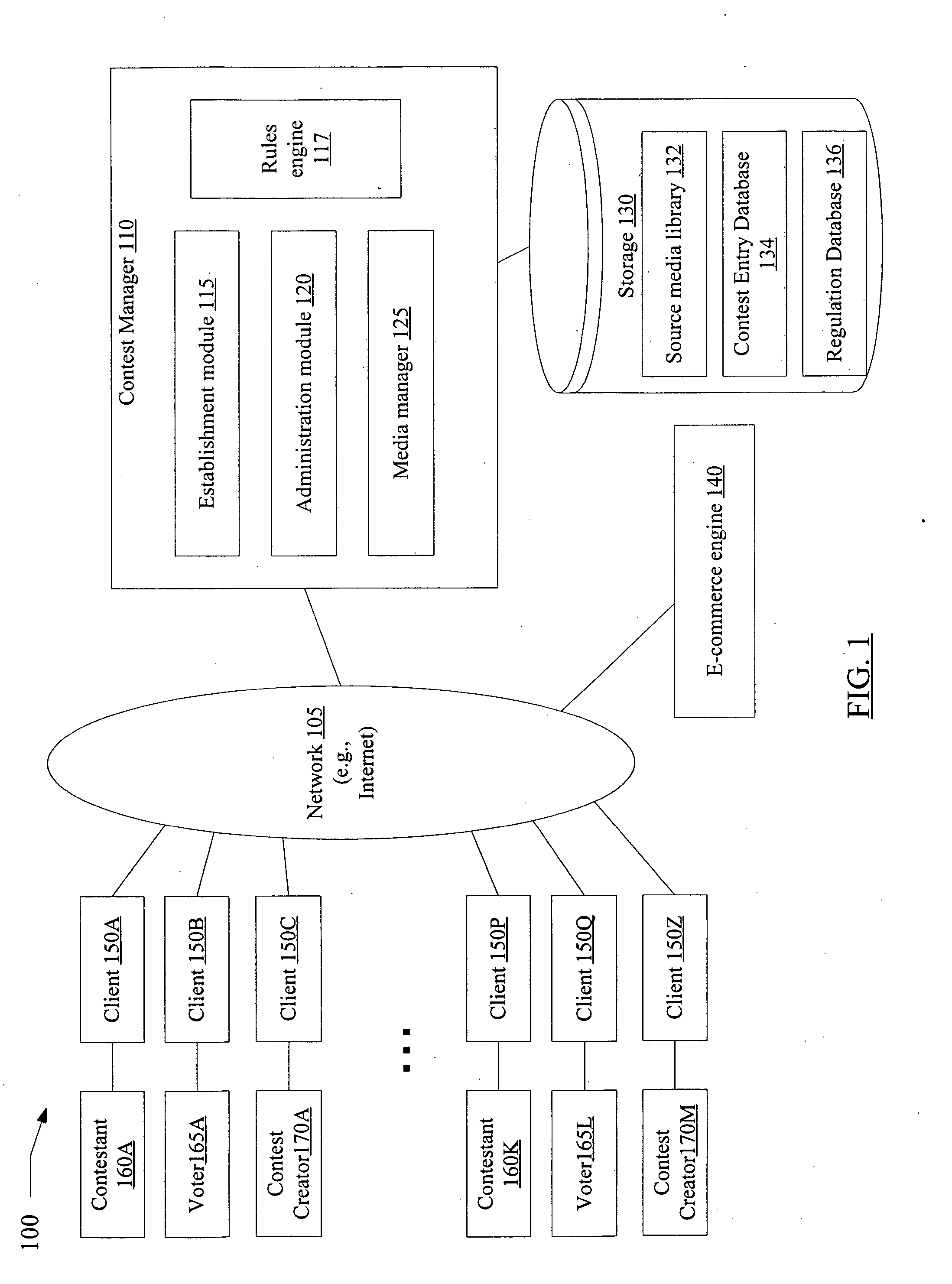

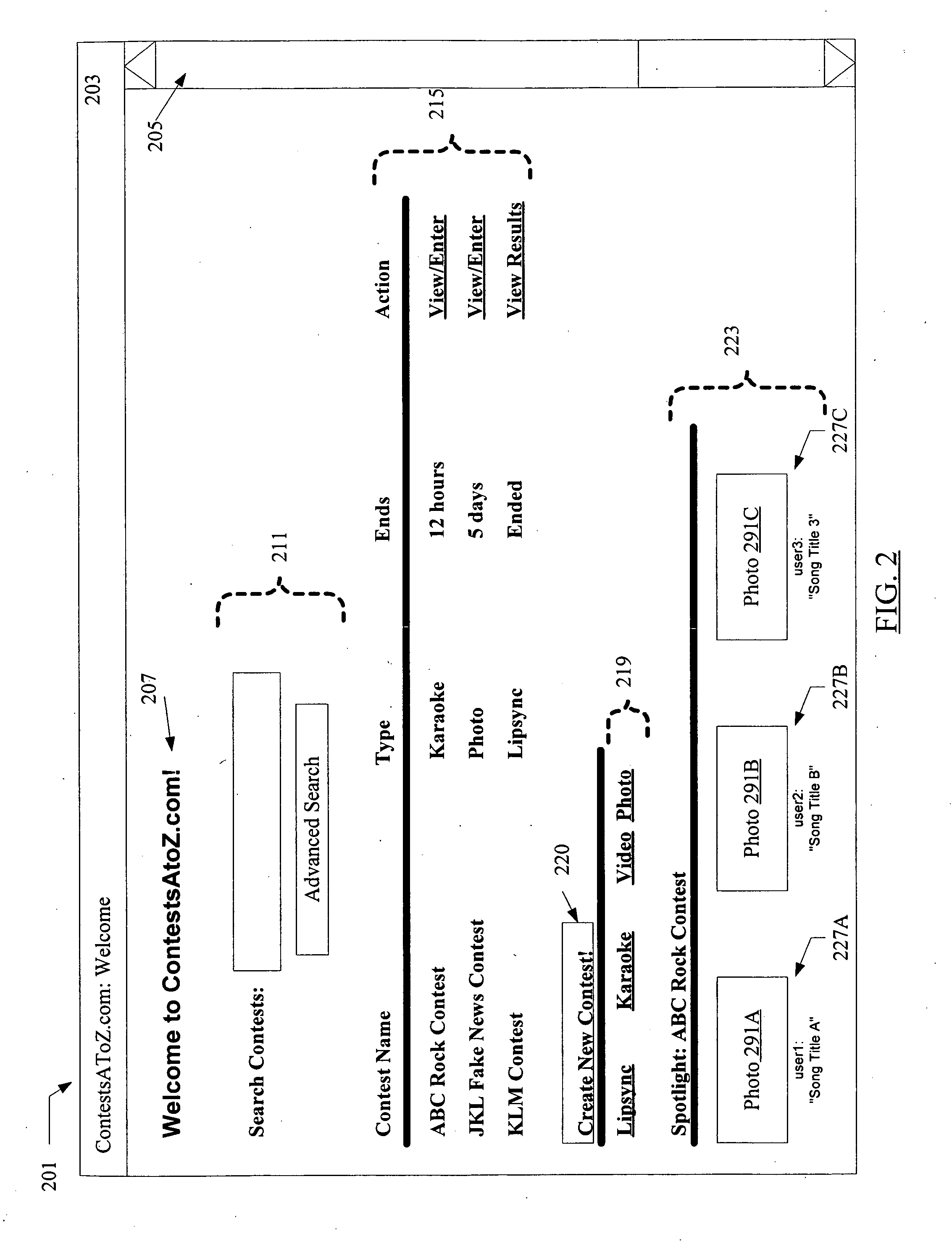

Automated reward management for network-based contests

ActiveUS20070244749A1Low costReduce effortElectrophonic musical instrumentsAdvertisementsReward managementProgram instruction

A system for automated reward management for network-based contests includes one or more processors and memory coupled to the processors, where the memory stores program instructions executable by the processors to implement a contest manager. The contest manager is configured to collect an entry fee corresponding to each entry of a plurality of entries submitted for a contest over a network, and provide a prize to a winning entry of the contest based at least in part on a total amount of entry fees collected for the contest.

Owner:R2 SOLUTIONS

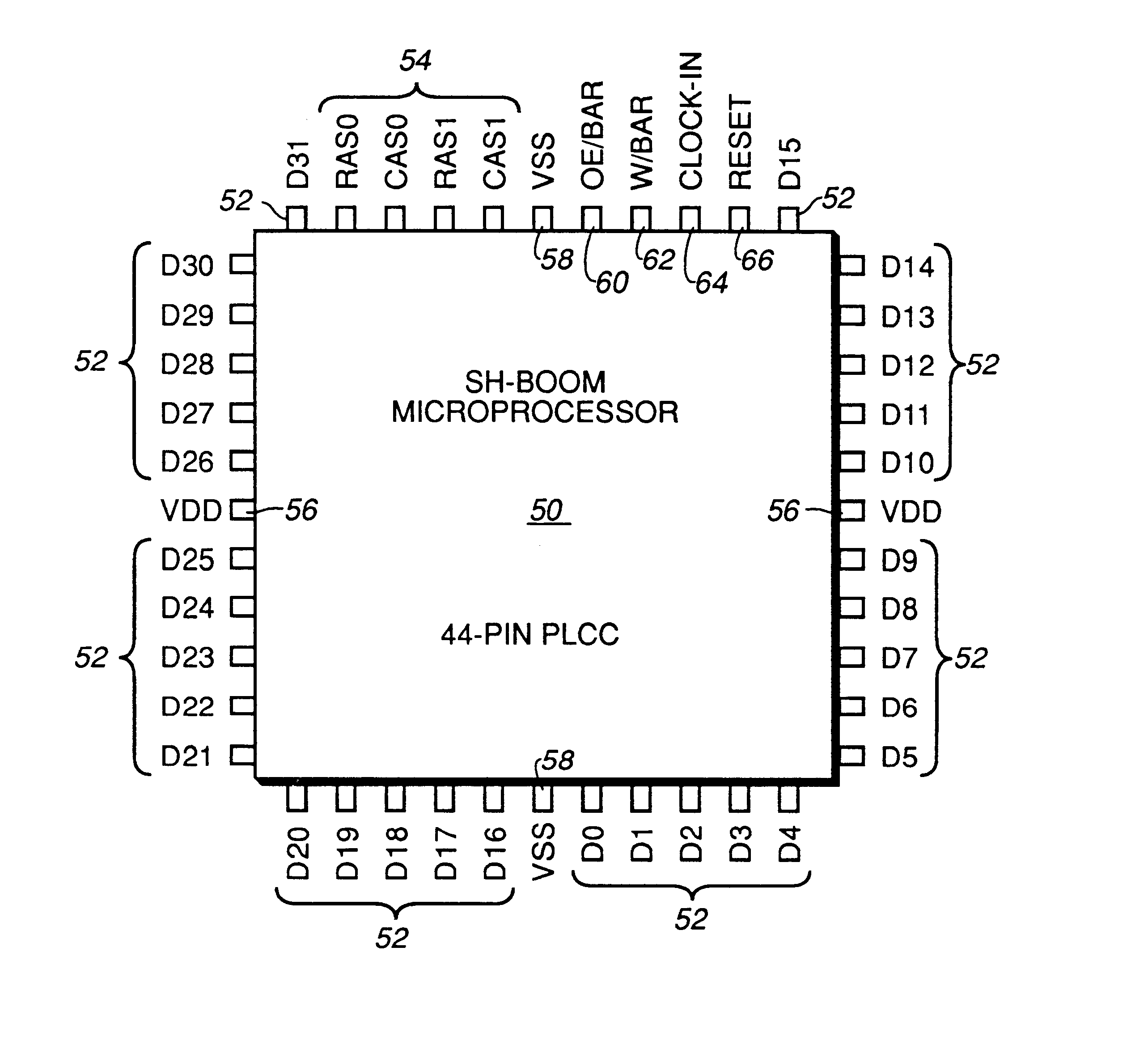

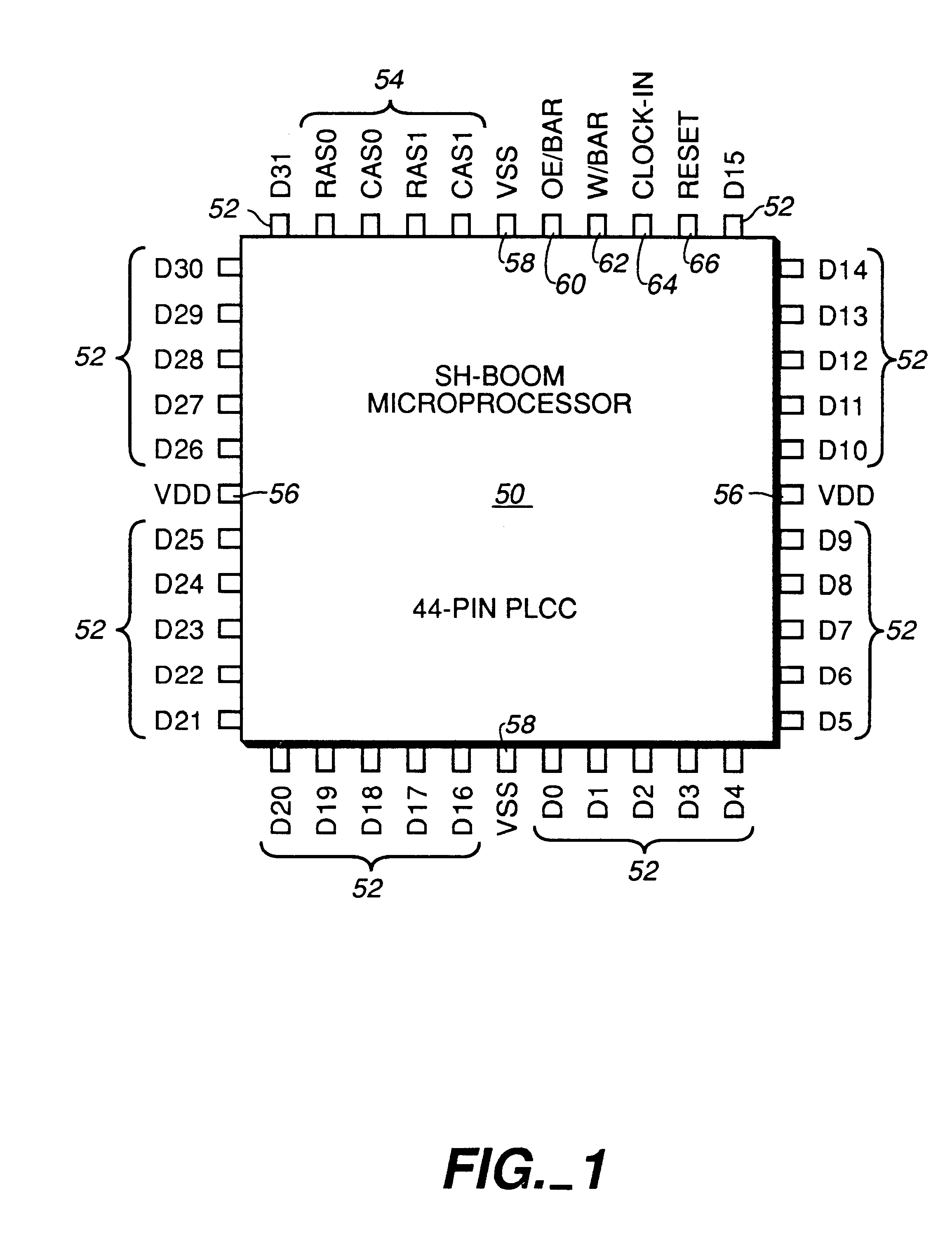

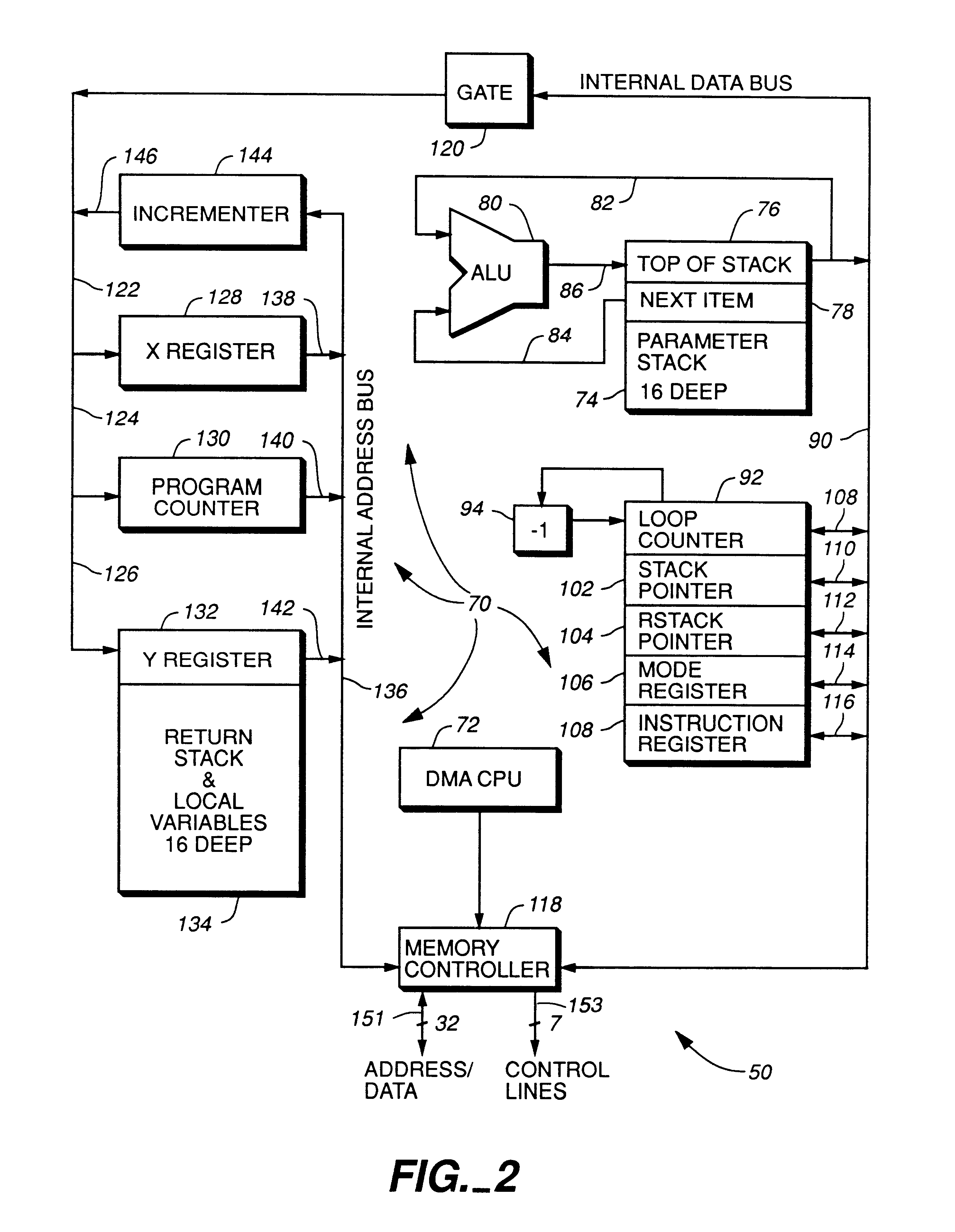

High performance microprocessor having variable speed system clock

InactiveUS6598148B1Improve performanceWithout sacrificing microprocessor speedRandom number generatorsInstruction analysisComputer architectureStatic random-access memory

A microprocessor integrated circuit including a processing unit disposed upon an integrated circuit substrate is disclosed herein. The processing unit is designed to operate in accordance with a predefined sequence of program instructions stored within an instruction register. A memory, capable of storing information provided by the processing unit and occupying a larger area of the integrated circuit substrate than the processing unit, is also provided within the microprocessor integrated circuit. The memory may be implemented using, for example dynamic or static random-access memory. A variable output frequency system clock, such as generated by a ring oscillator, is also disposed on the integrated circuit substrate.

Owner:MOORE CHARLES H TTE UTD 03 21 2006 THE EQUINOX TRUST

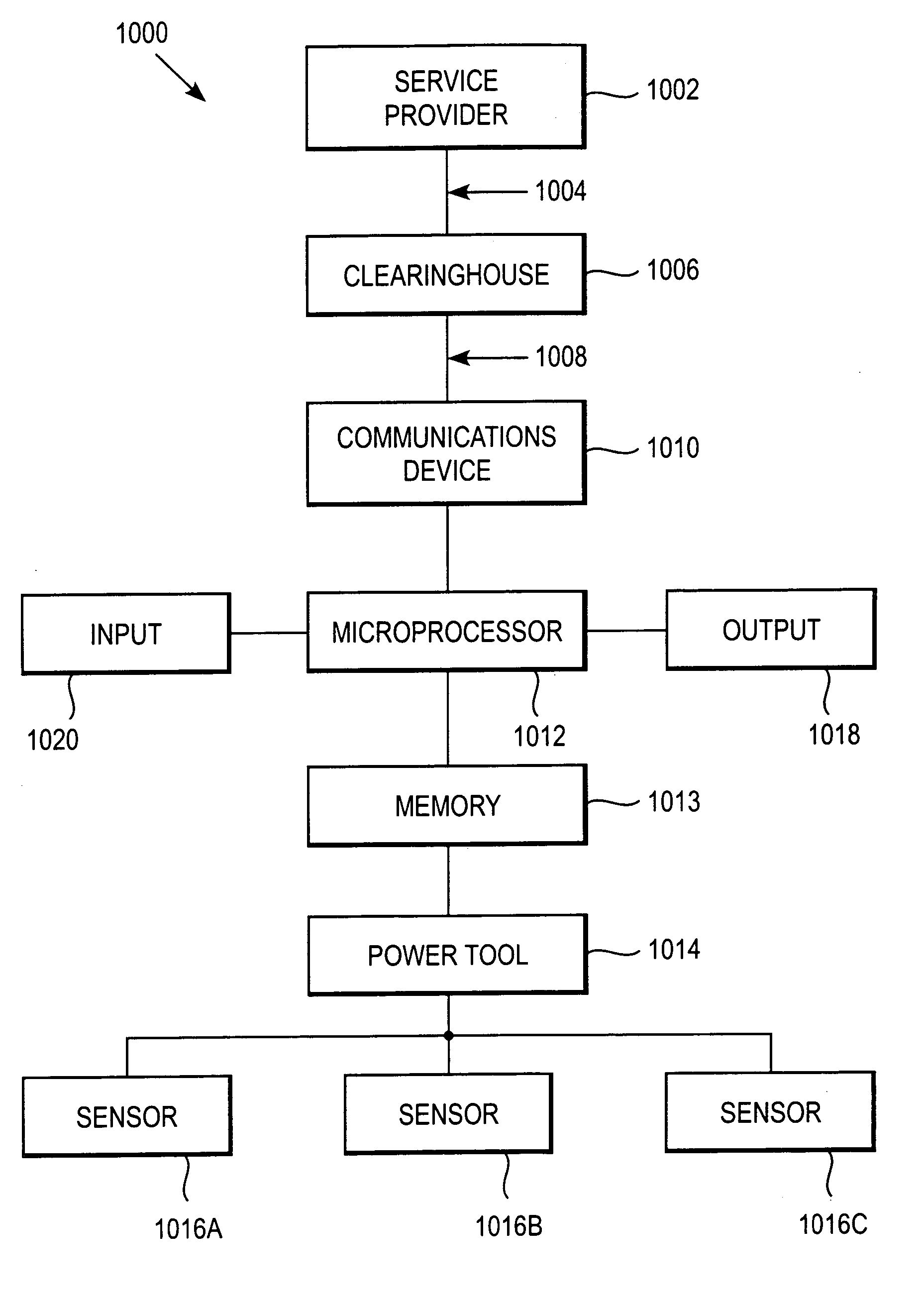

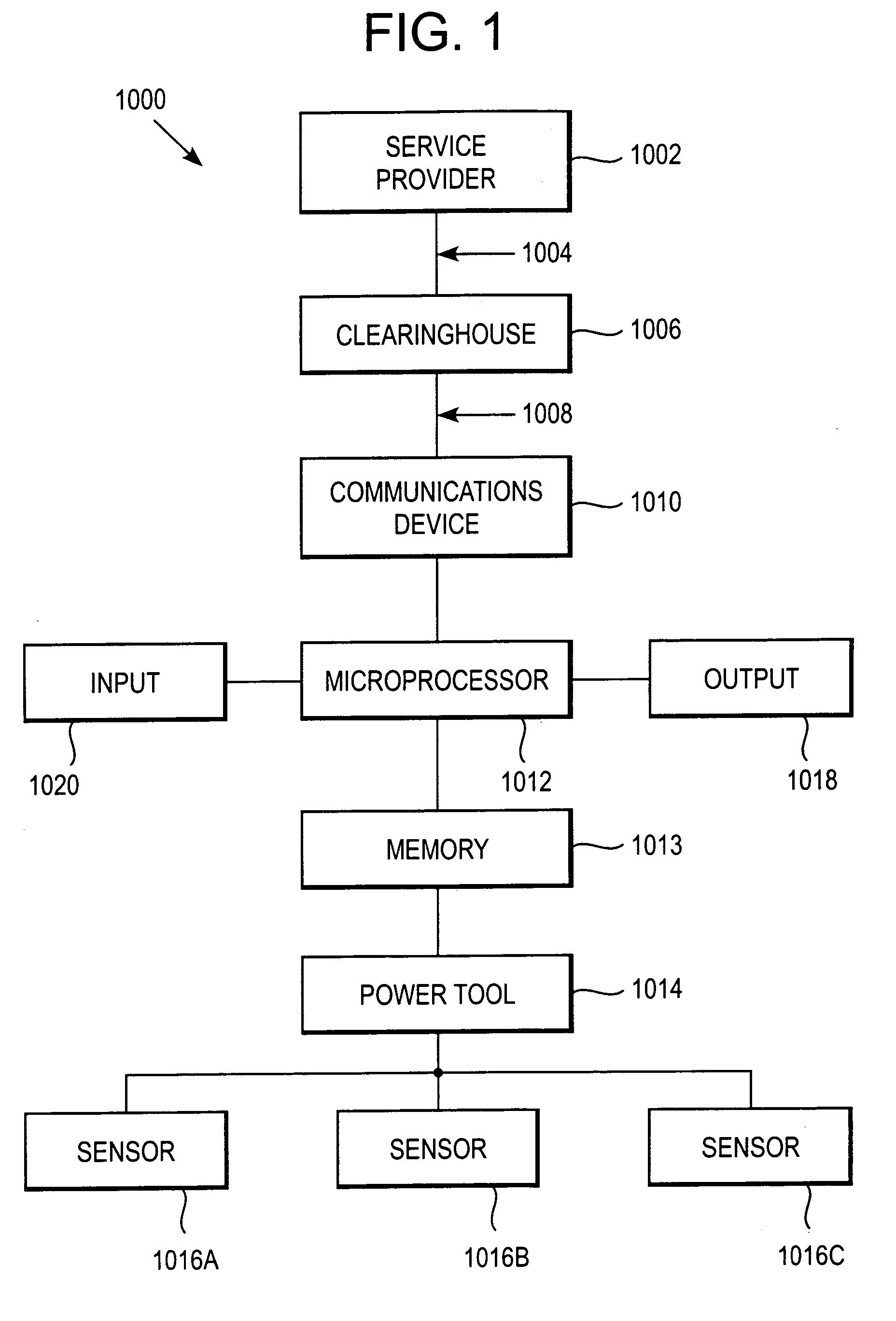

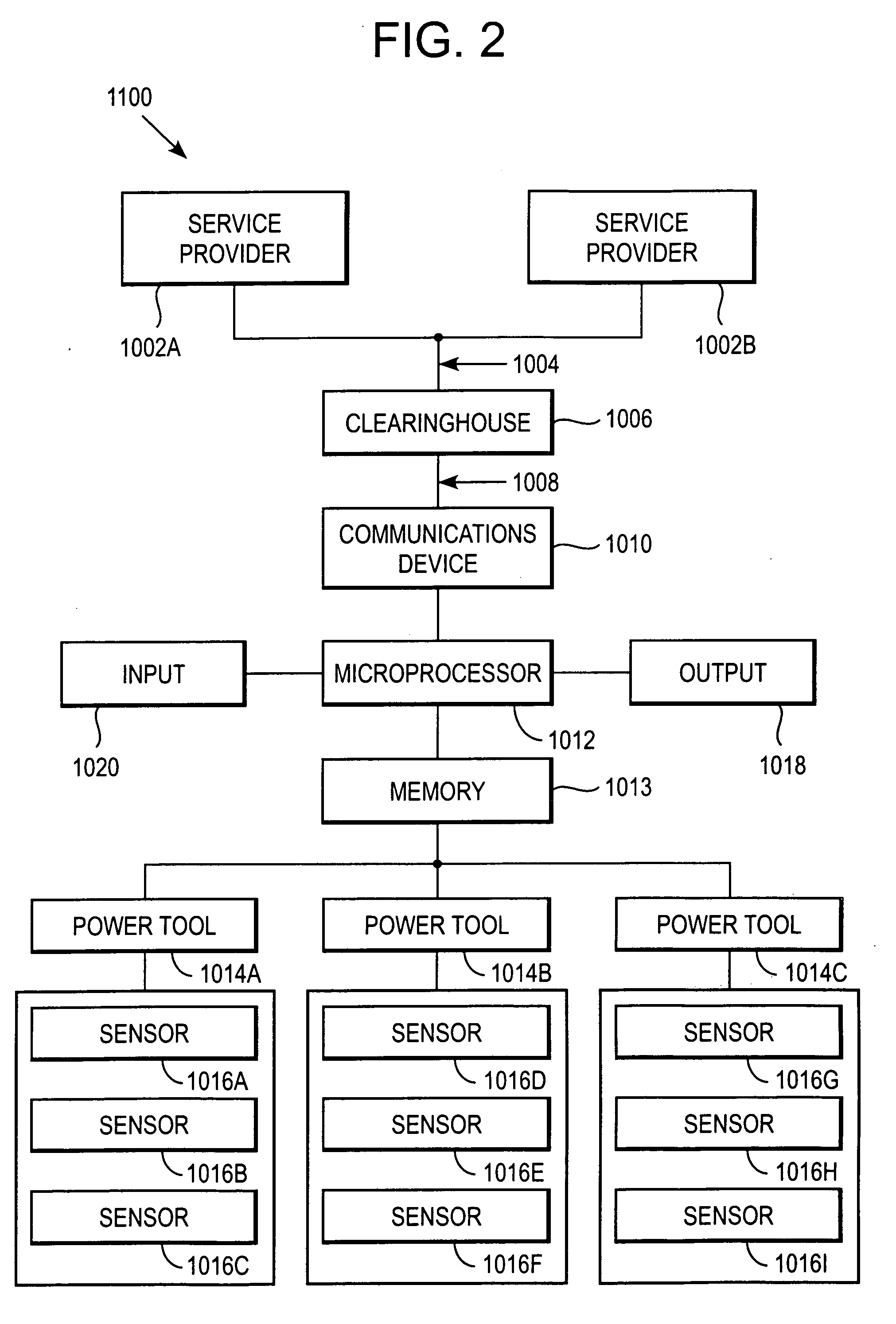

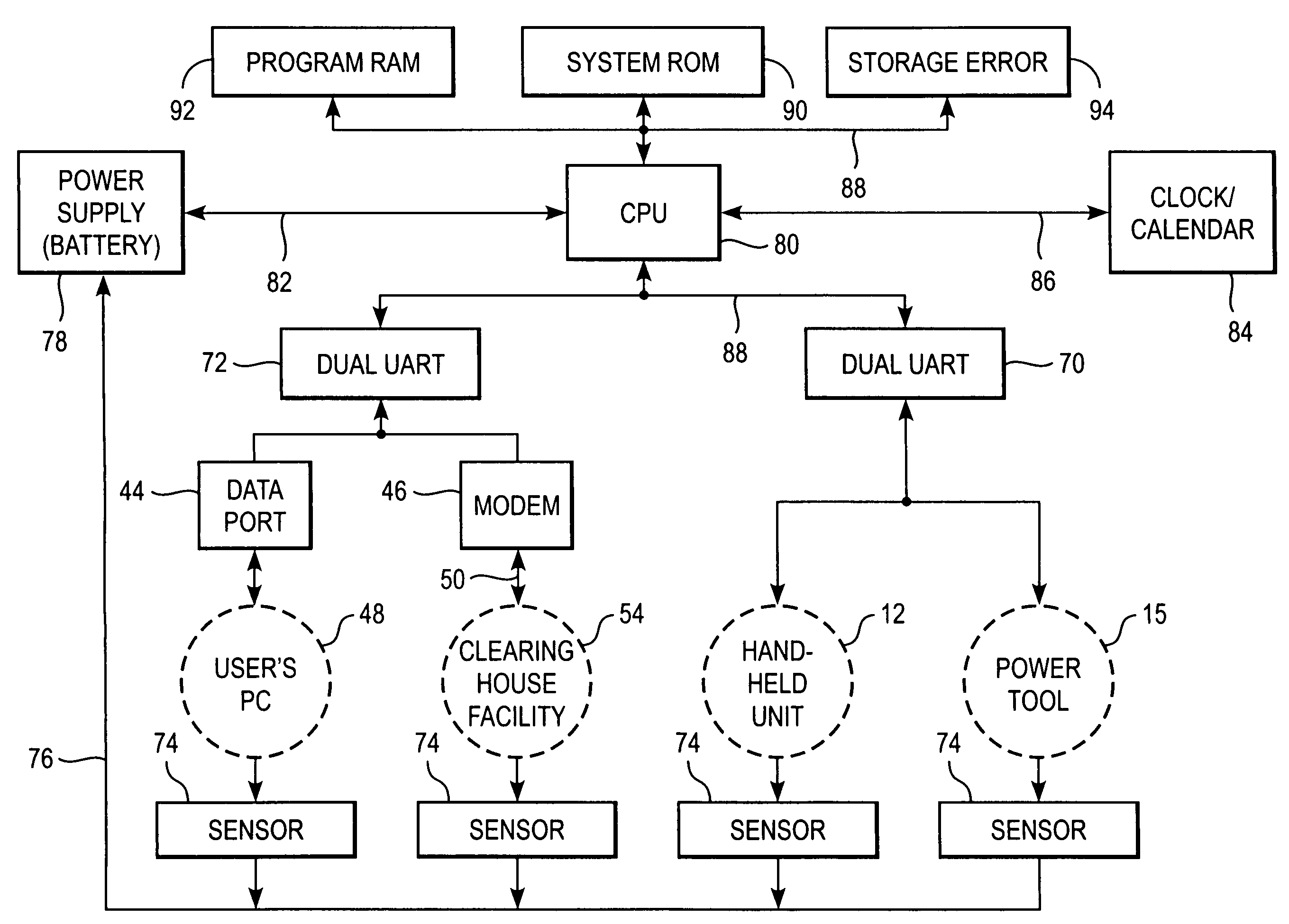

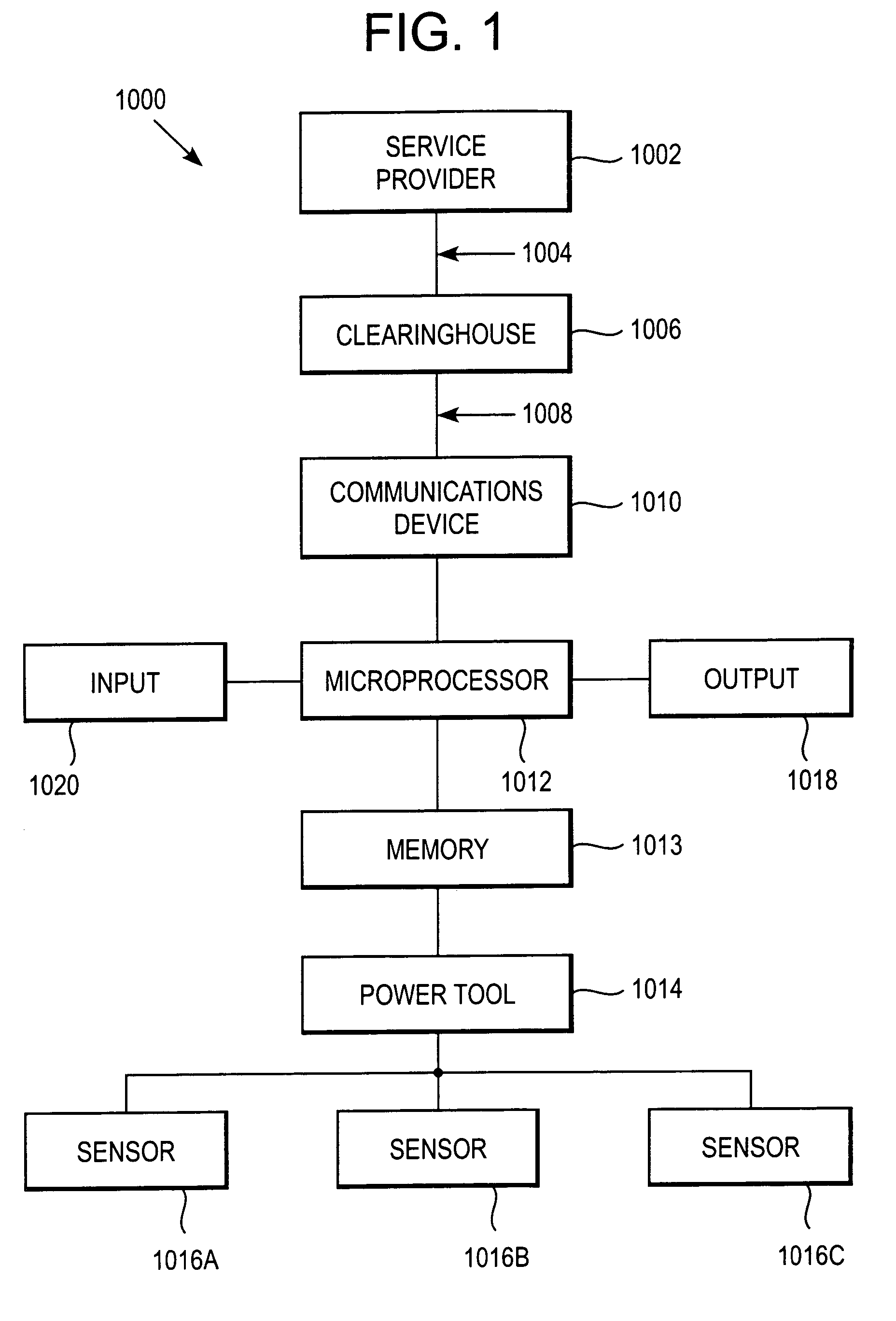

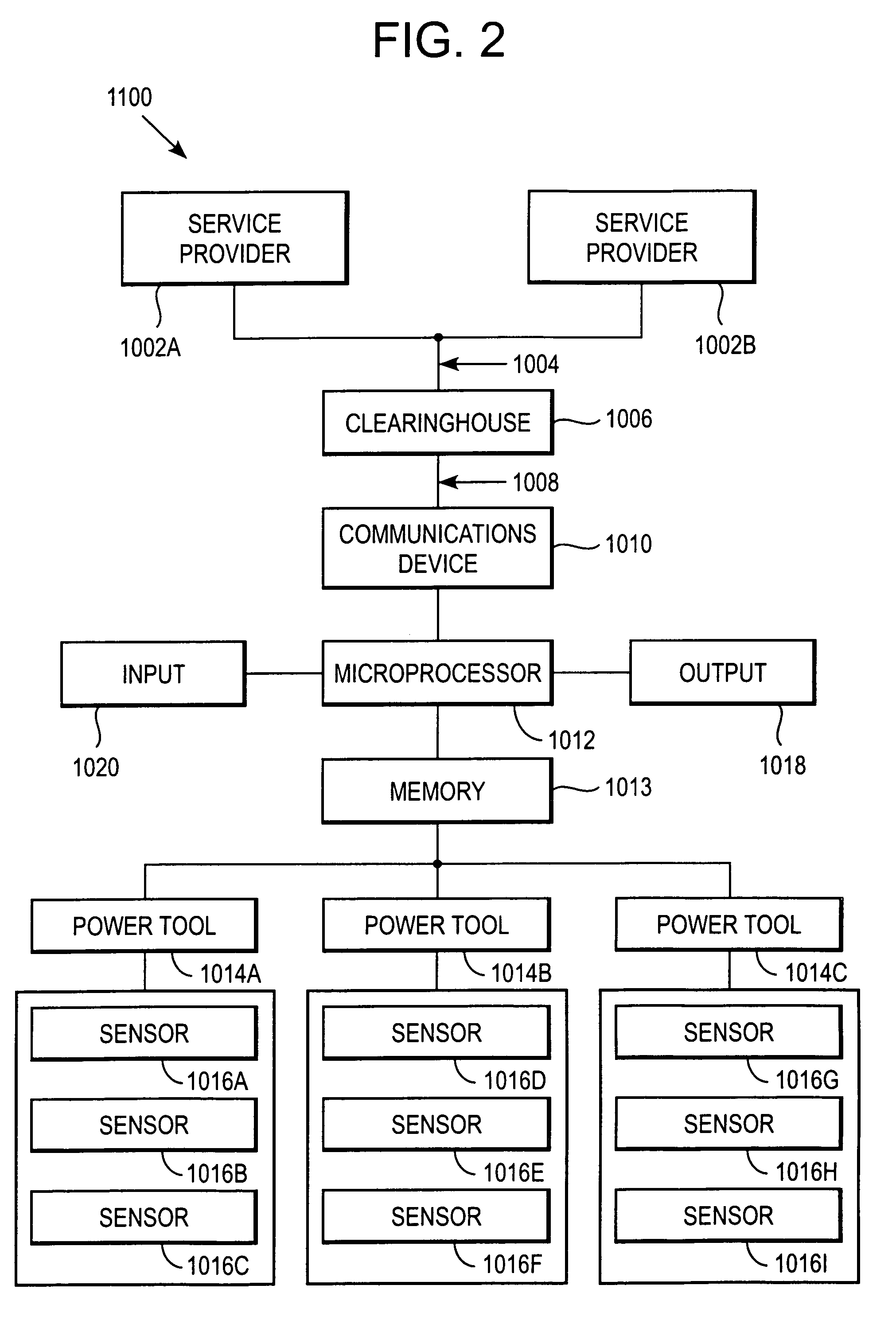

Modular microprocessor-based power tool system

InactiveUS20060155582A1Testing/calibration apparatusTurning machine accessoriesProgram instructionDisplay device

A power tool system and method of using the same is provided. The system can include a programmable microprocessor device including at least one input mechanism, and a memory having instructions and / or other information. The system can also include a display; at least one power tool having at least one sensor operable for monitoring a parameter associated with operation of the power tool. The system can further include a communications device connectable in signal communication with both the programmable microprocessor device and the at least one sensor and program instructions. The method can include the steps of (i) using stored program instructions to generate power tool related information on at least one display and (ii) collecting power tool related data using a programmable microprocessor.

Owner:HEALTH HERO NETWORK

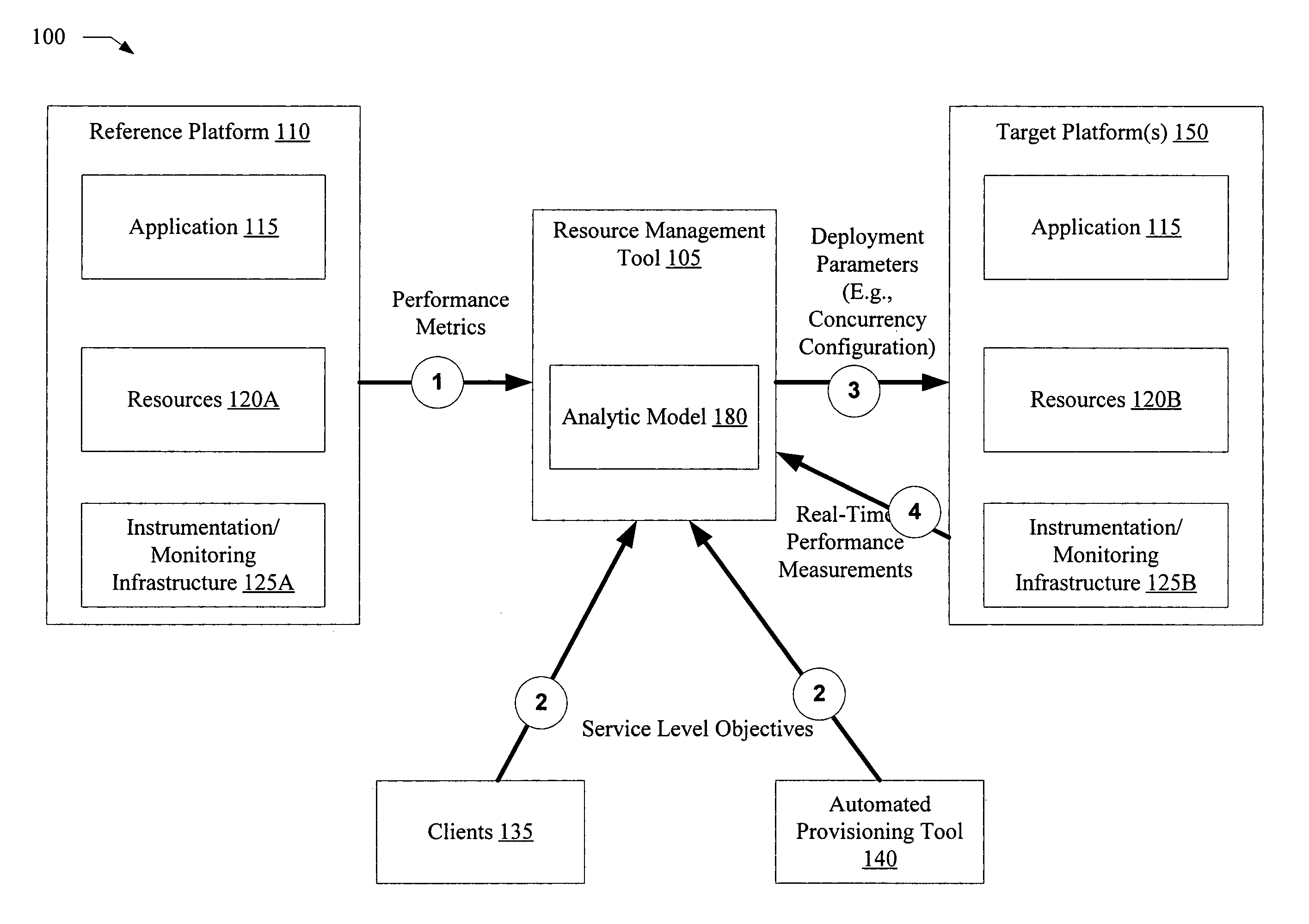

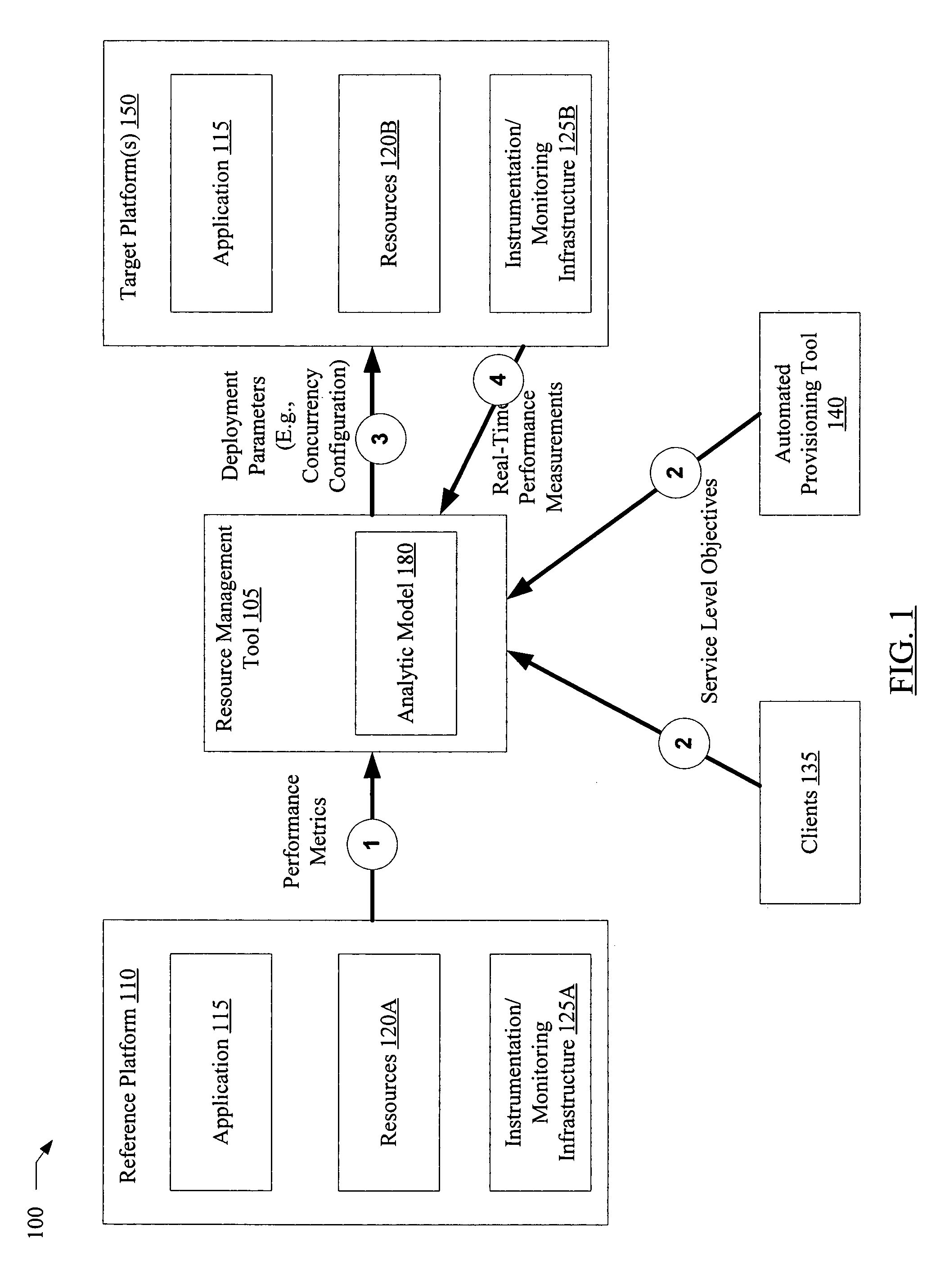

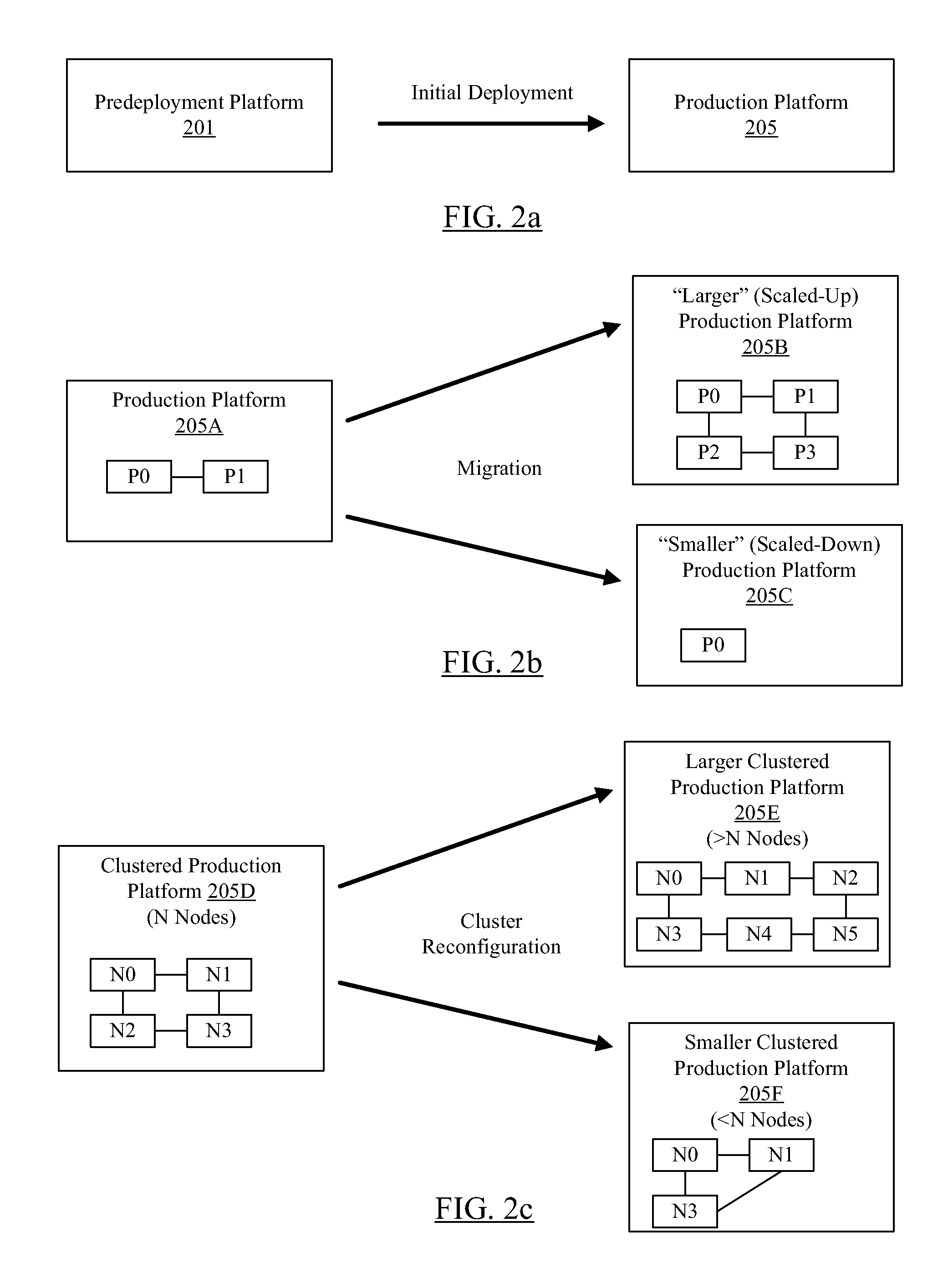

Automated concurrency configuration of multi-threaded programs

InactiveUS7757214B1Accurately reflectImprove the level ofDigital computer detailsSpecific program execution arrangementsAnalytic modelProgram instruction

A system for automated concurrency configuration of multi-threaded programs comprises one or more processors and memory coupled to the processors. The memory stores program instructions executable by the processors to implement a resource management tool. The resource management tool is configured to determine respective target values for one or more concurrency configuration parameters to be set in a deployment of an application using an analytic model and a set of performance metrics obtained from the application (e.g., values of throughput, response times, and corresponding resource utilization measurements), and to deploy the application with the concurrency configuration parameters set to the target values.

Owner:SYMANTEC OPERATING CORP

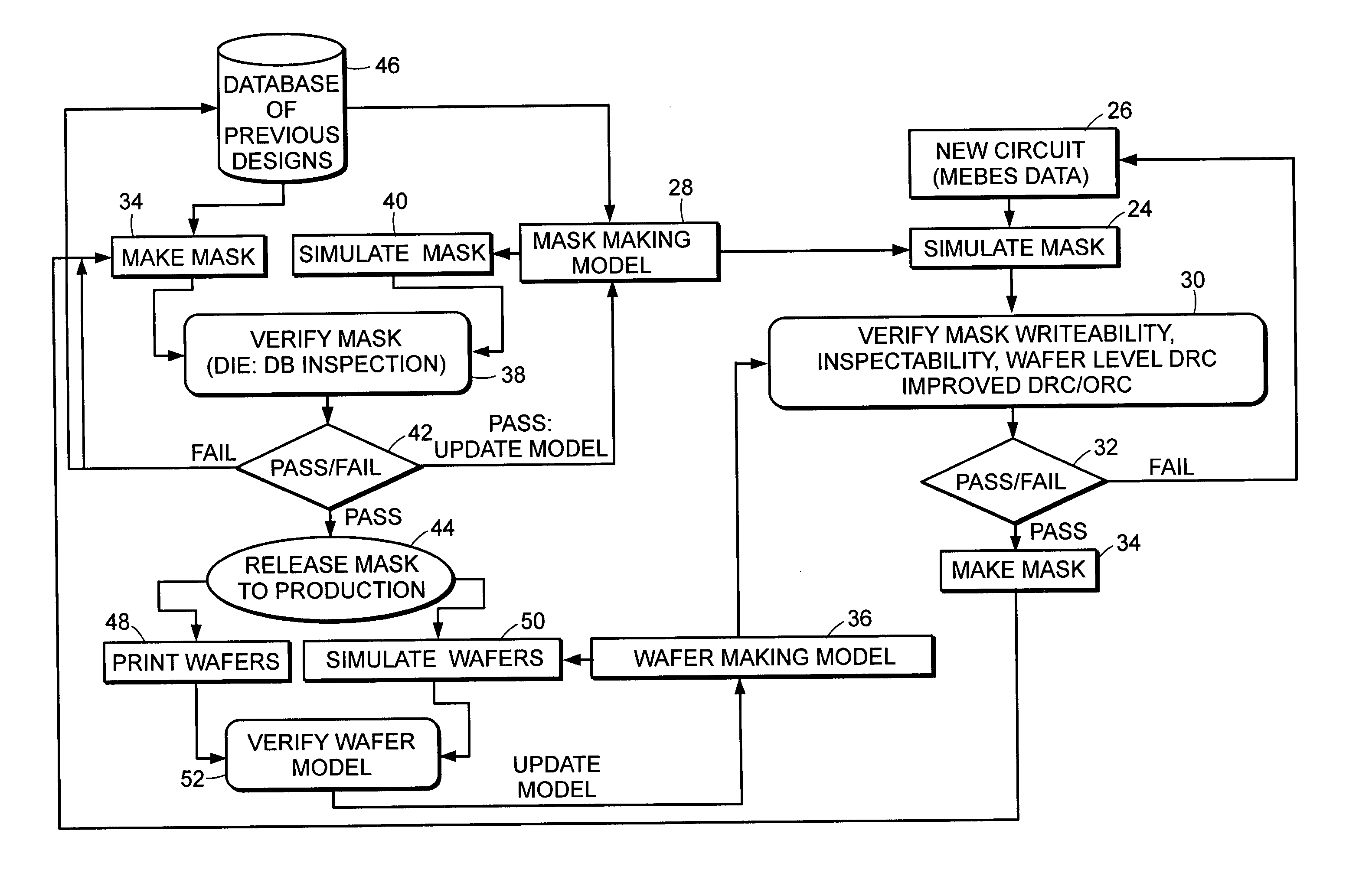

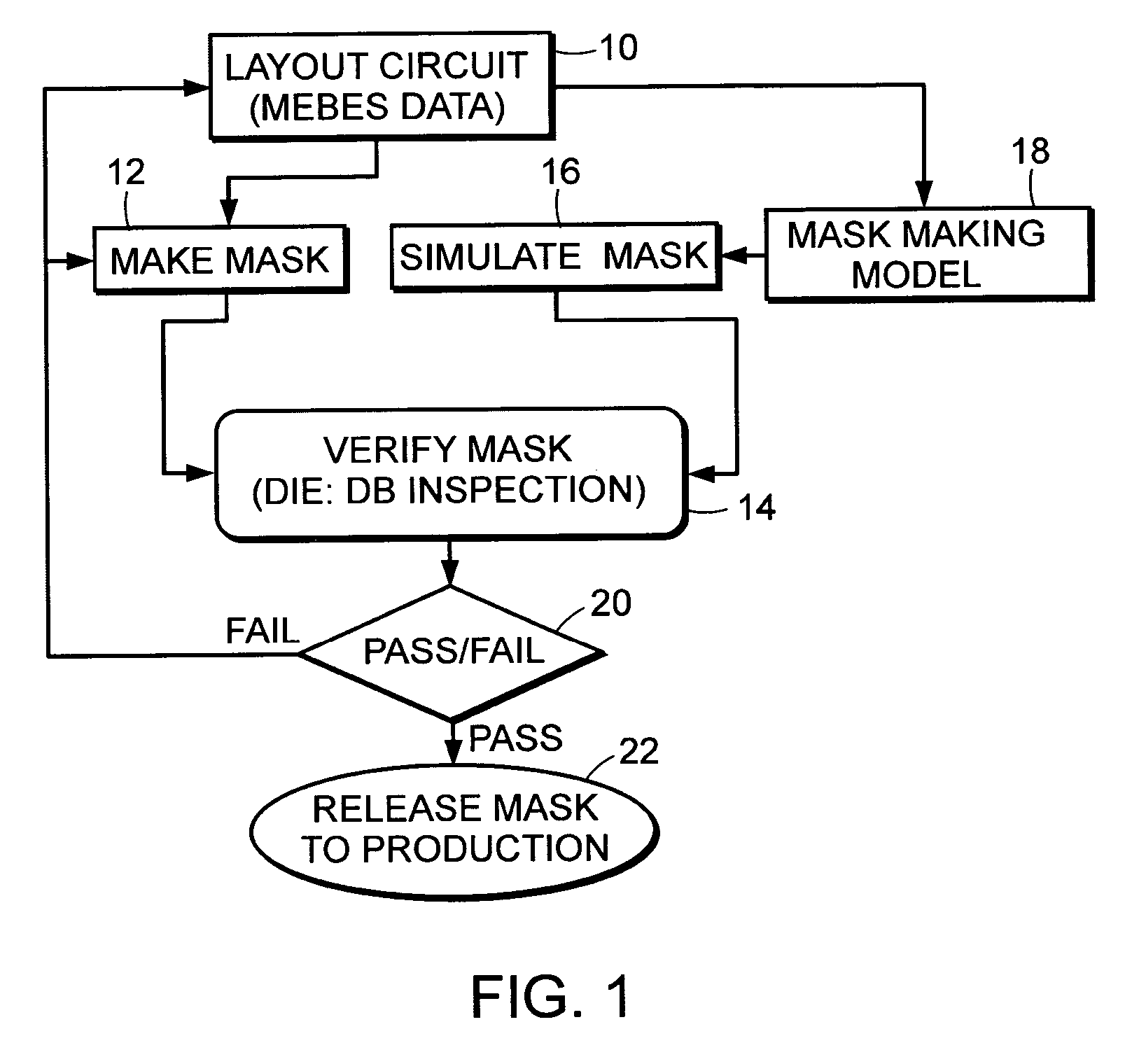

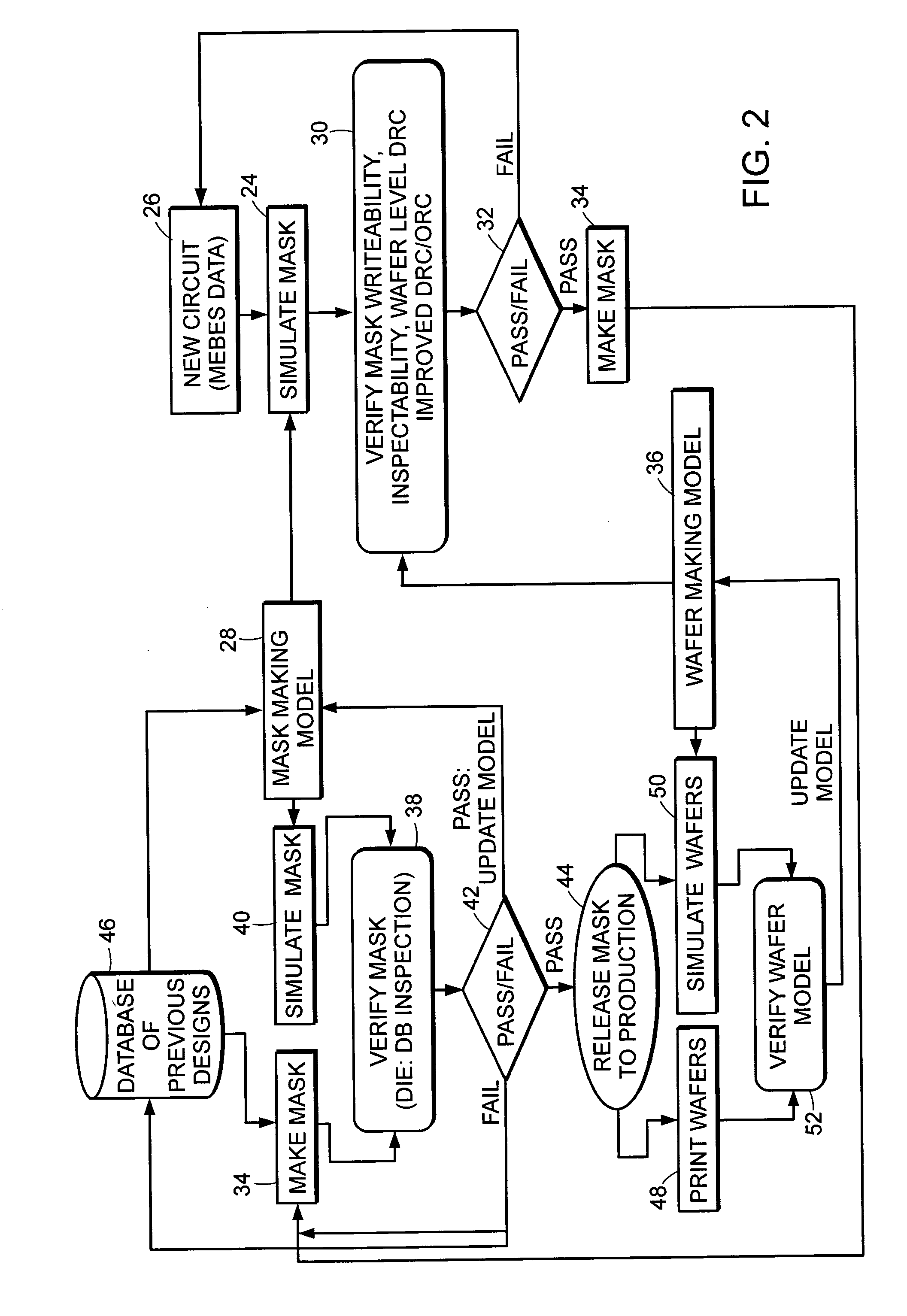

Methods, systems, and carrier media for evaluating reticle layout data

ActiveUS20060062445A1Forming accuratelyCharacter and pattern recognitionCAD circuit designProgram instructionComputer science

Various computer-implemented methods are provided. One method for evaluating reticle layout data includes generating a simulated image using the reticle layout data as input to a model of a reticle manufacturing process. The simulated image illustrates how features of the reticle layout data will be formed on a reticle by the reticle manufacturing process. The method also includes determining manufacturability of the reticle layout data using the simulated image. The manufacturability is a measure of how accurately the features will be formed on the reticle. Also provided are various carrier media that include program instructions executable on a computer system for performing a method for evaluating reticle layout data as described herein. In addition, systems configured to evaluate reticle layout data are provided. The systems include a computer system and a carrier medium that includes program instructions executable on the computer system for performing method(s) described herein.

Owner:KLA TENCOR TECH CORP

Modular microprocessor-based power tool system

InactiveUS7613590B2Turning machine accessoriesTesting/calibration apparatusProgram instructionDisplay device

A power tool system and method of using the same is provided. The system can include a programmable microprocessor device including at least one input mechanism, and a memory having instructions and / or other information. The system can also include a display; at least one power tool having at least one sensor operable for monitoring a parameter associated with operation of the power tool. The system can further include a communications device connectable in signal communication with both the programmable microprocessor device and the at least one sensor and program instructions. The method can include the steps of (i) using stored program instructions to generate power tool related information on at least one display and (ii) collecting power tool related data using a programmable microprocessor.

Owner:HEALTH HERO NETWORK

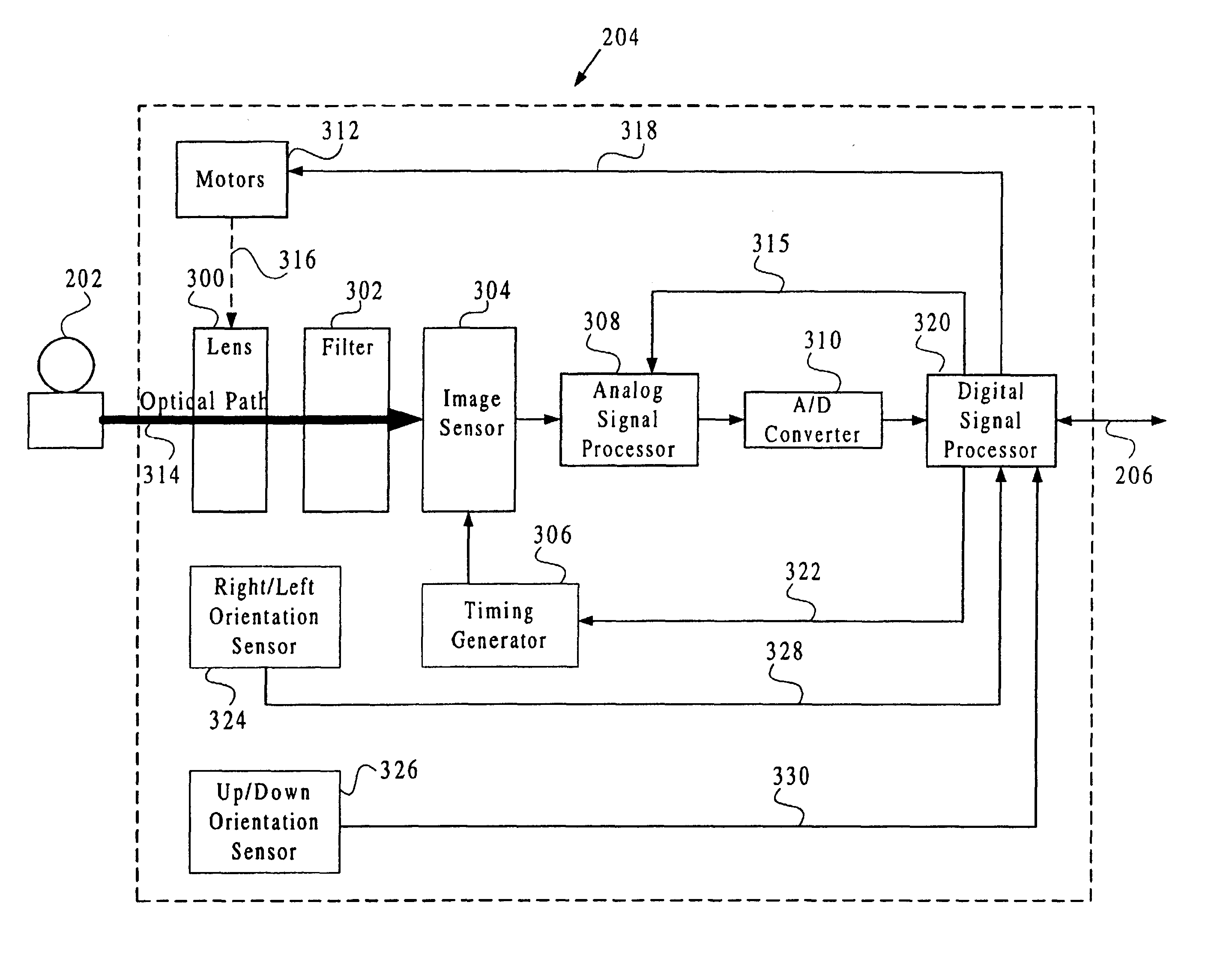

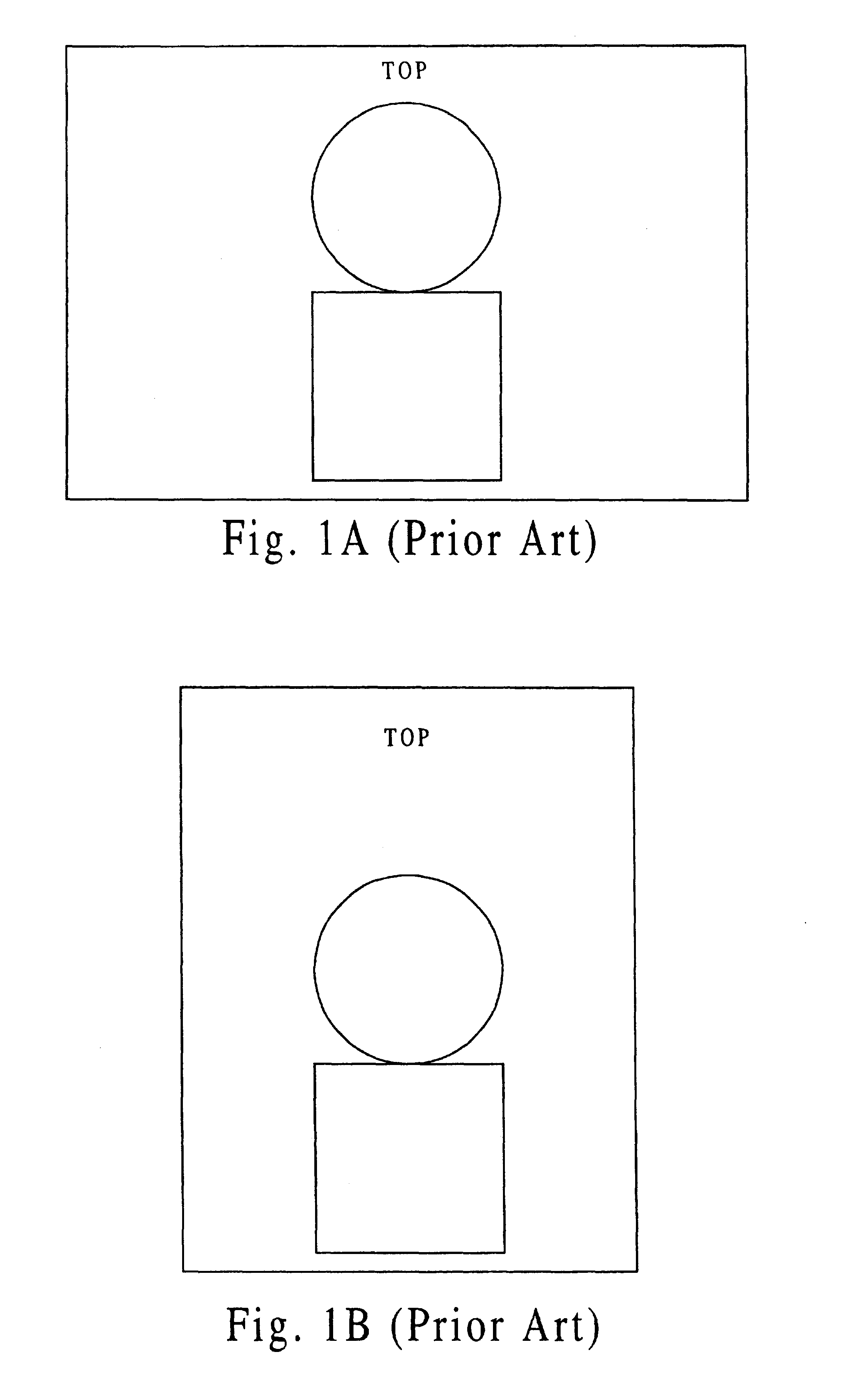

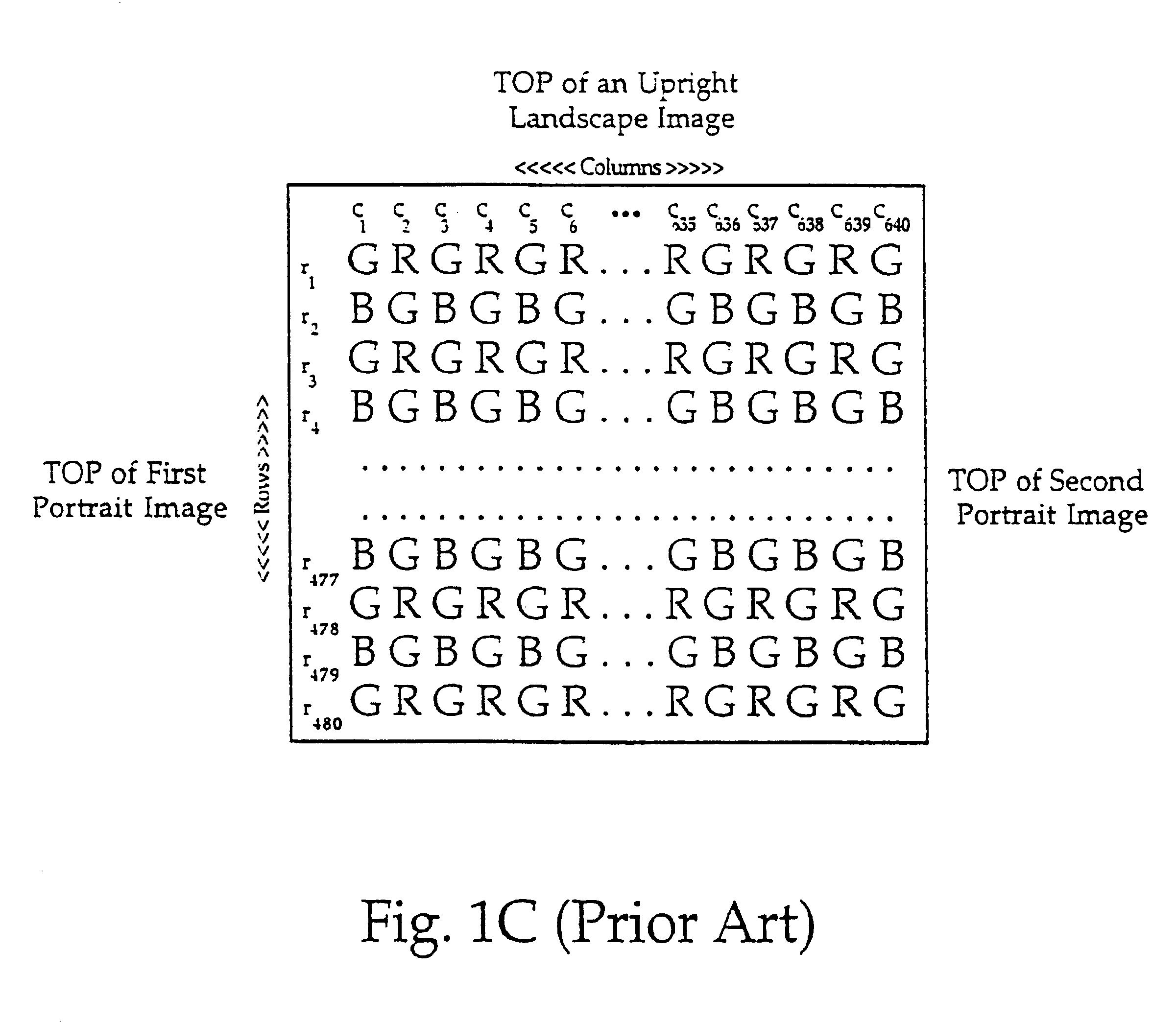

Apparatus and method for rotating the display orientation of a captured image

InactiveUSRE38896E1Television system detailsTelevision system scanning detailsImaging processingProgram instruction

The apparatus of the present invention preferably comprises an image sensor, an orientation sensor, a memory and a processing unit. The image sensor is used for generating captured image data. The orientation sensor is coupled to the image sensor, and is used for generating signals relating to the position of the image sensor. The memory, has an auto-rotate unit comprising program instructions for transforming the captured image data into rotated image data in response to the orientation sensor signals. The processing unit, executes program instructions stored in the memory, and is coupled to the image sensor, the orientation sensor and the memory. The method of the present invention preferably comprises the steps of: generating image data representative of an object with an image sensor; identifying an orientation of the image sensor relative to the object during the generating step; and selectively transferring the image data to an image processing unit in response to the identifying step.

Owner:APPLE INC

Automated administration of network-based contests

InactiveUS20070244585A1Adjust in timeVideo gamesSelective content distributionProgram instructionThe Internet

A system for automated administration of network-based contests includes one or more processors and memory coupled to the processors, where the memory stores program instructions executable by the processors to implement a contest manager. The contest manager is configured to receive a plurality of contest entries over a network such as the Internet for a contest, and to administer the contest in an automated manner in accordance with one or more contest specifications also received over the network.

Owner:OATH INC

Network-based contest creation

InactiveUS20070244570A1DelayDelay minimizationComputer controlOffice automationProgram instructionComputer science

A system for network-based contest creation includes one or more processors and memory coupled to the processors, where the memory stores program instructions executable by the processors to implement a contest manager. The contest manager is configured to receive a request via a network to establish a contest, and to automatically establish the contest in accordance with one or more contest specifications included in the request.

Owner:OATH INC

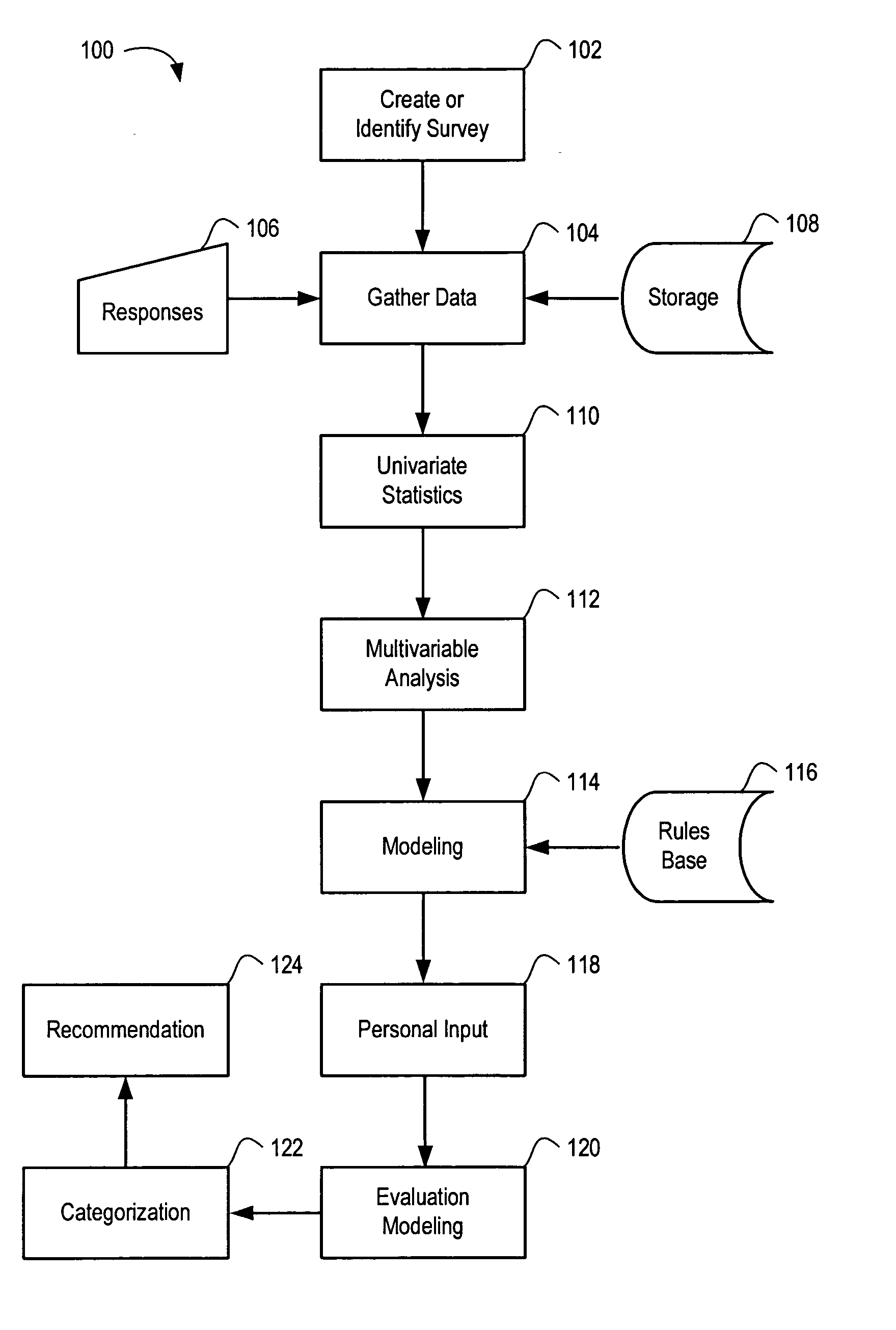

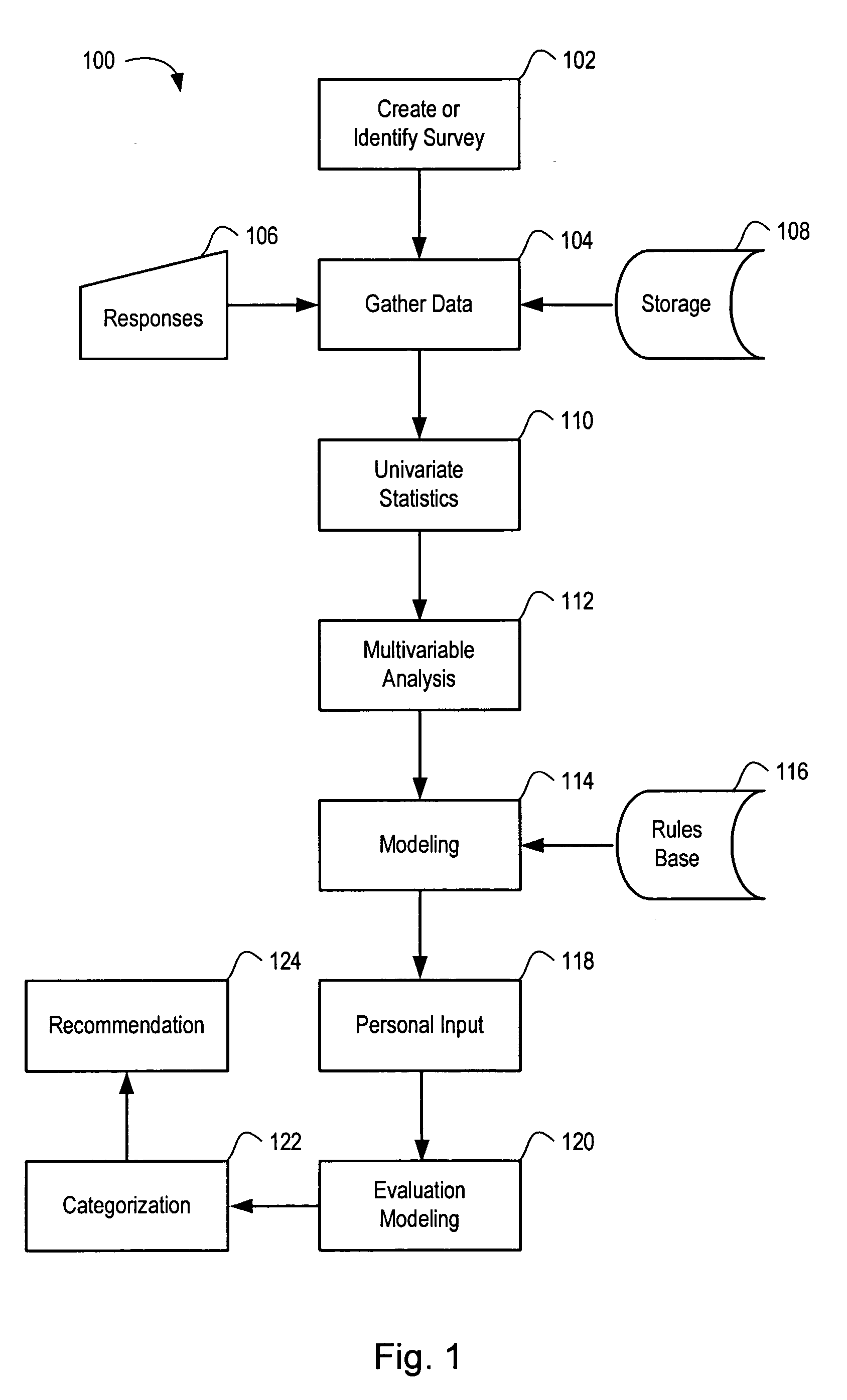

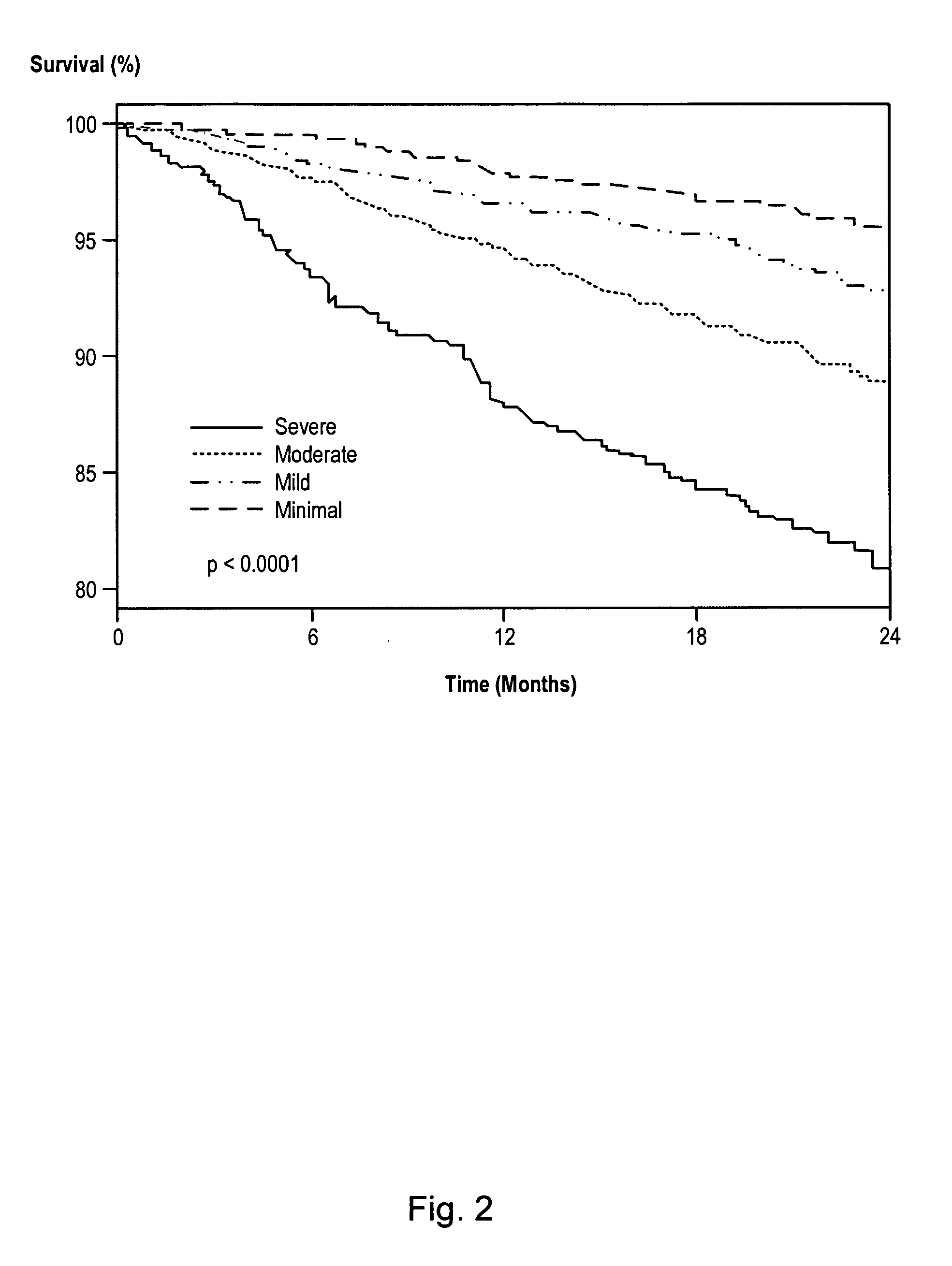

Systems and methods for risk stratification of patient populations

ActiveUS20050203773A1Disseminate reduced redundancy requestsReduce redundancyAnalogue computers for chemical processesComputer-assisted medical data acquisitionProgram instructionHealth risk

A statistical processing system includes a server operably configured with program instructions implementing a plurality of statistical models to at least one of (a) predict a health outcome based on questionnaire responses, (b) assist a patient's choice of therapeutic modality based on questionnaire responses, and (c) assess a health risk or status based on questionnaire responses. Also provided is a research agency communicating with the server and contracted to provide the statistical models using a visual interface communicated by the server. The server is configured to analyze requests received from users relating to a plurality of said statistical models to reduce redundancy in requests for patient data.

Owner:TERUMO MEDICAL CORP

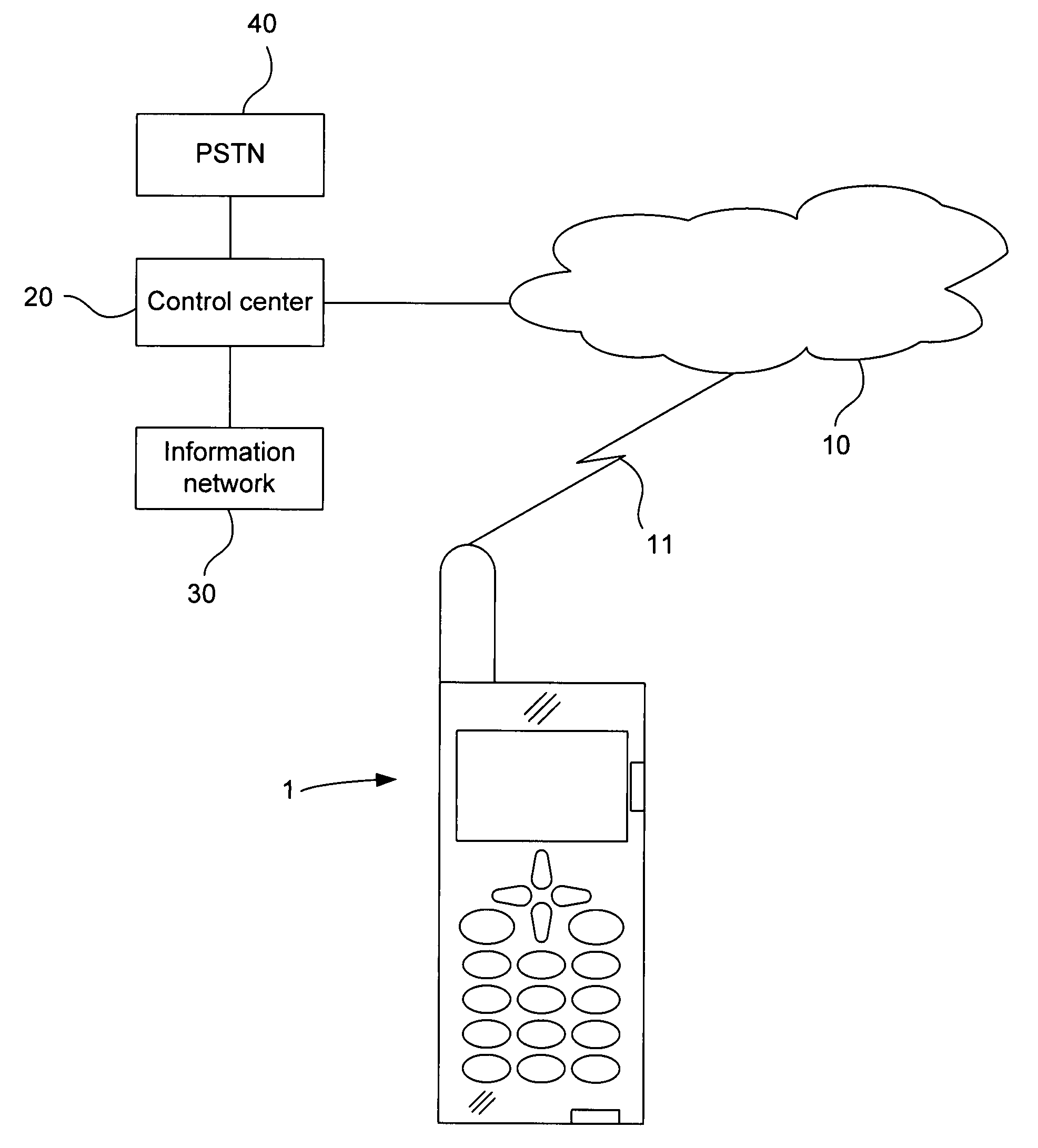

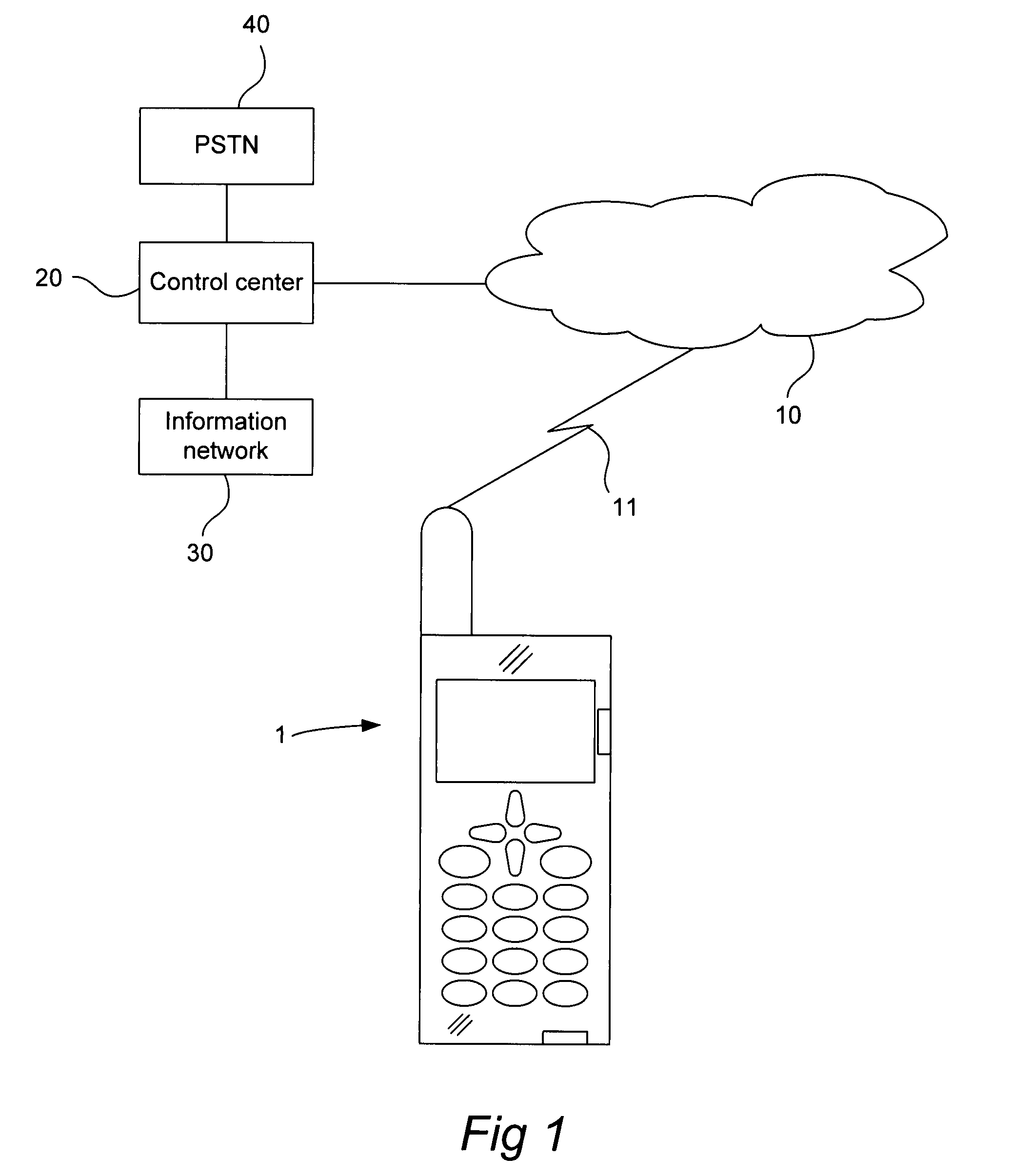

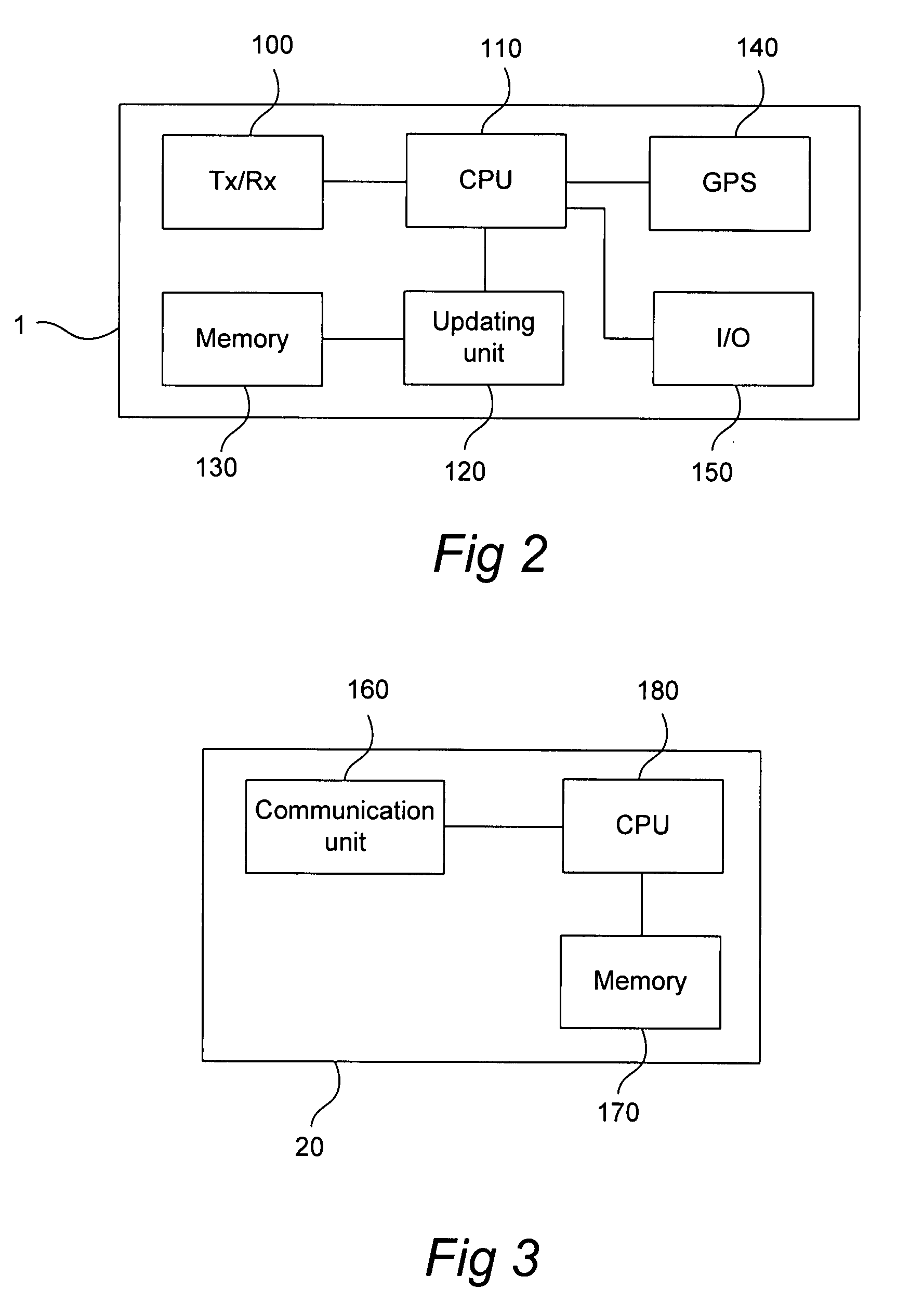

Method for Disabling a Mobile Device

InactiveUS20080293397A1Unauthorized useSubstation equipmentAutomatic exchangesProgram instructionMobile device

Methods for disabling a mobile device (1) having communication capabilities. A message comprising disabling data for disabling at least one functionality of the mobile device (1) is transmitted from a control center (2) to the mobile device (1). The disabling data comprises data for altering program instructions for at least one functionality of the mobile device (1), thereby disabling said functionality. A mobile device (1) and a control center (20) are configured for implementing the methods.

Owner:SONY ERICSSON MOBILE COMM AB

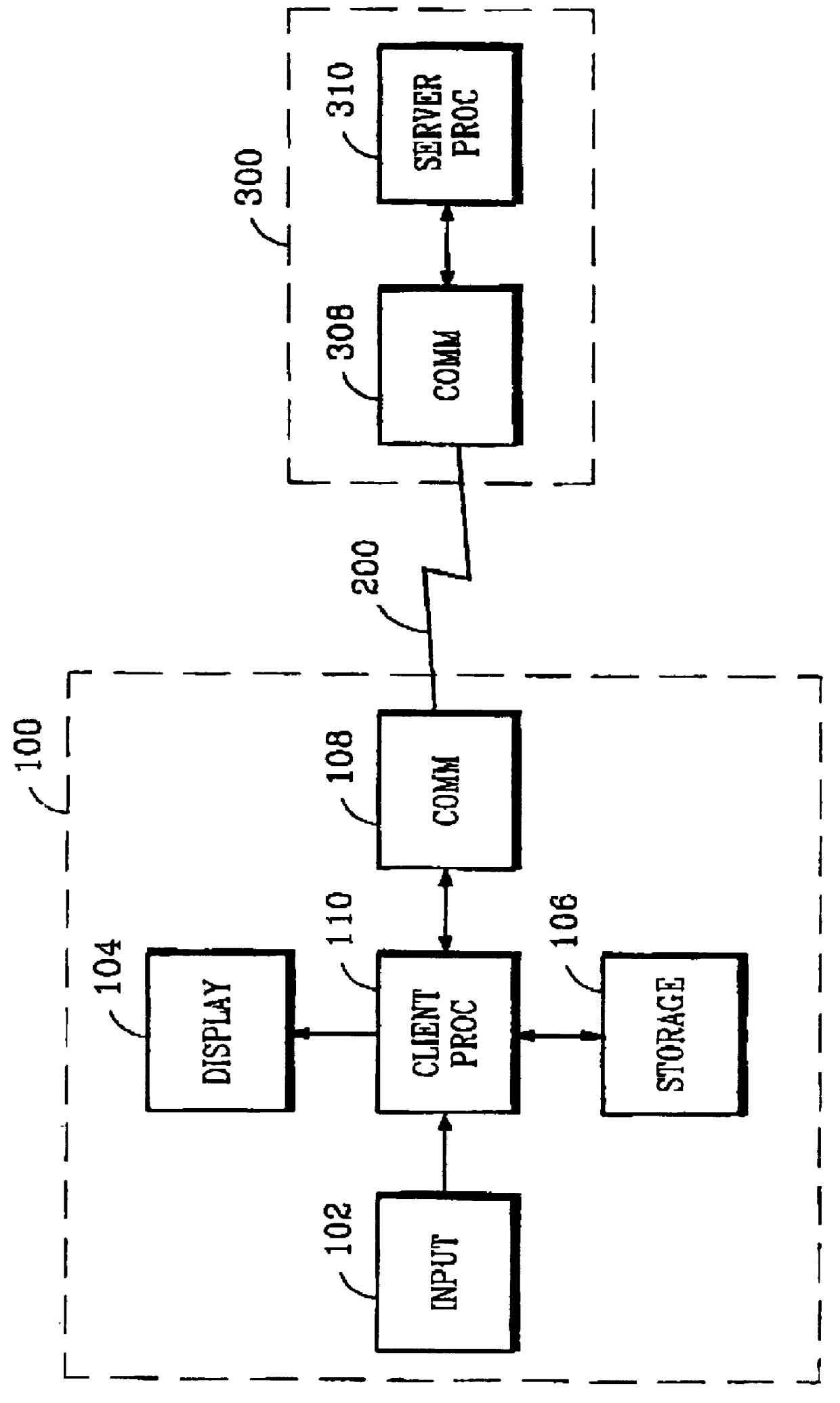

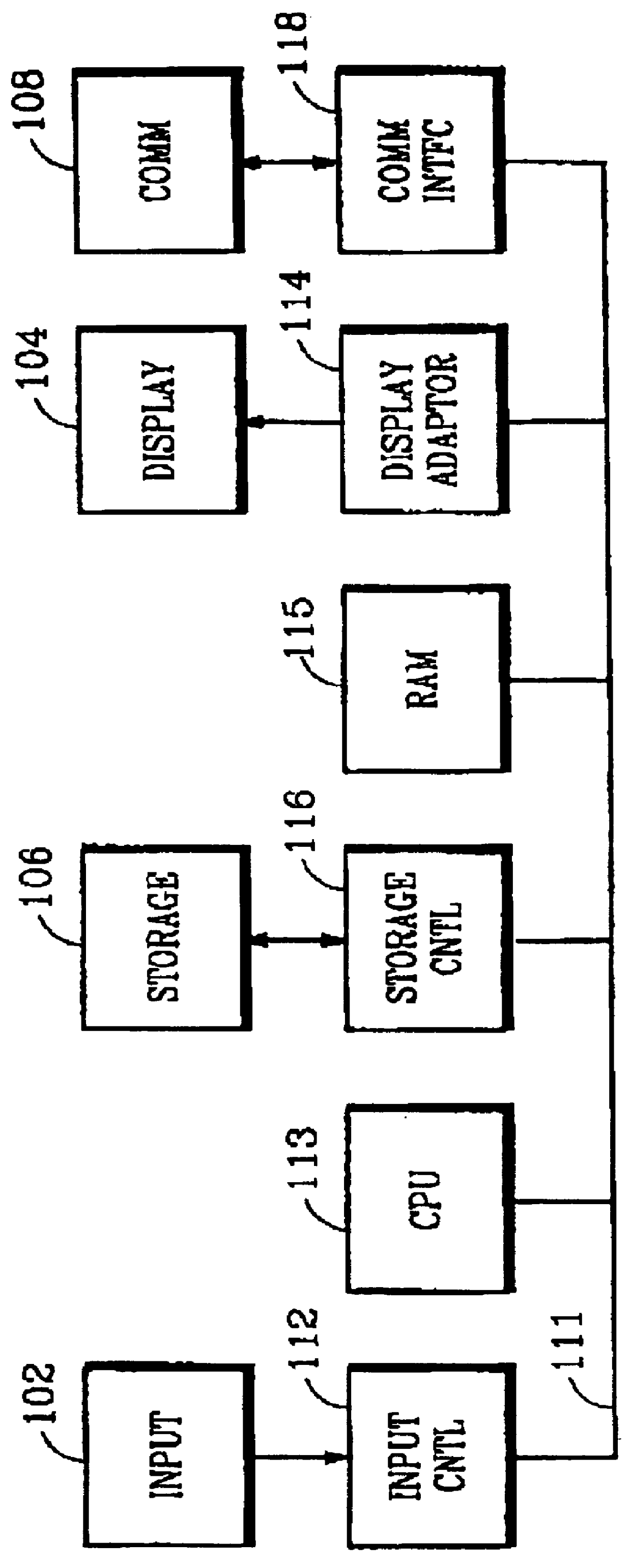

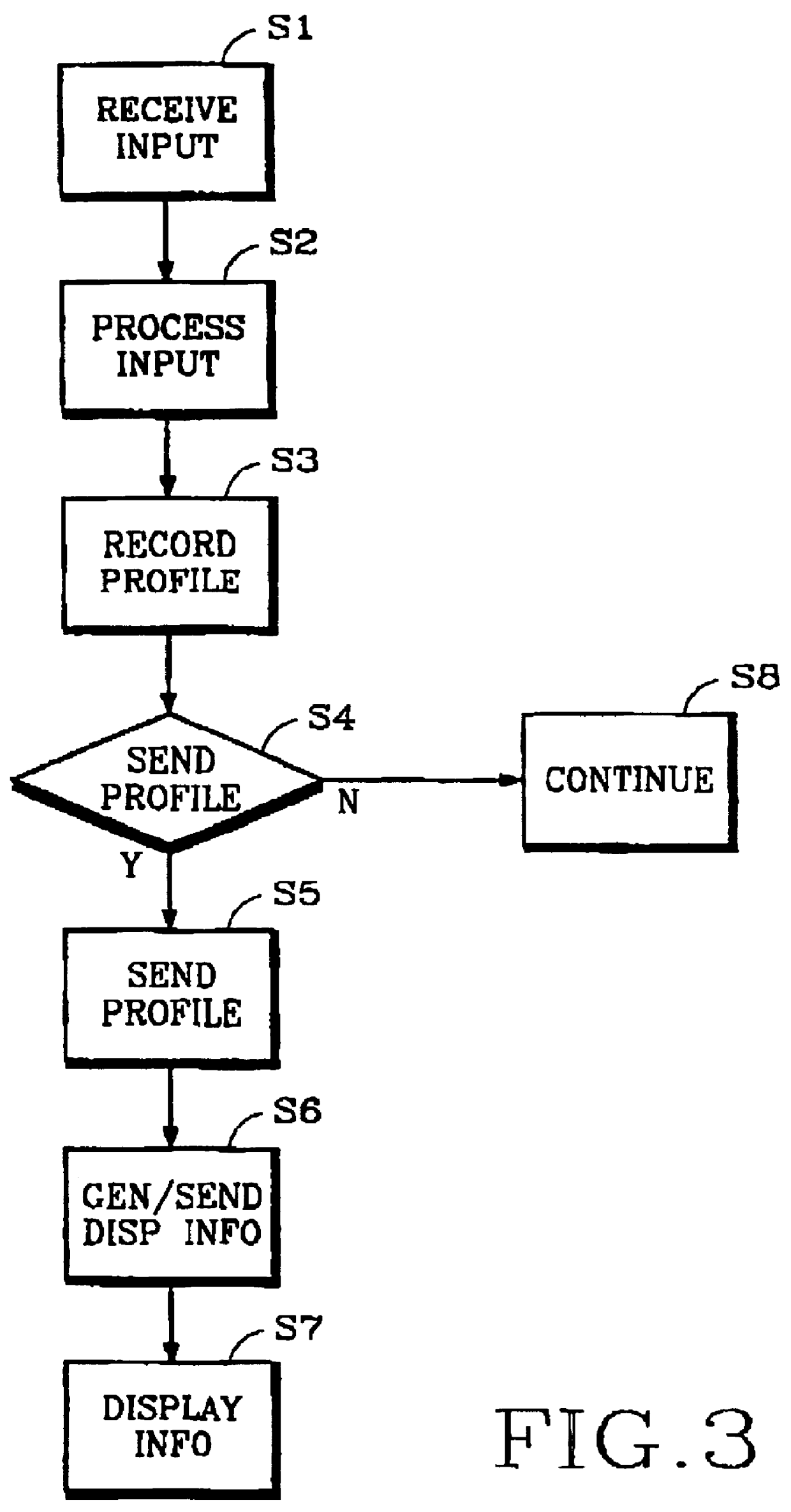

Method and apparatus for distributing over a network unsolicited information to a targeted audience

InactiveUS6119164AAvoid confictMultiple digital computer combinationsElectric digital data processingProgram instructionInformation transmission

In response to input received from an operator, a workstation fully performs programmed instructions to carry out operator requests represented by the input. In addition, the workstation also records profile information derived from data representing operator choices and sends that profile information to a server along a communications path such as a telephonic link to a publicly-accessible network. The server analyzes the profile information, generates display information in response to the profile information, and returns display information along the communications path to the workstation. In turn, the workstation presents the display information to the operator. In this manner, information customized according to profiles can be delivered to people and organizations most likely to be interested in the information content.

Owner:FULL CIRCLE SOFTWARE

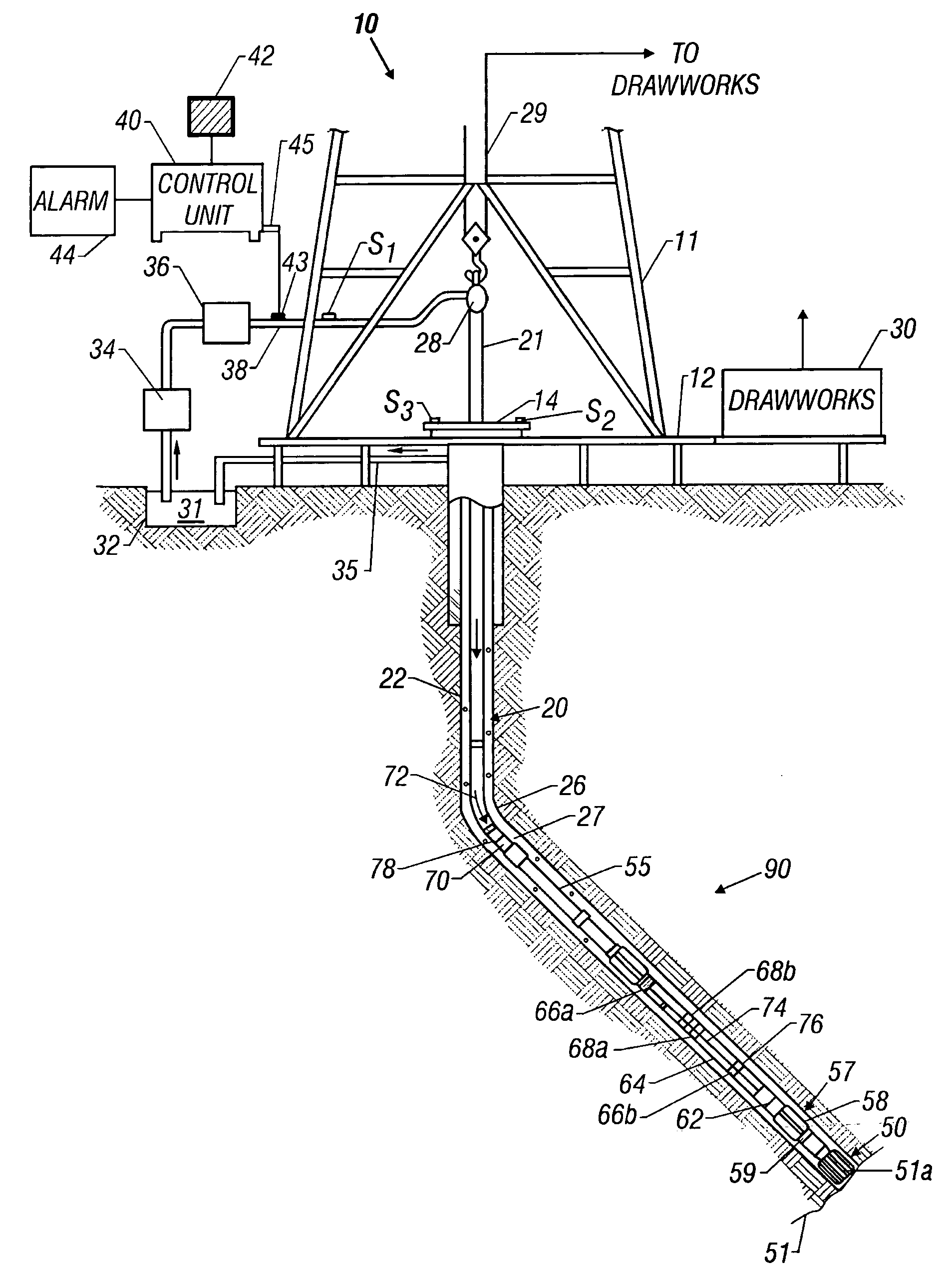

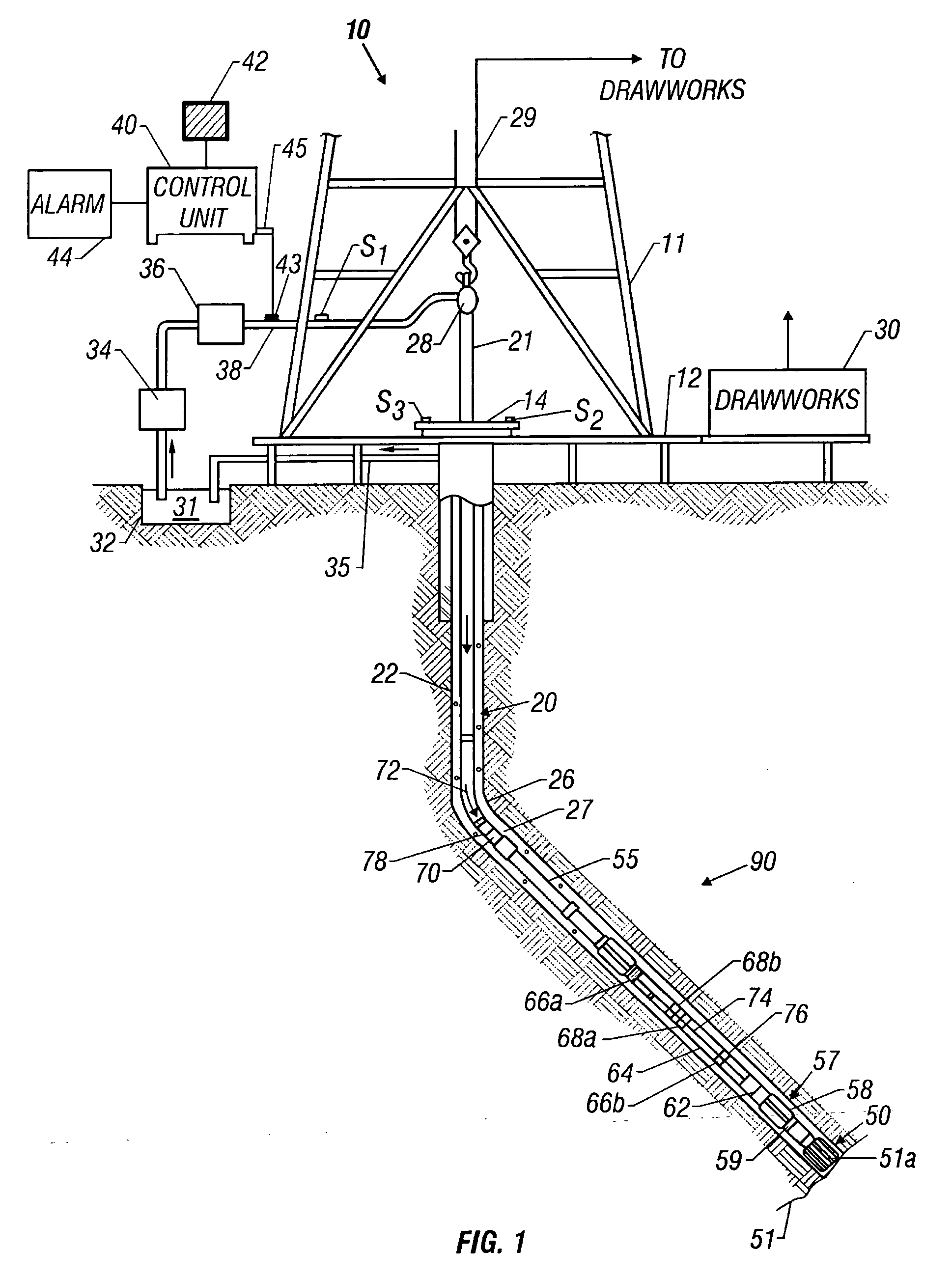

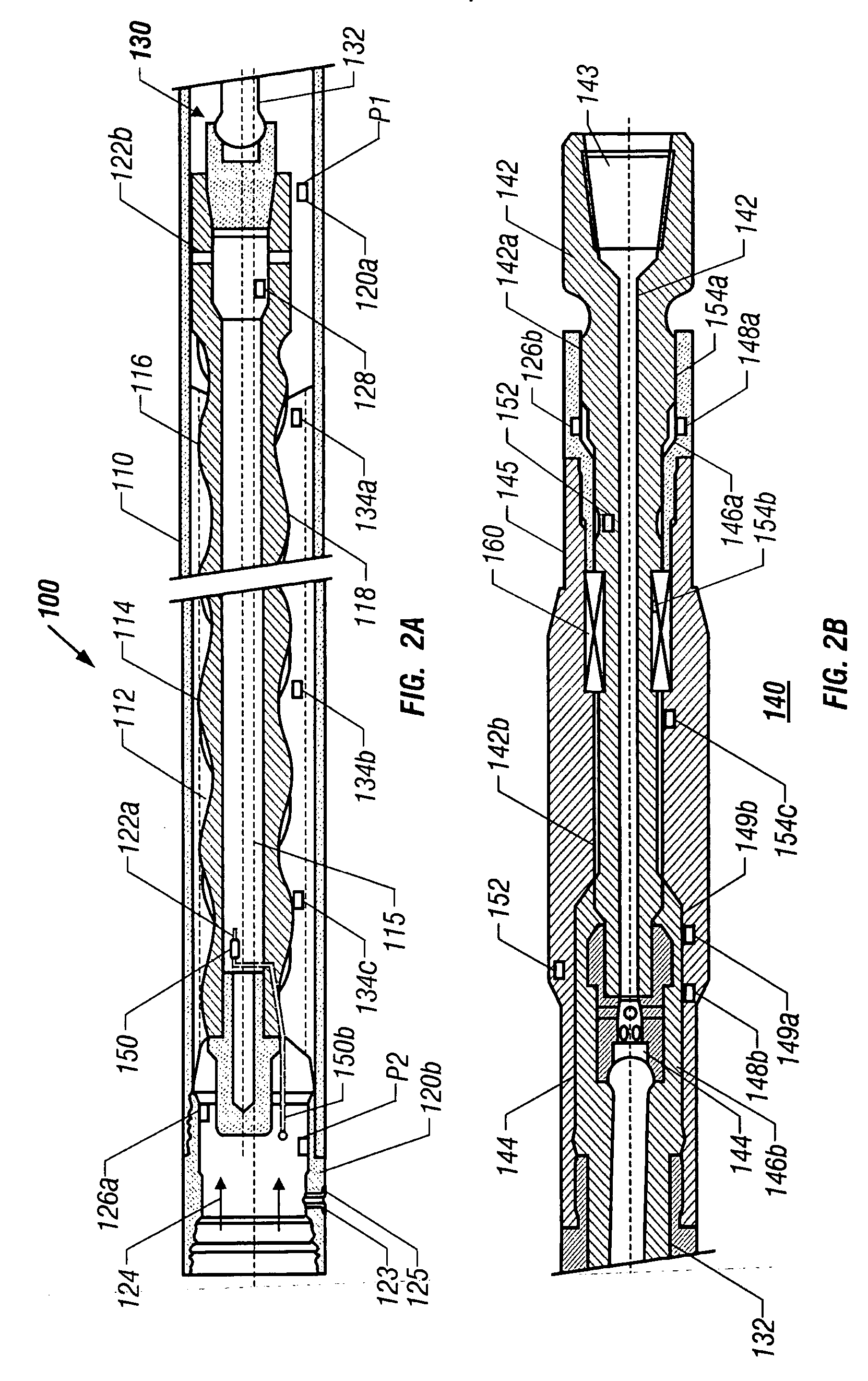

Method and apparatus for enhancing directional accuracy and control using bottomhole assembly bending measurements

A system for drilling a well comprises a tubular member having a bottomhole assembly at a bottom end thereof disposed in a wellbore. A first sensor is disposed in the bottomhole assembly at a predetermined axial location for detecting bending in a first axis and generating a first bending signal in response thereto, where the first axis is substantially orthogonal to a longitudinal axis of the bottomhole assembly. A second sensor is disposed in the bottomhole assembly at the predetermined axial location for detecting bending in a second axis and generating a second bending signal in response thereto, where the second axis is substantially orthogonal to the longitudinal axis. A processor receives the first bending signal and the second bending signal and relates the first bending signal and the second bending signal to a borehole curvature according to programmed instructions.

Owner:BAKER HUGHES INC

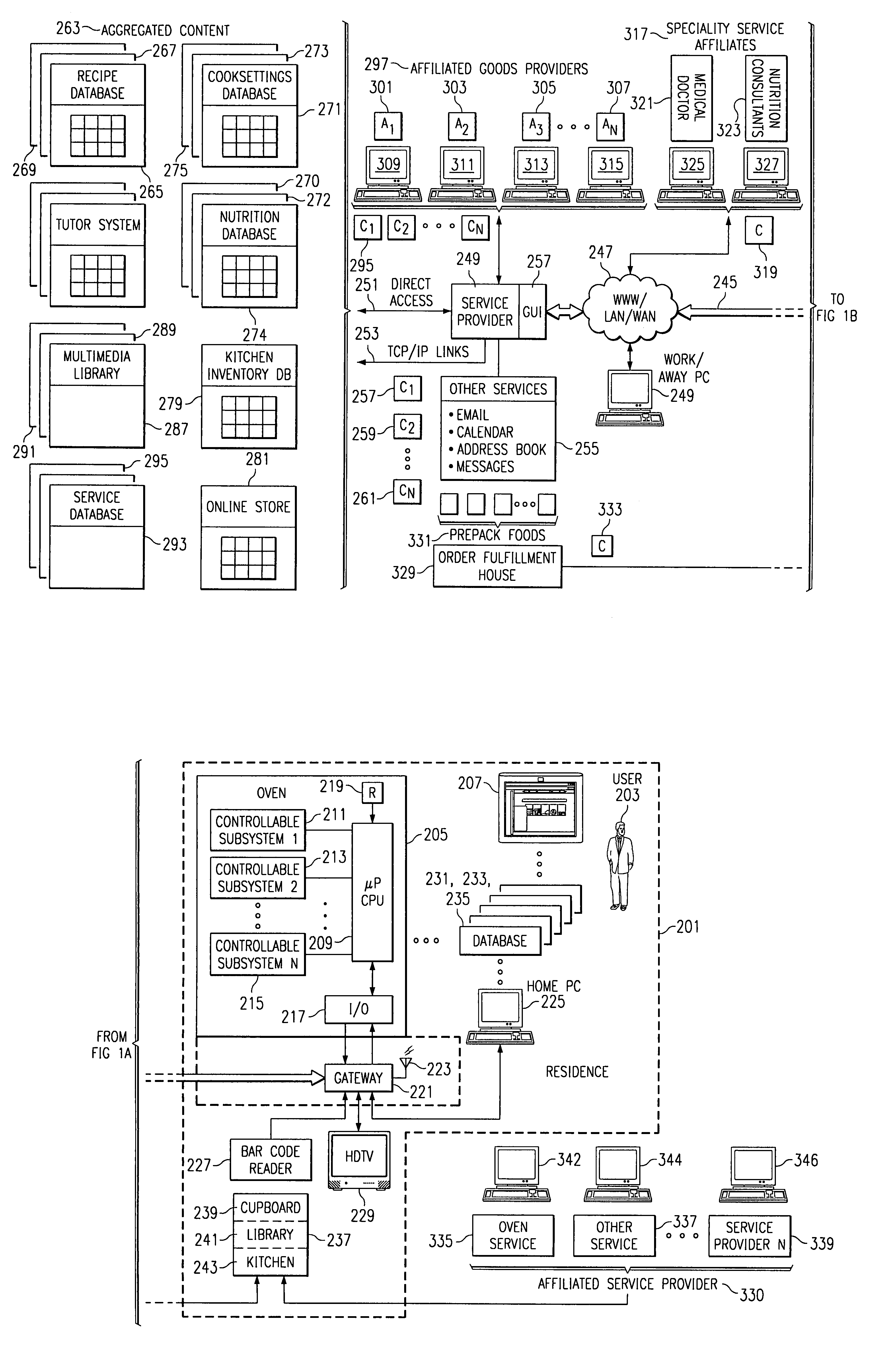

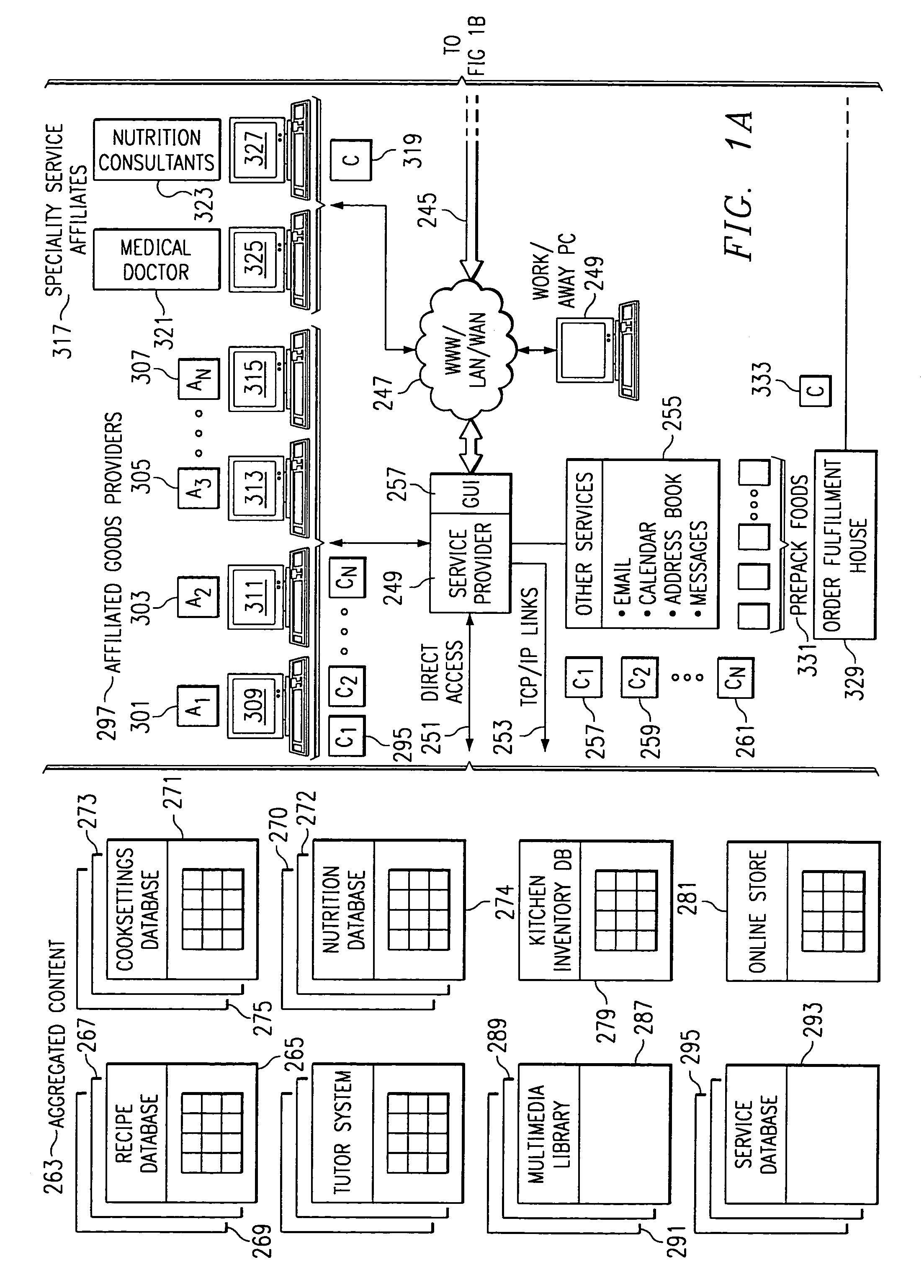

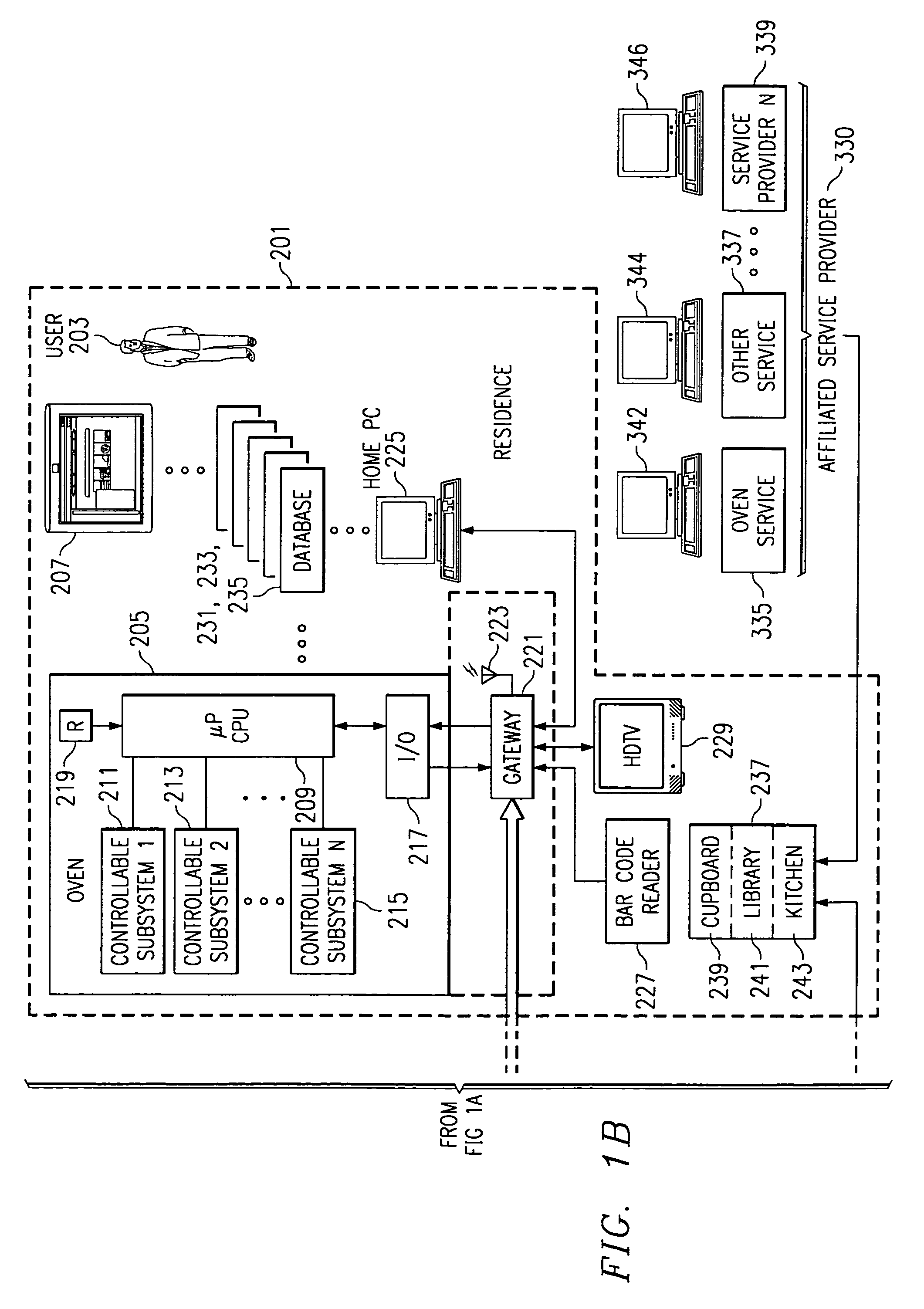

Rapid cooking oven with broadband communication capability to increase ease of use

An improved oven for use in a residence is described. The oven includes a cooking chamber, a programmable controller for executing program instructions, memory media for recording executable program instructions, and at least one controllable cooking system under control of the programmable controller, which provides a data-processing-controlled high speed cooking process which may be applied to food placed in the oven chamber. A plurality of cooking programs are recorded in the memory media of the oven. These define a plurality of high speed cooking routines available for use with the oven. A gateway server is communicatively coupled to the programmable controller. It manages the communication of digital content which is at least in-part related to operation and utilization of the improved oven. A broadband communication channel extends from a source of digital content, which is external to the residence, to the residence. The broadband communication channel delivers particular digital content related to the oven through the gateway server for distribution within the residence, including distribution to the programmable controller of the oven in order to facilitate cooking operations utilizing the oven.

Owner:TURBOCHEF TECH INC