Field programmable gata array (FPGA)-based metric floating-point multiplier design

A floating-point multiplier, decimal technology, used in instrumentation, computing, electrical digital data processing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

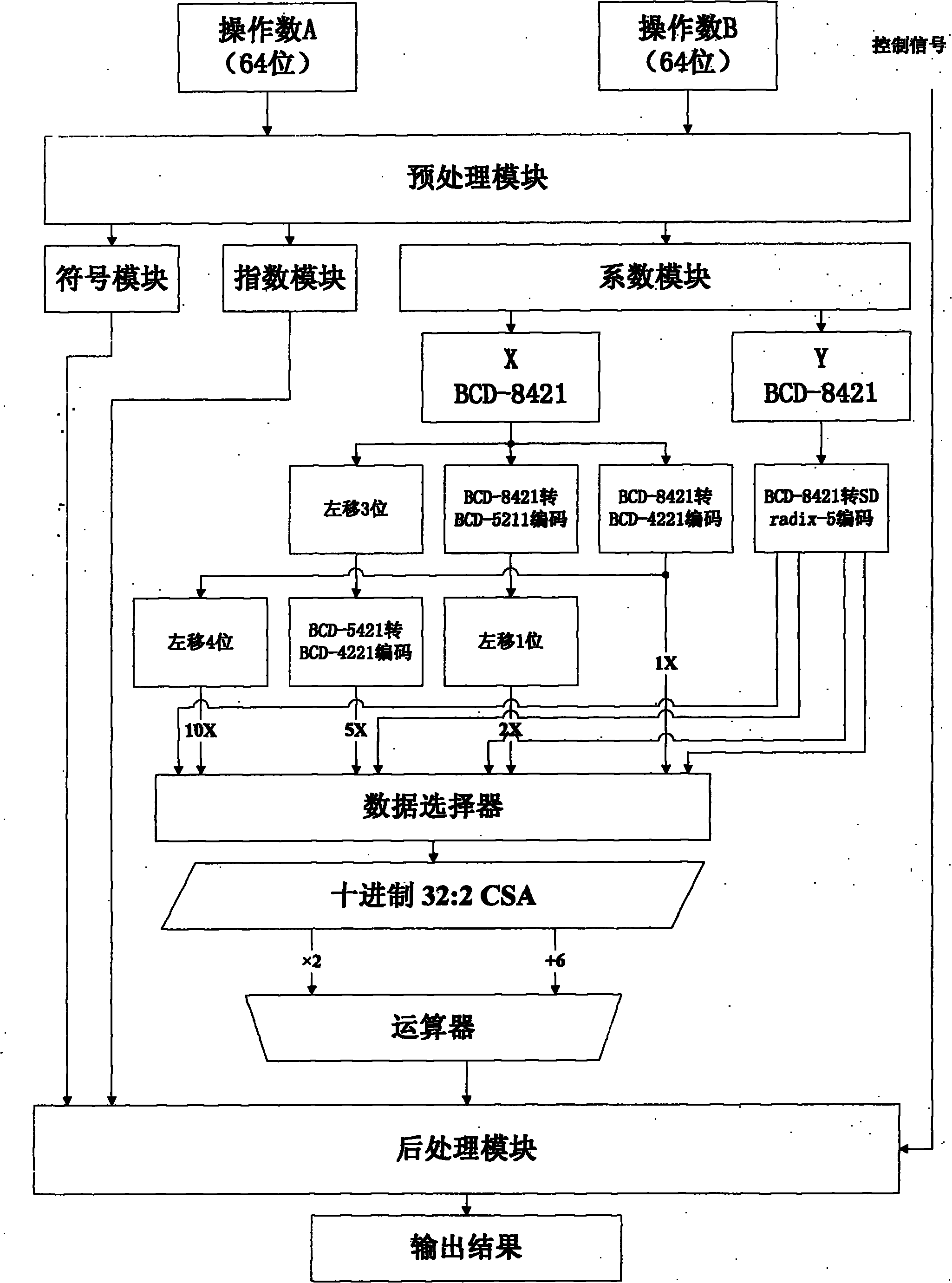

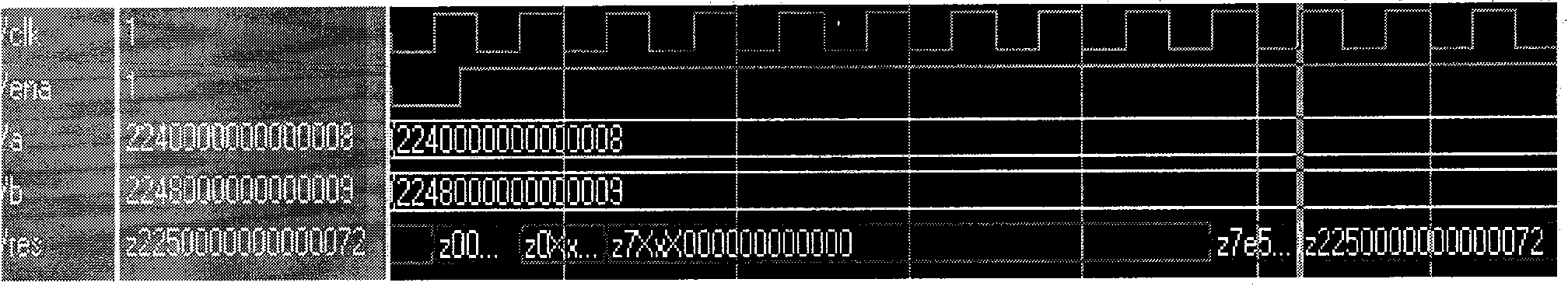

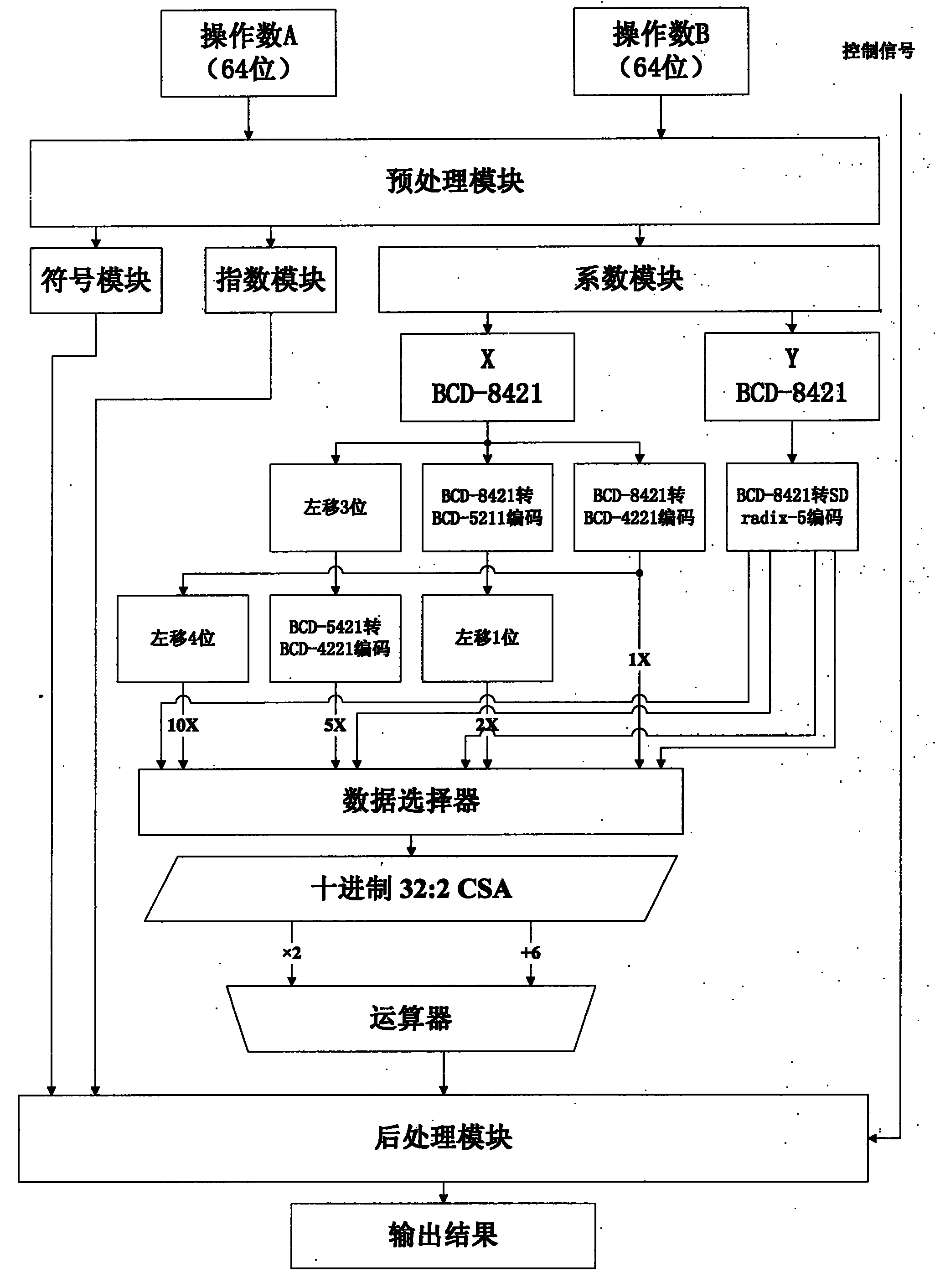

[0068] exist figure 1 In the process, firstly, the model of the decimal floating-point multiplier is designed according to the representation specification of the decimal floating-point number and the principle of multiplication, and then the algorithm is selected or written according to the specific functions that each module of the model needs to realize, and then according to the algorithm principle and logical expression and the whole The connection relationship of the system, using Verilog HDL hardware description language programming and Modelsim professional simulation software to compile and simulate to realize the system design, and finally download and verify on the FPGA platform, and realize the design of the decimal floating-point multiplier based on FPGA by hardware. The specific flow of decimal floating-point multiplication operation is as follows: first, two registers are designed to store the input operands, and then output to the preprocessing module for operan...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More