Approximate floating-point multiplier for neural network processor and floating-point multiplication

A floating-point multiplier and multiplication technology, which is applied in the field of neural network processors, can solve problems such as unsatisfactory, increased operating power consumption, and obstacles to the application of neural network processors, so as to achieve high performance and improve work energy efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below through specific embodiments in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

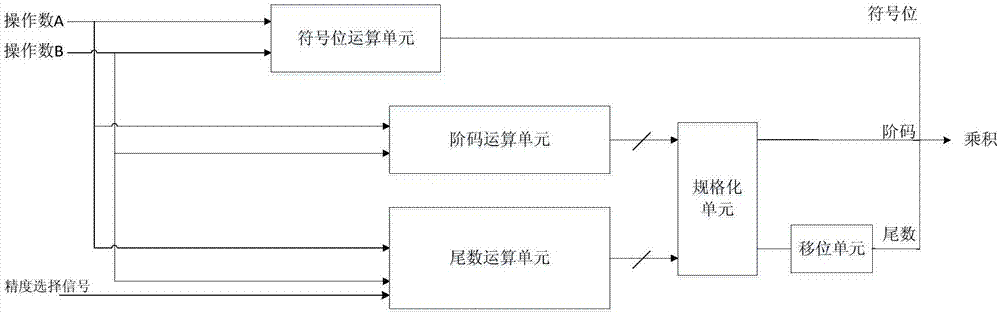

[0040] figure 1 It is a schematic structural diagram of an approximate floating-point multiplier according to an embodiment of the present invention. The approximate floating-point multiplier includes a sign bit operation unit, an exponent code operation unit, a mantissa operation unit, a normalization unit and a shift unit. Such as figure 1 As shown, the floating-point multiplier receives two operands A and B to be multiplied, and outputs the product (can be denoted as C). The operands A and B and their product are all floating-point numbers, and each floating-point number is store...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More