64-bit fixed and floating point multiplier unit supporting complex operation and subword parallelism

A complex number operation and complex number multiplication technology, applied in the field of 64-bit fixed-floating point multipliers, can solve the problems of increasing chip area and power consumption, rapid expansion of multiplier computing resources, and reducing performance, so as to reduce key path delays, The effect of reducing computing resource overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be described in further detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

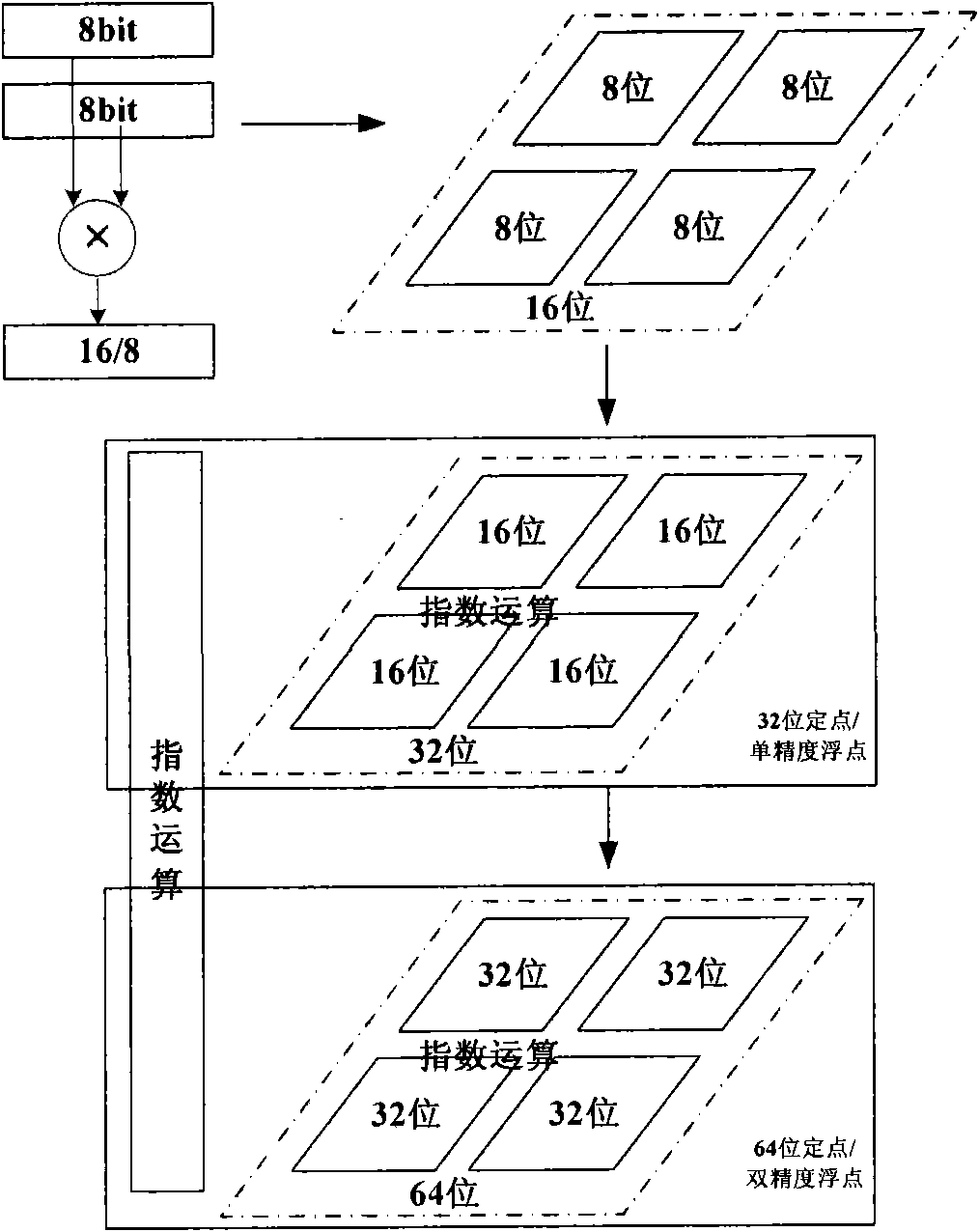

[0035] The 64-bit fixed-floating-point multiplier provided by the present invention is a fixed-floating-point multiplier that supports subword parallel and complex operations. The multiplier supports 8, 16, 32, and 64 fixed-point multiplication operations, and supports simplified IEEE754 standard Single / double-precision floating-point operations, and supports 32, 64-bit complex multiplication.

[0036] Firstly, the realization principle of the present invention is introduced below, which mainly includes subword integration scheme, optimized subword integration structure and complex multiplication operation.

[0037] 1), subword integration scheme

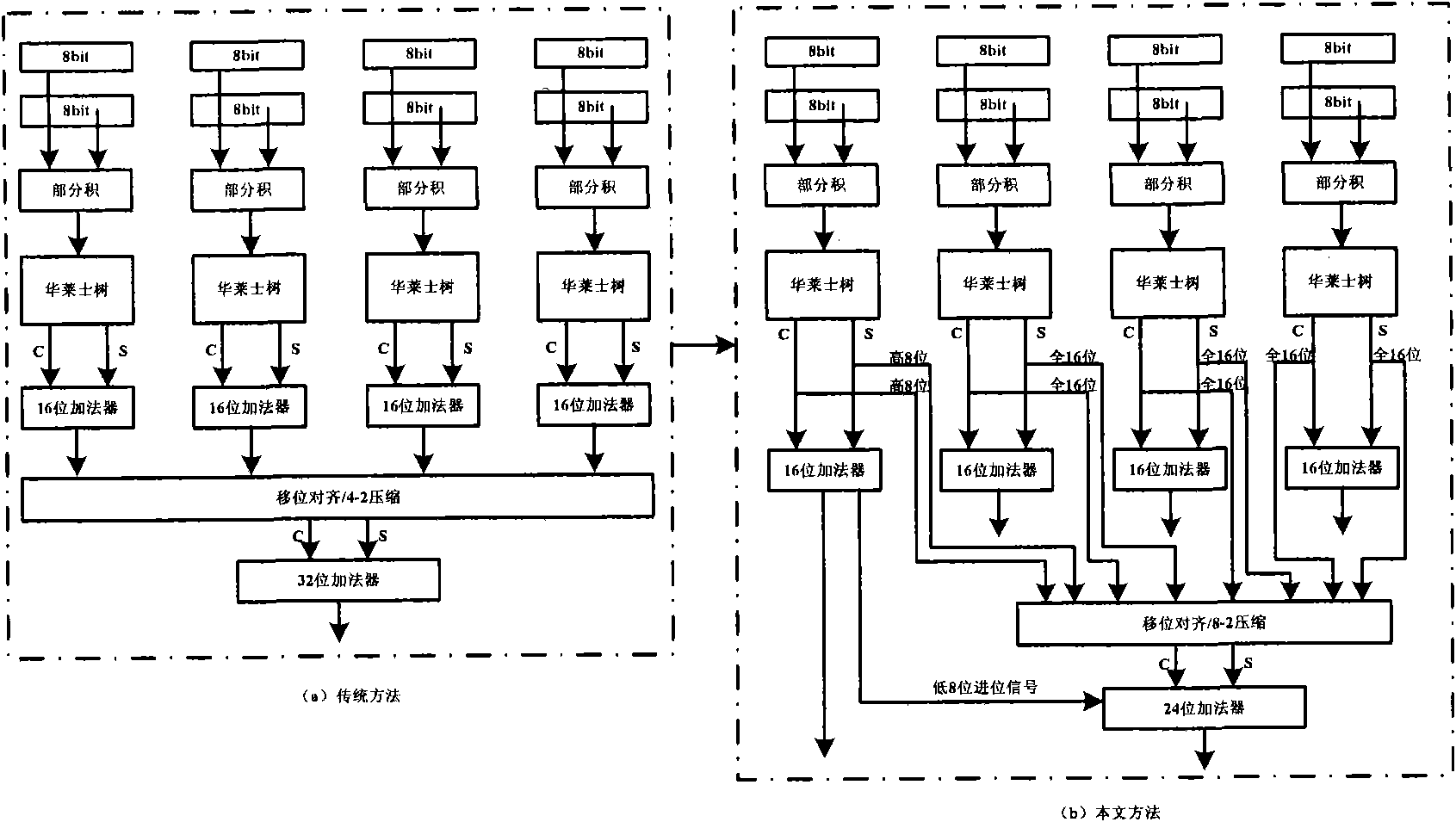

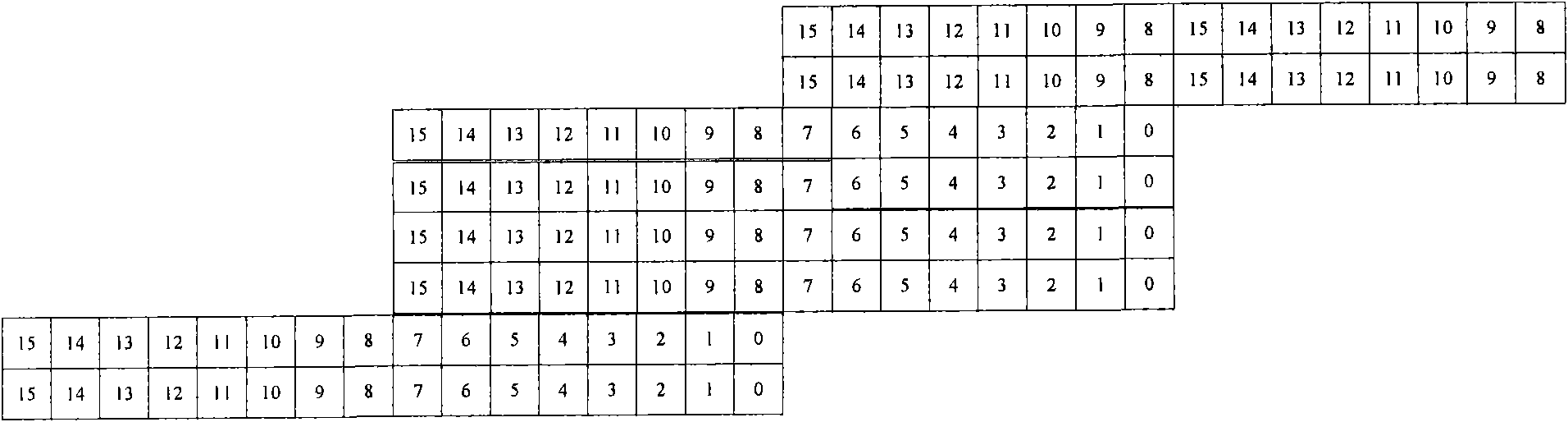

[0038] Subword integration refers to combining multipliers with smaller b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More