Fixed-point and floating-point operation part with shared multiplier structure in GPDSP

A floating-point operation and multiplier technology, which is applied in the calculation using the number system and the non-contact manufacturing equipment for calculation, etc. The effect of improving the utilization of hardware resources

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments.

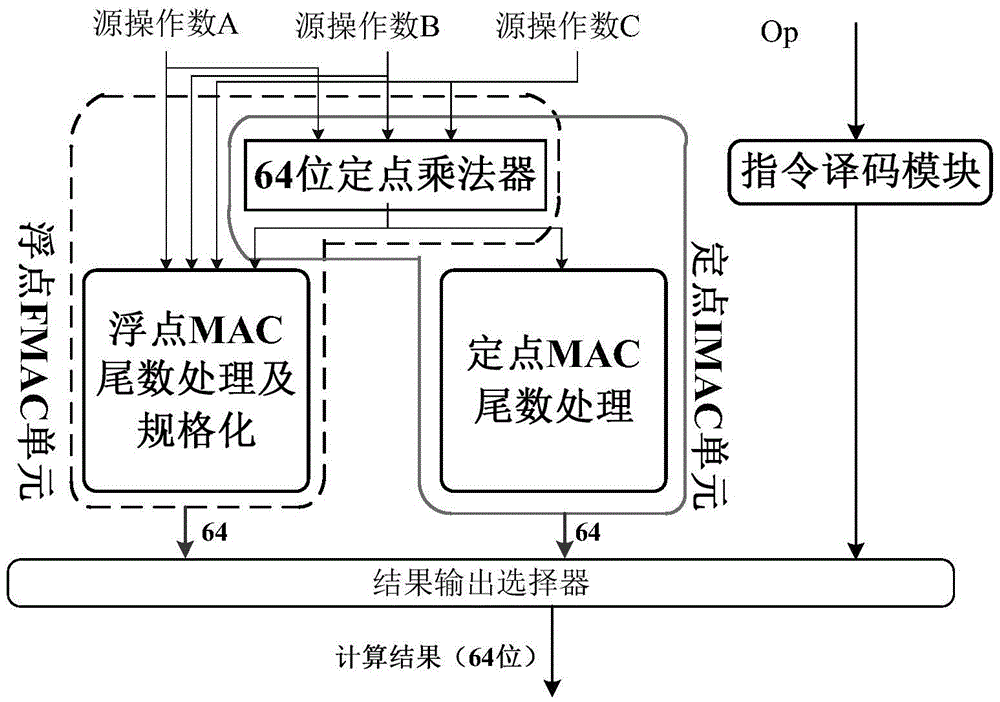

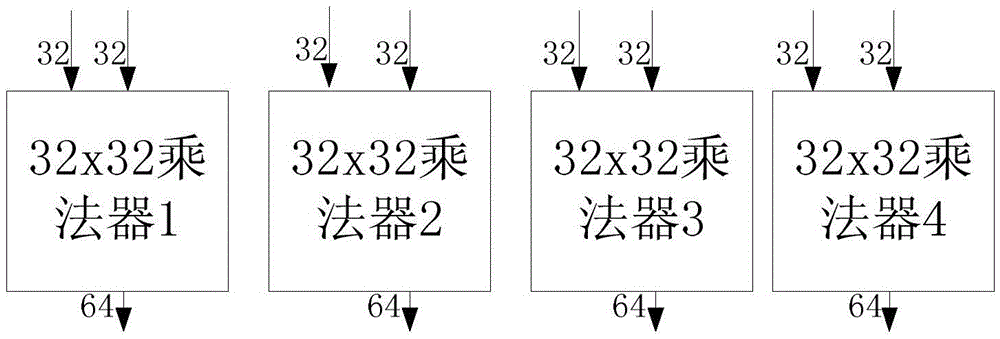

[0039] like figure 1 As shown, the fixed-point floating-point arithmetic unit of the GPDSP shared multiplier structure of the present invention includes a shared 64-bit fixed-point multiplier, a floating-point multiply-add unit MAC (FMAC) and a fixed-point multiply-add unit MAC (IMAC). The floating-point multiplication and addition unit FMAC supports IEEE-754 standard double-precision floating-point operations and IEEE-754 standard SIMD structure double single-precision floating-point multiplication, multiplication and addition, multiplication and subtraction, and complex multiplication operations; the fixed-point multiplication and addition unit IMAC supports 64 1-bit signed or unsigned fixed-point multiply operation and dual 32-bit signed or unsigned fixed-point multiply operation for SIMD structures.

[0040] The GPDSP of the pres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More