Patents

Literature

93results about How to "Additional circuitry" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

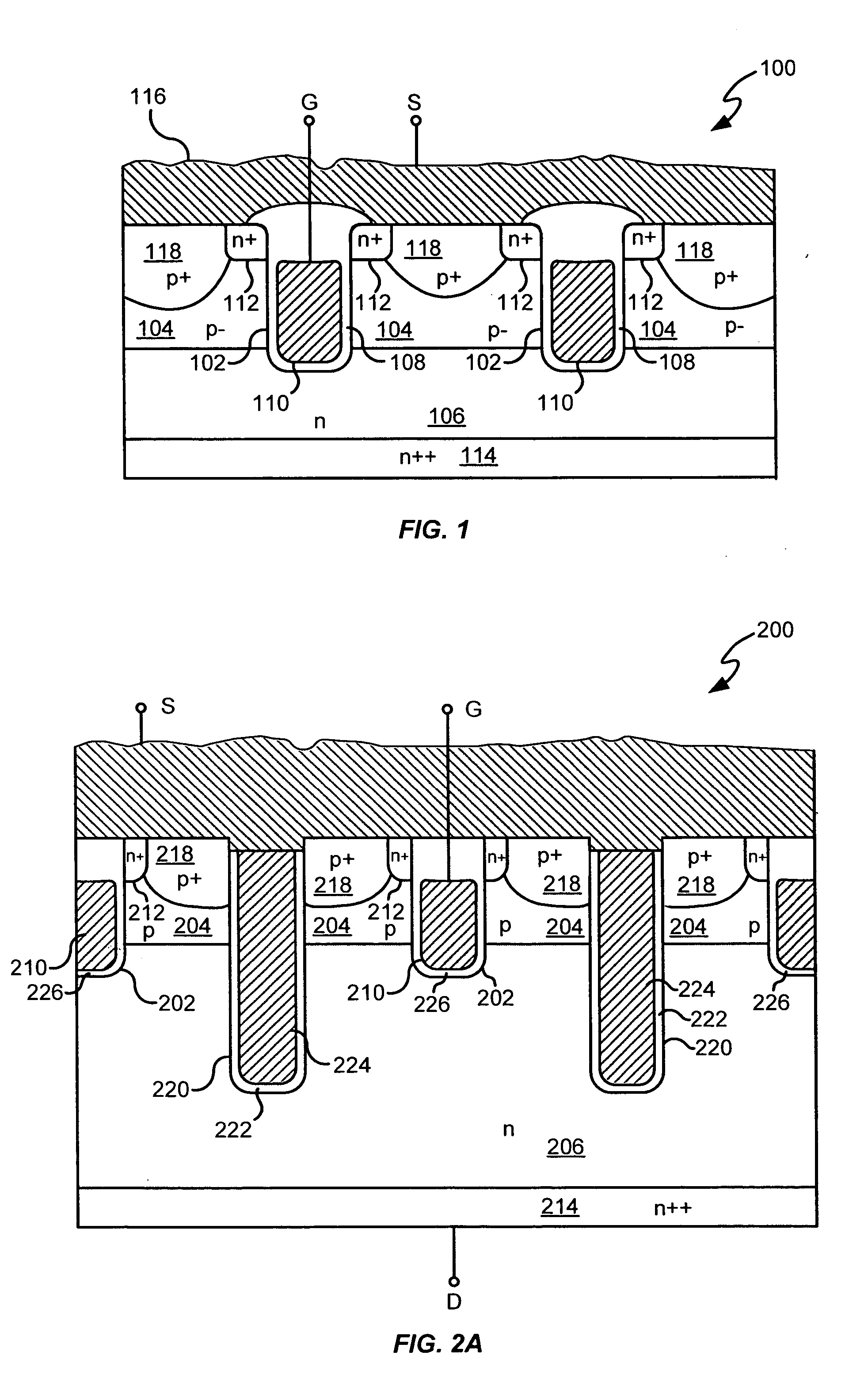

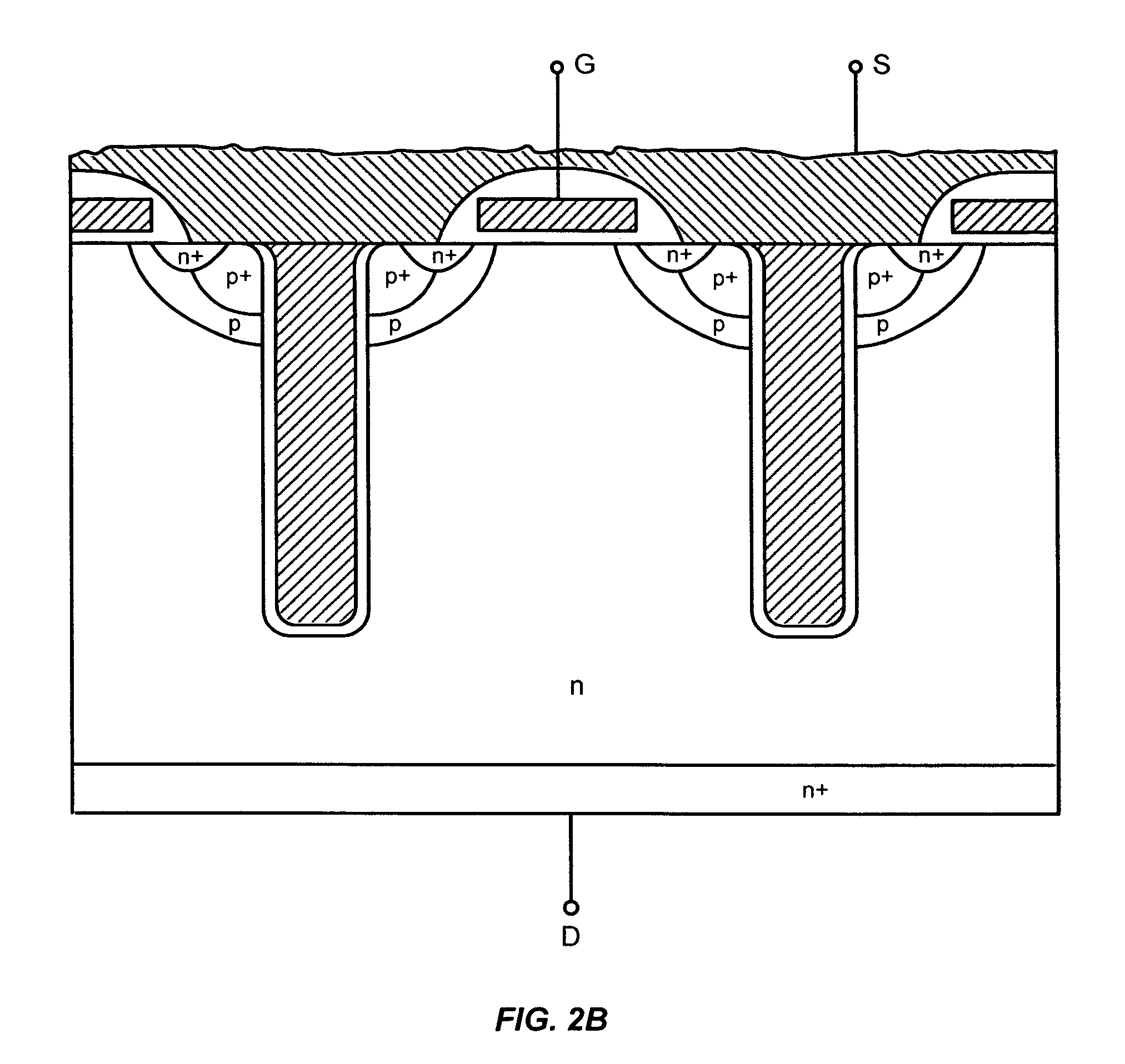

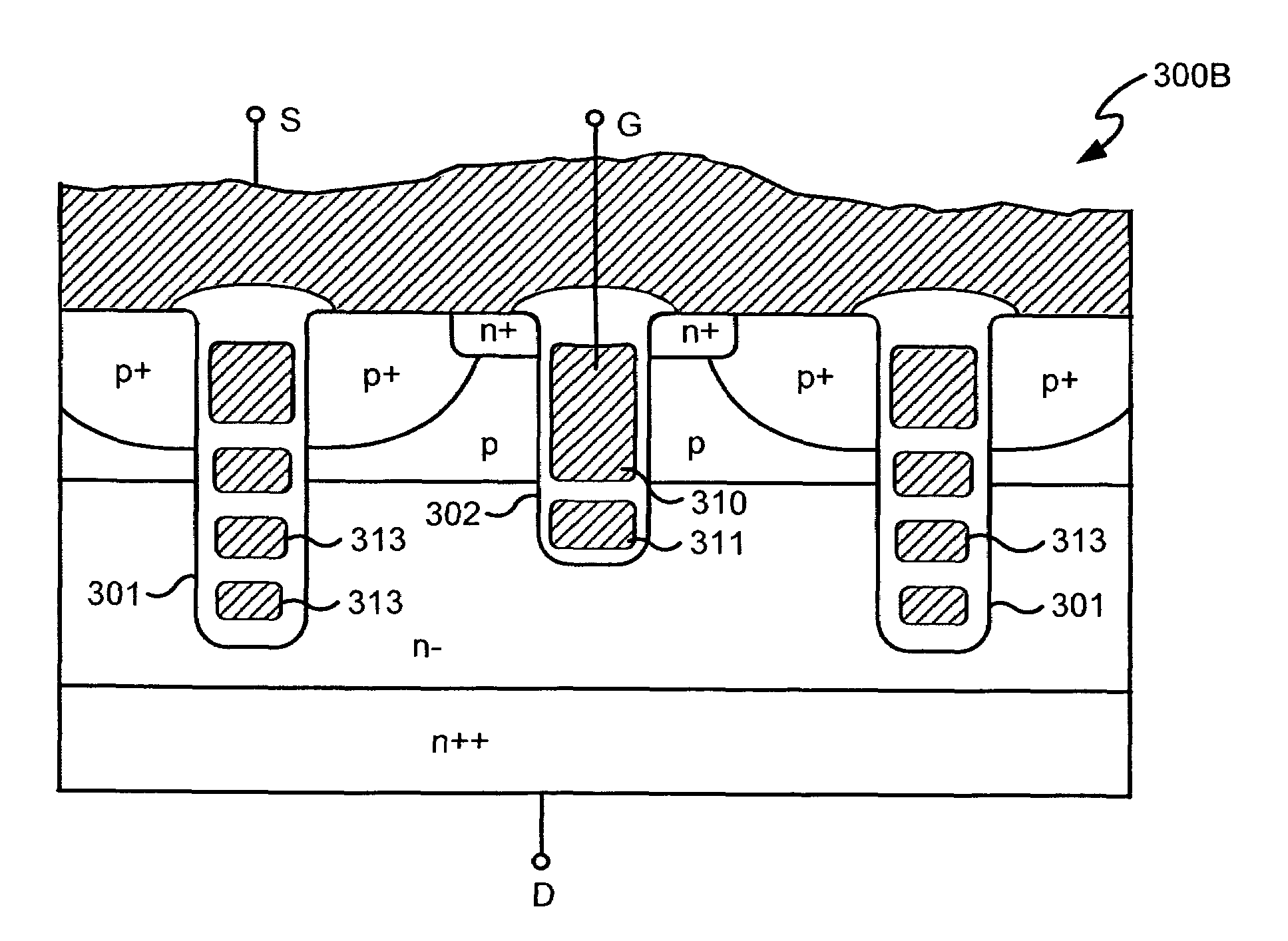

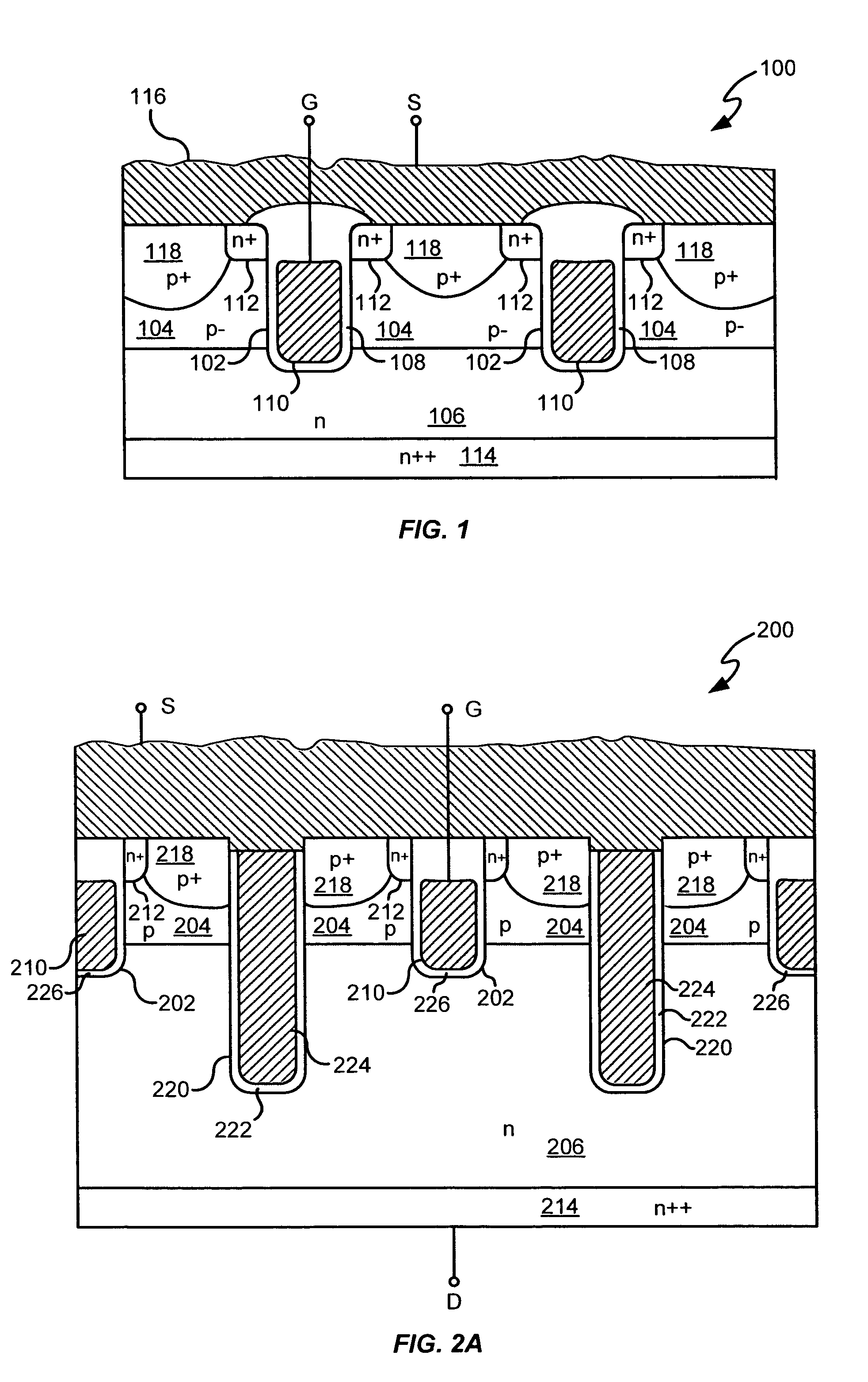

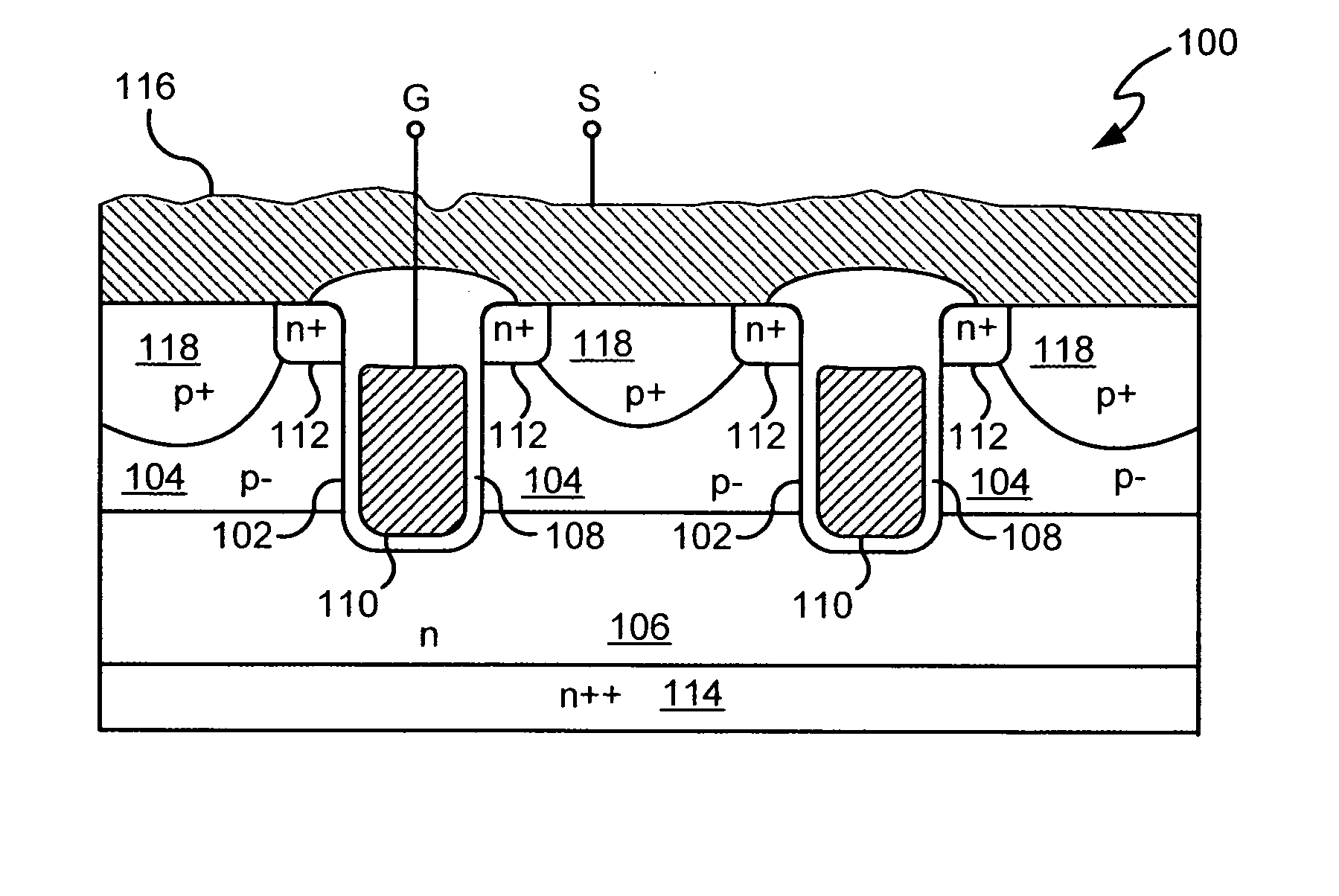

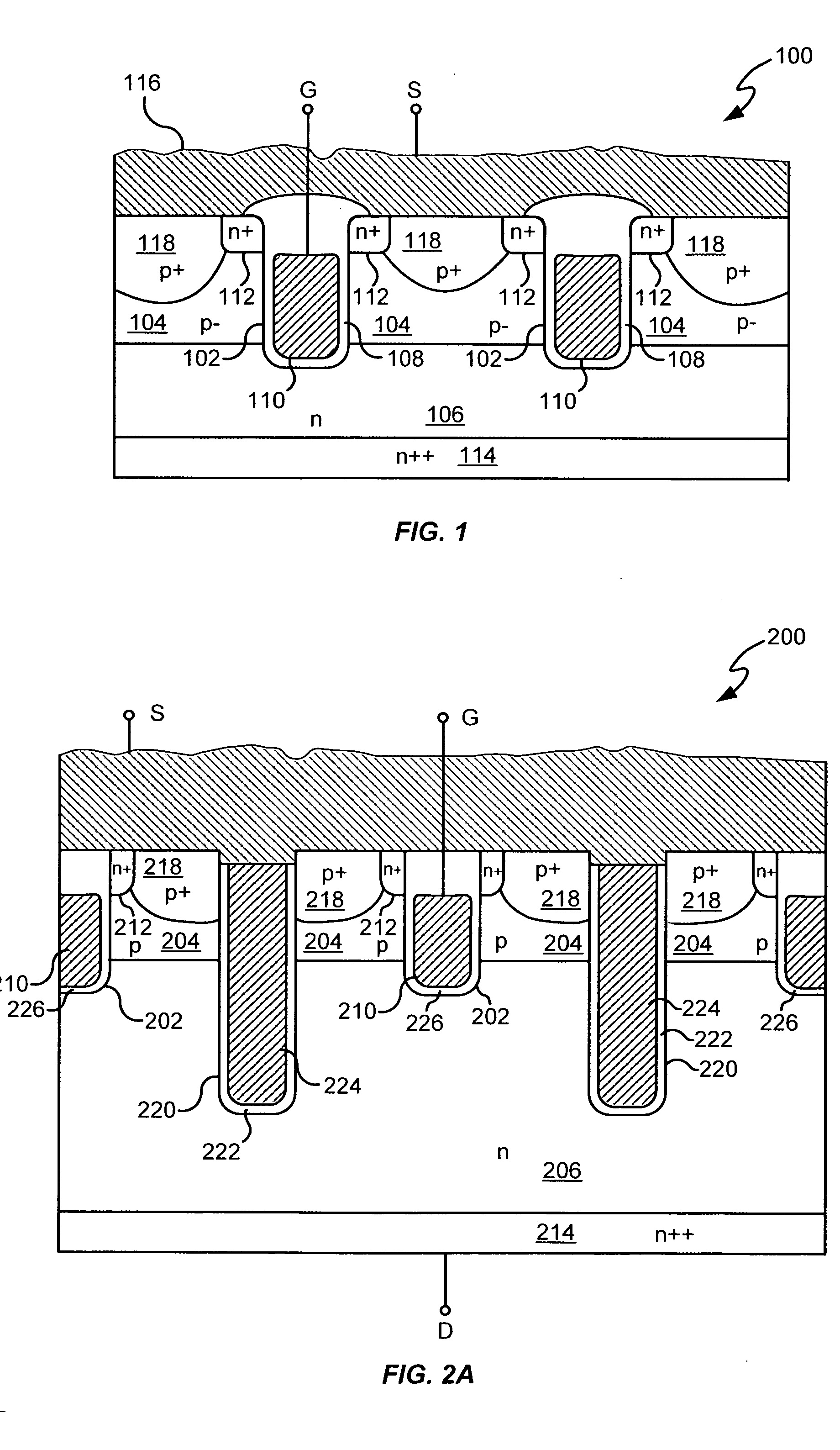

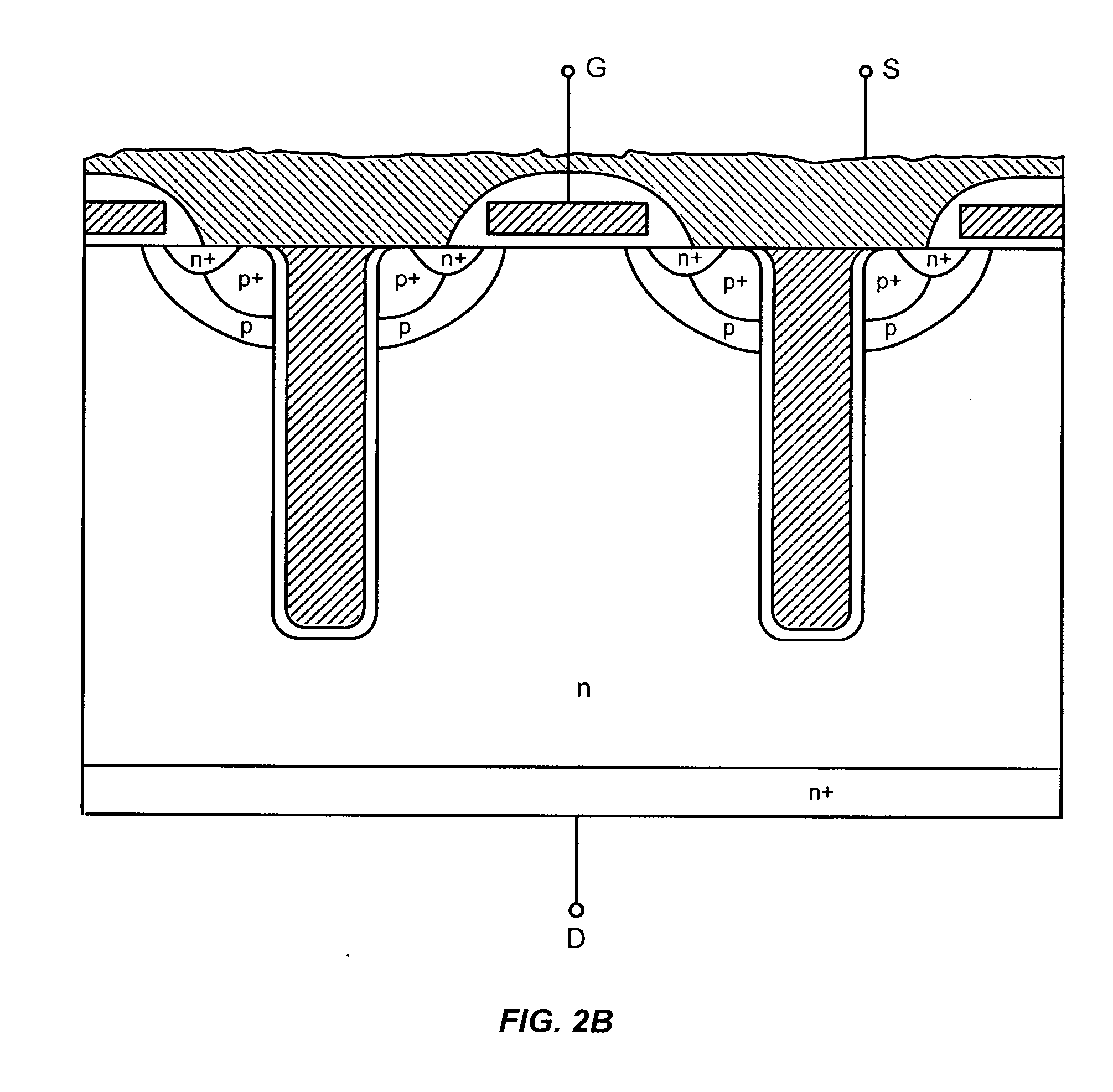

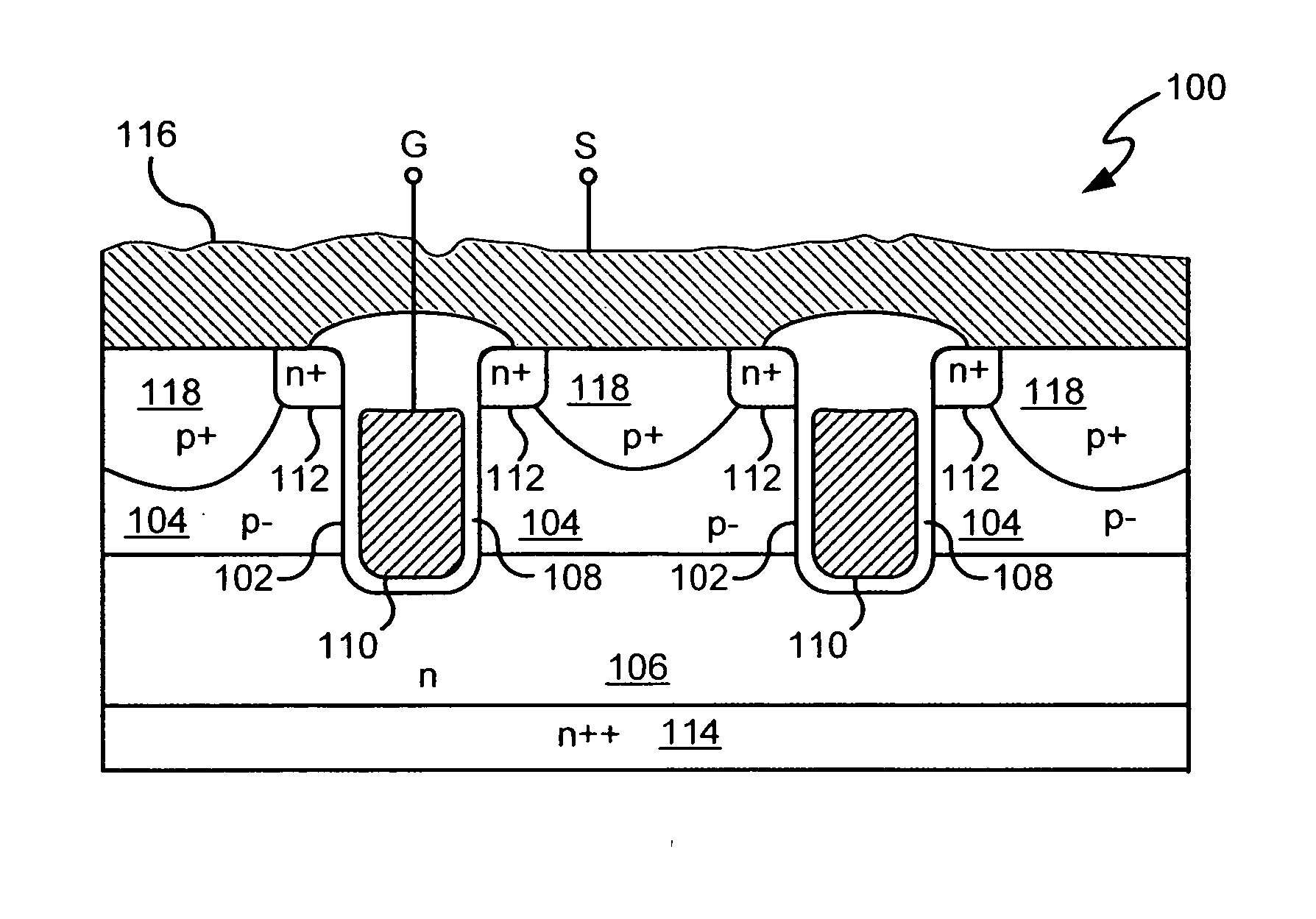

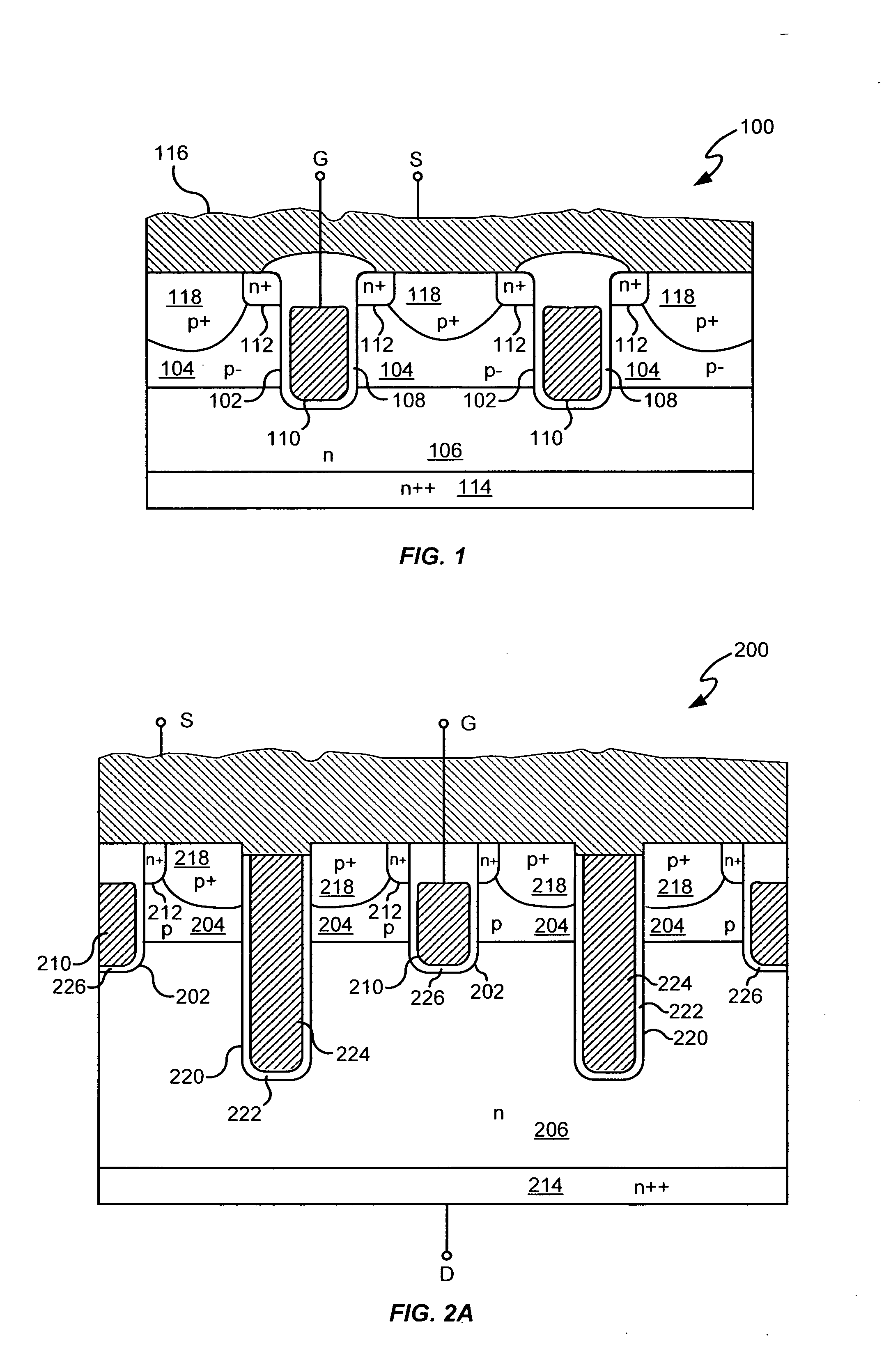

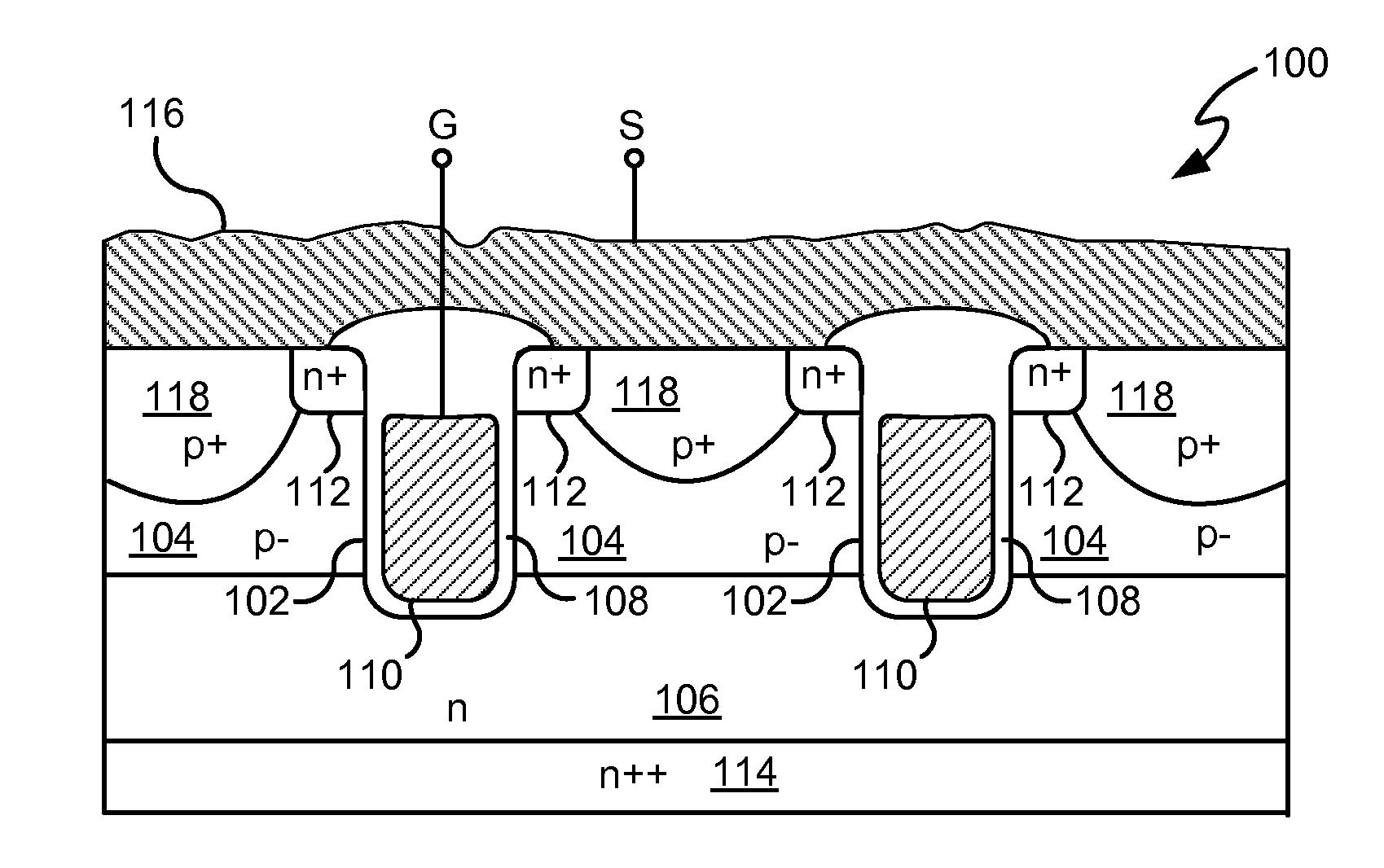

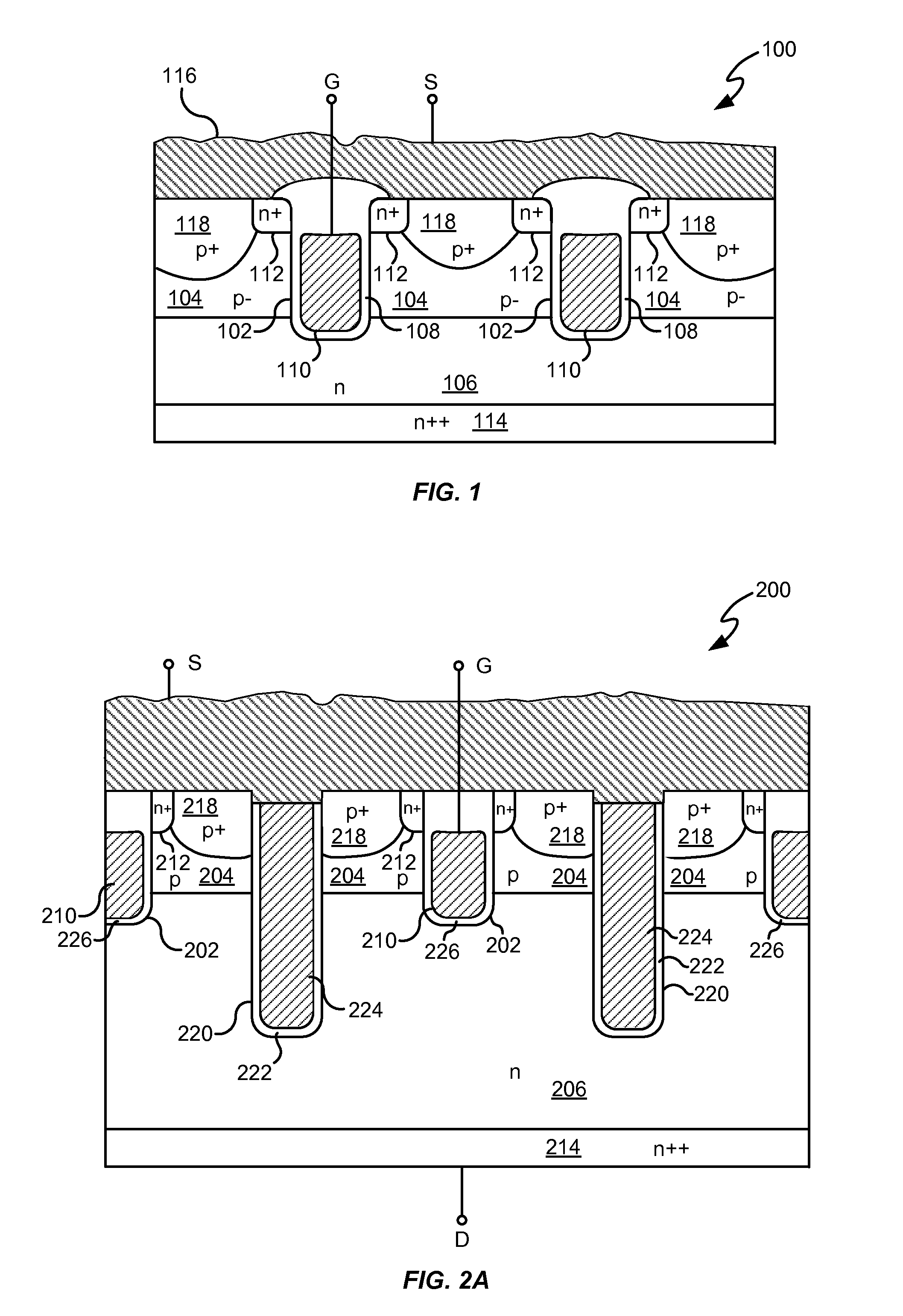

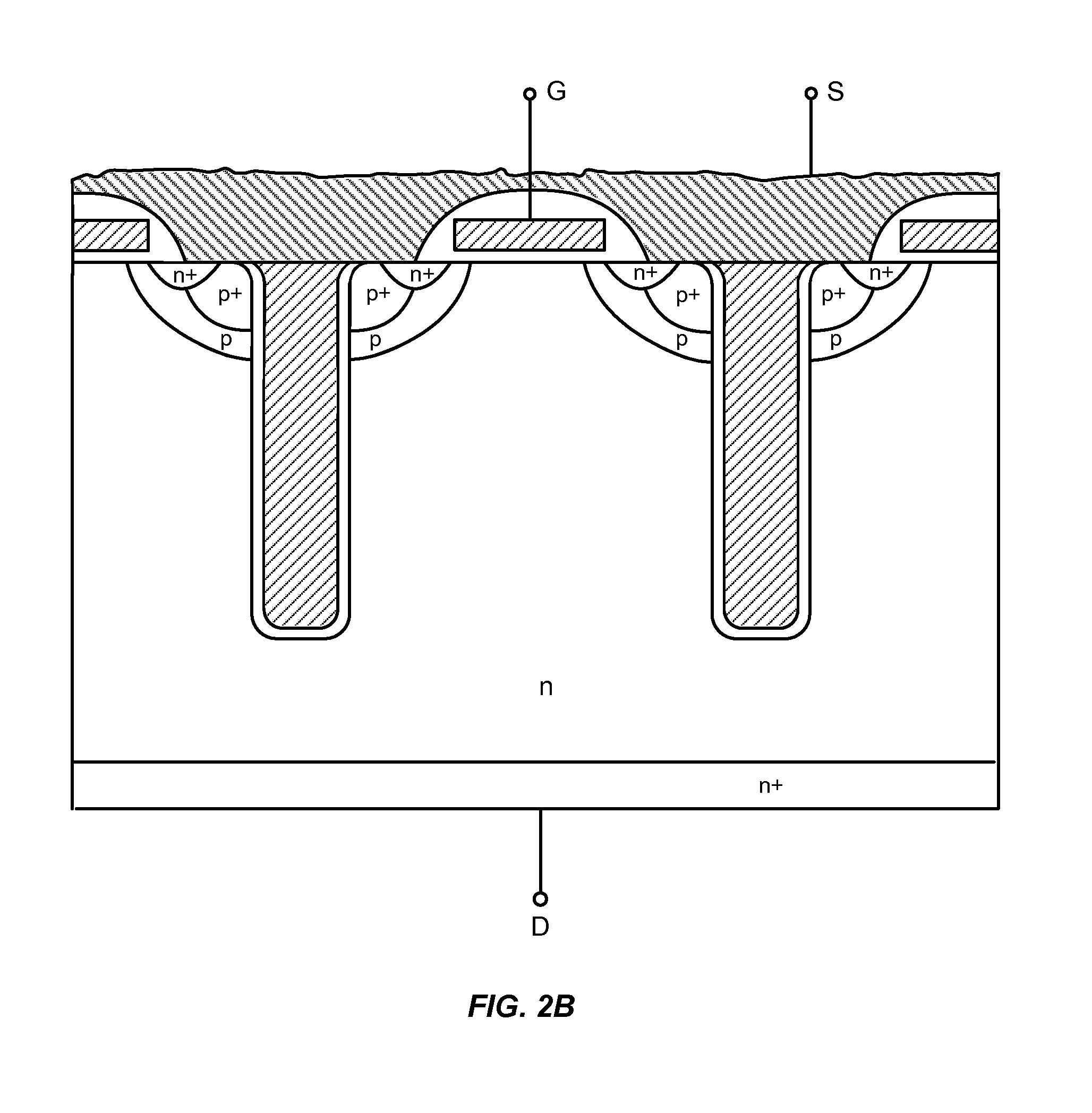

Power semiconductor devices and methods of manufacture

ActiveUS20050167742A1Improved voltage performanceFast switching speedEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh voltage

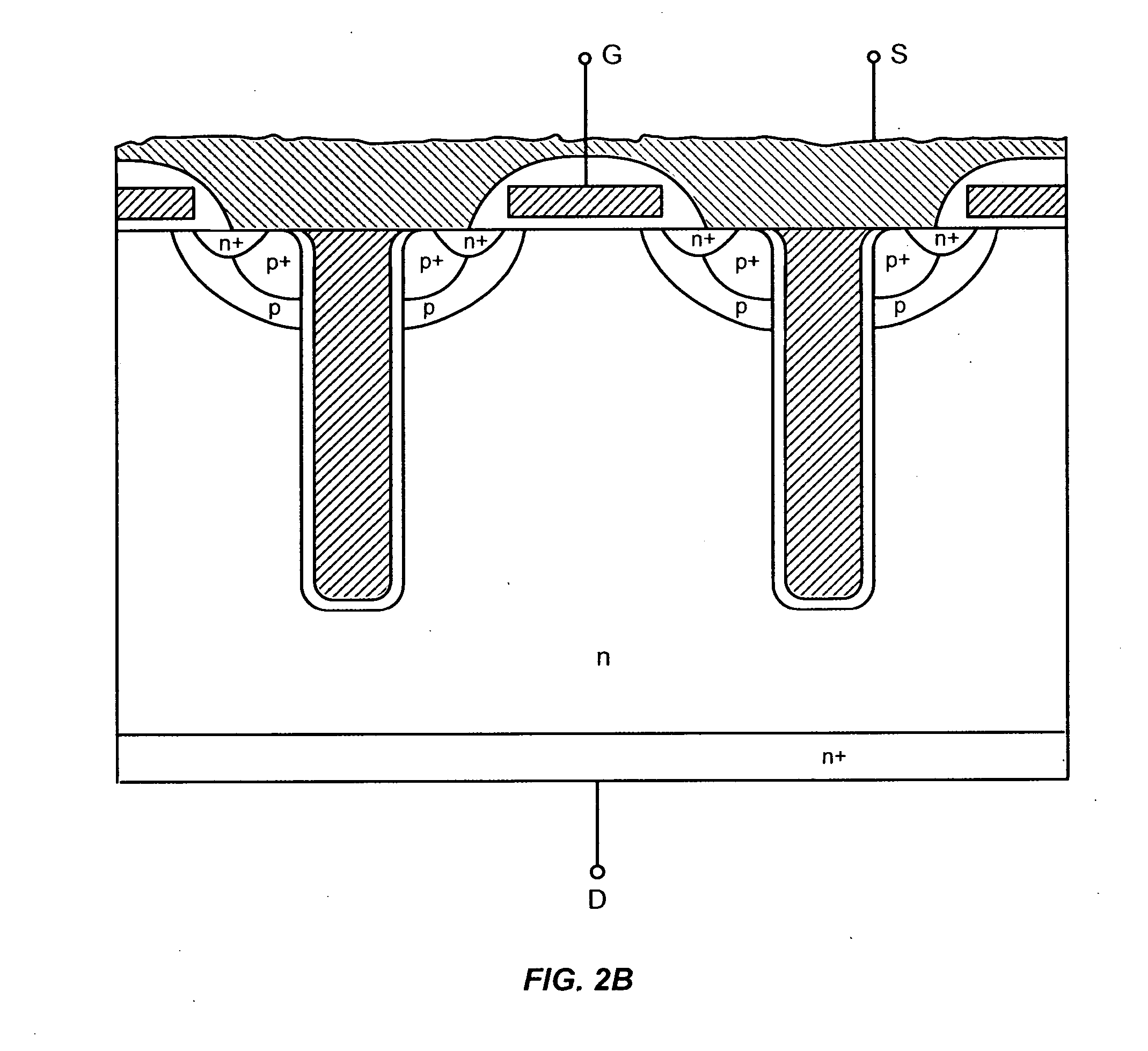

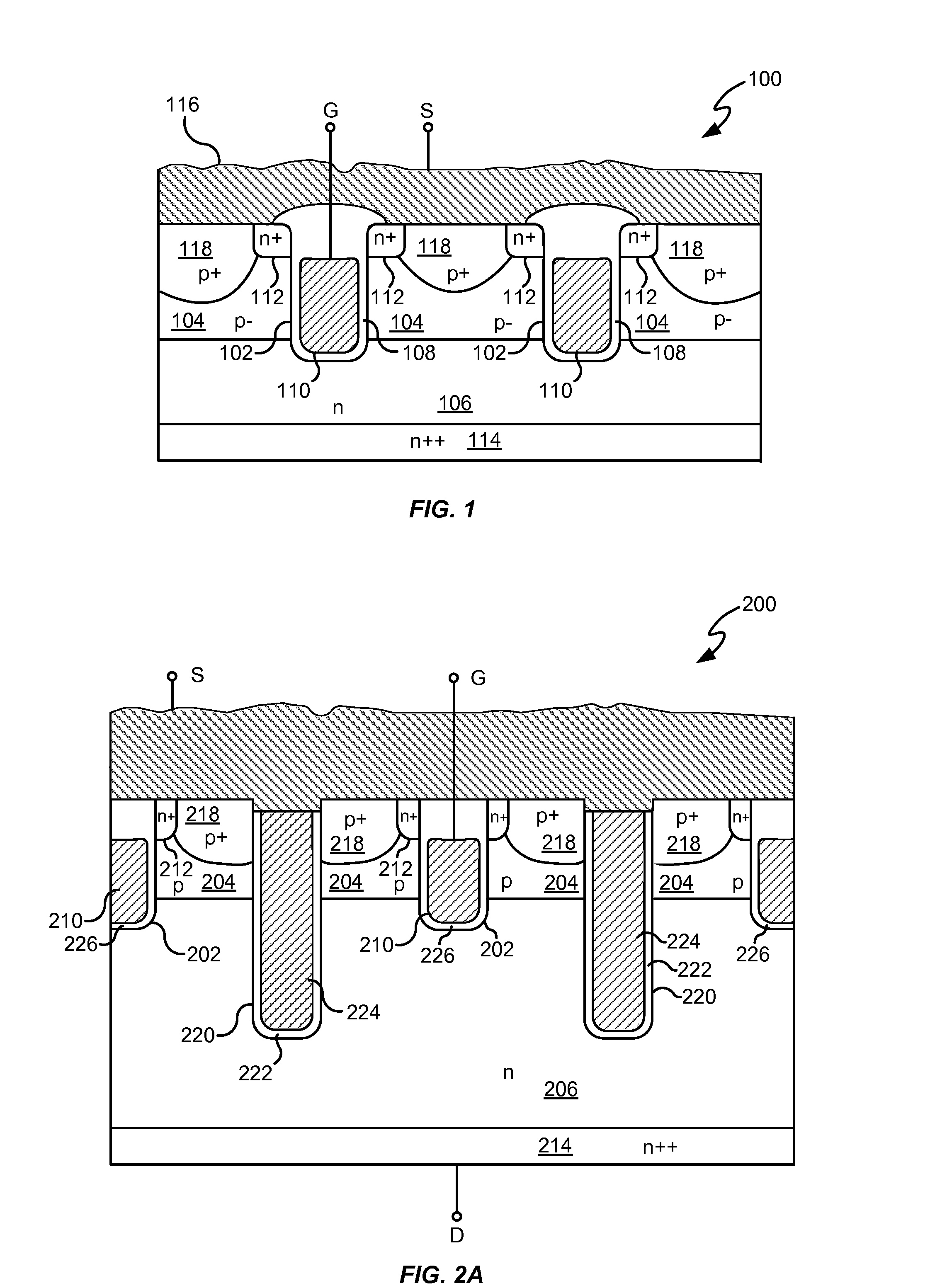

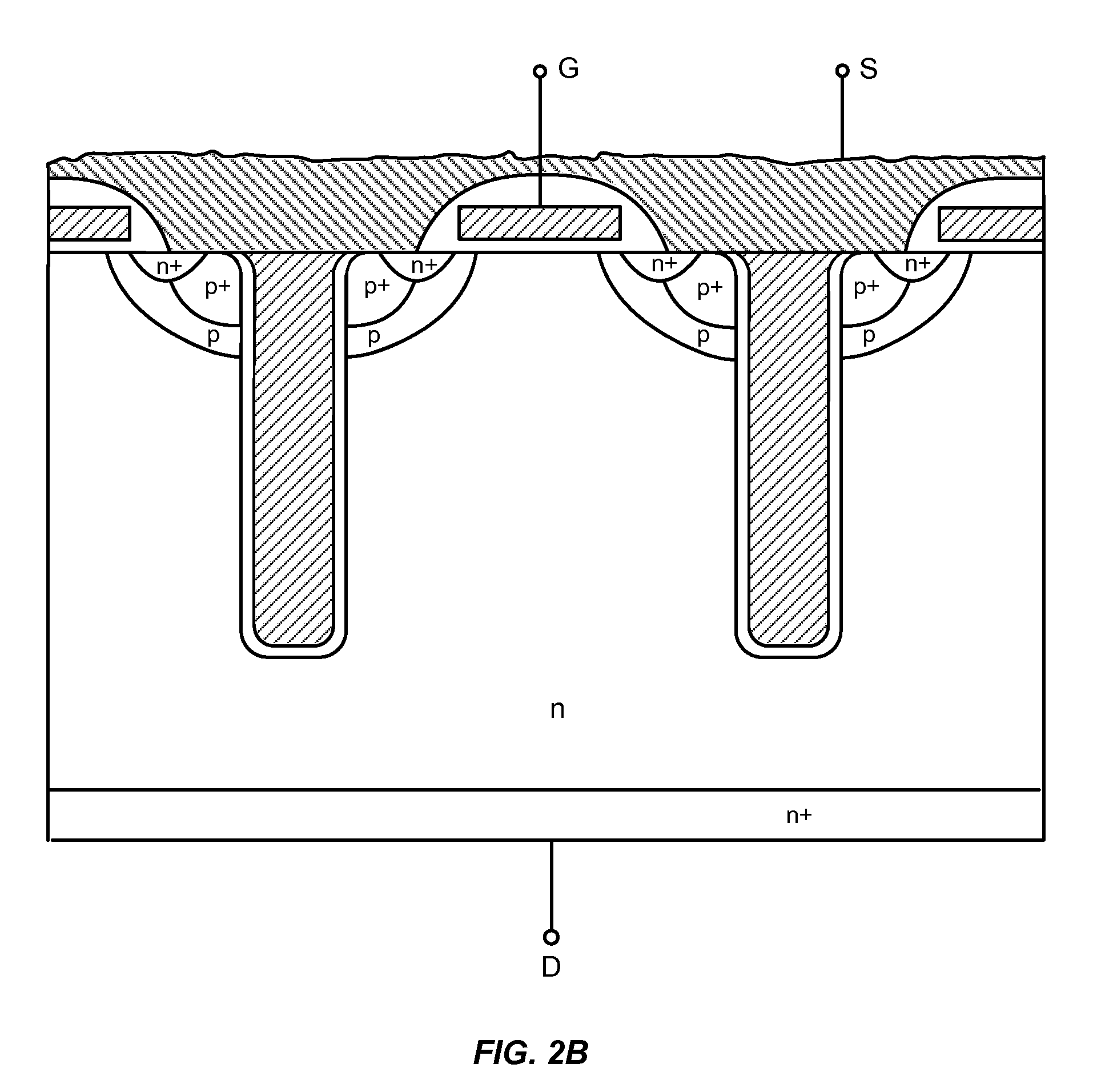

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

Power semiconductor devices and methods of manufacture

ActiveUS7345342B2Simple structureEasy to packEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

Power semiconductor devices and methods of manufacture

InactiveUS20060214221A1Improved voltage performanceFast switching speedTransistorEfficient power electronics conversionEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

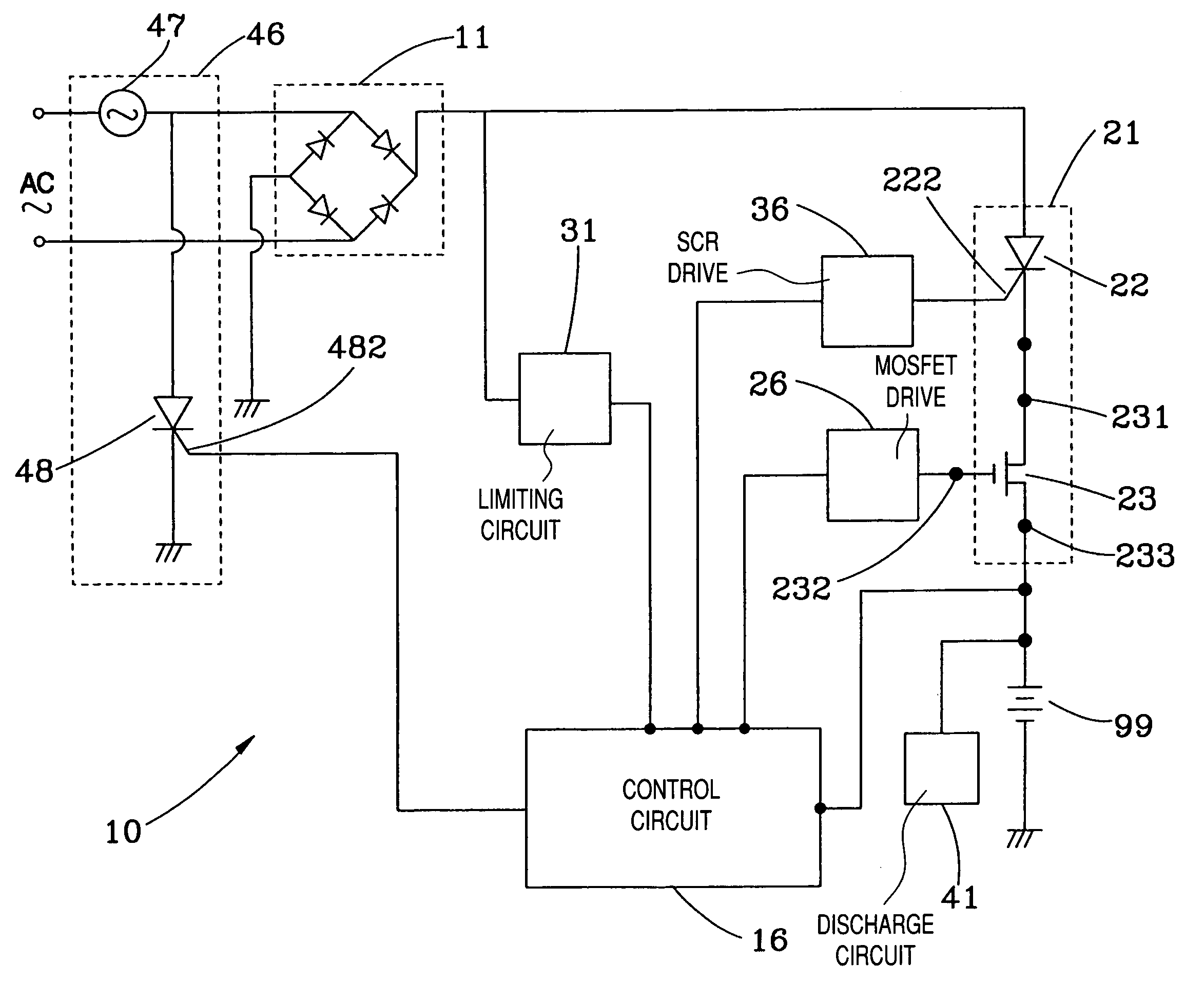

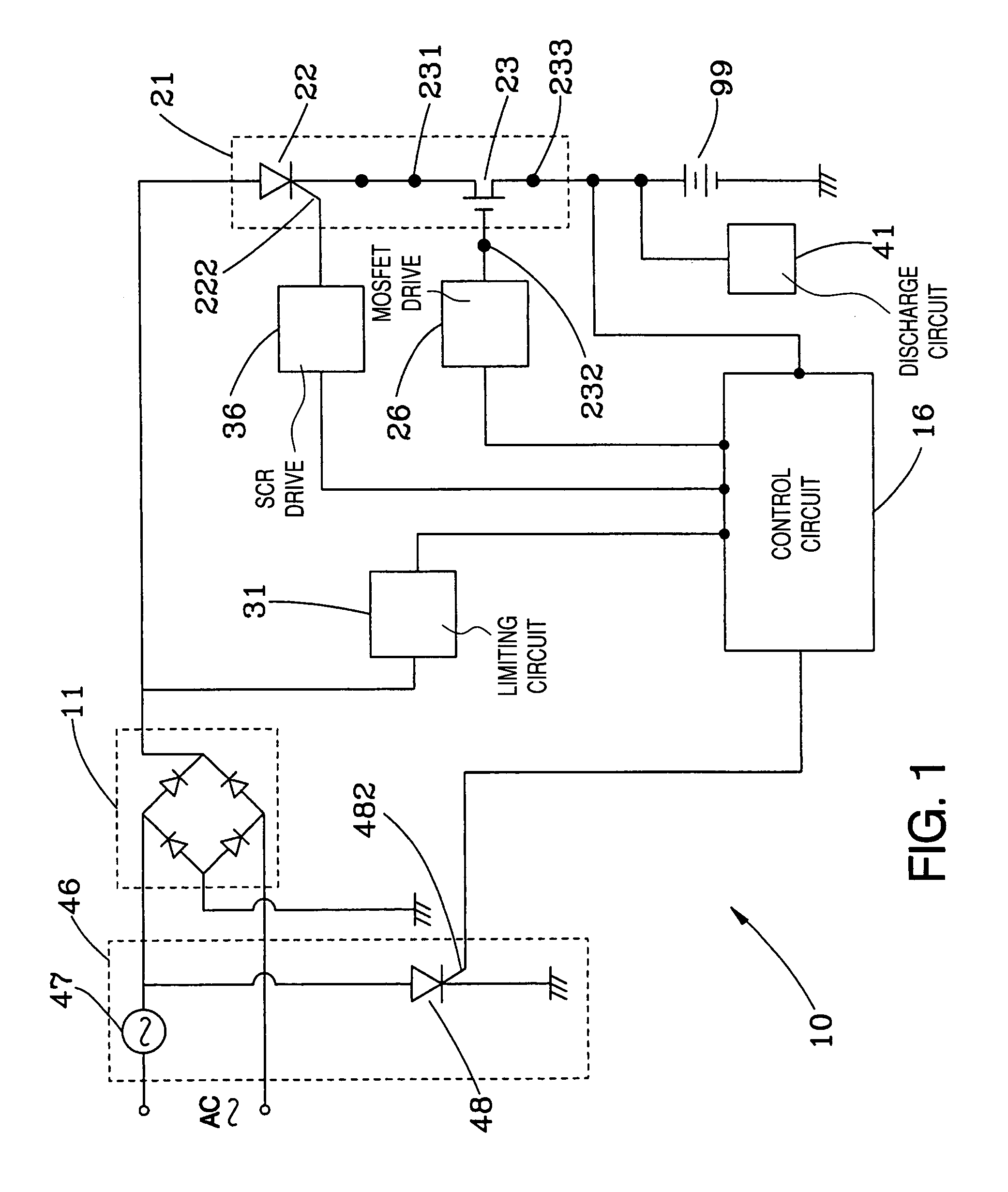

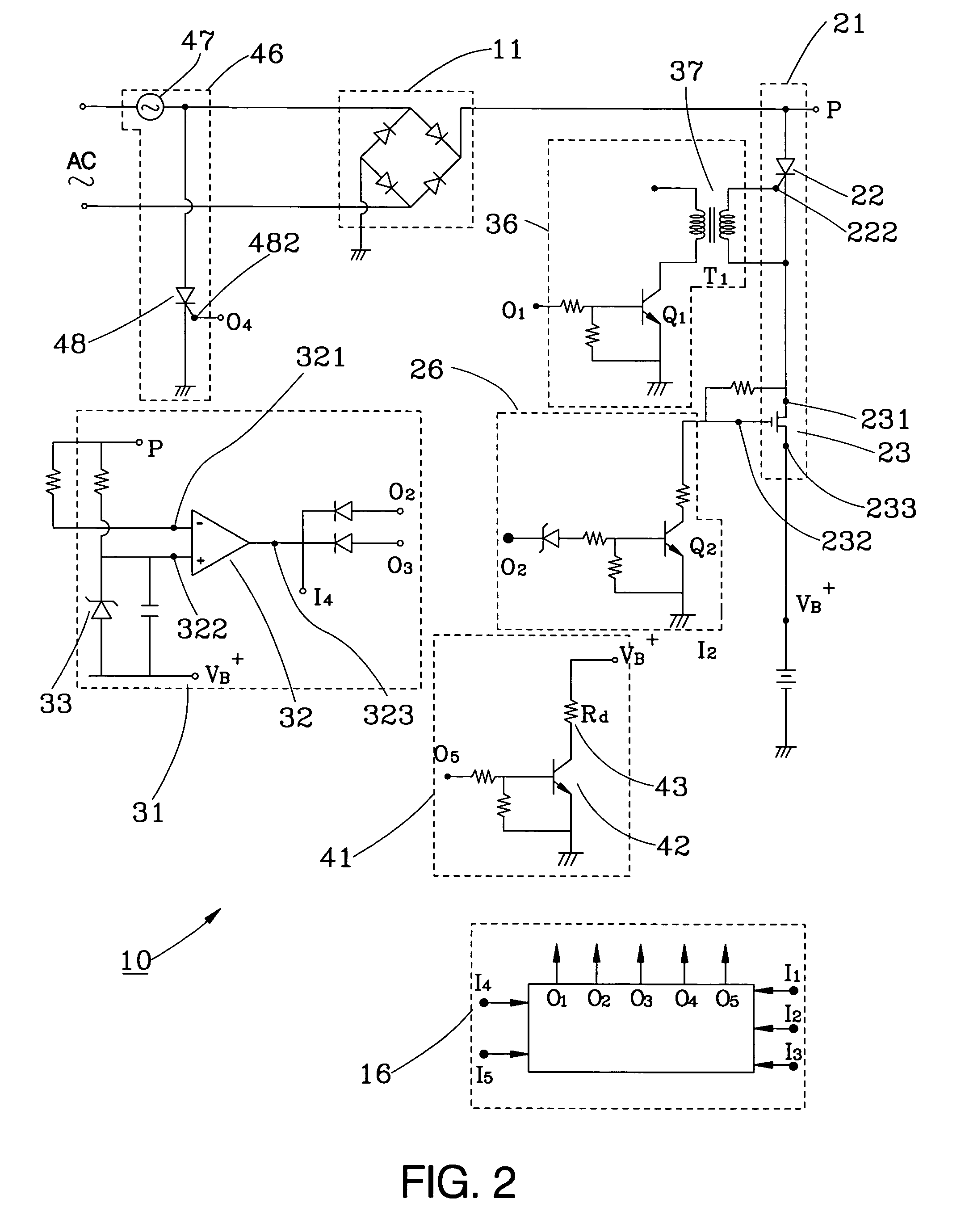

Battery charging and/or DC power supply circuitry

InactiveUS6977485B1Improved battery chargingSmall sizeAc-dc conversionElectric powerAC powerBattery charge

A battery charging and / or DC power supply circuitry employs a control circuit through an SCR drive circuit and an MOS drive circuit to control when to turn on / off a semiconductor switch unit and to turn on the semiconductor switch unit while an initial section of each positive half wave of an AC power source and an terminating section of the same are located below a predetermined level for intercepting partial power for charging. While charging a battery, the circuitry is lightweight, small-sized, and to enhance the life of the battery. While being a DC power supply, the circuitry is small-sized, high-efficiency, and low-cost.

Owner:MOBILETRON ELECTRONICS

Power semiconductor devices and methods of manufacture

ActiveUS20060214222A1Improved voltage performanceFast switching speedTransistorEfficient power electronics conversionEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

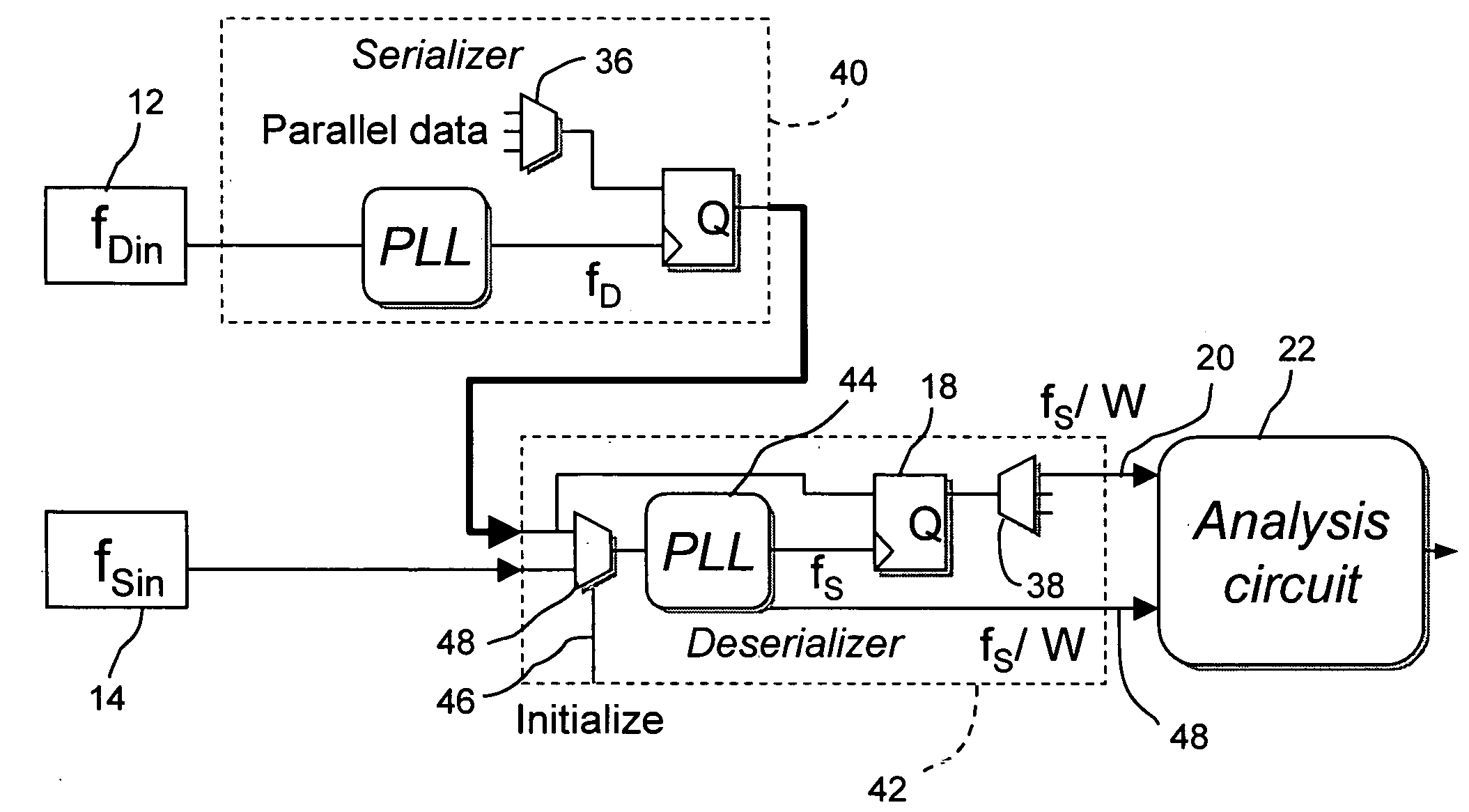

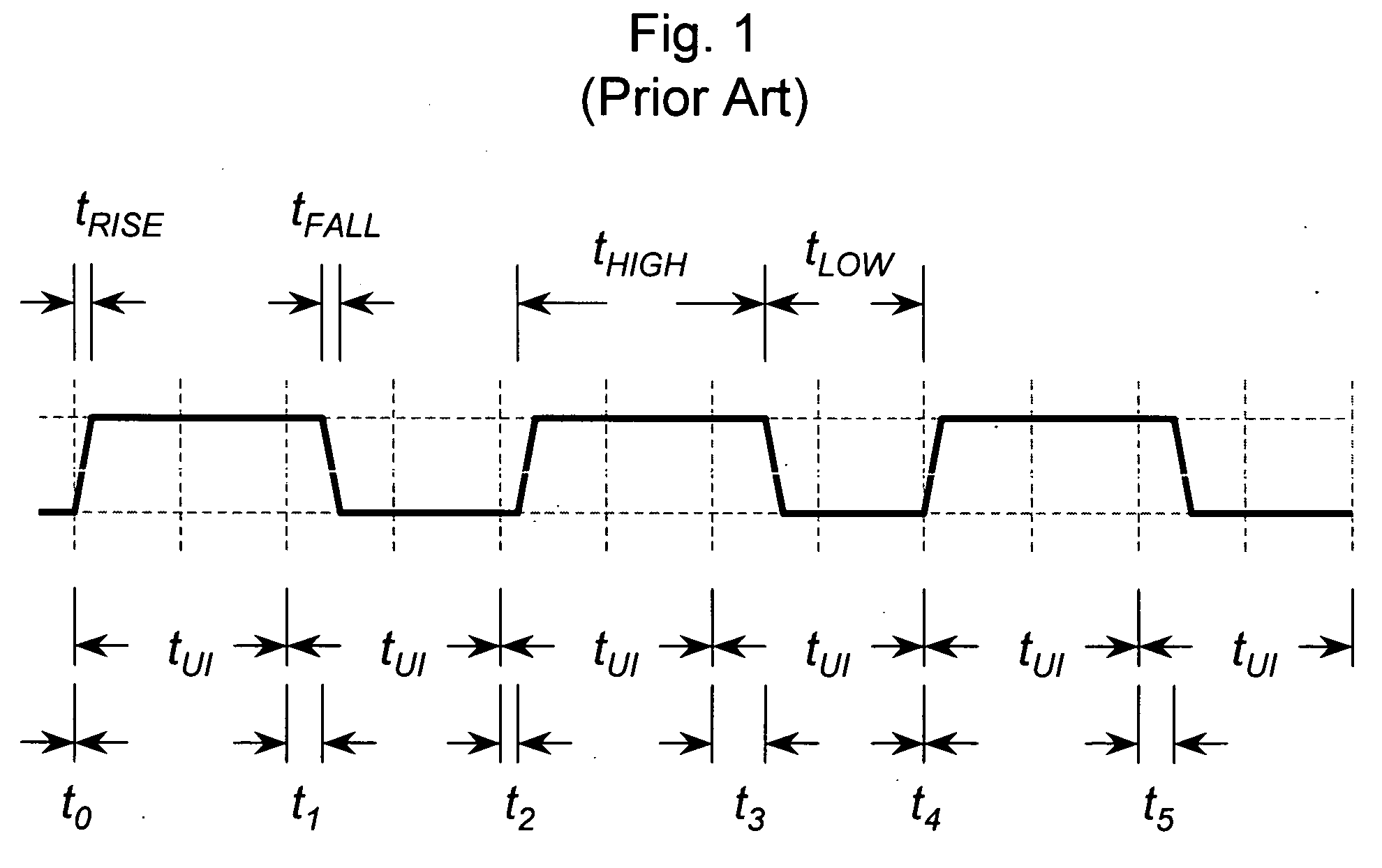

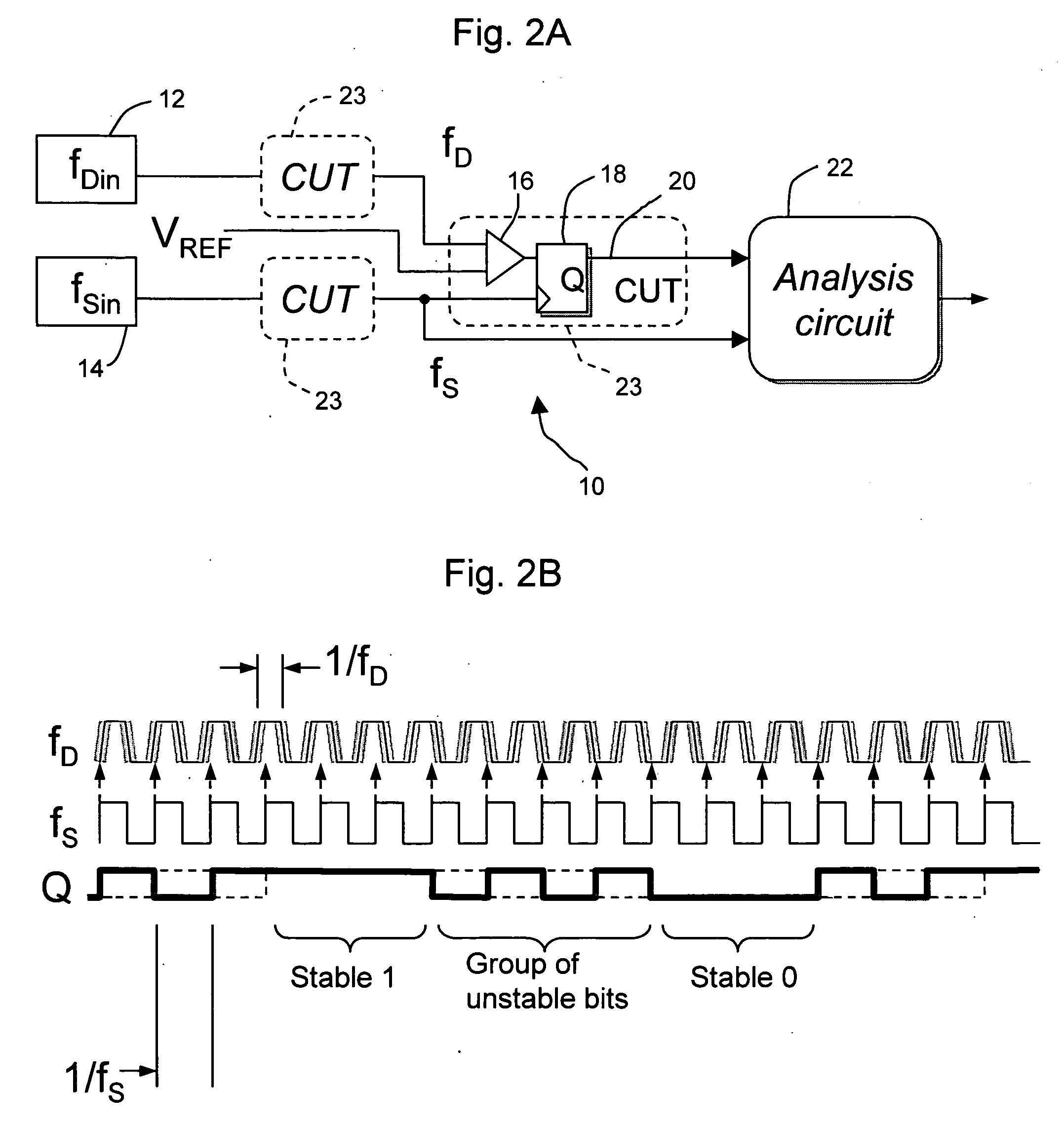

Circuit and method for measuring jitter of high speed signals

ActiveUS20050069031A1Accurate measurementMinimal and no impactError detection/prevention using signal quality detectorNoise figure or signal-to-noise ratio measurementData signalData rate

A method and circuit for measuring a statistical value of jitter for a data signal having a data rate fD, comprises digitally sampling the data signal at a sampling rate, fS, to produce sampled logic values, where fD / fS is a predetermined non-integer ratio; and analyzing the sampled values to deduce a statistical value of the jitter.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

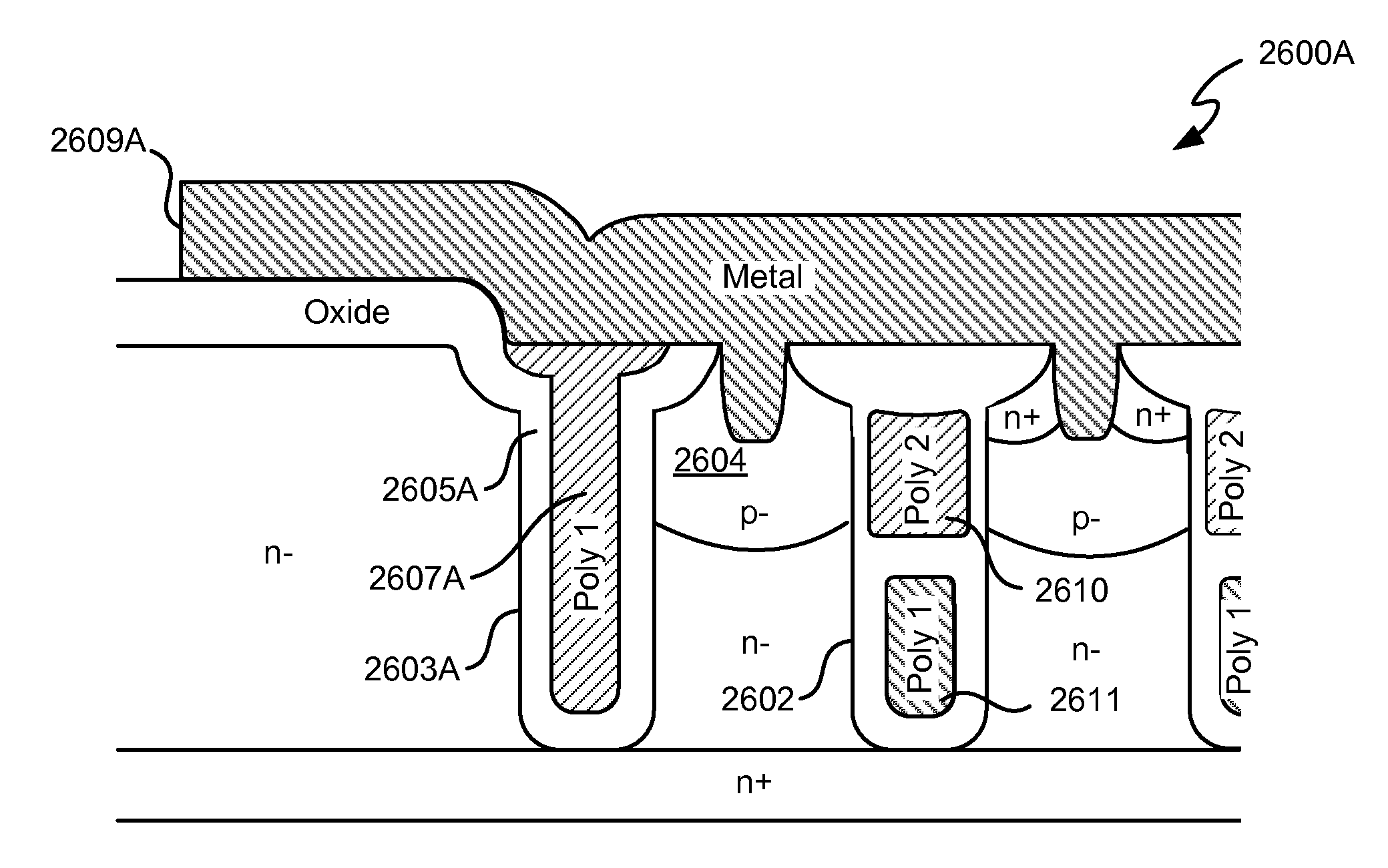

Methods of Making Power Semiconductor Devices with Thick Bottom Oxide Layer

ActiveUS20080138953A1Simple structureEasy to packTransistorEfficient power electronics conversionPower semiconductor deviceHigh density

A method for forming thick oxide at the bottom of a trench formed in a semiconductor substrate includes forming a conformal oxide film that fills the trench and covers a top surface of the substrate. and etching the oxide film off the top surface of the substrate and inside the trench to leave a substantially flat layer of oxide having a target thickness at the bottom of the trench. The oxide film can be deposited by sub-atmospheric chemical vapor deposition processes, directional Tetraethoxysilate (TEOS) processes, or high density plasma deposition processes that form a thicker oxide at the bottom of the trench than on the sidewalls of the trench.

Owner:SEMICON COMPONENTS IND LLC

Power Semiconductor Devices Having Termination Structures and Methods of Manufacture

InactiveUS20080135931A1Simple structureEasy to packTransistorEfficient power electronics conversionPower semiconductor deviceDielectric

A semiconductor power device includes a drift region of a first conductivity type, a well region extending above the drift region and having a second conductivity type opposite the first conductivity type, an active trench extending through the well region and into the drift region, source regions having the first conductivity type formed in the well region adjacent the active trench, and a first termination trench extending below the well region and disposed at an outer edge of an active region of the device. The sidewalls and bottom of the active trench are lined with dielectric material, and substantially filled with a first conductive layer forming an upper electrode and a second conductive layer forming a lower electrode, the upper electrode being disposed above the lower electrode and separated therefrom by inter-electrode dielectric material. The first termination trench can be lined with a layer of dielectric material that is thicker than the dielectric material lining the sidewalls of the active trench, and is substantially filled with conductive material.

Owner:SEMICON COMPONENTS IND LLC

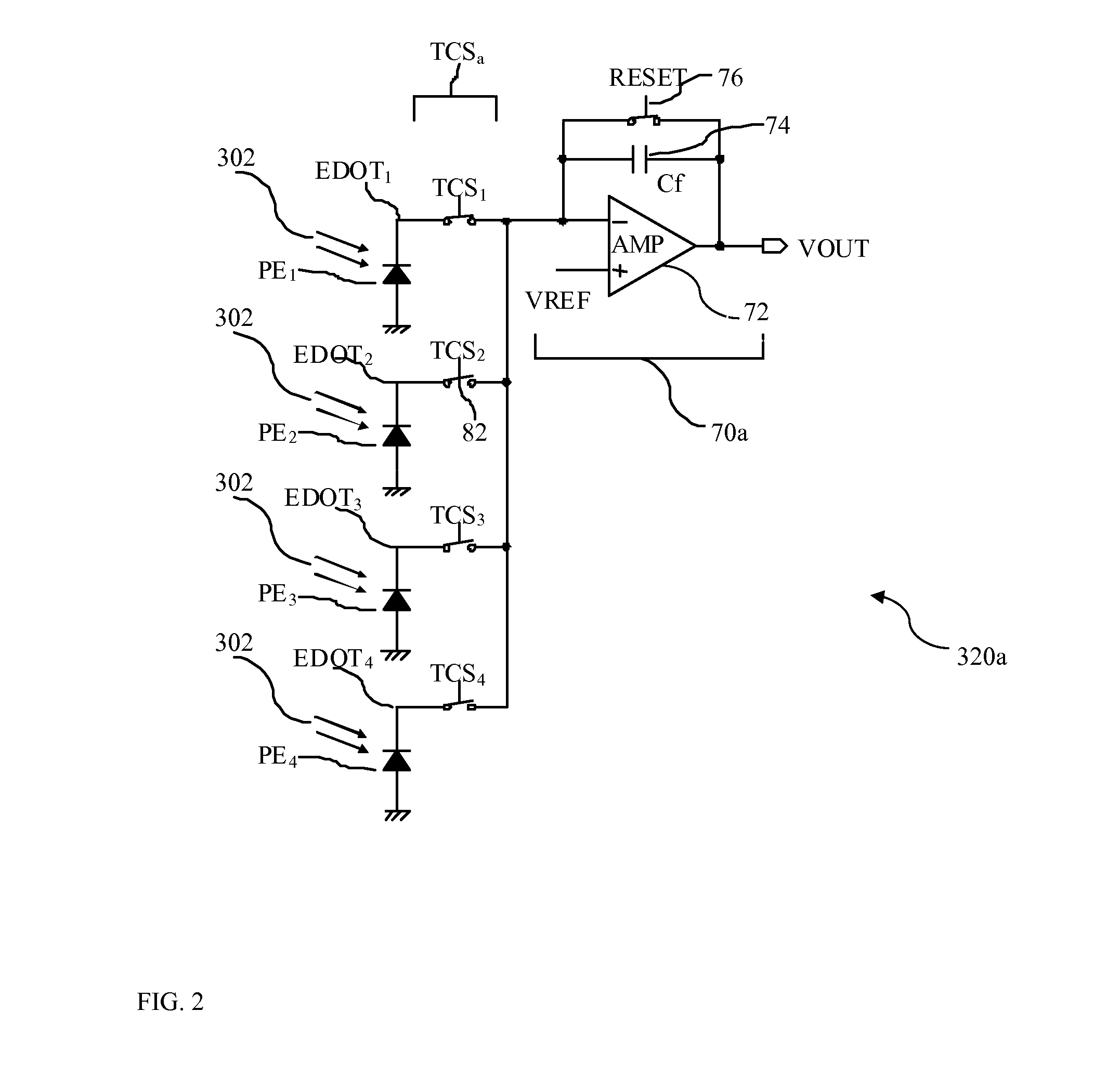

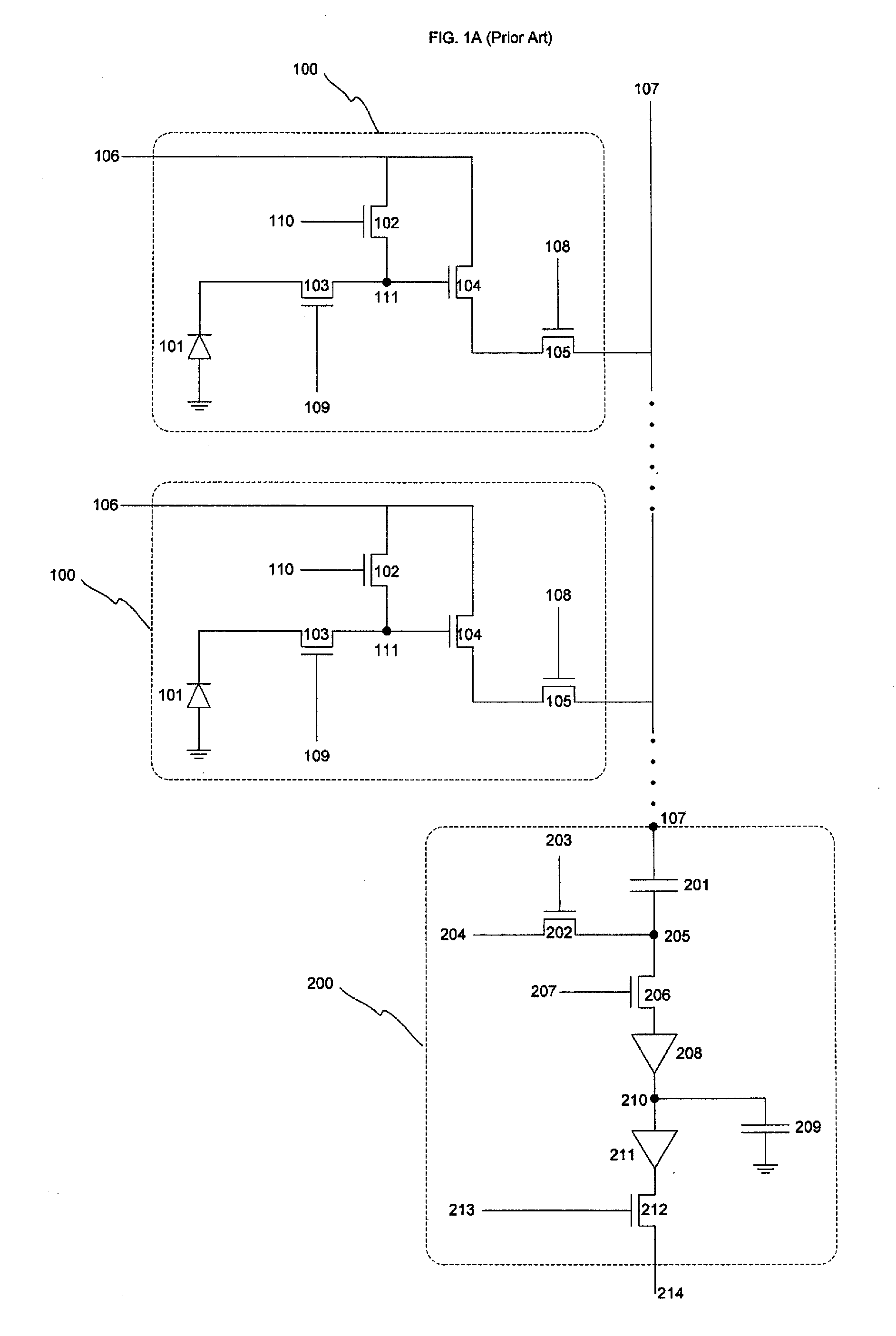

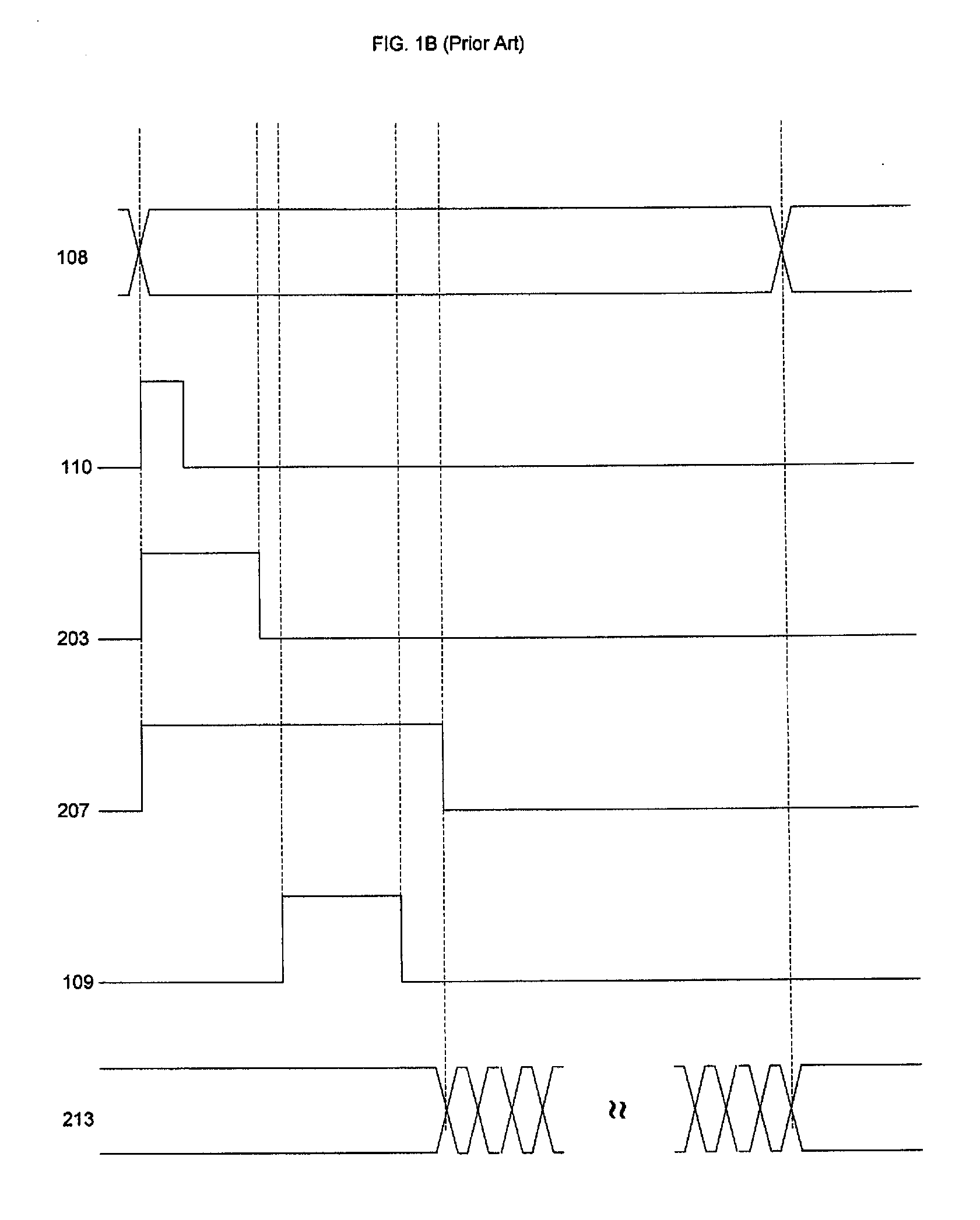

Multi-resolution Image Sensor Array with High Image Quality Pixel Readout Circuitry

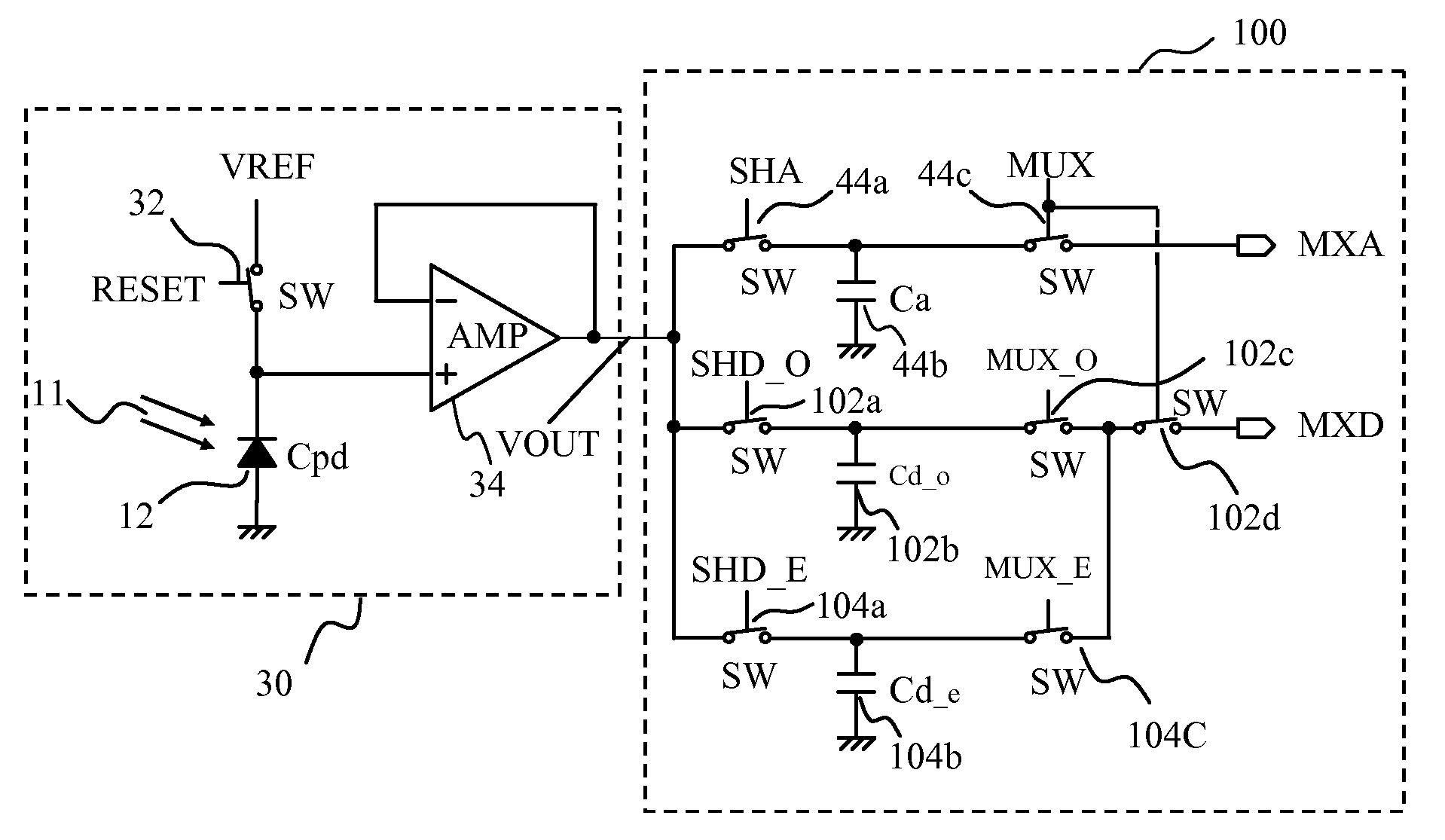

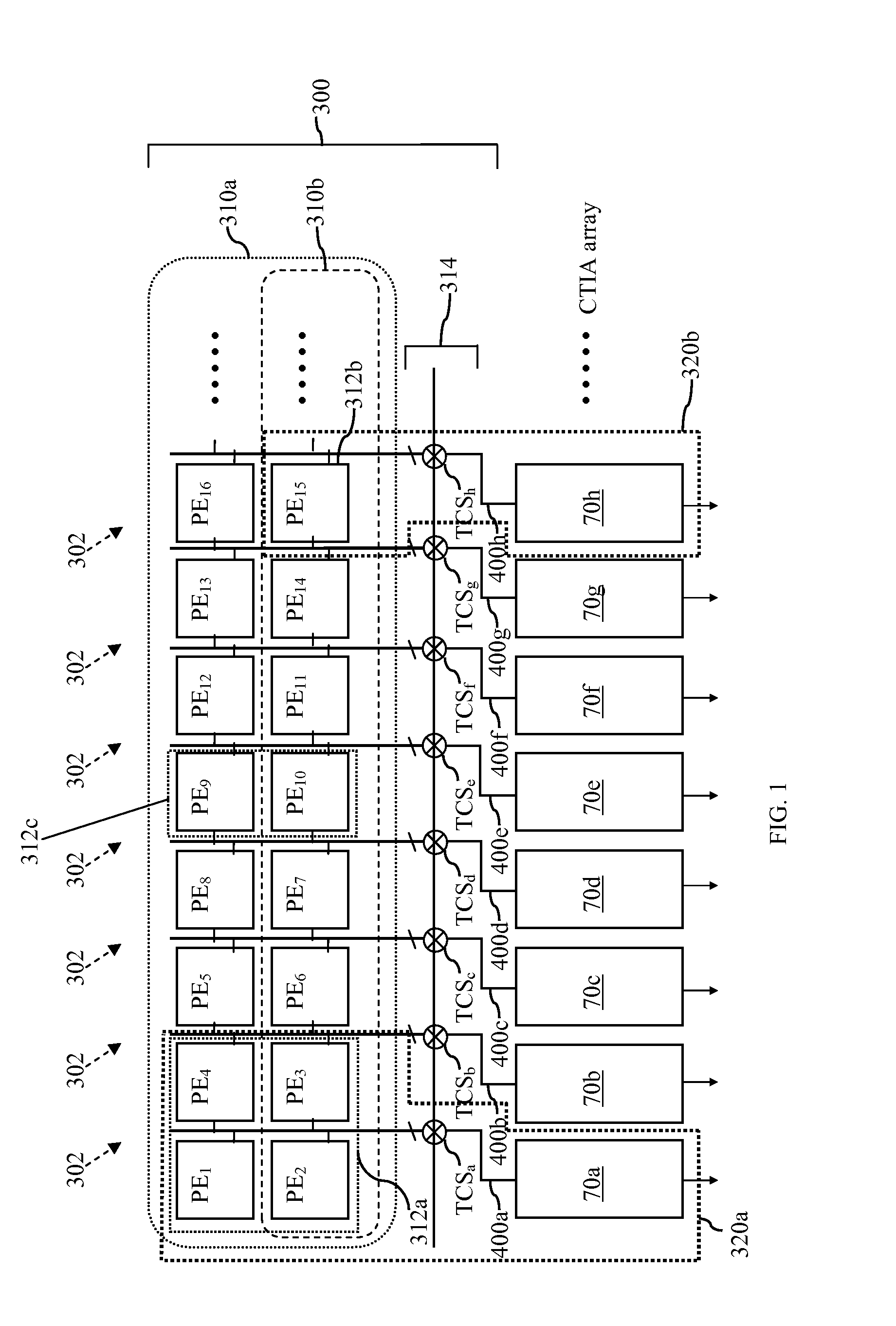

InactiveUS20090091648A1Improve performanceImprove image qualityTelevision system detailsTelevision system scanning detailsSensor arrayCMOS sensor

A configurable, compact multi-resolution linear image sensor array is disclosed. The multi-resolution image sensor array employs a spatial array of photoelectric sites with each site having an image output terminal and a cluster of switched photo-detector elements. To effect a high quality snapshot operation mode for a high pixel count array, a transfer control switch is added bridging each photo-detector element and its correspondingly connected negative input terminal of an operational amplifier to form an active pixel sensor circuit. To minimize a reset kTC noise associated with numerous traditional active pixel sensor circuits, an in-pixel KTC noise-correlated correlated multiple sampling (CMS) circuitry is also proposed to replace an otherwise traditional correlated double sampling (CDS) circuitry.

Owner:CMOS SENSOR

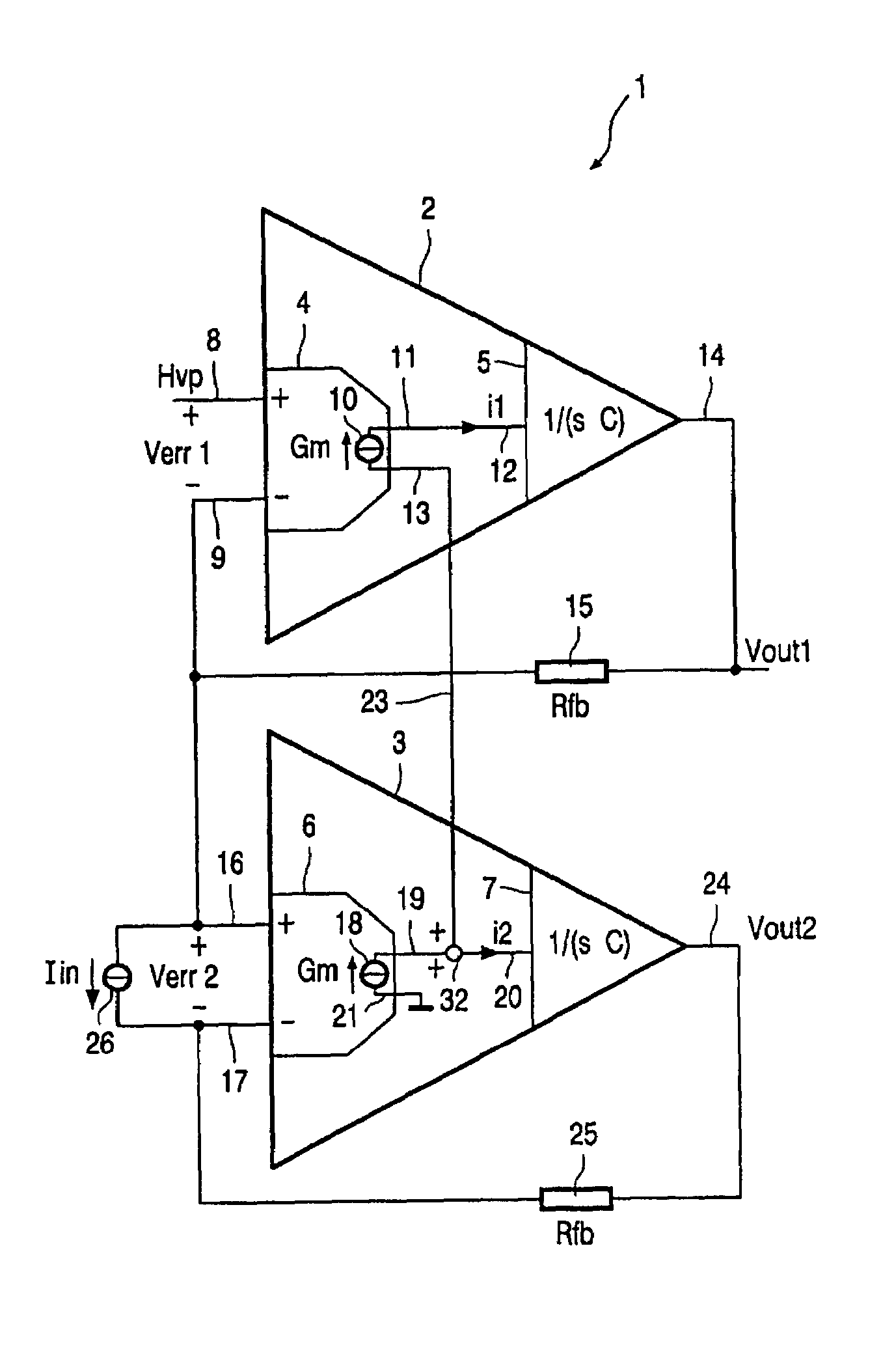

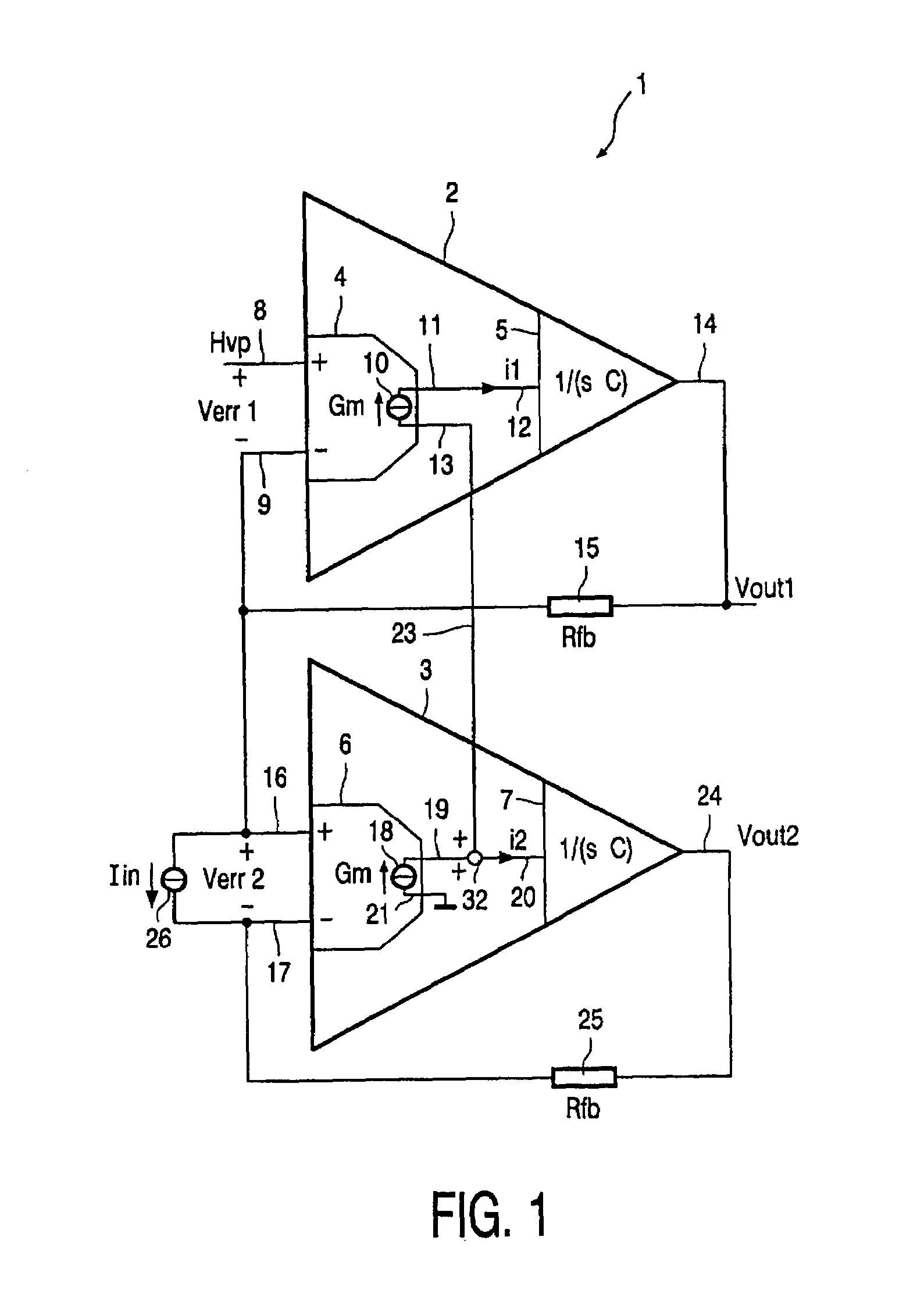

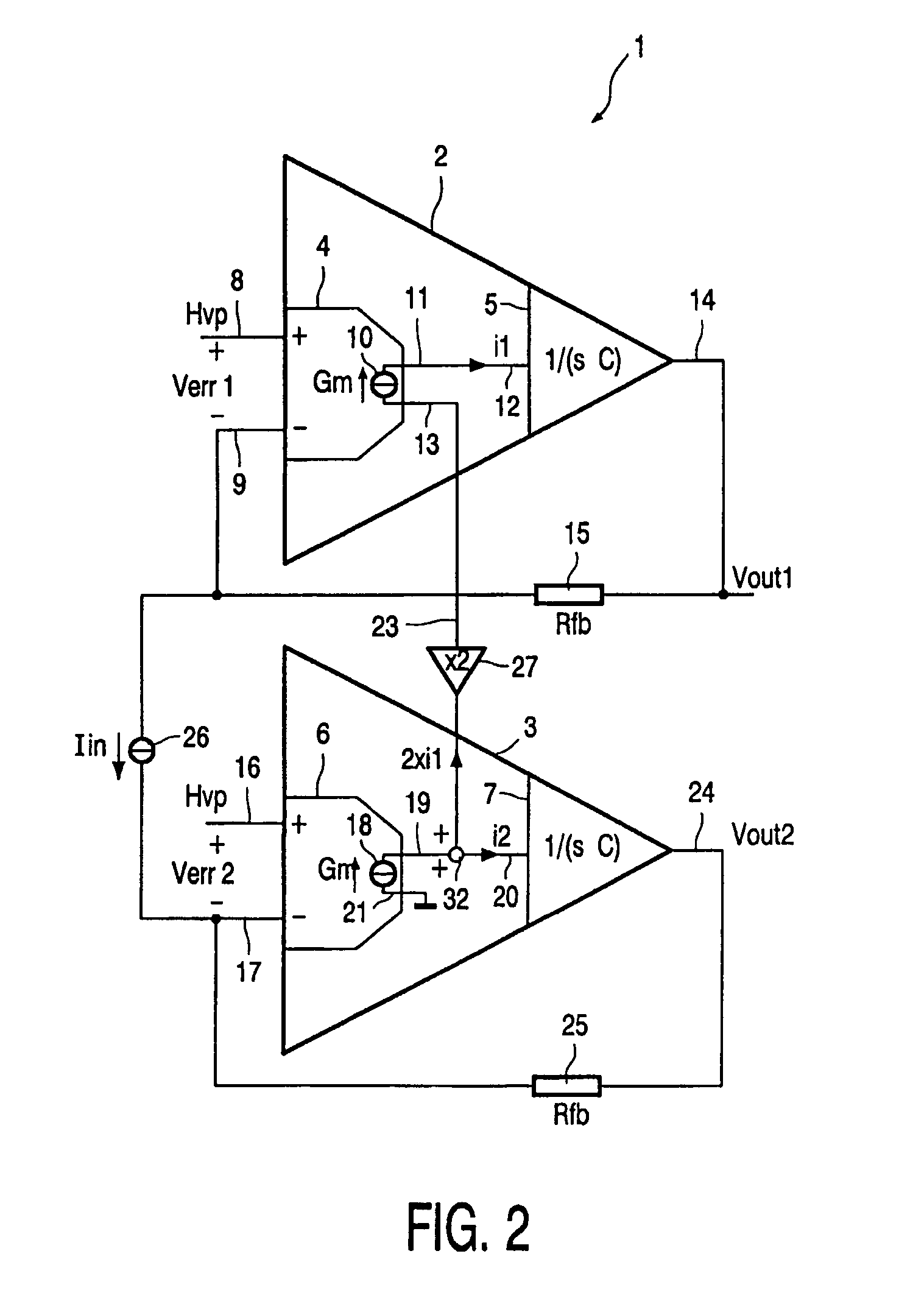

Power amplifier module with distortion compensation

InactiveUS7068099B2Reduce conductionImprove transconductanceNegative-feedback-circuit arrangementsAmplifier combinationsAudio power amplifierEngineering

The invention relates to a power amplifier module comprising a first amplifier 2 having a first front-end 4 and a first backend amplifier stage 5 and a second amplifier 3 having a second front-end 6 and a second backend amplifier stage 7, the first amplifier and the second amplifier being arranged in a Bridge Tied Load (BTL) configuration with feedback over the load,characterized in thatthe first and the second backend amplifier stages having point symmetrical transfer functions with respect to the origin,the input current i1 of the first backend amplifier stage being substantially equal to the input current i2 of the second backend amplifier stage.

Owner:NXP BV

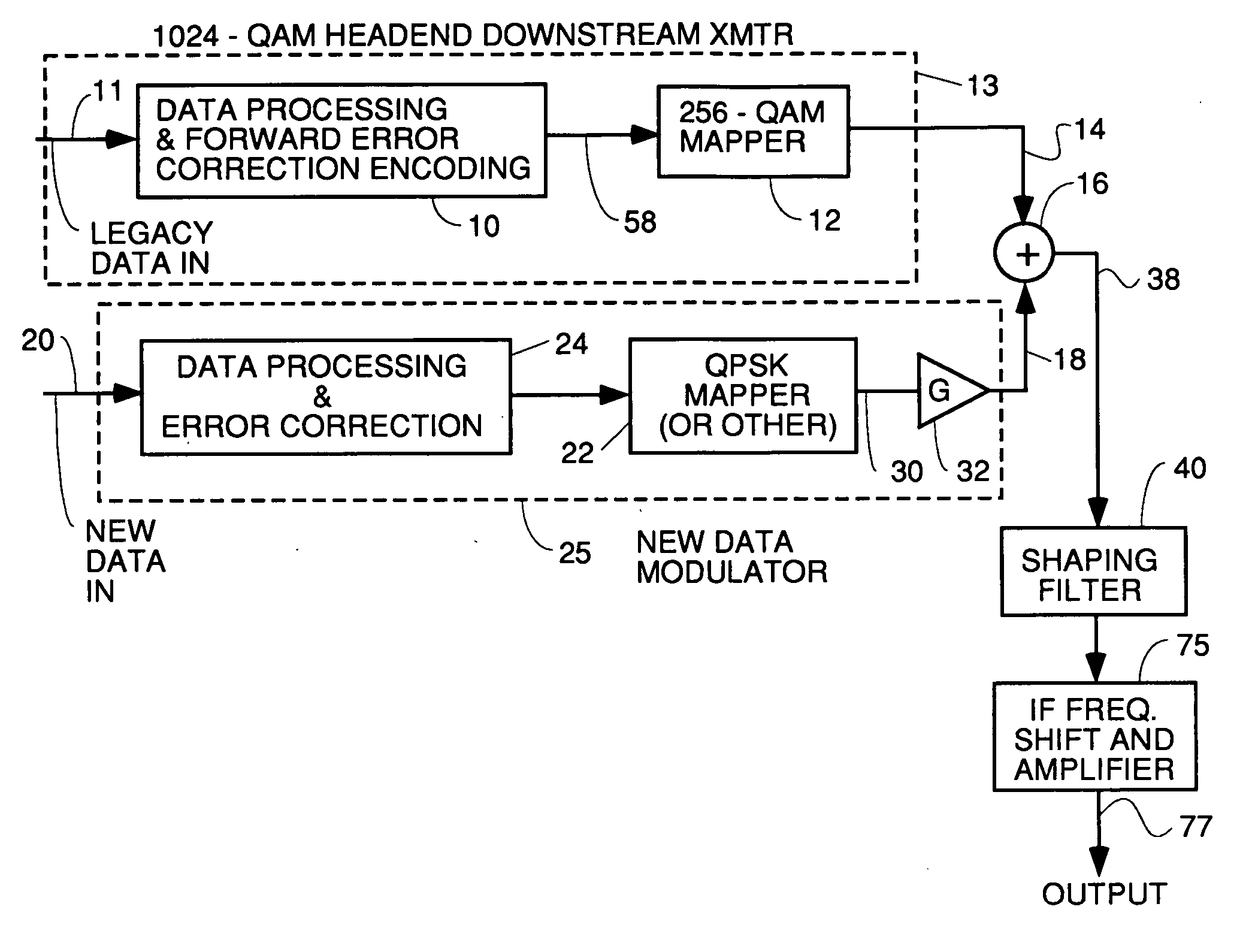

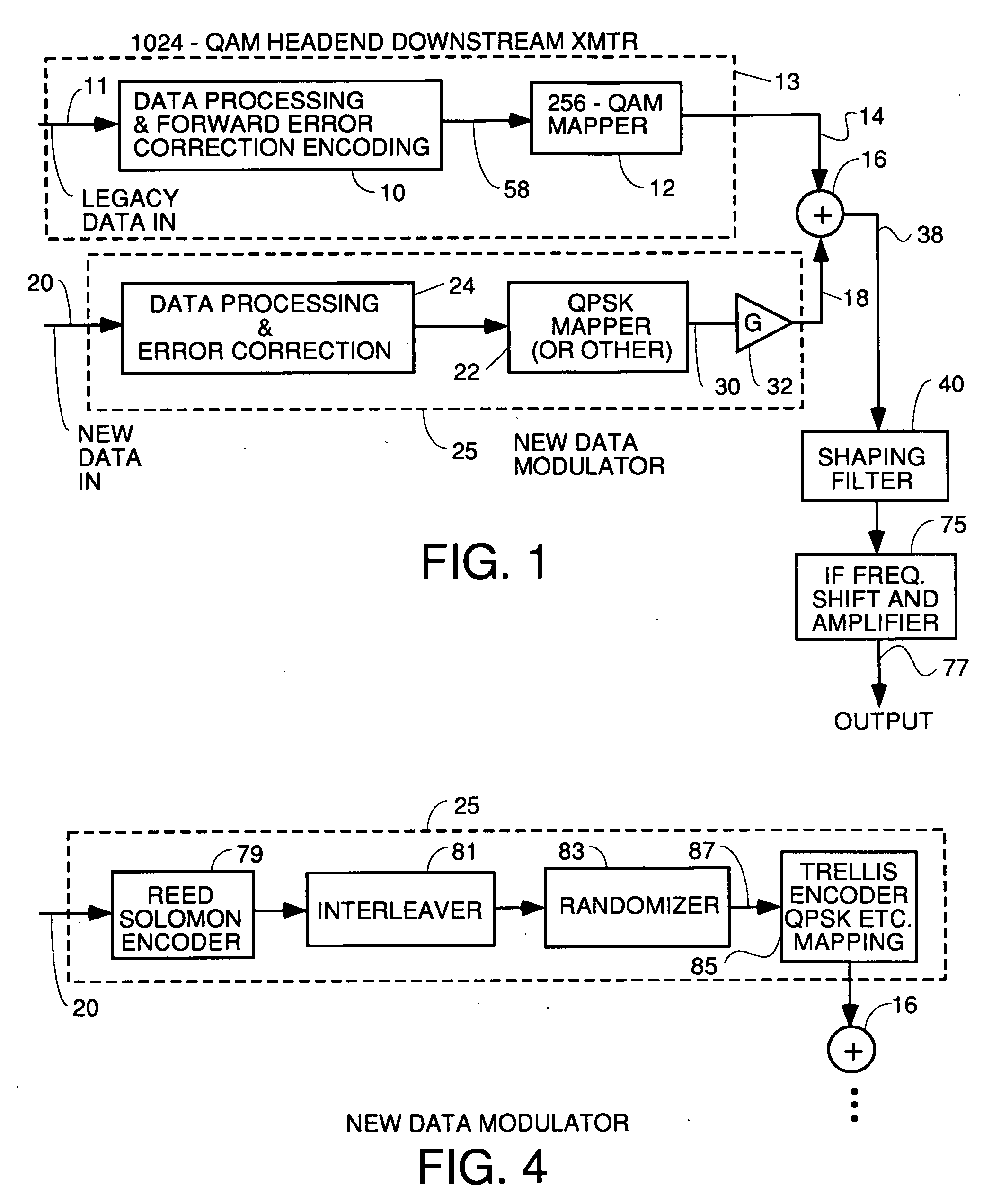

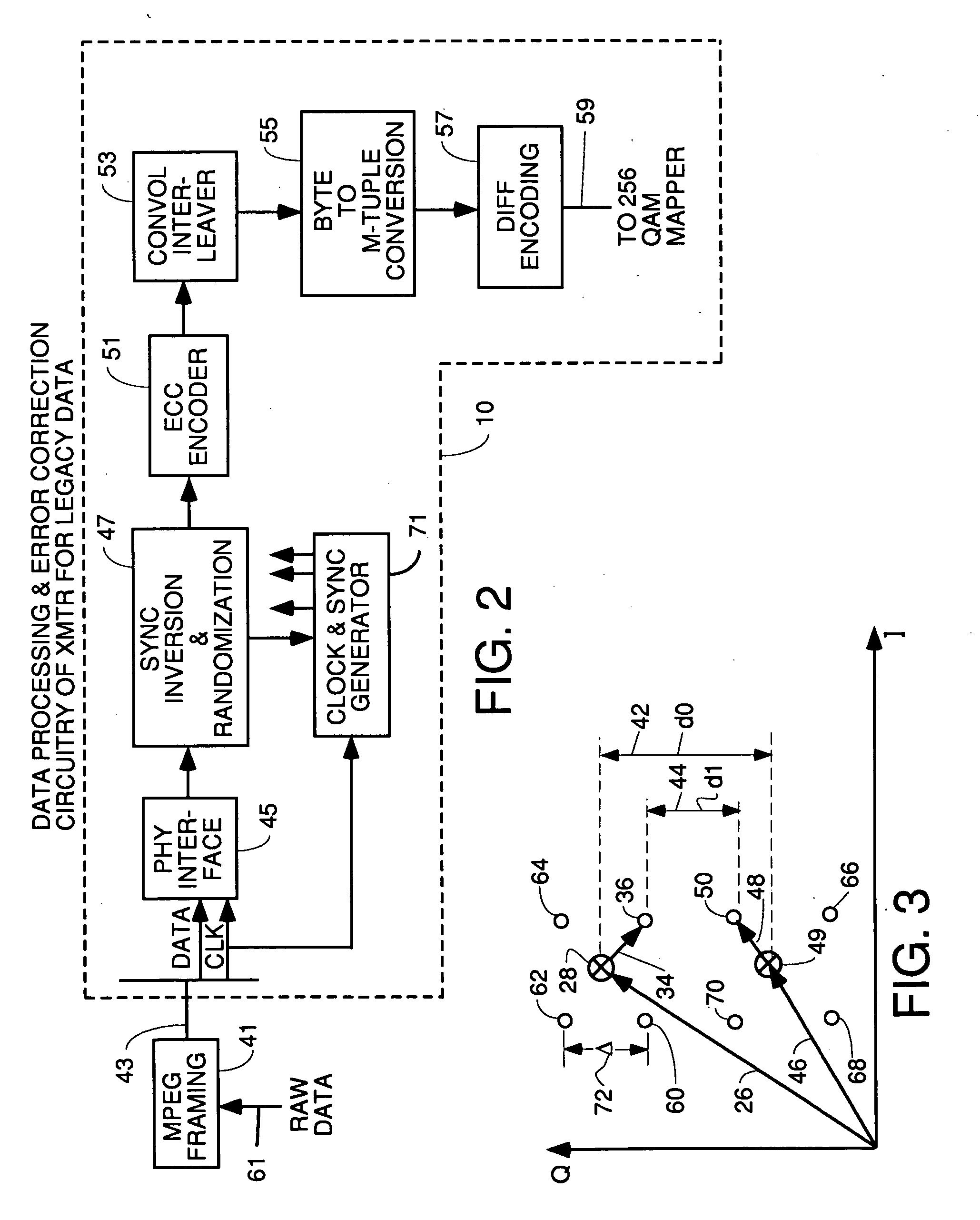

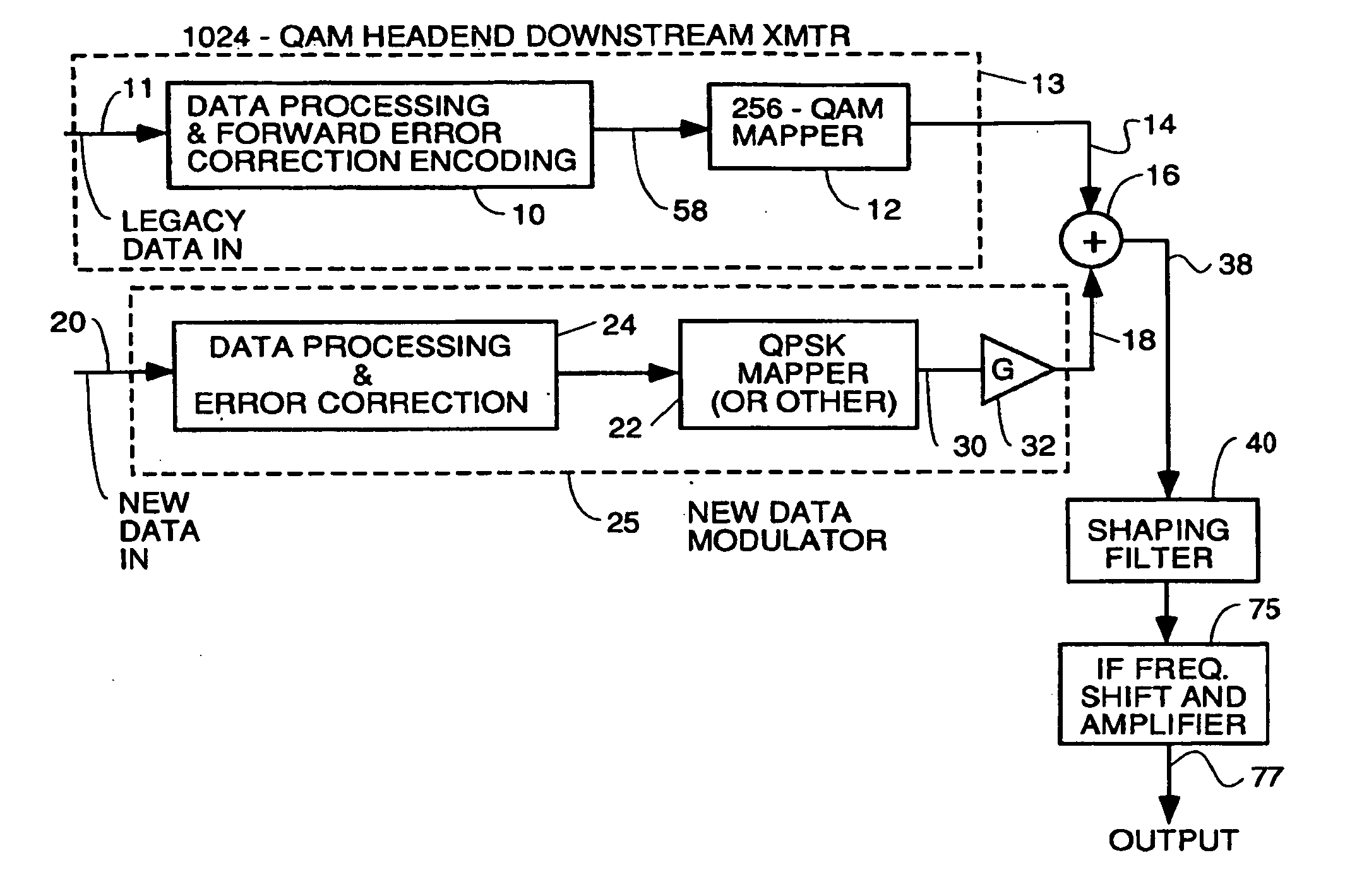

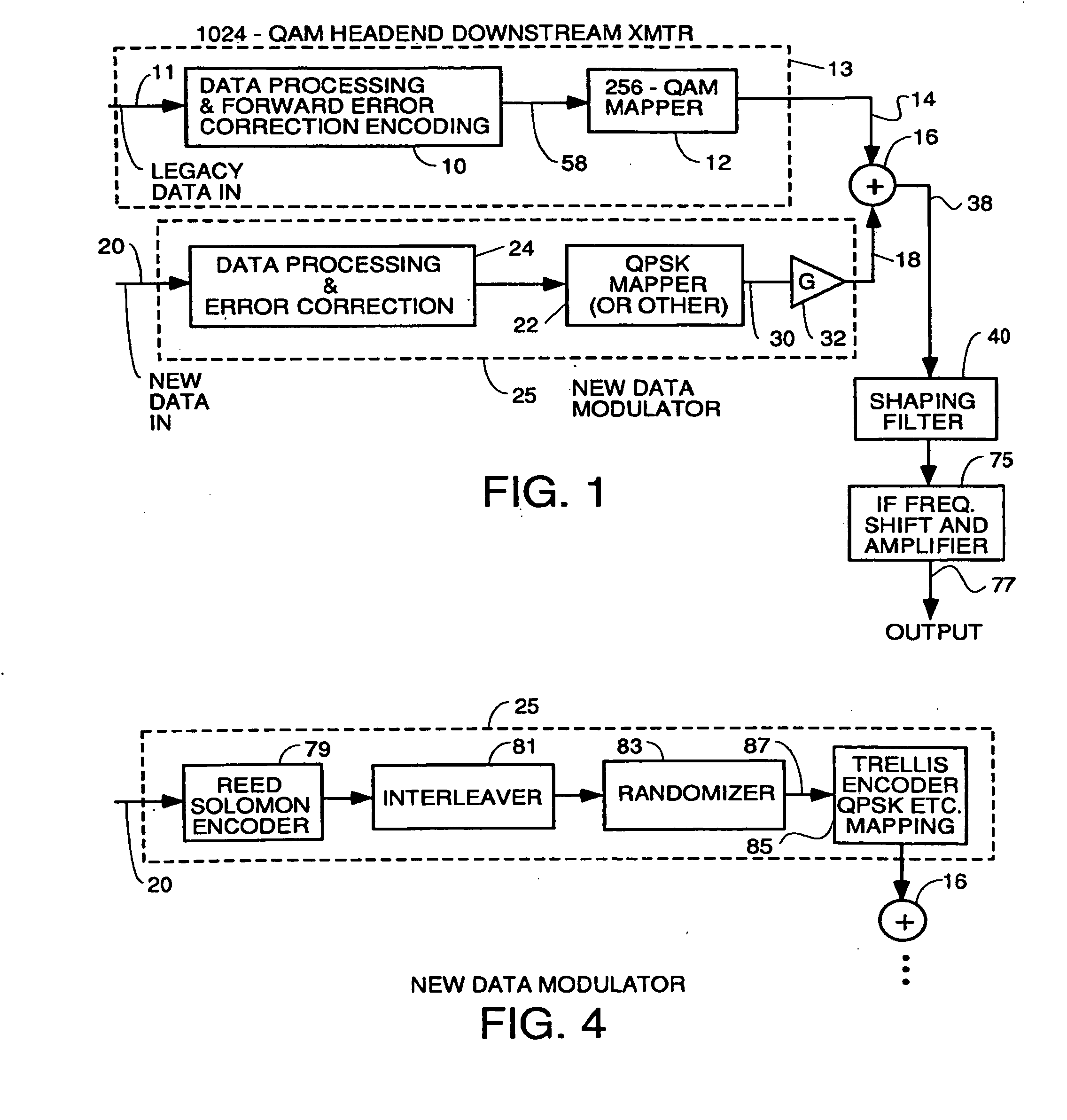

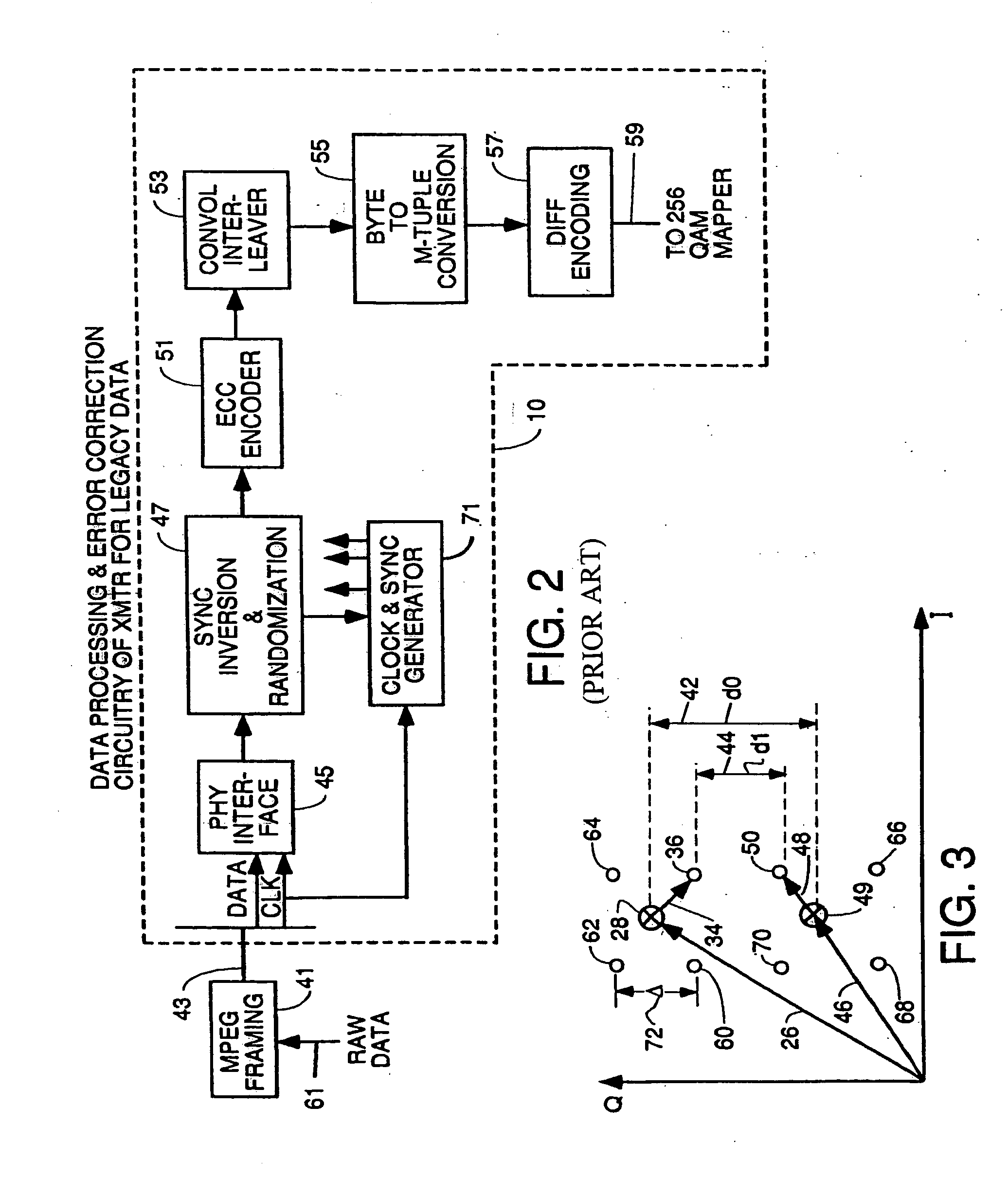

Downstream transmitter and cable modem receiver for 1024 QAM

InactiveUS20060085727A1Shortening HFC lengthMinimize reflectionSimultaneous amplitude and angle modulationData representation error detection/correctionModem deviceAudio power amplifier

A headend transmitter that transmits 1024 QAM including a 256 QAM modulator which has been modified to have more aggressive forward error correction processing. The 256 QAM modulator outputs 256 QAM points to a summer. Another data modulator receives additional data to be transmitted in a separate, substantially less complex constellation. This modulator processes the additional data to do forward error correction thereon and then maps the encoded data into a less complex constellation such as QPSK, 16 QAM etc. The additional data constellation points are then amplified in a variable gain amplifier and fed to a summer where each additional data point is added by vector summation to one 256 QAM point. The output 1024 QAM point is filtered and shifted to the desired transmission frequency. Legacy cable modem receivers can still receive the 256 QAM point since the addition of the new data just appears to be noise which they can overcome using the parity bits encoded in the transmitted symbols. 1024 QAM cable modem receivers receive both the 256 QAM points and the new data points and output both.

Owner:AVAGO TECH INT SALES PTE LTD

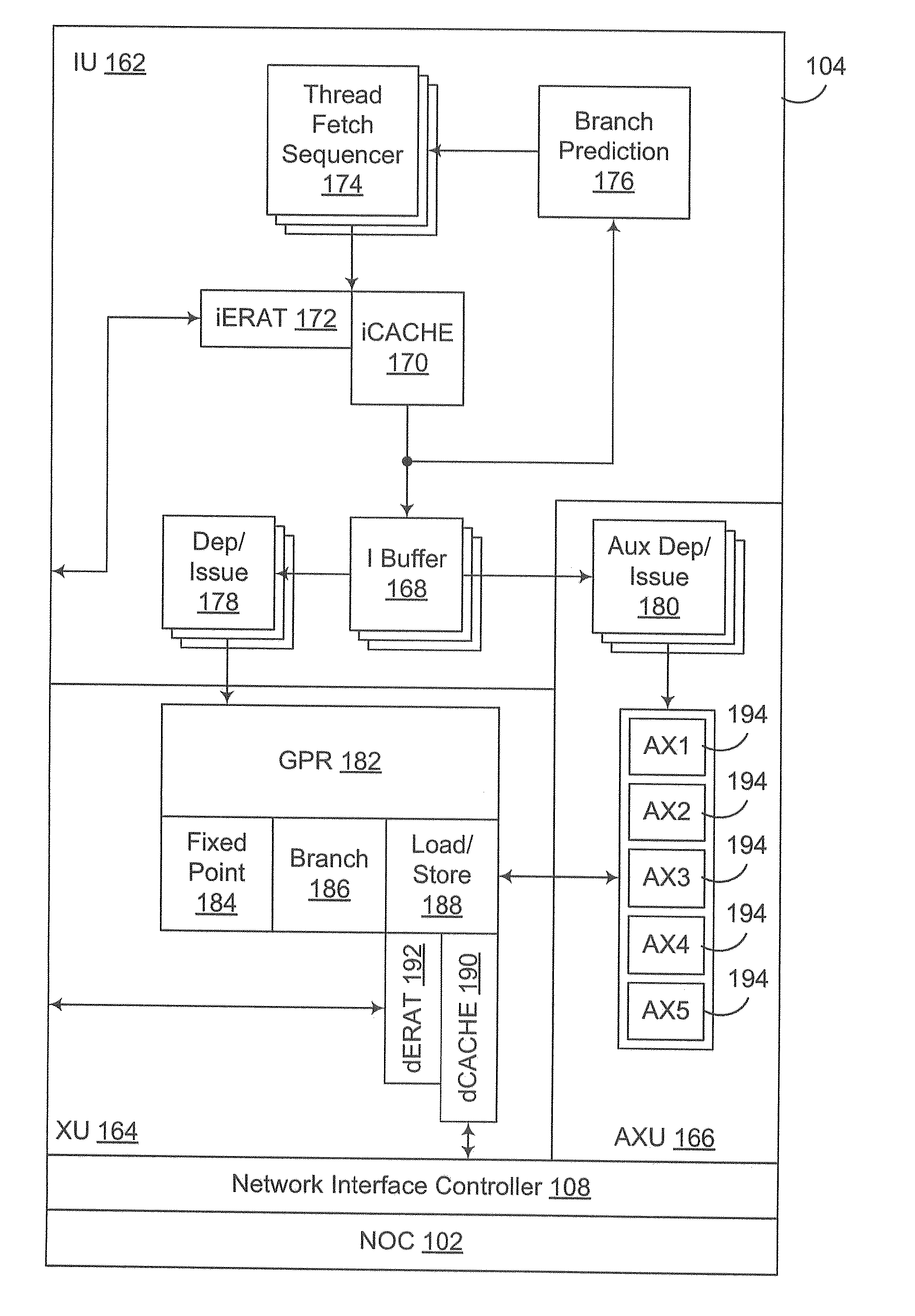

Fault tolerant stability critical execution checking using redundant execution pipelines

InactiveUS20110302450A1GreatAdditional circuitryDigital computer detailsRedundant operation error correctionComputer scienceExecution unit

A circuit arrangement and method utilize existing redundant execution pipelines in a processing unit to execute multiple instances of stability critical instructions in parallel so that the results of the multiple instances of the instructions can be compared for the purpose of detecting errors. For other types of instructions for which fault tolerant or stability critical execution is not required or desired, the redundant execution pipelines are utilized in a more conventional manner, enabling multiple non-stability critical instructions to be concurrently issued to and executed by the redundant execution pipelines. As such, for non-stability critical program code, the performance benefits of having multiple redundant execution units are preserved, yet in the instances where fault tolerant or stability critical execution is desired for certain program code, the redundant execution units may be repurposed to provide greater assurances as to the fault-free execution of such instructions.

Owner:IBM CORP

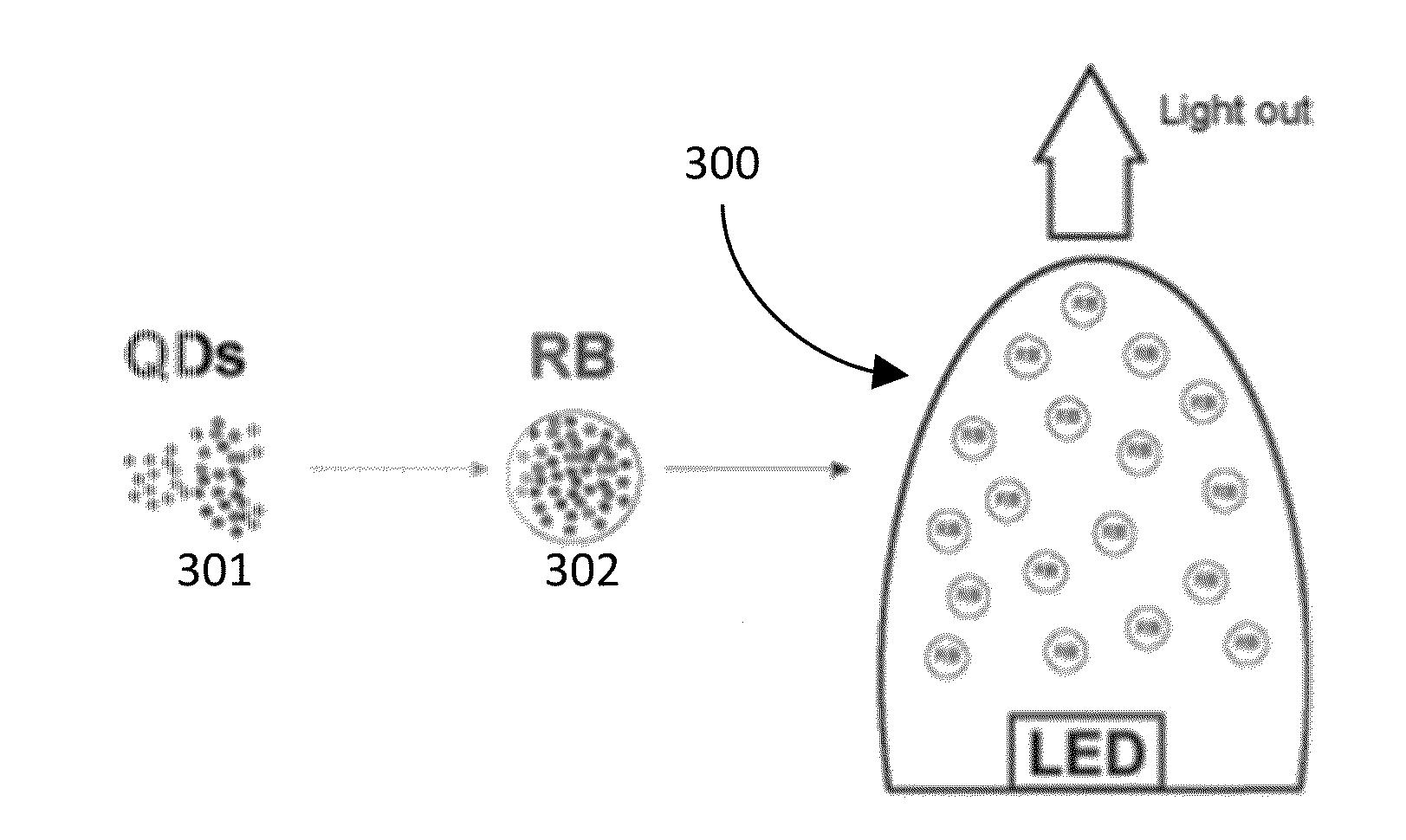

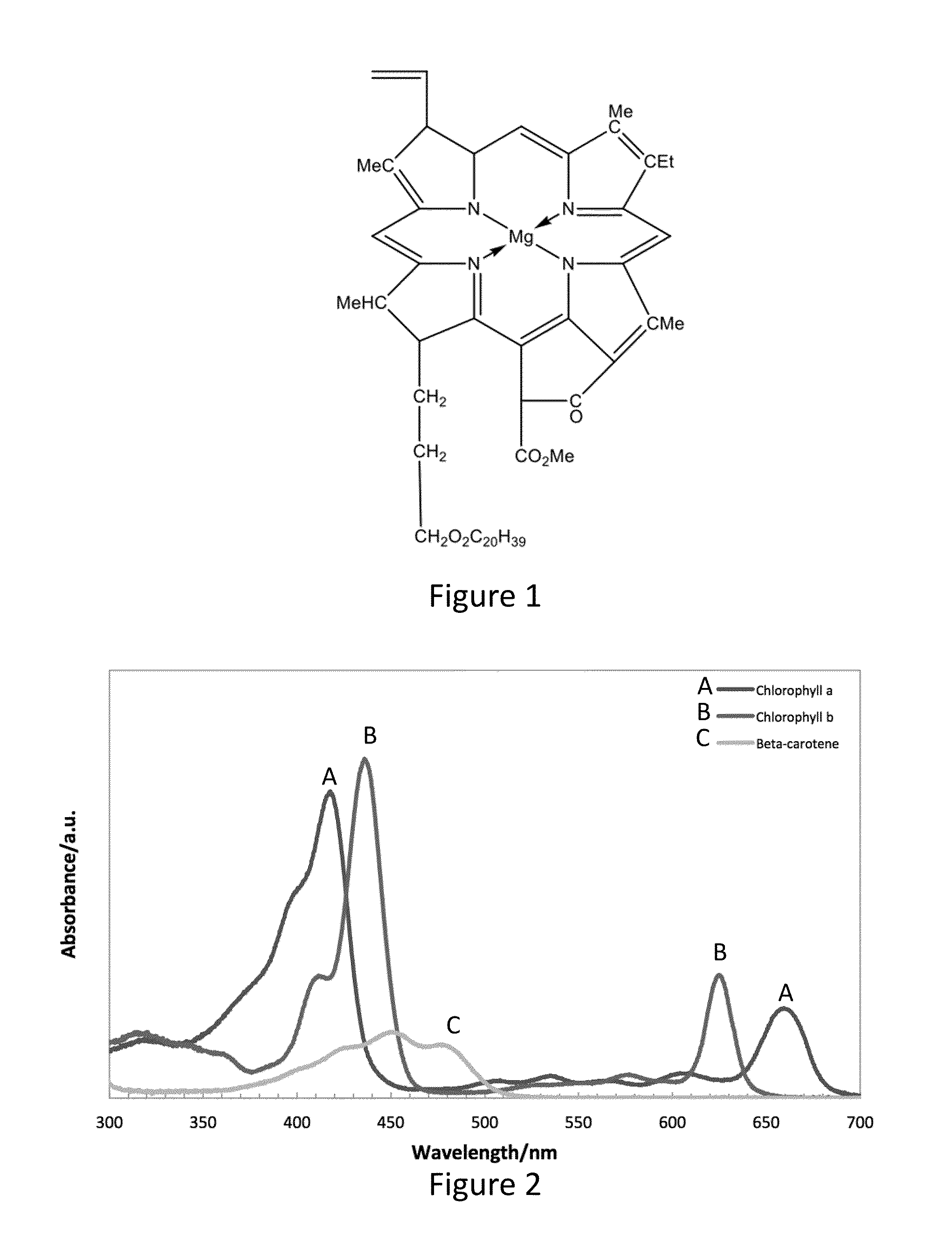

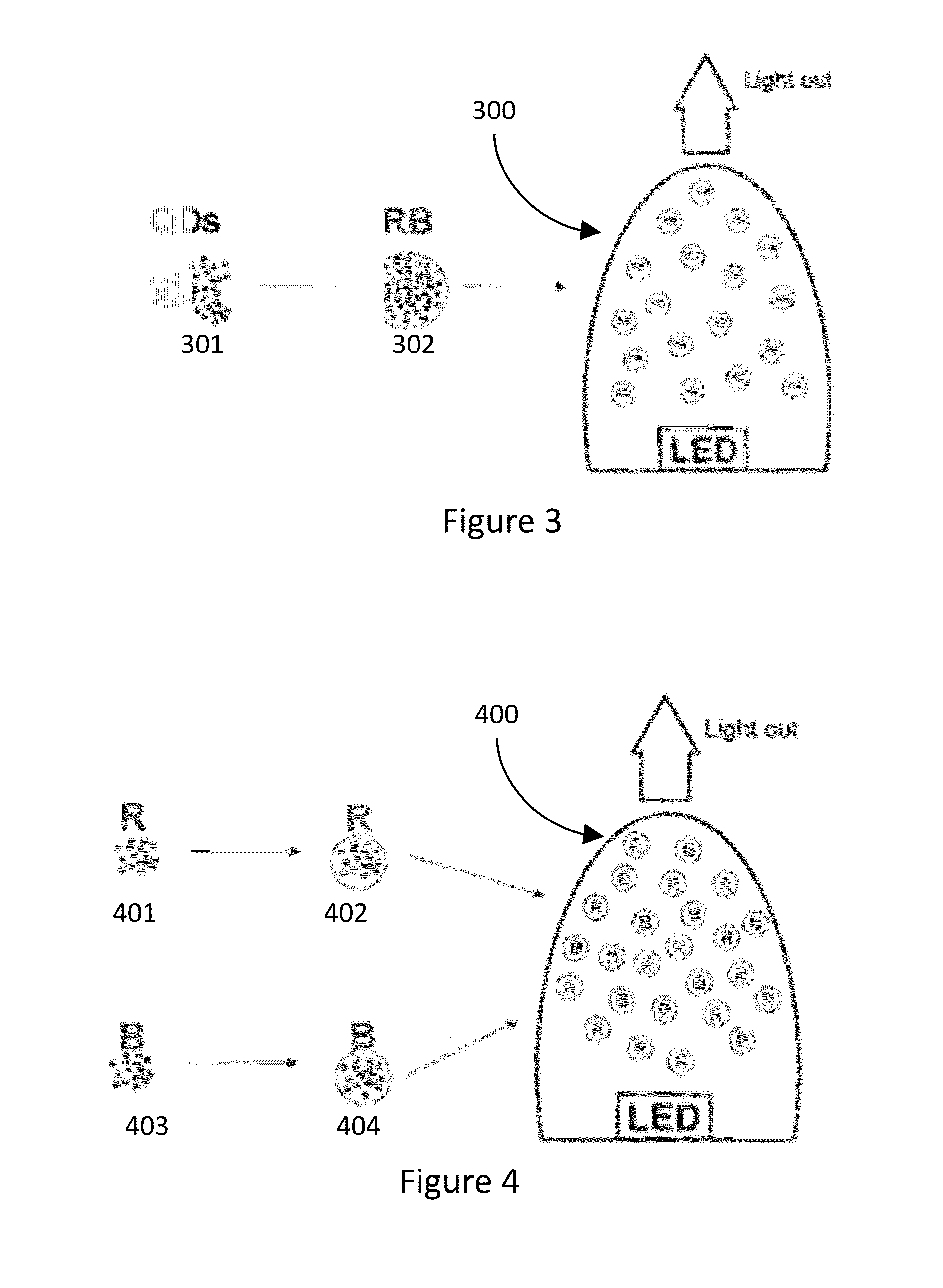

Quantum Dot LED's to Enhance Growth in Photosynthetic Organisms

InactiveUS20130326941A1High photoluminescence quantum yieldPromotes algae growthBioreactor/fermenter combinationsBiological substance pretreatmentsPhotosynthetic pigmentQuantum dot

Quantum dot (QD) LEDs useful for plant, algael and photosynthetic bacterial growth applications. The QD LEDs utilizes a solid state LED (typically emitting blue or UV light) as the primary light source and one or more QD elements as a secondary light source that down-converts the primary light. The emission profile of the QD LED can be tuned to correspond to the absorbance spectrum of one or more photosynthetic pigments of the organism.

Owner:NANOCO TECH LTD

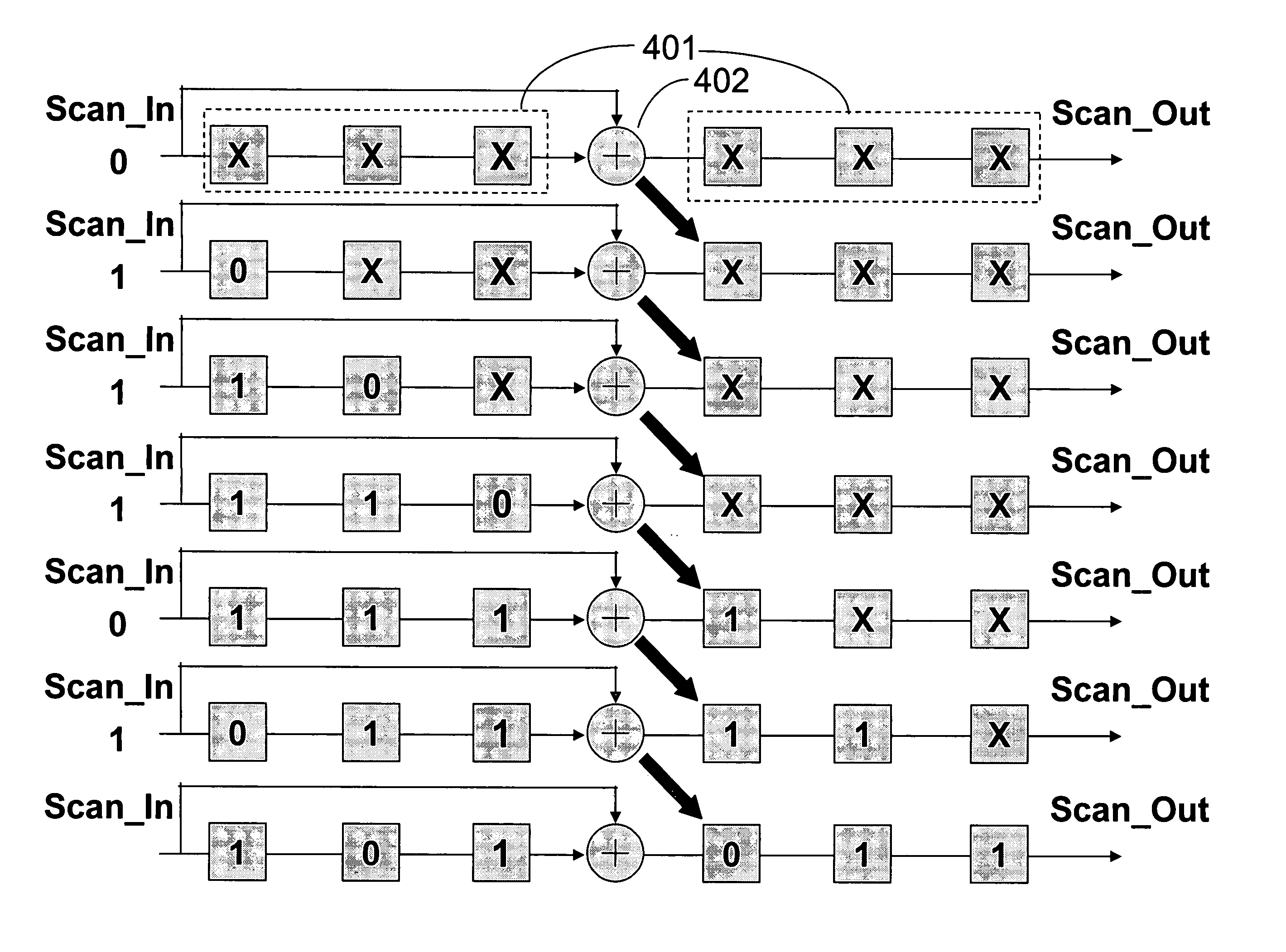

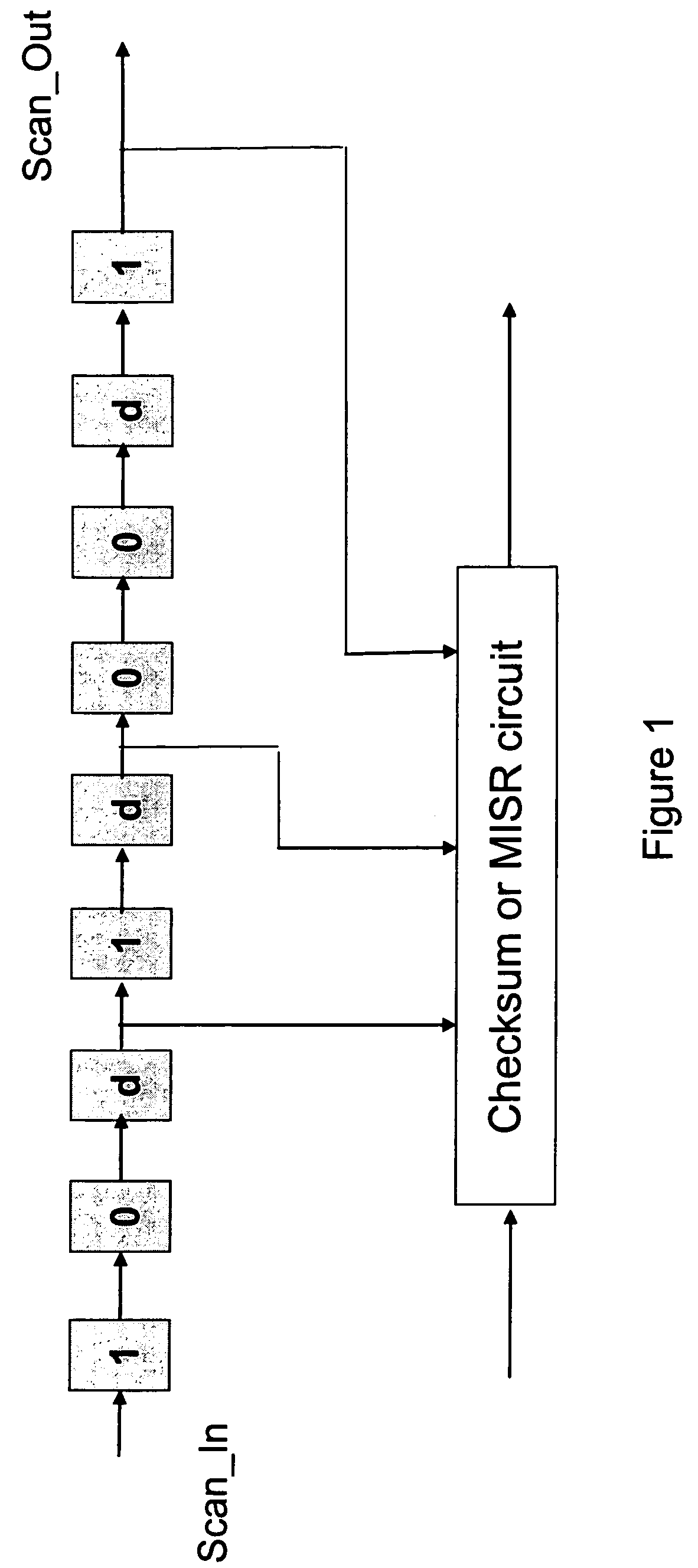

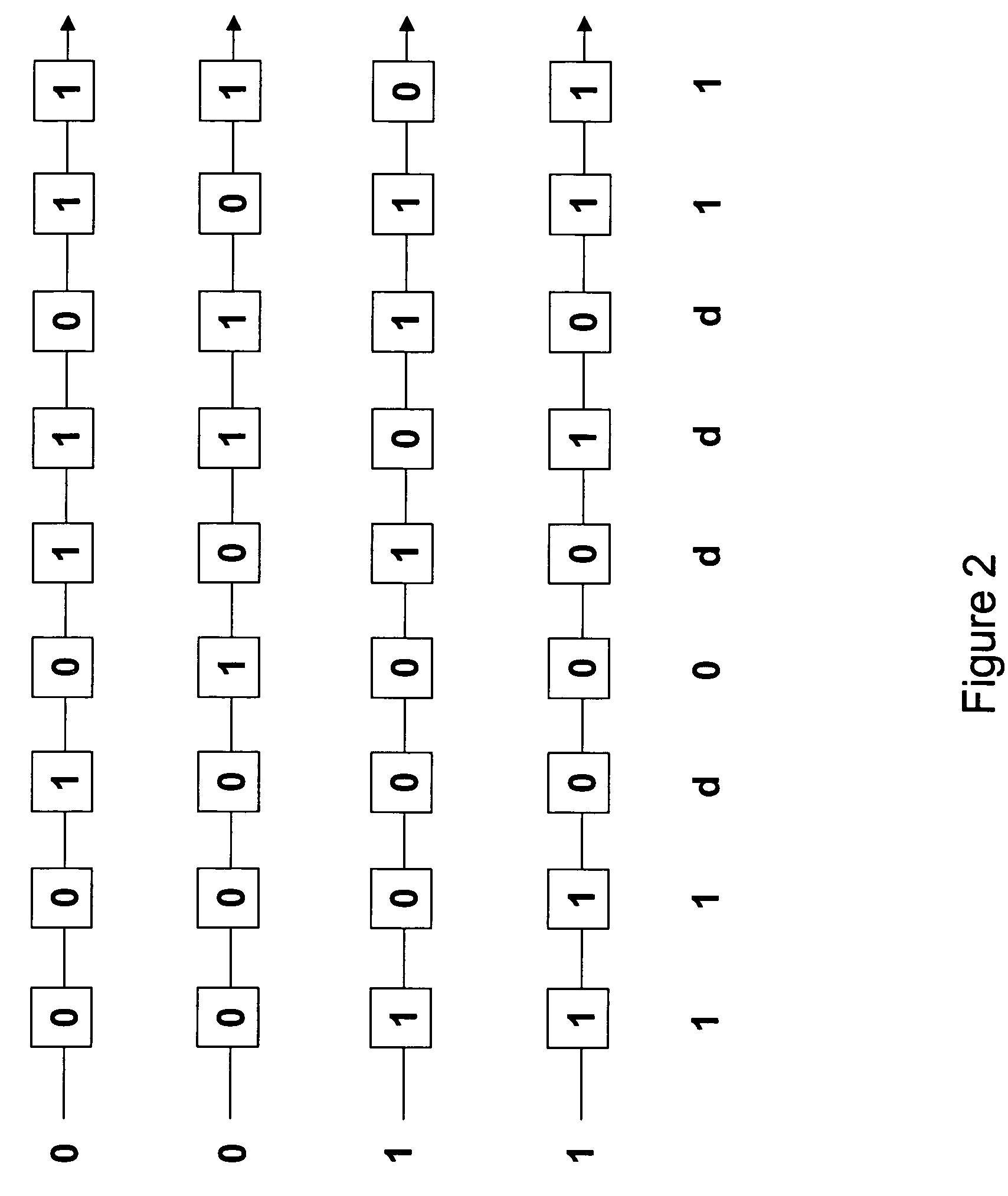

Accelerated scan circuitry and method for reducing scan test data volume and execution time

InactiveUS7197681B2Shorten the timeReduce volumeElectronic circuit testingError detection/correctionCouplingControl signal

An architecture and methodology for test data compression using combinational functions to provide serial coupling between consecutive segments of a scan-chain are described. Compressed serial-scan sequences are derived starting from scan state identifying desired Care_In values and using symbolic computations iteratively in order to determine the necessary previous scan-chain state until computed previous scan-chain state matches given known starting scan-chain state. A novel design for a new flip-flop is also presented that allows implementing scan-chains that can be easily started and stopped without requiring an additional control signal. Extensions of the architecture and methodology are discussed to handle unknown (X) values in scan-chains, proper clocking of compressed data into multiple scan-chains, the use of a data-spreading network and the use of a pseudo-random signal generator to feed the segmented scan-chains in order to implement Built In Self Test (BIST).

Owner:AMERICAN PATENTS LLC +1

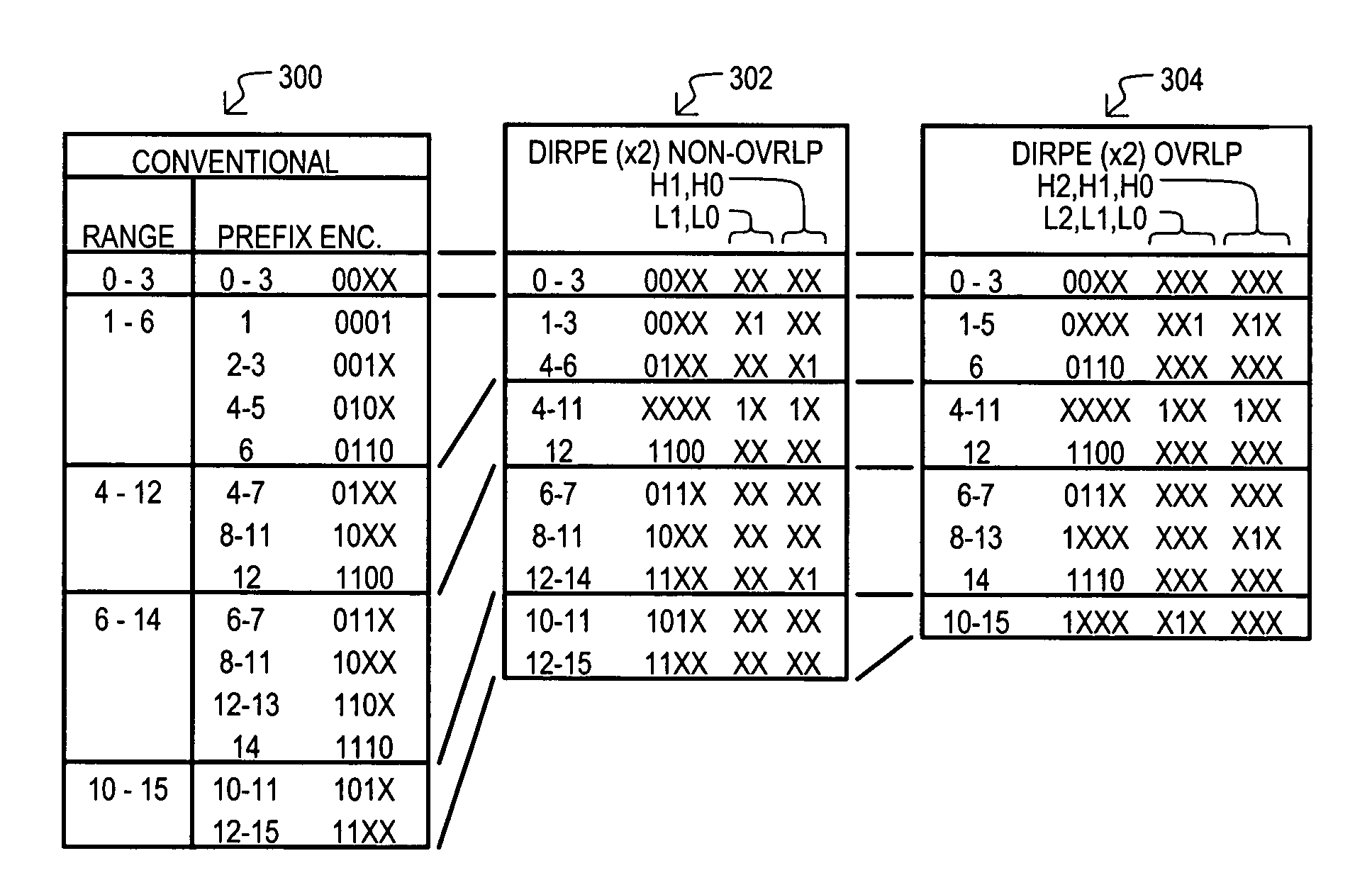

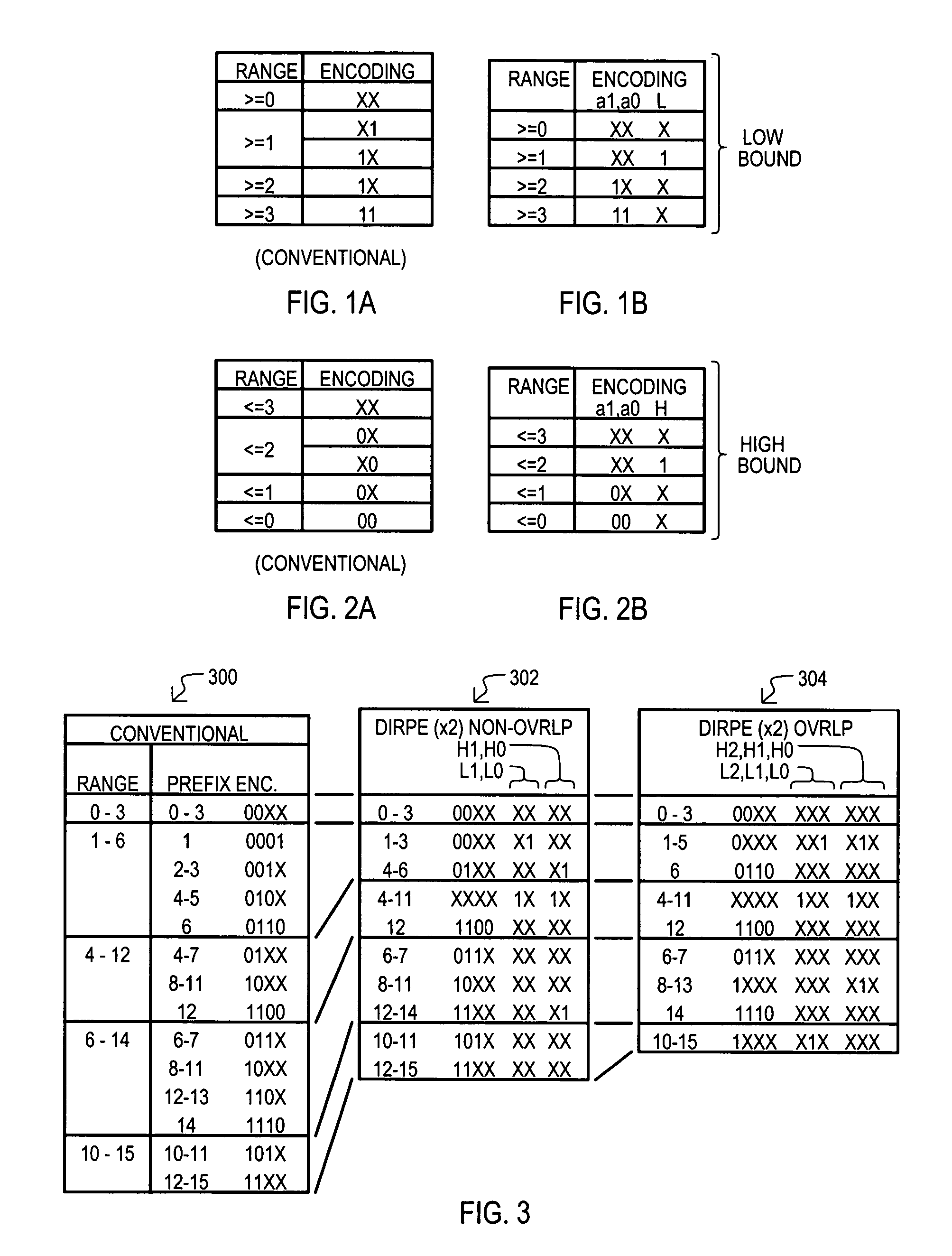

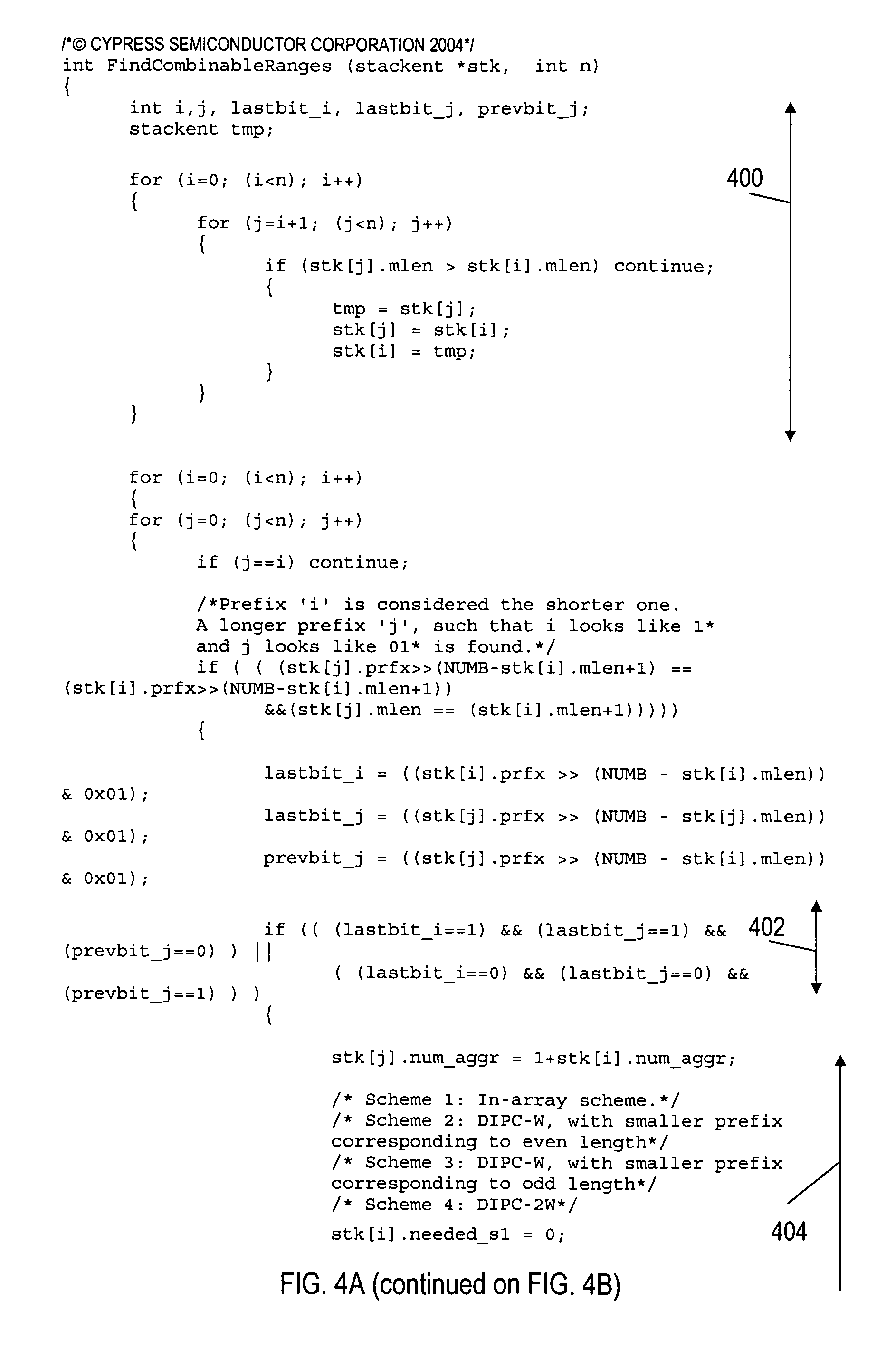

Range code compression method and apparatus for ternary content addressable memory (CAM) devices

InactiveUS7711893B1Reduce in quantityIncrease in sizeDigital storageMemory systemsPartial representationOne-hot

A content addressable memory (CAM) device, method, and method of generating entries for range matching are disclosed. A CAM device (800) according to one embodiment can include a pre-encoder (806) that encodes range bit values W into additional bits E. Additional bits E can indicate compression of range rules according to particular bit pairs. A CAM array (802) can include entries that store compressed range code values (RANGE) with corresponding additional bit values (ENC). Alternate embodiments can include pre-encoders that encode portions of range values (K1 to Ki) in a “one-hot” fashion. Corresponding CAM entries can include encoded value having sections that each represent increasingly finer divisions of a range space.

Owner:AVAGO TECH INT SALES PTE LTD

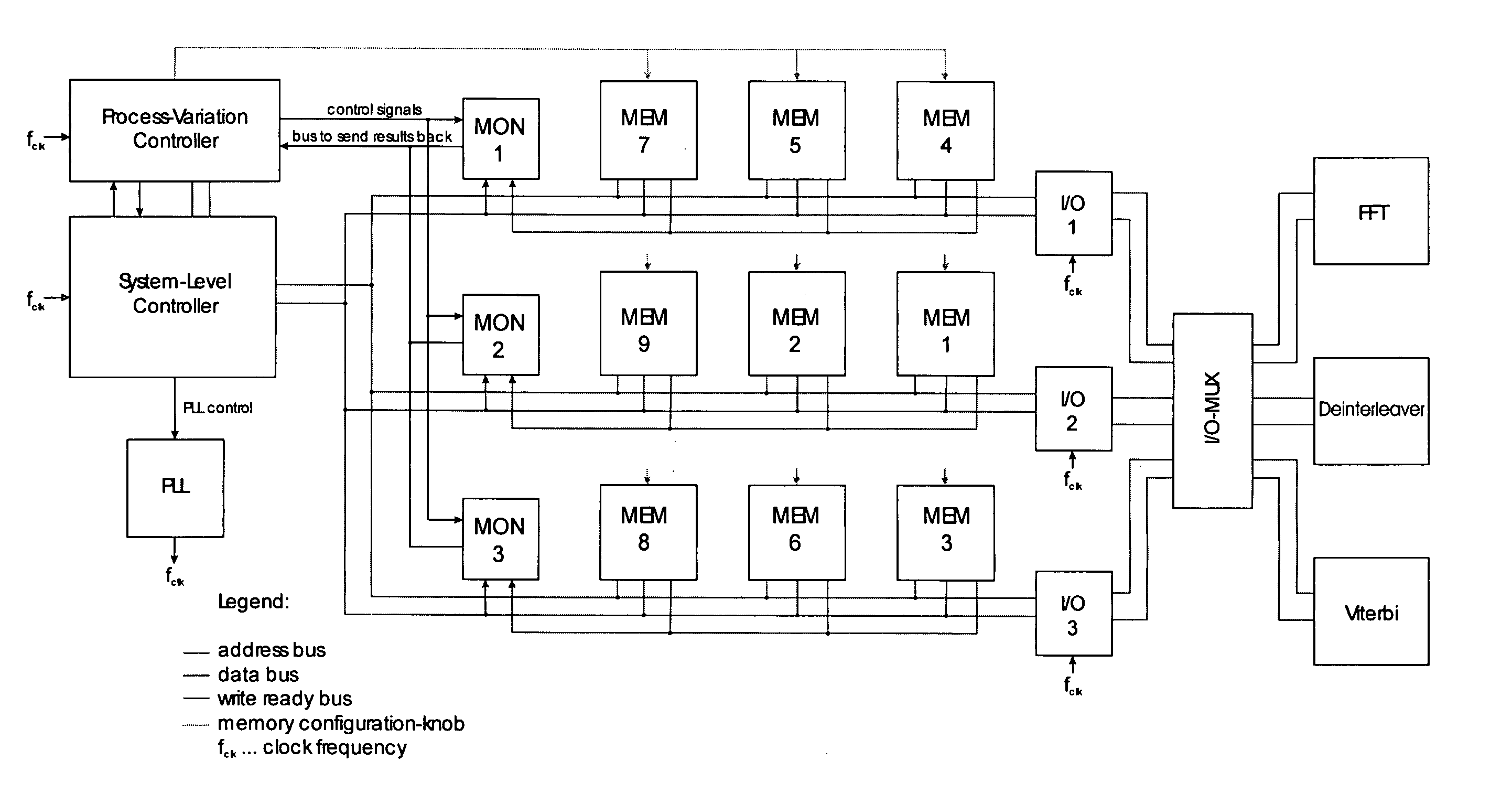

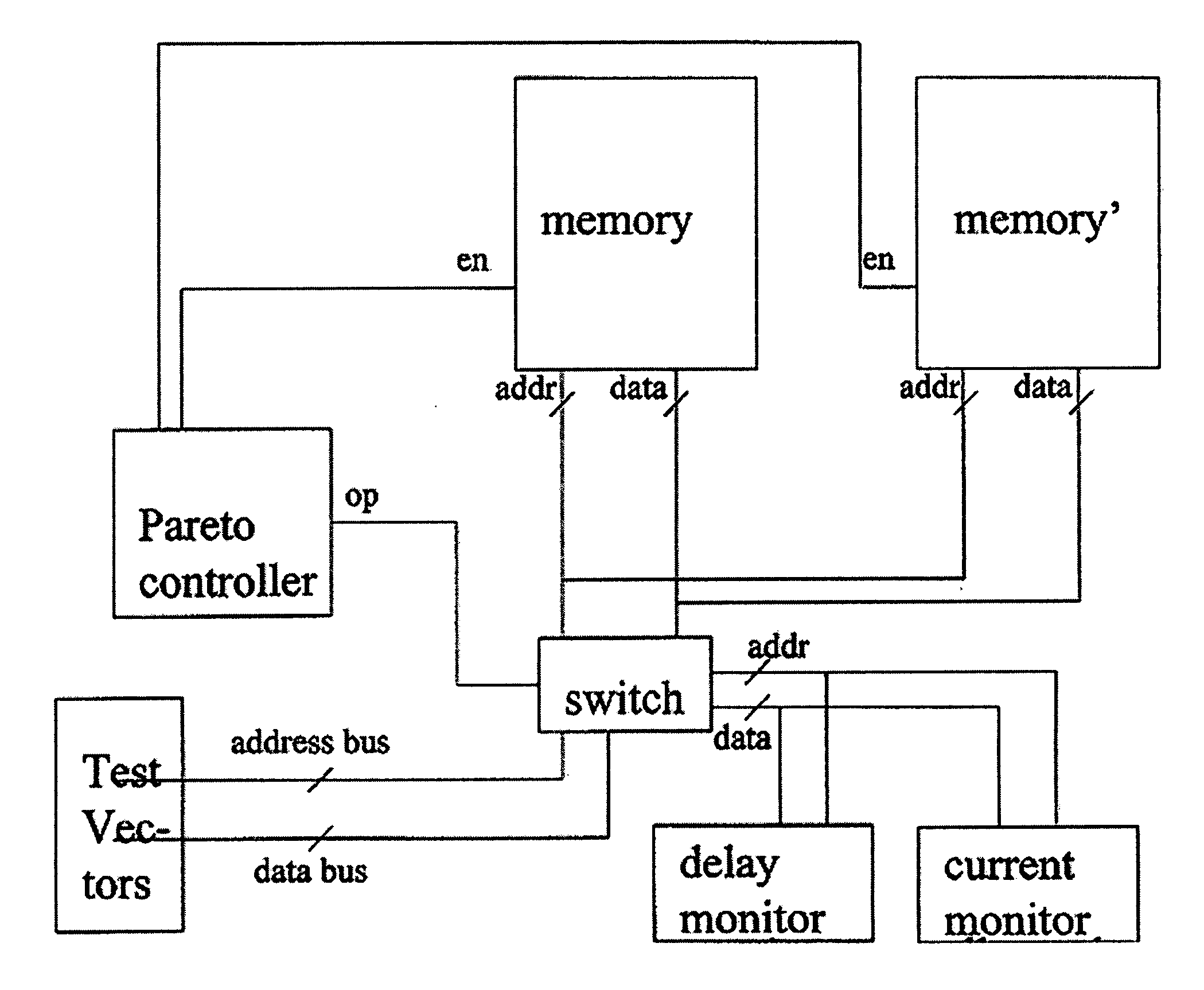

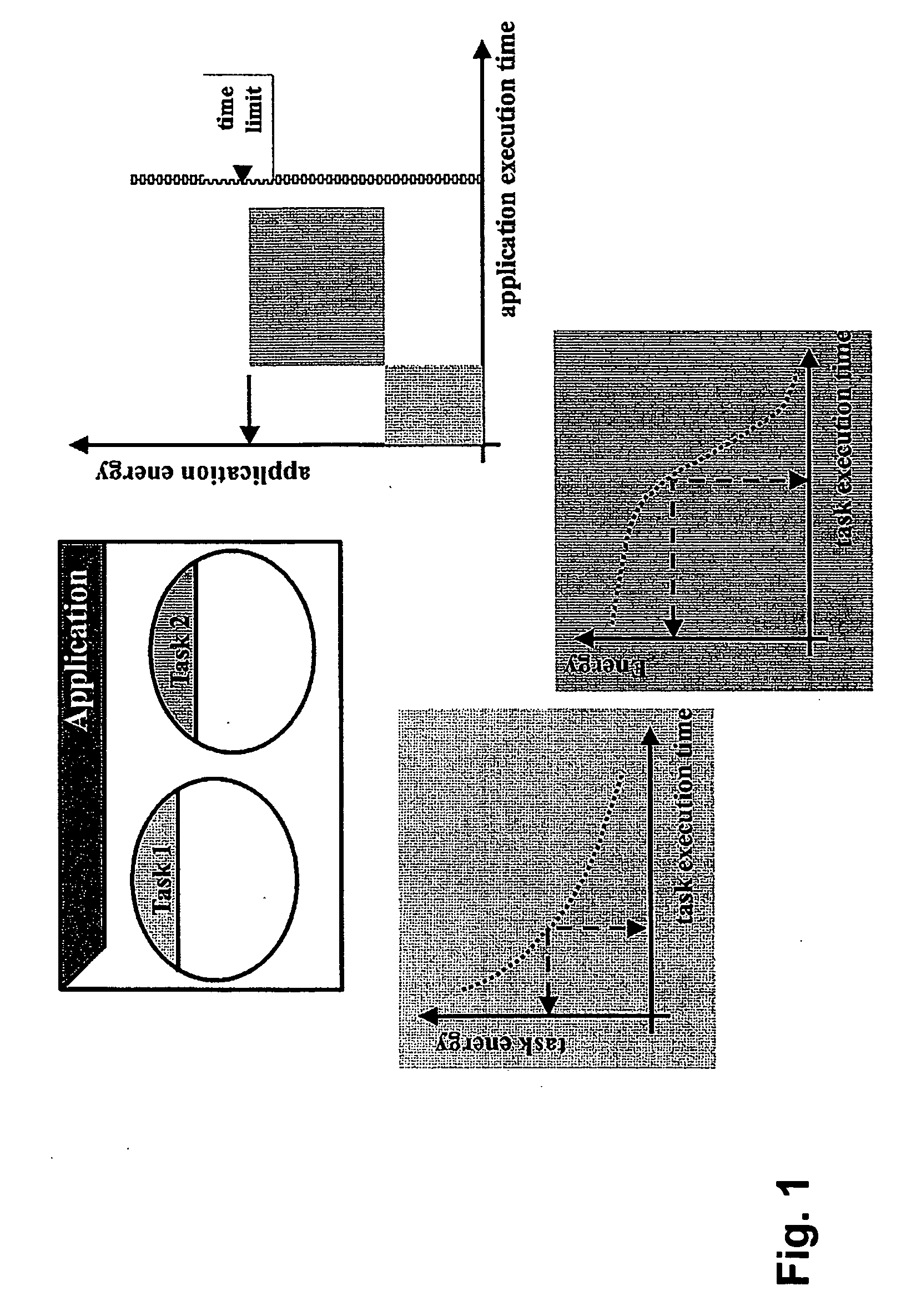

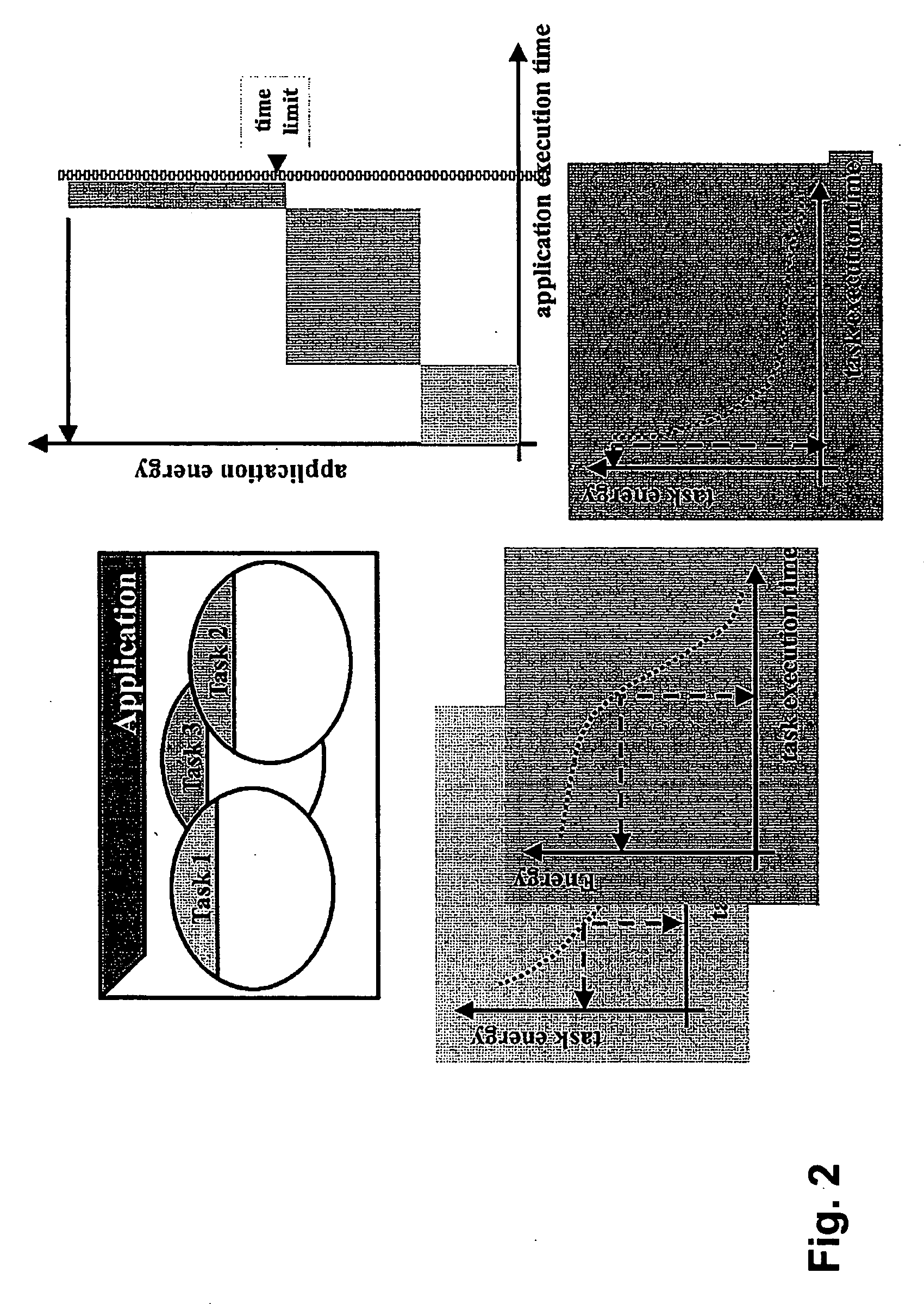

Method and apparatus for designing and manufacturing electronic circuits subject to process variations

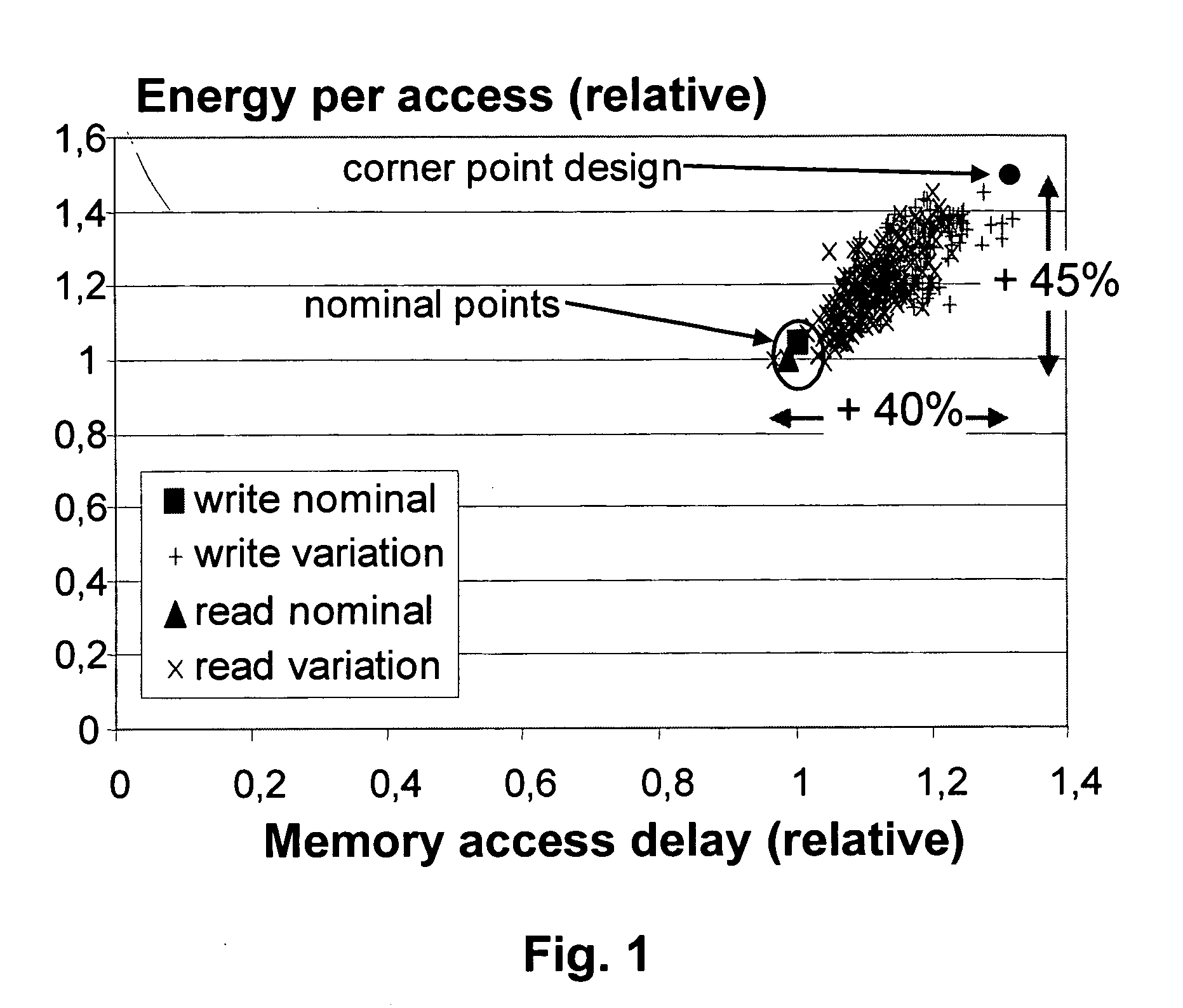

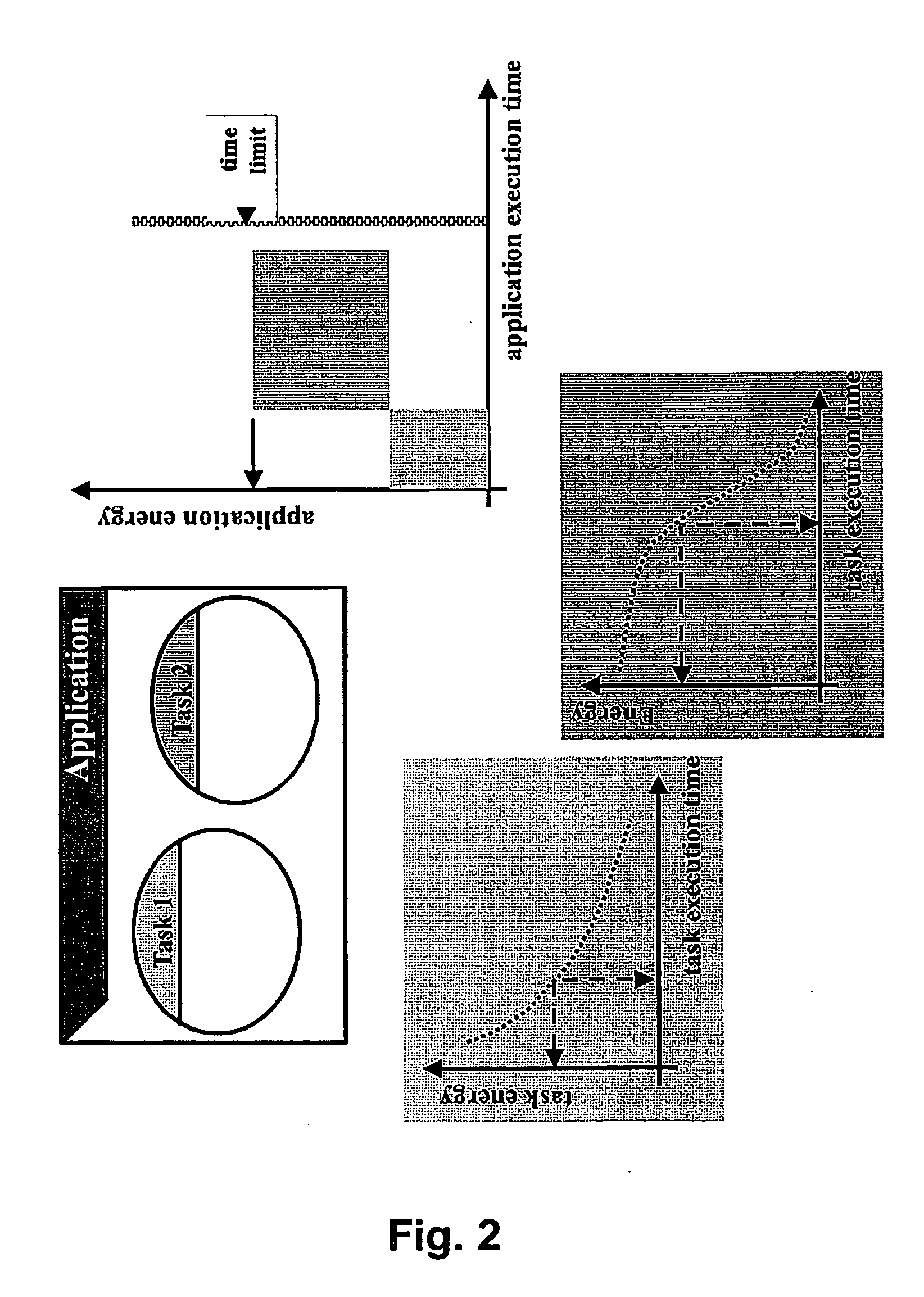

ActiveUS20050235232A1Additional circuitryImprove the environmentDetecting faulty computer hardwareCAD circuit designDisplay deviceTrade offs

Methods and apparatus are described in which, at design-time a thorough analysis and exploration is performed to represent a multi-objective “optimal” trade-off point or points, e.g. on Pareto curves, for the relevant cost (C) and constraint criteria. More formally, the trade-off points may e.g. be positions on a hyper-surface in an N-dimensional Pareto search space. The axes represent the relevant cost (C), quality cost (Q) and restriction (R) criteria. Each of these working points is determined by positions for the system operation (determined during the design-time mapping) for a selected set of decision knobs (e.g. the way data are organized in a memory hierarchy). The C-Q-R values are determined based on design-time models that then have to be “average-case” values in order to avoid a too worst-case characterisation. At processing time, first a run-time BIST manager performs a functional correctness test, i.e. checks all the modules based on stored self-test sequences and “equivalence checker” hardware. All units that fail are deactivated (so that they cannot consume any power any more) and with a flag the run-time trade-off controllers, e.g. Pareto controllers, are informed that these units are not available any more for the calibration or the mapping. At processing time, also a set of representative working points are “triggered” by an on-chip trade-off calibration manager, e.g. a Pareto calibration manager, that controls a set of monitors which measure the actual C-Q-R values and that calibrates the working points to their actual values. Especially timing monitors require a careful design because correctly calibrated absolute time scales have to be monitored.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

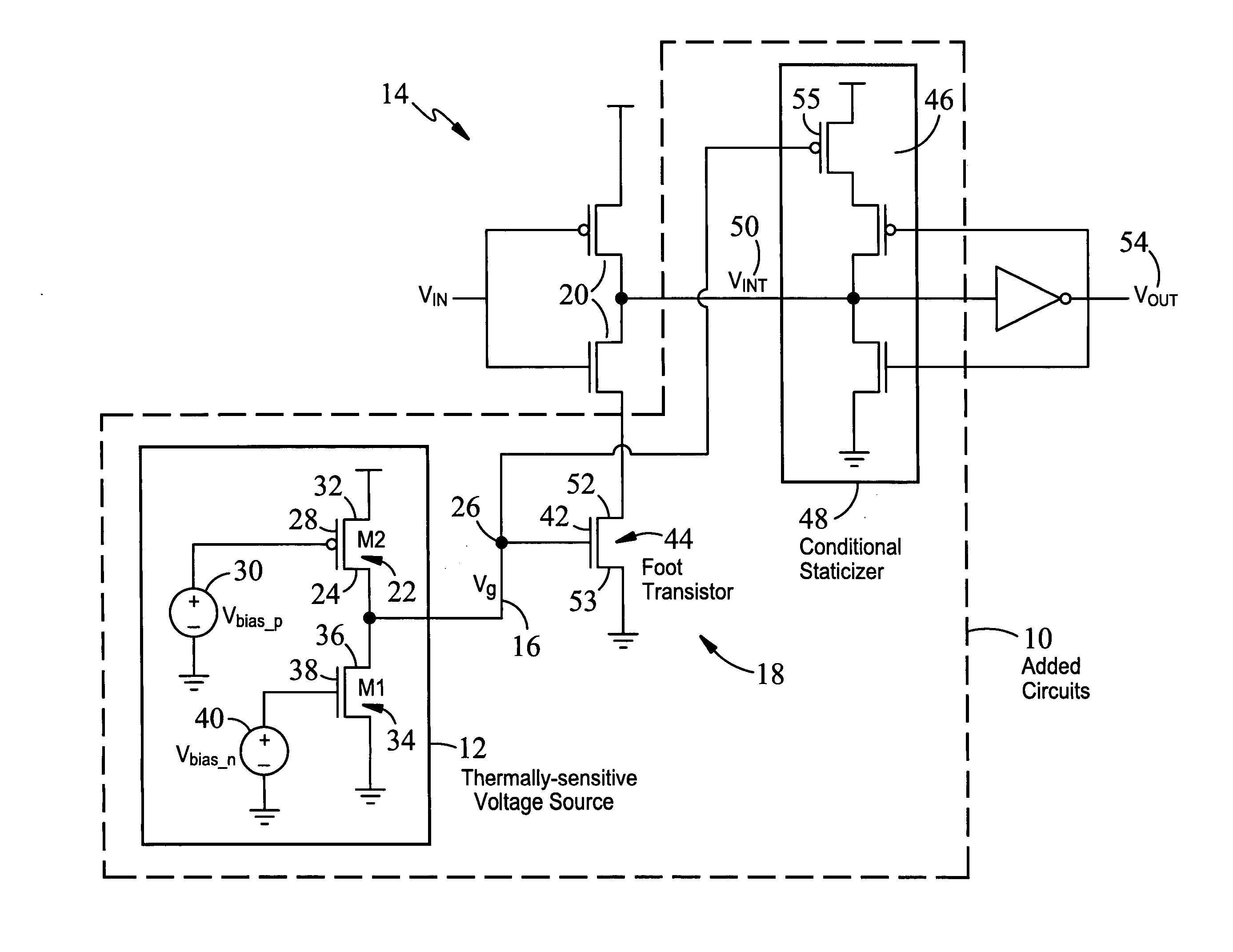

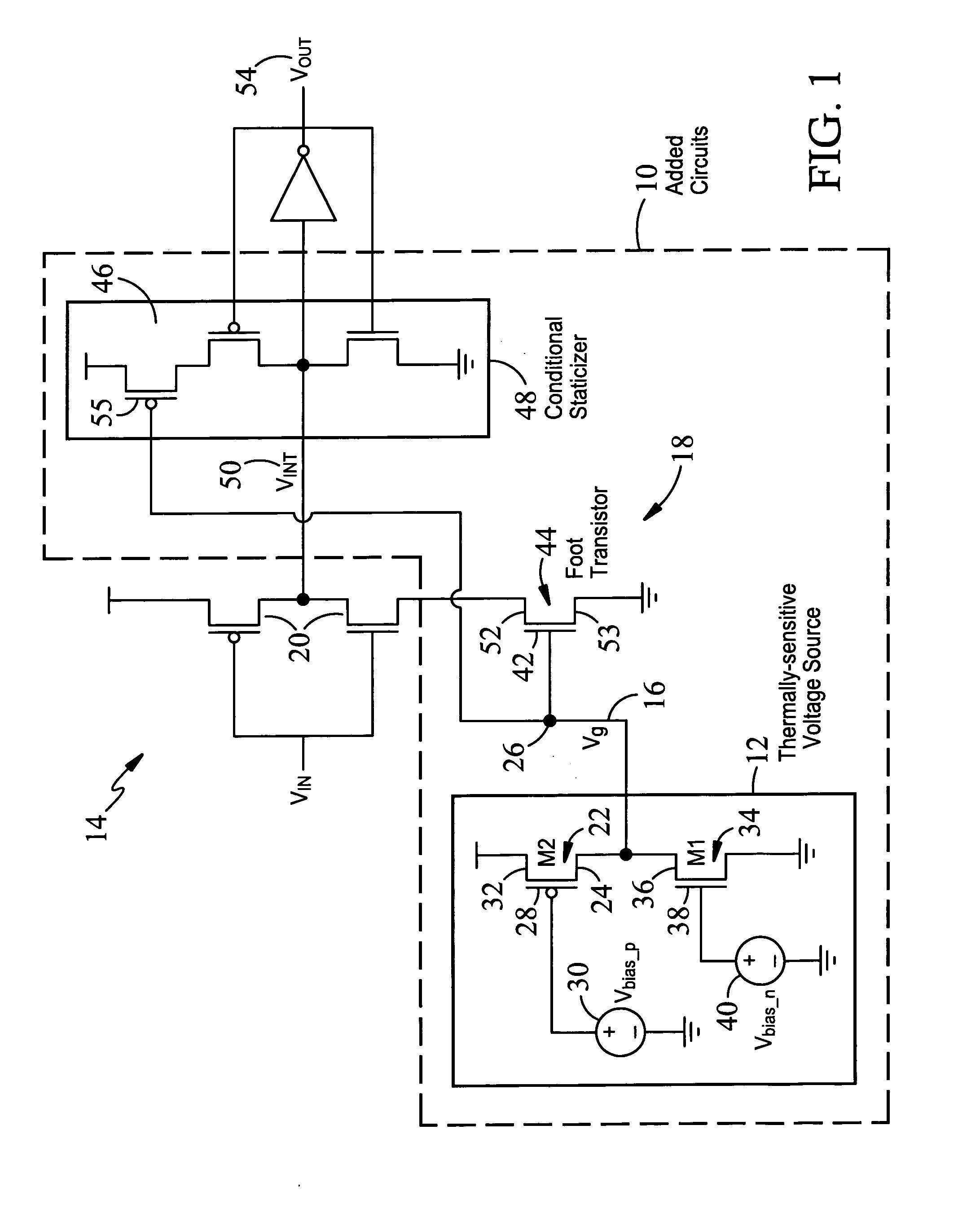

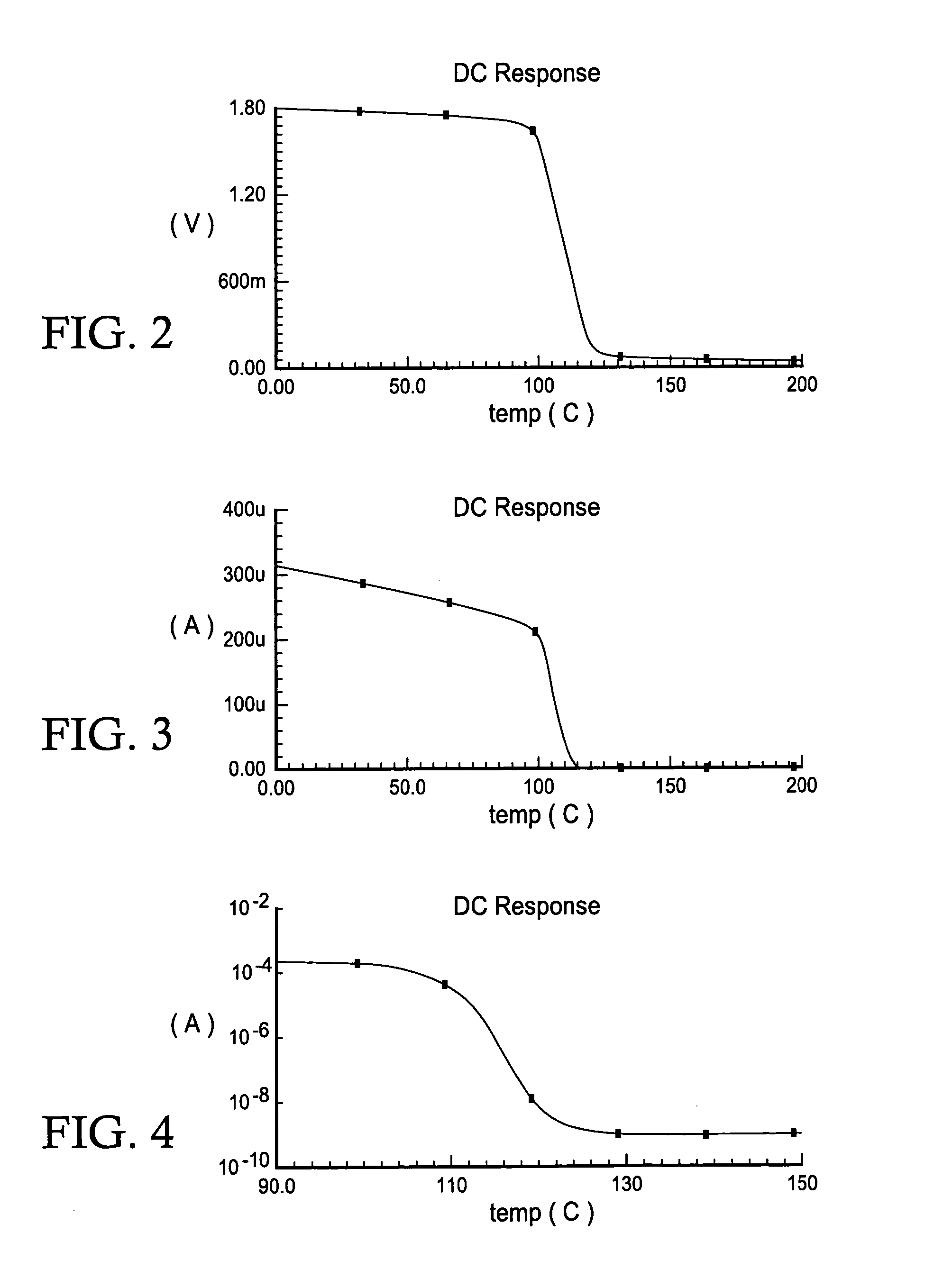

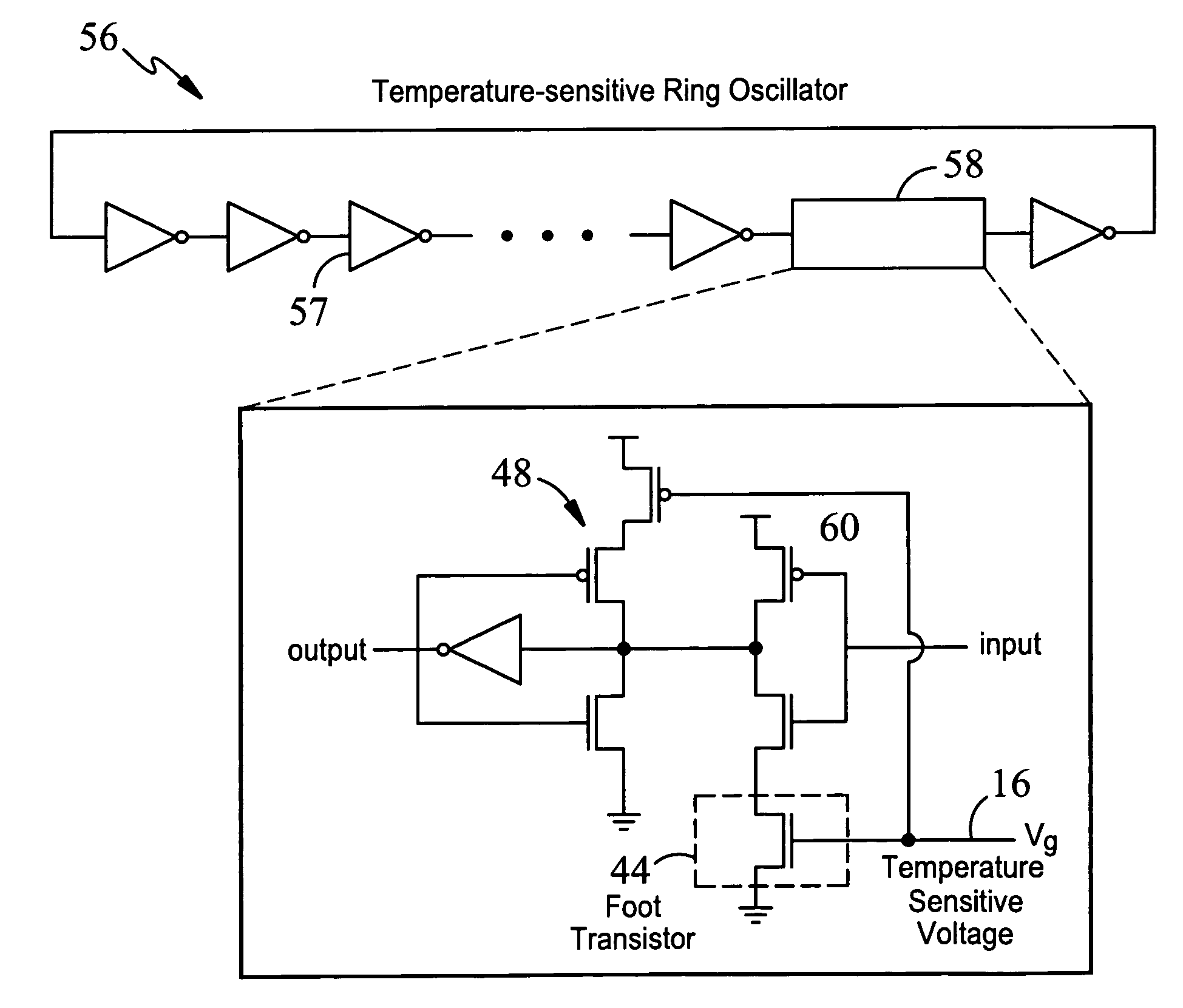

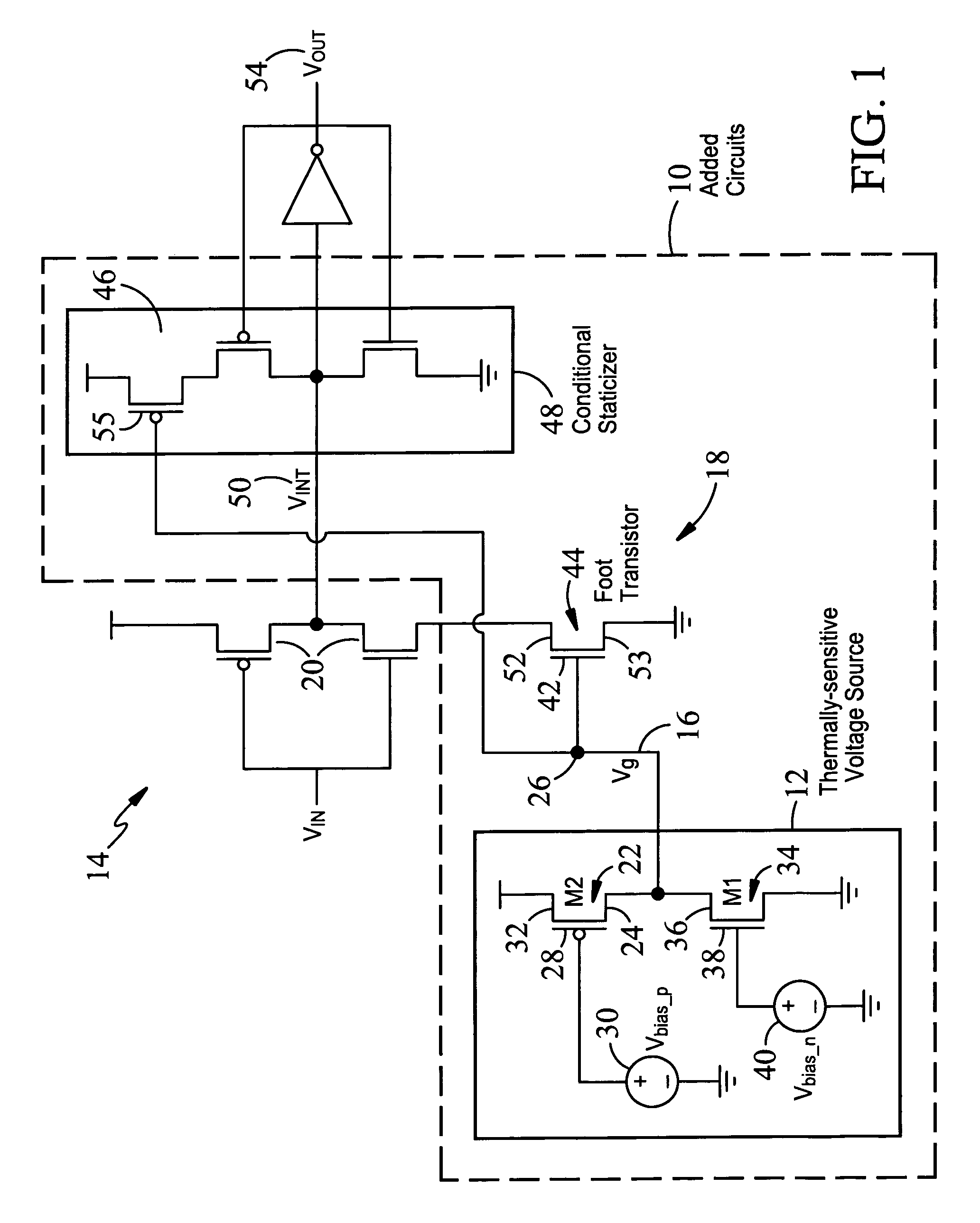

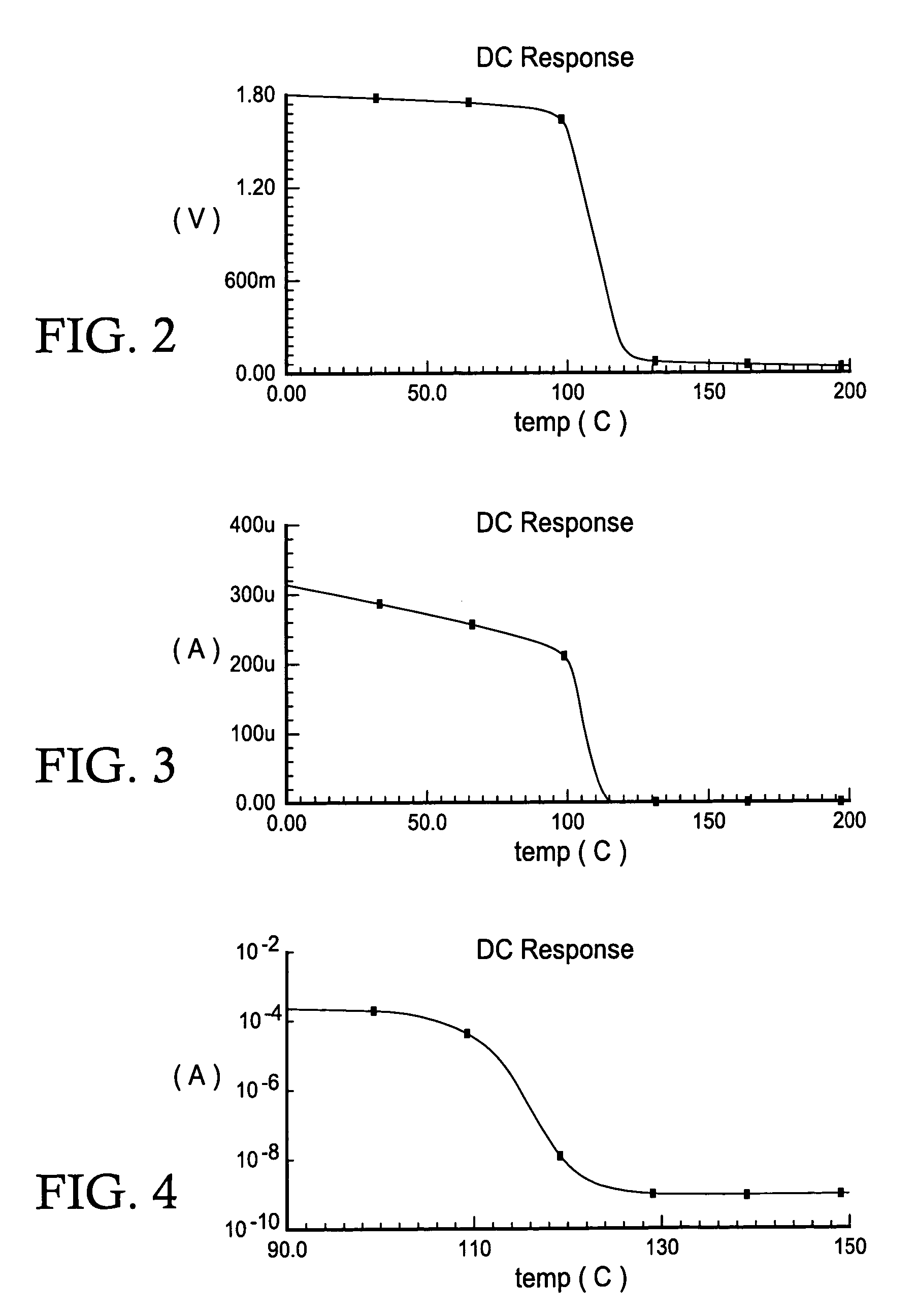

Self-timed thermally-aware circuits and methods of use thereof

InactiveUS20070200608A1Without imposing significant implementation overheadStall-free performance-throttlingElectronic switchingNetwork modifications to reduce temperatureVoltage sourceThreshold temperature

Apparatus and methods for regulating gate delays of synchronous and asynchronous digital circuits. Thermally-sensitive circuits include, generally, temperature sensitive voltage sources outputting a voltage signal indicative of the temperature of the digital circuit, where the voltage signal reflects non-linear temperature sensitivity above a predetermined threshold temperature, and delay mechanisms receiving said temperature sensitive voltage signal(s) as input and being configured to automatically continuously modulate the speed of signal propagation through the circuit in response to said voltage signal, thereby causing circuit elements within the circuits to switch less frequently and consequently causing the circuit elements to generate less heat with increasing circuit temperature.

Owner:CORNELL RES FOUNDATION INC

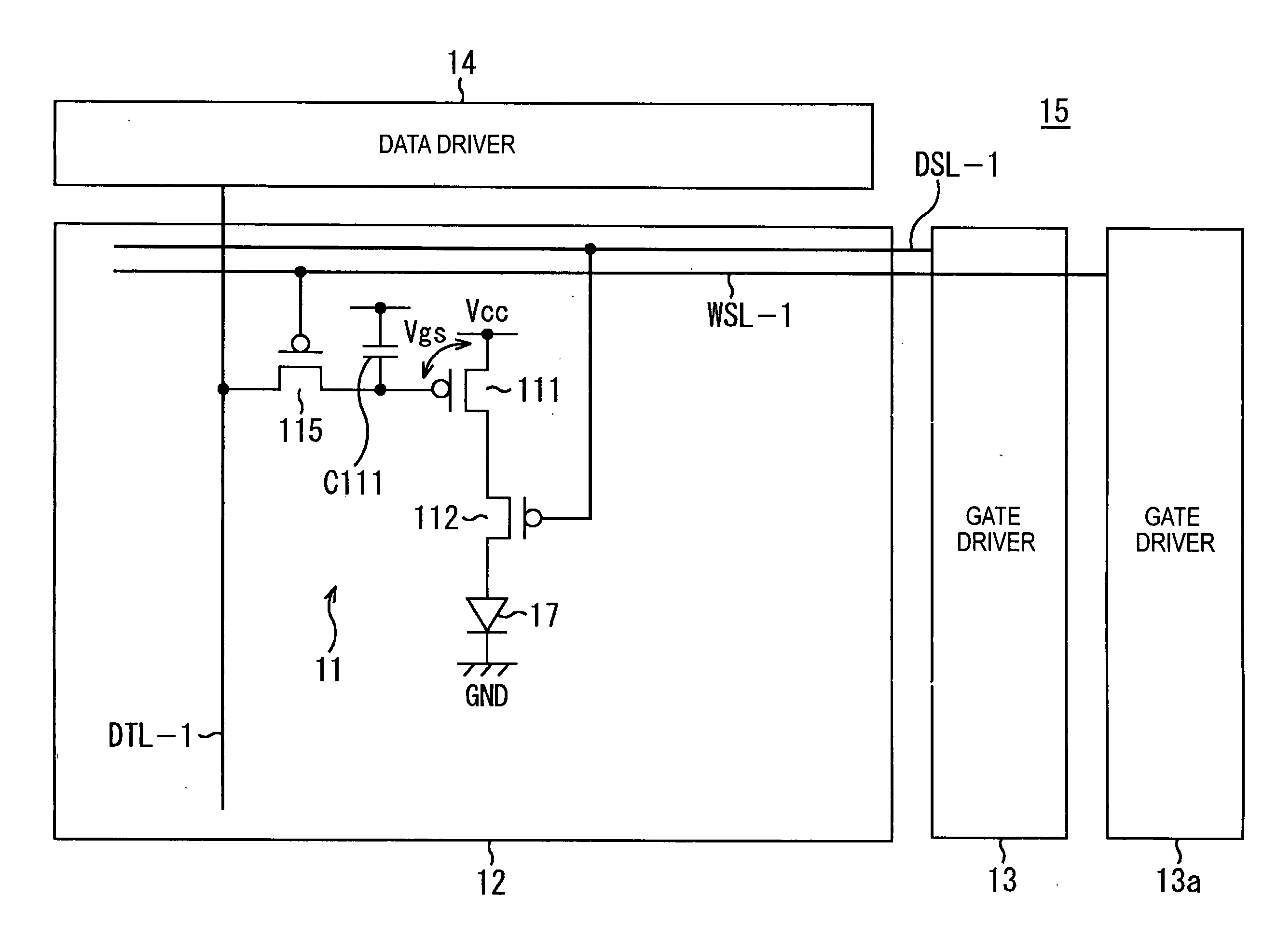

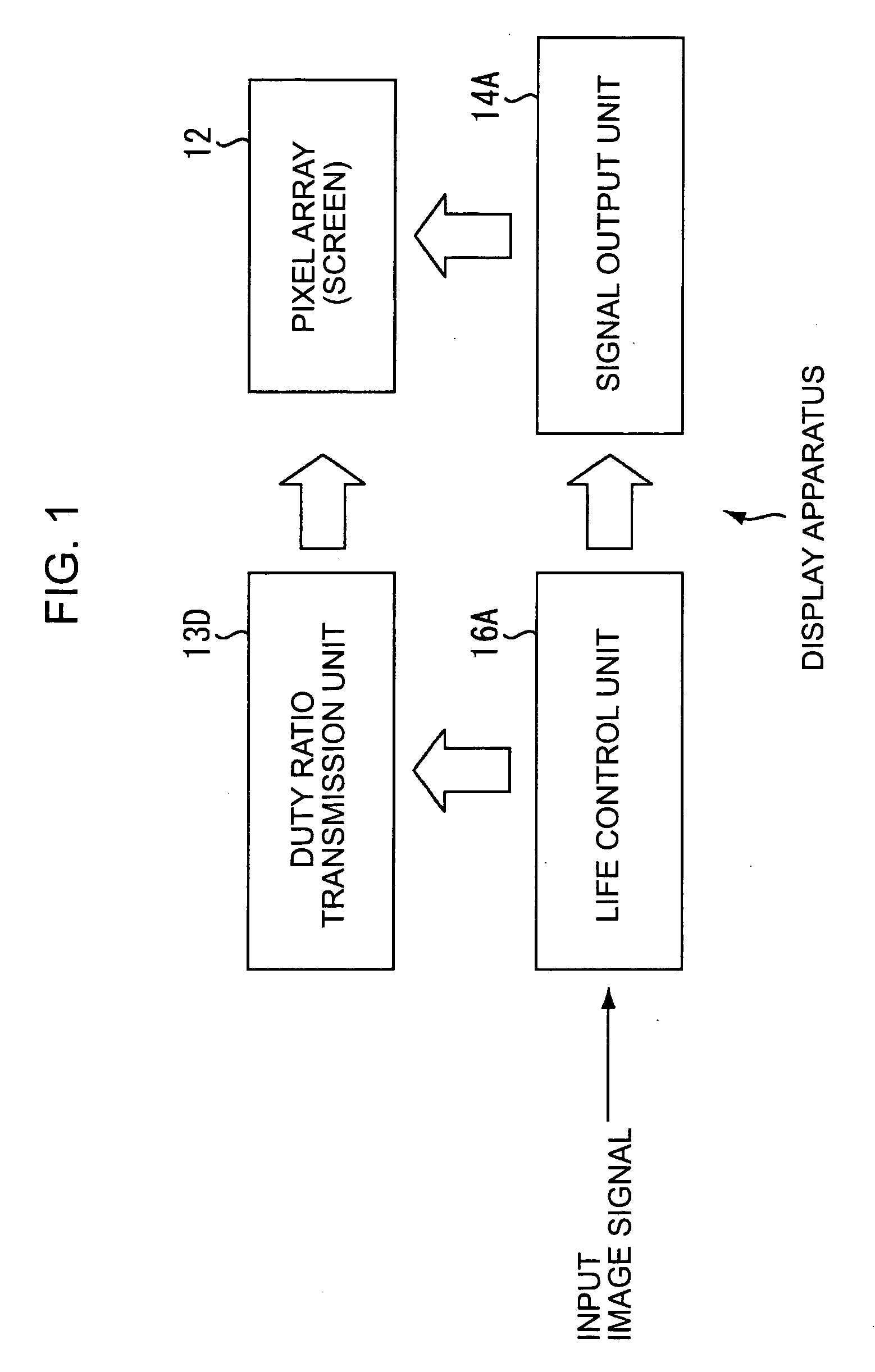

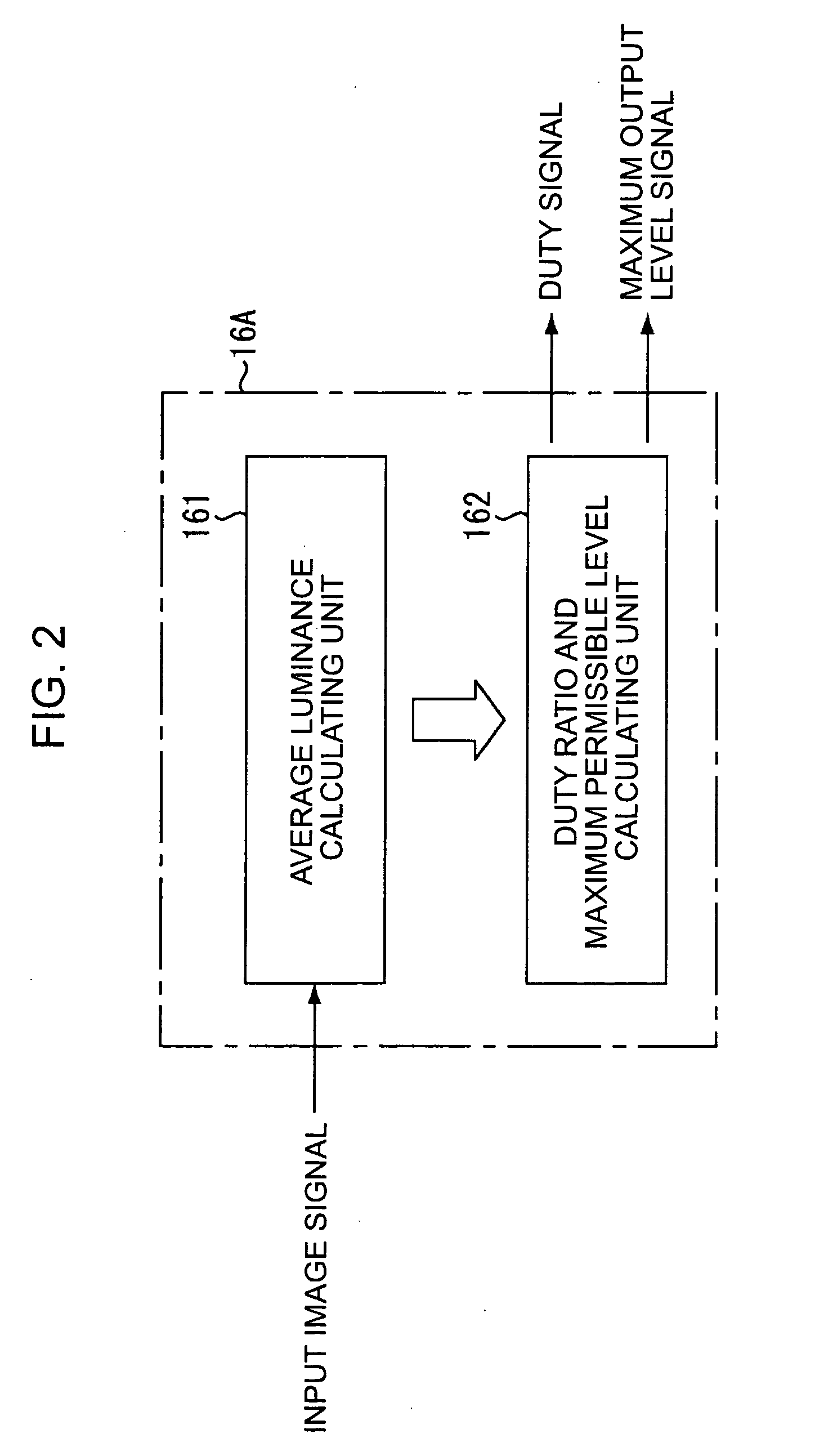

Display apparatus and driving method for the same

ActiveUS20060017394A1Prolong lifeSuppress amount of lightCathode-ray tube indicatorsInput/output processes for data processingEngineeringImage signal

A display apparatus includes a pixel array, a life control unit, a signal output unit, and a duty ratio transmission unit. The pixel array, including light-emitting elements constituting a screen, displays each frame of an image on the screen by emitting light having a luminance in accordance with a level of an image signal and continuously emits light from the screen within each frame for an amount of time specified by a duty ratio. The life control unit extends the life of the light-emitting elements by simultaneously adjusting the maximum permissible level of the image signal and the duty ratio. The signal output unit drives the screen to display an image by outputting an image signal adjusted within the maximum permissible level to the pixel array. The duty ratio transmission unit for enabling the screen to emit light for an amount of time specified transmitting an adjusted duty ratio to the pixel array.

Owner:JOLED INC

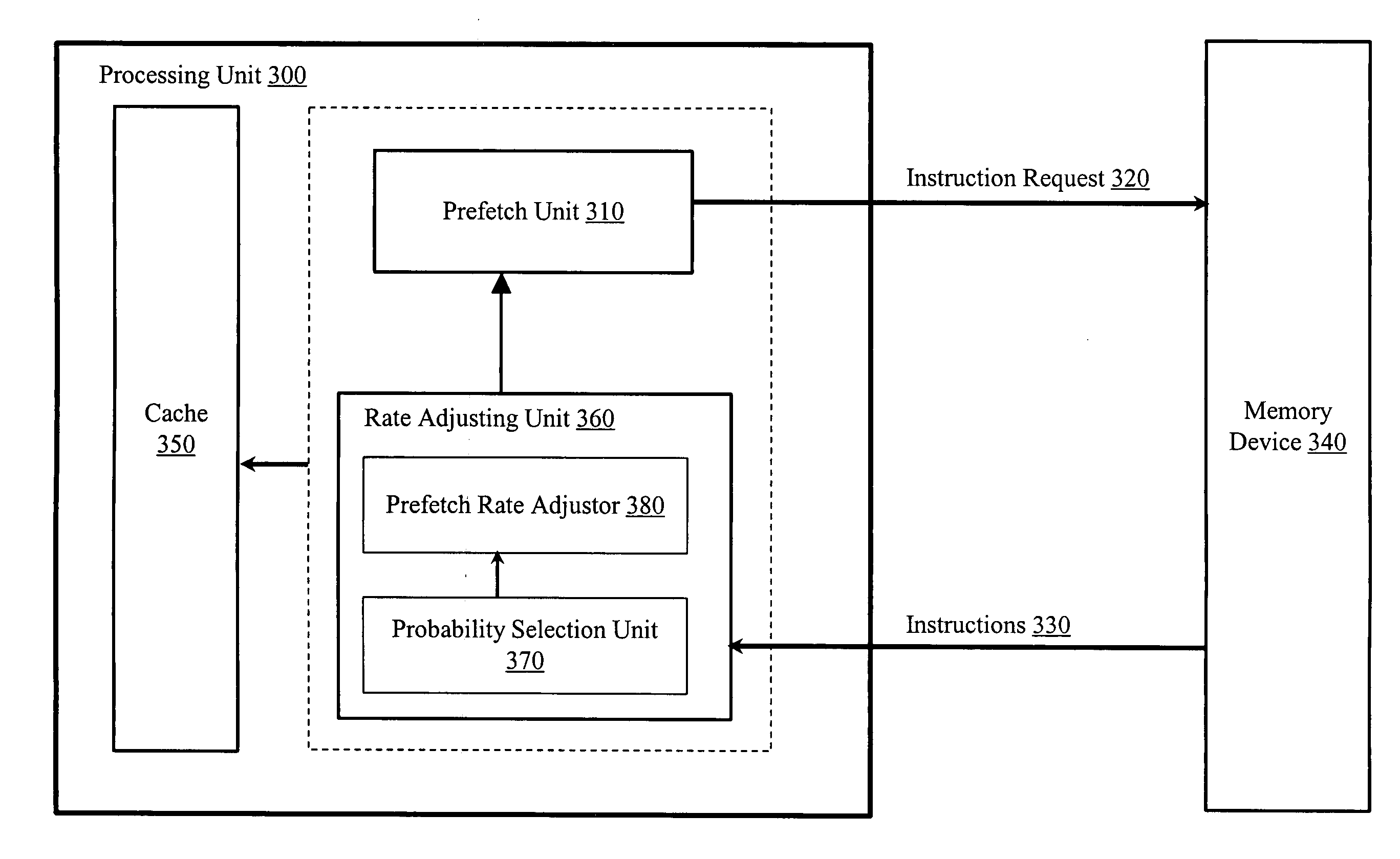

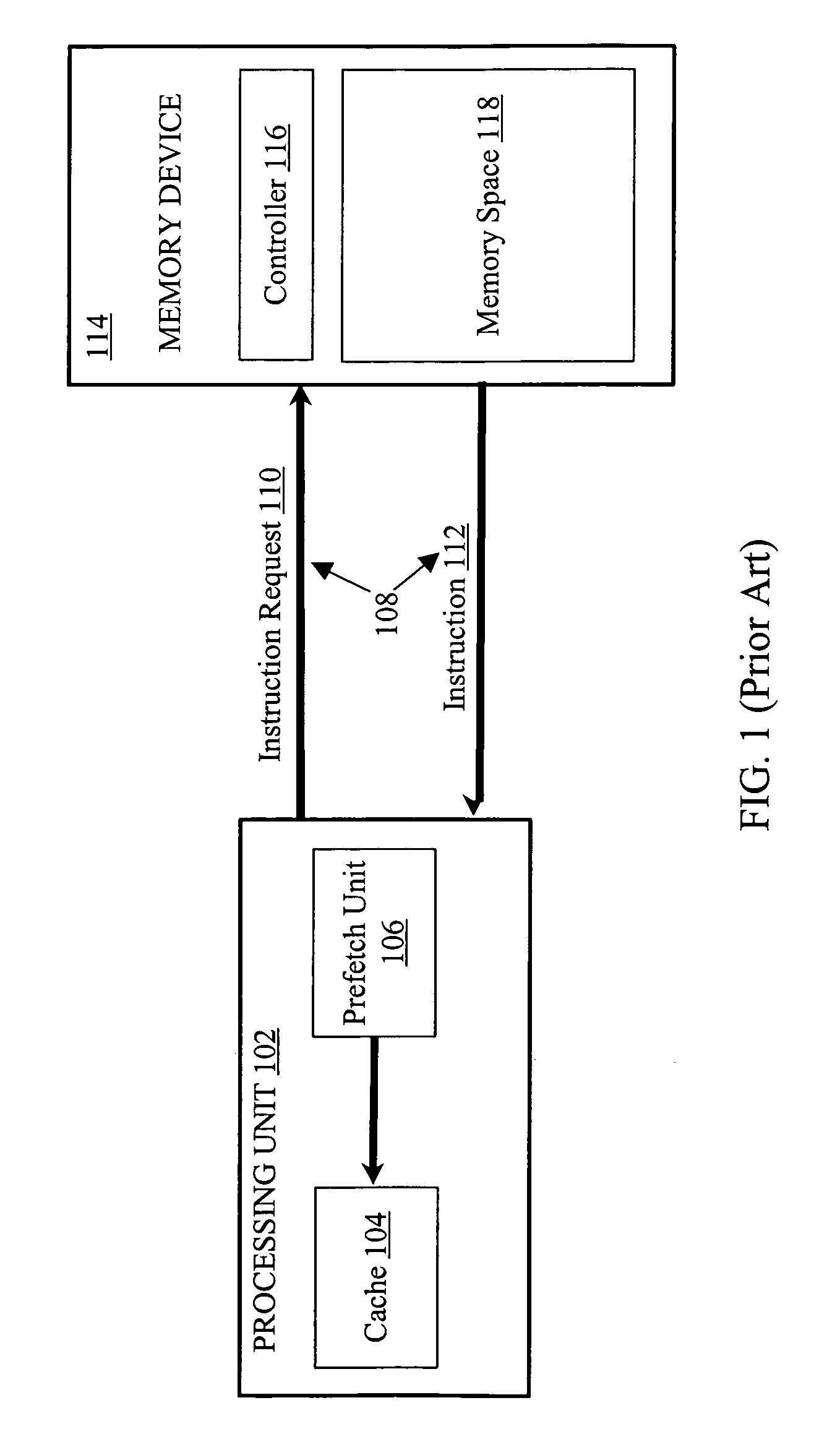

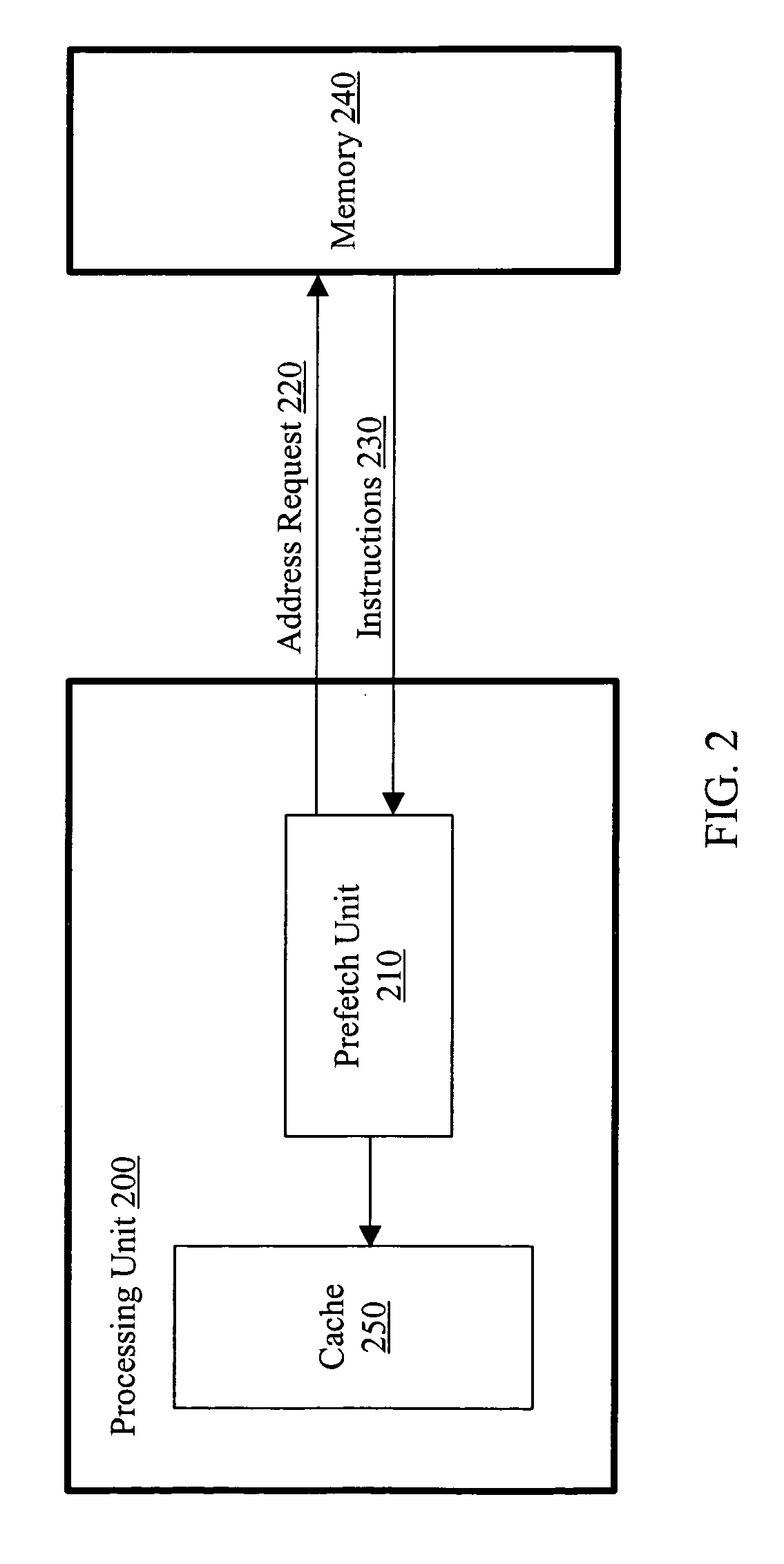

System, circuit, and method for adjusting the prefetch instruction rate of a prefetch unit

ActiveUS7103757B1Reduce in quantityEasy to processDigital computer detailsSpecific program execution arrangementsParallel computingPower consumption

A system, circuit, and method are presented for adjusting a prefetch rate of a prefetch unit from a first rate to a second rate by determining a probability factor associated with a branch instruction. The circuit and method may determine the probability factor based on a type of disparity associated with the branch instruction. The circuit and method may further be adapted to calculate the second rate based on the probability factor. The ability to adjust the prefetch rate of a prefetch unit advantageously decreases the number of memory transactions, thereby decreasing the power consumption of a processing unit.

Owner:VERISILICON HLDGCO LTD

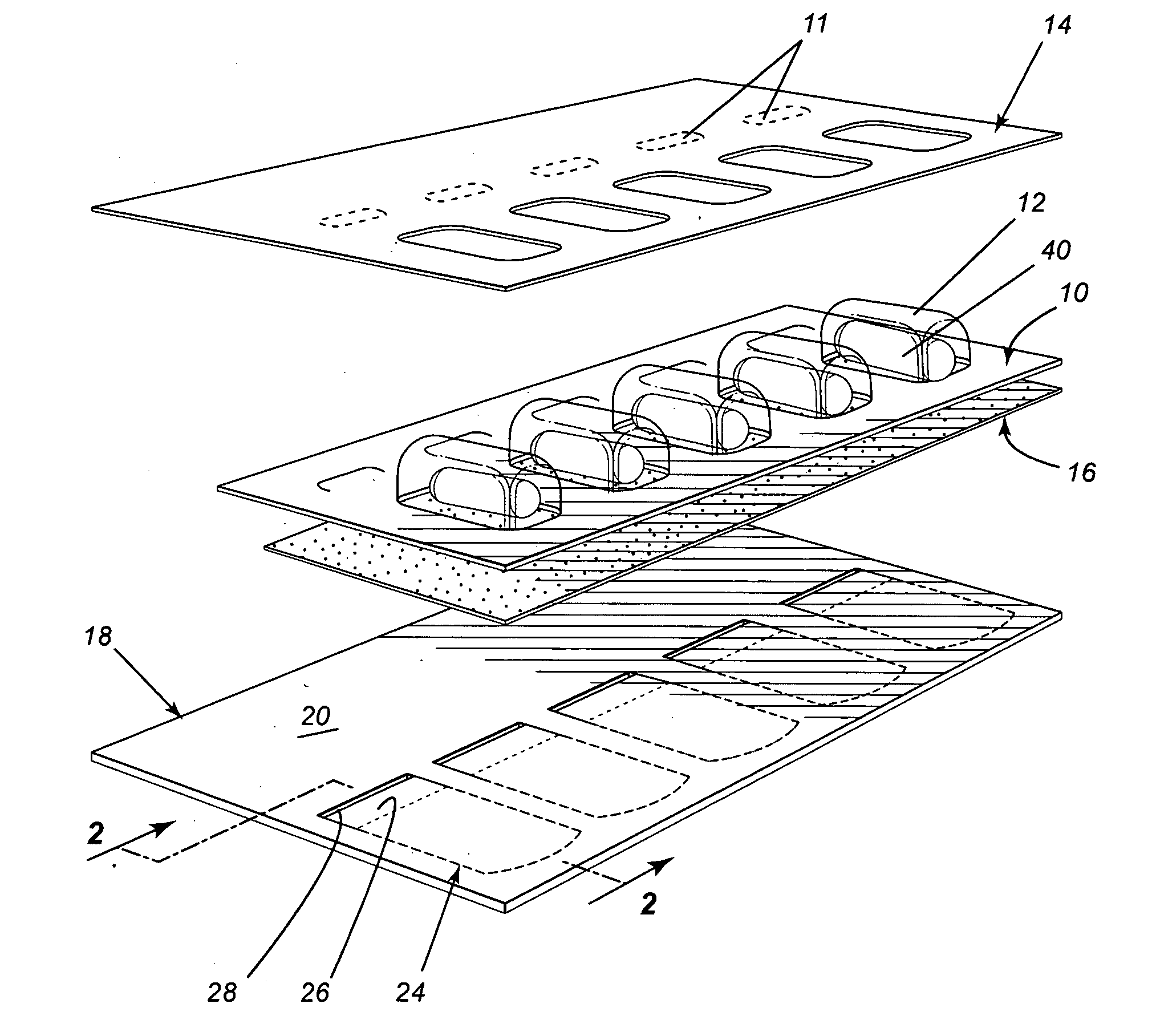

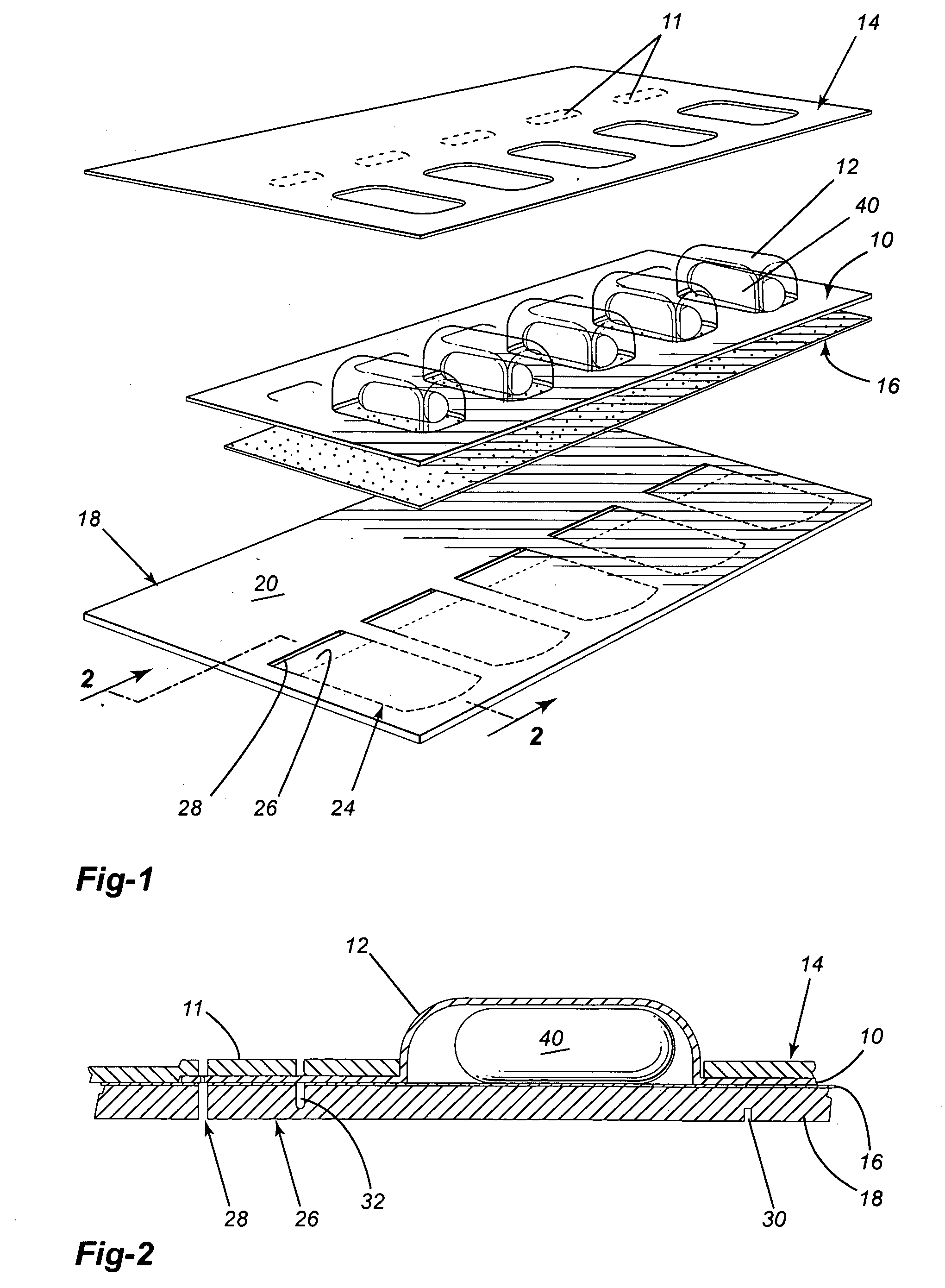

Push and peel pack for dispensing medicants

InactiveUS20070221534A1Additional circuitryEasy to manufactureSmall article dispensingPharmaceutical containersPaperboardEngineering

A push and peel child resistant and senior friendly tamper evident package comprising a blister sheet with U cuts for pushing an outer layer of interior tabs, the blister sheet having blister pockets projecting from a front side thereof, a rupturable foil layer being adhered to the blister layer and reinforcing the paperboard material adhered to the foil layer, an inner data layer with diecut oval holes, the paperboard layer having a tear strip formed therein, the tear strip being defined by a cut into the paperboard layer from the side thereof adhered to the foil layer, the cut extending only a certain percentage of the total thickness of the paperboard such that a controlled delamination of the paperboard layer occurs when the tear strip is removed. This provides a precise reinforcement of the foil layer.

Owner:INTINI THOMAS D

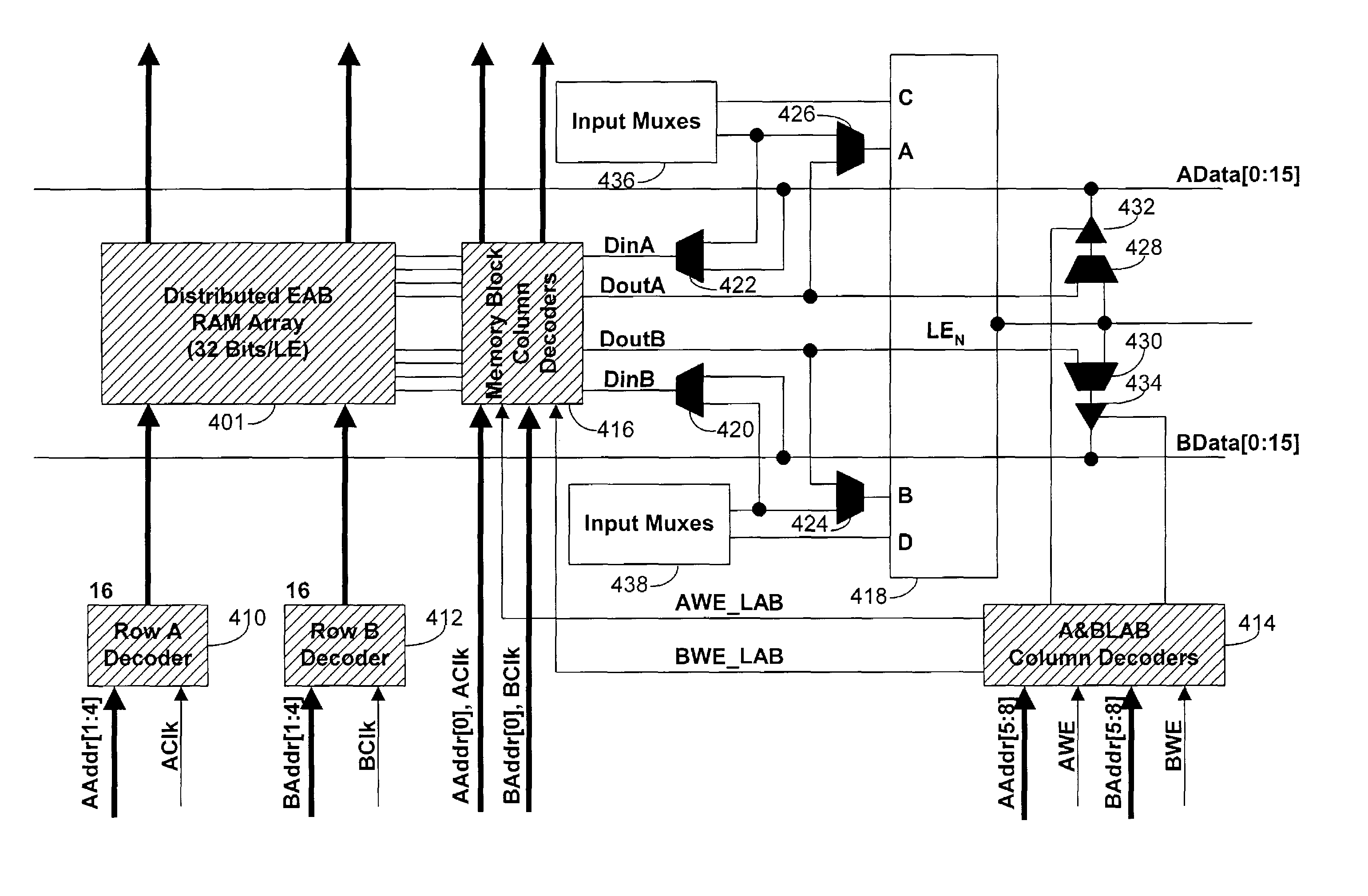

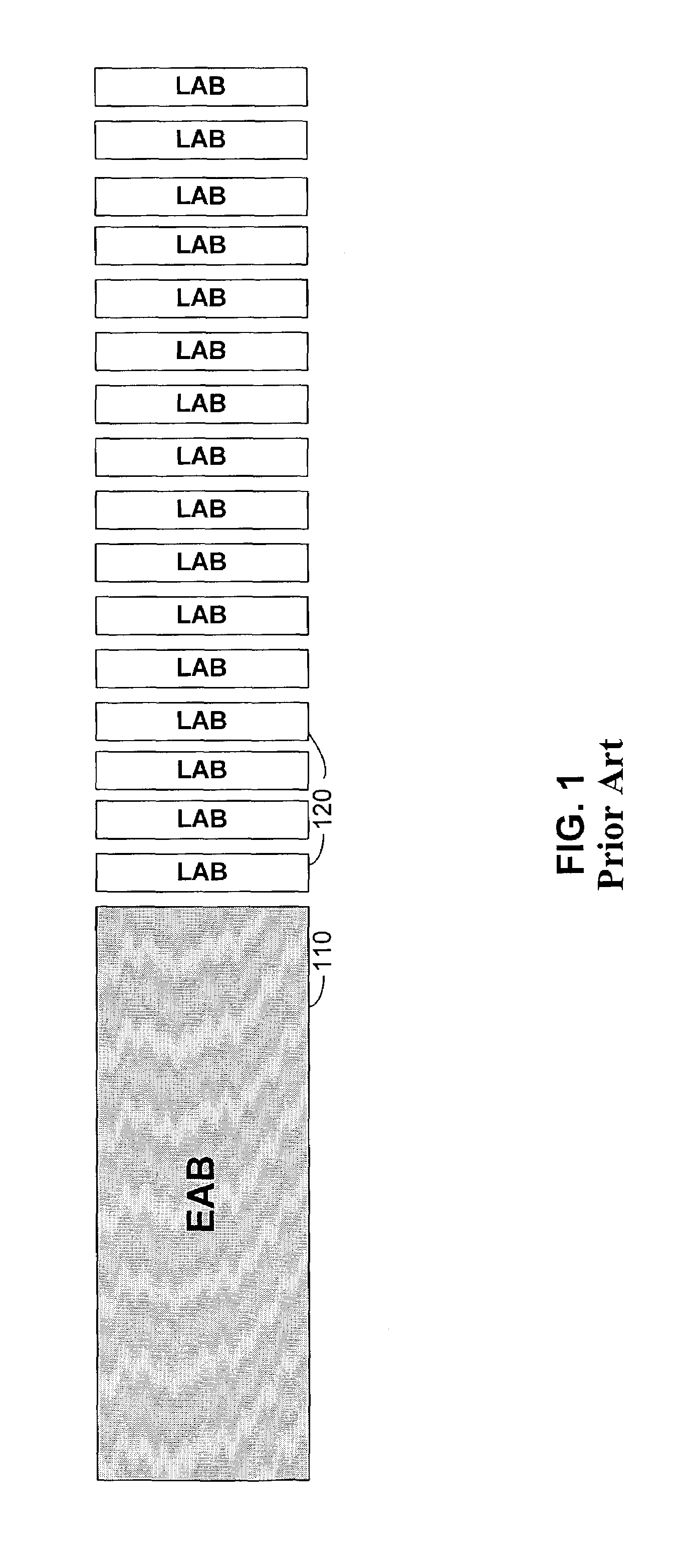

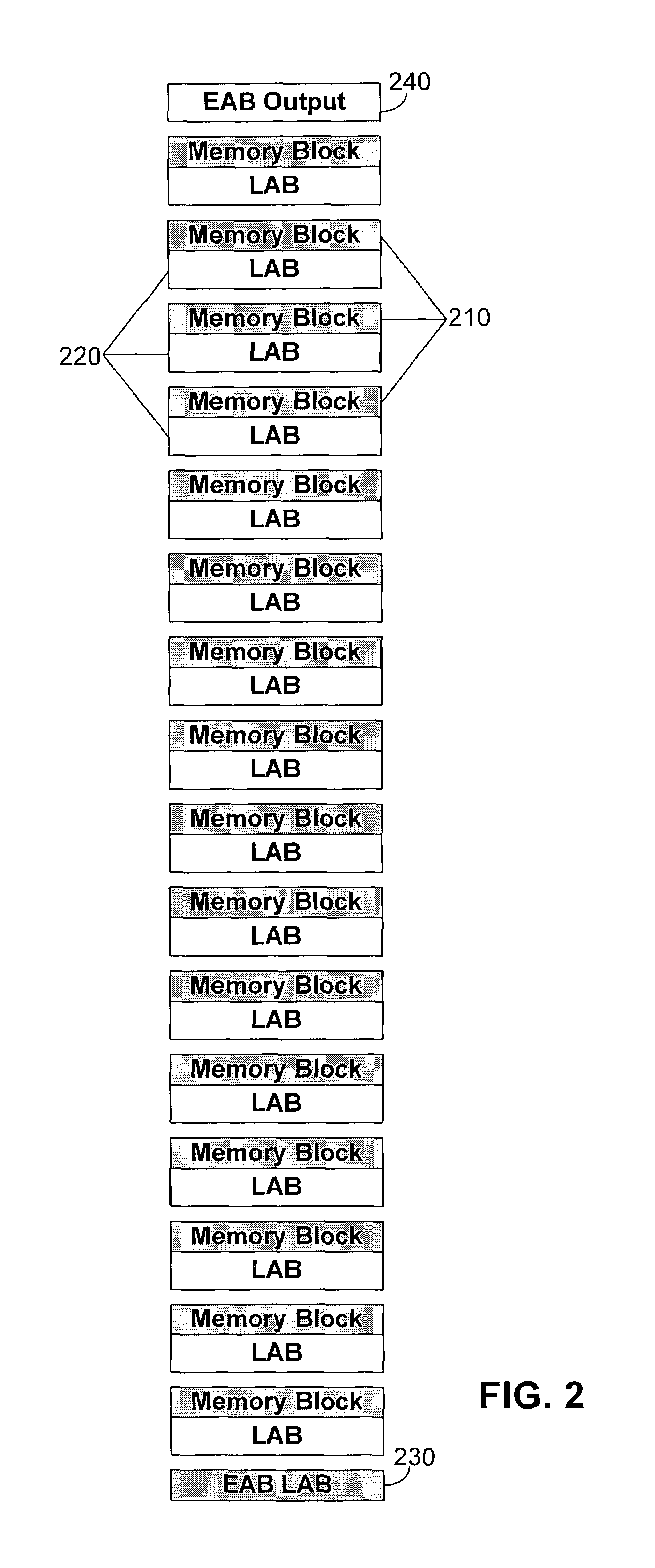

Versatile RAM for programmable logic device

InactiveUS7111110B1Reduce the amount requiredEfficiently enableData resettingDigital storageComputer architectureProgrammable logic device

Circuits and methods for providing versatile RAM for a programmable logic device are provided. These circuits and methods preferably allow signal lines that may be used to provide inputs for logic elements to be used instead for addressing memory blocks that form the versatile RAM.

Owner:ALTERA CORP

Self-timed thermally-aware circuits and methods of use thereof

InactiveUS7411436B2Without imposing significant implementation overheadStall-free performance-throttlingElectronic switchingNetwork modifications to reduce temperatureAsynchronous circuitEngineering

Apparatus and methods for regulating gate delays of synchronous and asynchronous digital circuits. Thermally-sensitive circuits include, generally, temperature sensitive voltage sources outputting a voltage signal indicative of the temperature of the digital circuit, where the voltage signal reflects non-linear temperature sensitivity above a predetermined threshold temperature, and delay mechanisms receiving said temperature sensitive voltage signal(s) as input and being configured to automatically continuously modulate the speed of signal propagation through the circuit in response to said voltage signal, thereby causing circuit elements within the circuits to switch less frequently and consequently causing the circuit elements to generate less heat with increasing circuit temperature.

Owner:CORNELL RES FOUNDATION INC

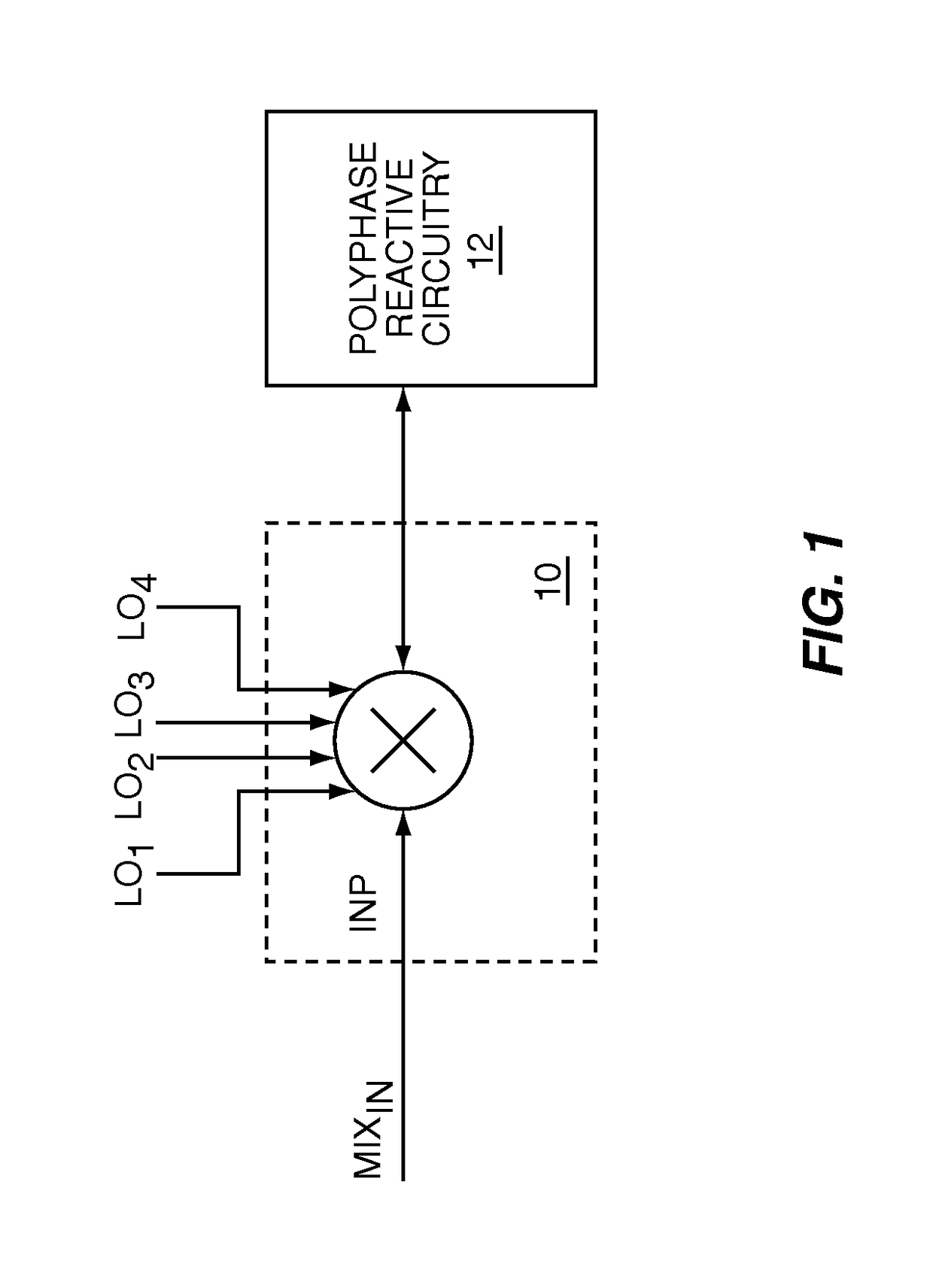

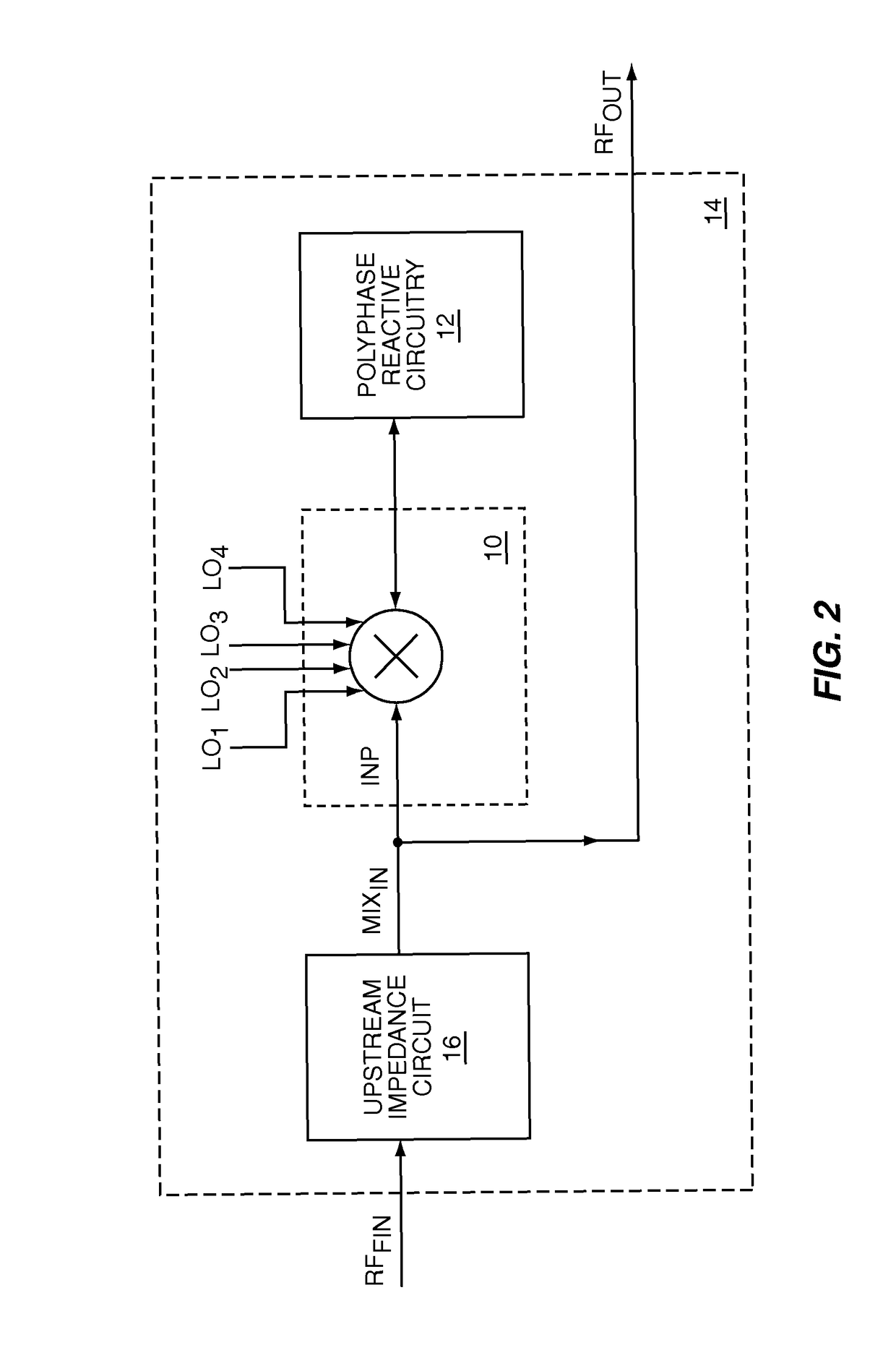

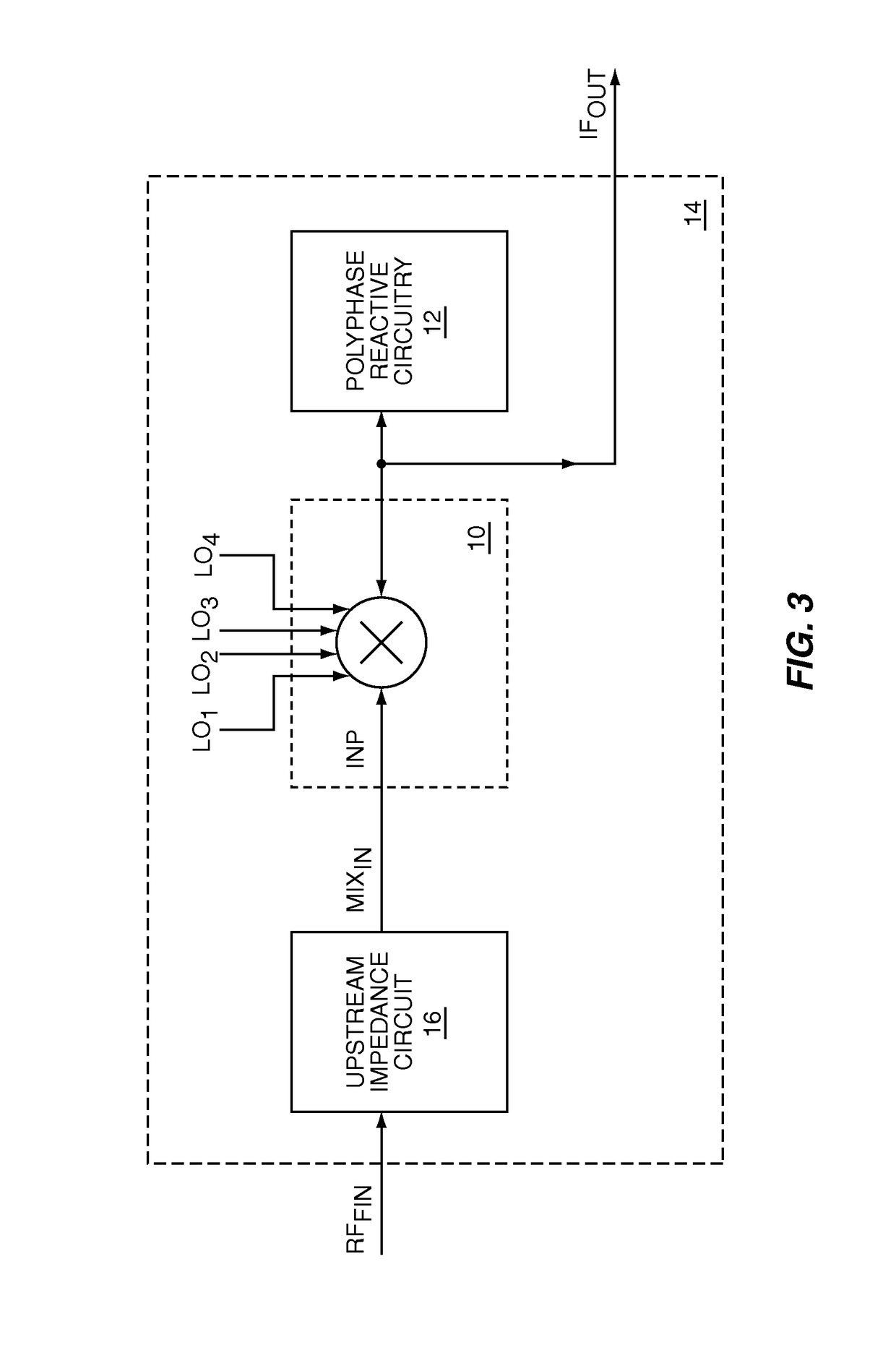

Controllable input impedance radio frequency mixer

ActiveUS8121577B1Improve receiver selectivityMaximize energy transferComputations using contact-making devicesSingle output arrangementsImpedance responseBandpass filtering

The present invention is a controllable input impedance RF mixer, which when fed from a high impedance source, such as a current source, provides a high quality factor (Q) impedance response associated with an impedance peak. The high-Q impedance response may be used as a high-Q RF bandpass filter in a receive path upstream of down conversion, which may improve receiver selectivity and replace surface acoustic wave (SAW) or other RF filters. The present invention uses polyphase reactive circuitry, such as capacitive elements, coupled to the down conversion outputs of an RF mixer. The RF mixer mixes RF input signals with local oscillator signals to translate the impedance of the polyphase reactive circuitry into the RF input impedance of the RF mixer. The RF input impedance includes at least one impedance peak. The local oscillator signals are non-overlapping to maximize the energy transferred to the polyphase reactive circuitry.

Owner:QORVO US INC

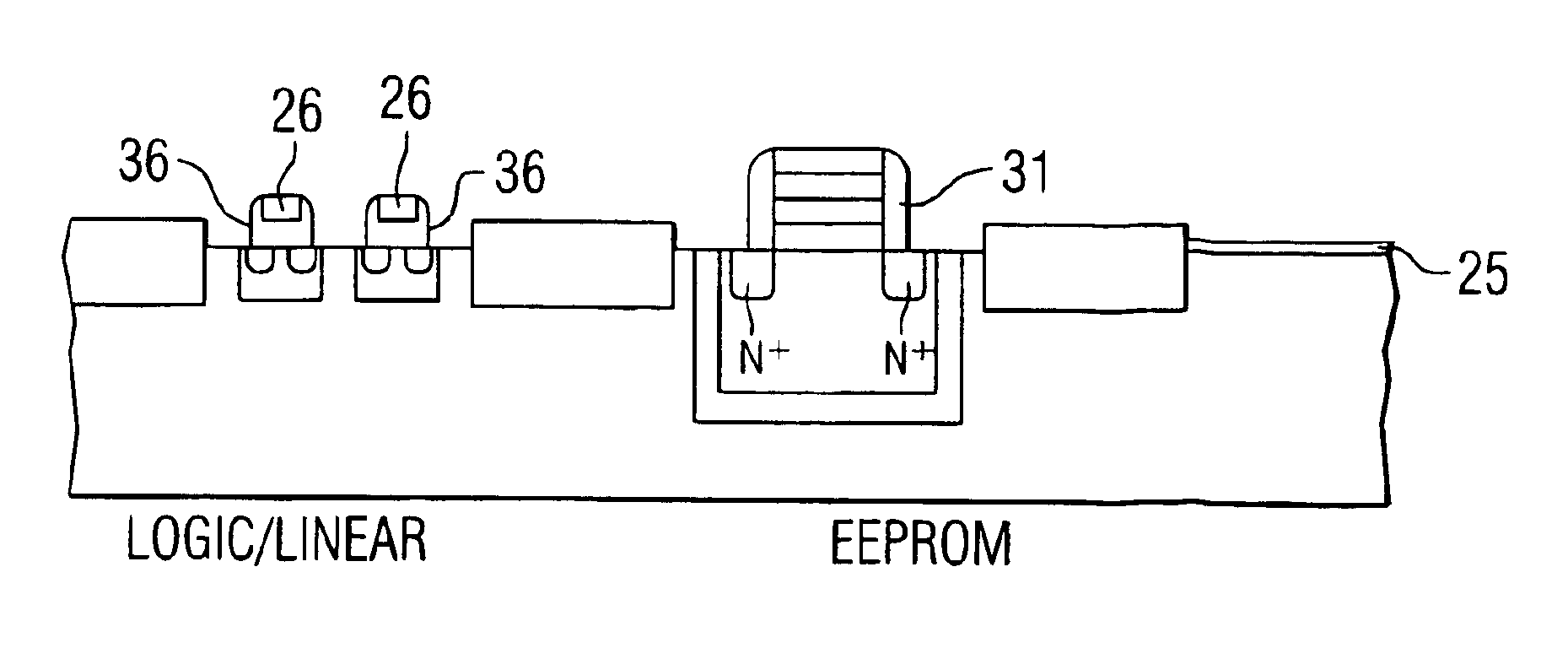

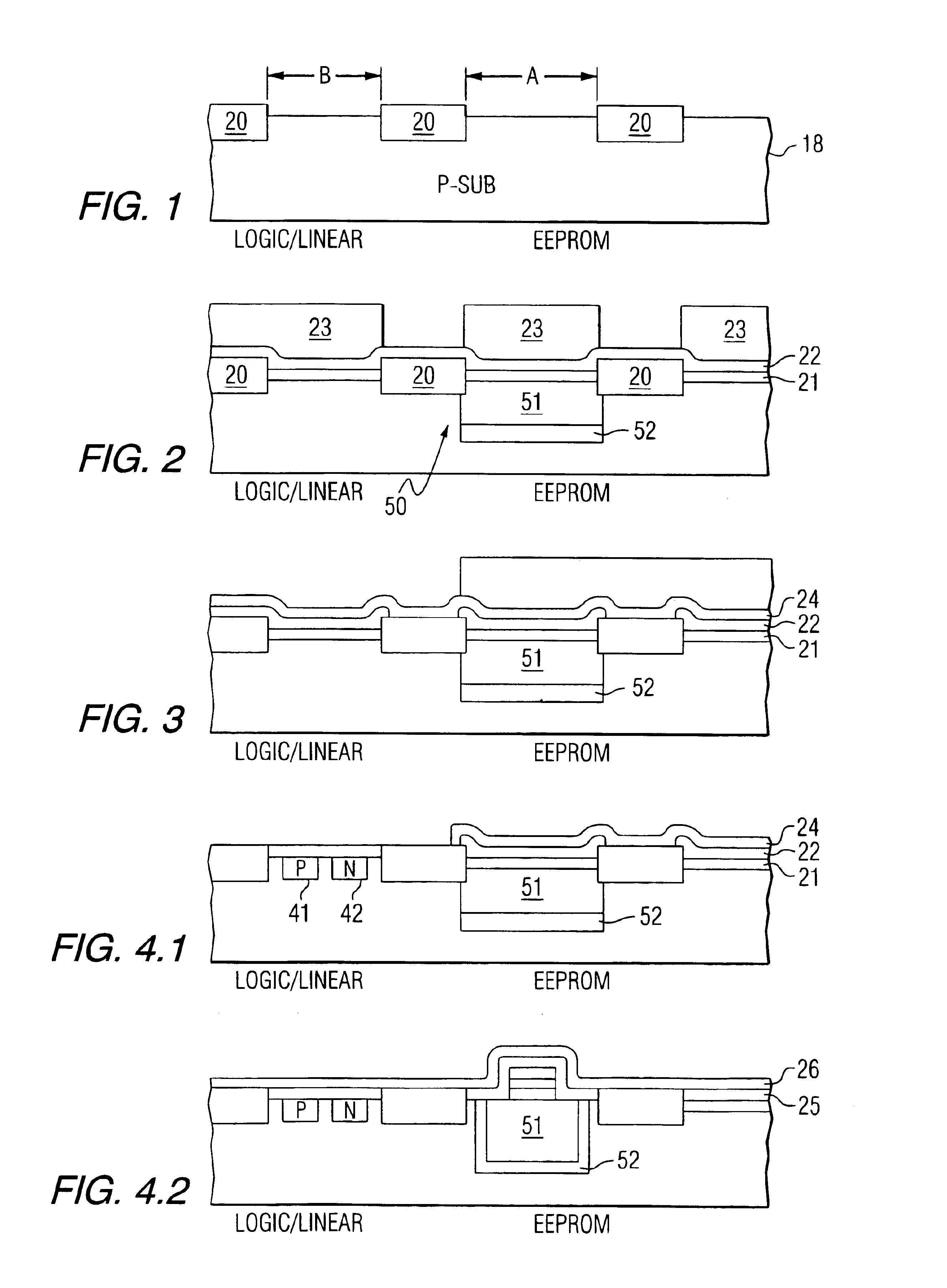

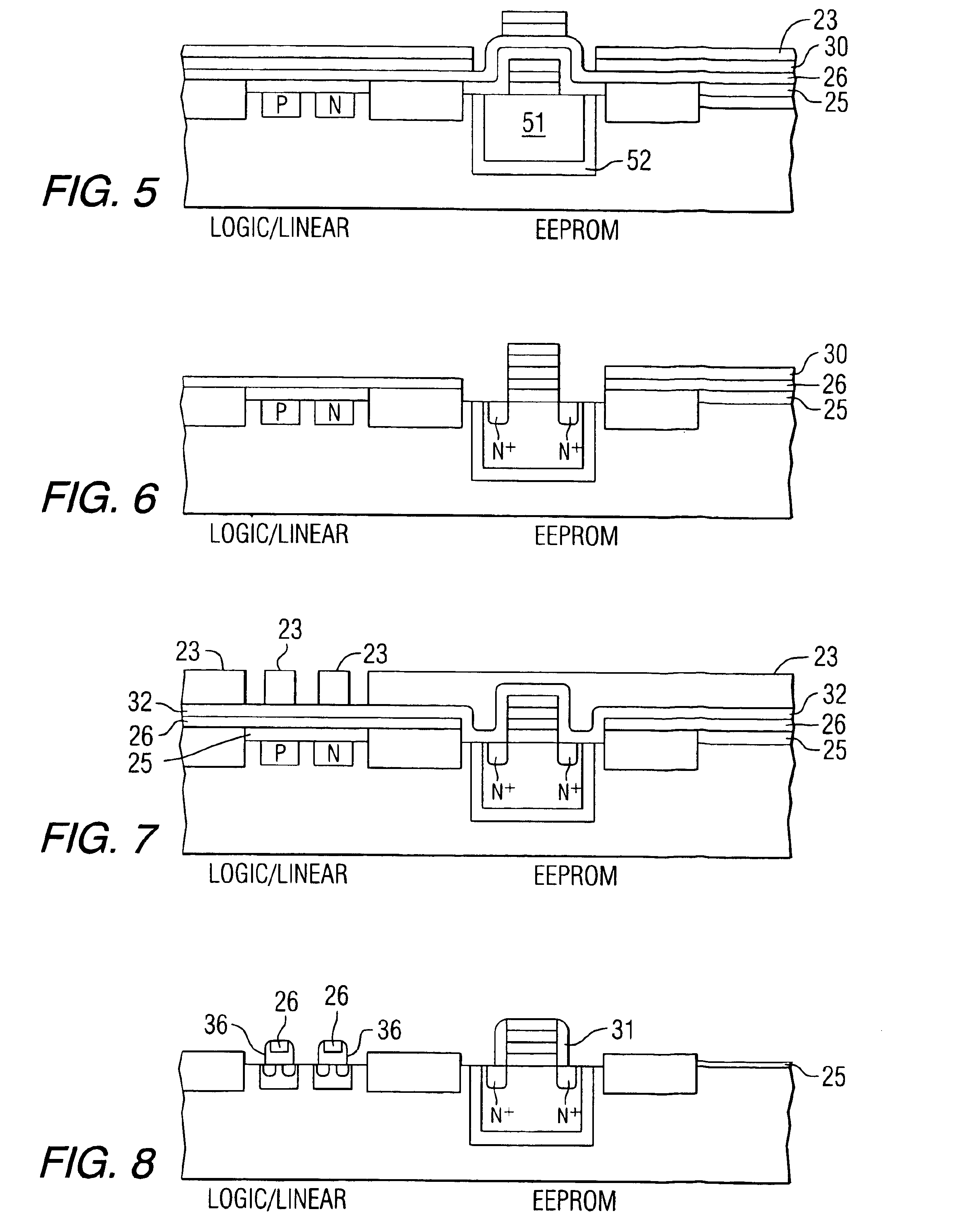

Flash memory cell and the method of making separate sidewall oxidation

InactiveUS6841824B2Avoid spendingIncreasing the thicknessTransistorSolid-state devicesElectrical conductorLinear region

A process and product for making integrated circuits with dense logic and / or linear regions and dense memory regions is disclosed. On a common substrate, a dual hard mask process separately forms stacks of logic and / or linear transistors and EEPROM memory transistors. By using the process, the logic and / or linear and memory transistors are made with different sidewall insulating layers. The logic and / or linear transistors have relatively thin sidewall insulating layers sufficient to provide isolation from adjacent devices and conductors. The memory transistors have thicker sidewall insulating layer to prevent the charge stored in the memory device from adversely influencing the operation of the memory transistor.

Owner:INFINEON TECH AG

Method and apparatus for designing and manufacturing electronic circuits subject to leakage problems caused by temperature variations and/or ageing

ActiveUS20060253204A1The degree of freedom becomes largerReduce design marginComputer controlCAD circuit designSystem requirementsTrade offs

First several possible working points are stored with different mappings to available modules. Each of these working points involves different trade-offs for important criteria related to performance and costs. At the design stage, these trade-off points for the criteria are not calibrated to the actual run-time conditions. Subsequently, based on actual values of the leakage criteria caused by temperature variations and / or ageing at given run-time conditions for (a subset of) the working points, it is possible to calibrate the trade-off curves and use a run-time controller to select the most suited working points afterward for an actual circuit. These active working points are selected to just meet the necessary system requirements on performance, while minimizing any of the important cost parameters.

Owner:INTERUNIVERSITAIR MICRO ELECTRONICS CENT (IMEC VZW)

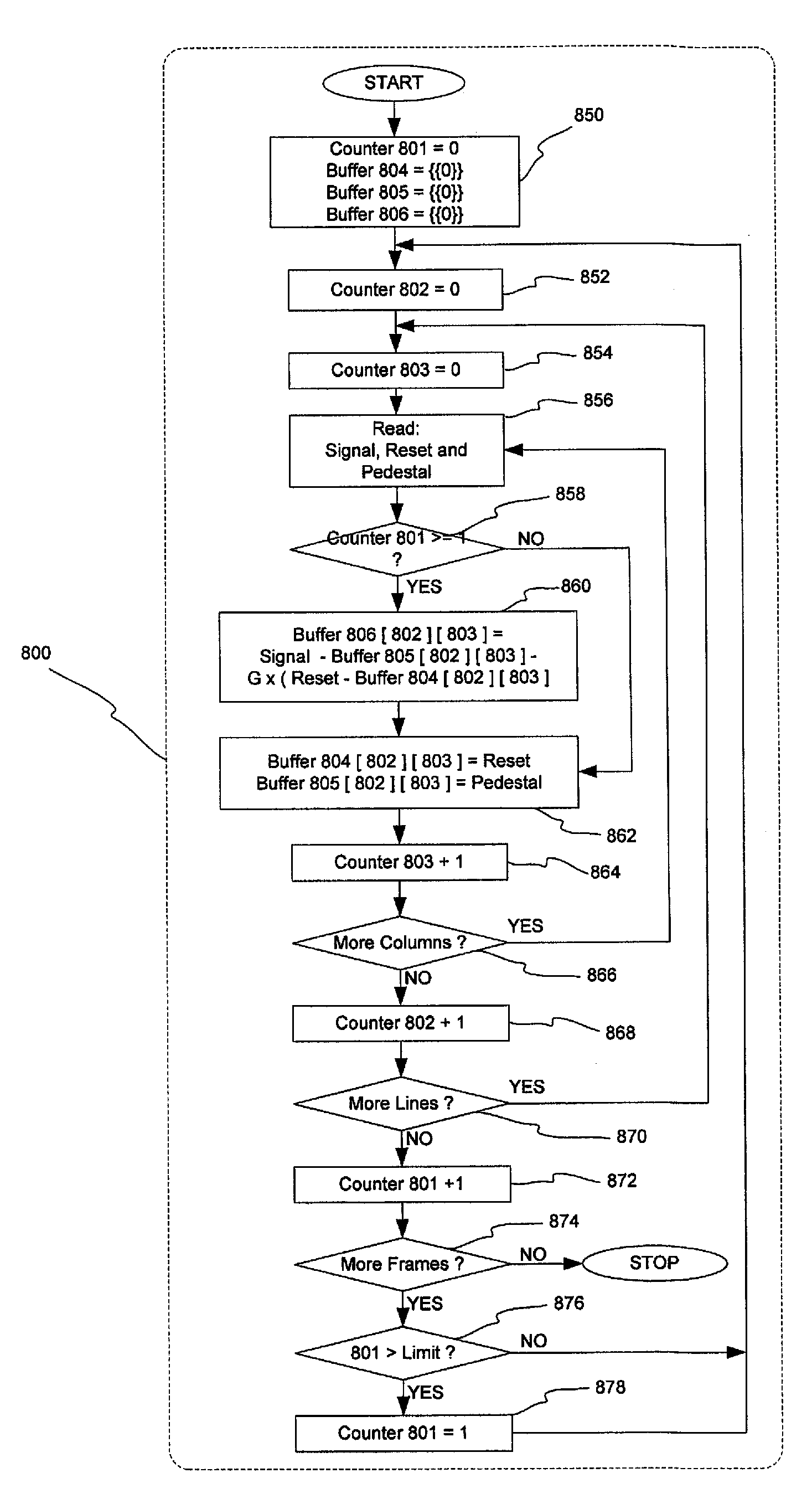

Ultra low noise CMOS imager

ActiveUS20080218620A1Lower noiseImprove performanceTelevision system detailsTelevision system scanning detailsEngineeringLow noise

A column buffer for use with a pixel cell array includes an amplifier coupled to three read-out circuits in parallel providing a signal corresponding to accumulated photon-generated charge in a pixel cell plus noise, a reset level plus noise, and a pedestal level, respectively. These three signals are used to generate an ultra-low noise signal Di=Si−Pi−G*(Ri−Ri-1), wherein S is the sampled signal, P is the pedestal level, R is the reset level, and G is a gain associated with a pixel cell, and wherein i is a frame number greater than 0. The three signals can be read-out simultaneously. In another embodiment, the three signals are obtained from a column buffer having only one output. In this case, the signals are read-out sequentially.

Owner:IMAGERLABS

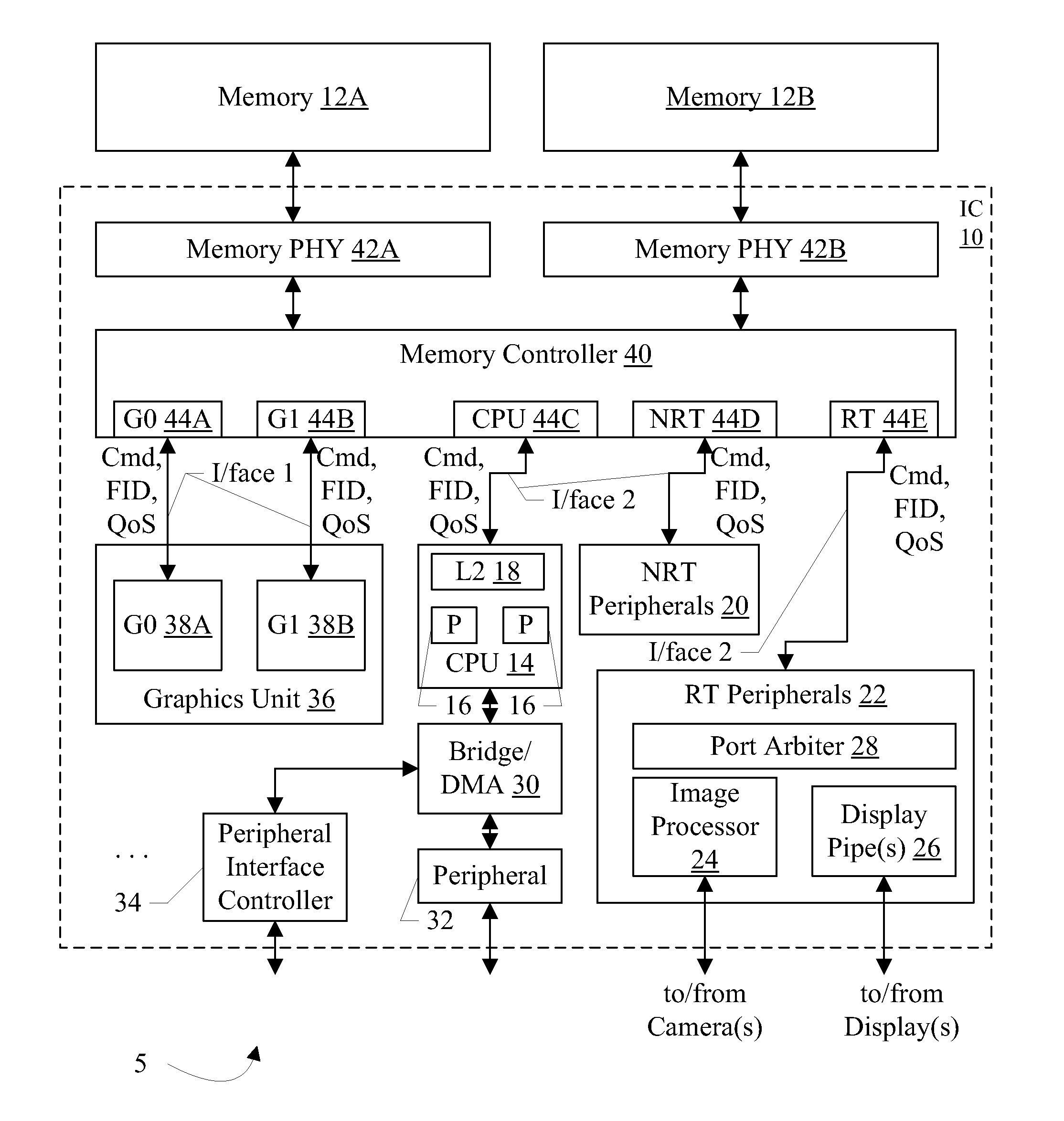

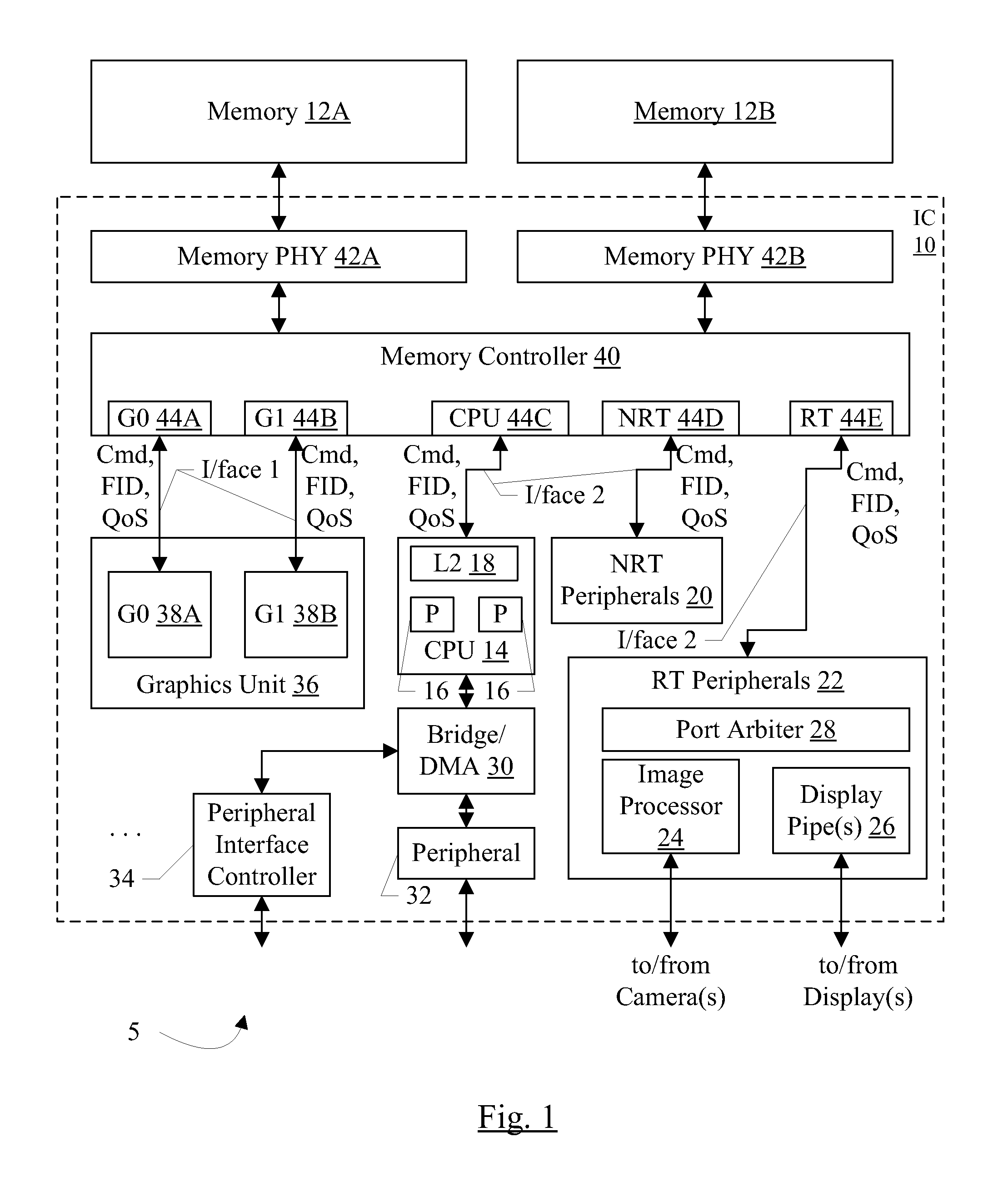

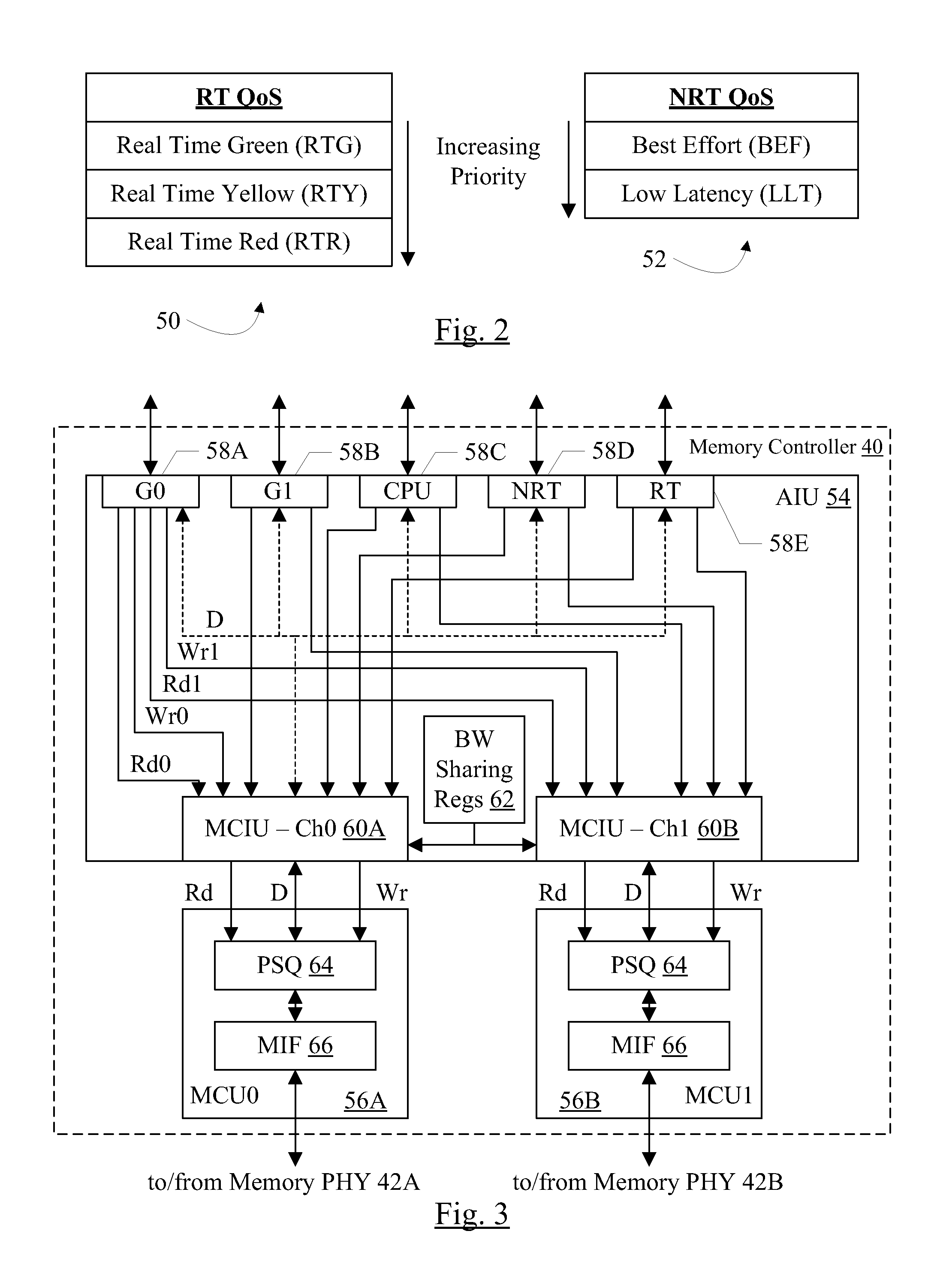

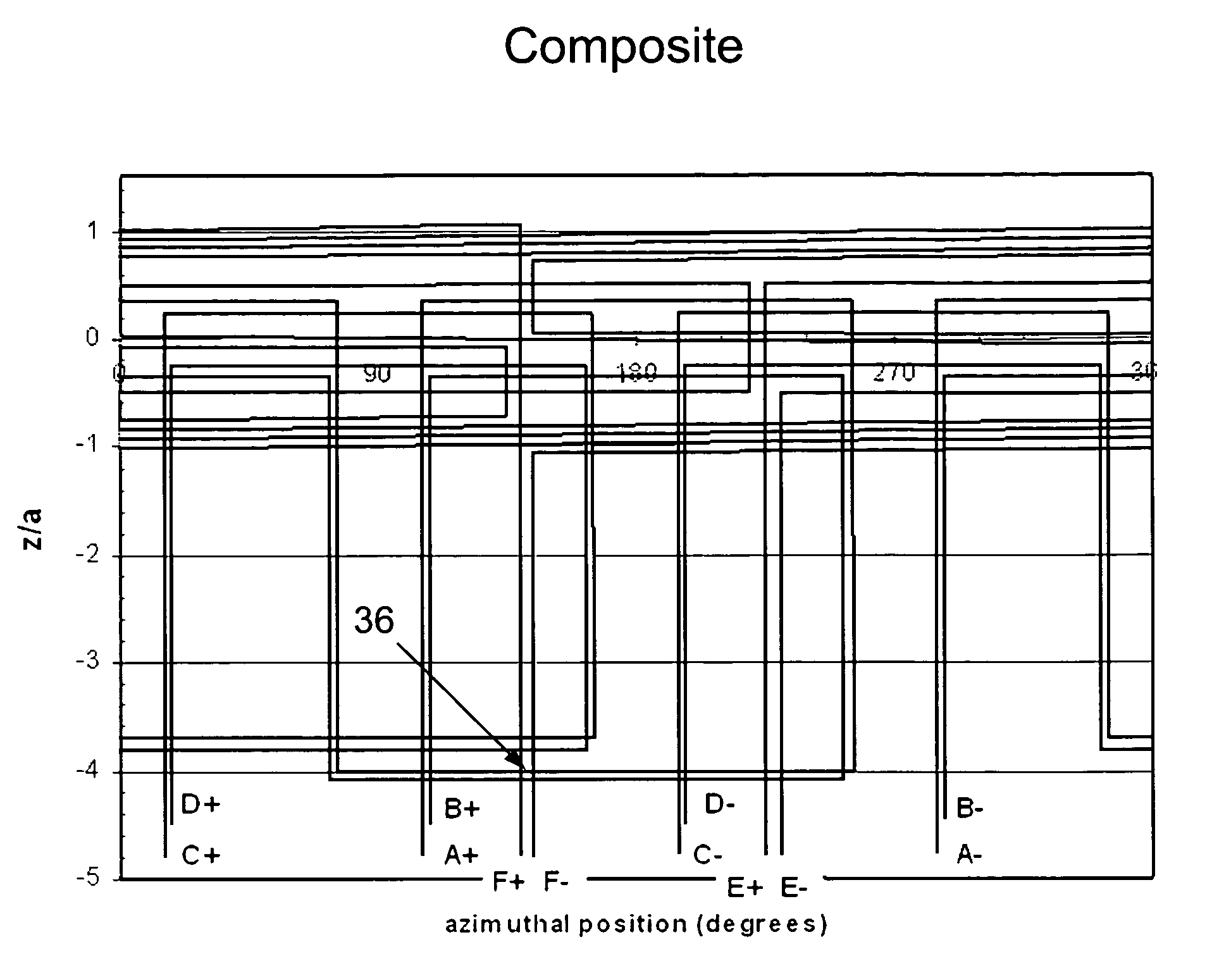

Multi-Ported Memory Controller with Ports Associated with Traffic Classes

InactiveUS20120072677A1Intelligent decisionSystems may be simplified and less costlyMemory systemsTraffic capacityMemory controller

In an embodiment, a memory controller includes multiple ports. Each port may be dedicated to a different type of traffic. In an embodiment, quality of service (QoS) parameters may be defined for the traffic types, and different traffic types may have different QoS parameter definitions. The memory controller may be configured to scheduled operations received on the different ports based on the QoS parameters. In an embodiment, the memory controller may support upgrade of the QoS parameters when subsequent operations are received that have higher QoS parameters, via sideband request, and / or via aging of operations. In an embodiment, the memory controller is configured to reduce emphasis on QoS parameters and increase emphasis on memory bandwidth optimization as operations flow through the memory controller pipeline.

Owner:APPLE INC

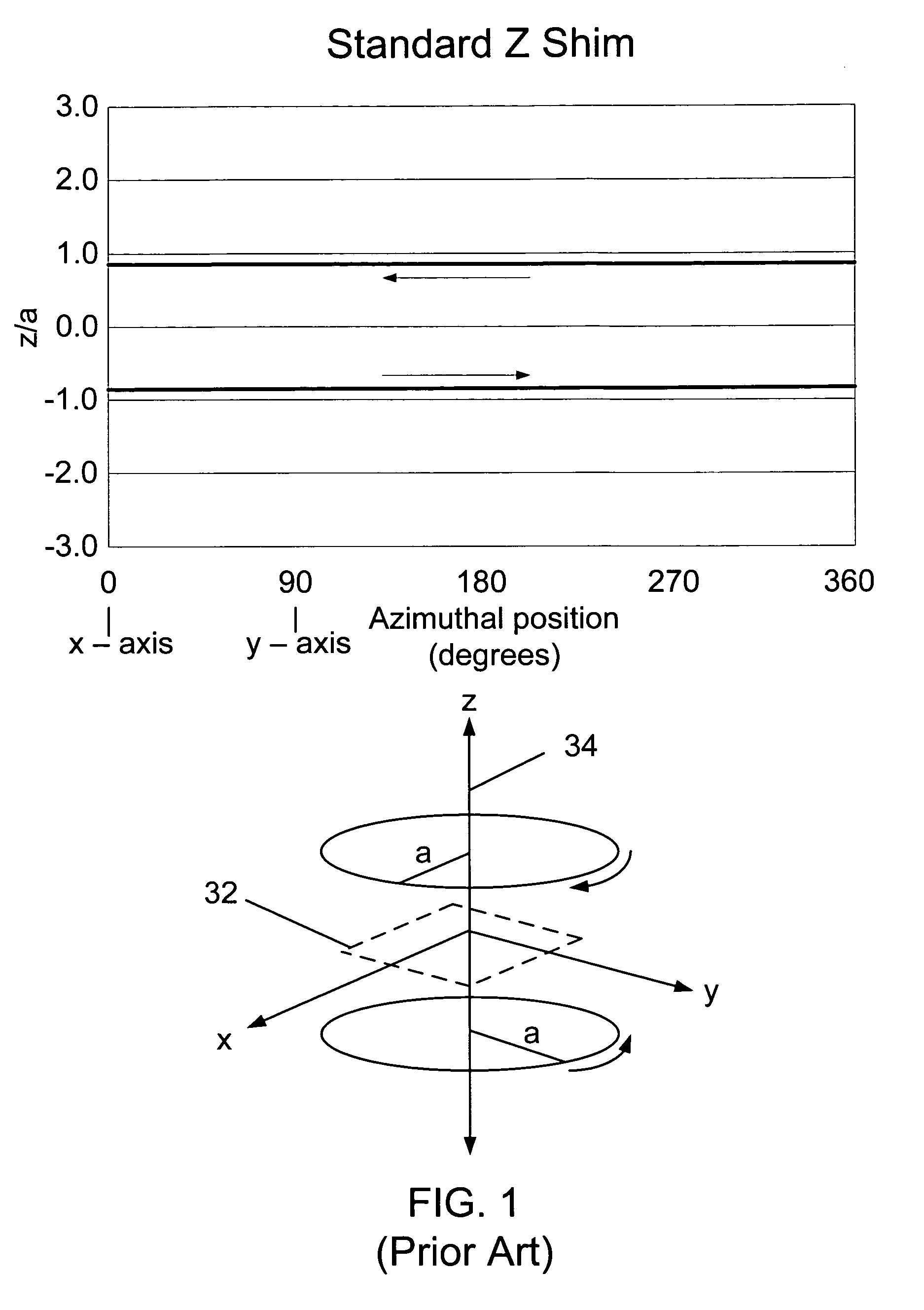

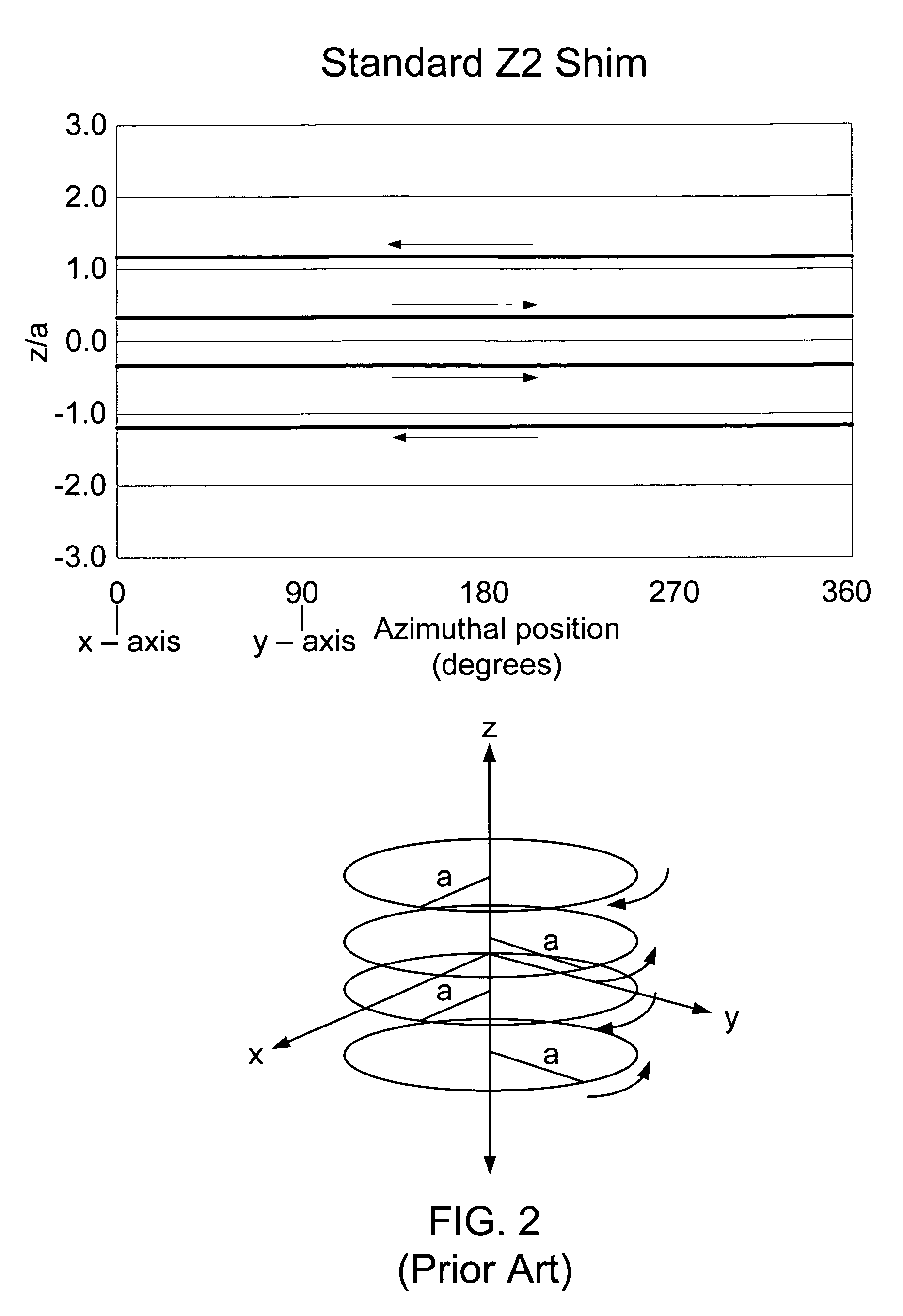

Magnetic shimming configuration with optimized turn geometry and electrical circuitry

InactiveUS7427908B1Simple structureOptimized turn geometryMagnetic measurementsMagnetsElectrical conductorEngineering

A magnetic shimming configuration for a high-field magnet having optimized turn geometry and electrical circuitry. The present invention accomplishes this by combining the corrective functionalities of the standard X and ZX shims into two single, simplified electrical circuits and conductors, optimized for field strength as a function of turn location. The standard Y and ZY shims were also replaced with two single, simplified circuits and conductor that is corrective of the Y and ZY fields. The new configuration also eliminates the need of additional “second, outboard turns” of the traditional X, ZX, Y, and ZY shims, located further away from the mid-plane.

Owner:FLORIDA STATE UNIV RES FOUND INC

Downstream transmitter and cable modem receiver for 1024 QAM

ActiveUS20090044083A1Quality improvementAdditional circuitryData representation error detection/correctionCode conversionModem deviceAudio power amplifier

A headend transmitter that transmits 1024 QAM including a 256 QAM modulator which has been modified to have more aggressive forward error correction processing. The 256 QAM modulator outputs 256 QAM points to a summer. Another data modulator receives additional data to be transmitted in a separate, substantially less complex constellation. This modulator processes the additional data to do forward error correction thereon and then maps the encoded data into a less complex constellation such as QPSK, 16 QAM etc. The additional data constellation points are then amplified in a variable gain amplifier and fed to a summer where each additional data point is added by vector summation to one 256 QAM point. The output 1024 QAM point is filtered and shifted to the desired transmission frequency. Legacy cable modem receivers can still receive the 256 QAM point since the addition of the new data just appears to be noise which they can overcome using the parity bits encoded in the transmitted symbols. 1024 QAM cable modem receivers receive both the 256 QAM points and the new data points and output both.

Owner:AVAGO TECH INT SALES PTE LTD

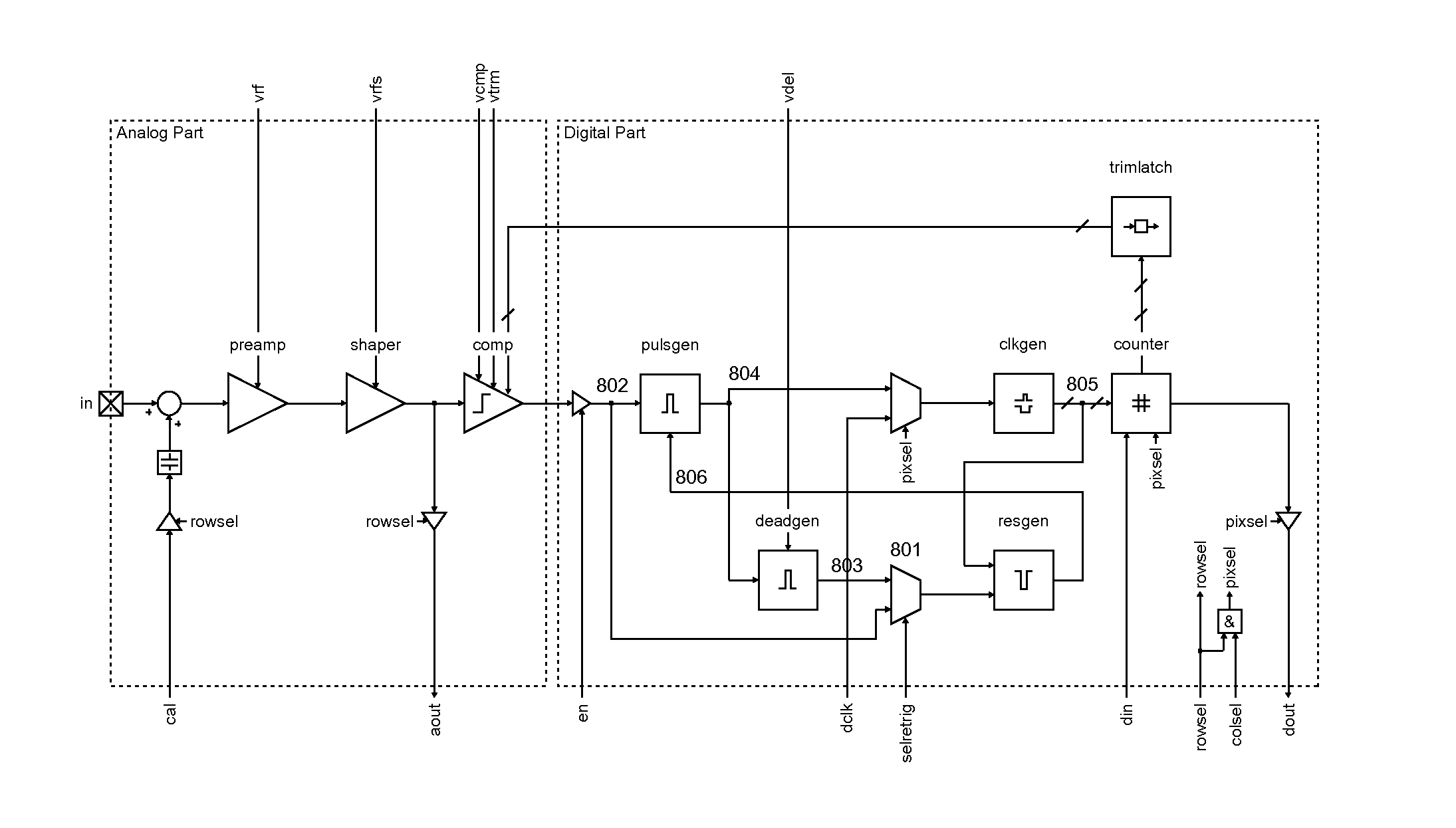

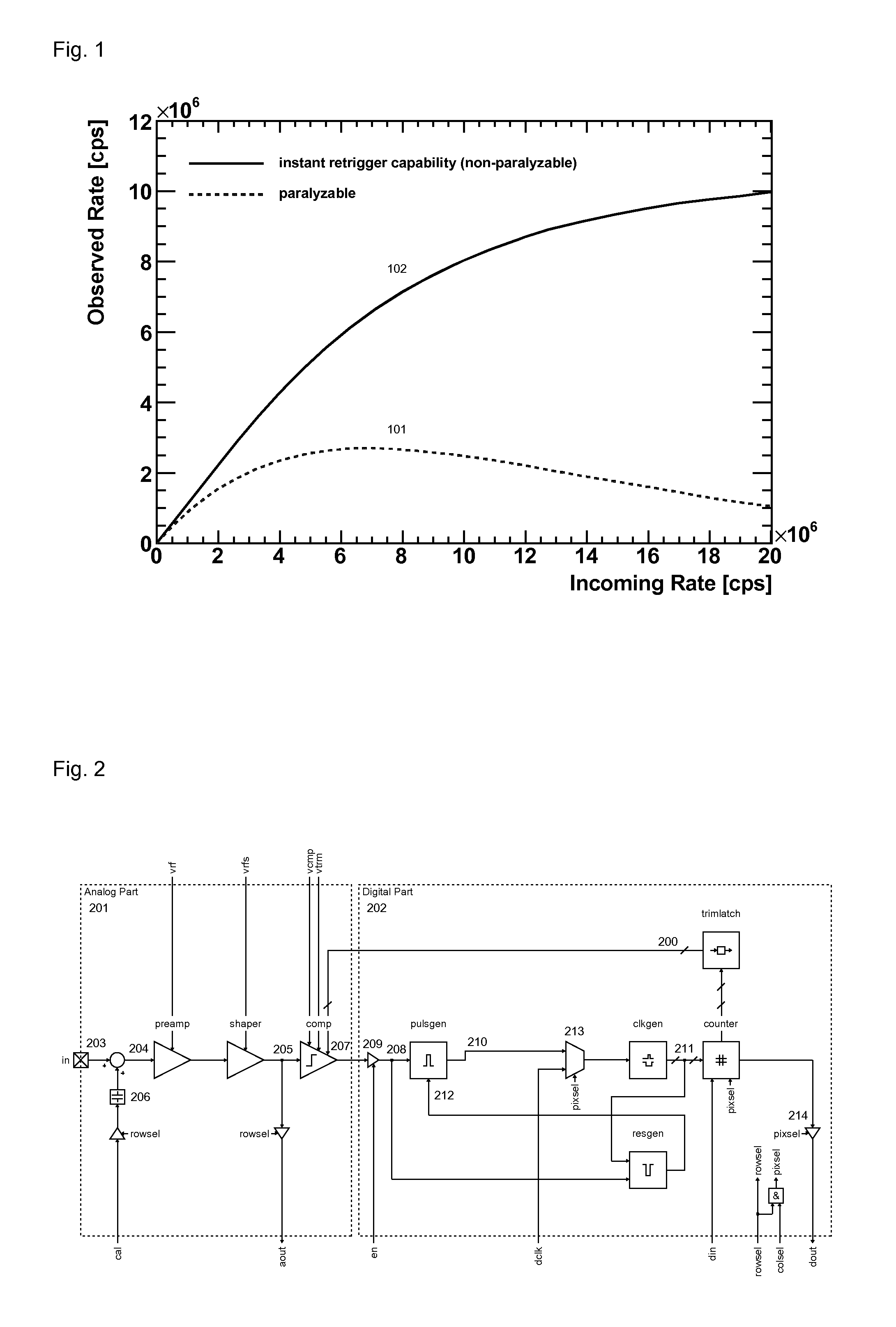

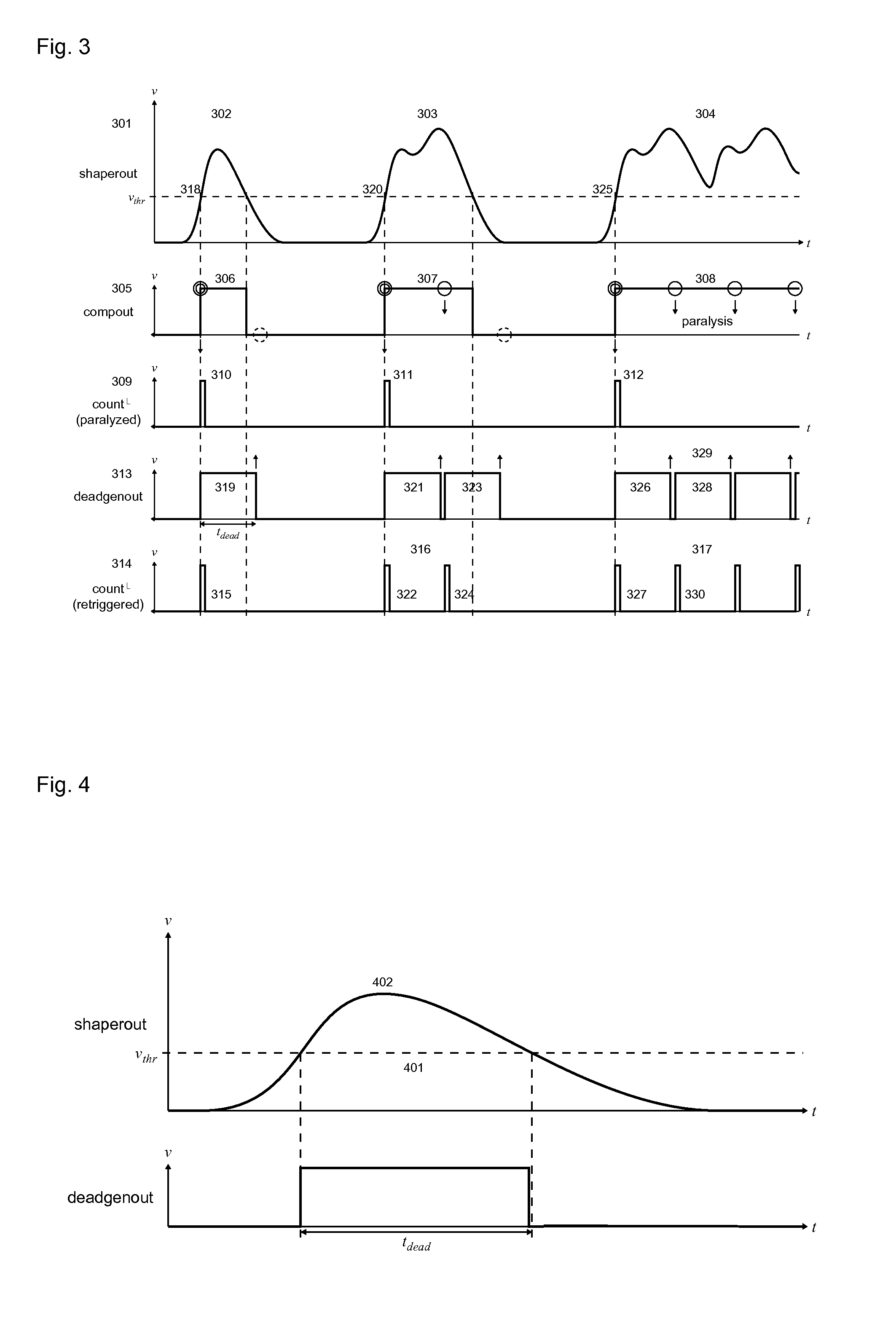

Photon counting imaging method and device with instant retrigger capability

ActiveUS20140191136A1Discriminate the width of a signal pulseAccurate timingMaterial analysis by optical meansPhotometry using electric radiation detectorsElectron holeDiscriminator

A method for photon counting imaging with improved high-rate counting performance includes the step of applying an instant retrigger capability with adjustable dead time in cells of the detector array and operates an apparatus using a layer of photo-sensitive material, an L×K array of photodetector elements arranged in the layer of the photosensitive material, an N×M array of readout unit cells, including amplifying elements and at least one readout unit cells for at least one photodetector elements. The readout unit cells are controlled by signal processing elements with each readout unit cell having internal signal processing elements to generate a discriminator output signal representing an amplified signal of the electron-hole pairs generated by an incident photon or a number of incident photons in the respective photodetector element. The discriminator output signal is generated by comparing the amplified signal with a predetermined threshold level and the discriminator output signal is generated whenever the amplified signal exceeds the threshold level.

Owner:DECTRIS LTD