Patents

Literature

31results about How to "Great" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

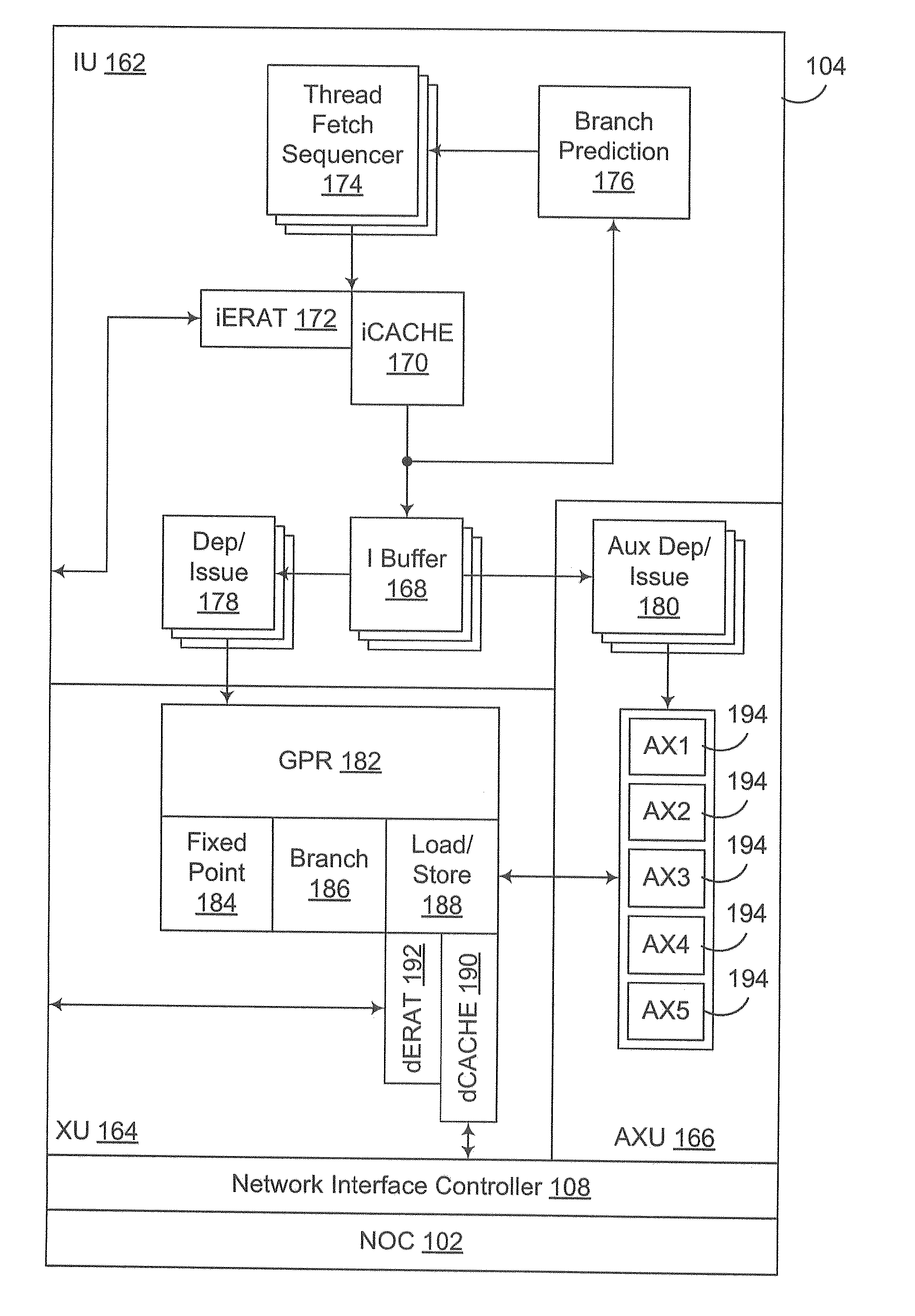

Fault tolerant stability critical execution checking using redundant execution pipelines

InactiveUS20110302450A1GreatAdditional circuitryDigital computer detailsRedundant operation error correctionComputer scienceExecution unit

A circuit arrangement and method utilize existing redundant execution pipelines in a processing unit to execute multiple instances of stability critical instructions in parallel so that the results of the multiple instances of the instructions can be compared for the purpose of detecting errors. For other types of instructions for which fault tolerant or stability critical execution is not required or desired, the redundant execution pipelines are utilized in a more conventional manner, enabling multiple non-stability critical instructions to be concurrently issued to and executed by the redundant execution pipelines. As such, for non-stability critical program code, the performance benefits of having multiple redundant execution units are preserved, yet in the instances where fault tolerant or stability critical execution is desired for certain program code, the redundant execution units may be repurposed to provide greater assurances as to the fault-free execution of such instructions.

Owner:IBM CORP

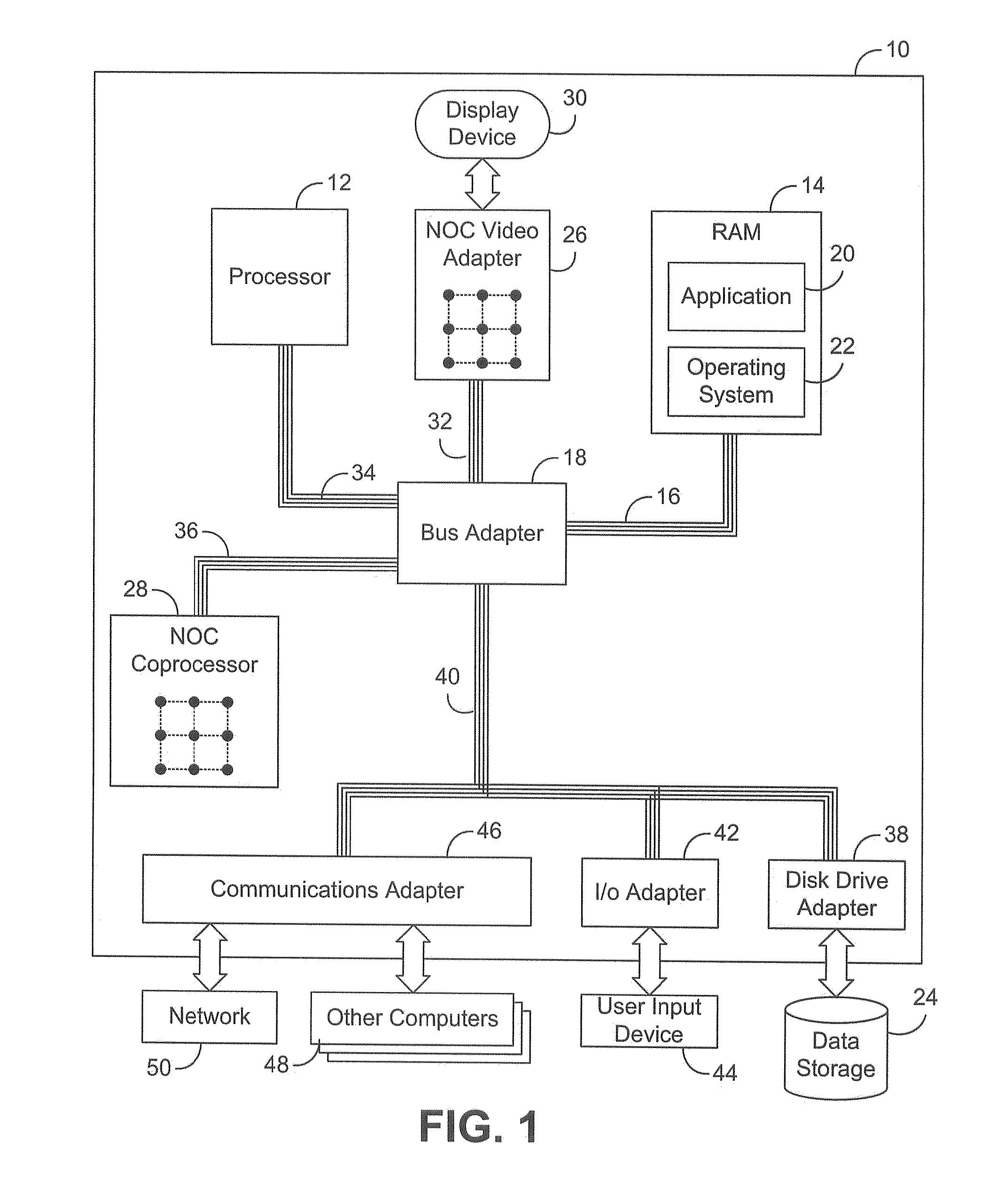

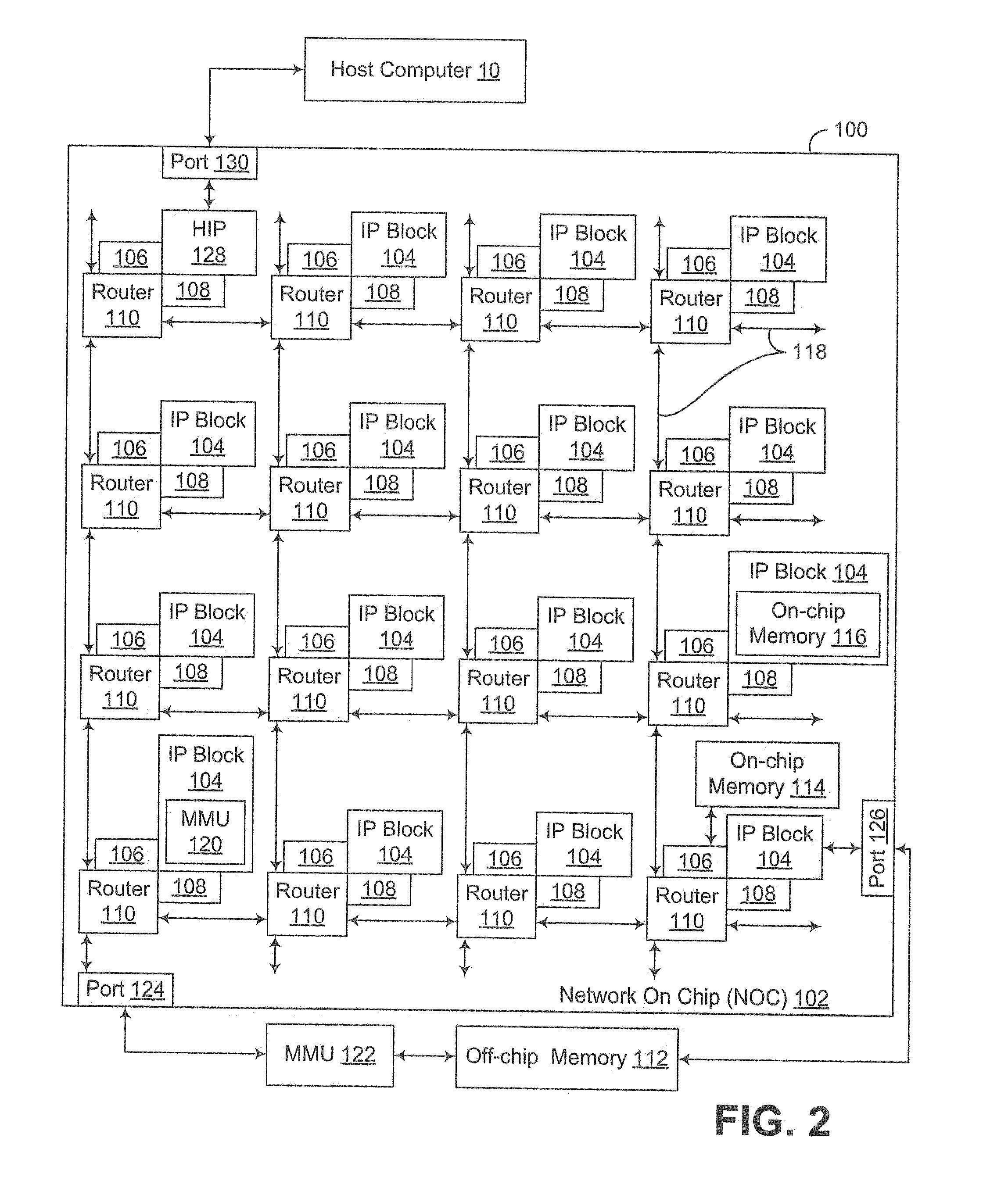

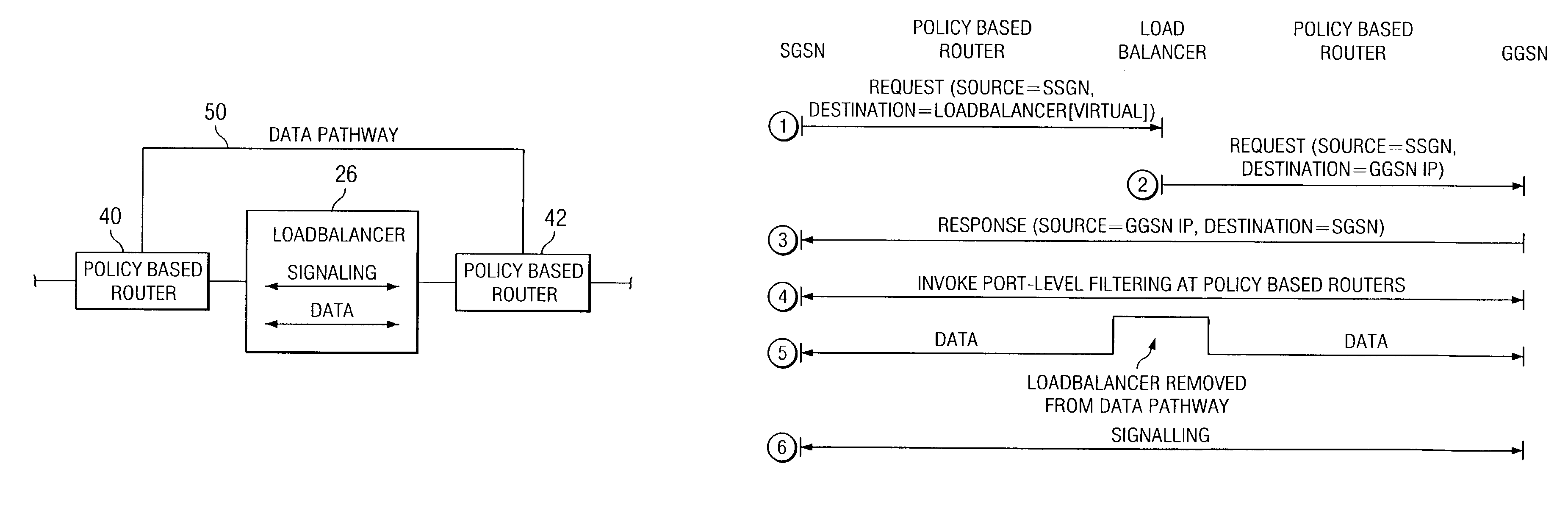

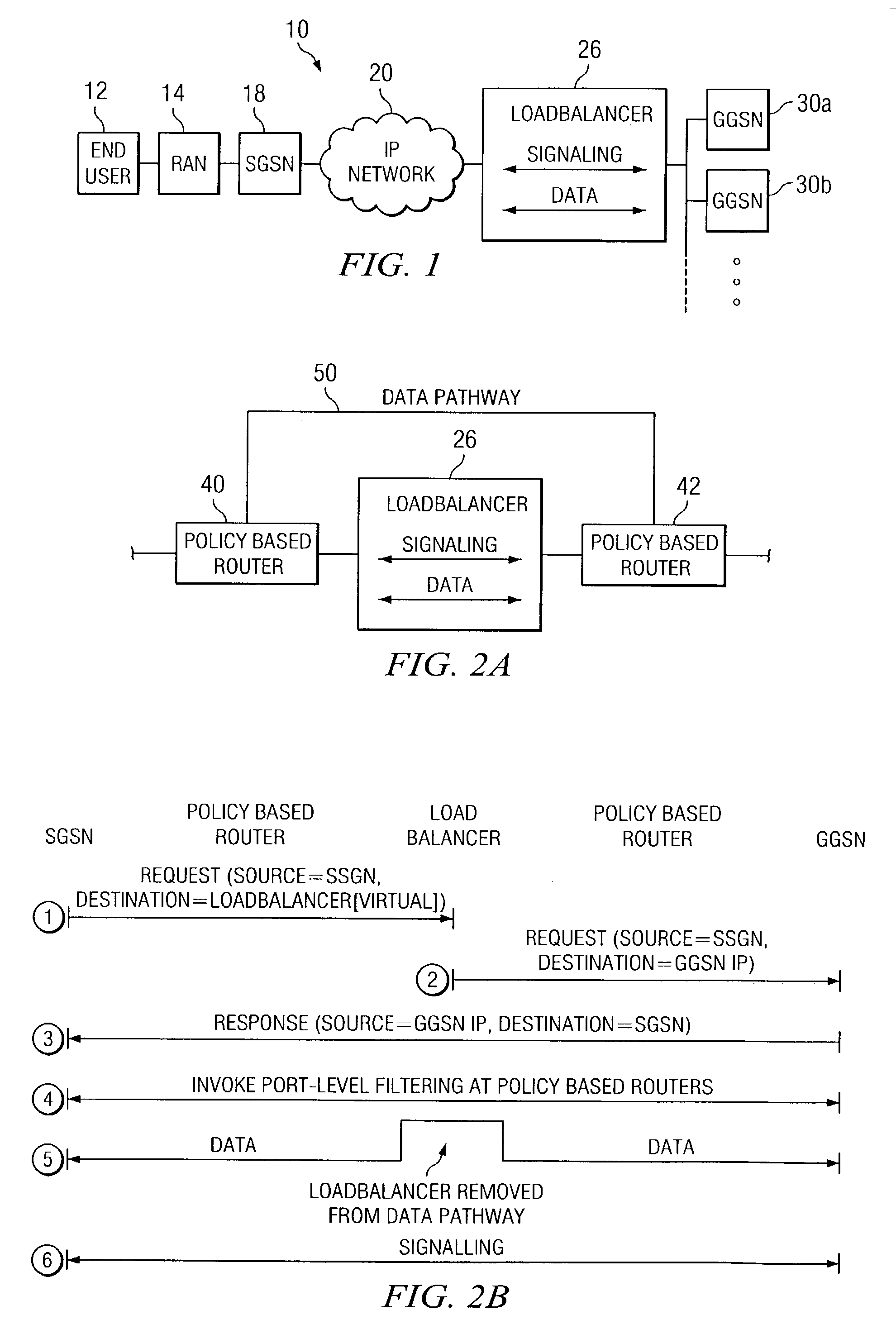

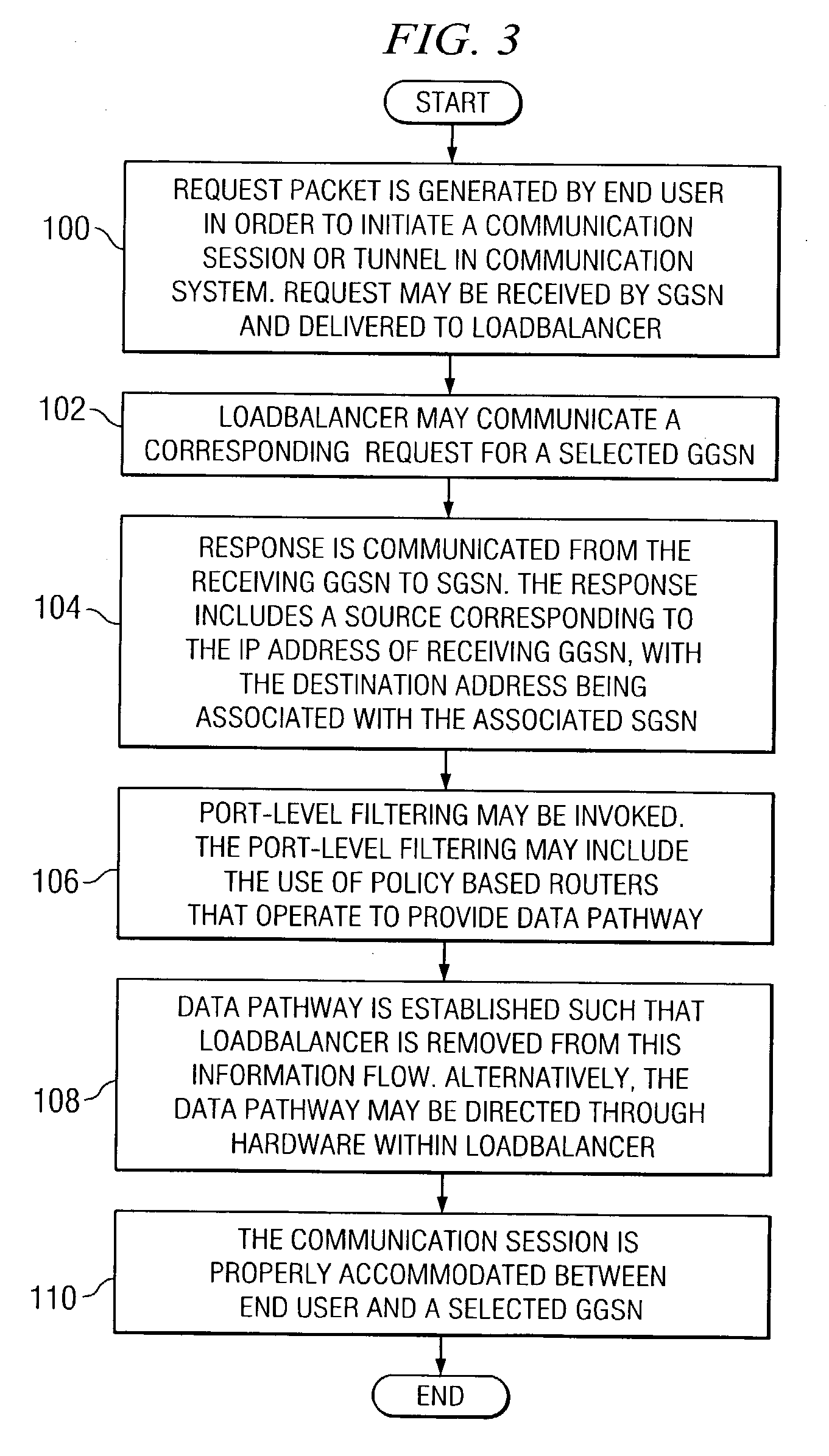

System and method for communicating data in a loadbalancing environment

ActiveUS7191235B1Reduce in quantityGreatNetwork traffic/resource managementMultiprogramming arrangementsTelecommunications linkSignalling pathways

A method for communicating data in a network environment is provided that includes receiving a request from an end user for a communications link, the request being used to initiate a communication session. A response is then received that is communicated to the end user in order to establish the communication session, the response being generated by a network node that was selected as a result of a loadbalancing decision. Port-level filtering for the communication session may then be invoked after the response such that separate data and signal pathways are established for selected information associated with the communication session.

Owner:CISCO TECH INC

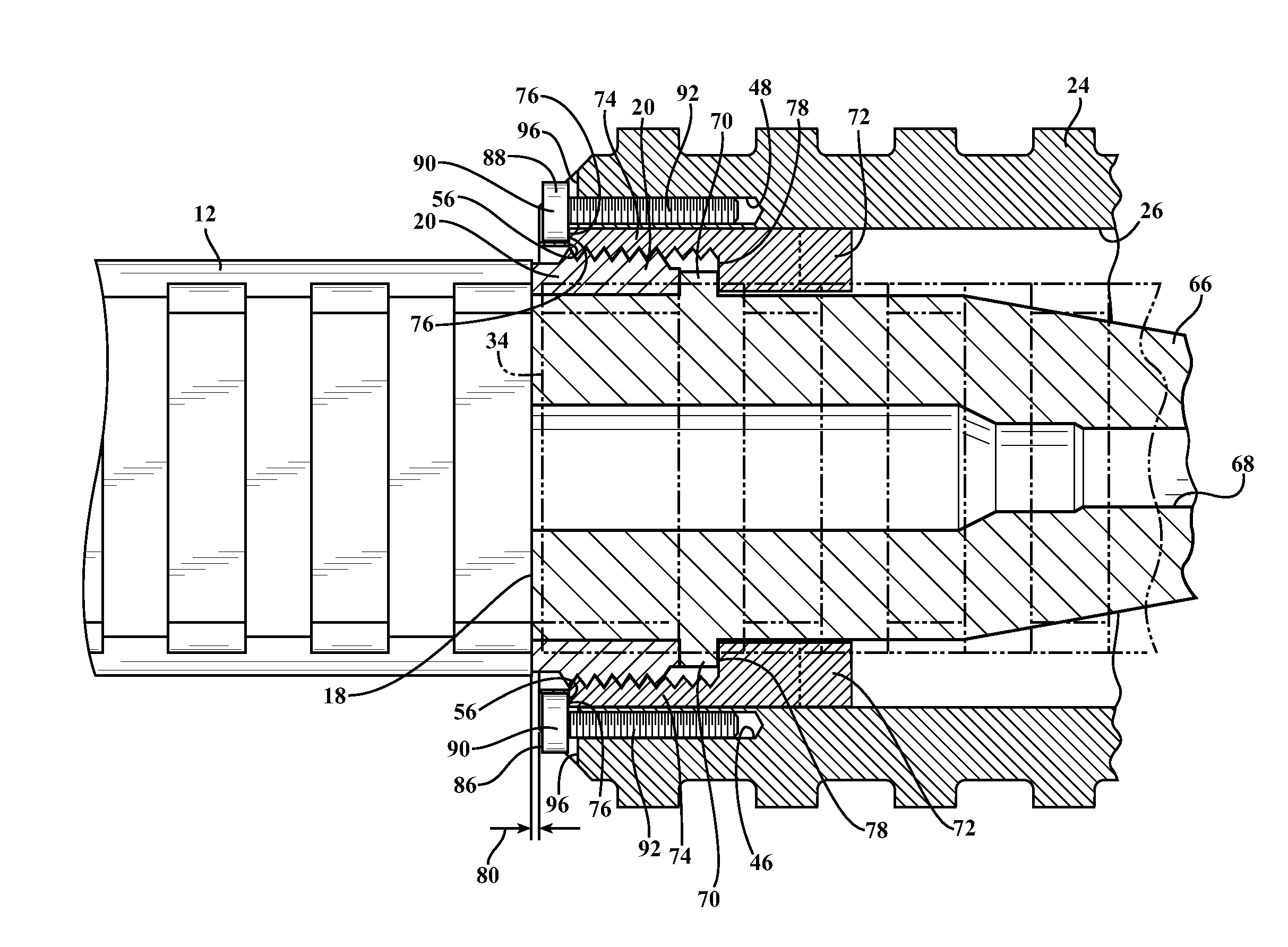

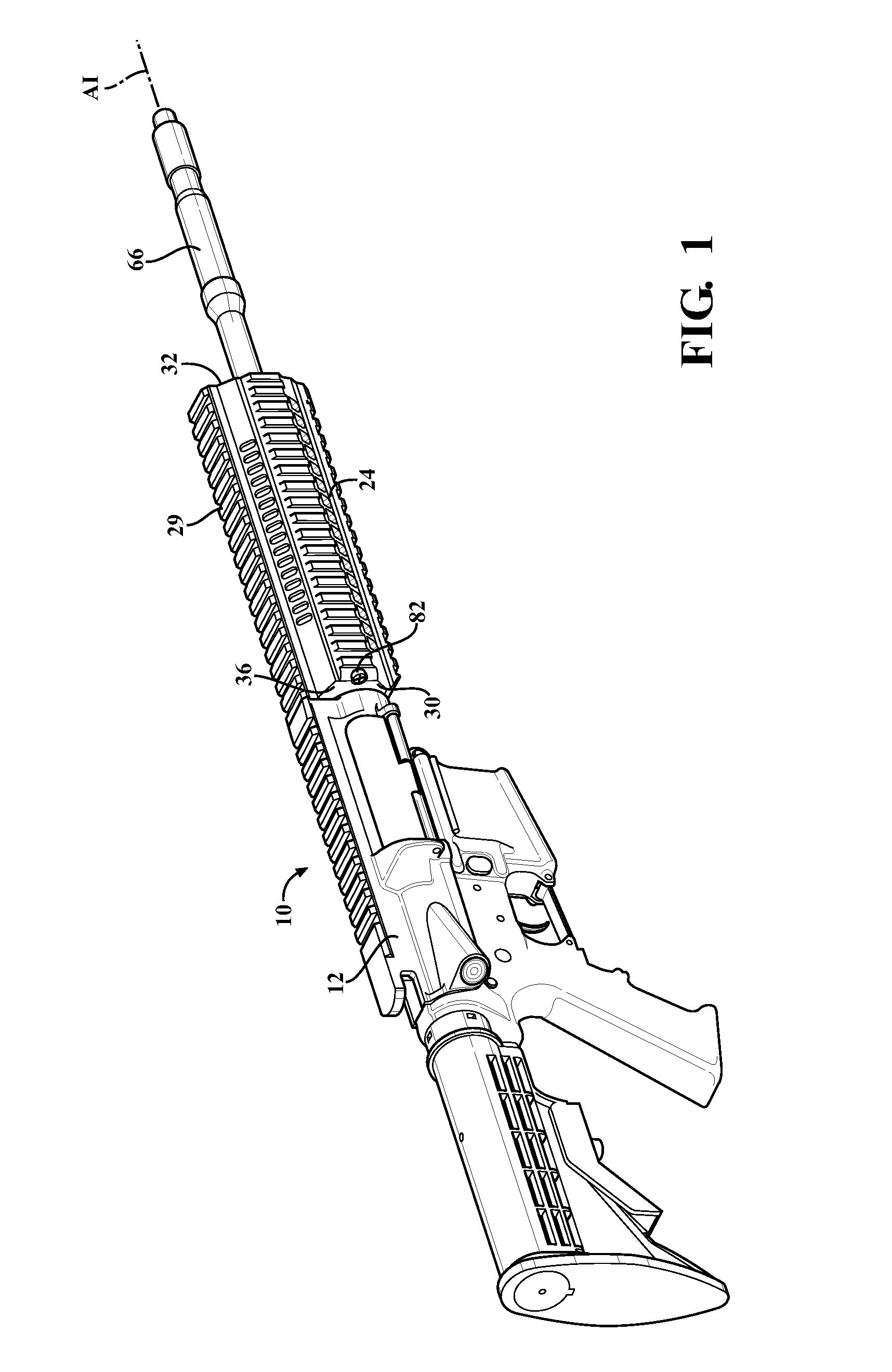

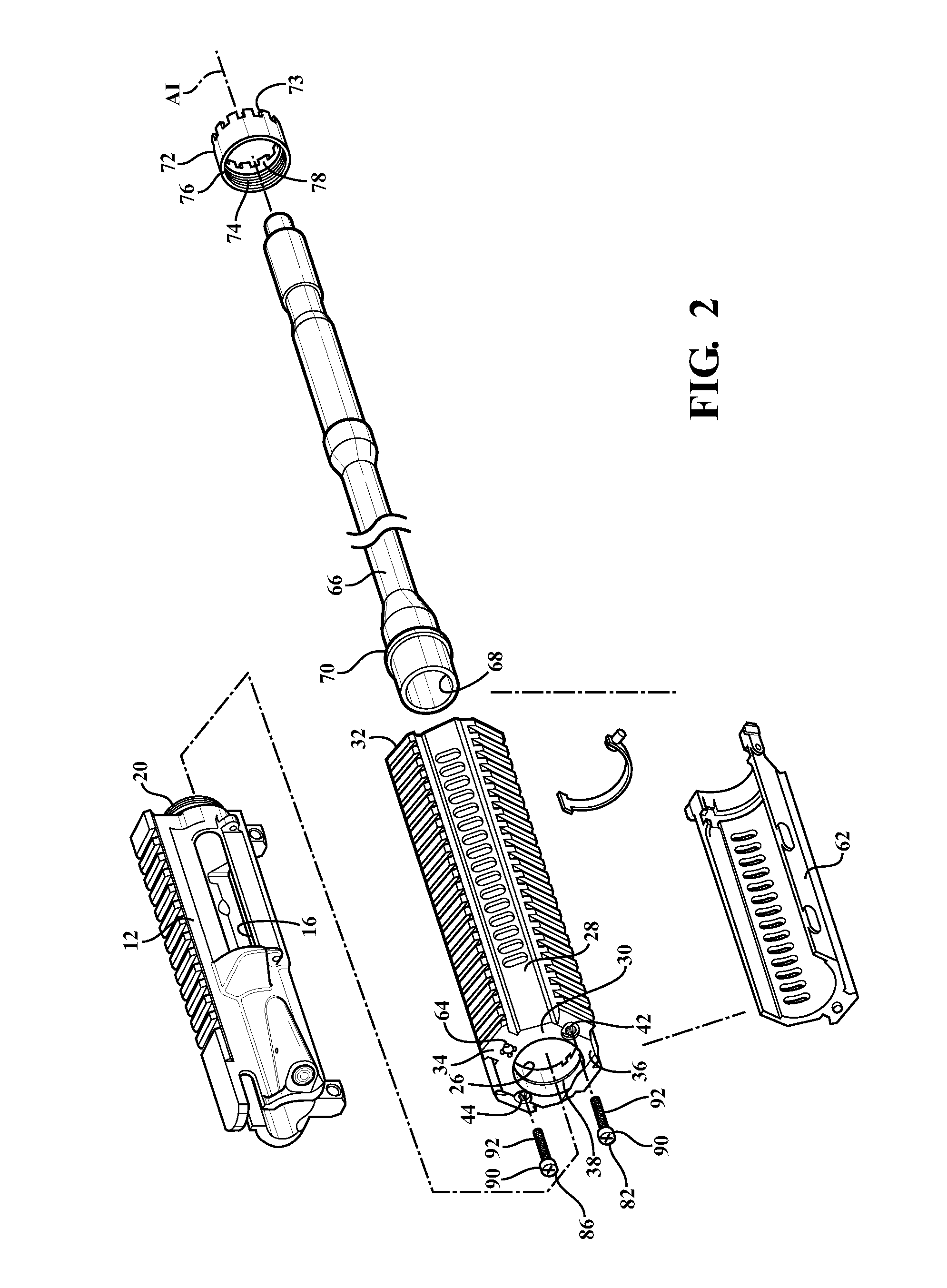

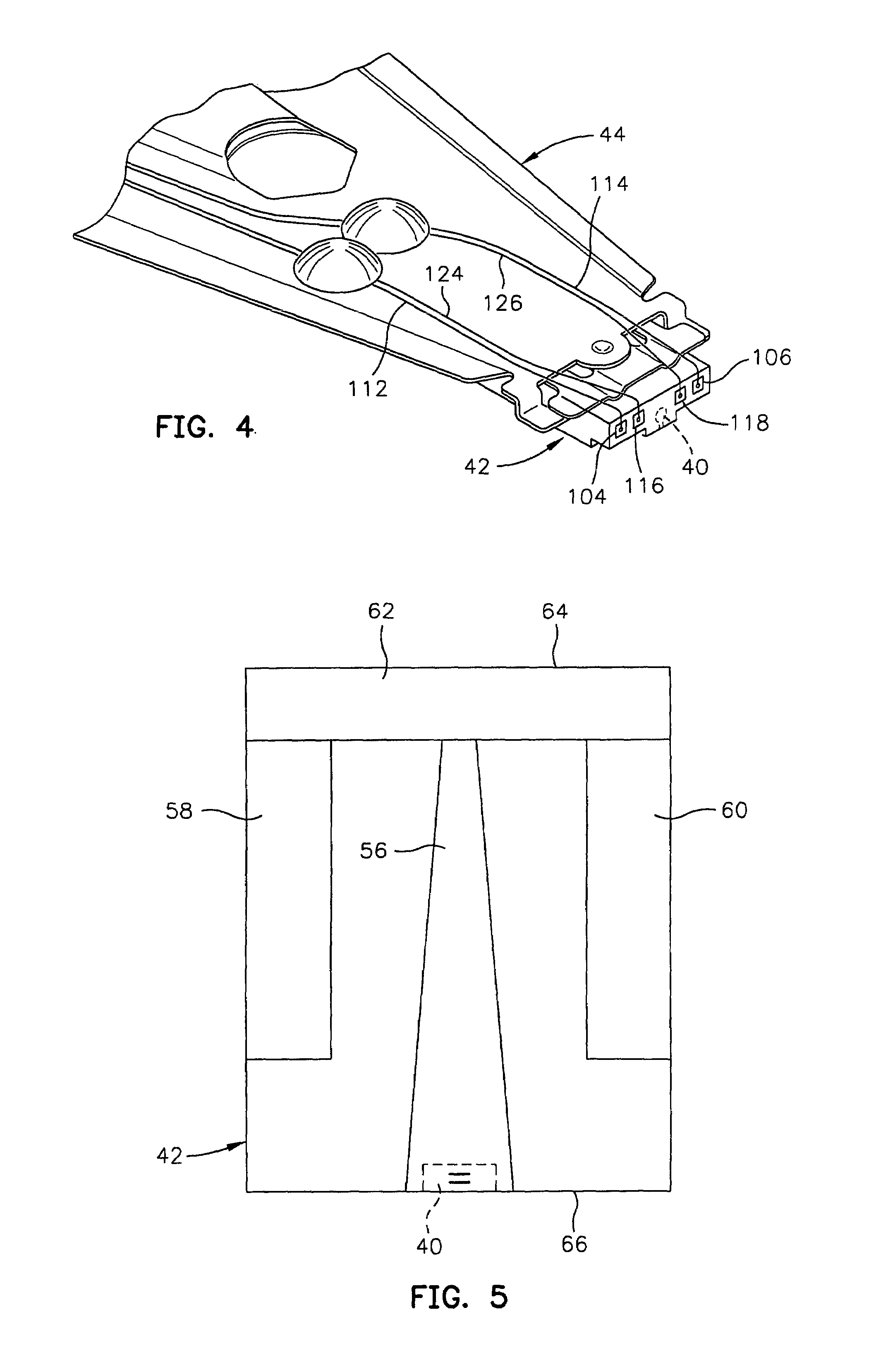

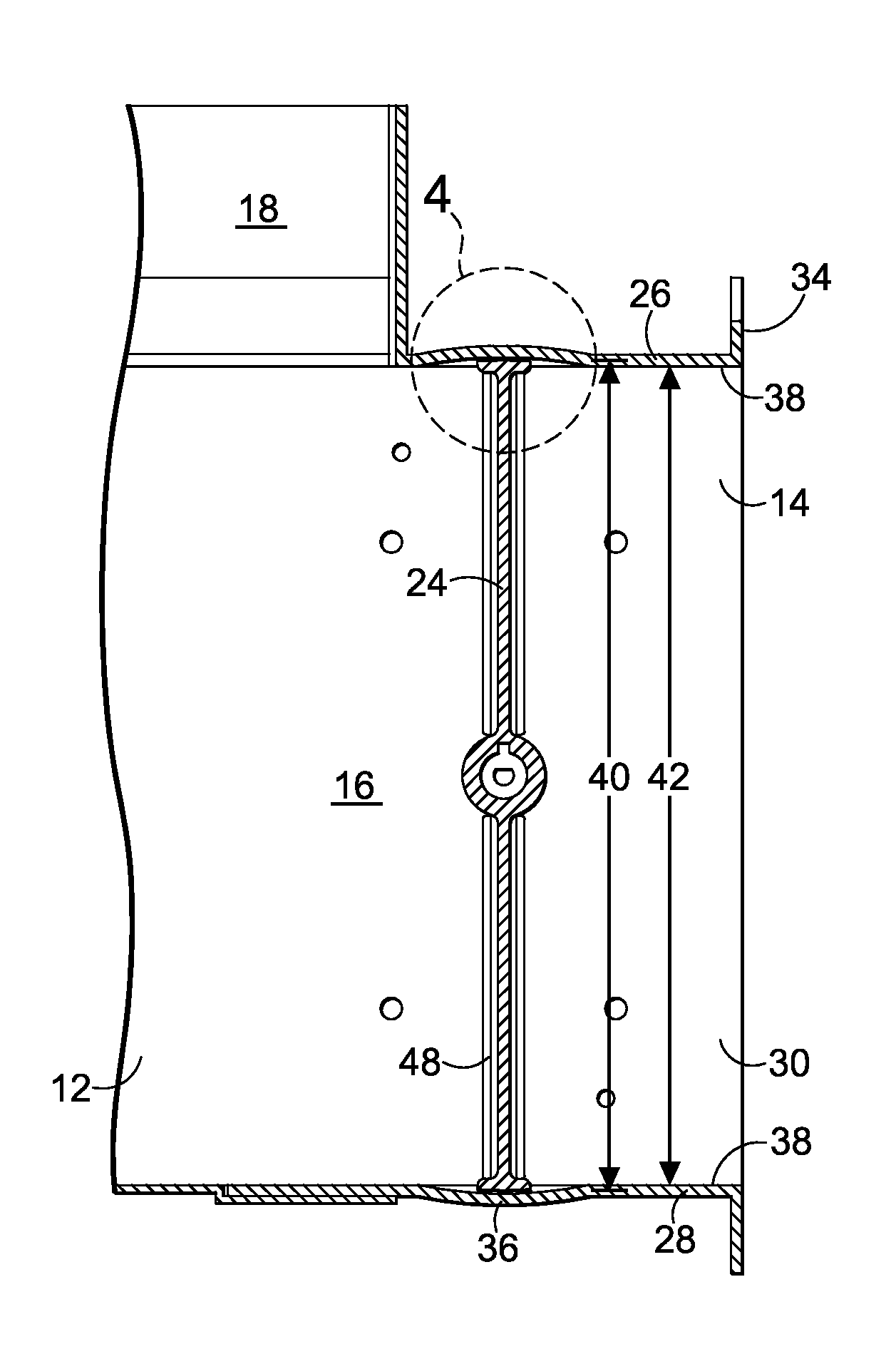

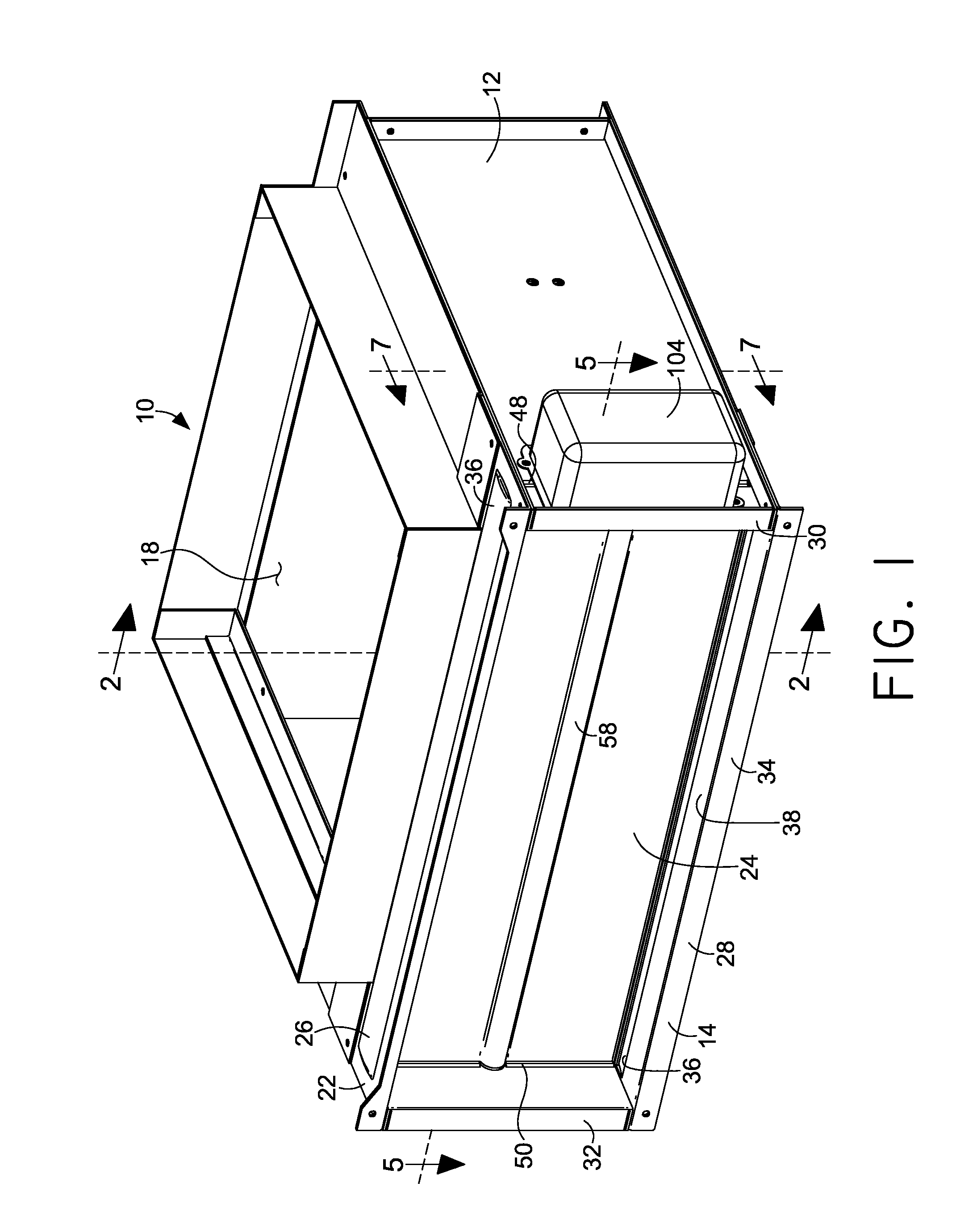

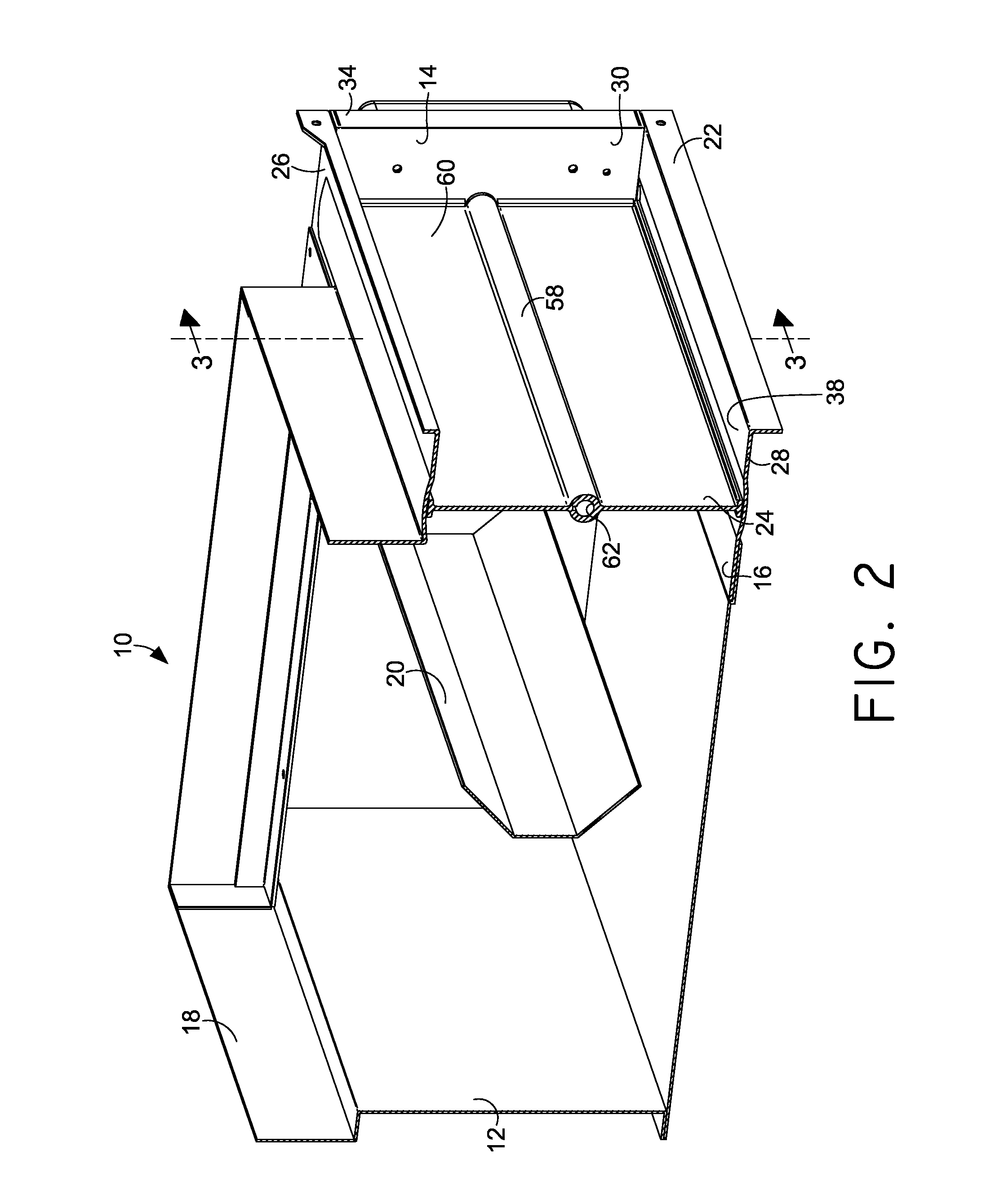

Hand guard mounting mechanism

A firearm comprising a receiver including a threaded end with the receiver extending along an axis and a hand guard having an exterior surface and defining a hand guard bore along the axis with the exterior surface terminating at a mating surface disposed about the threaded end. The firearm additionally includes a barrel disposed within the hand guard bore and abutting the threaded end and a nut abutting the barrel and engaging the threaded end of the receiver to secure the barrel to the receiver. The firearm further including a securing device with the exterior surface of the hand guard defining an engagement area providing access into the hand guard bore and the securing device interfacing with the engagement area and extending into the hand guard bore to abut the nut and securely mount the mating surface of the hand guard to the receiver.

Owner:ADCOR INDS

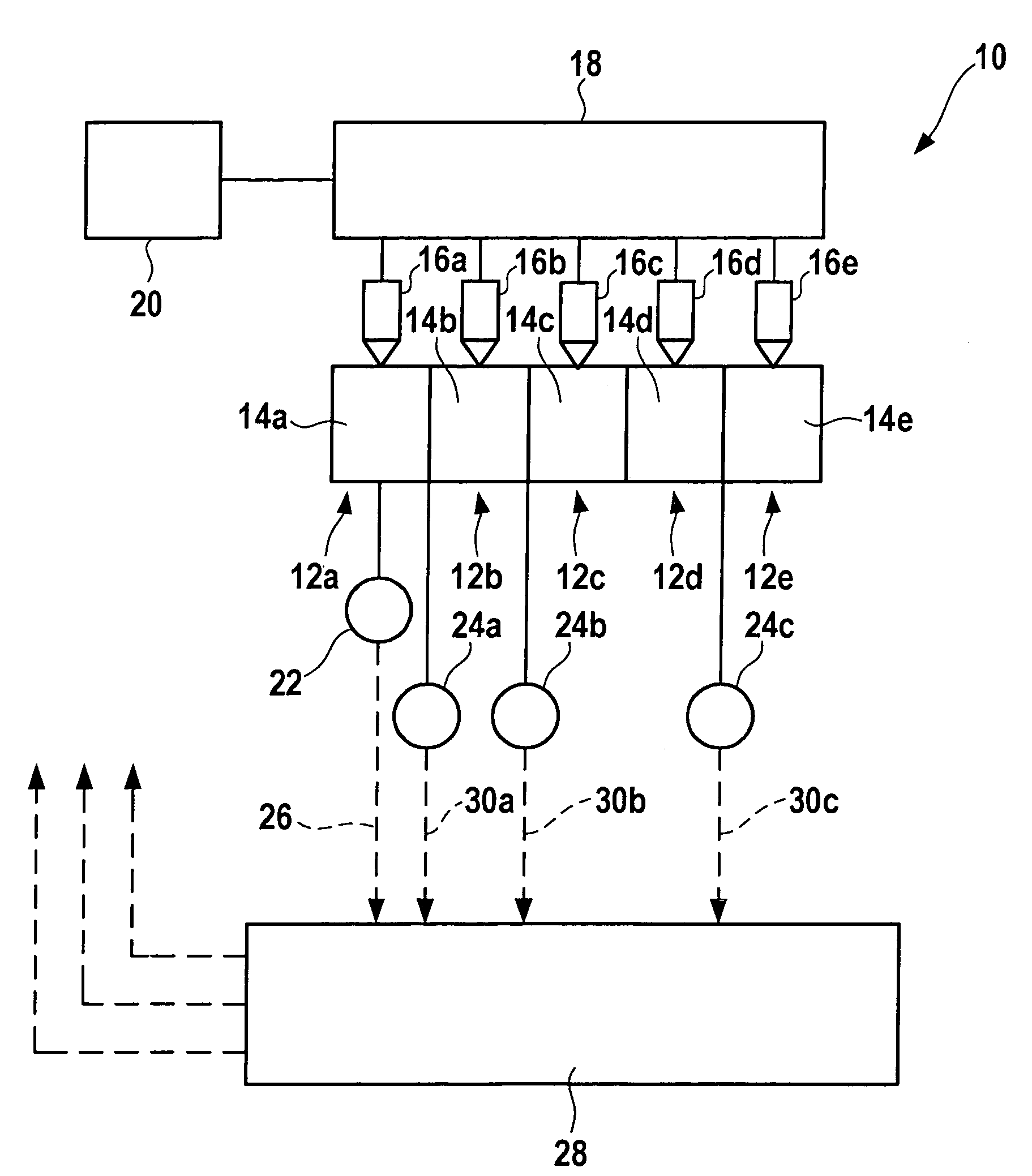

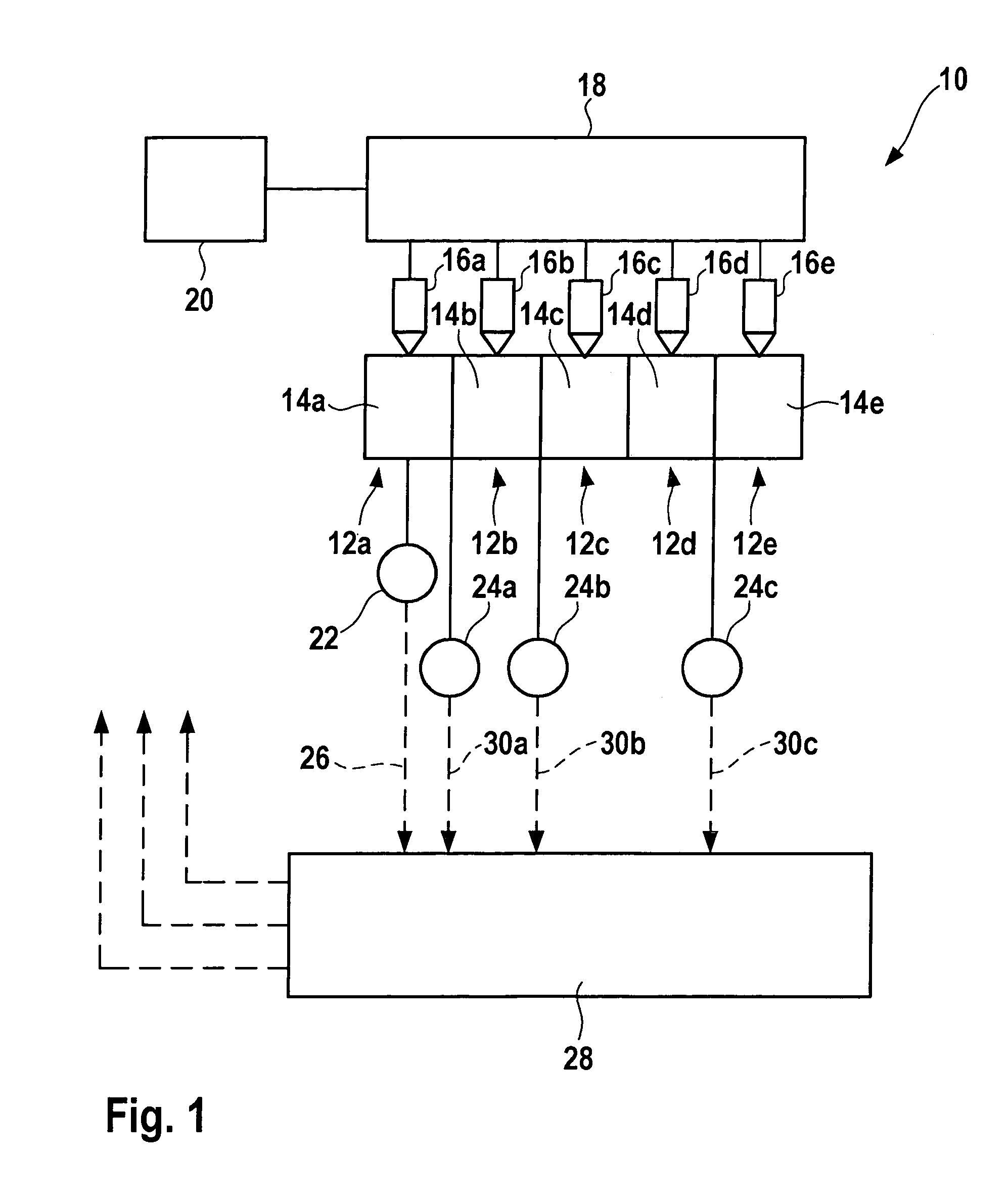

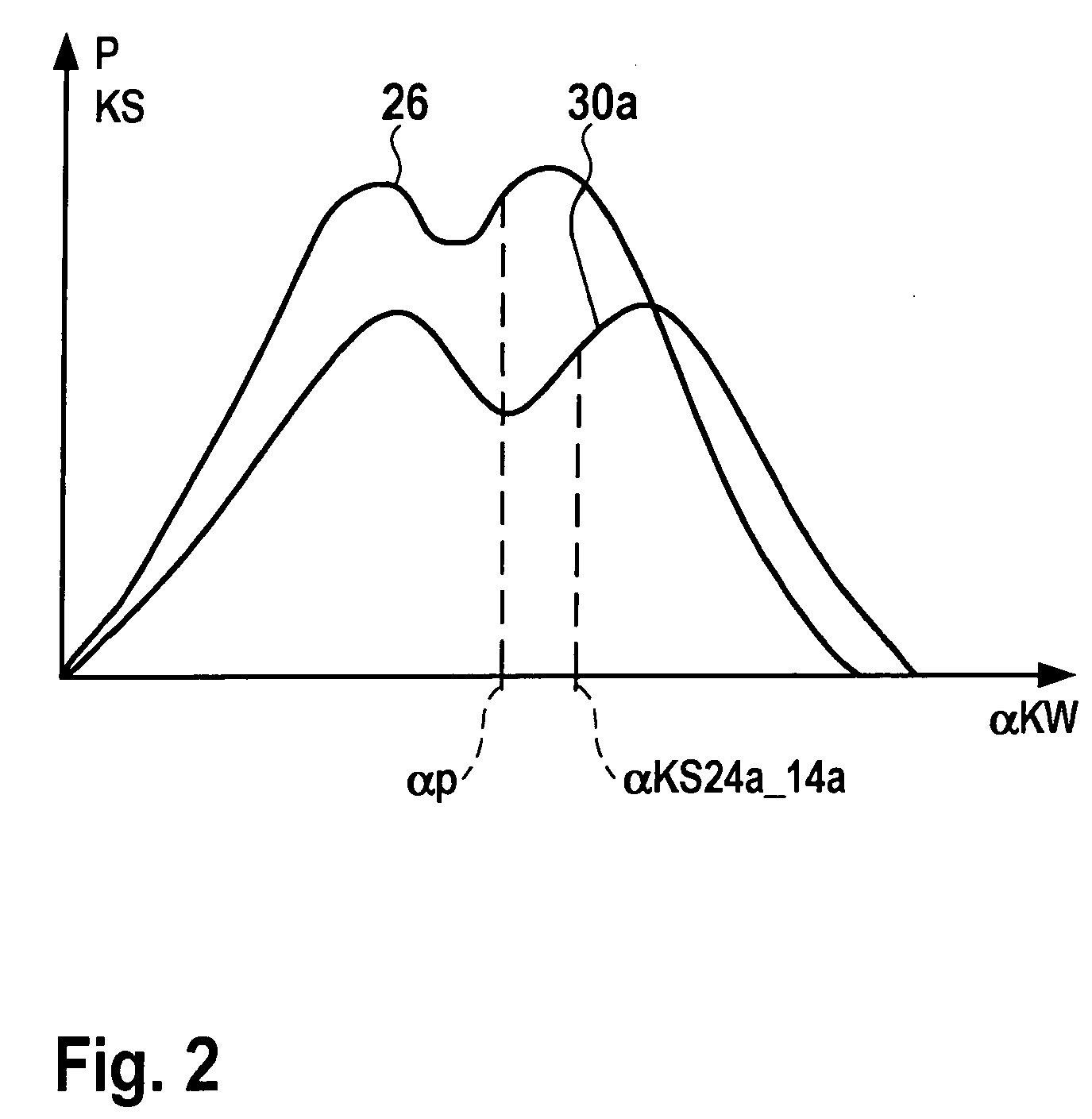

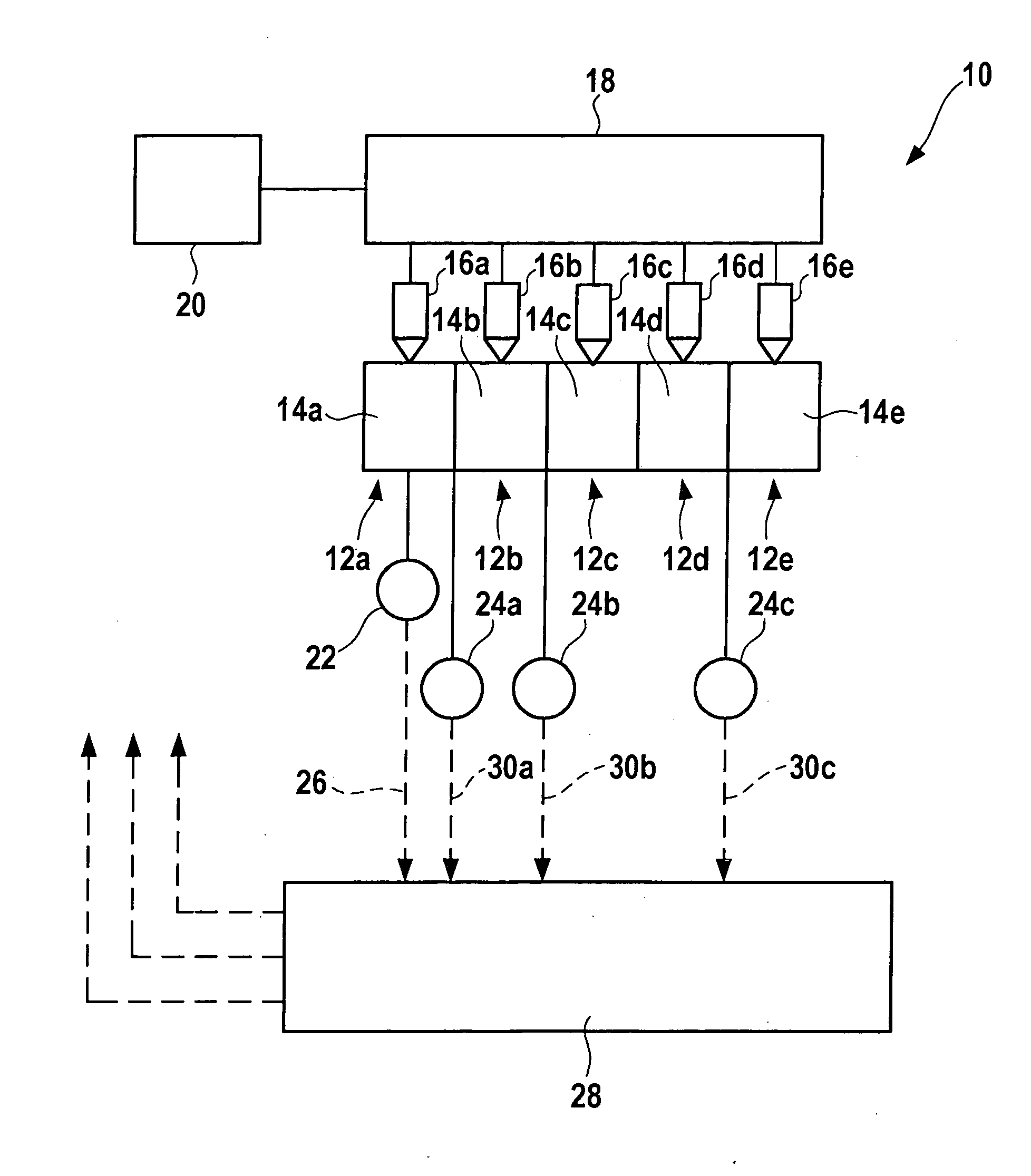

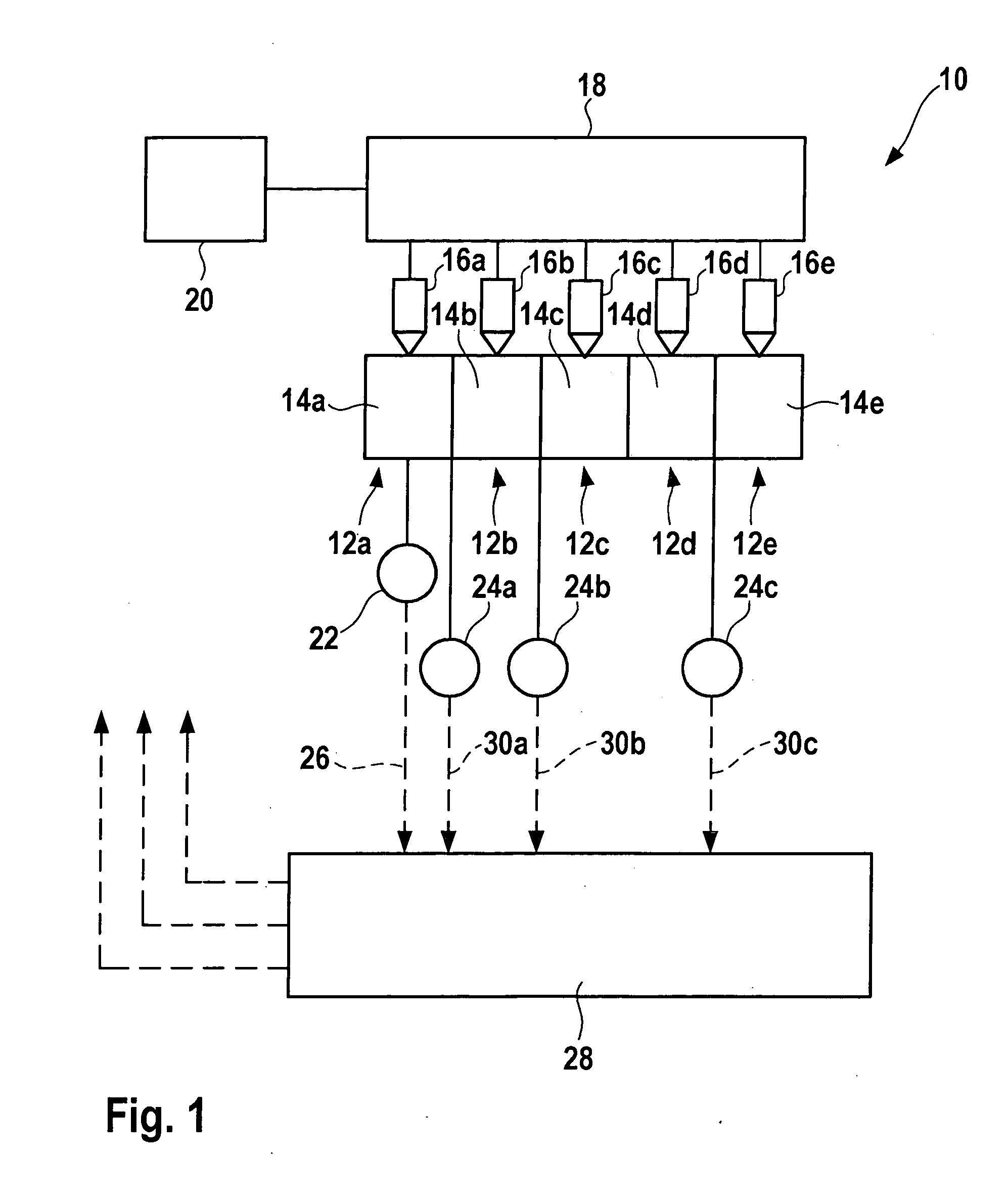

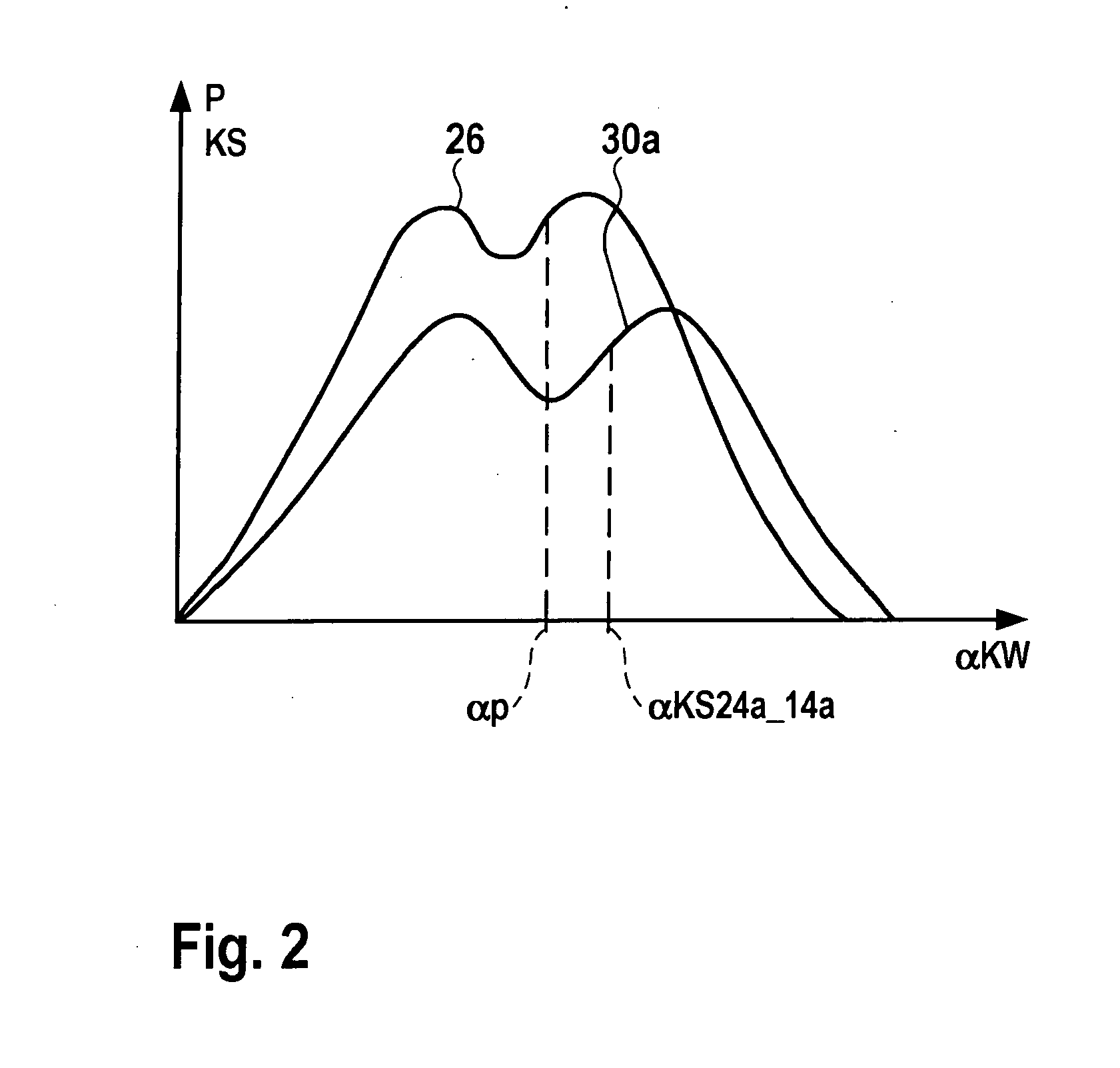

Method for operating an internal combustion engine

ActiveUS7260469B2Low accuracyGreatAnalogue computers for vehiclesElectrical controlCombustion chamberEngineering

In a method for operating an internal combustion engine, a first data quantity is derived based on a signal of a first sensor which detects the pressure in a first combustion chamber of a plurality of combustion chambers, and a second data quantity is derived based on a signal of a second sensor, which second data quantity is a function of the pressure variation in at least one of the plurality of combustion chambers. The first data quantity and the second data quantity are functions of the pressure variation in the same combustion chamber, and a drift of the second sensor is ascertained from a change over time in the second data quantity with respect to the first data quantity.

Owner:ROBERT BOSCH GMBH

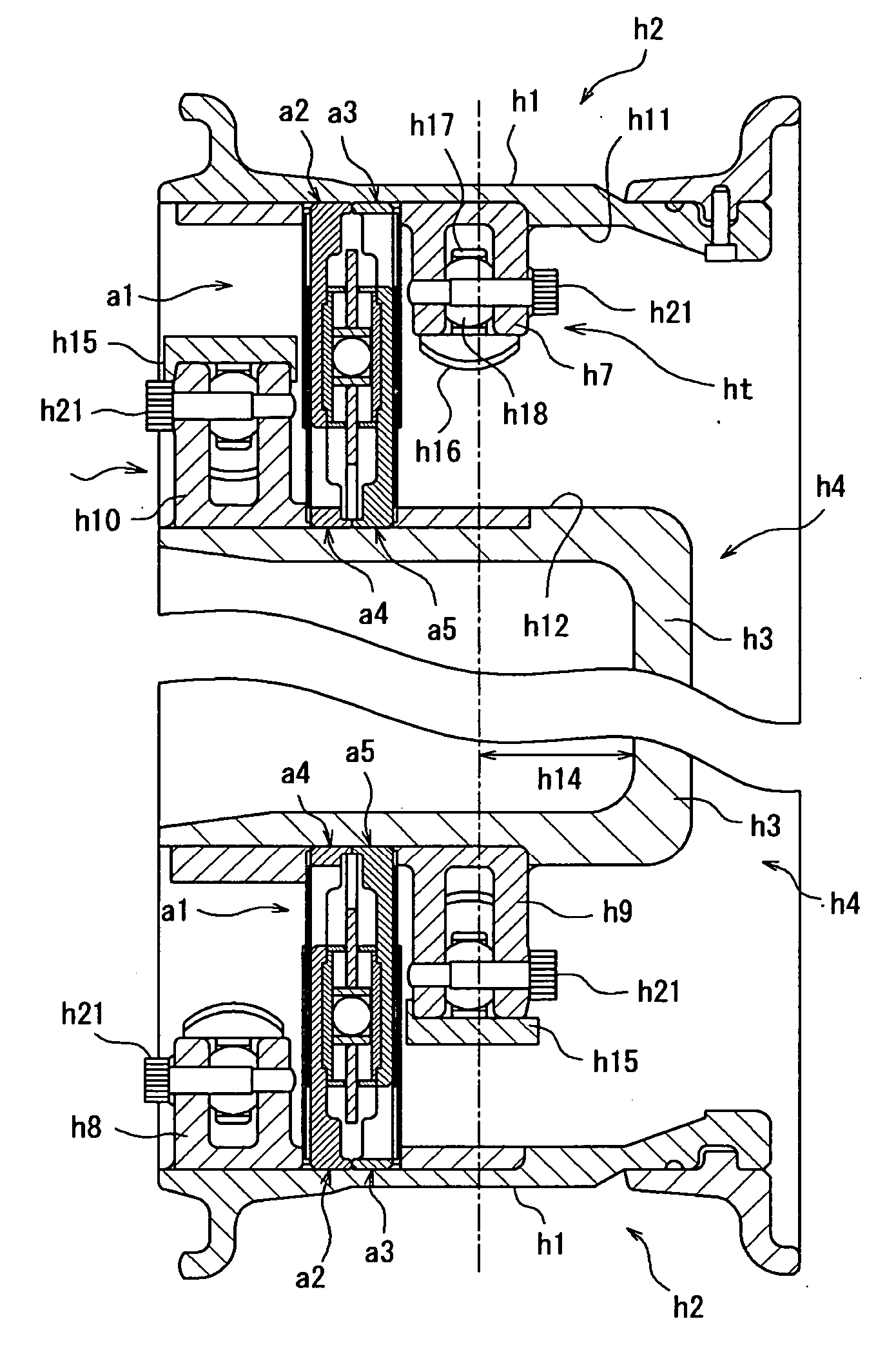

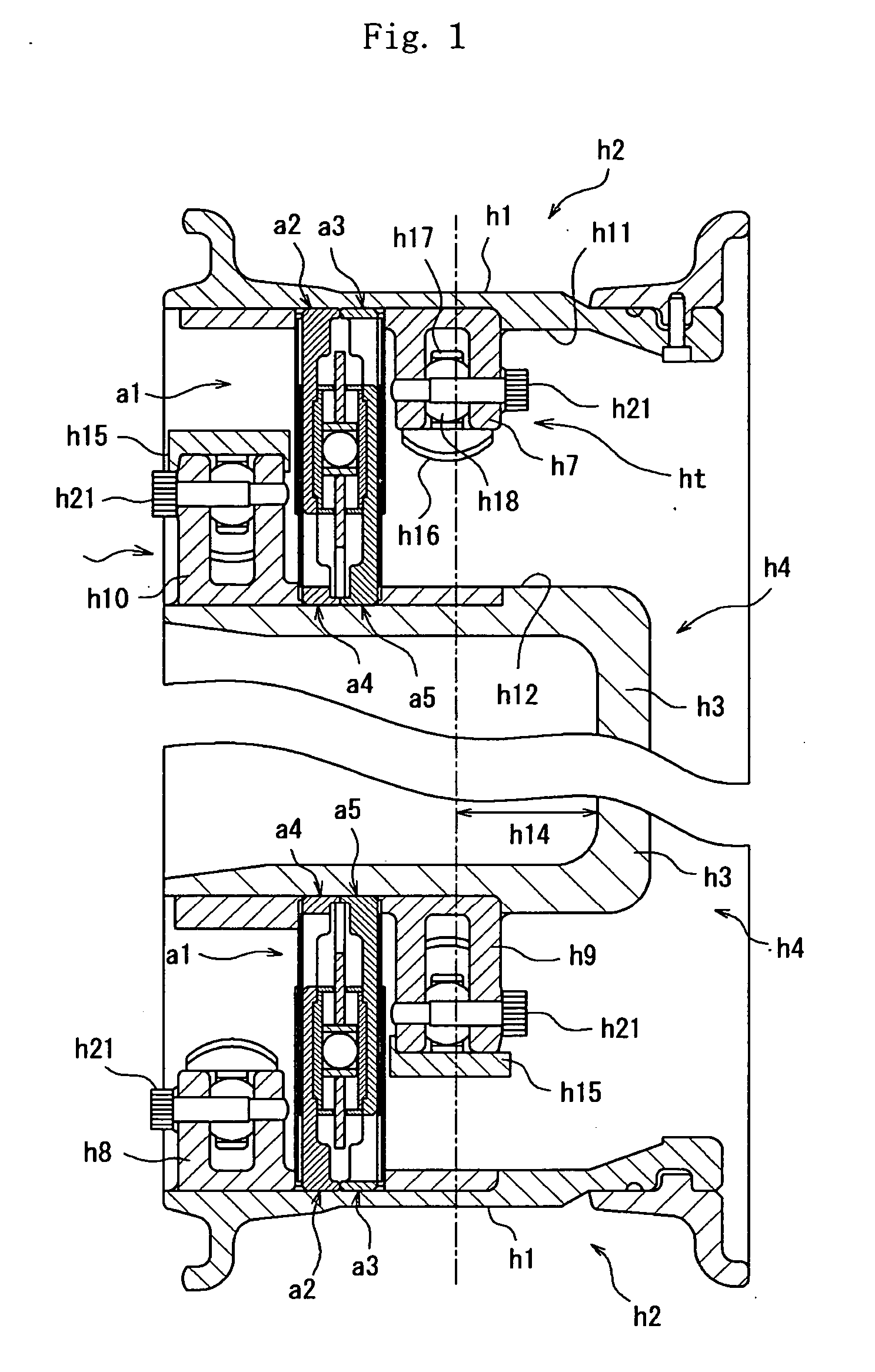

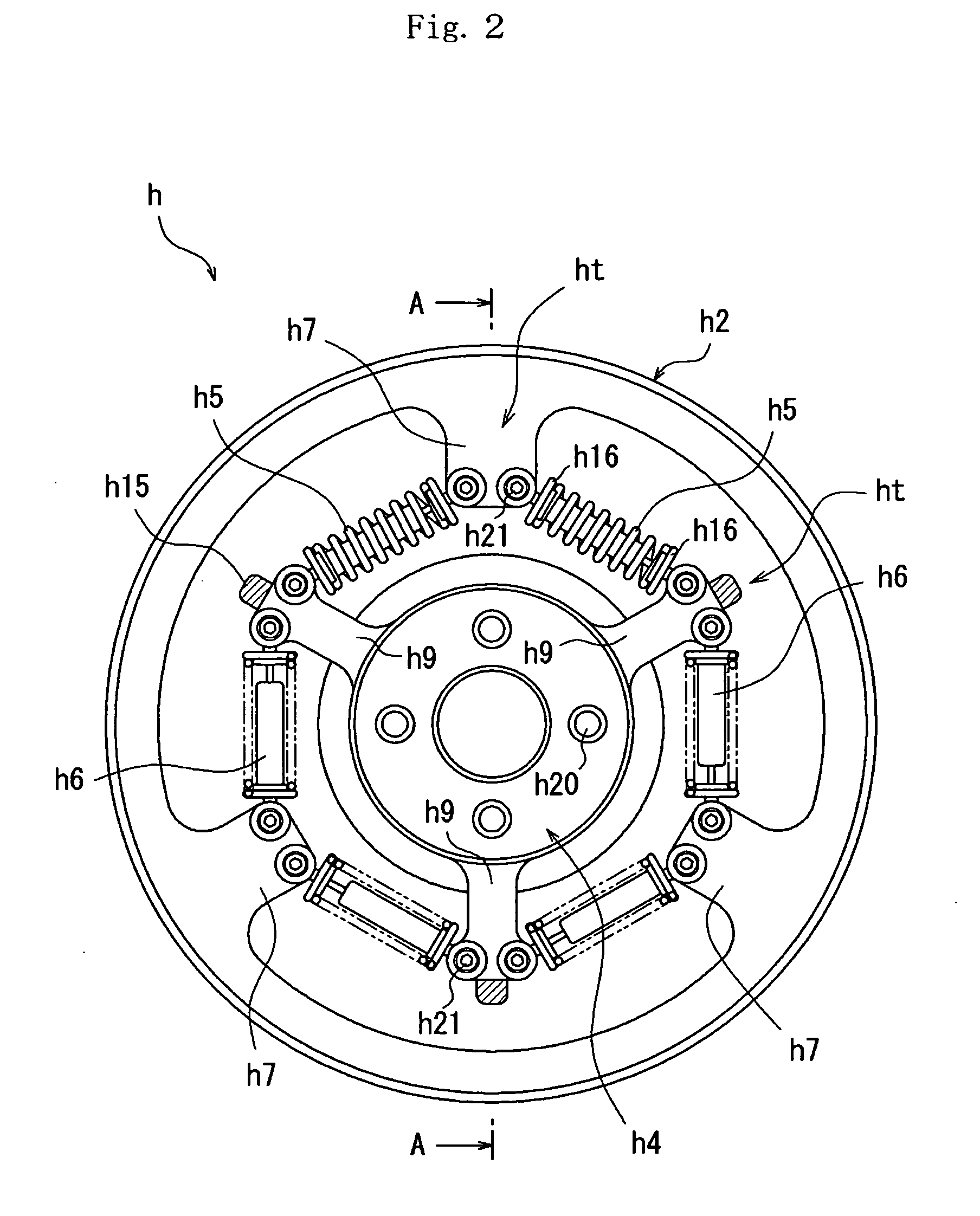

Eccentric thrust bearing assembly and a wheel with built-in suspension using the same

InactiveUS20070057480A1Increased decenterable rangeIncrease spaceRoller bearingsYielding couplingCircular discThrust bearing

An eccentric thrust bearing assembly mounted in a wheel with built-in suspension including: an outside wheel member including a rim portion to which a tire is mounted; an inside wheel member including a disk portion coupled with an axle; and an elastic member interposed between the outside wheel member and the inside wheel member, the bearing assembly permitting an eccentric relative movement between the wheel members while bearing an axial load applied between the wheel members.

Owner:JTEKT CORP +1

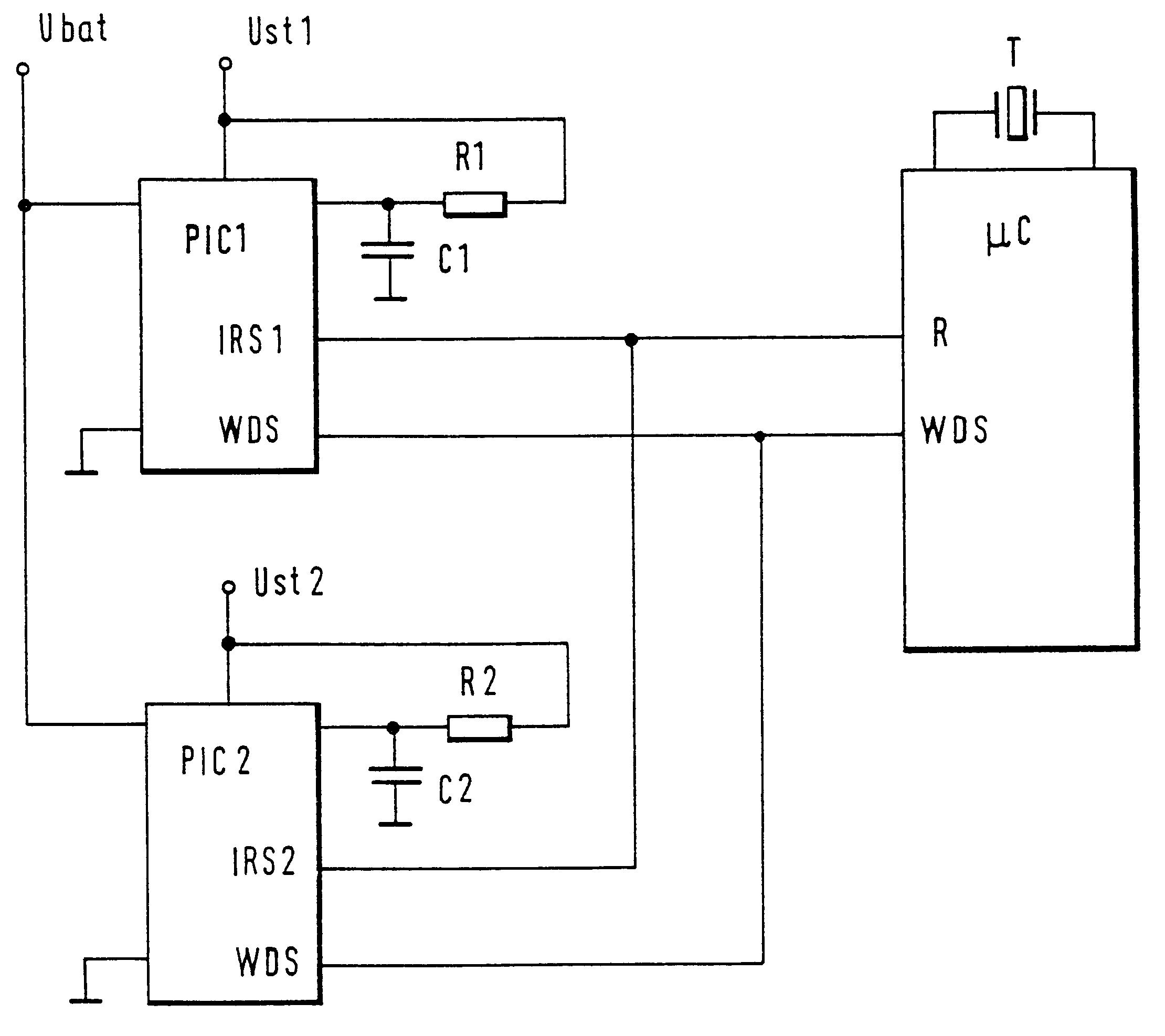

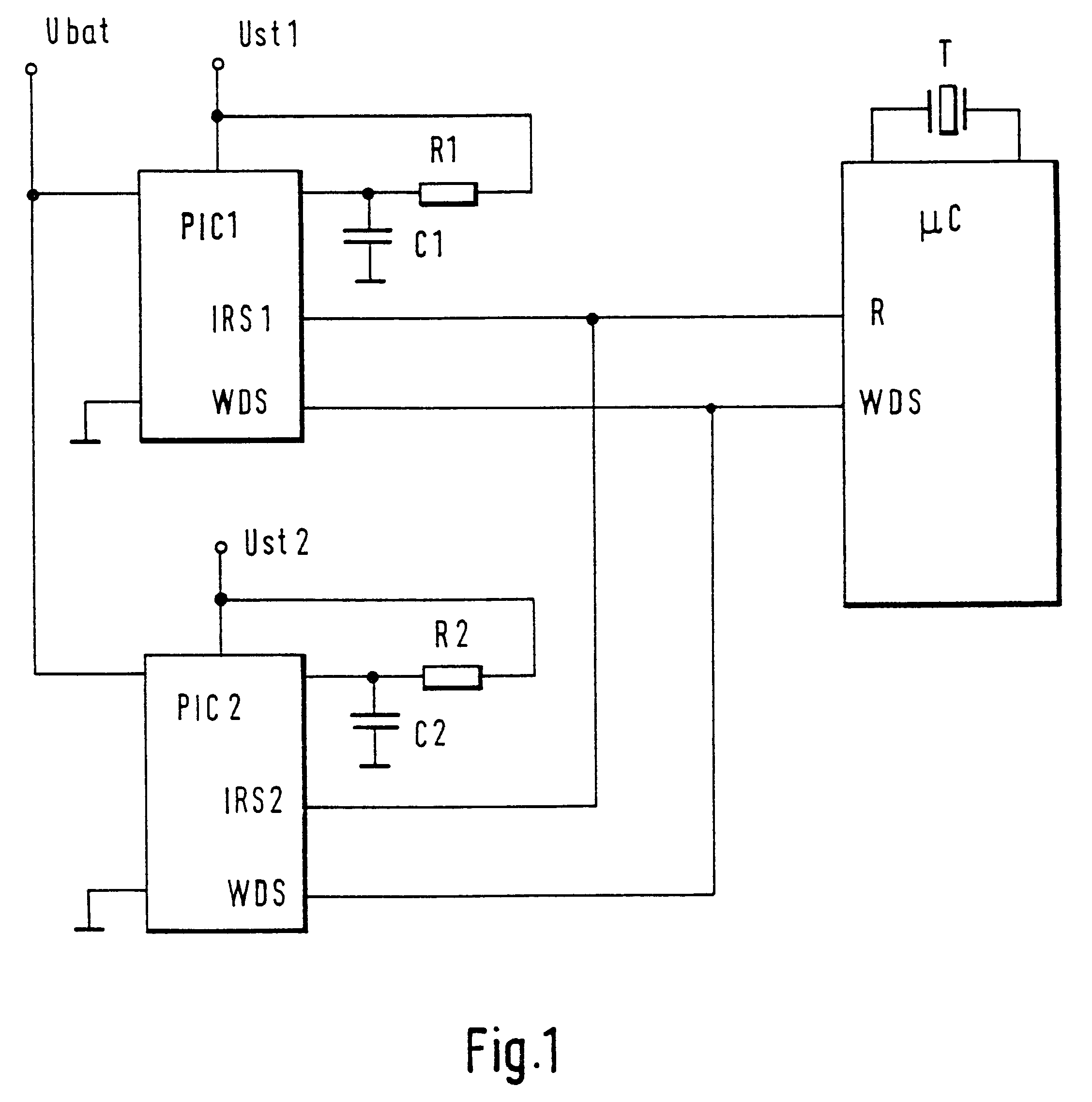

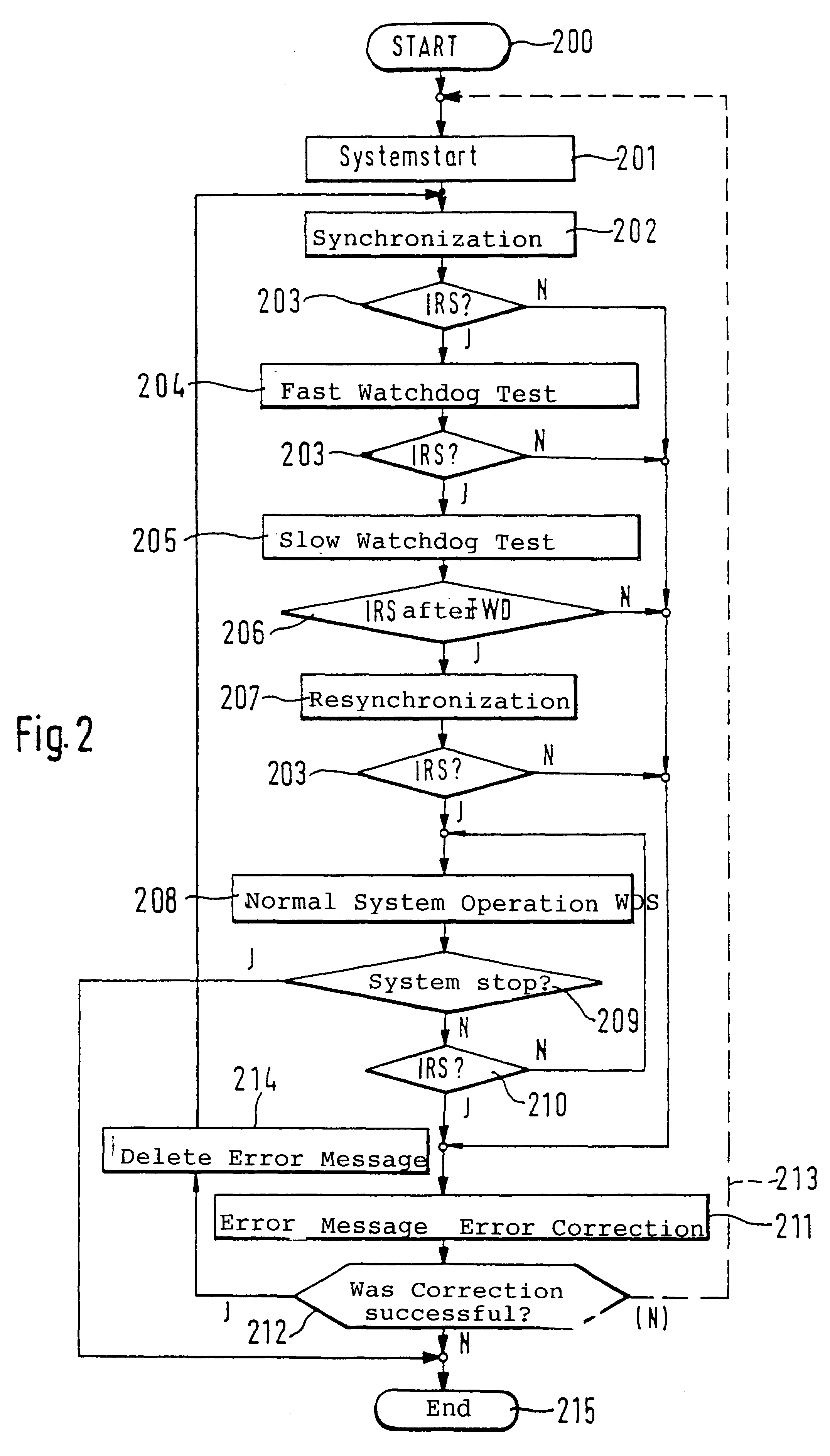

Method and device for synchronizing and testing a processor and a monitoring circuit

InactiveUS6675320B1GreatEnhanced advantageAnalogue computers for trafficHardware monitoringComputer hardwareLower limit

The invention relates to a method and apparatus for synchronizing at least one computer, having at least one monitoring circuit associated with this computer. The synchronization takes place through at least one transmitted signal (WDS) in the form of a double pulse from the computer (muC) to the peripheral components (PIC1, PIC2), which contain the monitoring circuits. To that end, shortly after the computer (muC) is started up at system start or after an HW reset, the signal (WDS) is sent to the at least one peripheral component (PIC1, PIC2). After this, the upper and lower limit of the signal sequence (WDS) to be regularly transmitted by the computer for the monitoring circuit are tested and therefore the function of the monitoring circuits is tested. As with the synchronization, the testing takes place with a reaction of the monitoring circuits by means of at least one acknowledgement signal (IRS1, IRS2, R).

Owner:ROBERT BOSCH GMBH

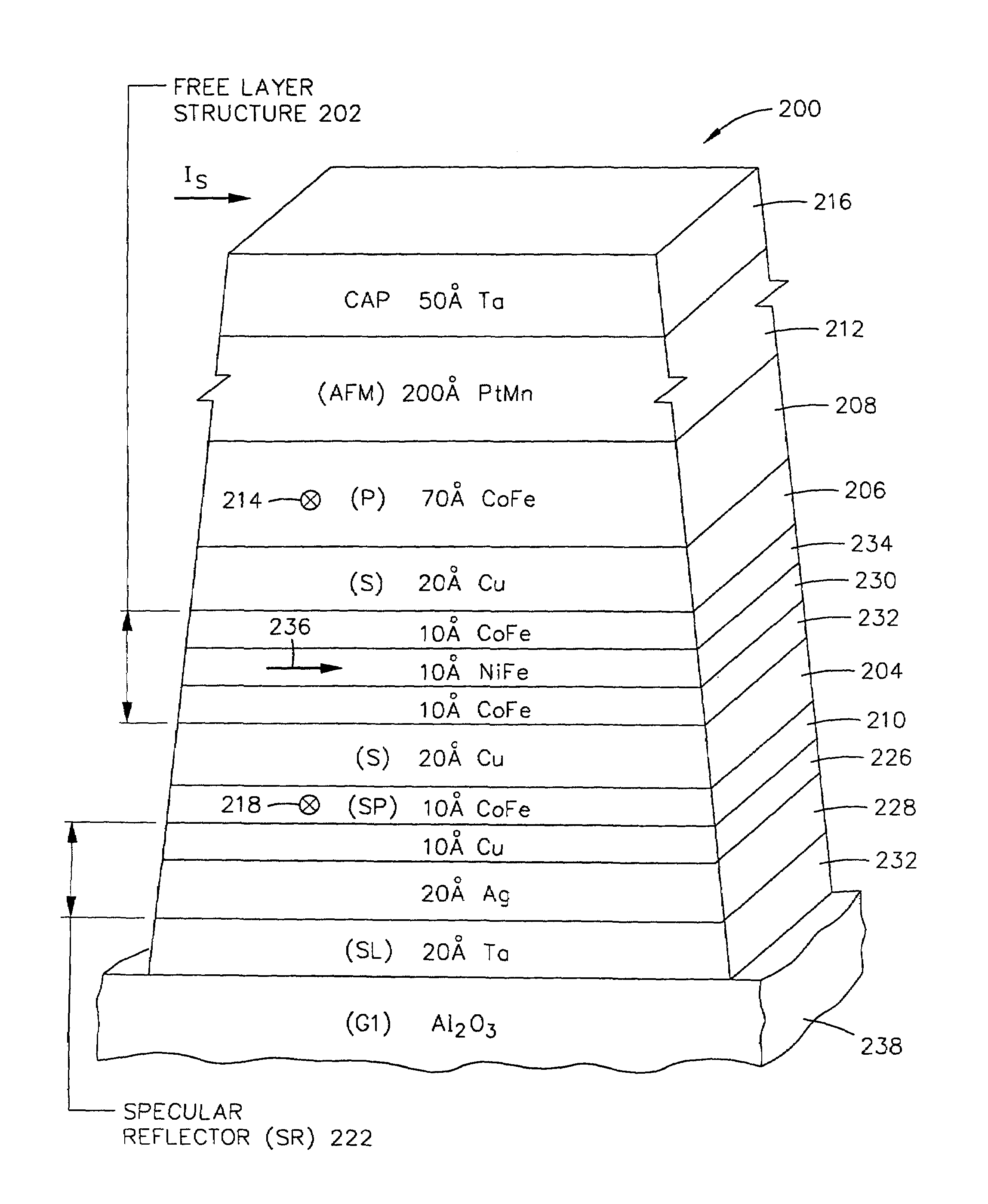

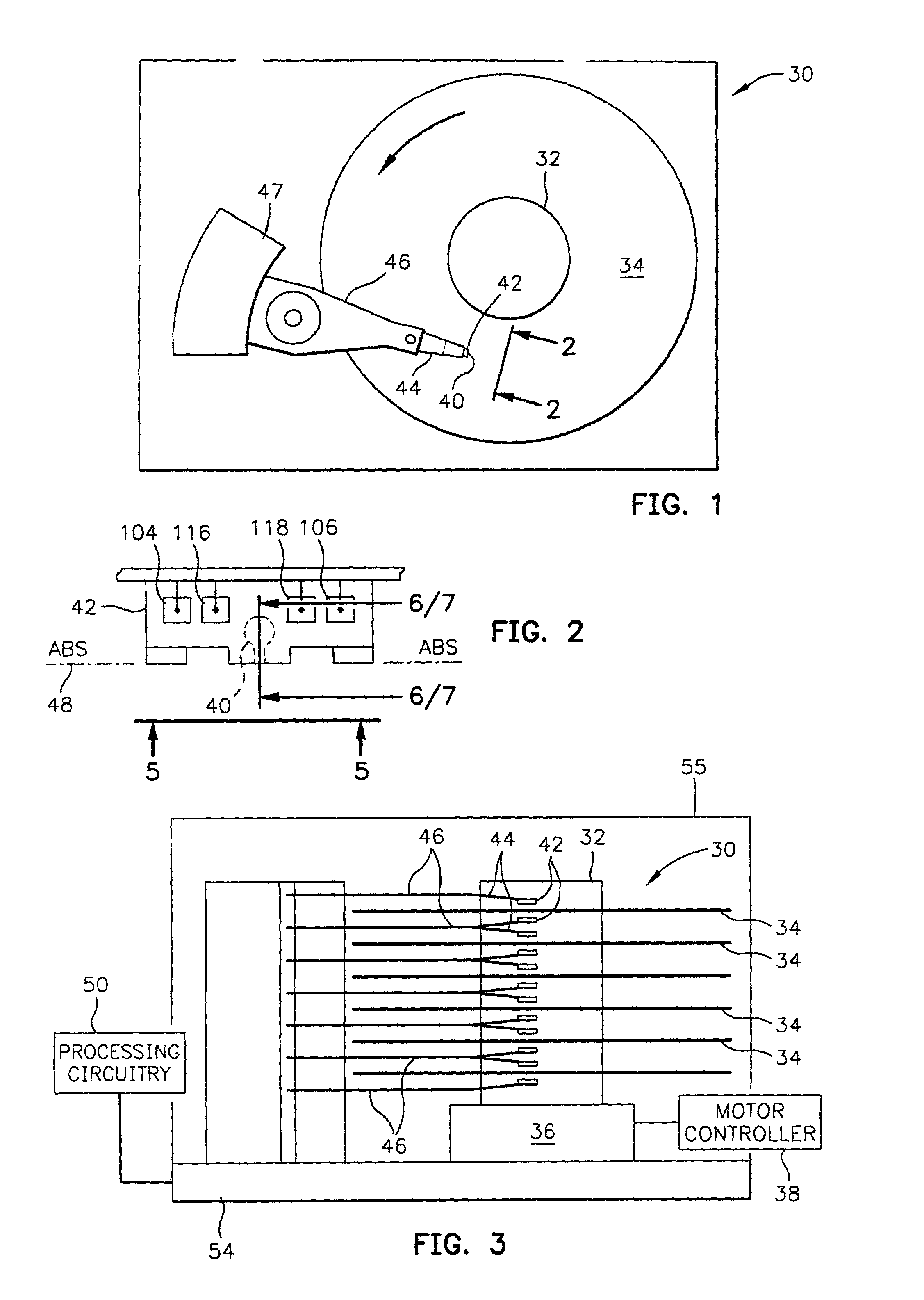

Method of making a dual GMR read head with self-pinned layer and specular reflector

InactiveUS6983530B2GreatReduction factorManufacture head surfaceNanomagnetismMean free pathSpecular reflection

A dual GMR or dual spin valve sensor has a self-pinned layer which has its magnetic moment pinned perpendicular to an air bearing surface by sense current fields from conductive layers in the dual spin valve sensor when a sense current is conducted therethrough. This scheme eliminates one of the antiferromagnetic pinning layers which is typically employed in a dual GMR or dual spin valve sensor. The self-pinned layer is thin so that its demagnetization field will not be greater than the sense current fields acting thereon. Because of the thinning of the self-pinned layer the spin valve effect of the spin valve sensor is degraded by scattering of conduction electrons at the boundary of the self-pinned layer. In order to overcome this problem a specular reflector layer is employed in contact with the self-pinned layer for reflecting the conduction electrons back into a mean free path of conduction electrons so that the spin valve effect on the self-pinned layer side of the spin valve sensor can be added to another spin valve effect on the other side of the free layer structure for providing a double spin valve effect with an improved read gap, as compared to prior art dual spin valve sensors.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

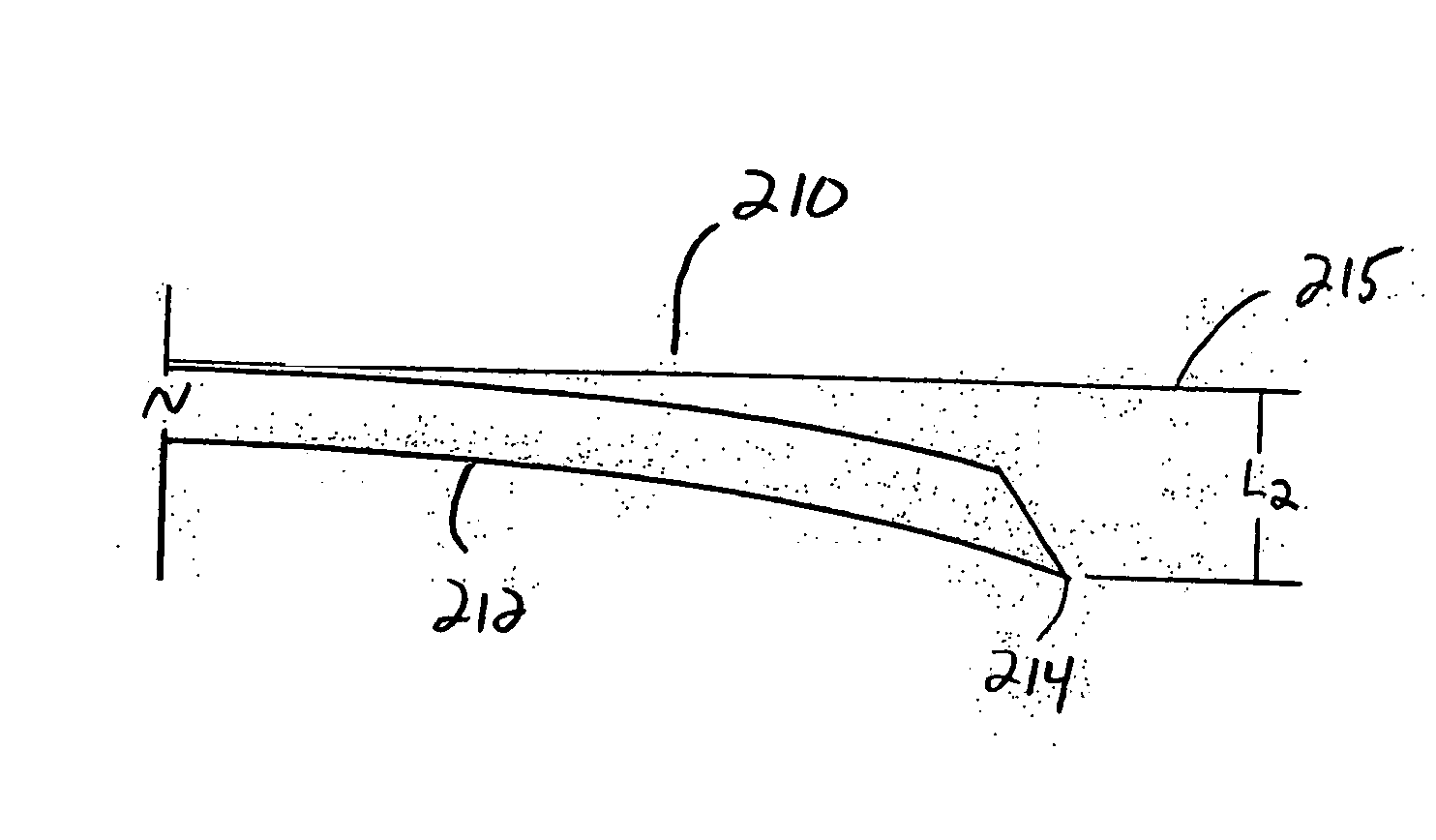

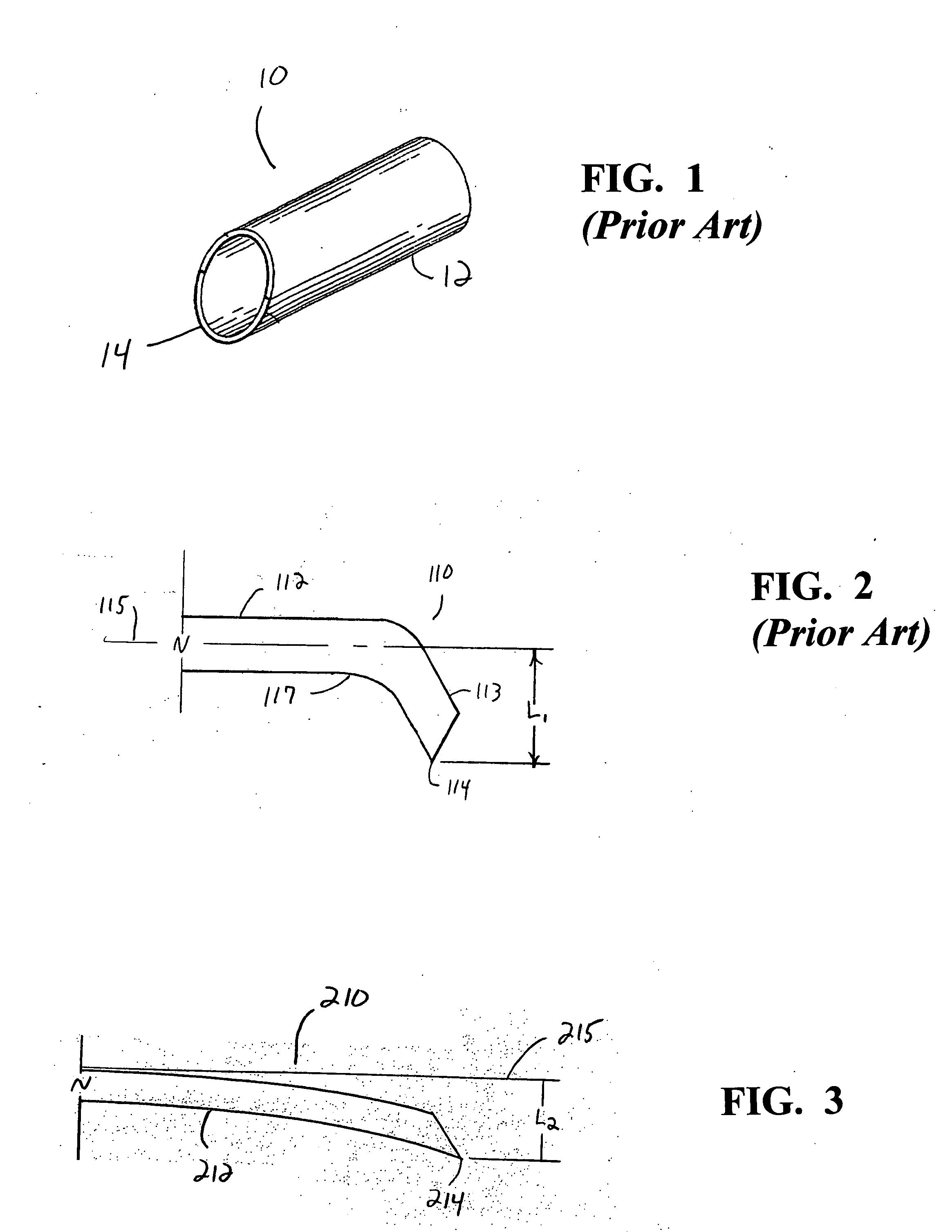

Phacoemulsification tip

A phacoemulsification tip having an arched or curved shaft. Such a feature serves to produce more efficient cutting during torsional vibration of the tip while maintaining a greater space between the distal end of the tip and the posterior capsule.

Owner:NOVARTIS AG

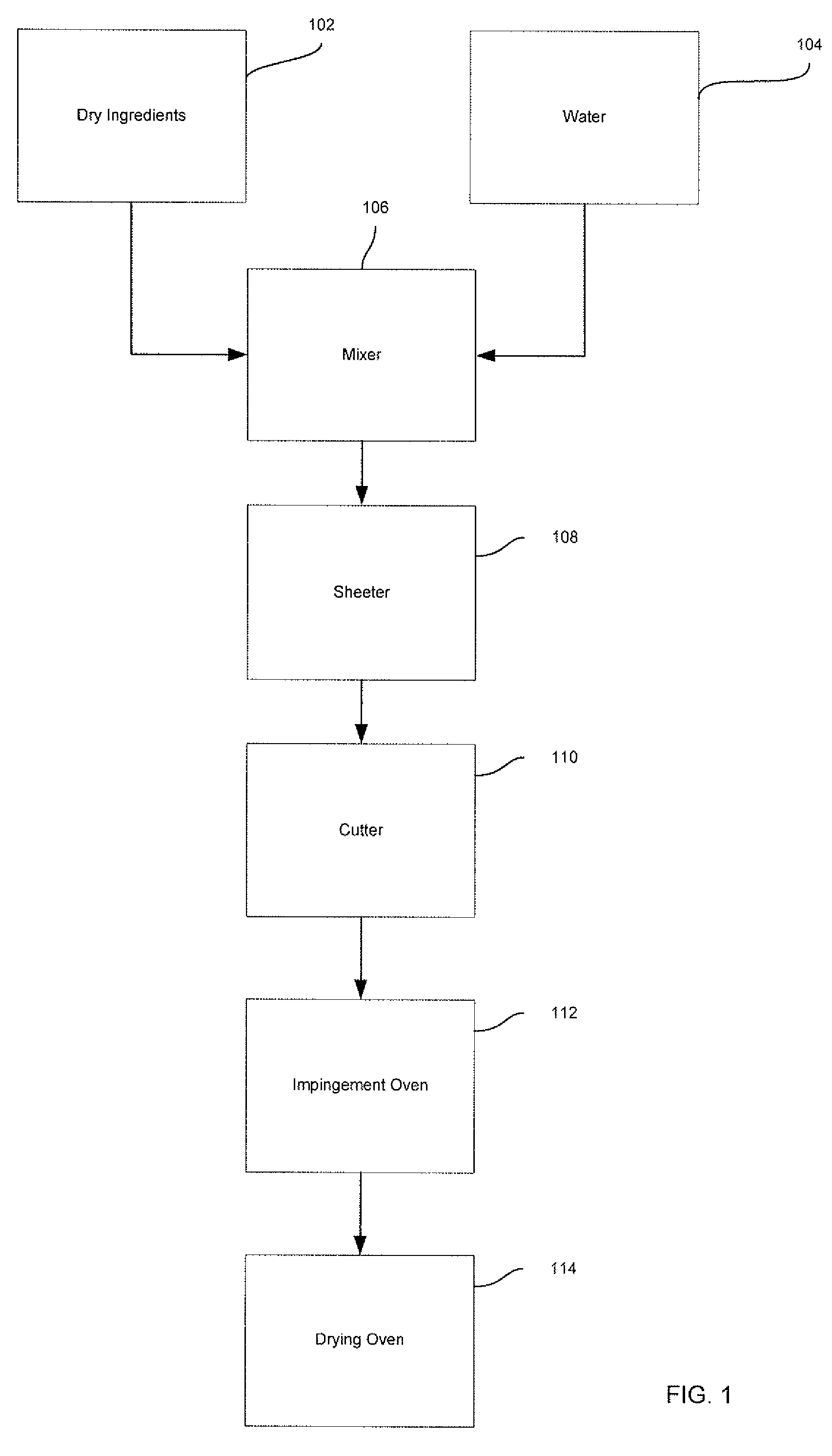

Baked Nut Snack Chip

InactiveUS20080102182A1Increase contentImproves Structural IntegrityDough treatmentBaking mixturesAdditive ingredientSnack food

Owner:FRITO LAY NORTH AMERICA INC

Method for operating an internal combustion engine

ActiveUS20070050124A1Low accuracyCost-effective and simple to installAnalogue computers for vehiclesElectrical controlCombustion chamberEngineering

In a method for operating an internal combustion engine, a first data quantity is derived based on a signal of a first sensor which detects the pressure in a first combustion chamber of a plurality of combustion chambers, and a second data quantity is derived based on a signal of a second sensor, which second data quantity is a function of the pressure variation in at least one of the plurality of combustion chambers. The first data quantity and the second data quantity are functions of the pressure variation in the same combustion chamber, and a drift of the second sensor is ascertained from a change over time in the second data quantity with respect to the first data quantity.

Owner:ROBERT BOSCH GMBH

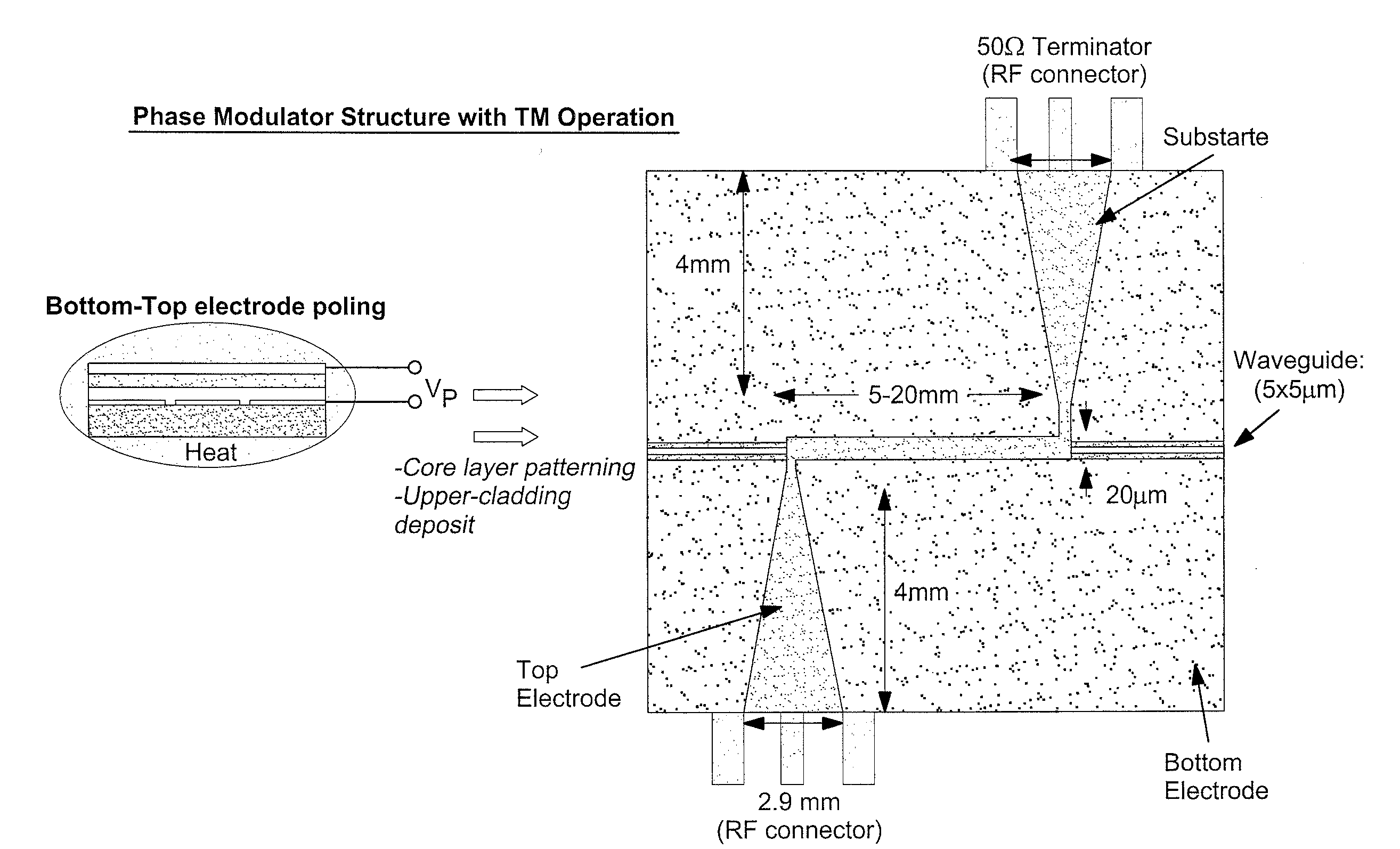

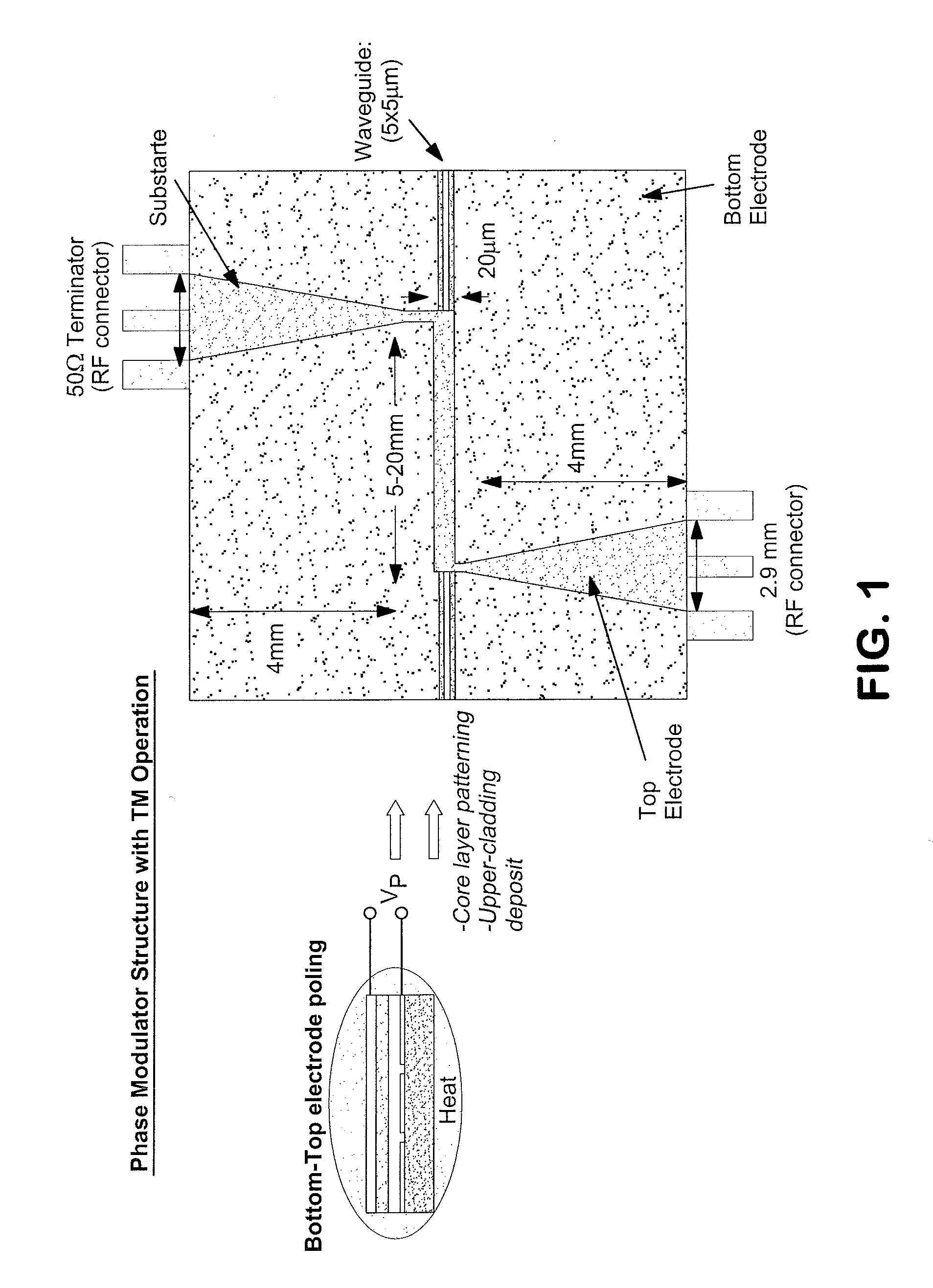

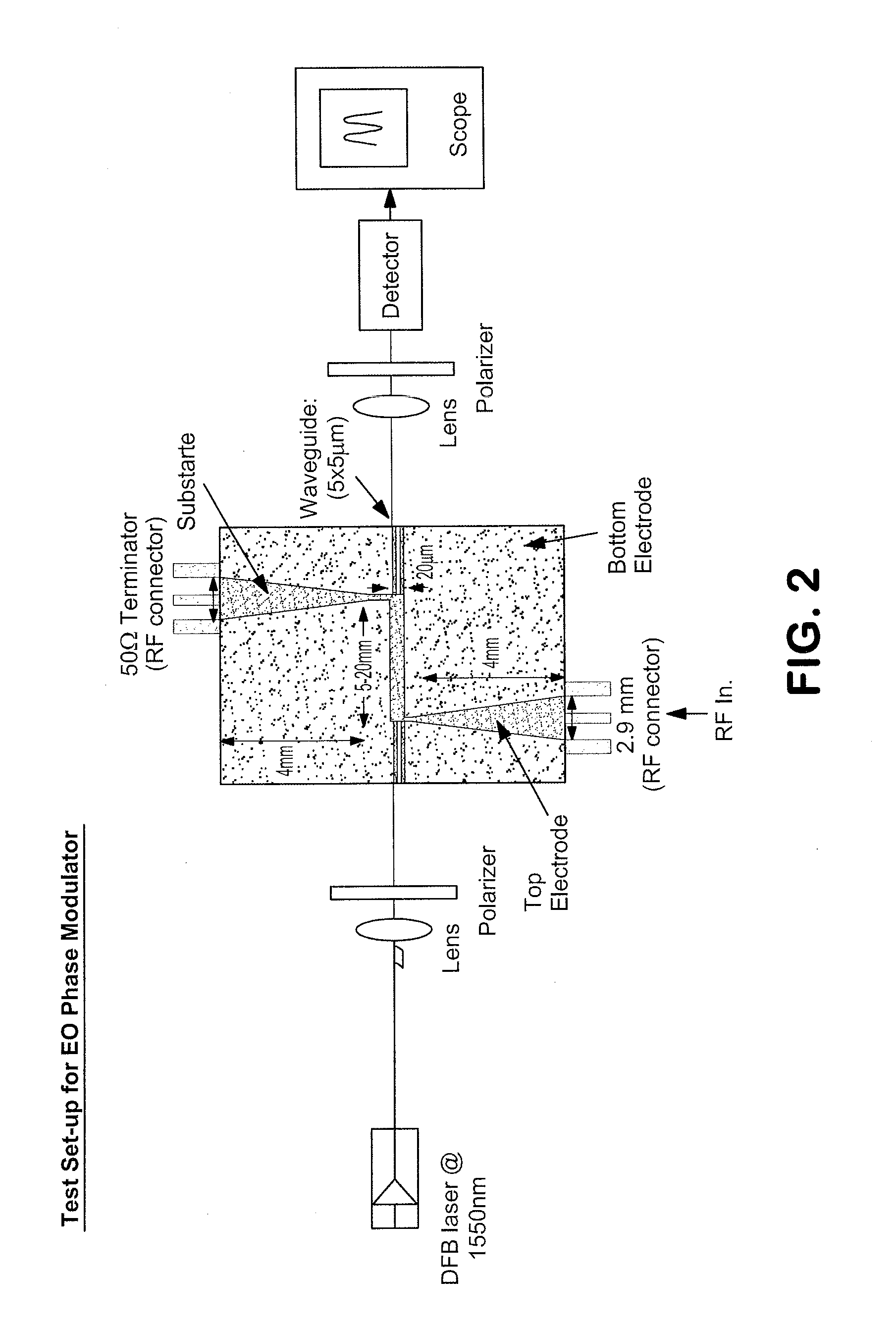

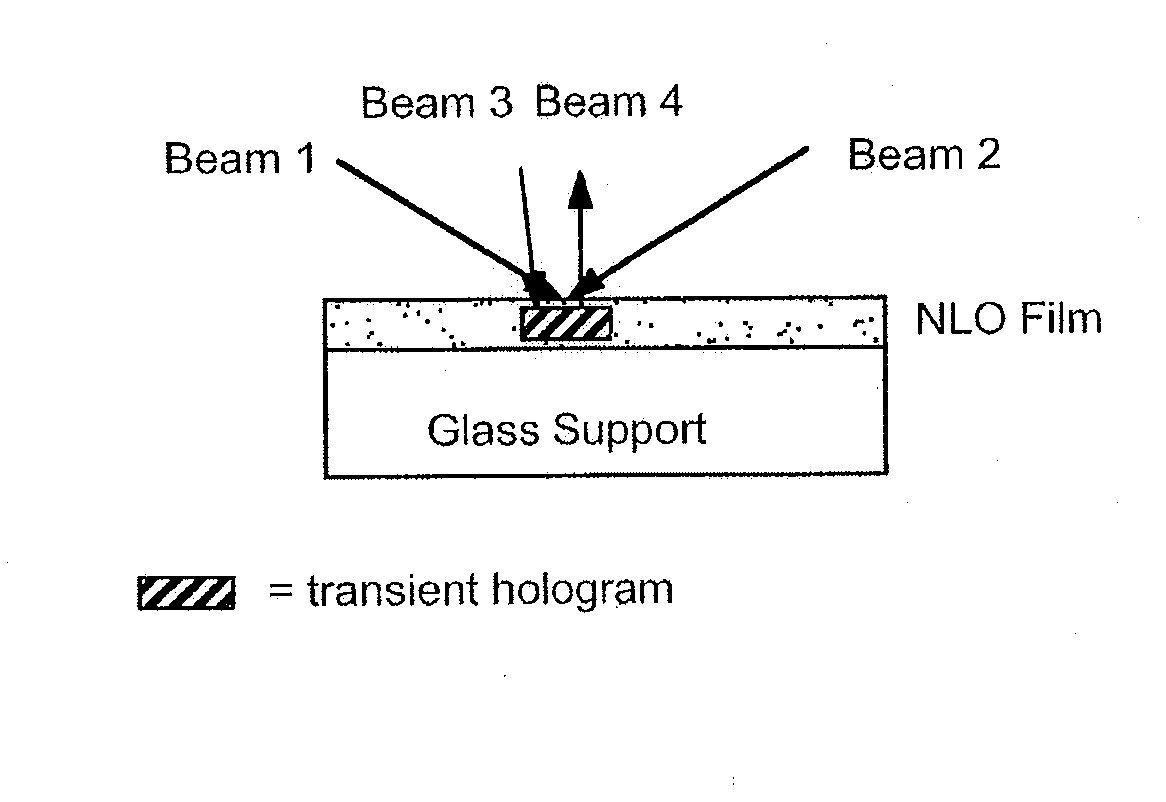

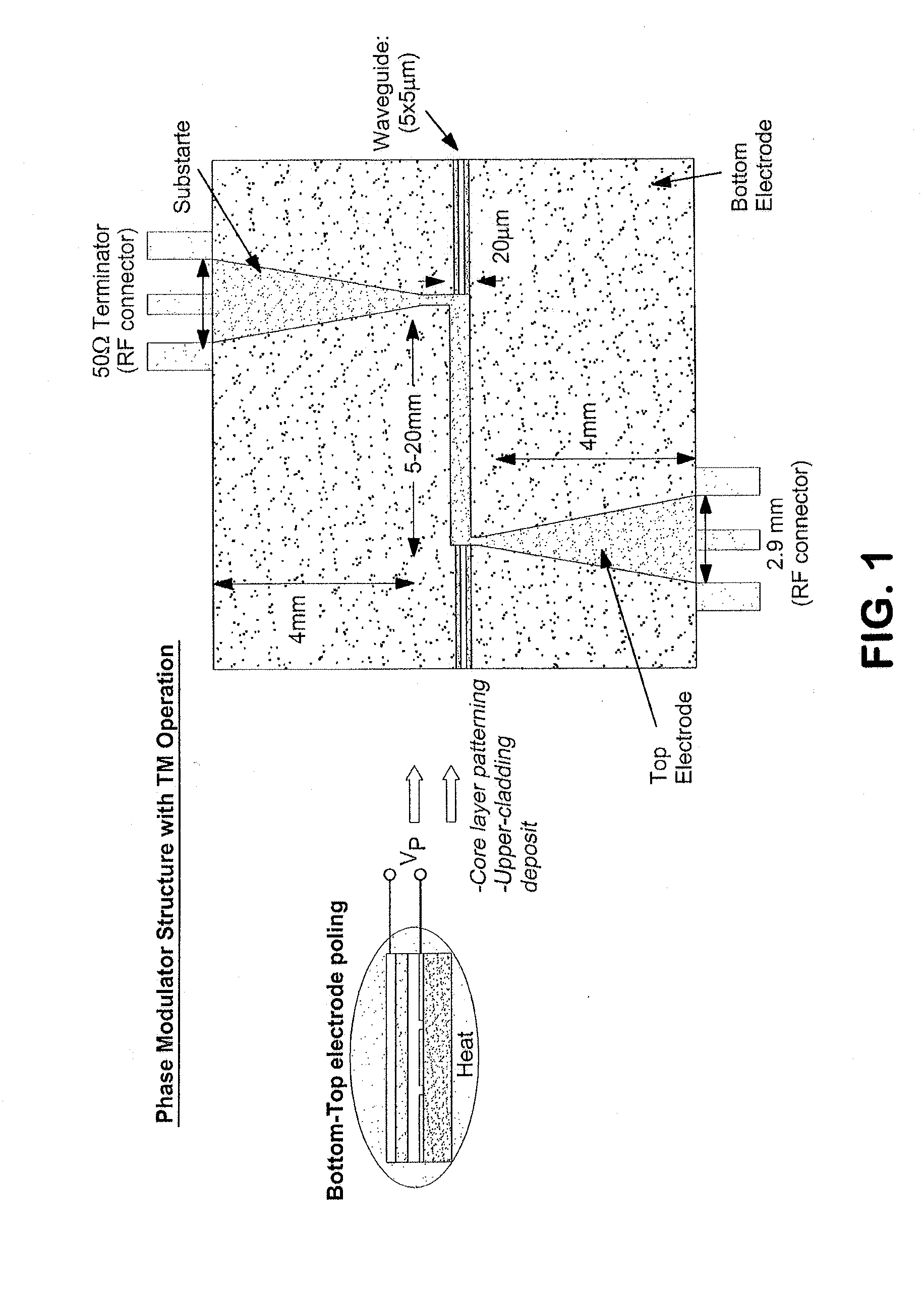

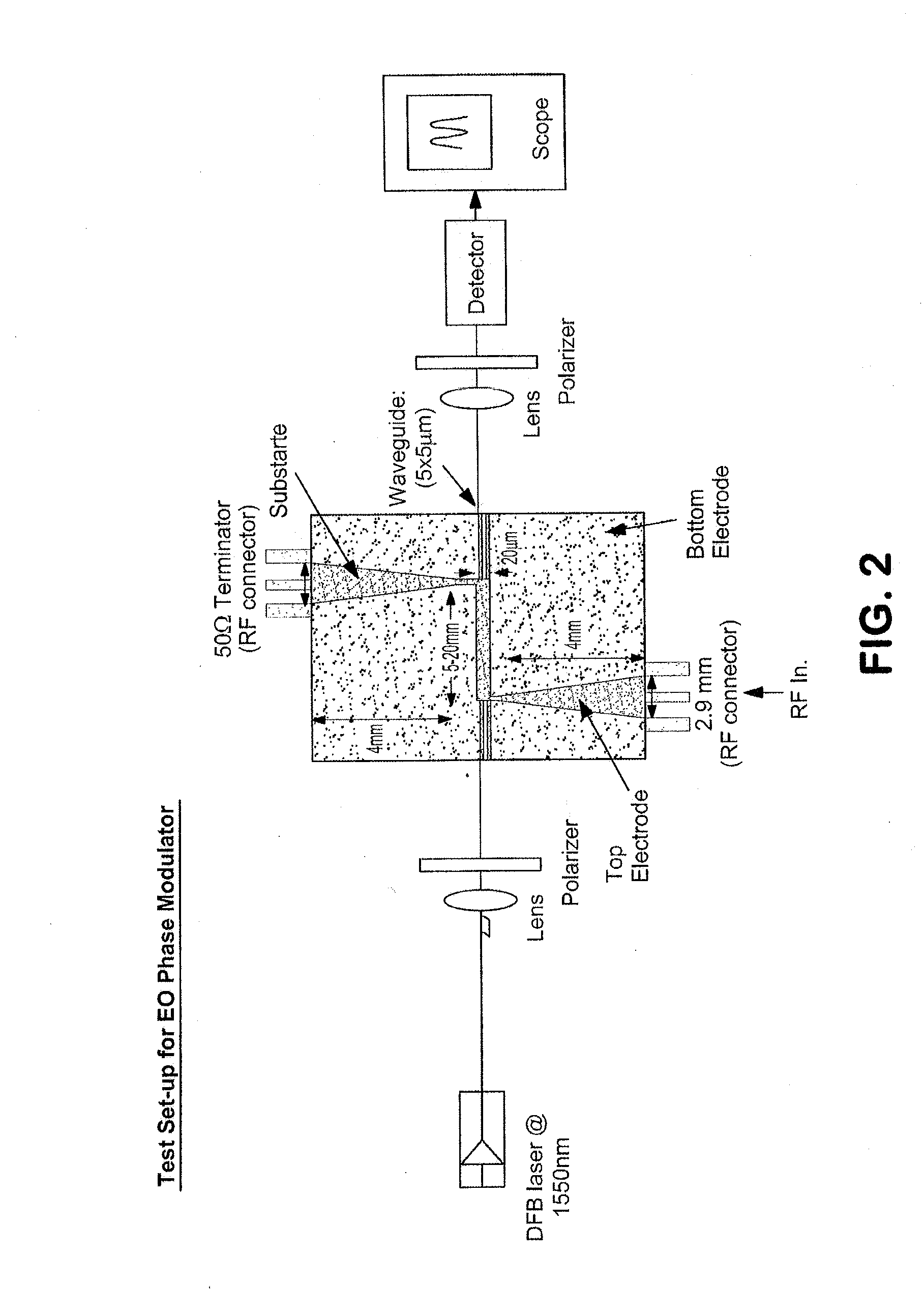

Stable free radical chromophores, processes for preparing the same, nonlinear optic materials and uses thereof in nonlinear optical applications

InactiveUS20120267583A1GreatImprove rigidityOrganic chemistryFinal product manufactureNonlinear optical materialChromophore

Nonlinear optic chromophores comprising stabilized radical structures, mixtures thereof, methods for their production, nonlinear optical materials containing such chromophores, and the use of such materials in electro-optic, solar conversion, photovoltaic and all-optical nonlinear devices are described.

Owner:LIGHTWAVE LOGIC INC

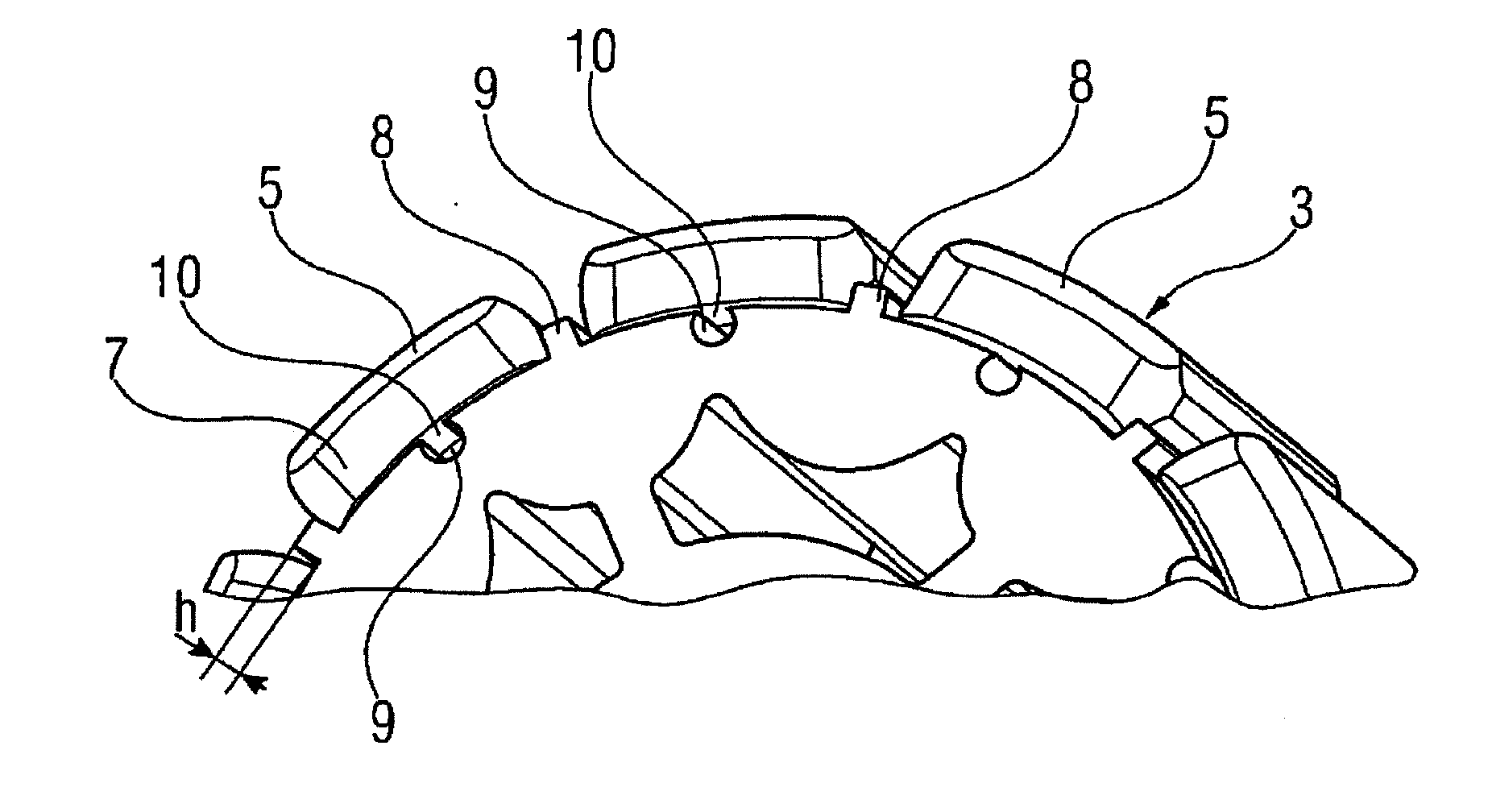

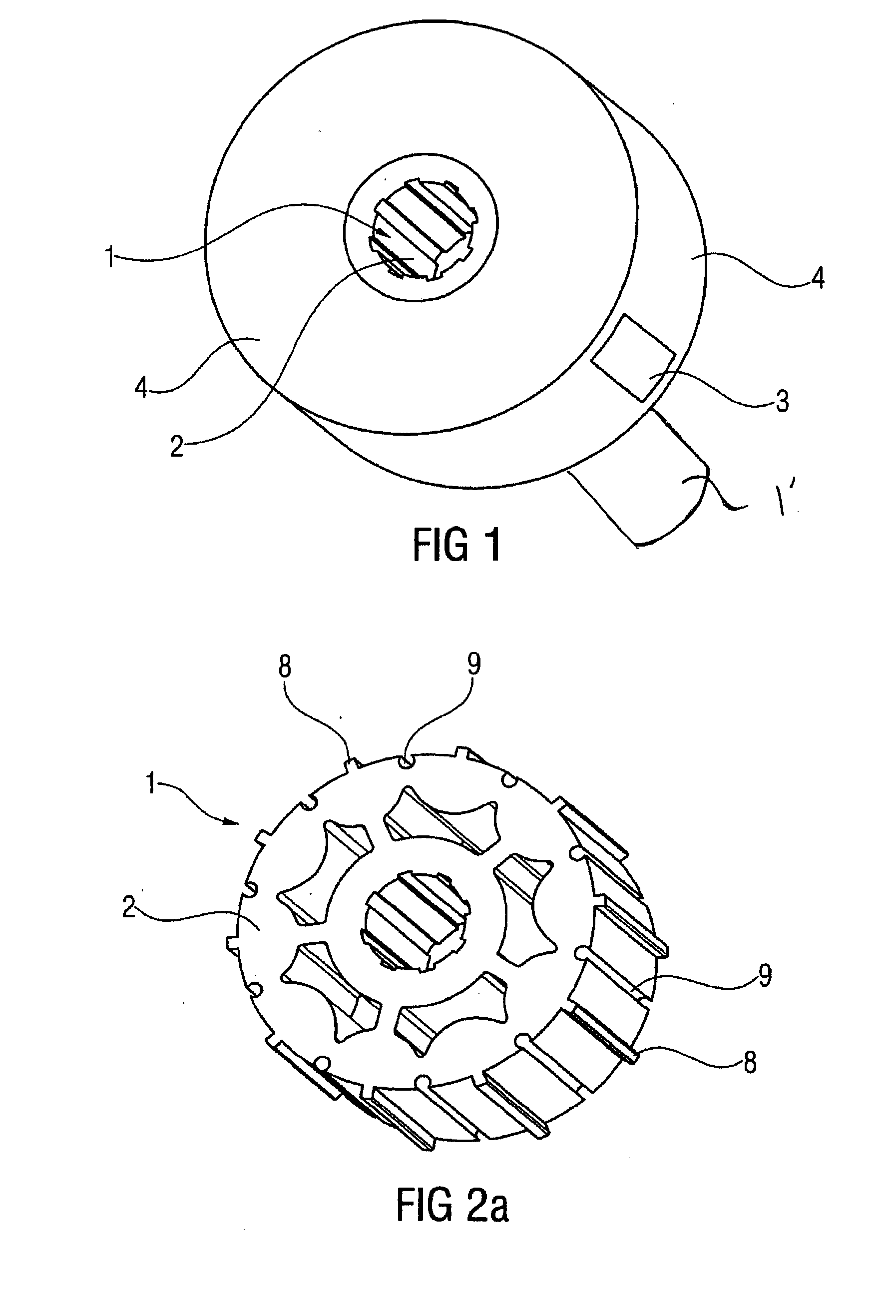

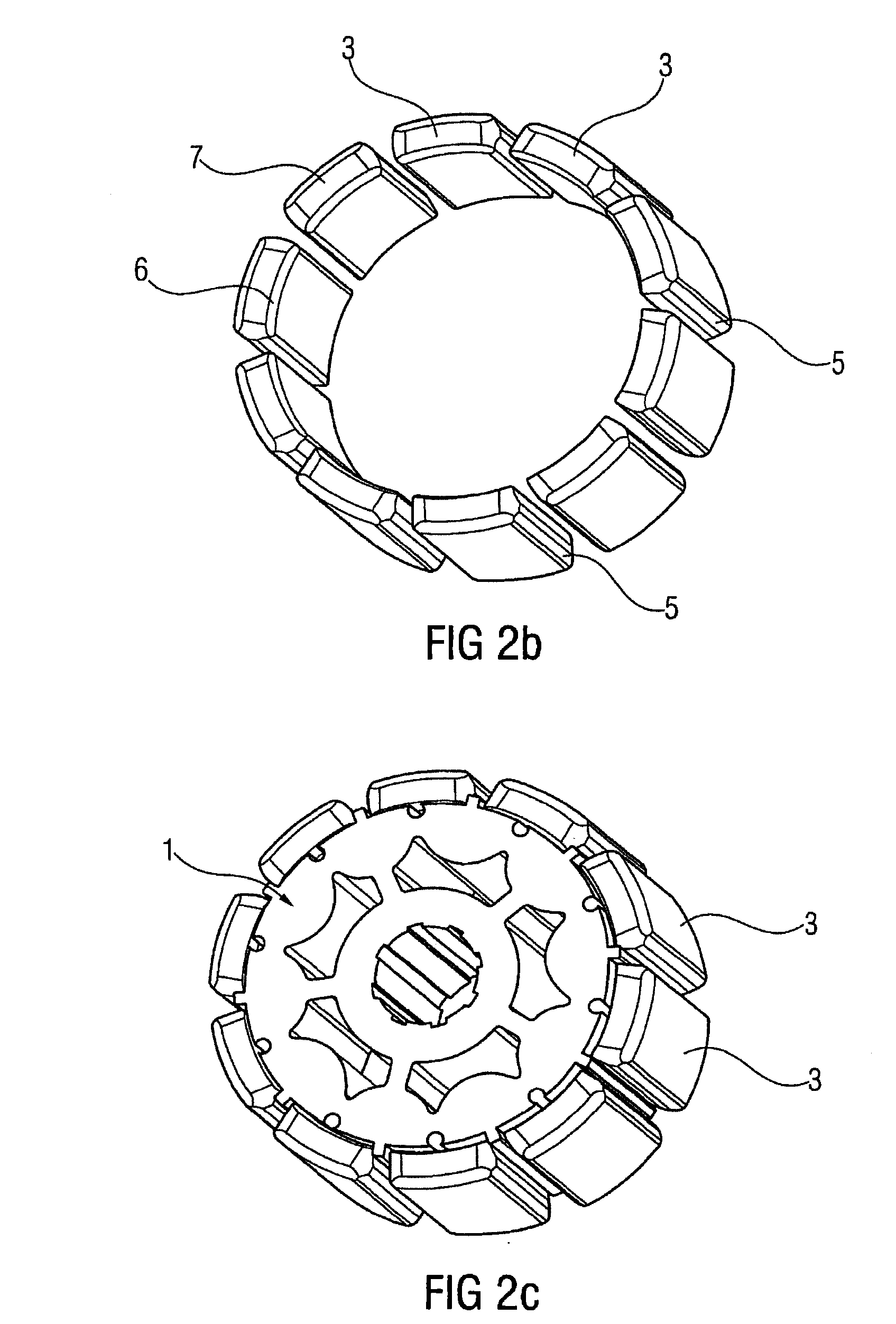

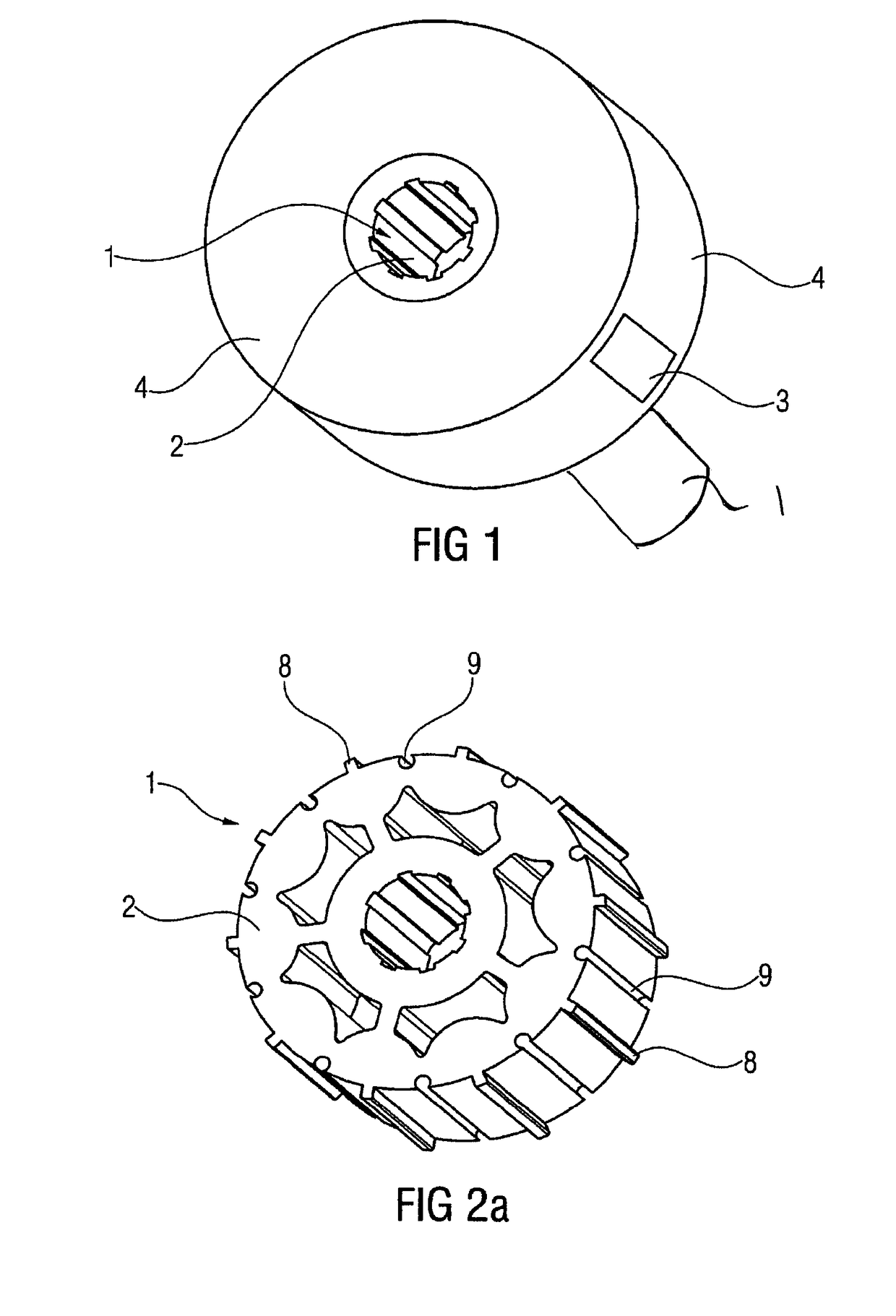

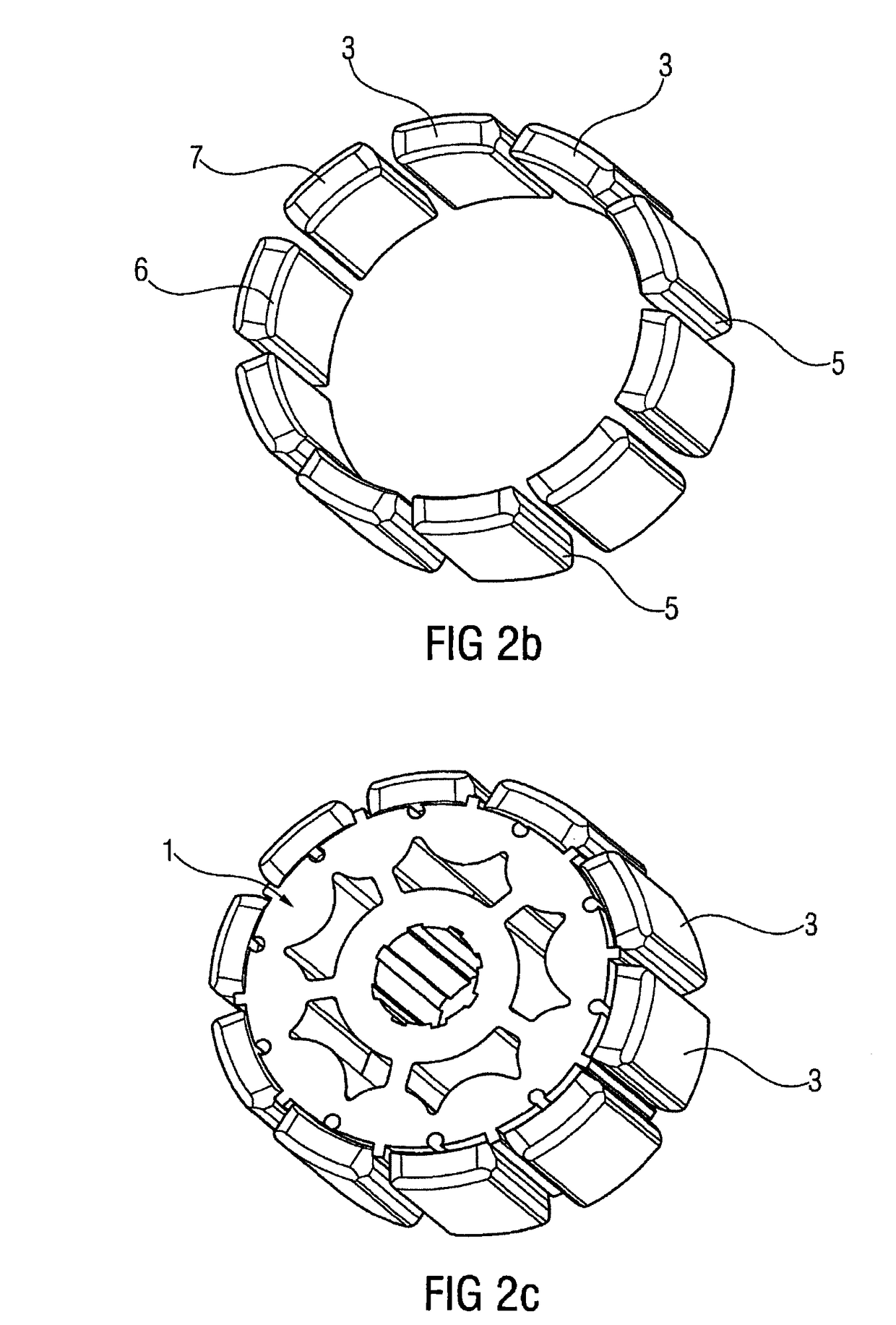

Rotor of an electric motor and method for producing the rotor

ActiveUS20150303752A1Easy to produceReduce usageMagnetic circuit rotating partsMagnetic circuit characterised by insulating materialsEngineeringMagnet

A rotor of an electric motor includes a laminated armature core, a shaft, magnets arranged on the circumference of the laminated armature core, and a plastic overmold. The laminated armature core has at least one associated channel on the circumference of the laminated armature core for each magnet. The channels extend parallel to the shaft, and the laminated armature core has radially oriented webs on the circumference. The webs (8) extend parallel to the shaft and a magnet (9) is arranged between each pair of webs (8), and the plastic overmold (4) encloses the laminated armature core (1) and the magnets (3) to such an extent that only the radial outer face of the magnets (3) is free of plastic (4).

Owner:VITESCO TECH GERMANY GMBH

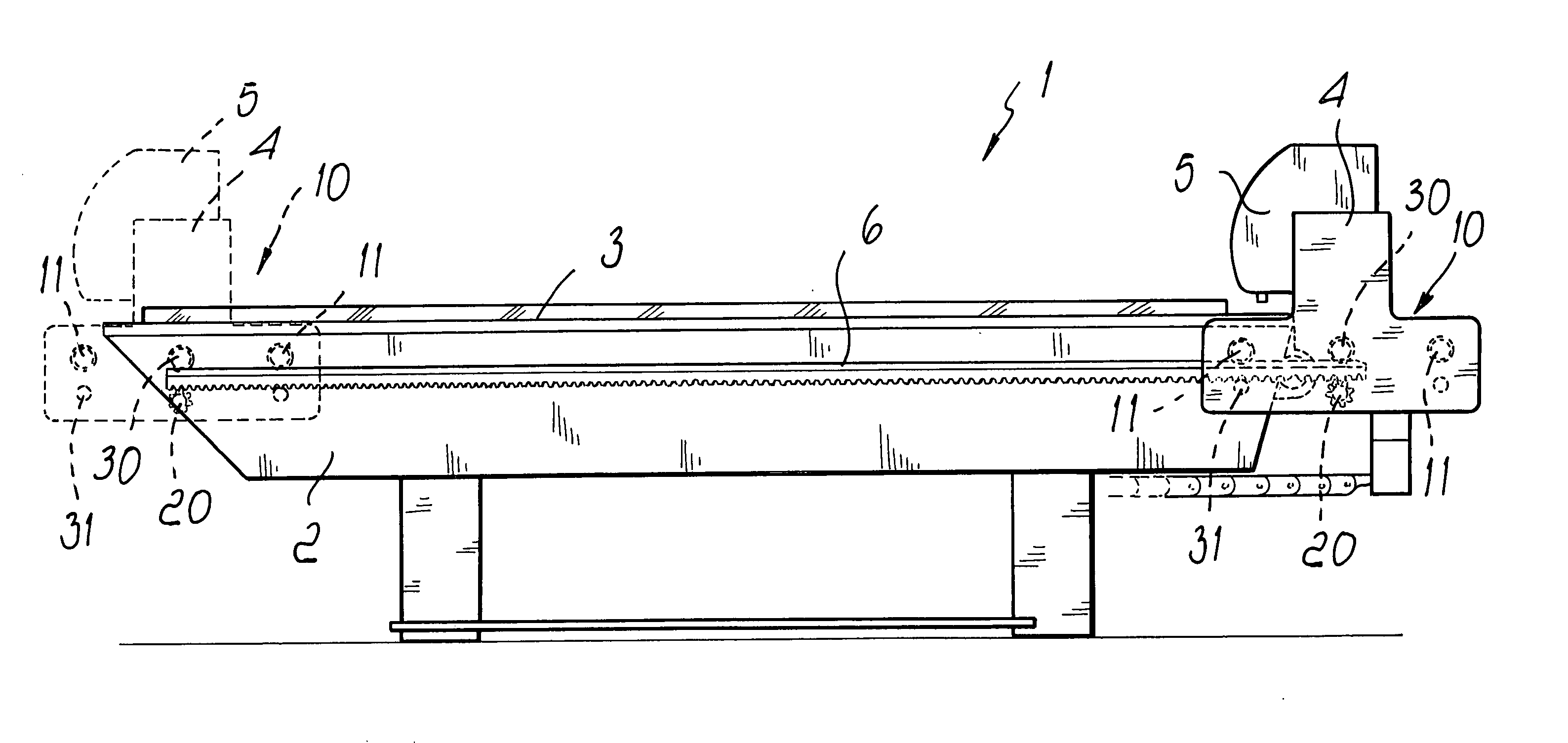

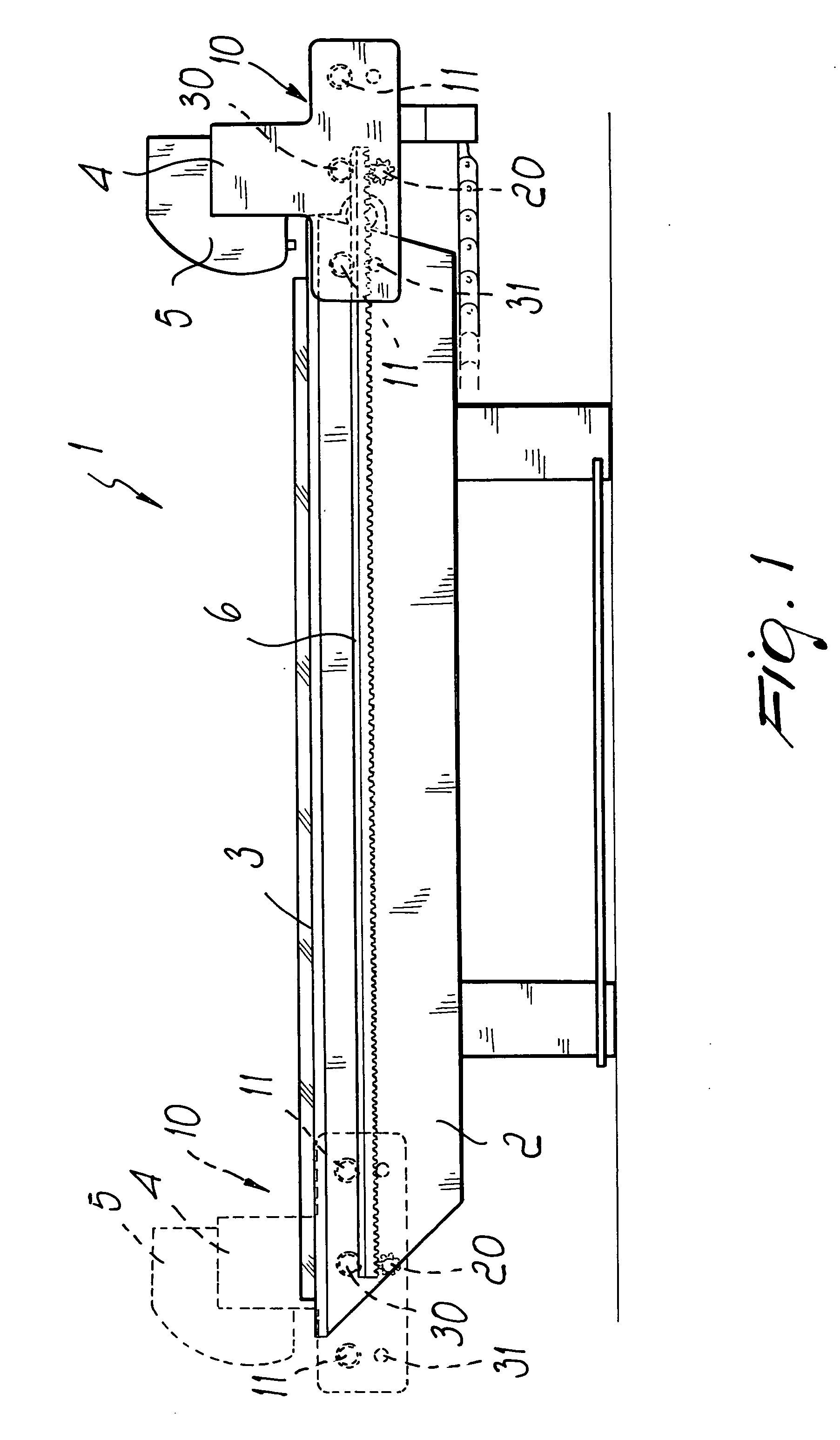

Glass pane cutting table allowing useful cutting dimensions optimization

InactiveUS20050217451A1Reduced dimensionFine surfaceLarge fixed membersGlass severing apparatusTruckMechanical engineering

A cutting table particularly for glass panes and the like, with cutting optimizing of the useful cutting dimensions, which comprises a frame forming cutting bed on which a cutting bridge is movable that supports a cutting head and can slide on guides fixed to the frame by means of sliding trucks provided with two mutually spaced upper wheels engageable with the upper part of the guides, a central upper wheel, which is arranged between the upper wheels, and at least two lower abutment elements, engageable with the lower part of the guides that are positioned on opposite sides with respect to the central upper wheel.

Owner:Z BAVELLONI

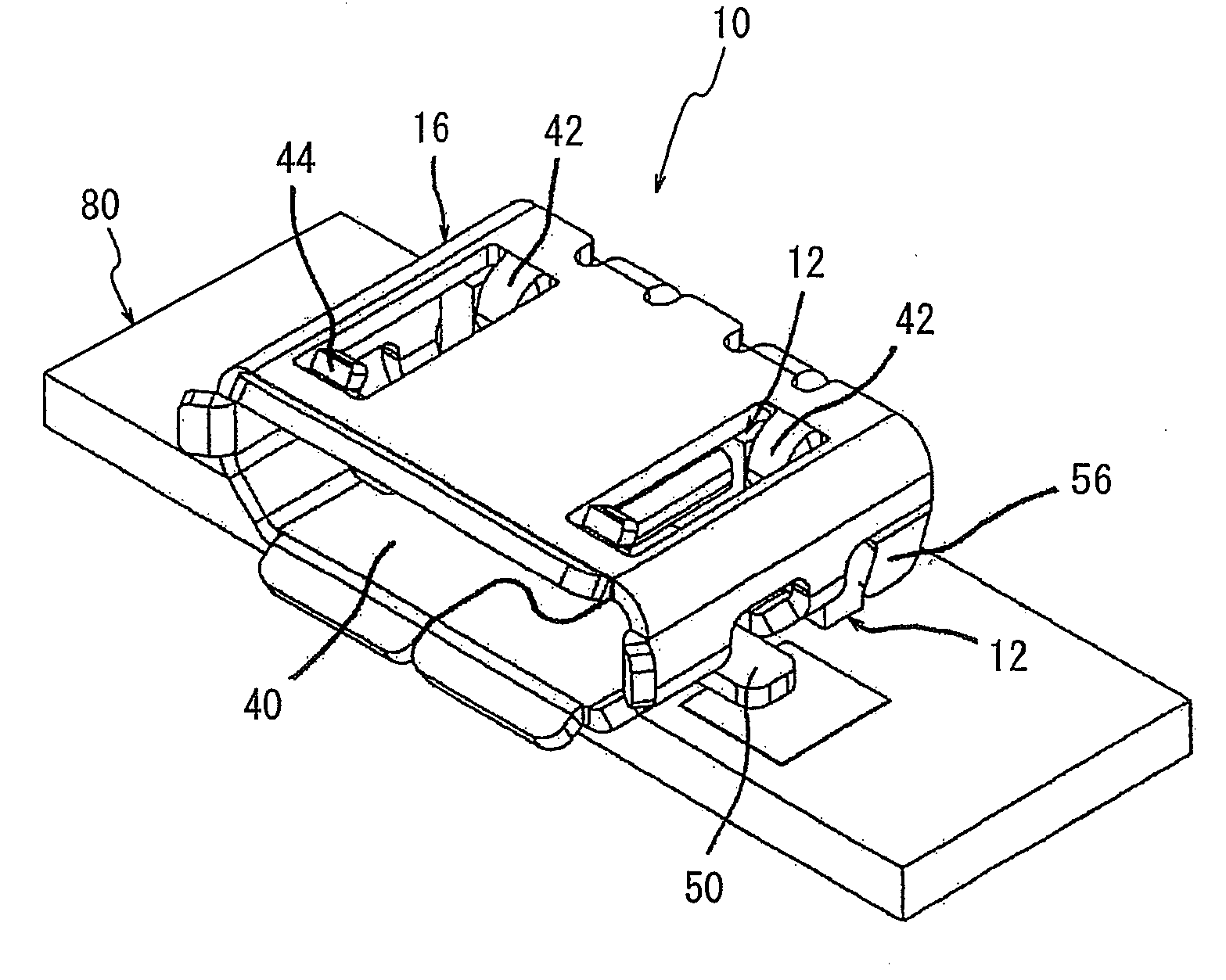

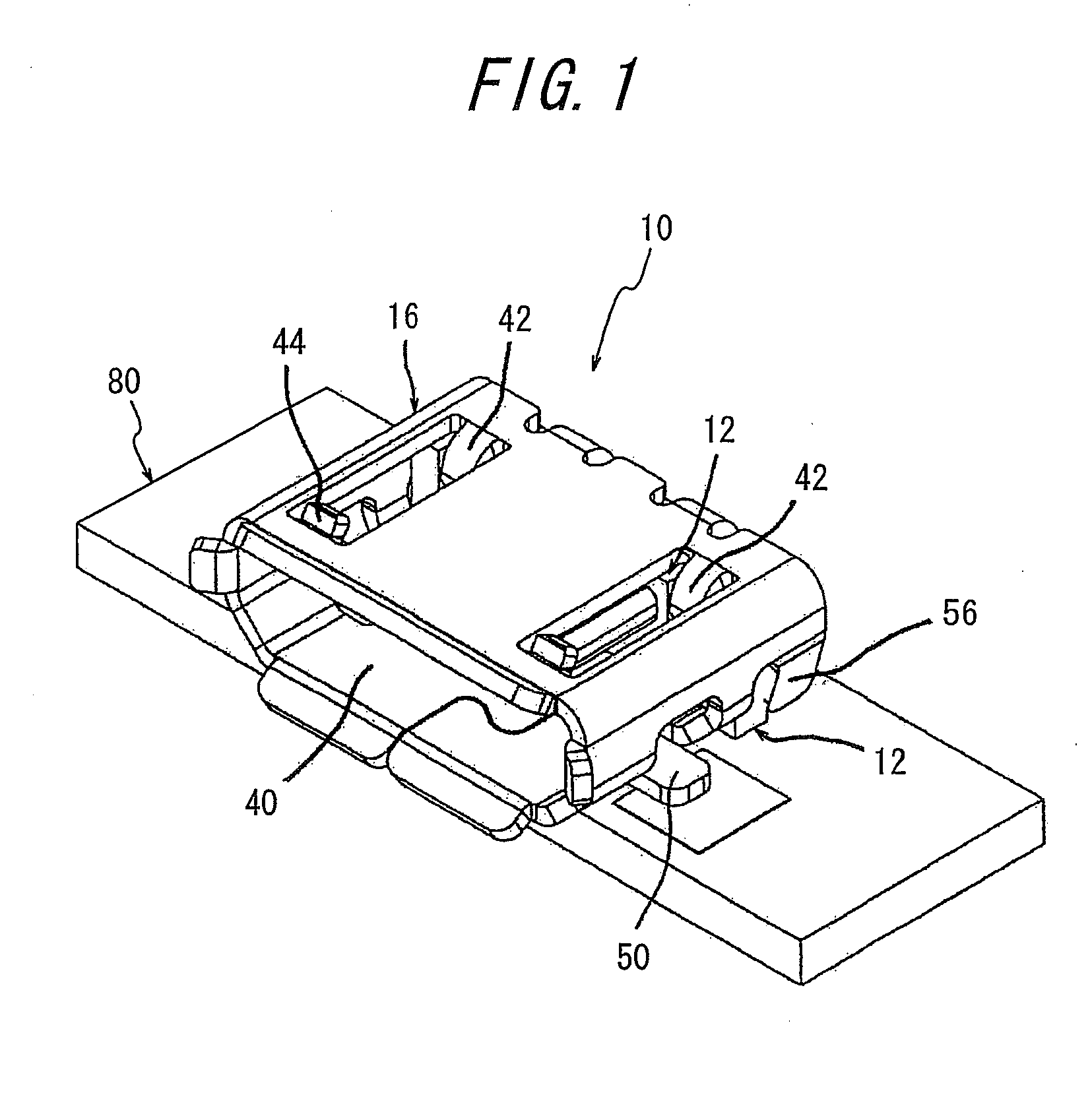

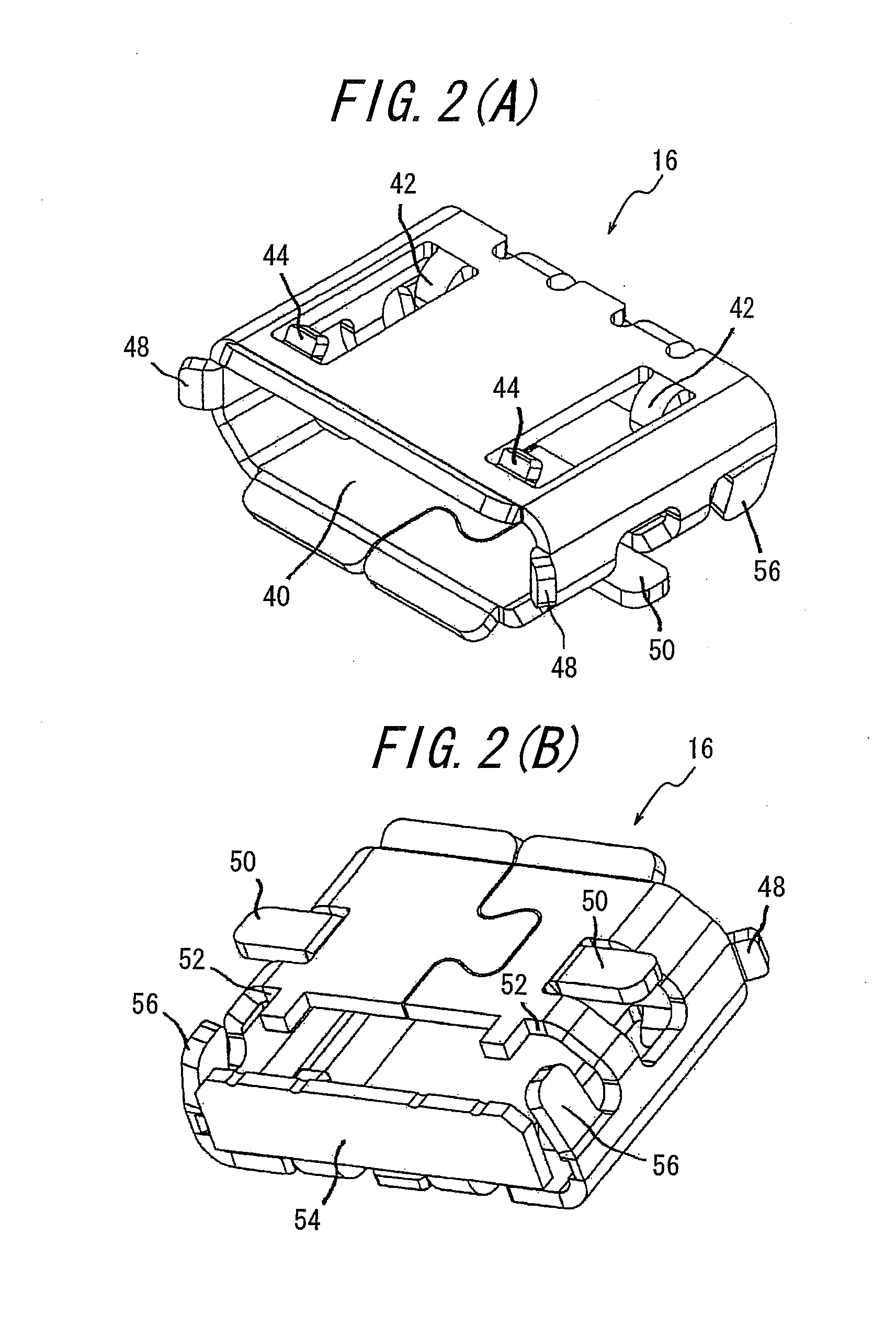

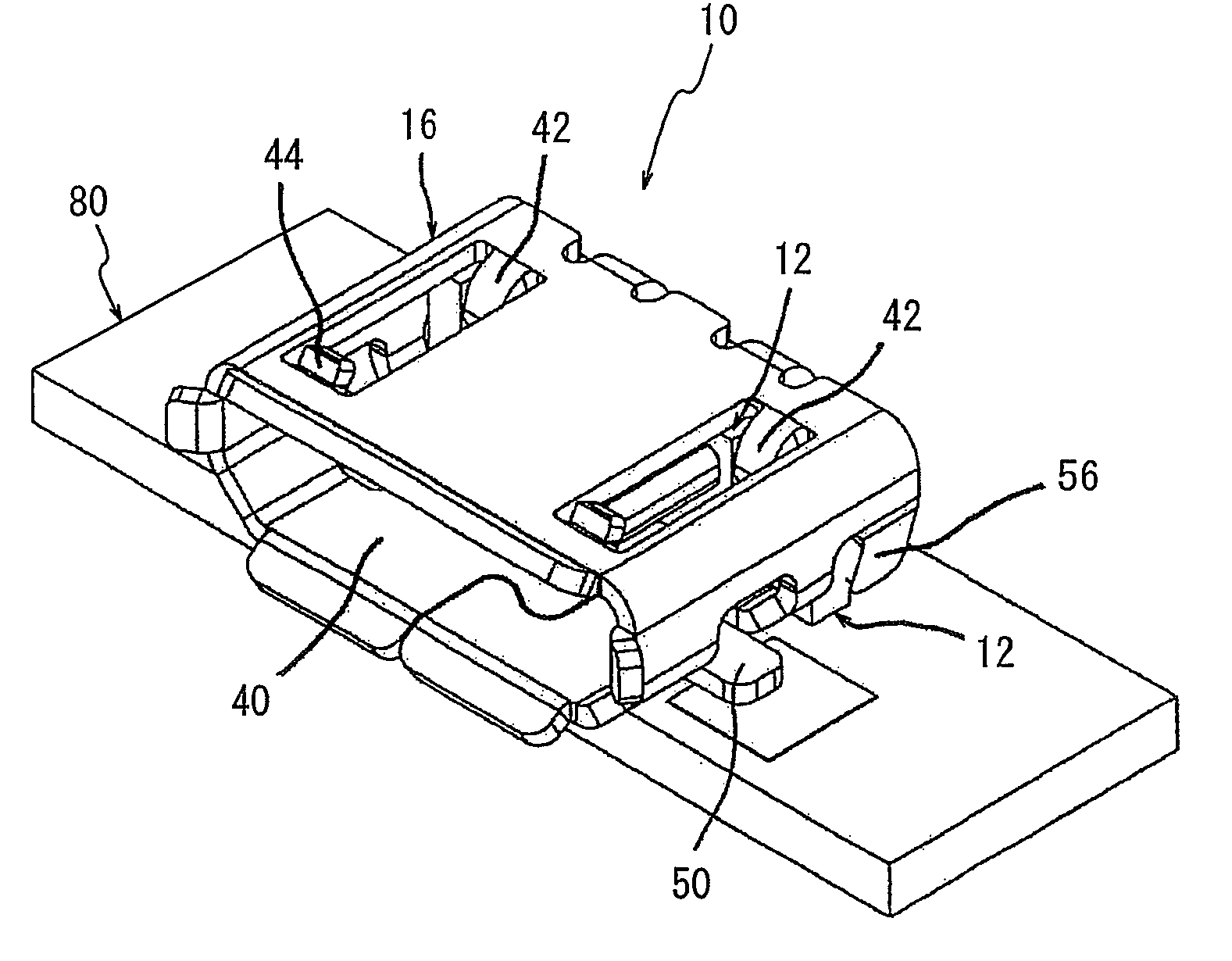

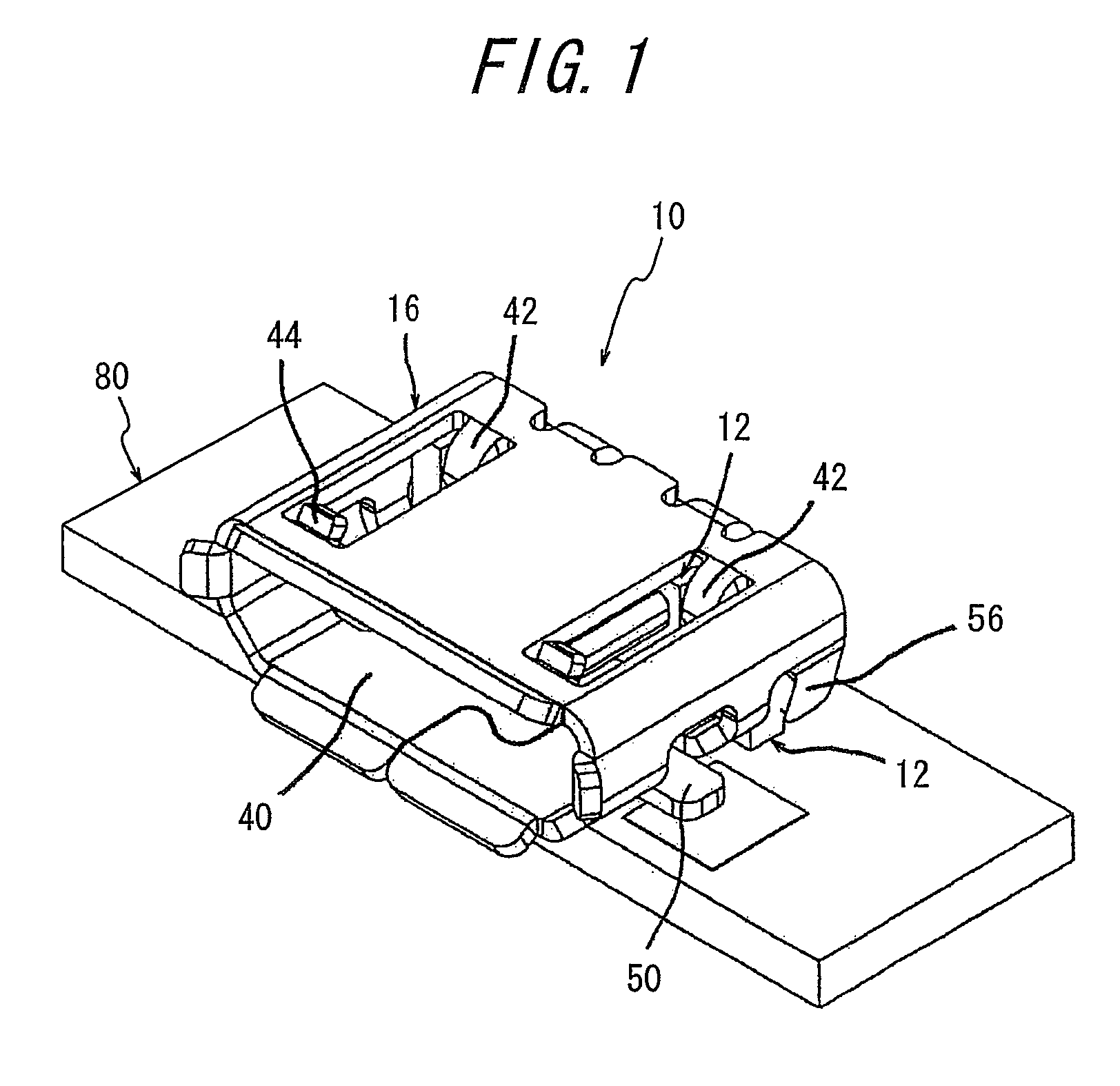

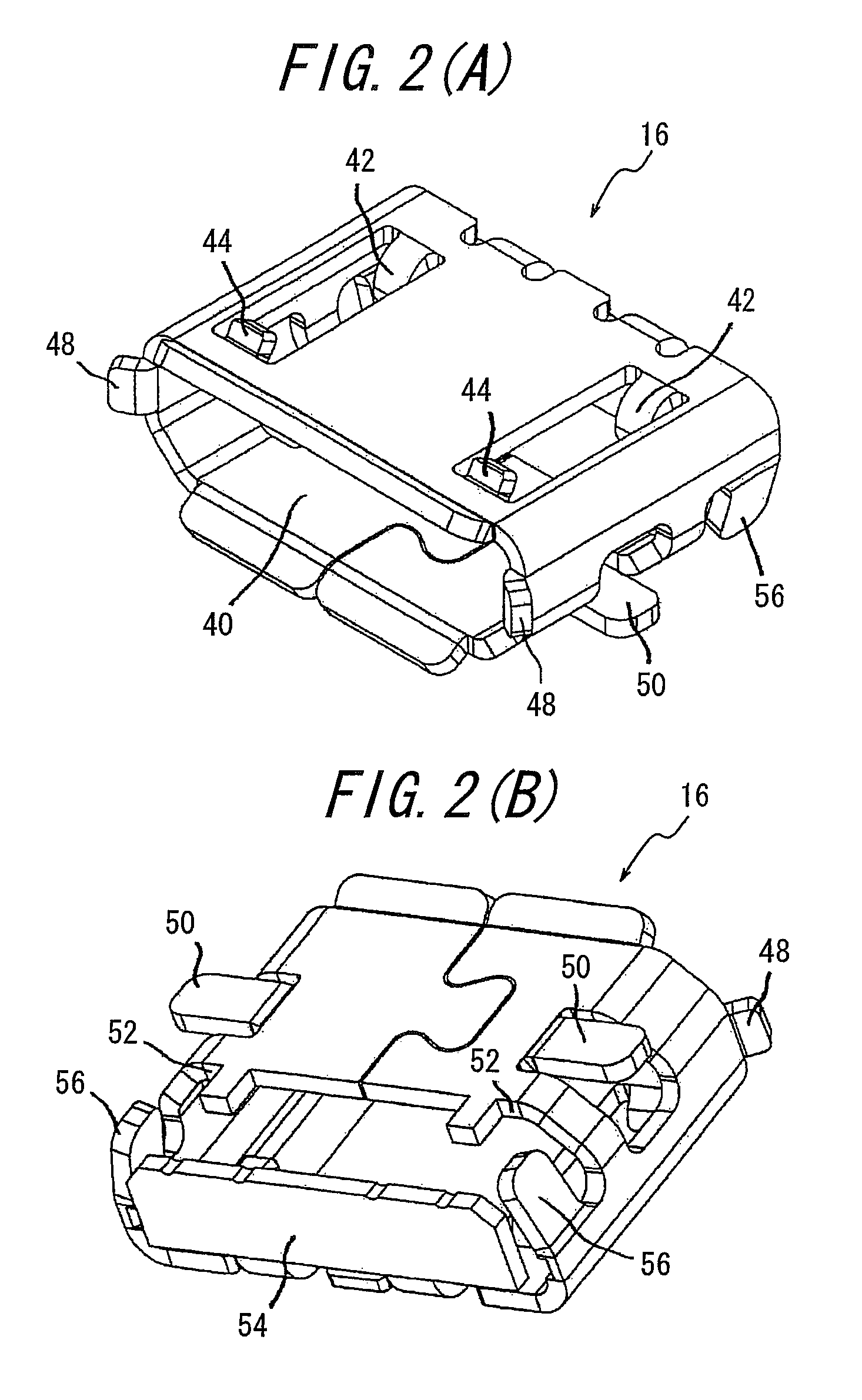

Electrical connector

InactiveUS20080214050A1Connection failureGreatRelieving strain on wire connectionTwo-part coupling devicesMating connectionEngineering

An electrical connector to be detachably fitted with a mating connector, including a plurality of contacts, a housing for arranging and holding the contacts, and a shell covering the housing and forming with the housing a fitting opening for the mating connector. The shell has at least one engaging piece, and the housing has an anchoring portion at a location corresponding to the engaging piece to cause the anchoring portion to engage the engaging piece, thereby restraining the housing from being displaced in the direction opposite to the fitting direction upon fitting with the mating connector. Even being miniaturized, the electrical connector is securely positioned relative to the mating connector when fitting with it, and the housing is securely prevented from being displaced upon the mating connector abutting against the housing, thereby completely preventing any defective connection.

Owner:DDK LTD

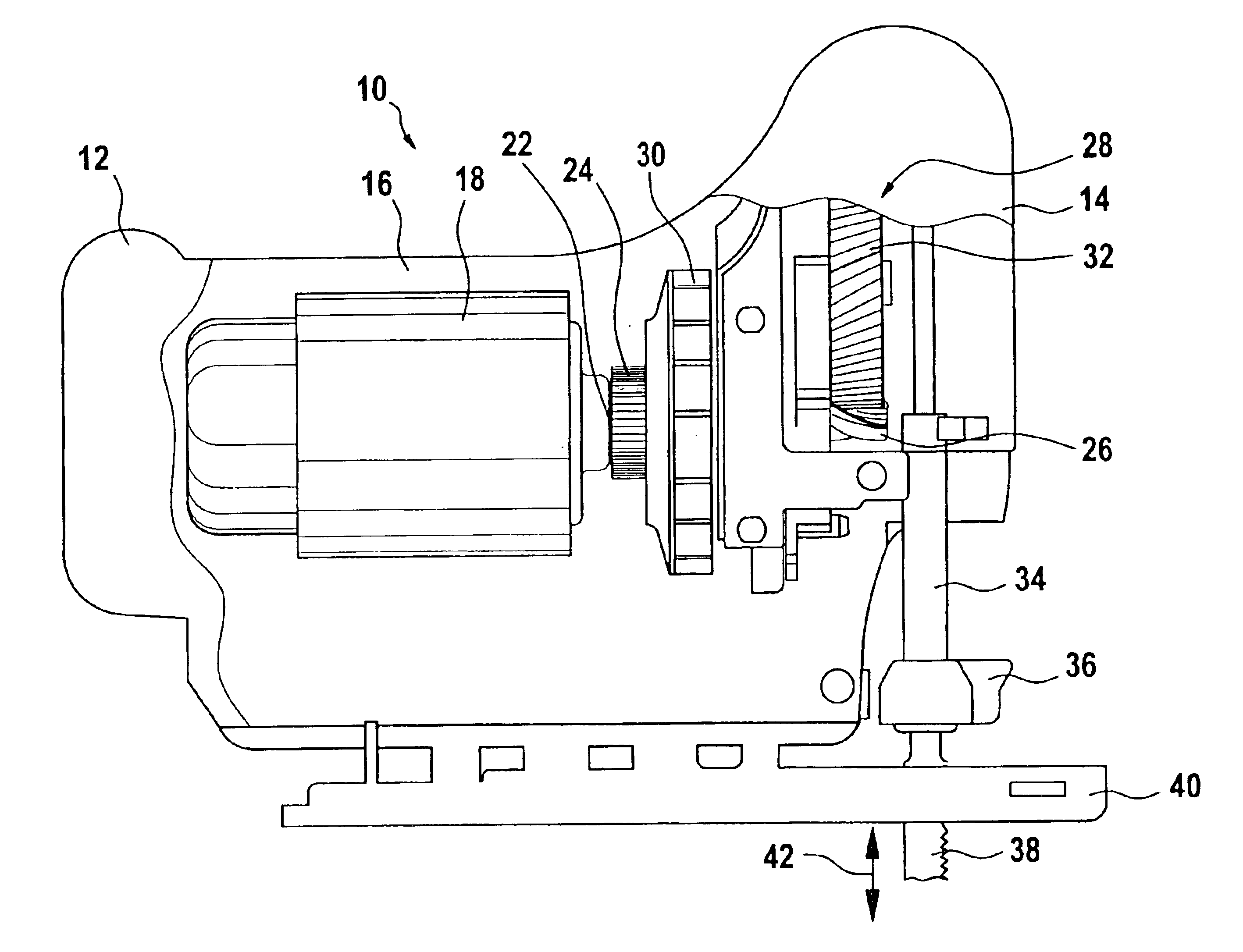

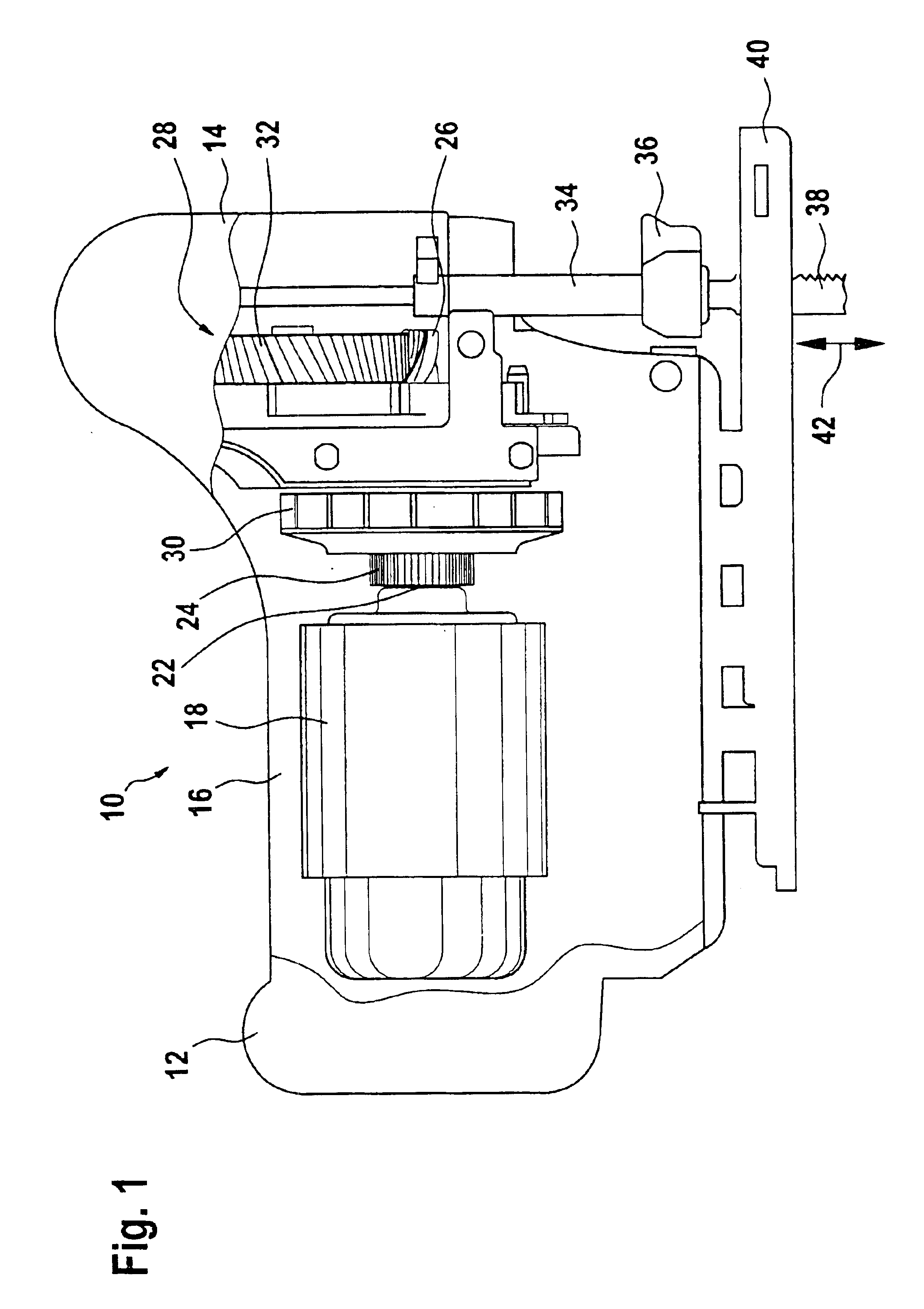

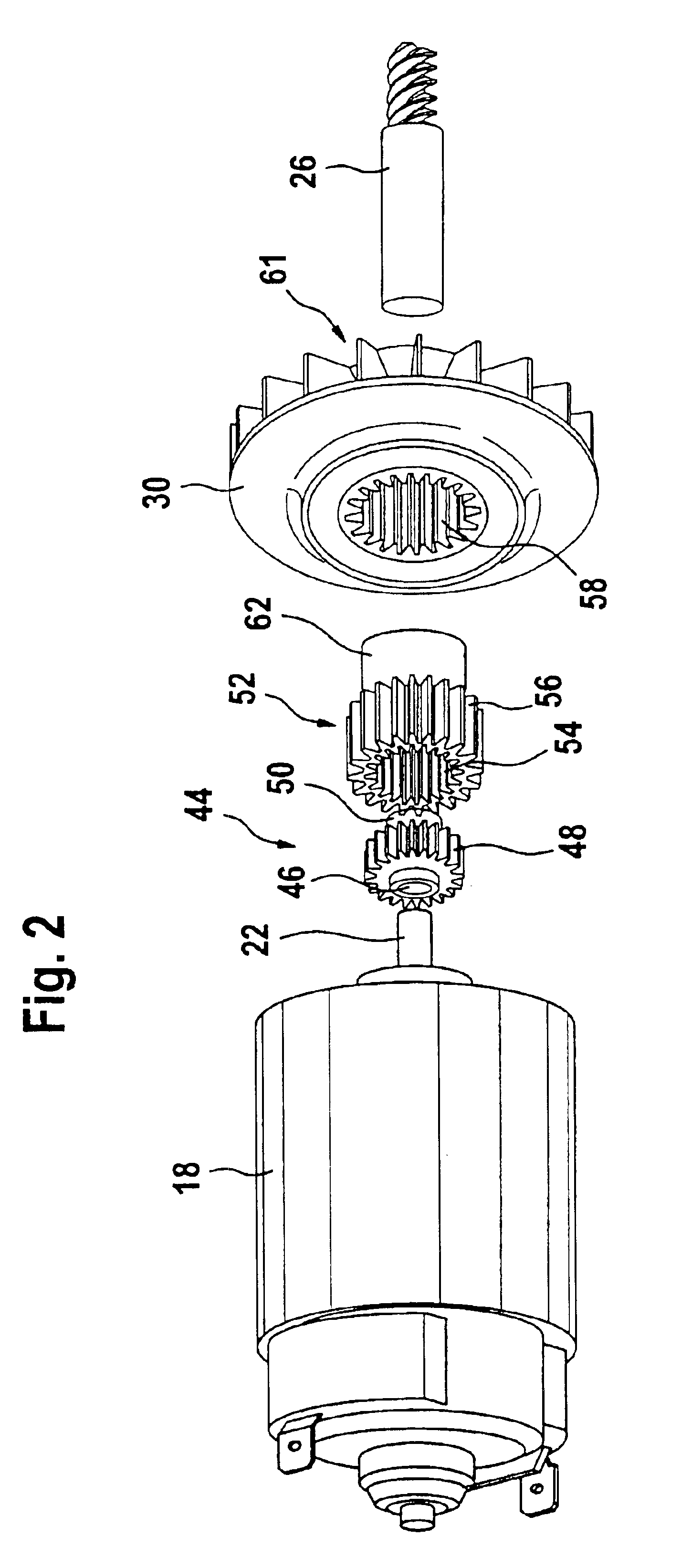

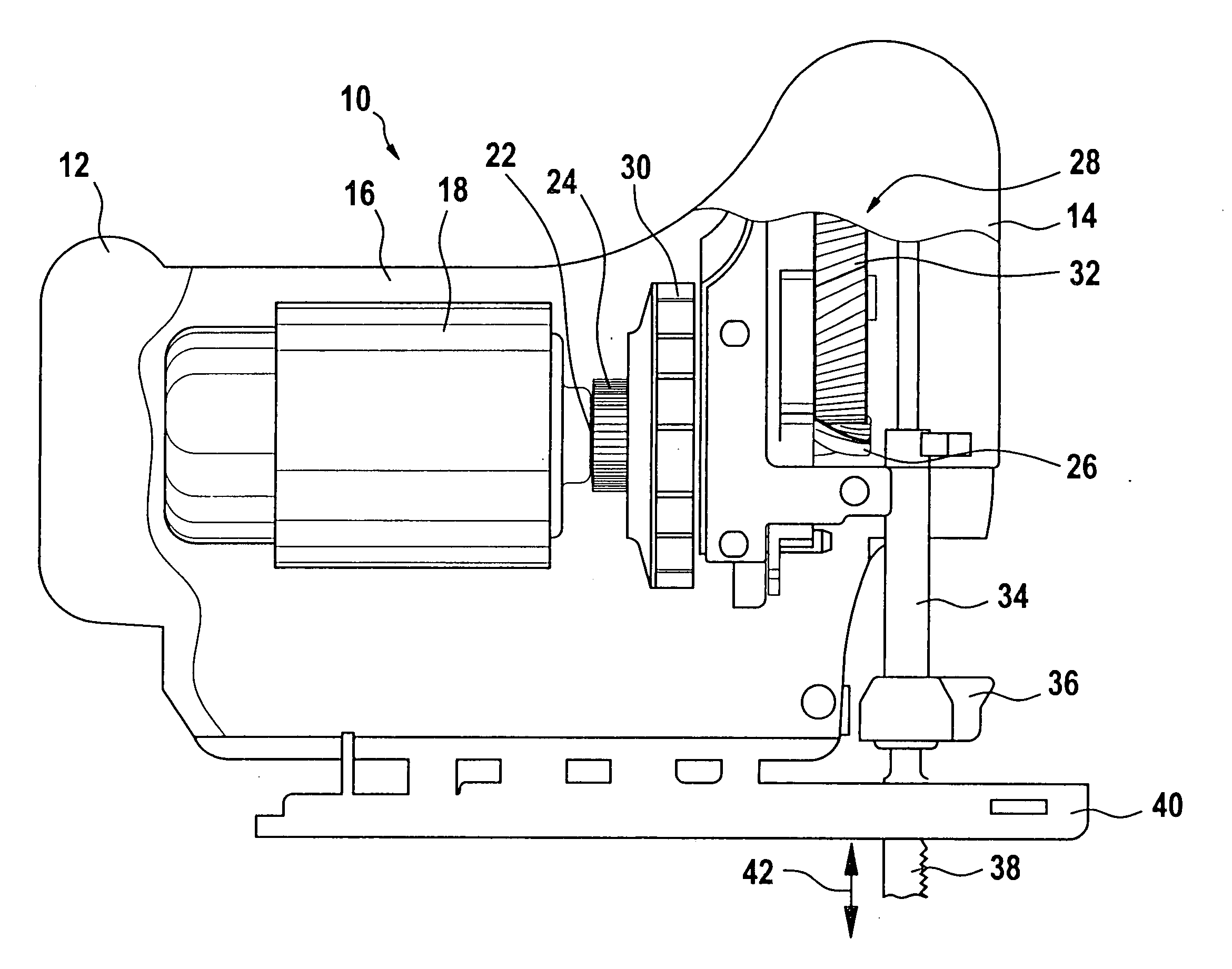

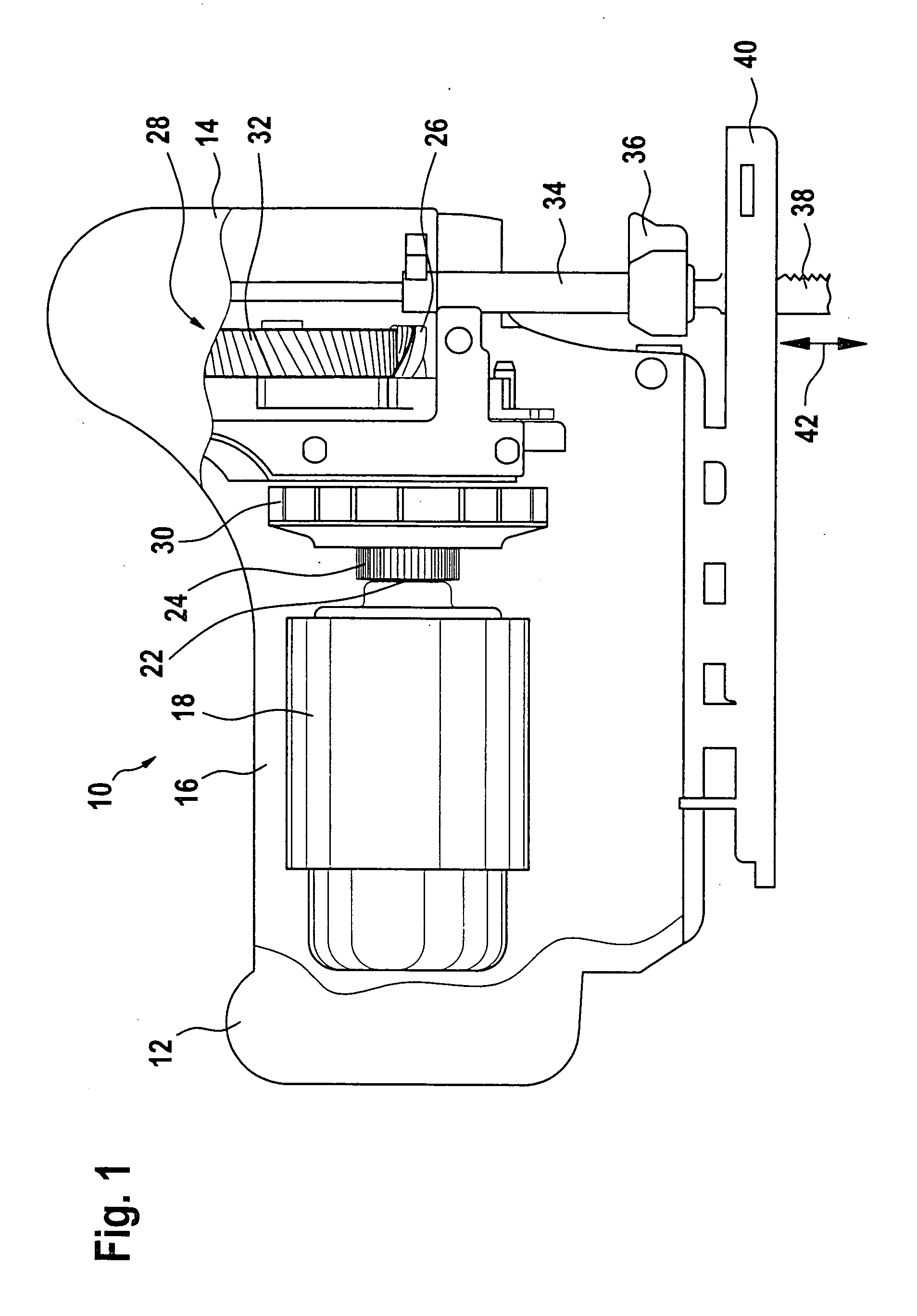

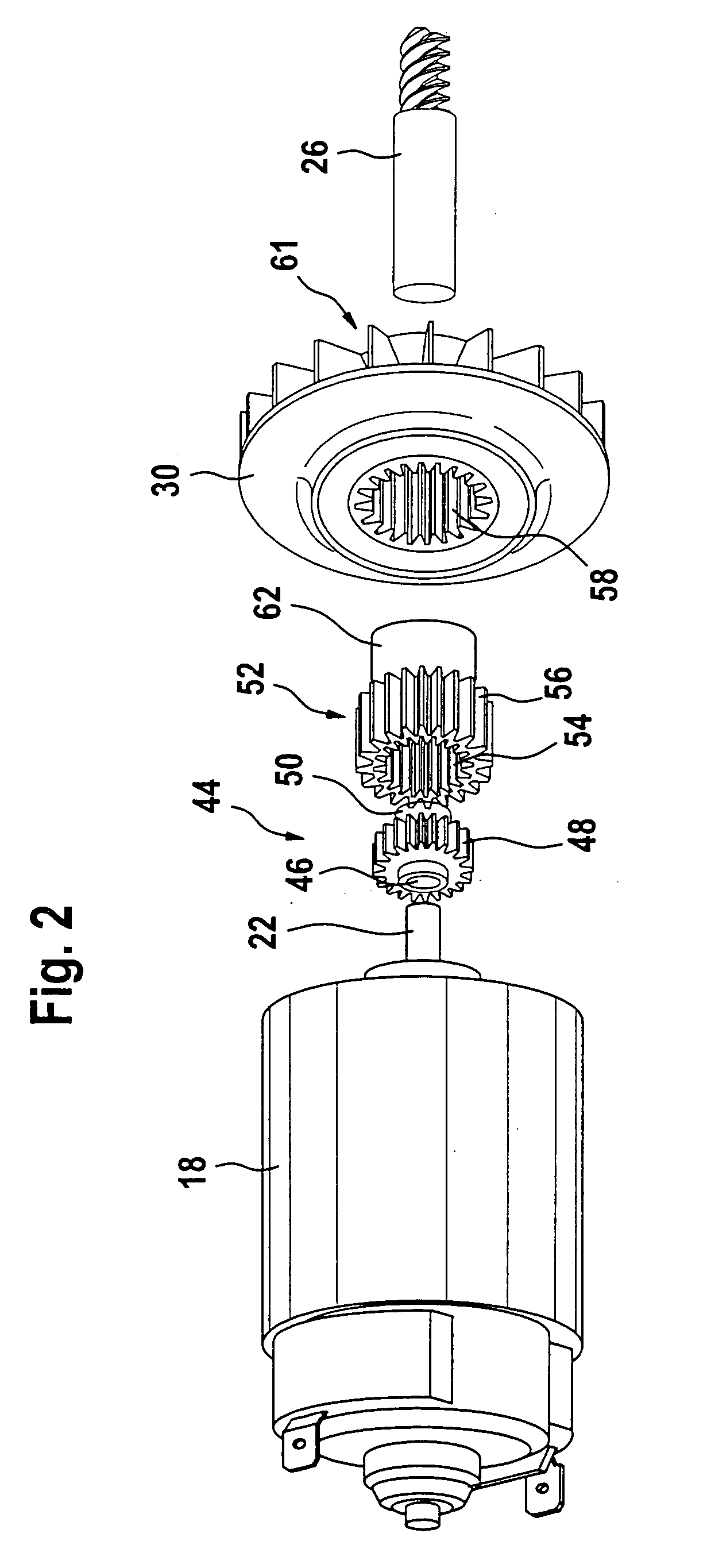

Hand-held saber saw

InactiveUS6920695B2GreatInvulnerable to shockMetal sawing devicesTransportation and packagingCouplingGear wheel

A reciprocating hand saw (10), having a motor housing (16) and a gearbox (28) that receive a battery-operated direct-current motor (18) with a motor shaft having a shaft end (22) and a gear (28), respectively, which gear—as known per se in reciprocating saws—is connected to the shaft end in a way driven to rotate and whose gear input pinion (26) converts the rotation of the motor shaft end (22) into an up-and-down motion of a push rod (34) that carries a sawblade (38), can be produced economically and is especially sturdy because the gear (28) and its gearbox (14) originate in a reciprocating saw that can be operated by alternating current, and because between the shaft end (22) and the gear input pinion (26), a multi-stage coupling (24), disposed in a manner fixed against relative rotation for transmitting torque, comprises parts that can be easily separated from one another.

Owner:ROBERT BOSCH GMBH

Electrical connector

InactiveUS7575466B2Connection failureGreatRelieving strain on wire connectionTwo-part coupling devicesMating connectionElectrical connector

An electrical connector to be detachably fitted with a mating connector, including a plurality of contacts, a housing for arranging and holding the contacts, and a shell covering the housing and forming with the housing a fitting opening for the mating connector. The shell has at least one engaging piece, and the housing has an anchoring portion at a location corresponding to the engaging piece to cause the anchoring portion to engage the engaging piece, thereby restraining the housing from being displaced in the direction opposite to the fitting direction upon fitting with the mating connector. Even being miniaturized, the electrical connector is securely positioned relative to the mating connector when fitting with it, and the housing is securely prevented from being displaced upon the mating connector abutting against the housing, thereby completely preventing any defective connection.

Owner:DDK LTD

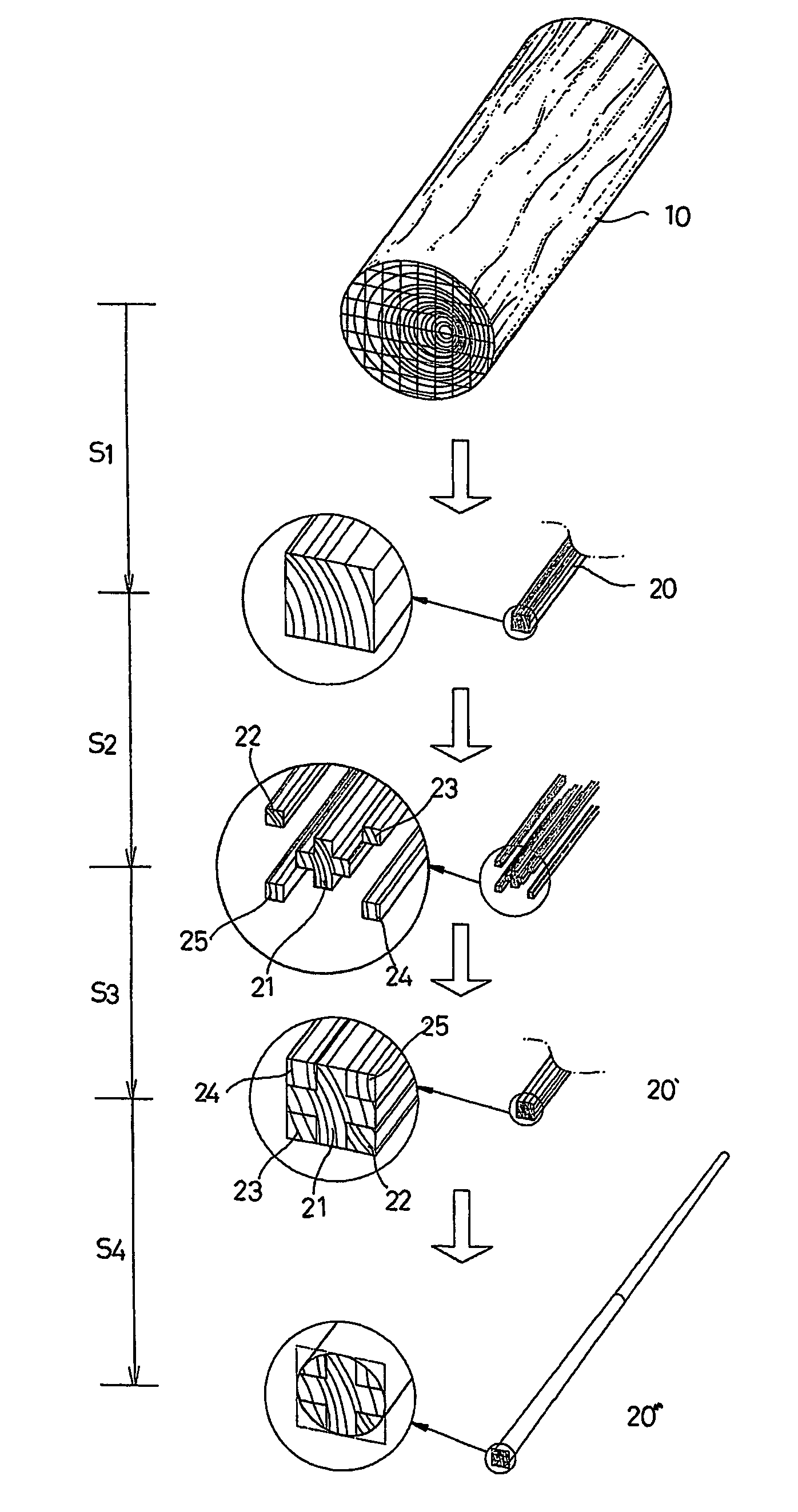

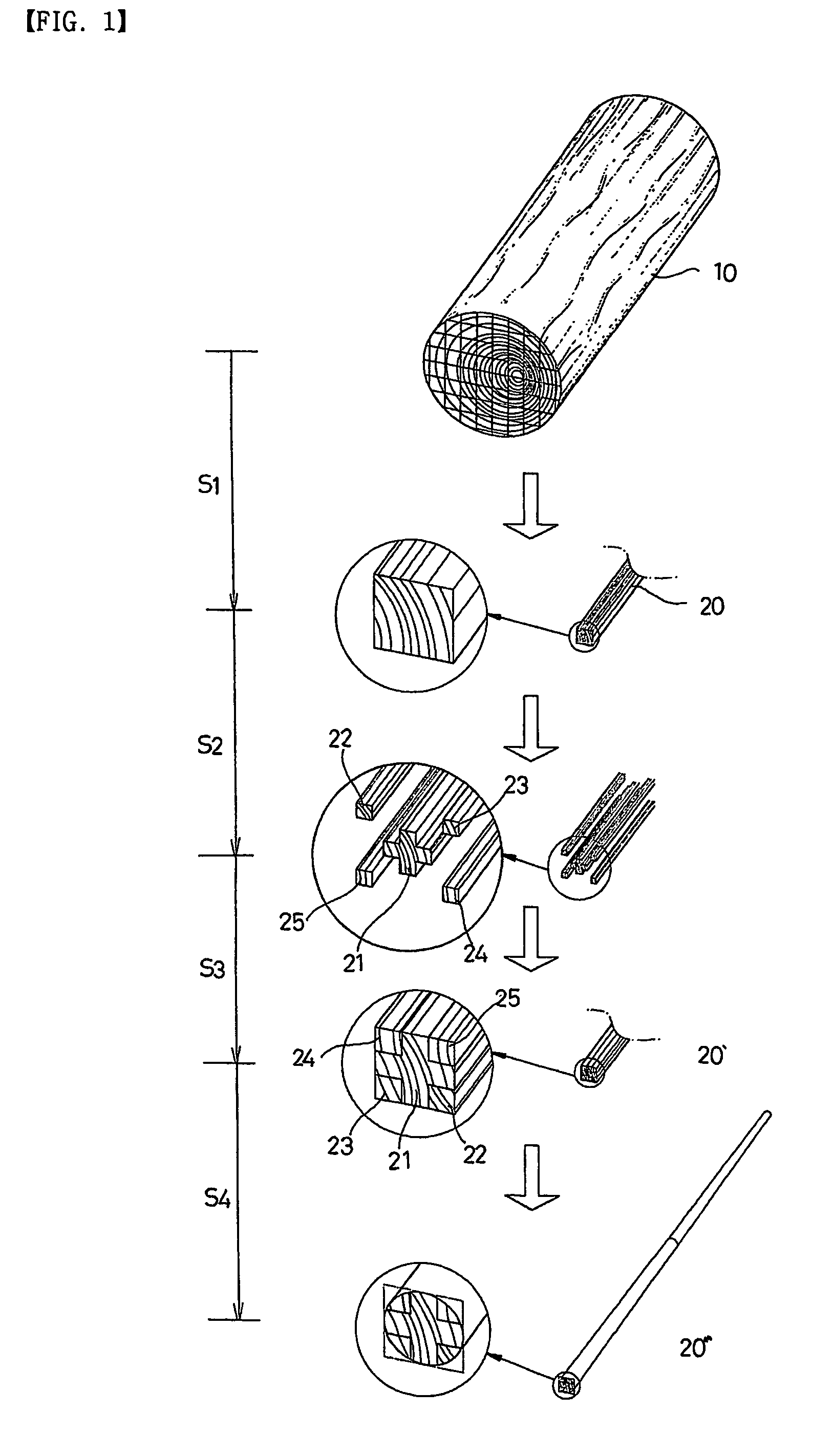

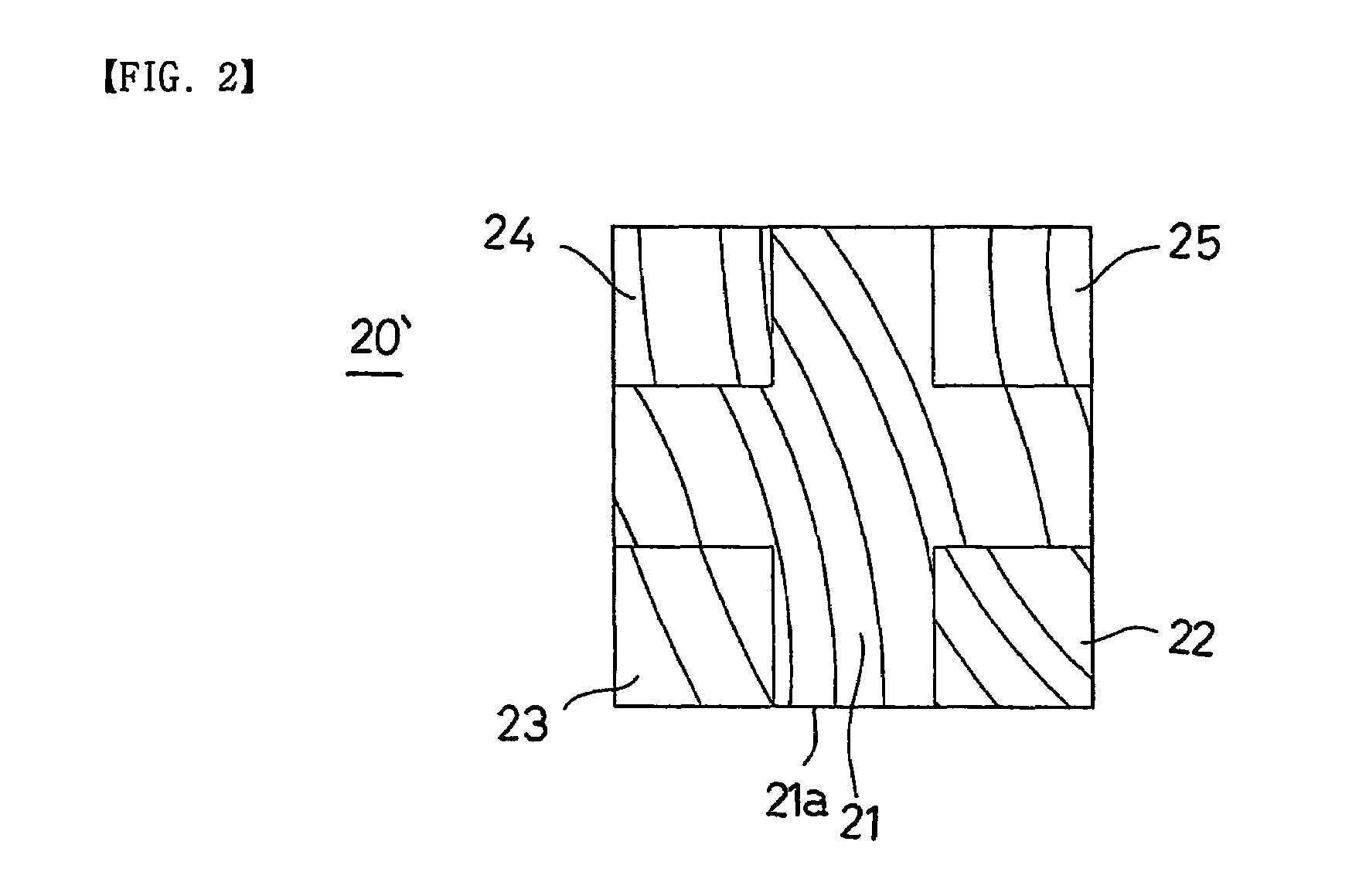

Billiard cue

A billiard cue less bendable than a standard wood cue, which is manufactured by dividing a square lumber (20), sawed from a wood material (10), into a central member (21), having a cross-shaped section in which longitudinal sides thereof are perpendicular to transverse sides lines thereof and end terminals thereof contact edges of the square lumber (20), and peripheral members (22, 23, 24, and 25) cut off from the central member, and the peripheral members (22, 23, 24, and 25) are then bonded to the central member (21) so that the direction of the annual rings of the peripheral members (22, 23, 24, and 25) is opposite to the direction of the annual rings of the central member (21), thereby offsetting stress applied to the central member (21) due to the orientation of the annual rings of the original square lumber (20), and applied to the peripheral members (22, 23, 24, and 25), and allowing maintaining its straight state without deformation.

Owner:KWON OH CHUL

Rotor of an electric motor and method for producing the rotor

ActiveUS10224772B2Easy to produceReduce usageMagnetic circuit rotating partsManufacturing stator/rotor bodiesEngineeringMagnet

A rotor of an electric motor includes a laminated armature core, a shaft, magnets arranged on the circumference of the laminated armature core, and a plastic overmold. The laminated armature core has at least one associated channel on the circumference of the laminated armature core for each magnet. The channels extend parallel to the shaft, and the laminated armature core has radially oriented webs on the circumference. The webs (8) extend parallel to the shaft and a magnet (9) is arranged between each pair of webs (8), and the plastic overmold (4) encloses the laminated armature core (1) and the magnets (3) to such an extent that only the radial outer face of the magnets (3) is free of plastic (4).

Owner:VITESCO TECH GERMANY GMBH

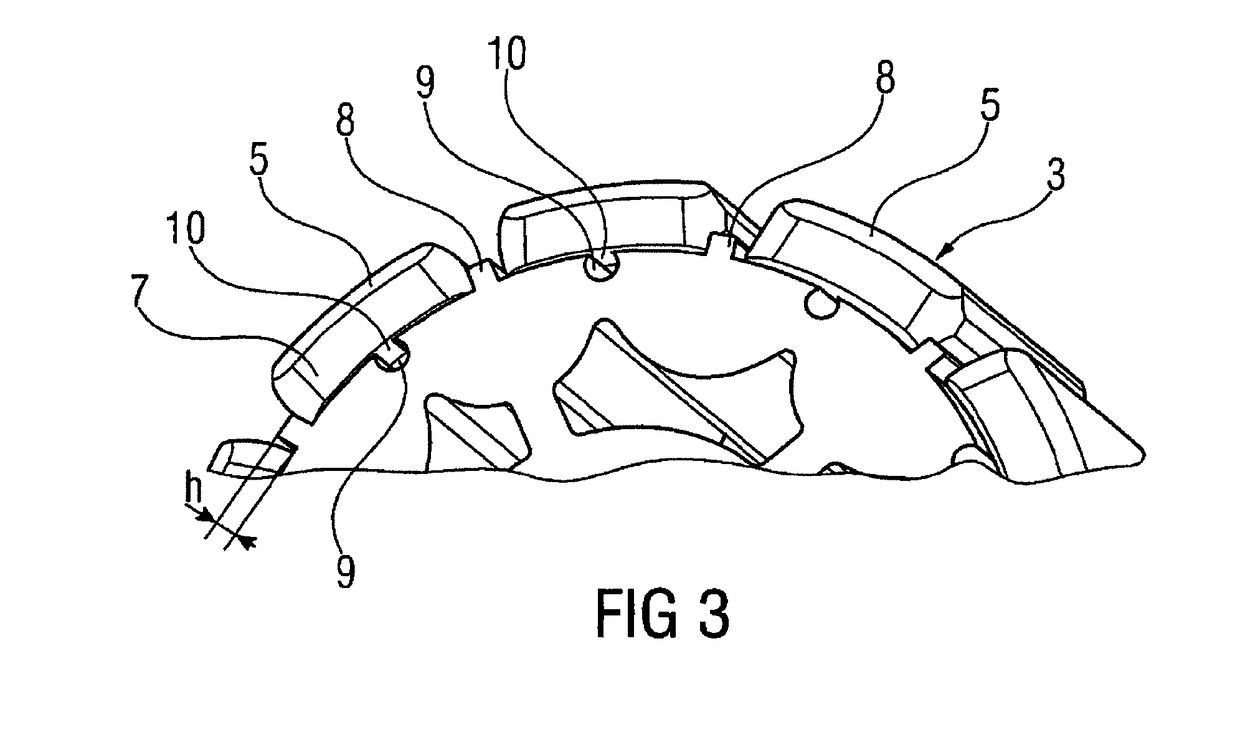

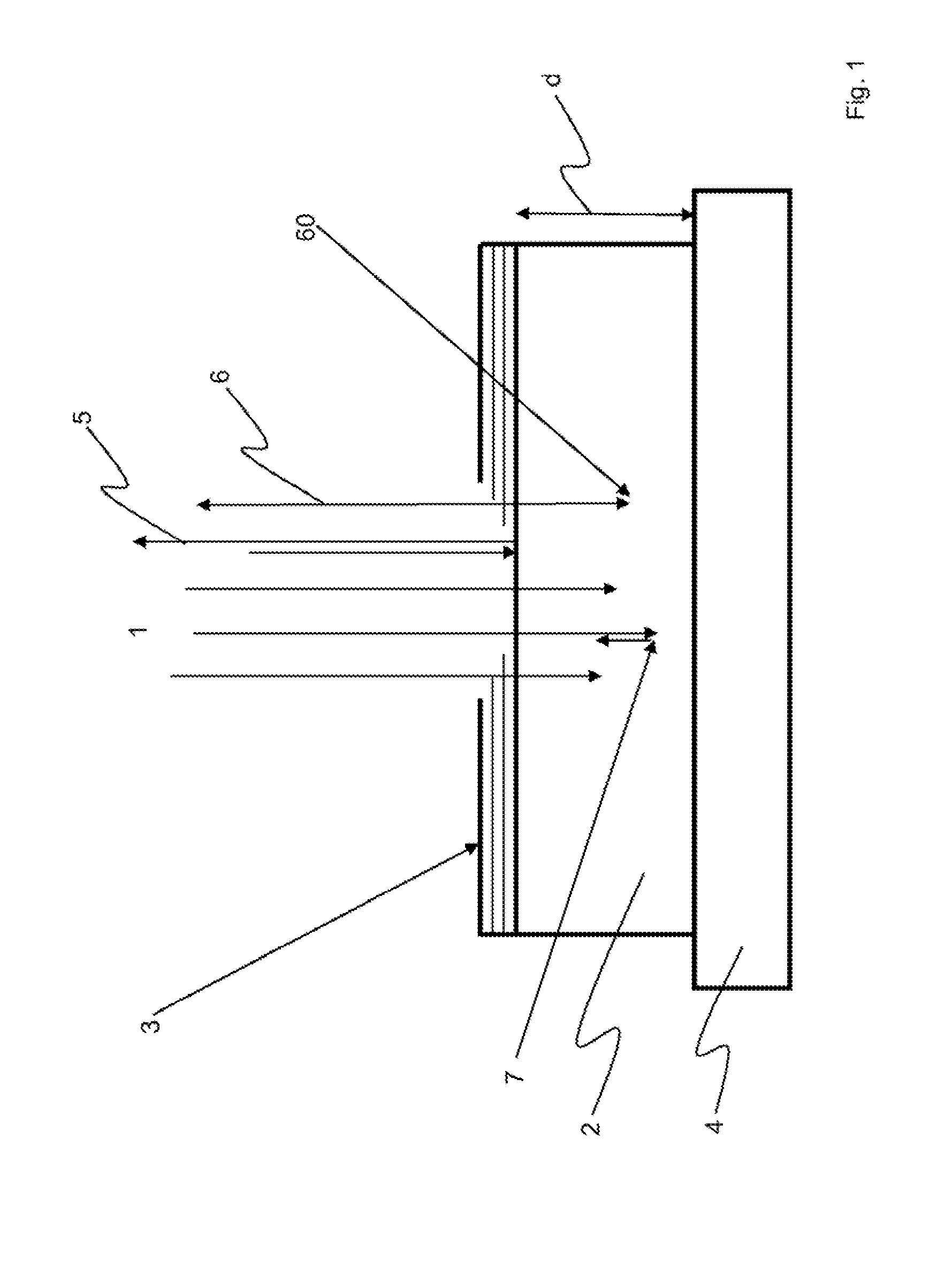

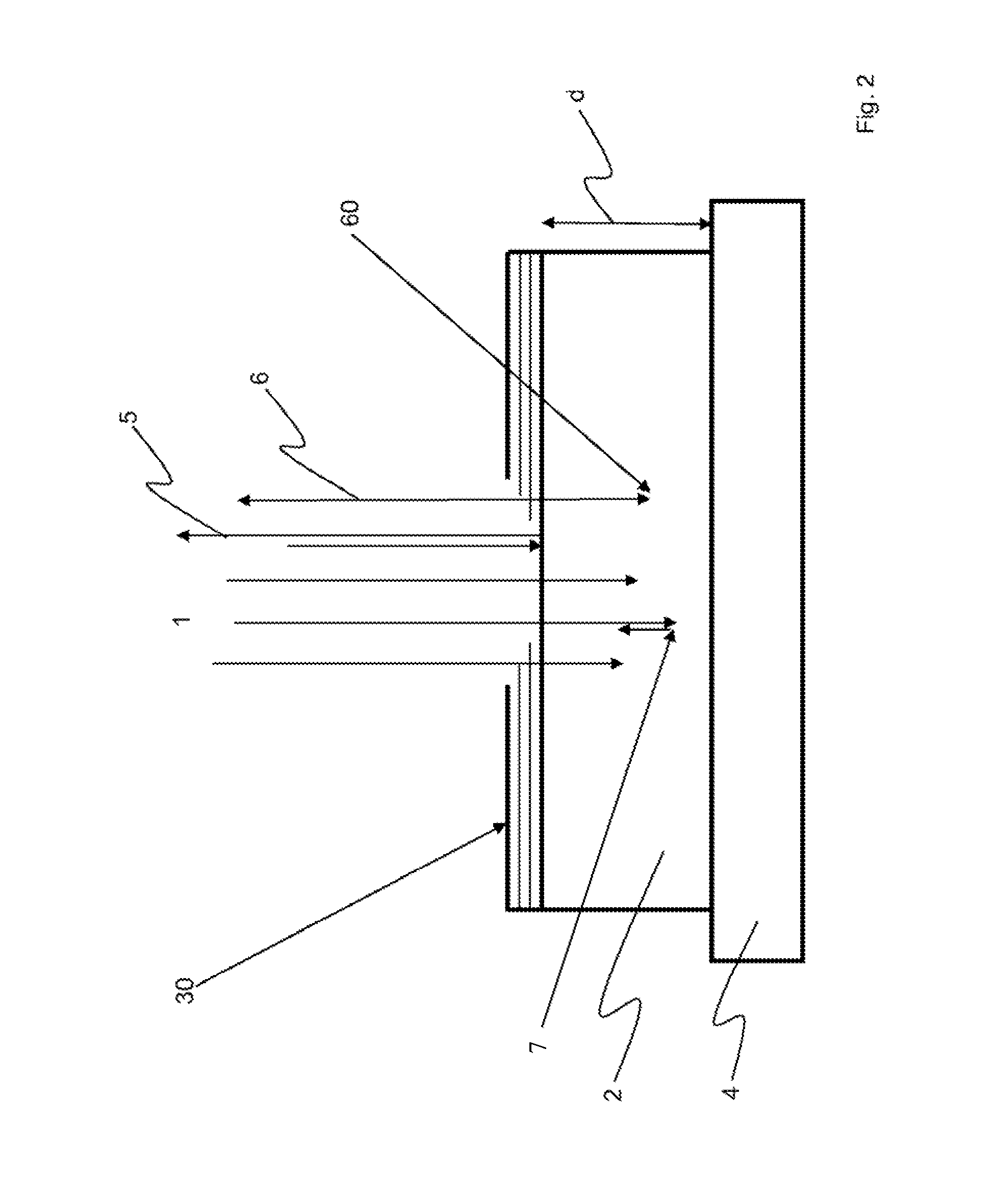

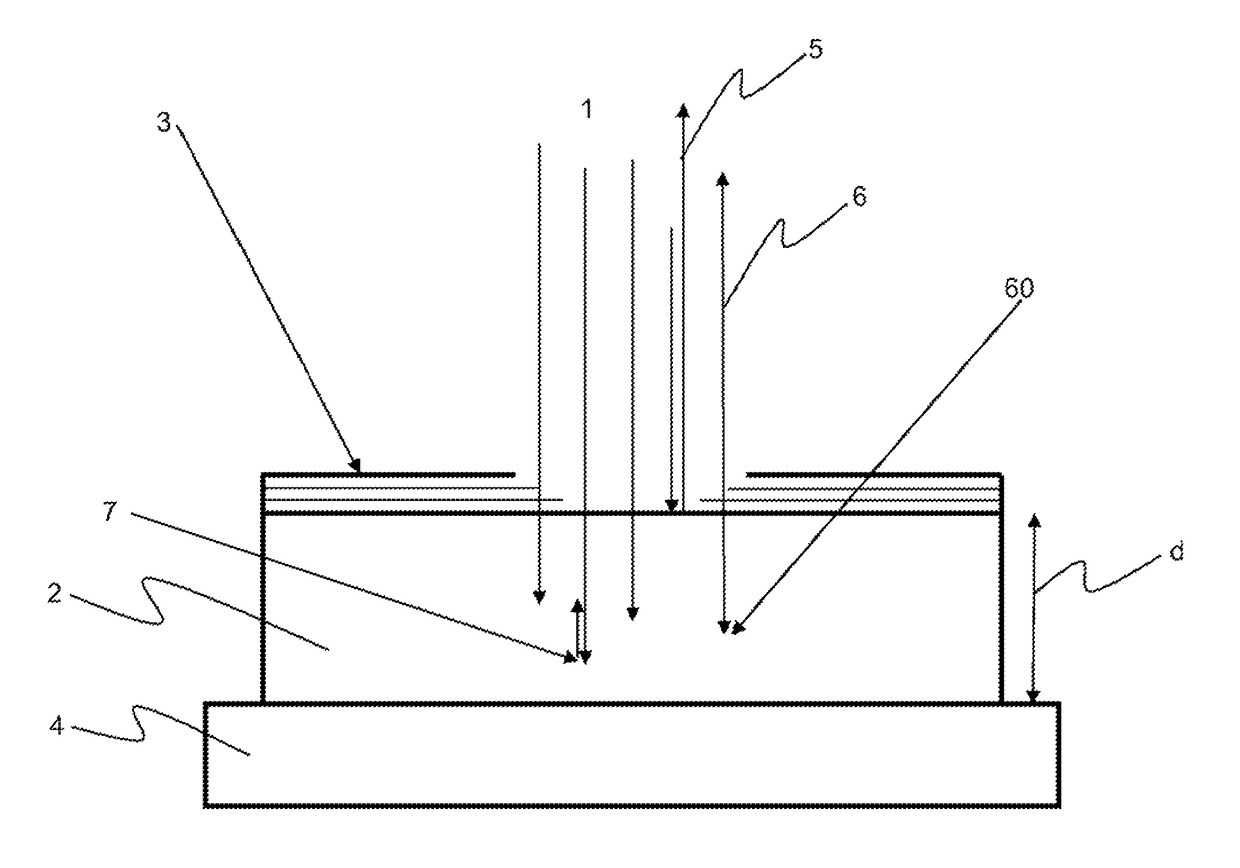

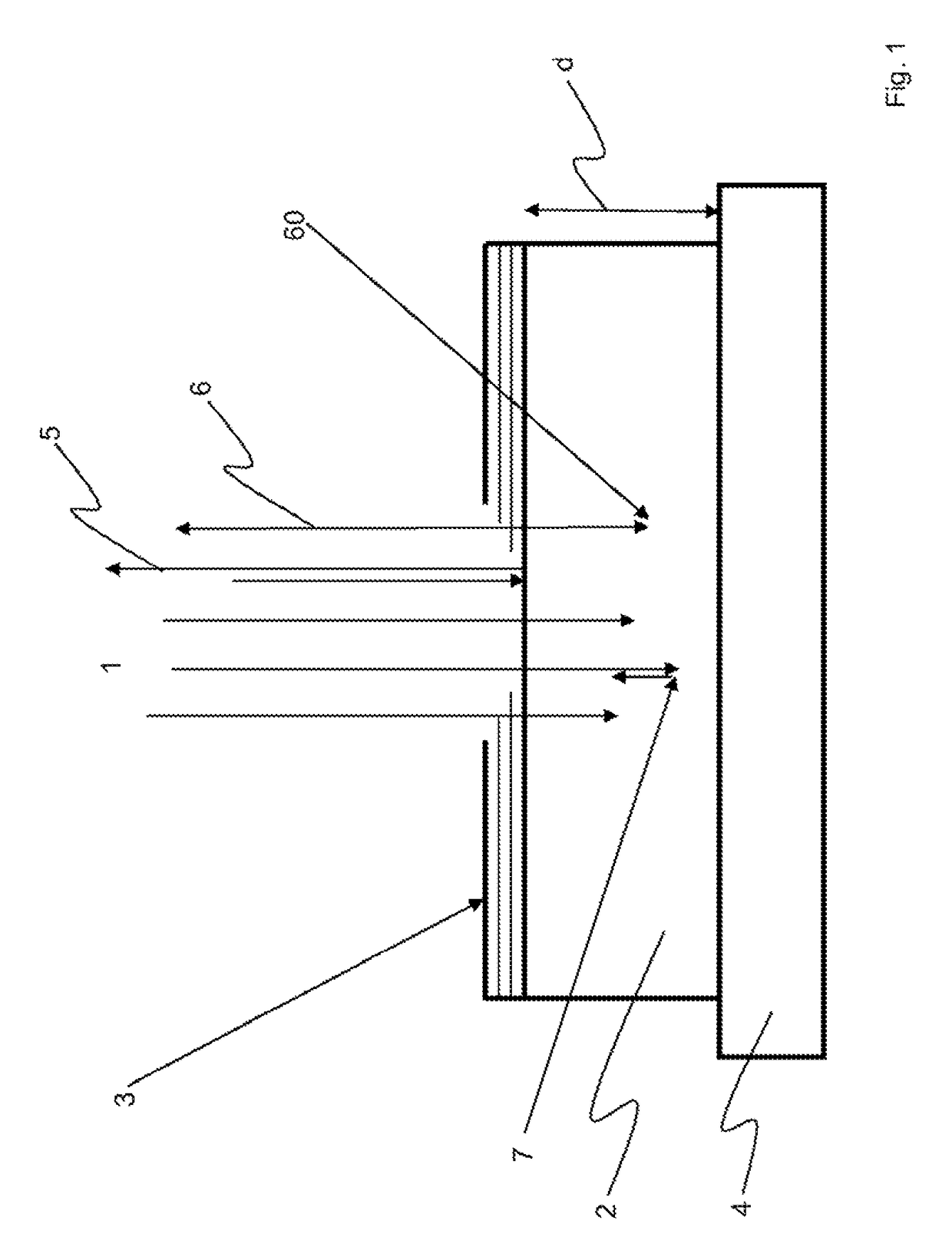

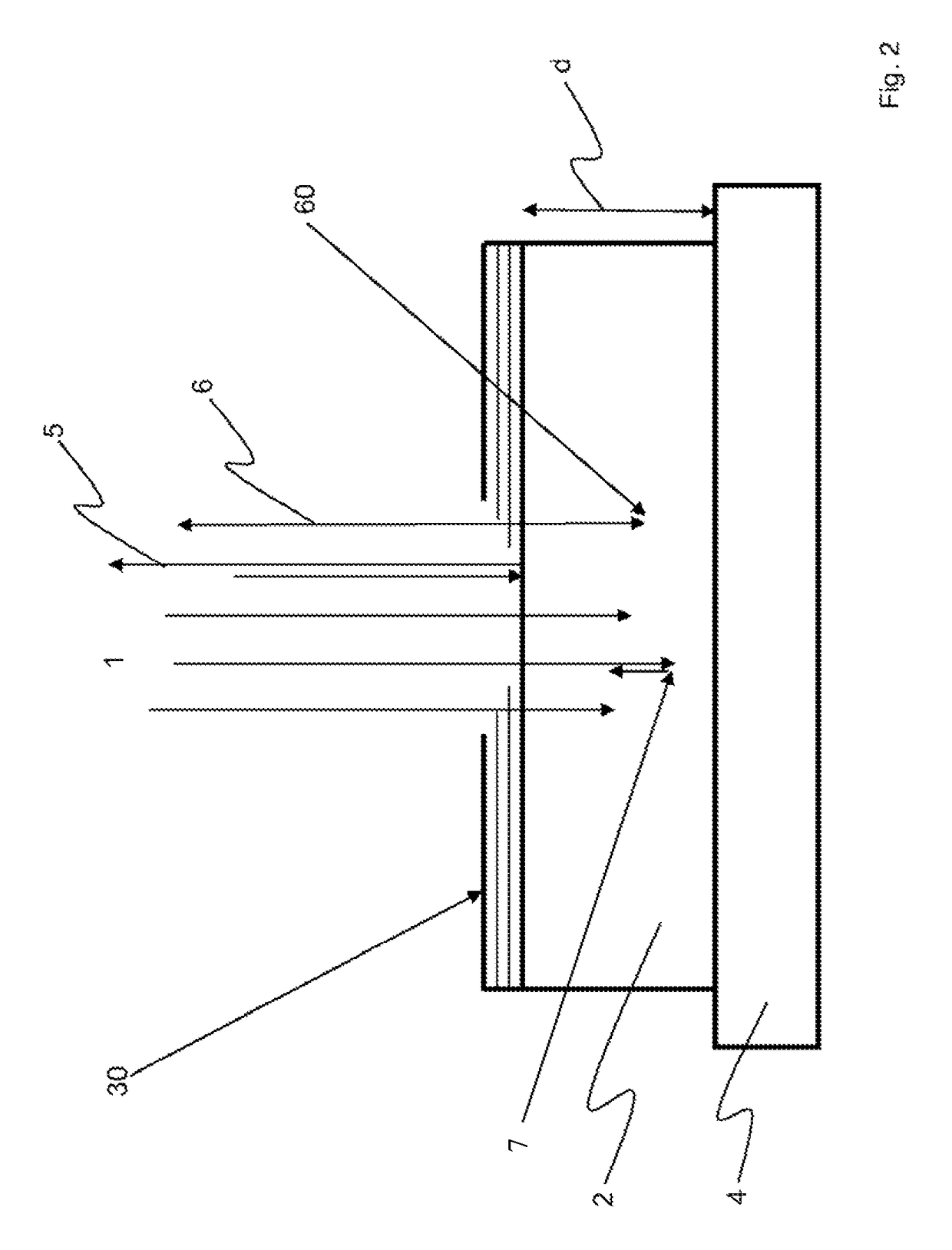

Generation of white light

An arrangement for generating white light is provided. The arrangement generates the white light by combining blue light and yellow light. The yellow light originates from a converter which transforms into yellow light virtually all blue light that enters the converter.

Owner:SCHOTT AG

Generation of white light

Owner:SCHOTT AG

Hand-held saber saw

InactiveUS20040055167A1GreatInvulnerable to shockMetal sawing devicesTransportation and packagingGear wheelCoupling

A reciprocating hand saw (10), having a motor housing (16) and a gearbox (28) that receive a battery-operated direct-current motor (18) with a motor shaft having a shaft end (22) and a gear (28), respectively, which gear-as known per se in reciprocating saws-is connected to the shaft end in a way driven to rotate and whose gear input pinion (26) converts the rotation of the motor shaft end (22) into an up-and-down motion of a push rod (34) that carries a sawblade (38), can be produced economically and is especially sturdy because the gear (28) and its gearbox (14) originate in a reciprocating saw that can be operated by alternating current, and because between the shaft end (22) and the gear input pinion (26), a multi-stage coupling (24), disposed in a manner fixed against relative rotation for transmitting torque, comprises parts that can be easily separated from one another.

Owner:ROBERT BOSCH GMBH

Damper vane and housing construction

ActiveUS20130273831A1Reduce amountGreat toleranceLighting and heating apparatusHeating and ventilation casings/coversEngineeringRidge

A damper having a housing includes a rotatable damper vane therein constructed to minimize the passage of air between the vane and the housing when the vane is in a closed position. The housing includes a pair of opposed walls having a channel or flute therein adjacent outer edges of the vane when the vane is in the closed position. The outer edges of the vane terminate in domed or arcuate shaped surfaces that generally correspond with the channel. The arcuate shaped surfaces are a distance apart that is greater than a distance between the opposed walls such that the arcuate shaped surfaces are received in the channels when the vane is in the closed position. The housing also includes a pair of opposed sidewalls having a ridge therein at a location that aligns with an edge of the vane when the vane is in the closed position.

Owner:AIRFIXTURE

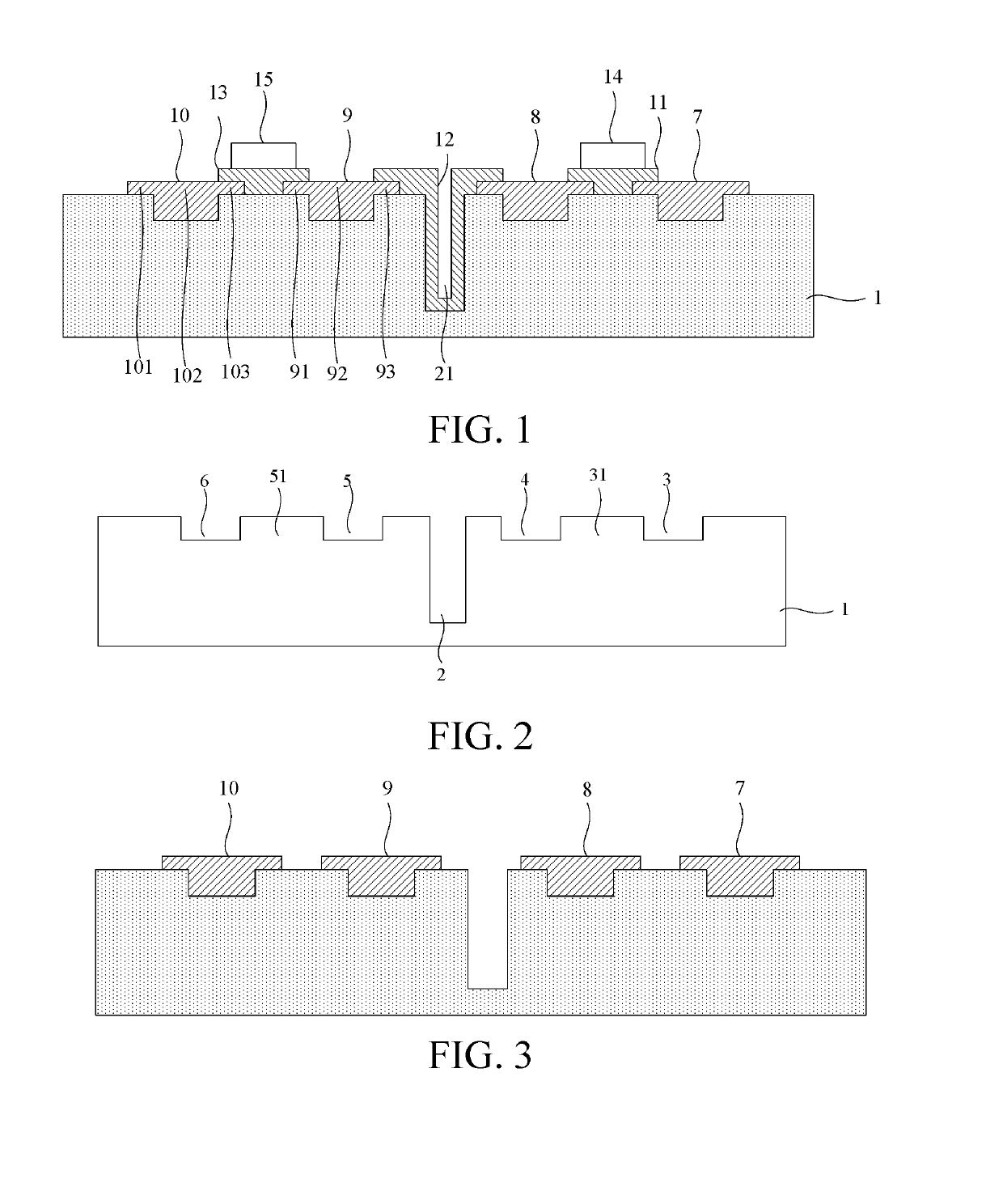

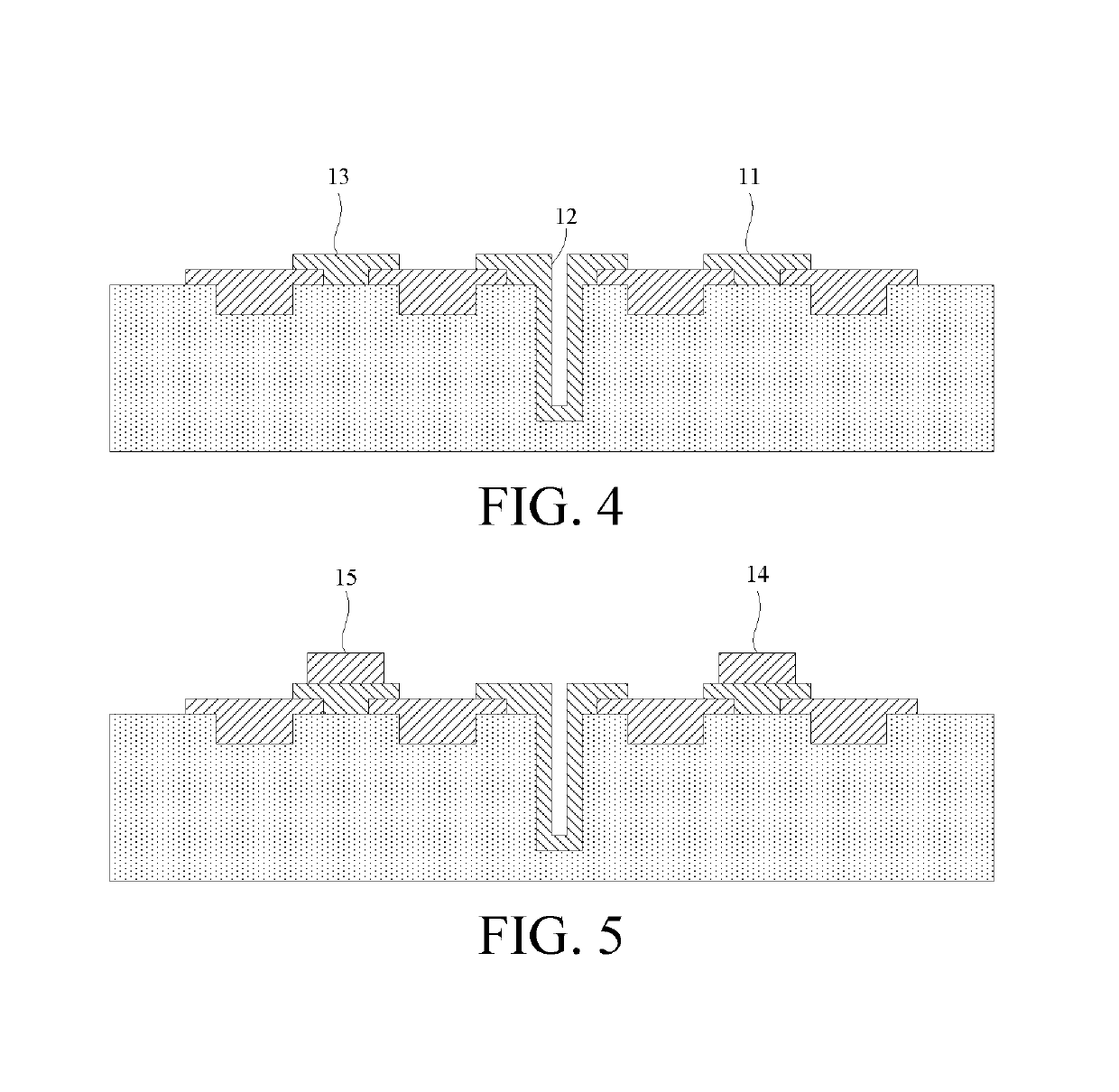

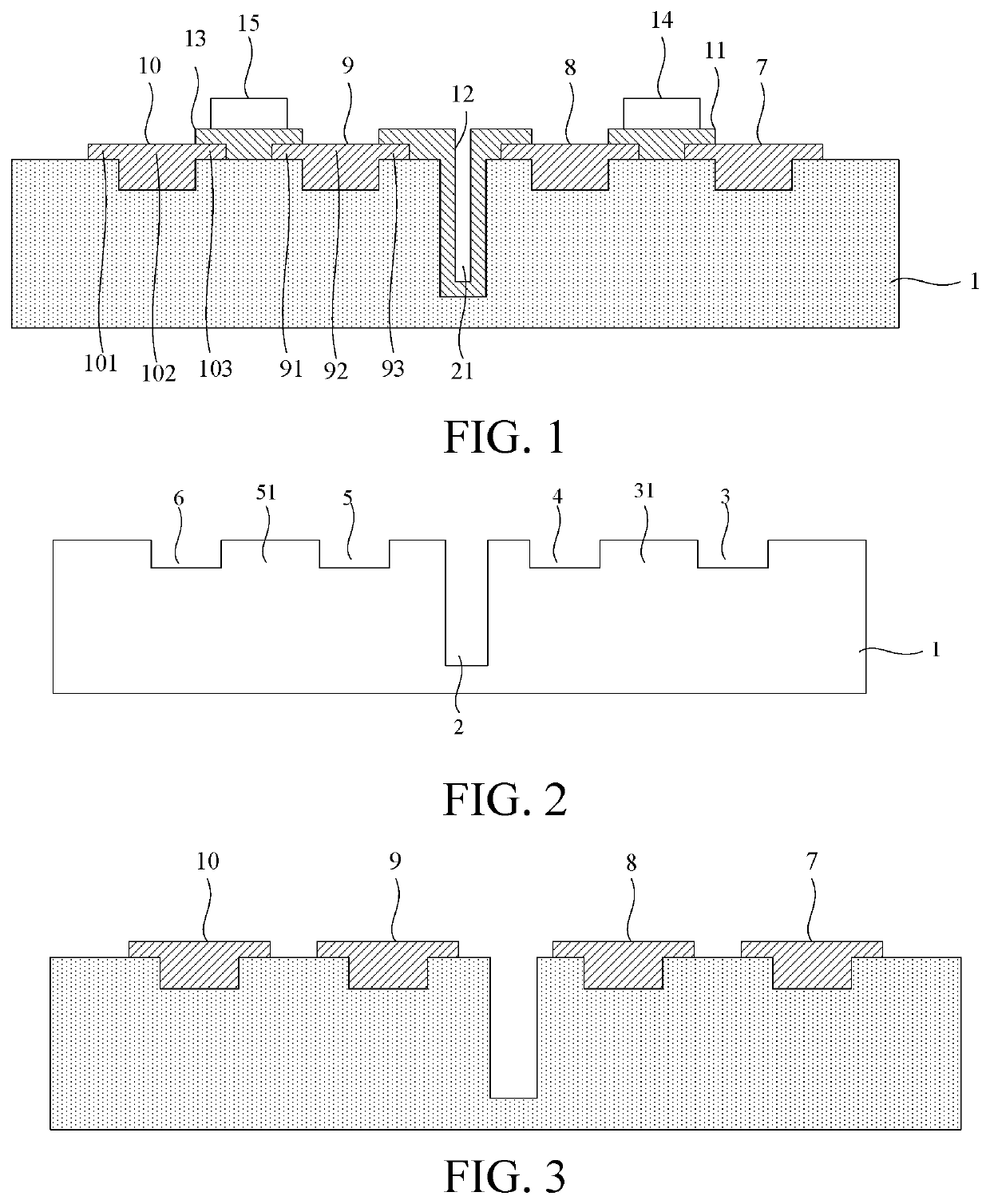

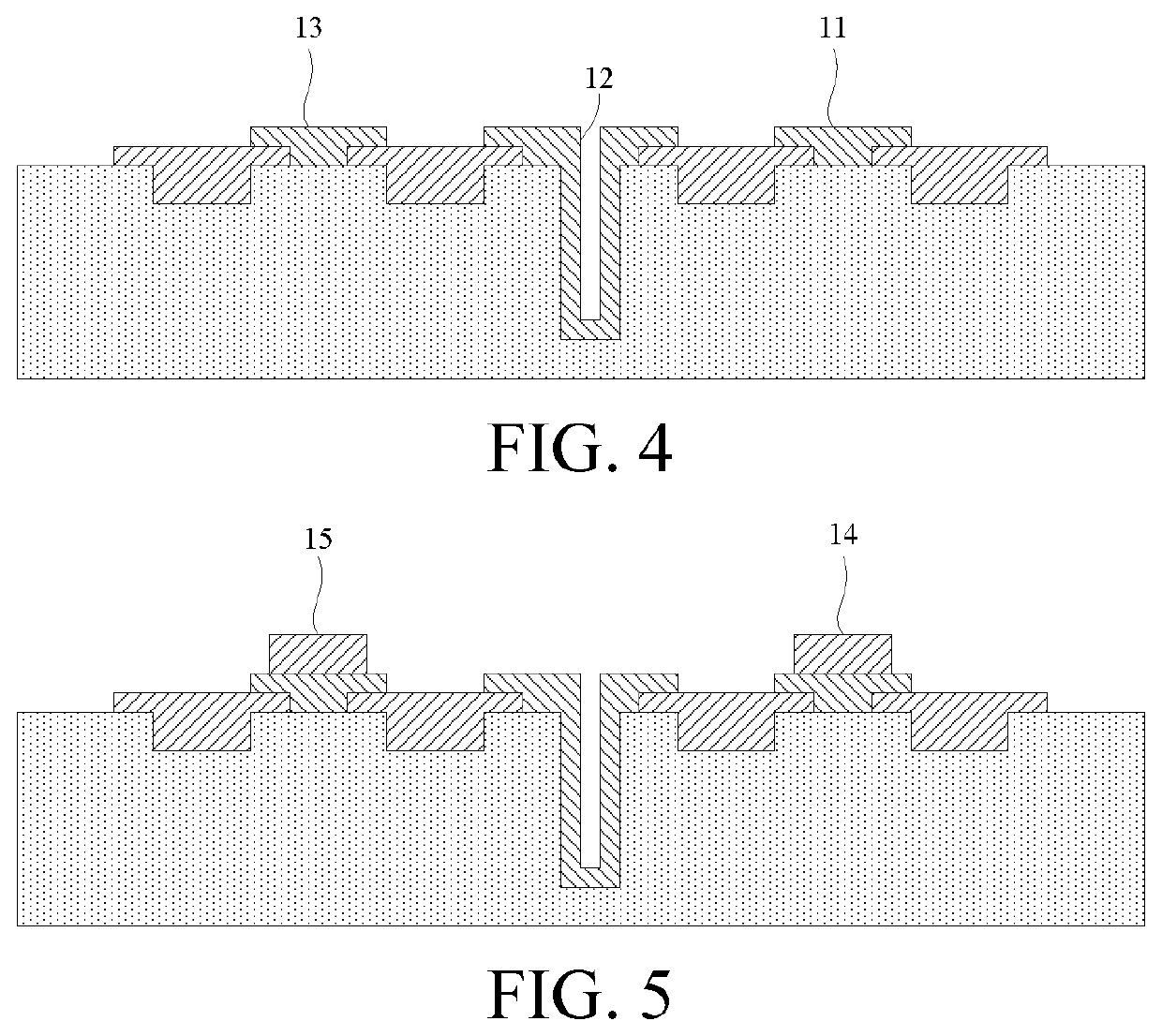

TFT structure based on flexible multi-layer graphene quantum carbon substrate material and method for manufacturing same

A TFT structure based on a flexible multi-layer graphene quantum carbon substrate material and a method for manufacturing the same. The TFT structure includes a multi-layer graphene quantum carbon substrate, a first source, a first drain, a first gate insulating layer, and a first gate. The multi-layer graphene quantum carbon substrate includes a first channel area, and a first drain area and a first source area that are located at corresponding recessed positions on the multi-layer graphene quantum carbon substrate that are separated from each other. The first channel area is located between the first drain area and the first source area, the first source is filled in the first source area, the first drain is filled in the first drain area, the first gate insulating layer is disposed on the first channel area, and the first gate is disposed on the first gate insulating layer.

Owner:GUANG DONG DONGBOND TECH CO LTD

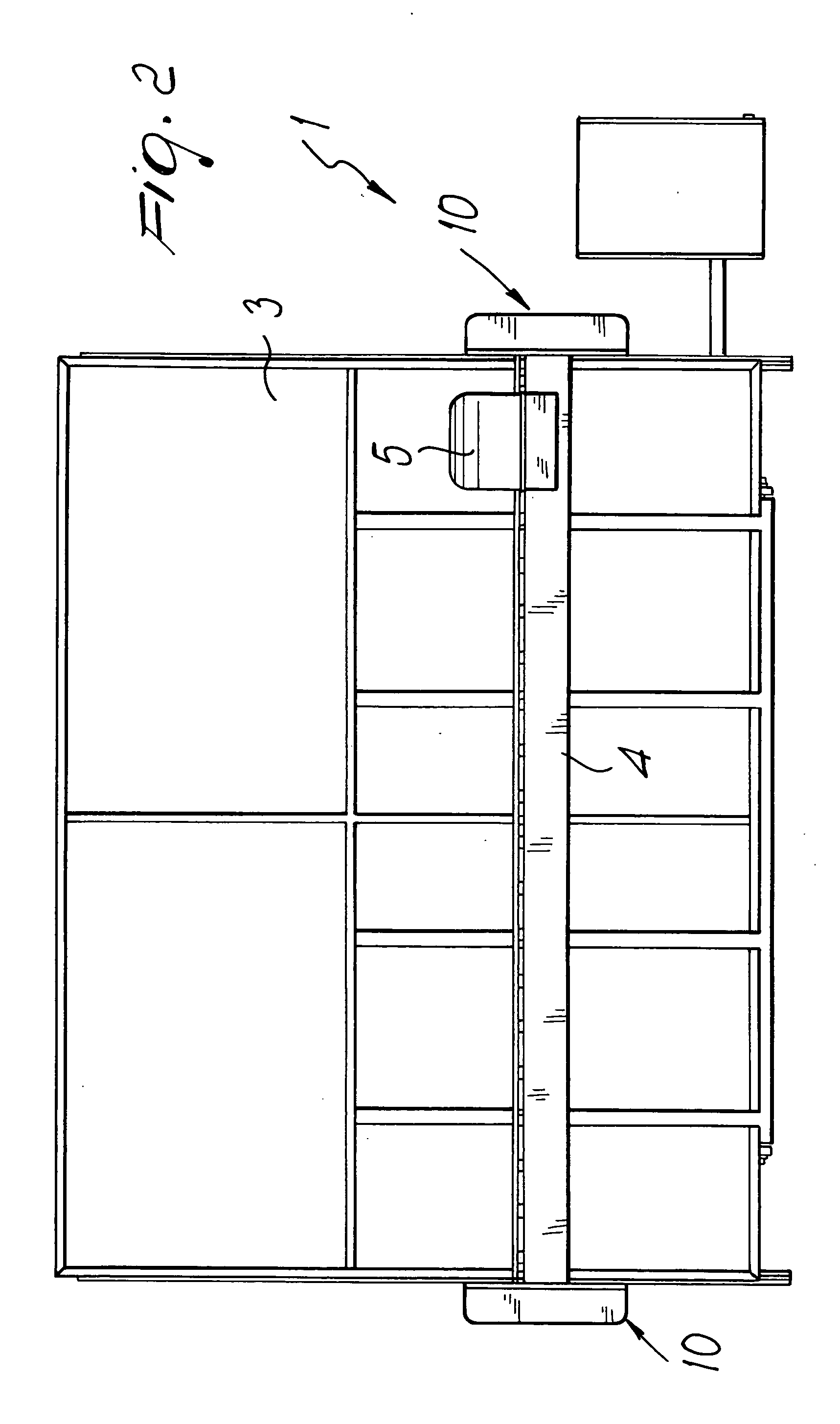

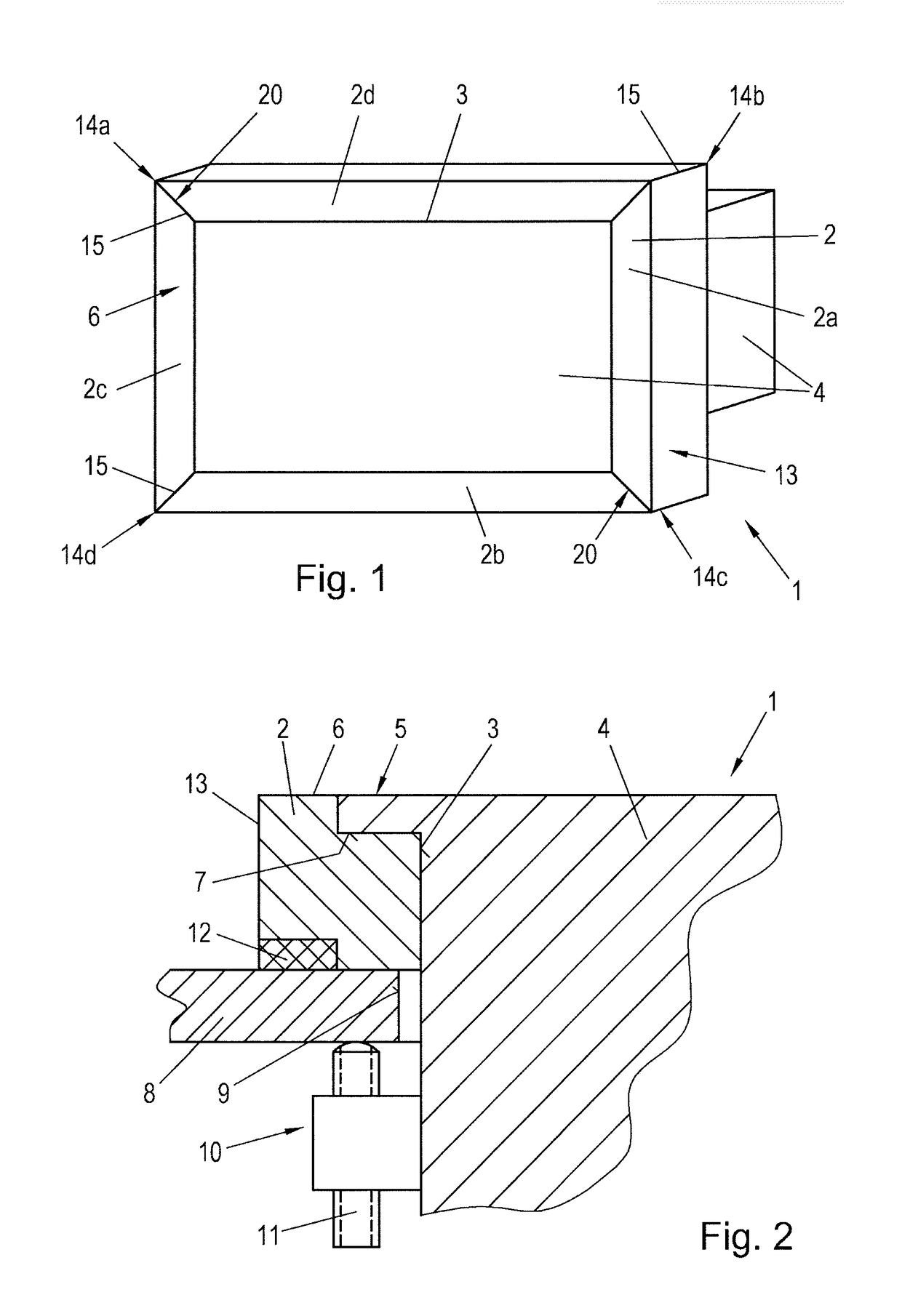

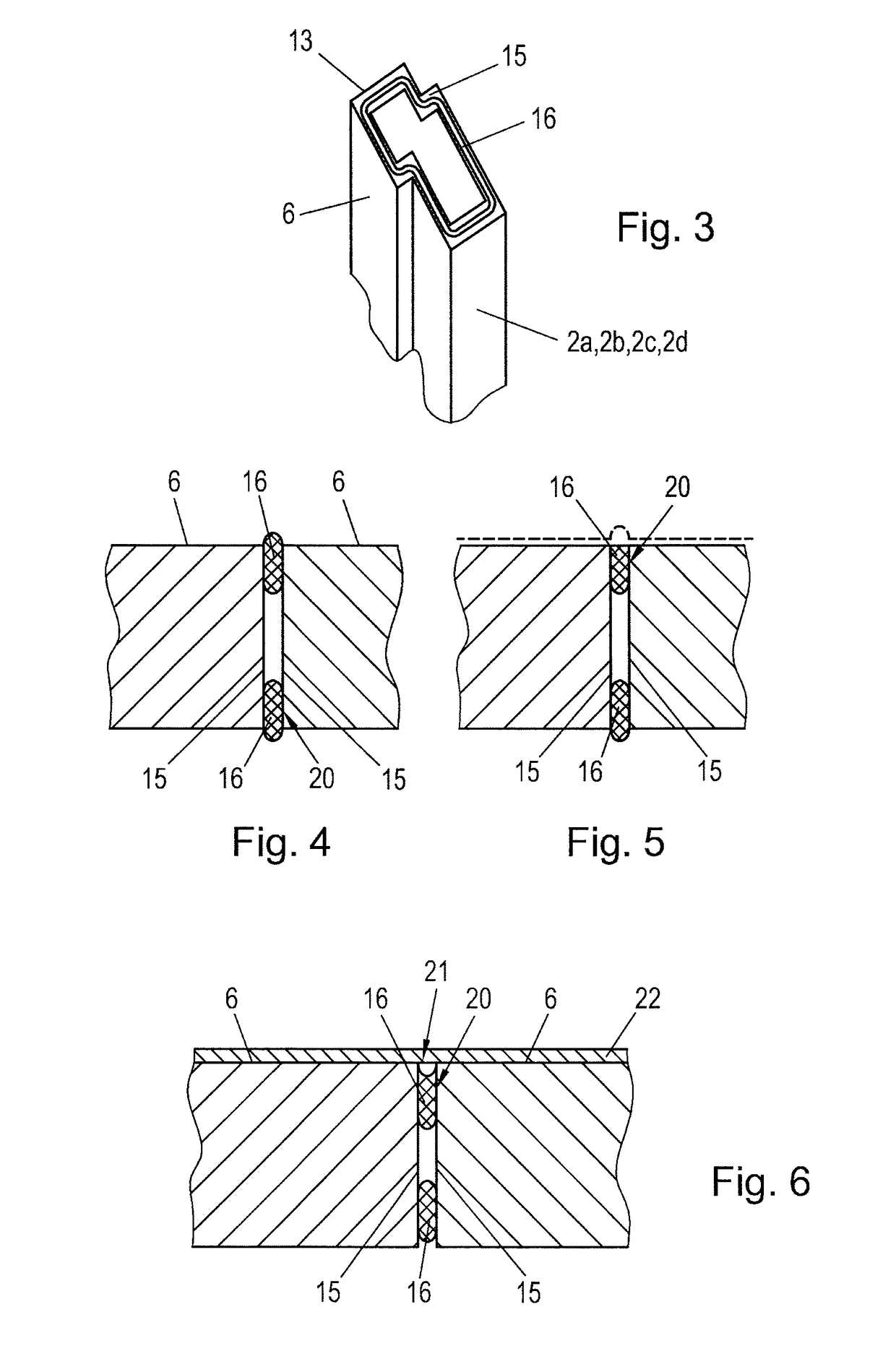

Input and output device with frame

ActiveUS10178788B2Easy to manufactureGood lookingTelevision system detailsDigital data processing detailsEngineeringOutput device

In order to manufacture an input and output device industrial use as cost-effectively as possible, while also fulfilling the demanding requirements in an industrial environment, it is provided that the frame of the input and output device is assembled from a plurality of individual frame sections which are connected to one another at the corners in order to form the frame and which are firmly bonded at the adjoining connecting surfaces in order to form a fully sealed external front face of the frame and a fully sealed external peripheral surface of the frame.

Owner:B&R IND AUTOMATION GMBH

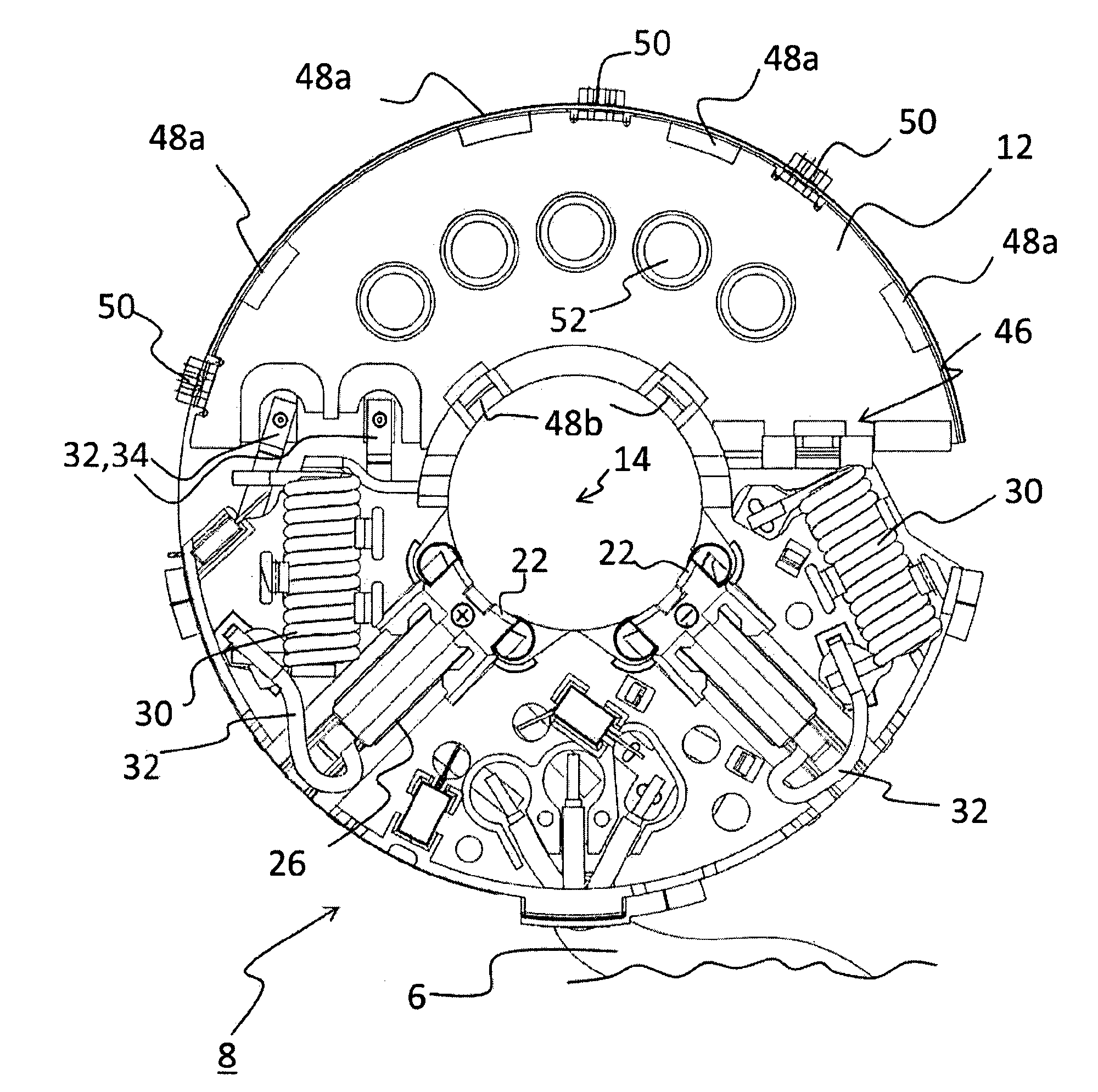

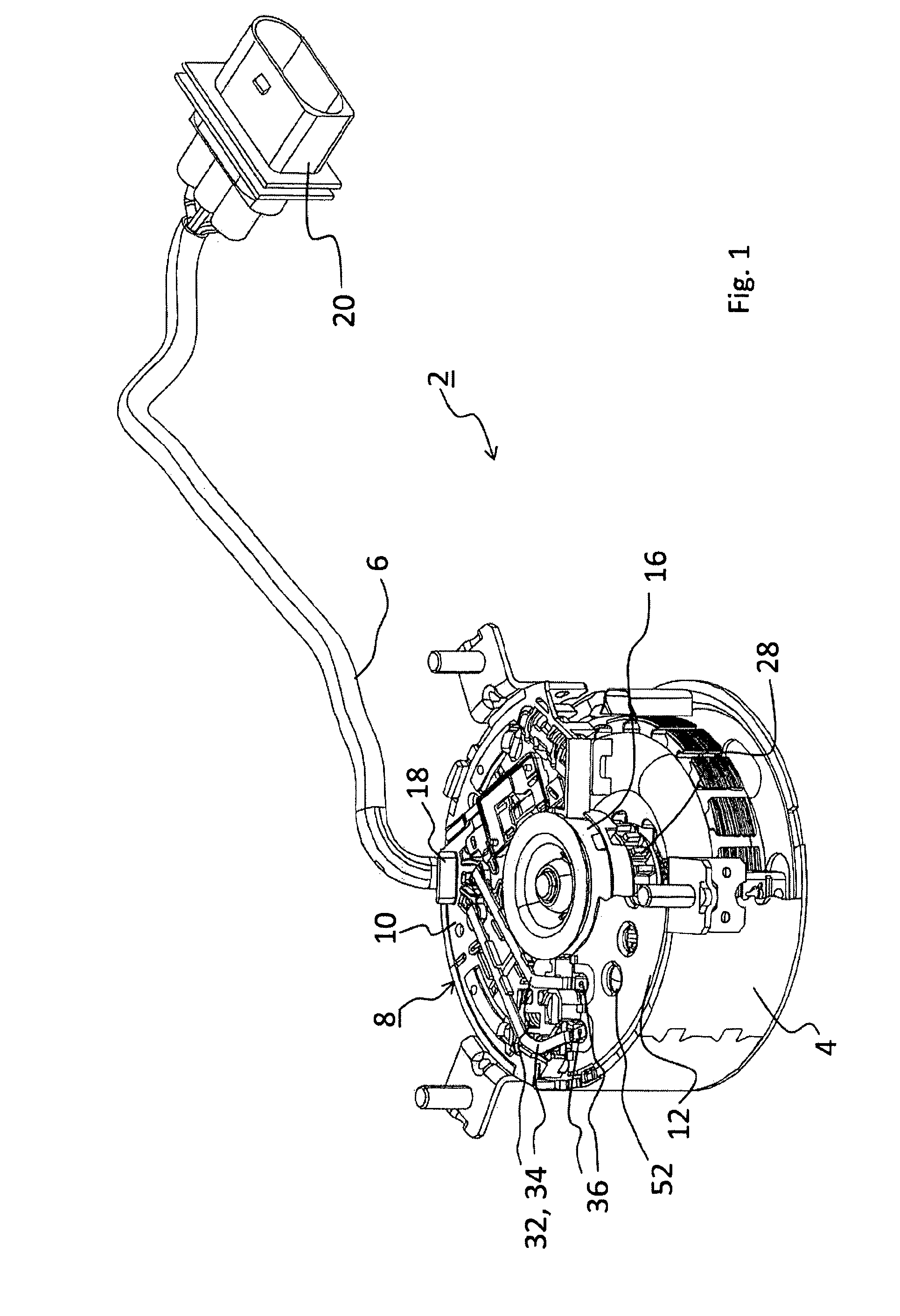

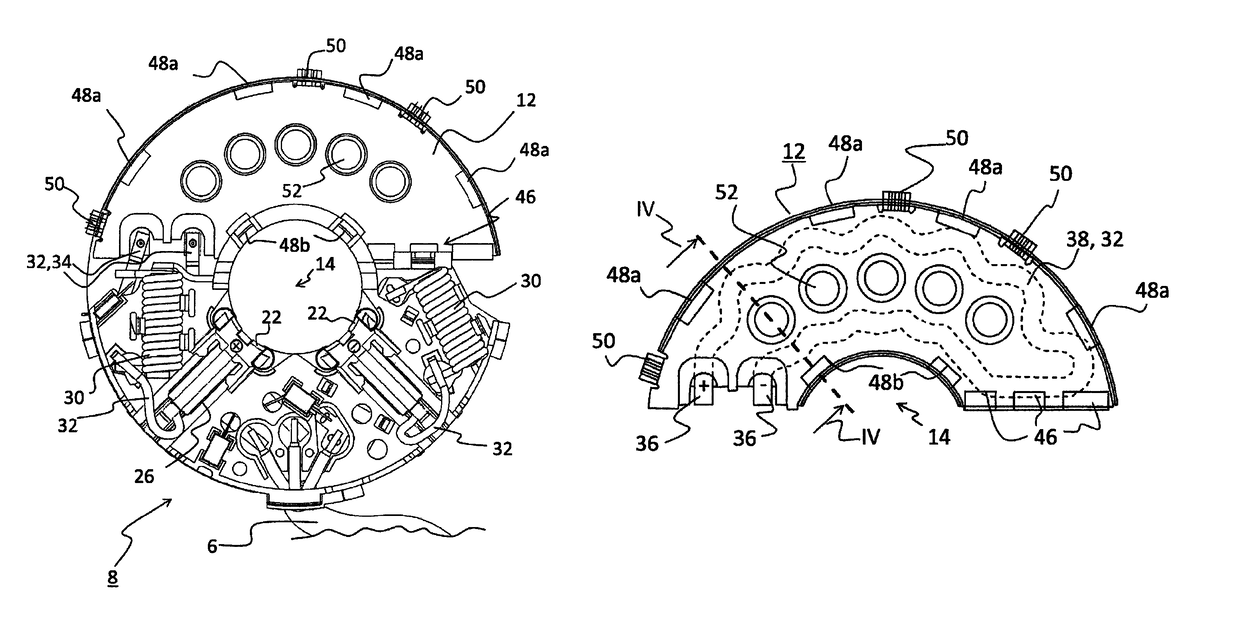

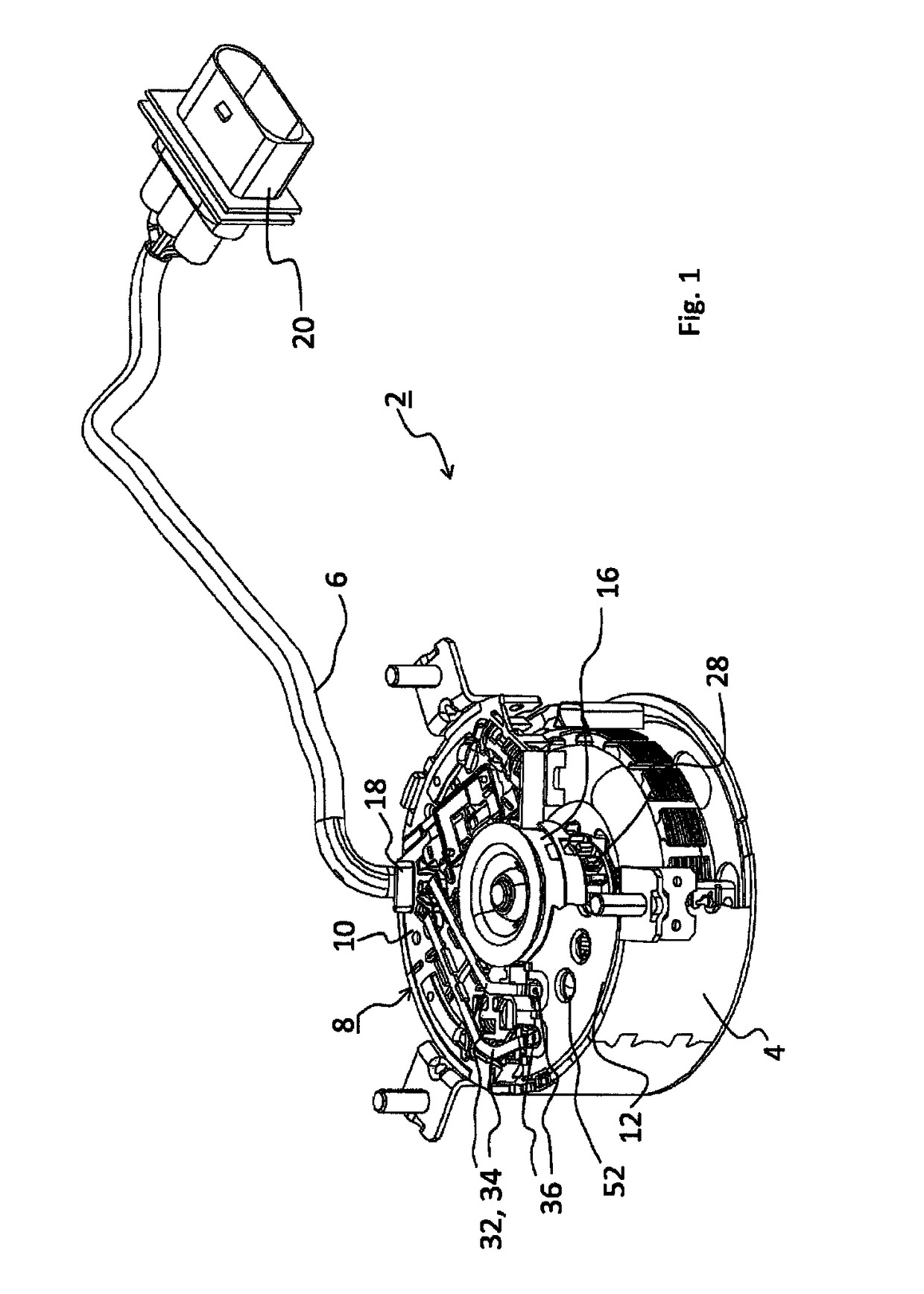

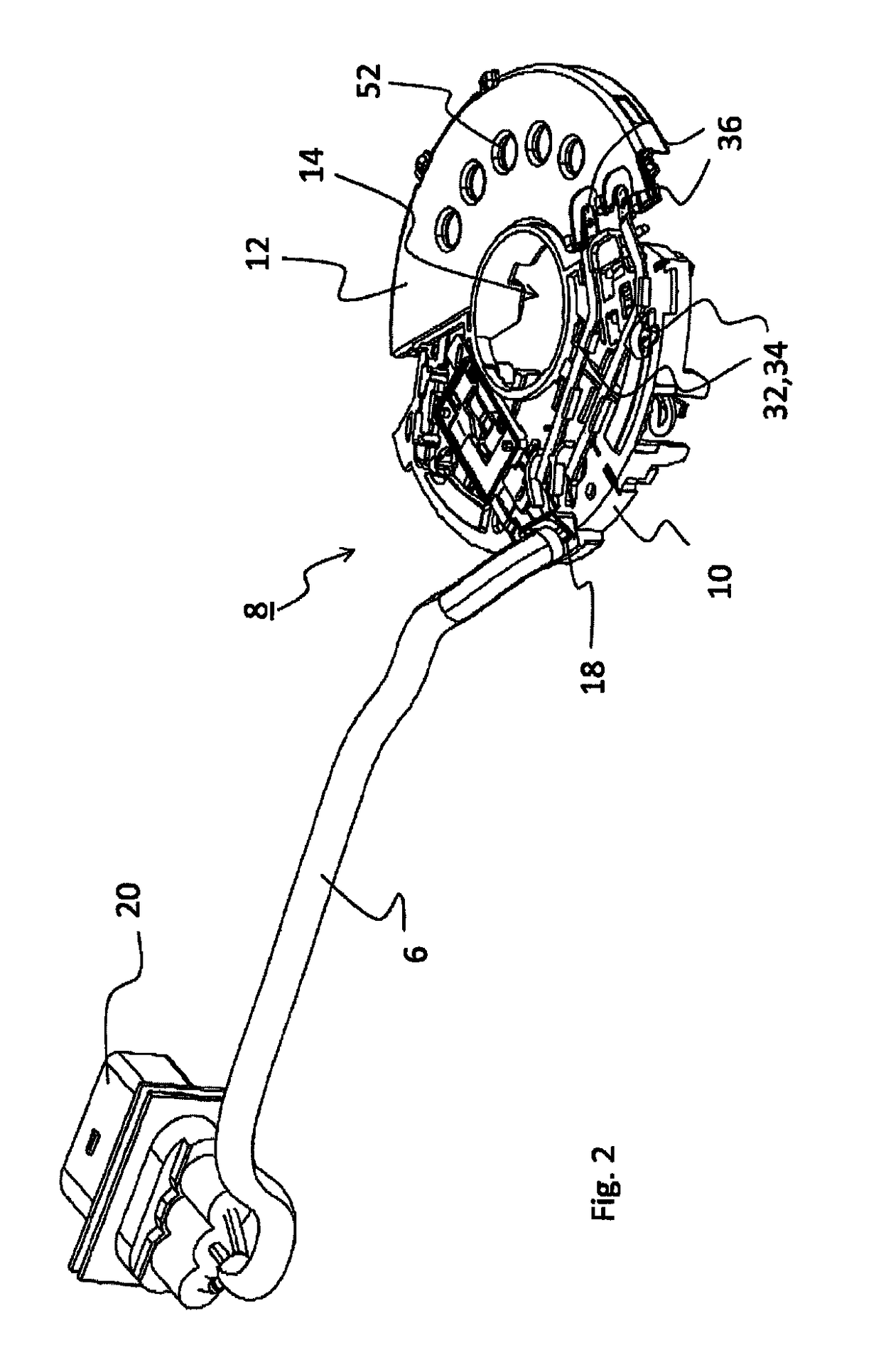

Brush system for an electric motor

ActiveUS20150084479A1Cost-effectivePrecise positioningRotary current collectorDC commutatorElectrical conductorEngineering

A brush system for an electric motor, having a substantially semiannular resistor housing into which an electric flat resistor is introduced, two resistor terminals which protrude from the resistor housing and can be coupled in an electrically conducting manner to a conductor path of the electric motor, and a substantially semi-circular support plate that includes two bus bars to electroconductively couple the conductor path to the terminals and to two brush elements. The two terminals are arranged on the same narrow side of the resistor housing.

Owner:BROSE FAHRZEUGTEILE GMBH & CO KG HALLSTADT (DE)

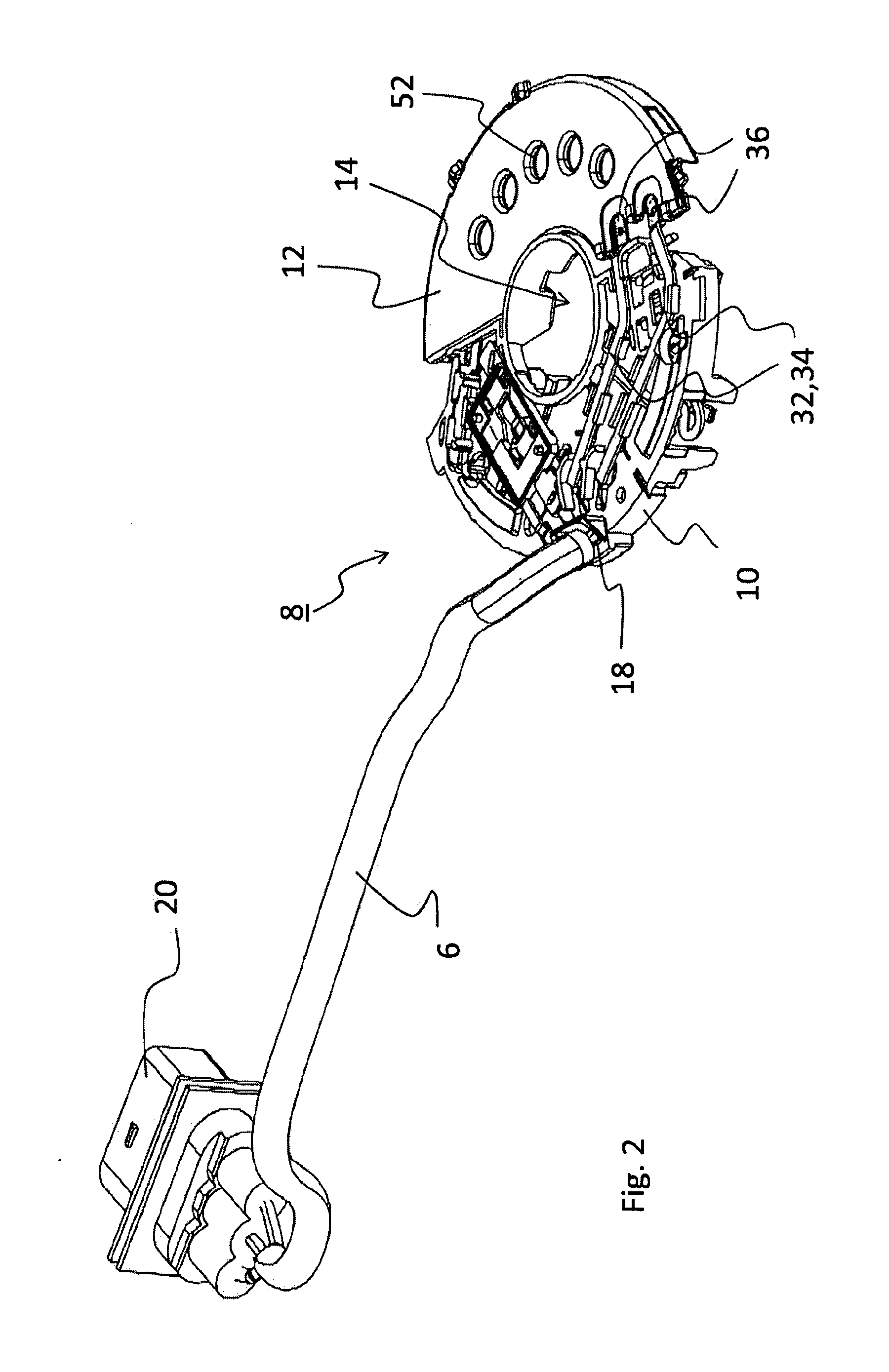

Solenoid Valve having Adjustable Spring Force

ActiveUS20200039491A1Easy to installPromote exchangeOperating means/releasing devices for valvesVehicle sub-unit featuresSolenoid valveSpring force

A solenoid valve, in particular for controlling a brake pressure of a wheel brake of a motor vehicle, includes a pole core, an axially moveably mounted armature, a valve element, a closure element, a plunger, and a pressure spring. One end of the armature is associated with the pole core. The valve sealing element is arranged at another end of the armature. The armature has an axial through-opening. The closure element is force-lockingly and / or interlockingly retained in the axial through-opening in a selectable position. The plunger is axially moveably mounted in the axial through-opening, which provides a connection to the pole core in an installation position. The pressure spring is positioned in the axial through-opening and is retained in a pretensioned manner between the plunger and the closure element. The closure element is designed as a three-dimensionally convex element.

Owner:ROBERT BOSCH GMBH

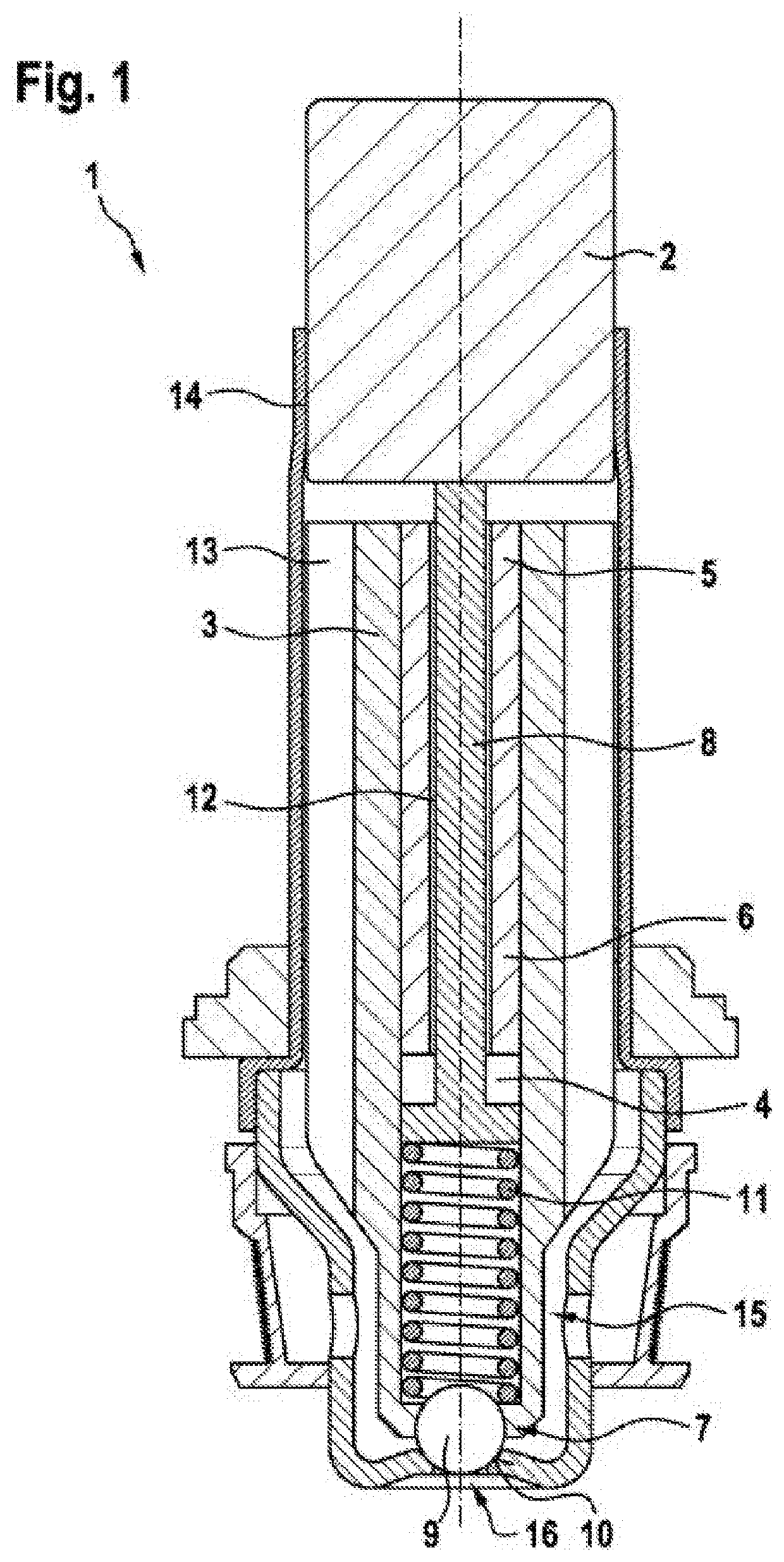

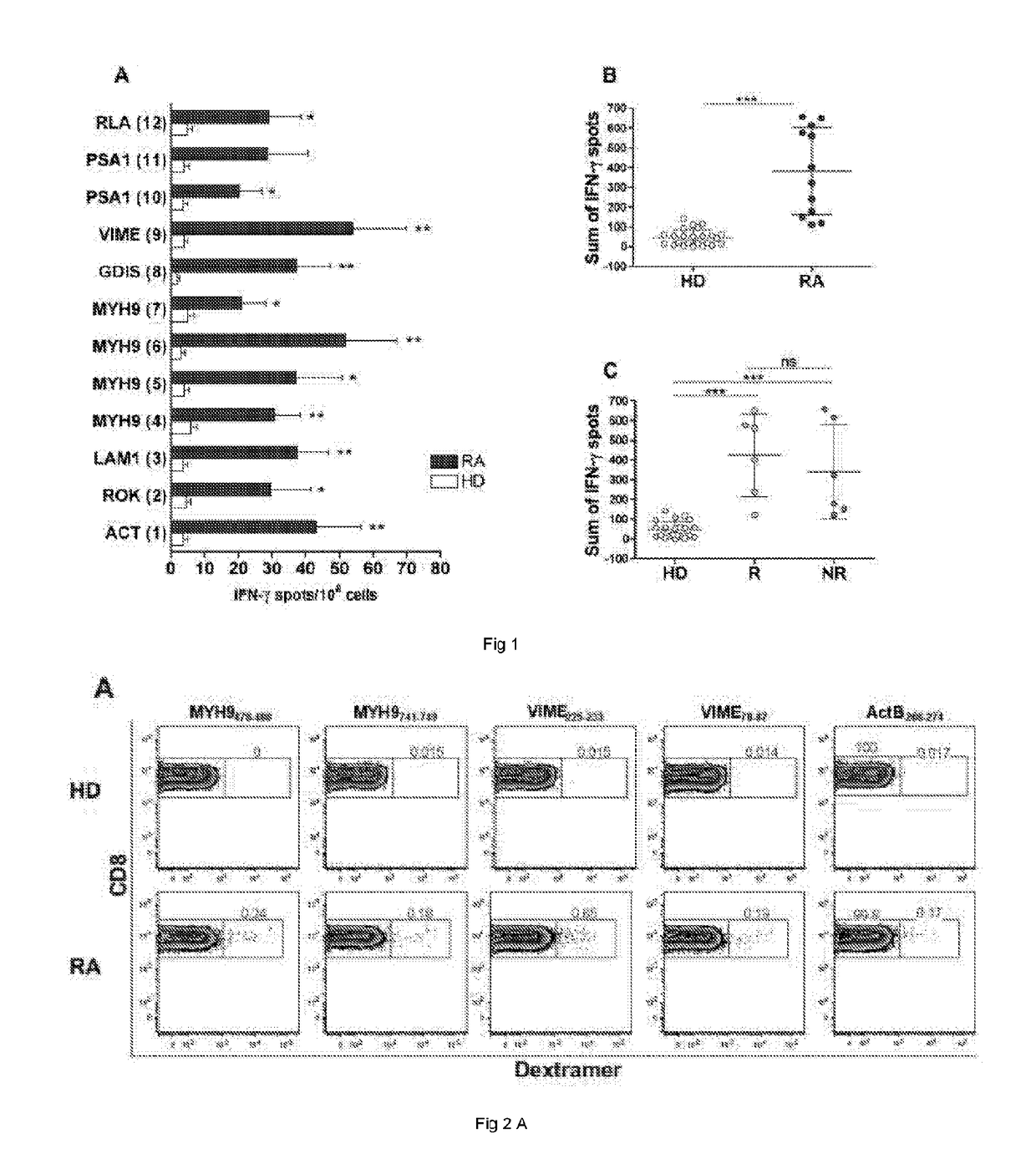

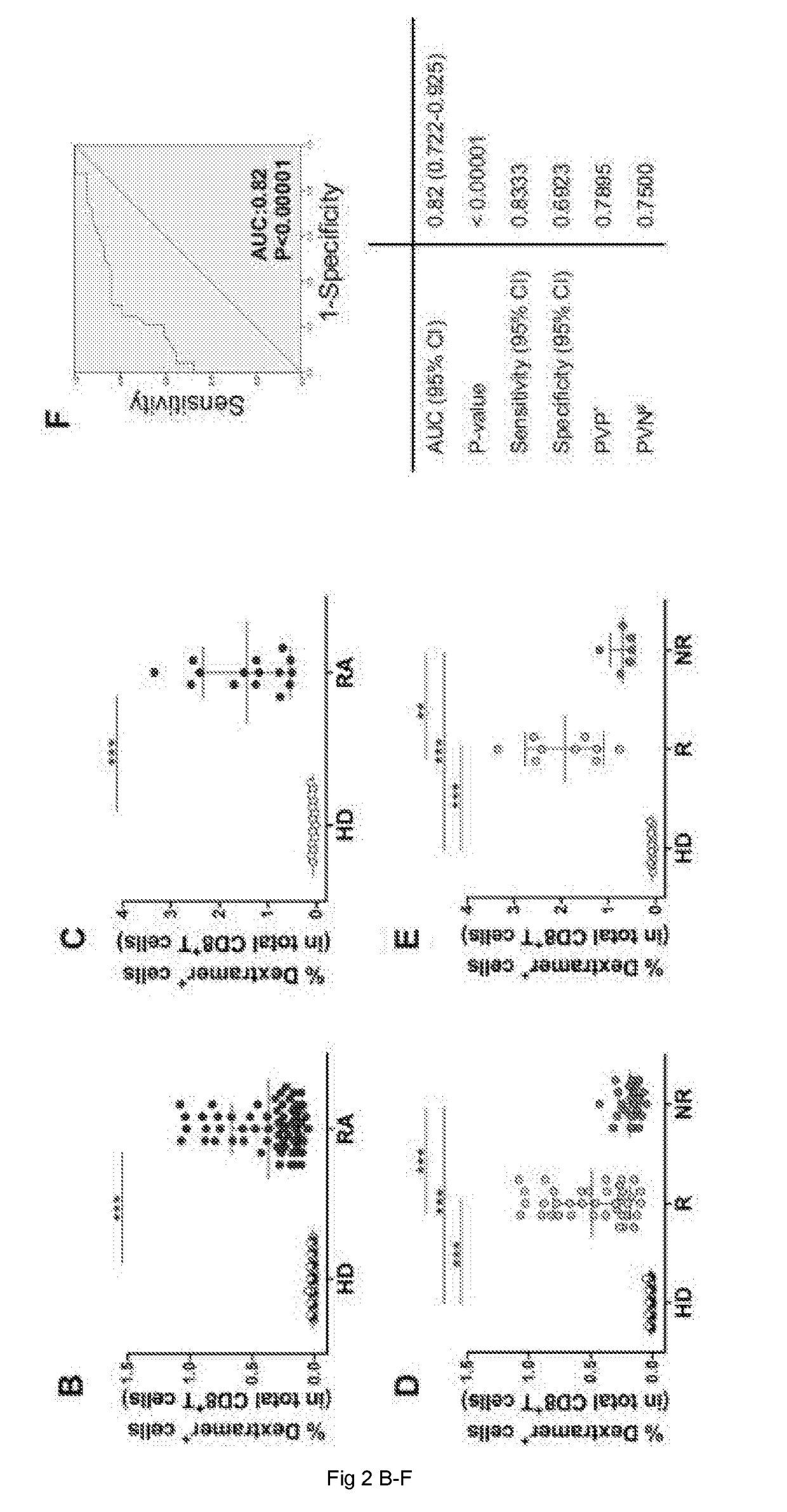

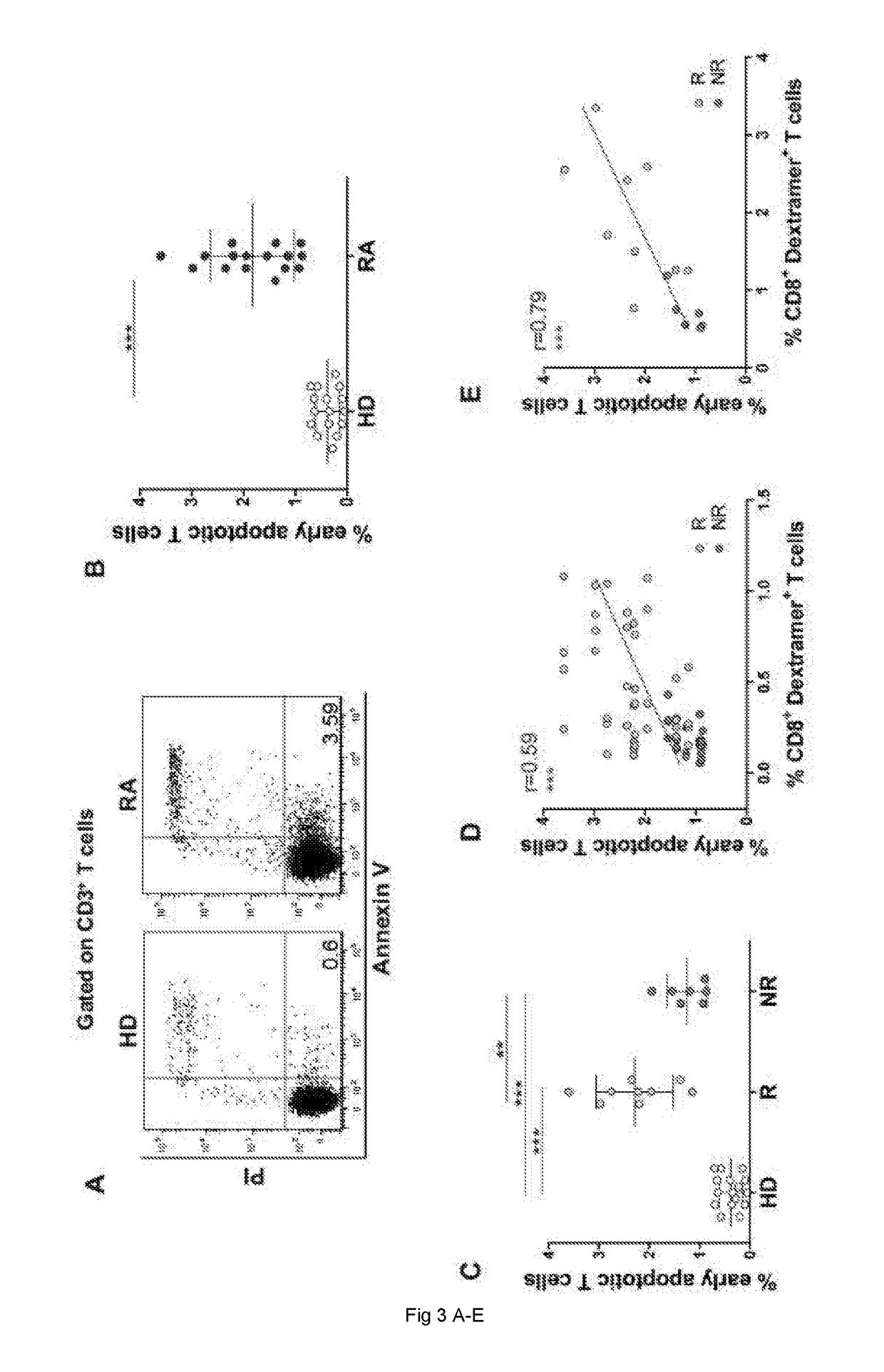

Method and kit for the predictive prognosis of responsiveness to treatments of autoimmune diseases

InactiveUS20170261505A1Improve economyGreatPeptide/protein ingredientsDisease diagnosisMHC class IAutoimmune condition

The present invention relates to the use of one or more MHC class I molecules dextramers (Dextramers®) associated with peptides corresponding to Apoptotic Epitopes of human CD8+ T cells for the predictive prognosis of responsiveness or non-responsiveness to treatments and / or for monitoring the therapeutic effectiveness of treatments with biological medicaments that block and / or inhibit TNF, and / or biological medicaments that block and / or inhibit cytokines or cytokine receptors and / or biological medicaments against B cells and / or biological medicaments that inhibit T cell co-stimulation in patients affected by autoimmune diseases, together with methods and kits for said predictive prognosis.

Owner:UNIV DEGLI STUDI DI ROMA

Stable Free Radical Chromophores and Mixtures Thereof, Processes for Preparing the Same, Nonlinear Optic Materials, and Uses Thereof in Nonlinear Optical Applications

InactiveUS20150048285A1GreatImprove rigidityOrganic chemistryFinal product manufactureNonlinear optical crystalChromogenic

Nonlinear optic chromophores comprising stabilized radical structures, mixtures thereof, methods for their production, nonlinear optical materials containing such chromophores, and the use of such materials in electro-optic, solar conversion, photovoltaic and all-optical nonlinear devices are described.

Owner:LIGHTWAVE LOGIC INC

Brush system for an electric motor

ActiveUS9774231B2Improved cable routingPrecise positioningDC commutatorStructural associationElectrical conductorEngineering

A brush system for an electric motor, having a substantially semiannular resistor housing into which an electric flat resistor is introduced, two resistor terminals which protrude from the resistor housing and can be coupled in an electrically conducting manner to a conductor path of the electric motor, and a substantially semi-circular support plate that includes two bus bars to electroconductively couple the conductor path to the terminals and to two brush elements. The two terminals are arranged on the same narrow side of the resistor housing.

Owner:BROSE FAHRZEUGTEILE GMBH & CO KG HALLSTADT (DE)

TFT structure based on flexible multi-layer graphene quantum carbon substrate material and method for manufacturing same

A TFT structure based on a flexible multi-layer graphene quantum carbon substrate material and a method for manufacturing the same. The TFT structure includes a multi-layer graphene quantum carbon substrate, a first source, a first drain, a first gate insulating layer, and a first gate. The multi-layer graphene quantum carbon substrate includes a first channel area, and a first drain area and a first source area that are located at corresponding recessed positions on the multi-layer graphene quantum carbon substrate that are separated from each other. The first channel area is located between the first drain area and the first source area, the first source is filled in the first source area, the first drain is filled in the first drain area, the first gate insulating layer is disposed on the first channel area, and the first gate is disposed on the first gate insulating layer.

Owner:GUANG DONG DONGBOND TECH CO LTD