Patents

Literature

77results about How to "Improve charge balance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

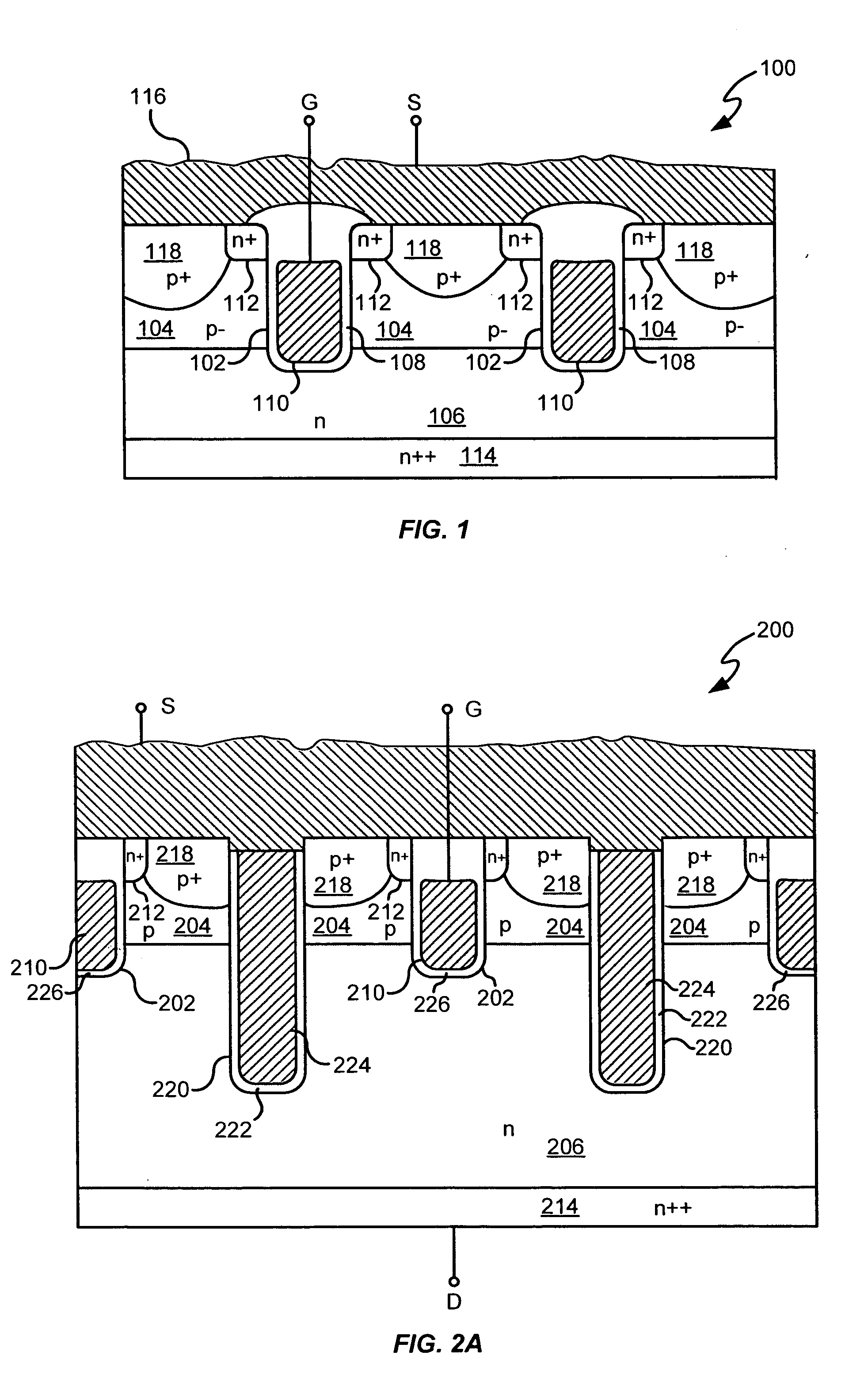

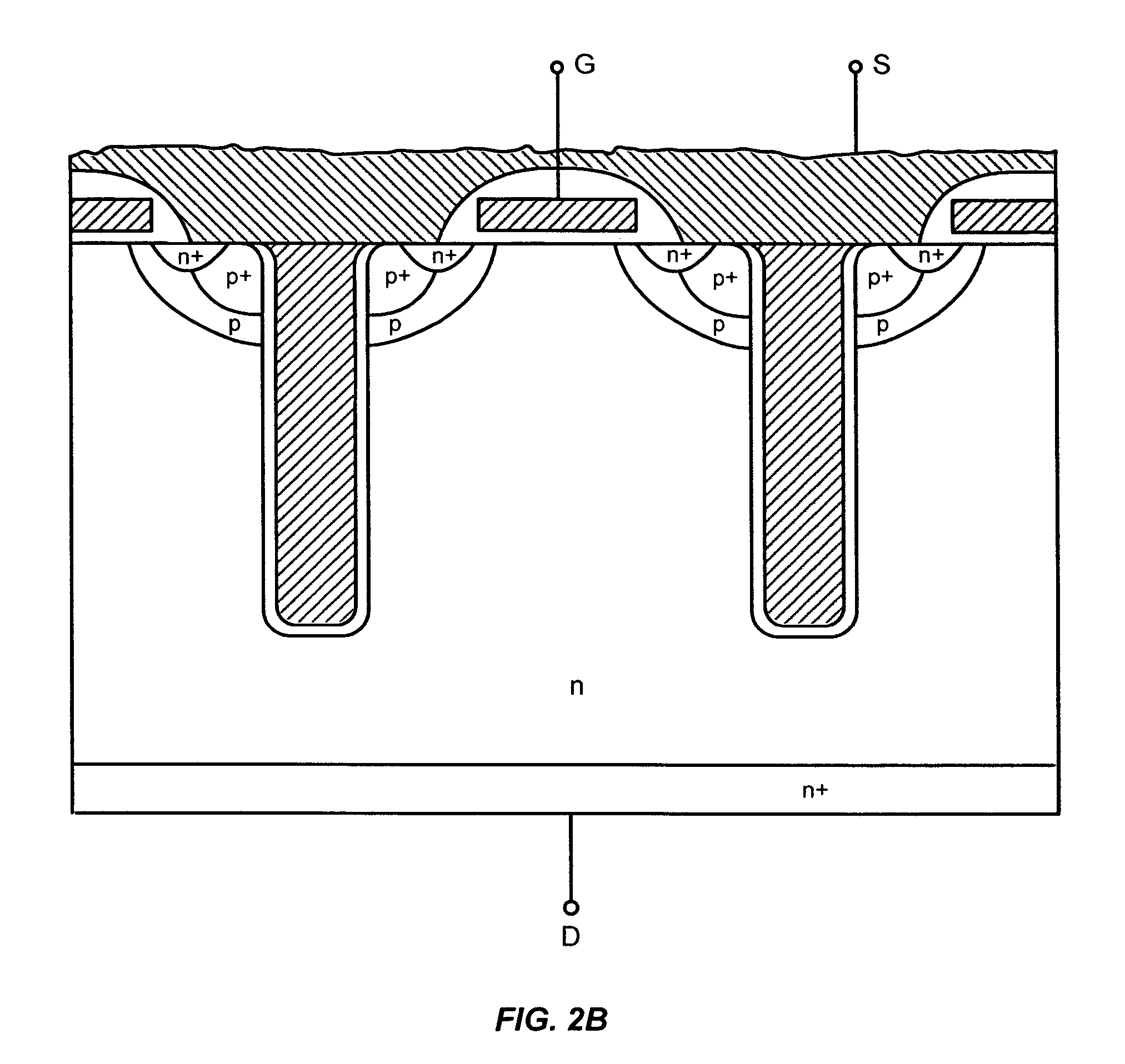

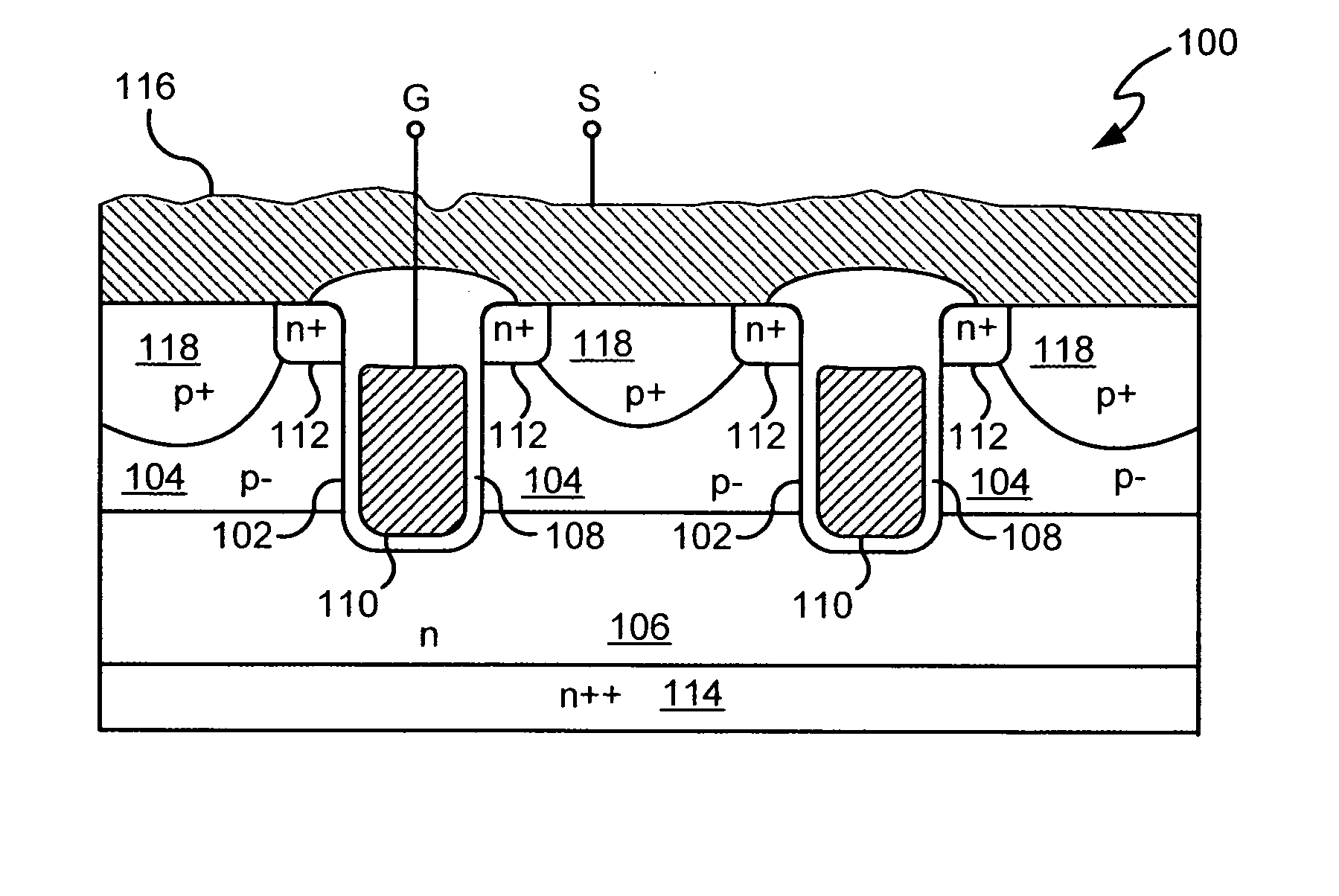

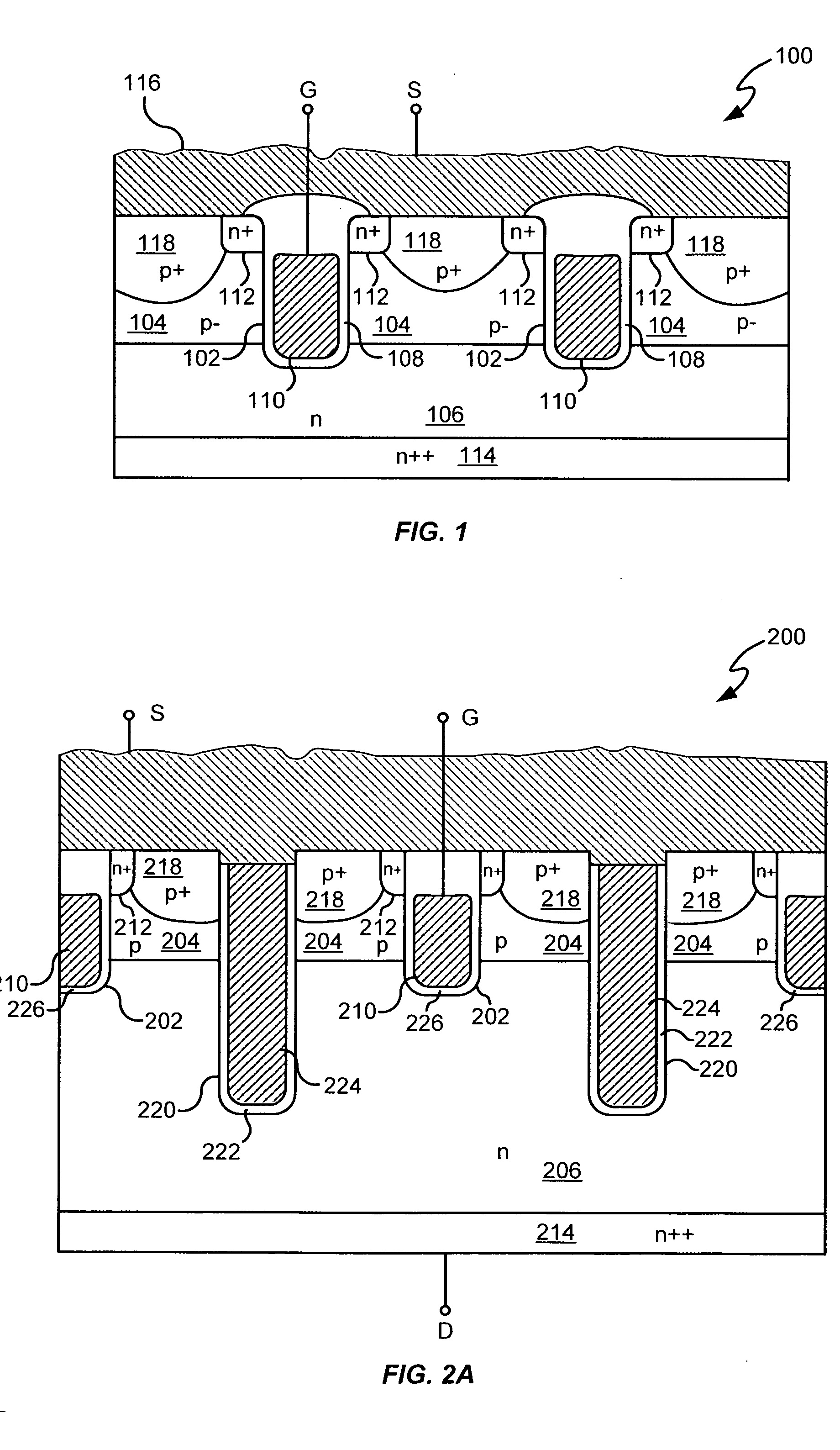

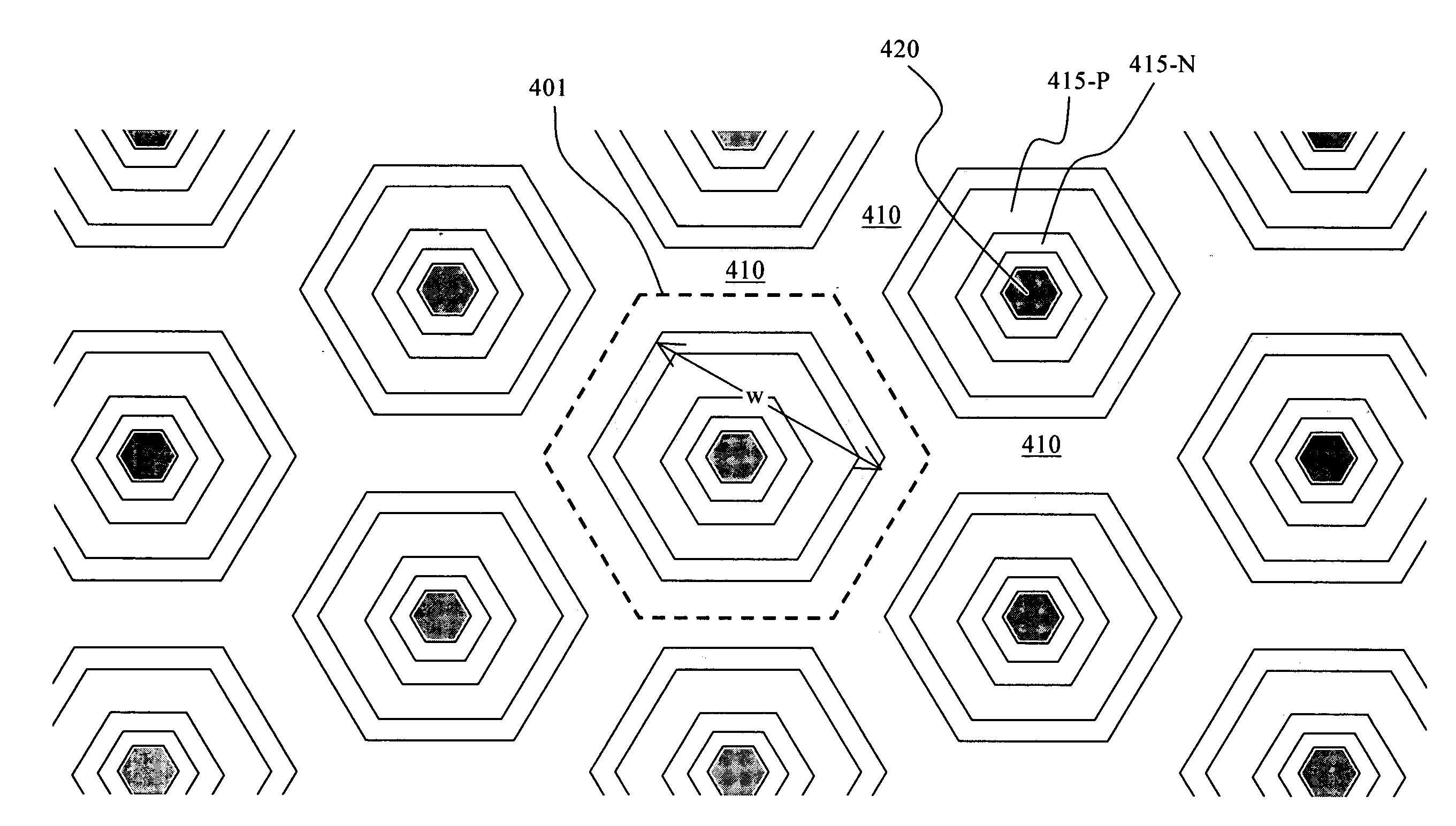

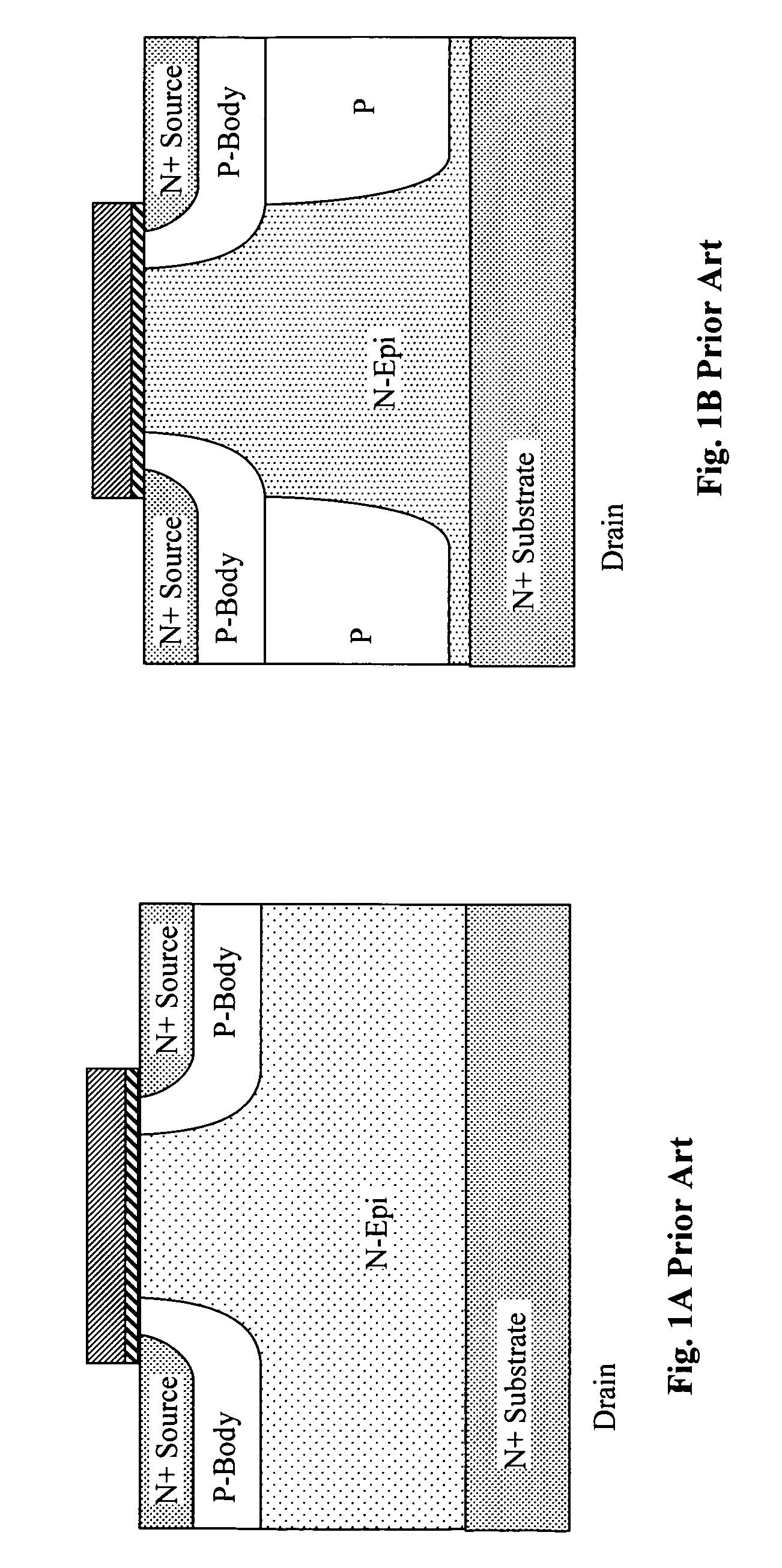

Power semiconductor devices and methods of manufacture

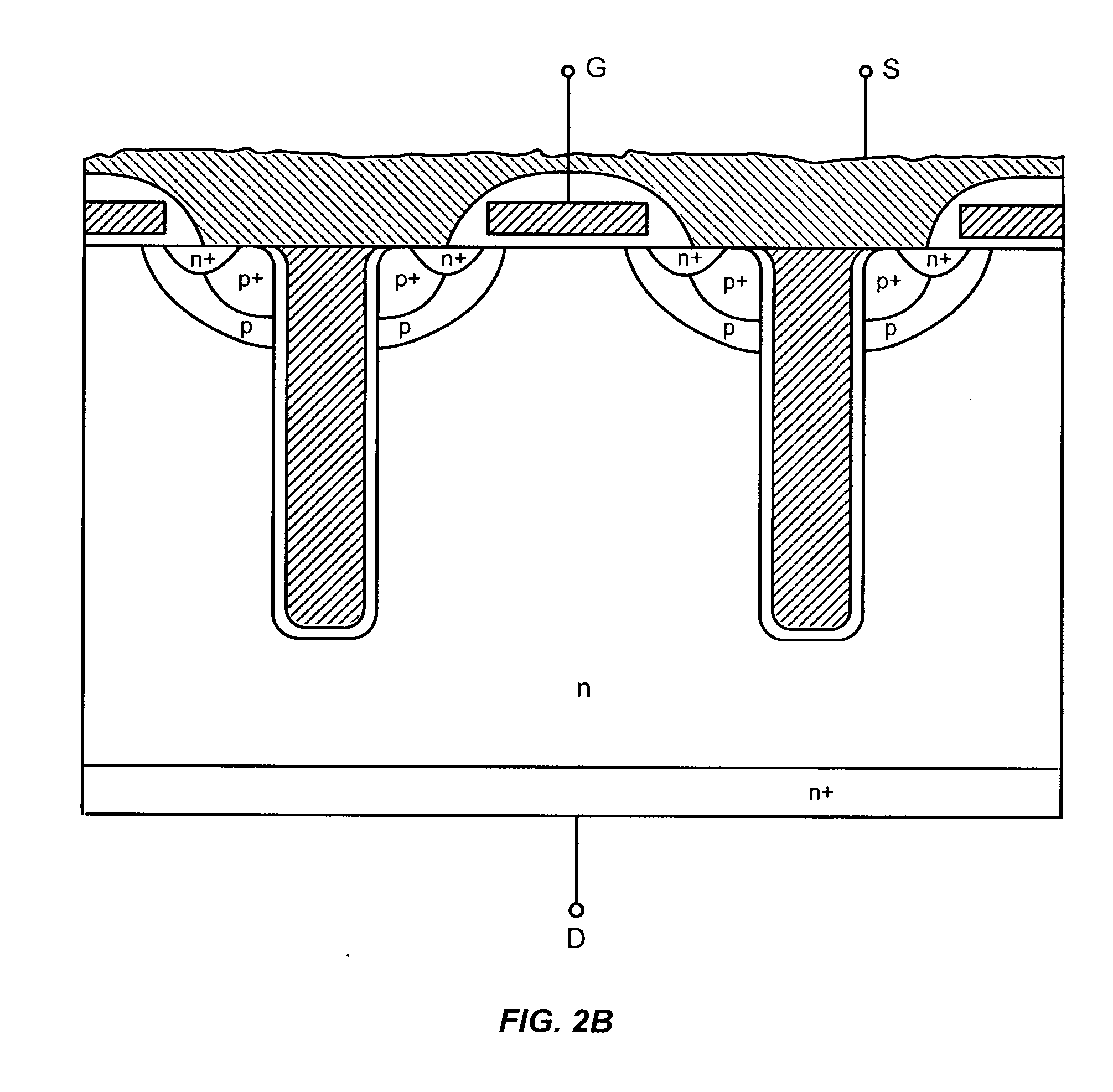

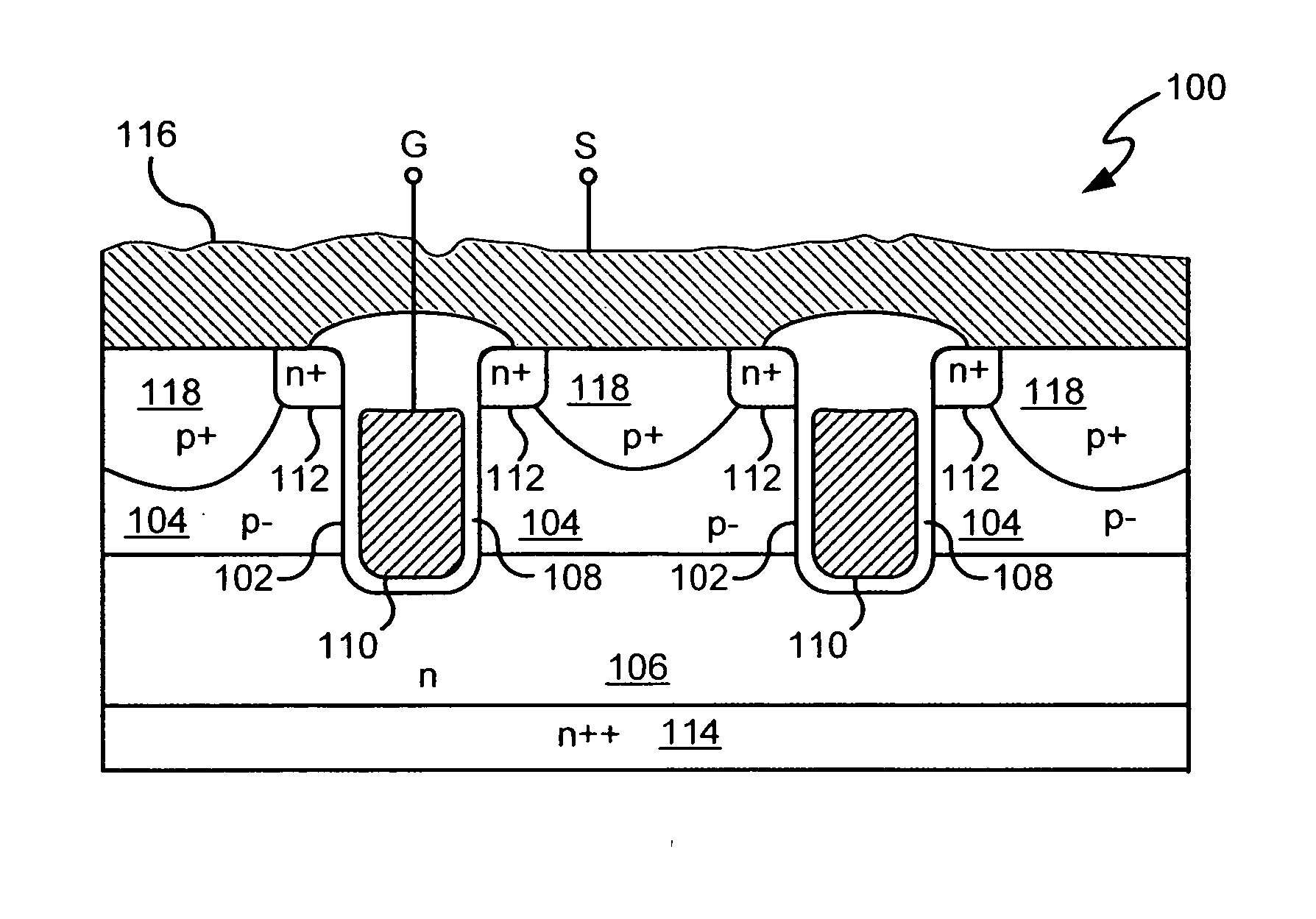

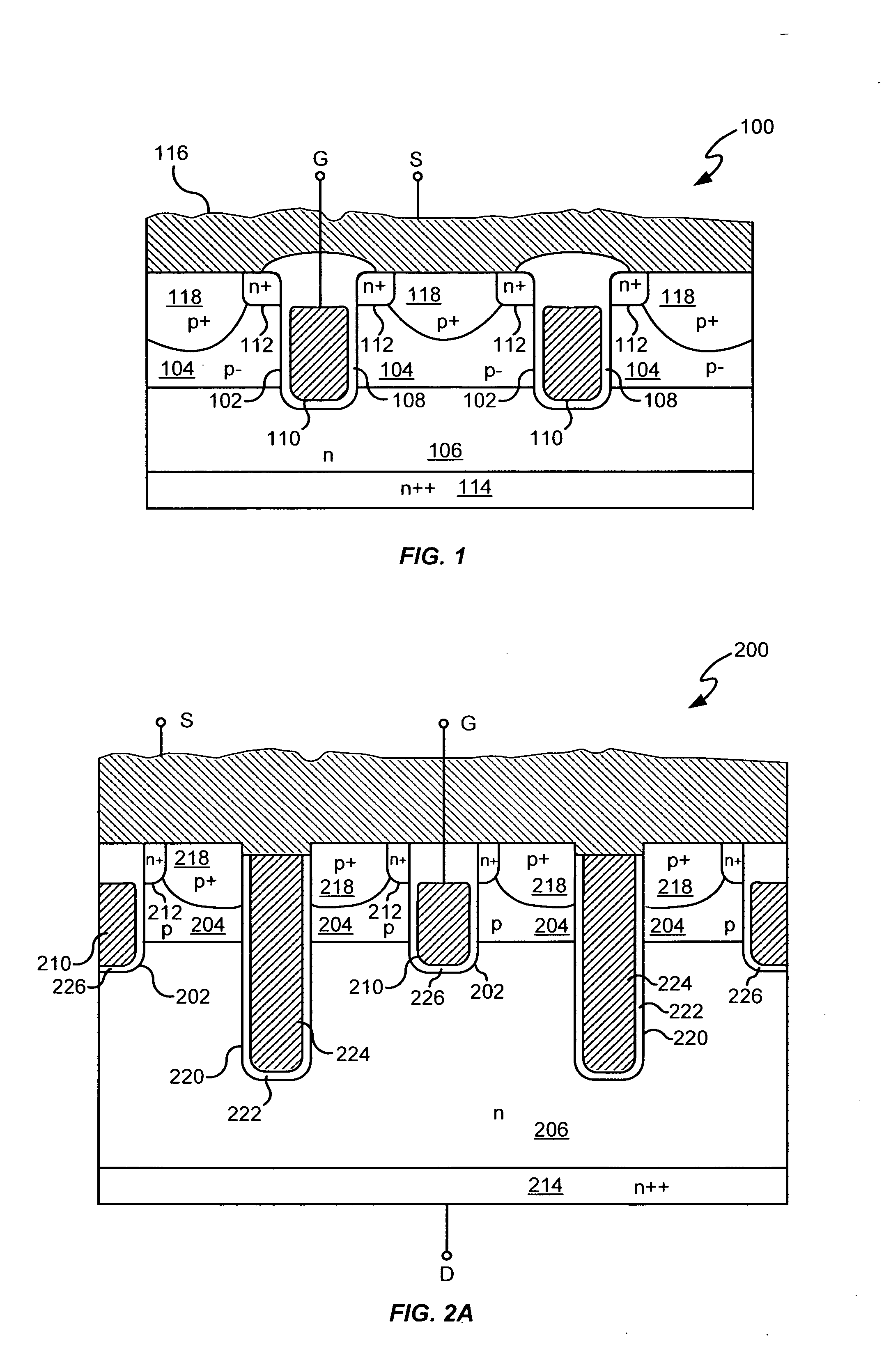

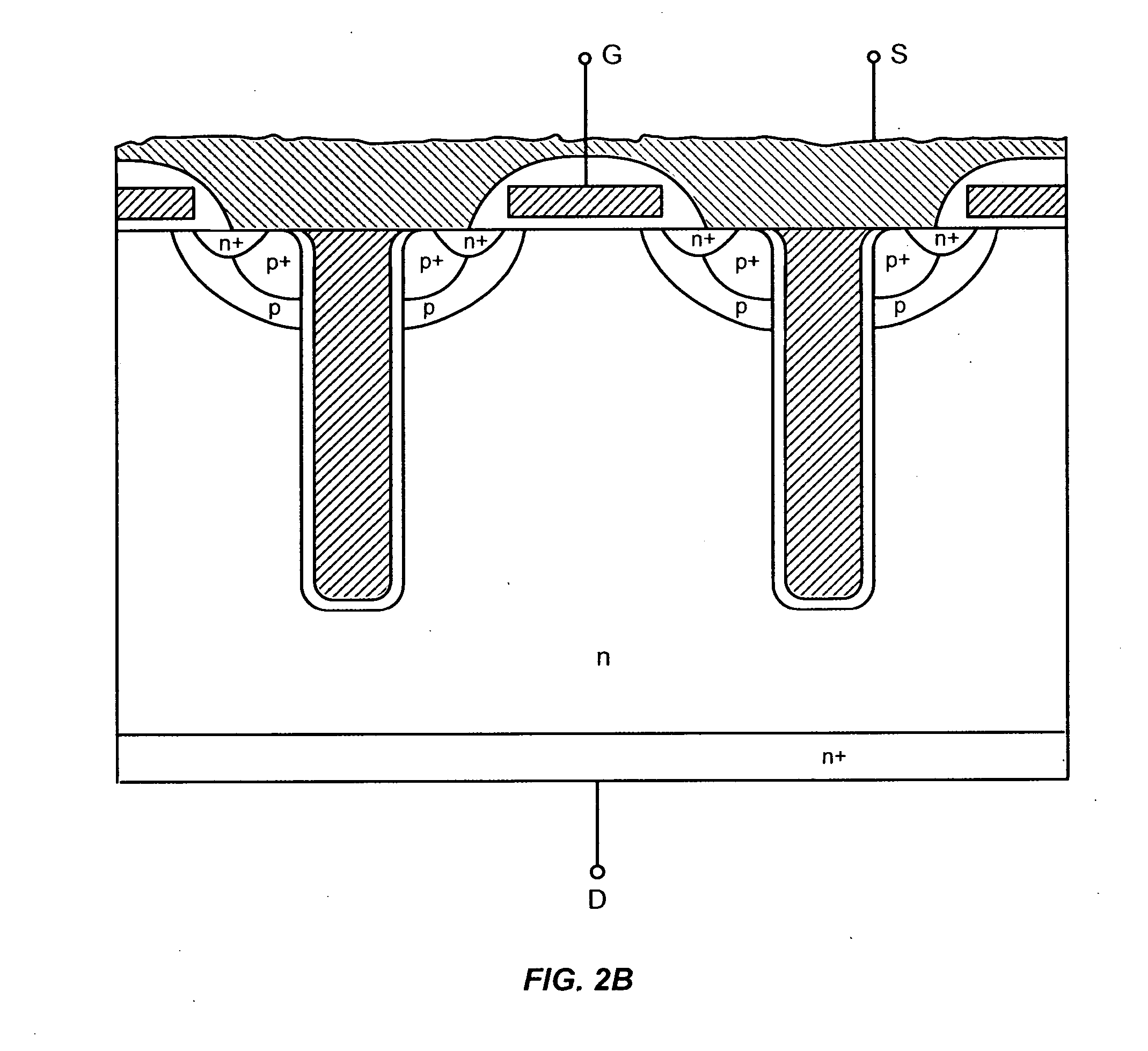

ActiveUS20050167742A1Improved voltage performanceFast switching speedEfficient power electronics conversionSemiconductor/solid-state device detailsEngineeringHigh voltage

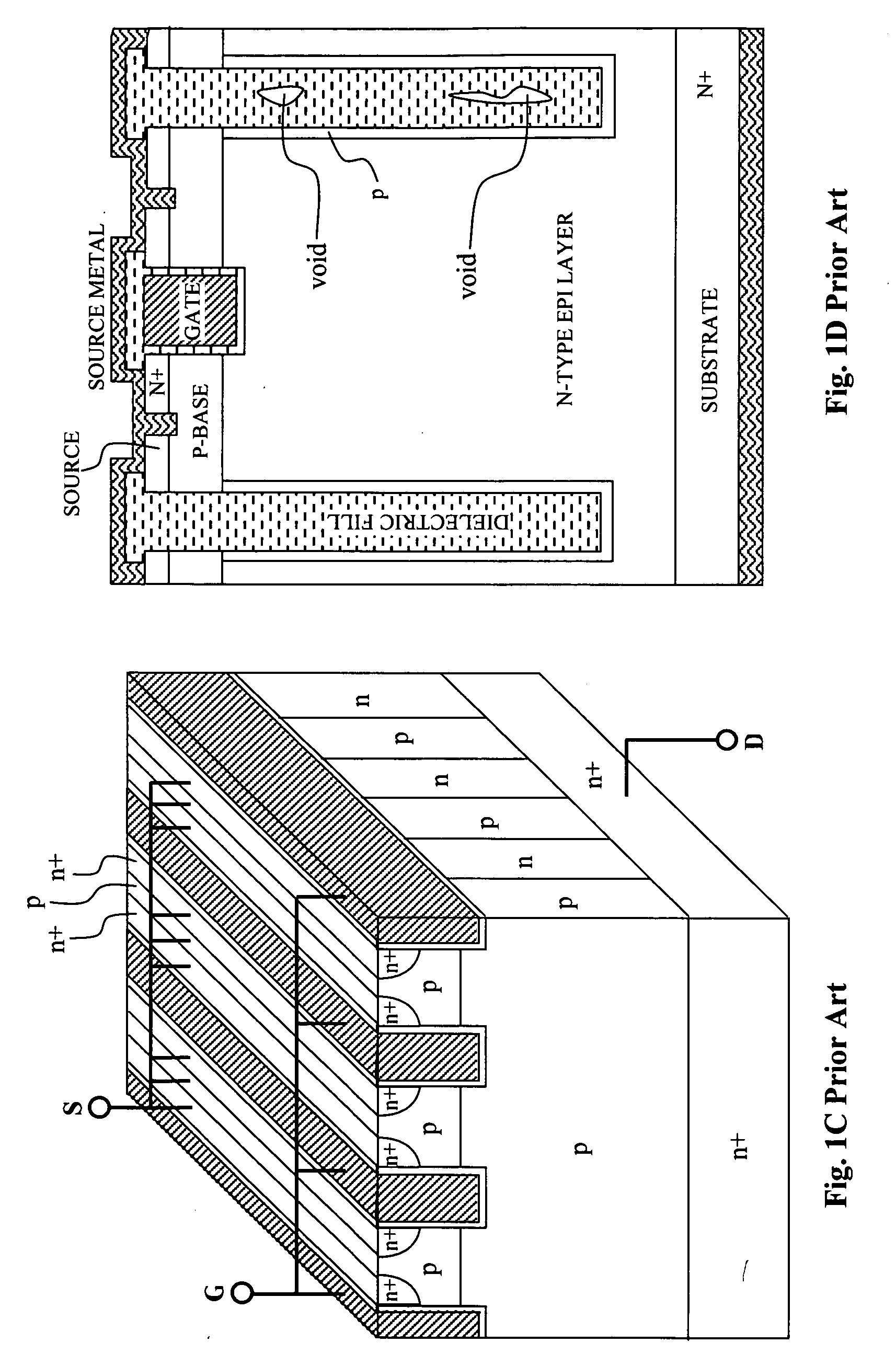

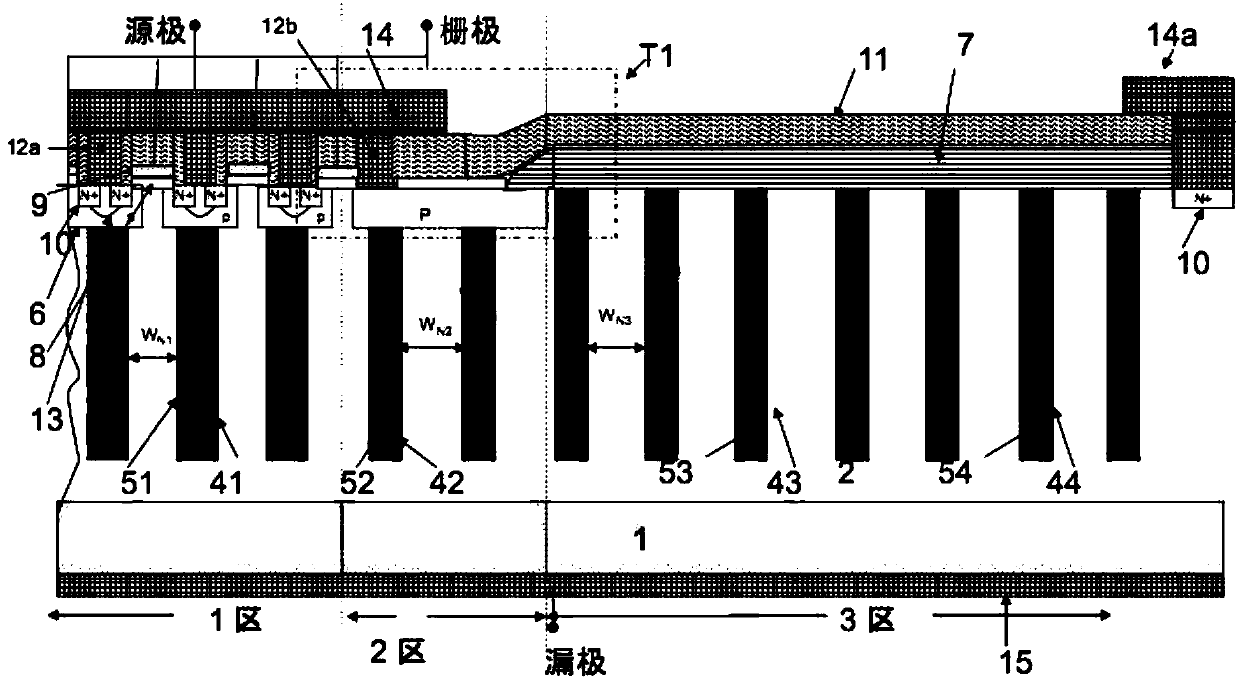

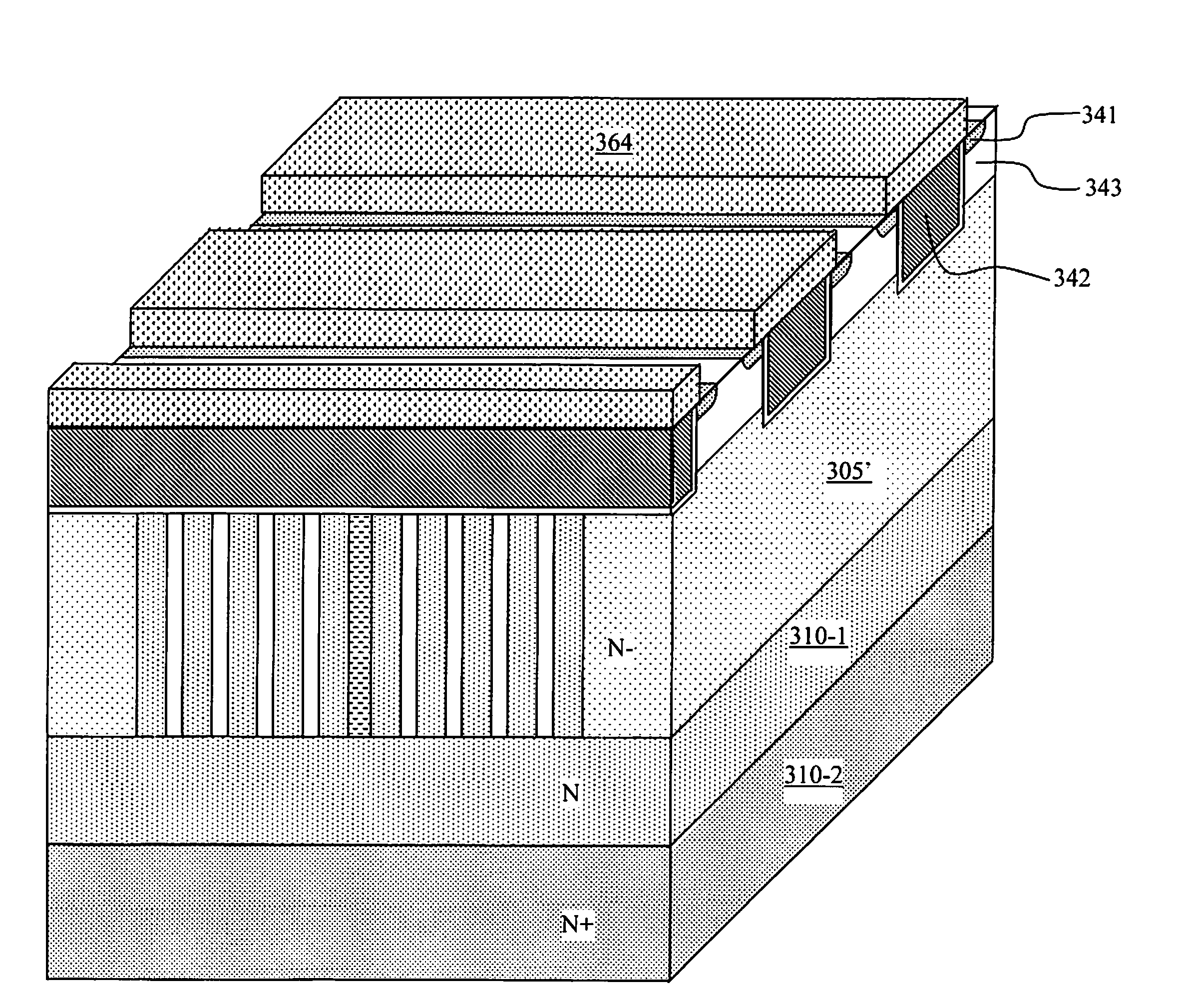

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

Power semiconductor devices and methods of manufacture

InactiveUS20060214221A1Improved voltage performanceFast switching speedTransistorEfficient power electronics conversionEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

Power semiconductor devices and methods of manufacture

ActiveUS20060214222A1Improved voltage performanceFast switching speedTransistorEfficient power electronics conversionEngineeringHigh pressure

Various embodiments for improved power devices as well as their methods of manufacture, packaging and circuitry incorporating the same for use in a wide variety of power electronic applications are disclosed. One aspect of the invention combines a number of charge balancing techniques and other techniques for reducing parasitic capacitance to arrive at different embodiments for power devices with improved voltage performance, higher switching speed, and lower on-resistance. Another aspect of the invention provides improved termination structures for low, medium and high voltage devices. Improved methods of fabrication for power devices are provided according to other aspects of the invention. Improvements to specific processing steps, such as formation of trenches, formation of dielectric layers inside trenches, formation of mesa structures and processes for reducing substrate thickness, among others, are presented. According to another aspect of the invention, charge balanced power devices incorporate temperature and current sensing elements such as diodes on the same die. Other aspects of the invention improve equivalent series resistance (ESR) for power devices, incorporate additional circuitry on the same chip as the power device and provide improvements to the packaging of charge balanced power devices.

Owner:SEMICON COMPONENTS IND LLC

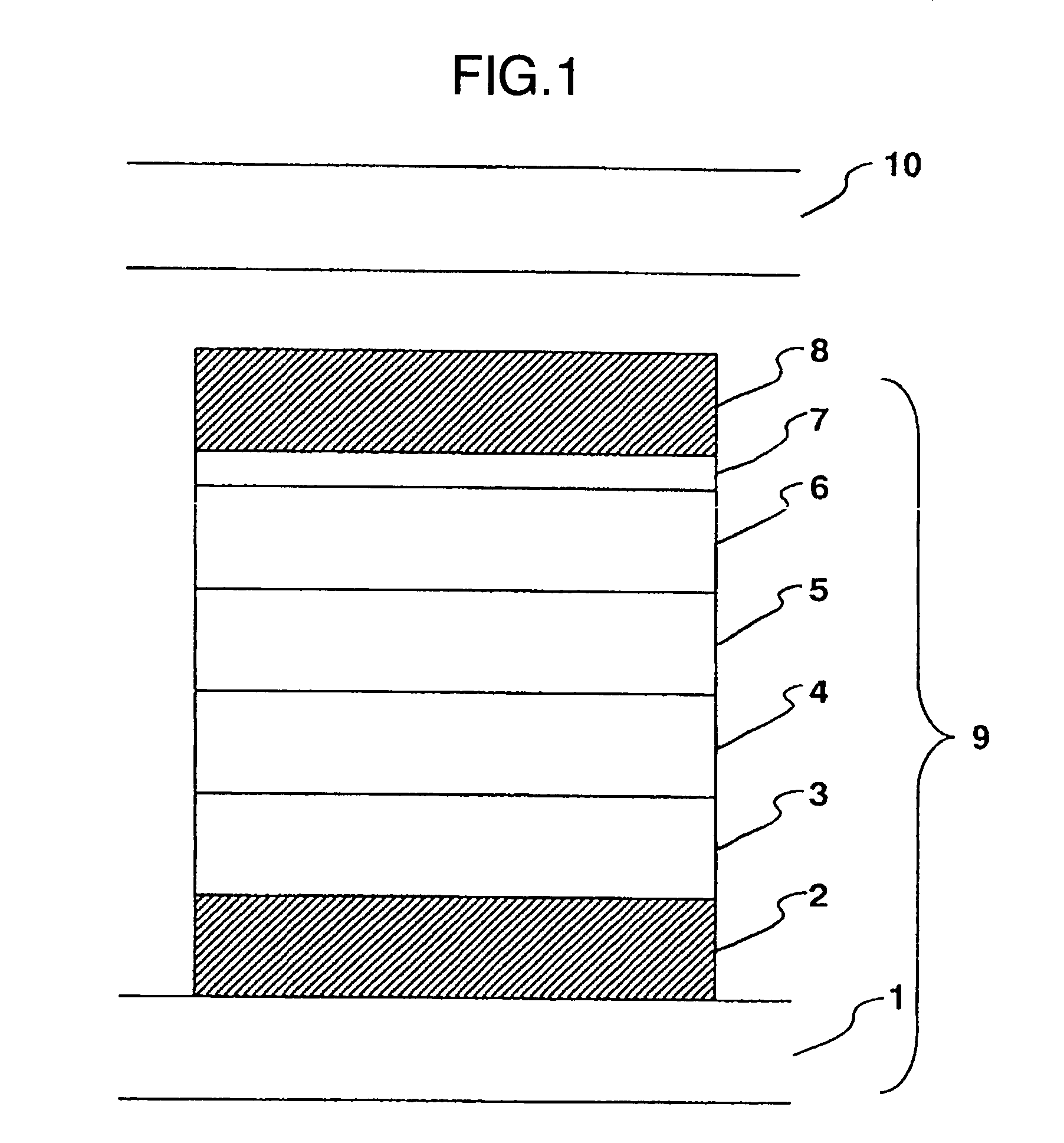

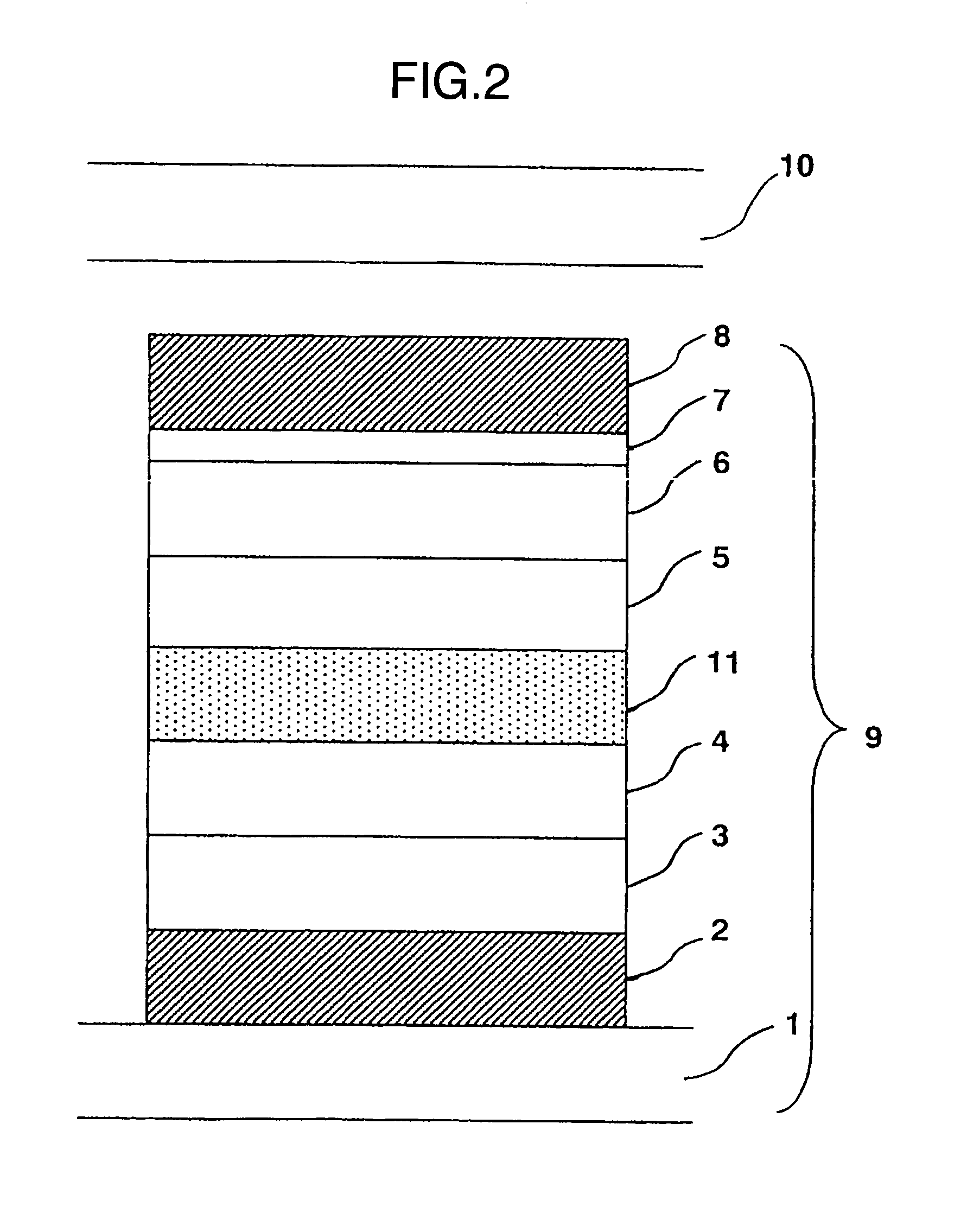

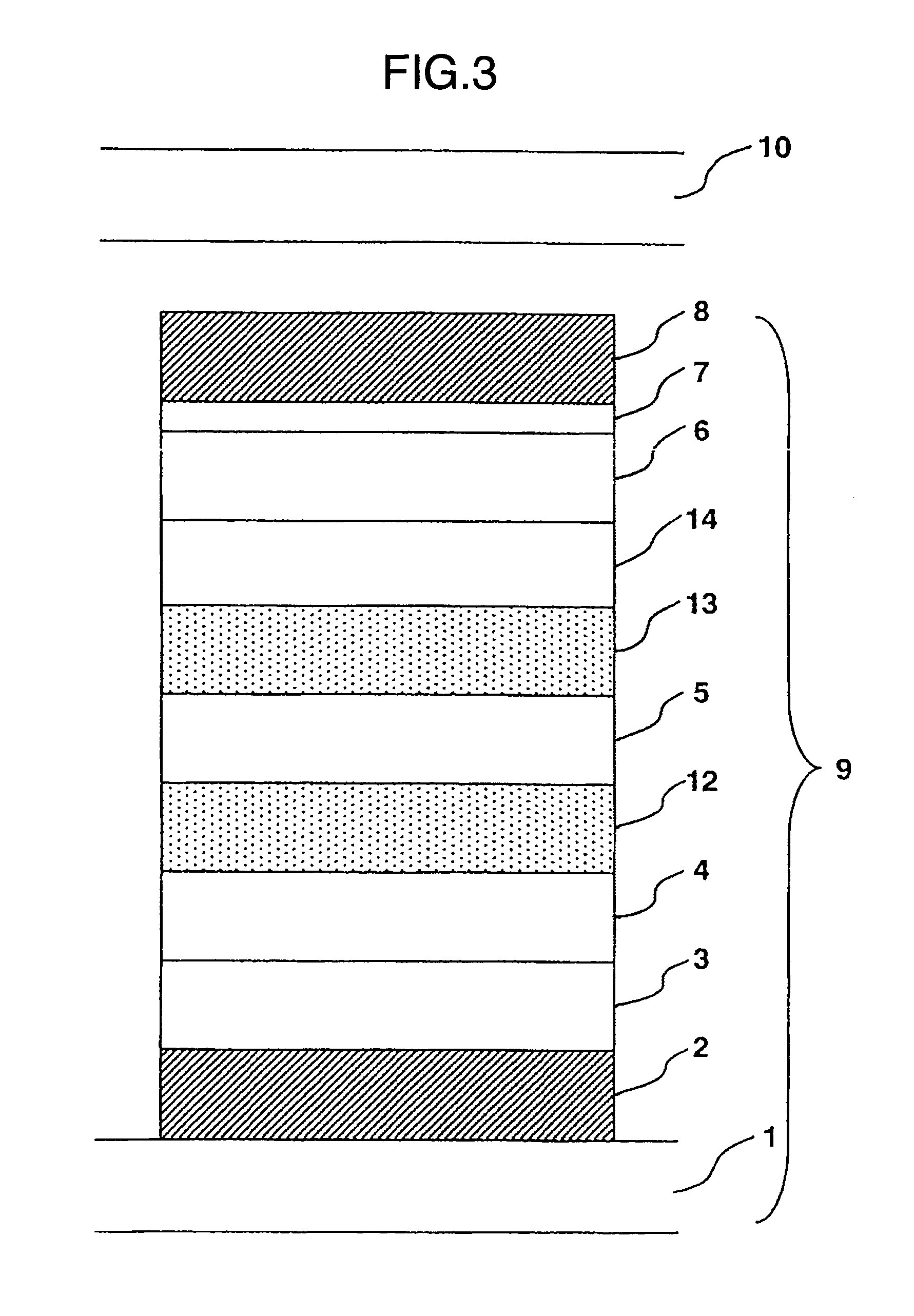

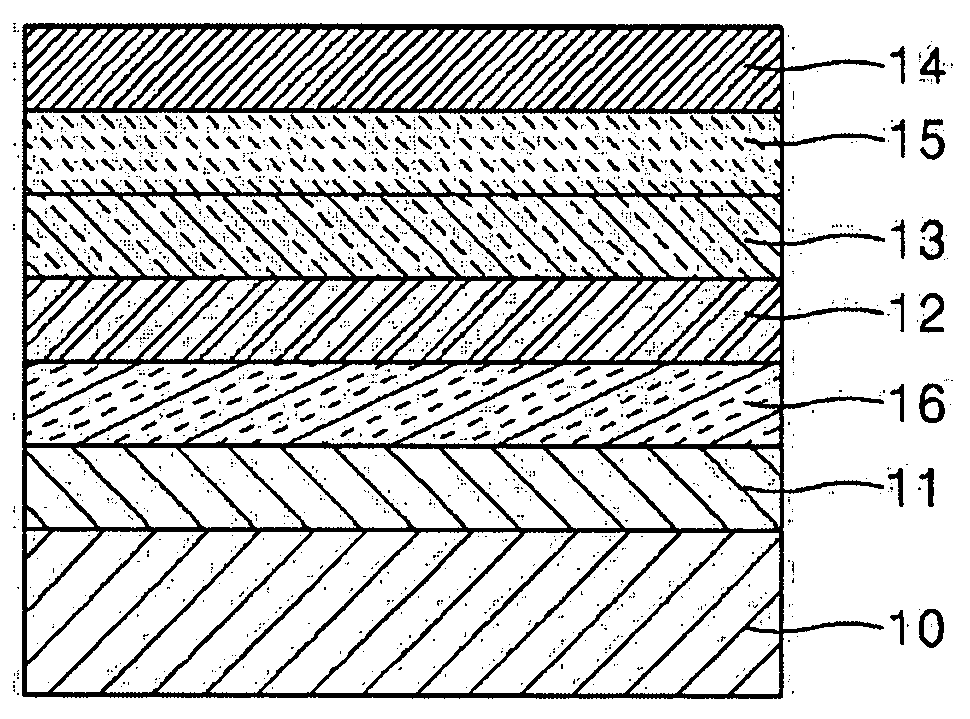

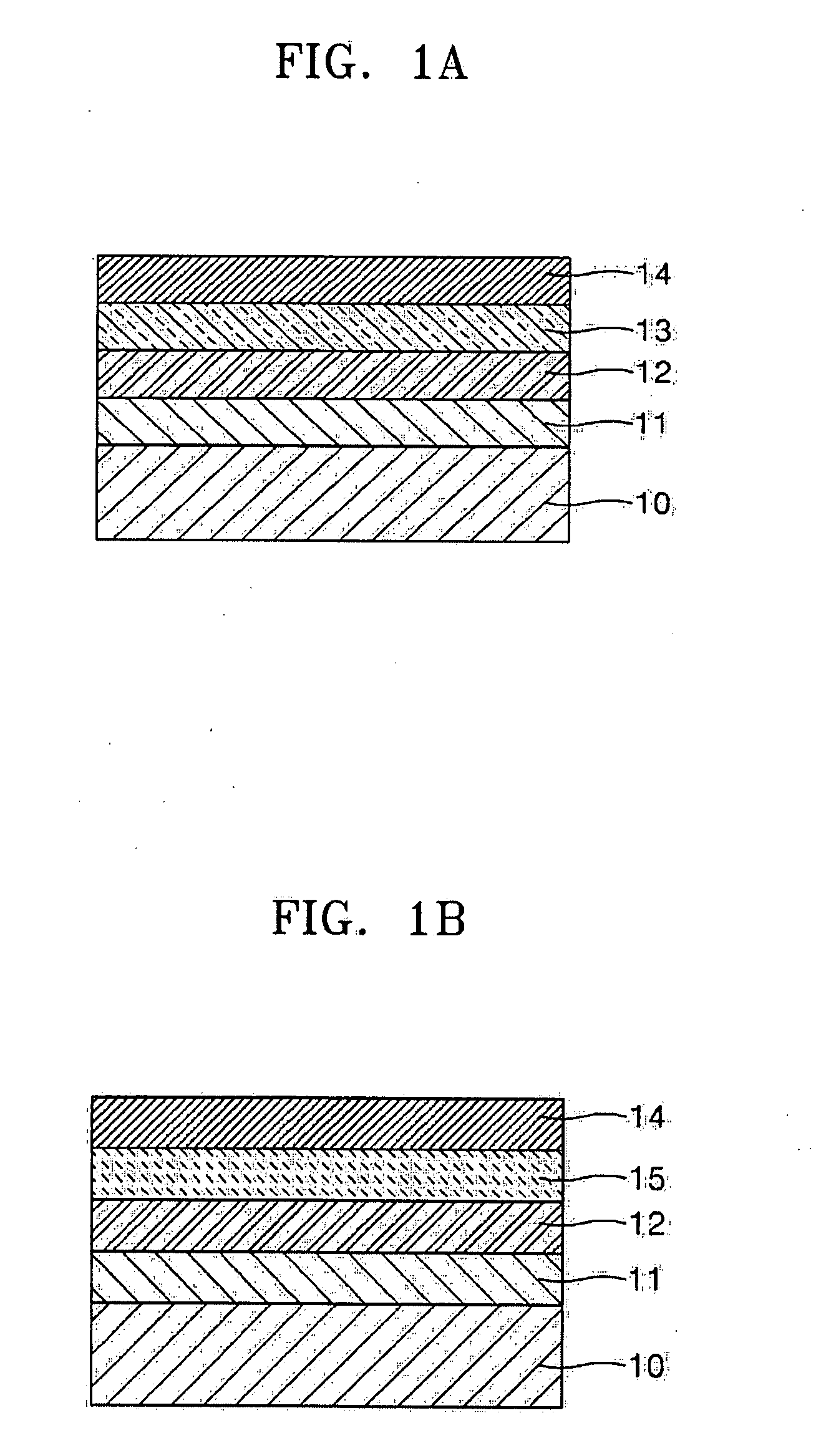

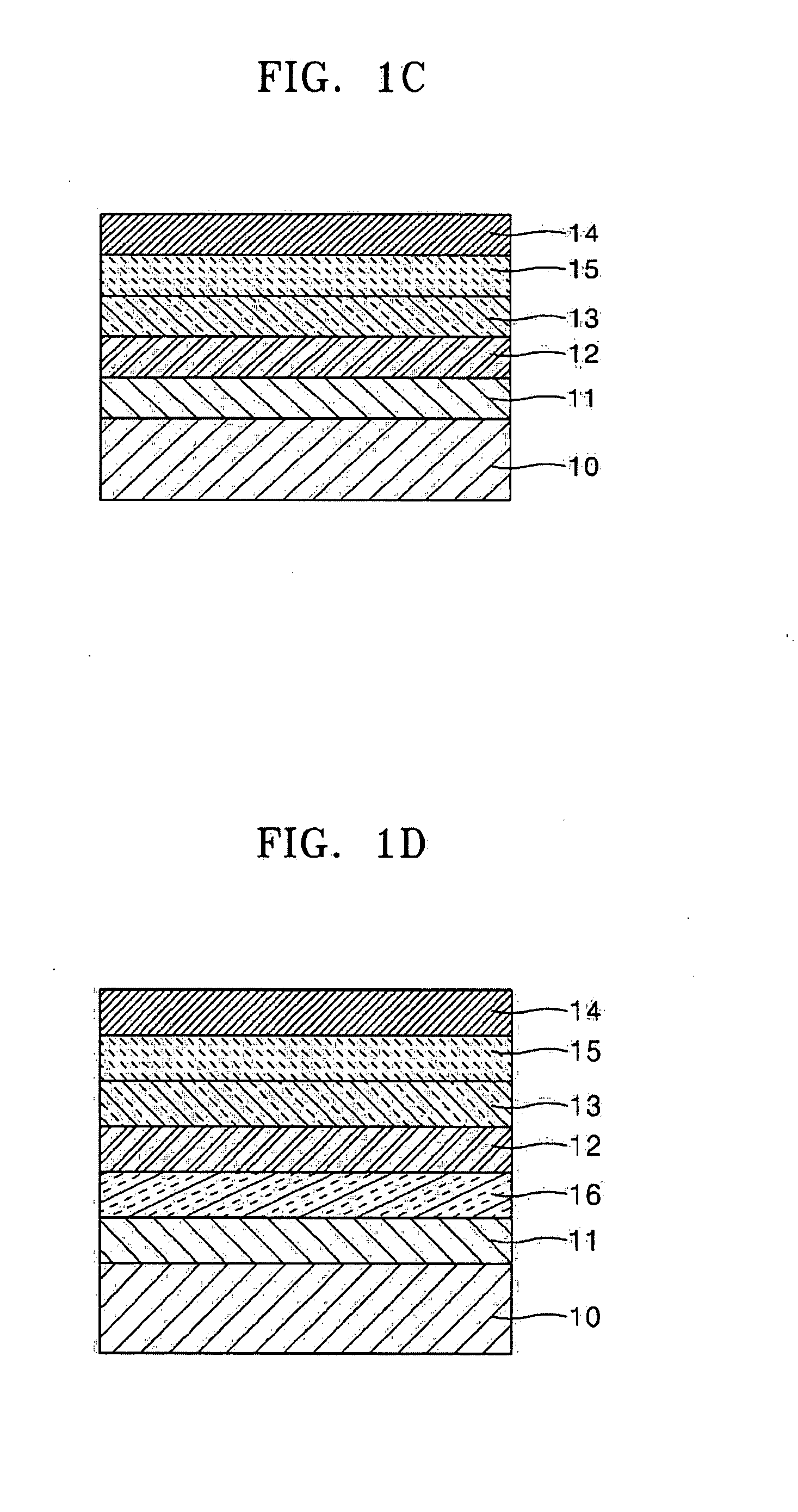

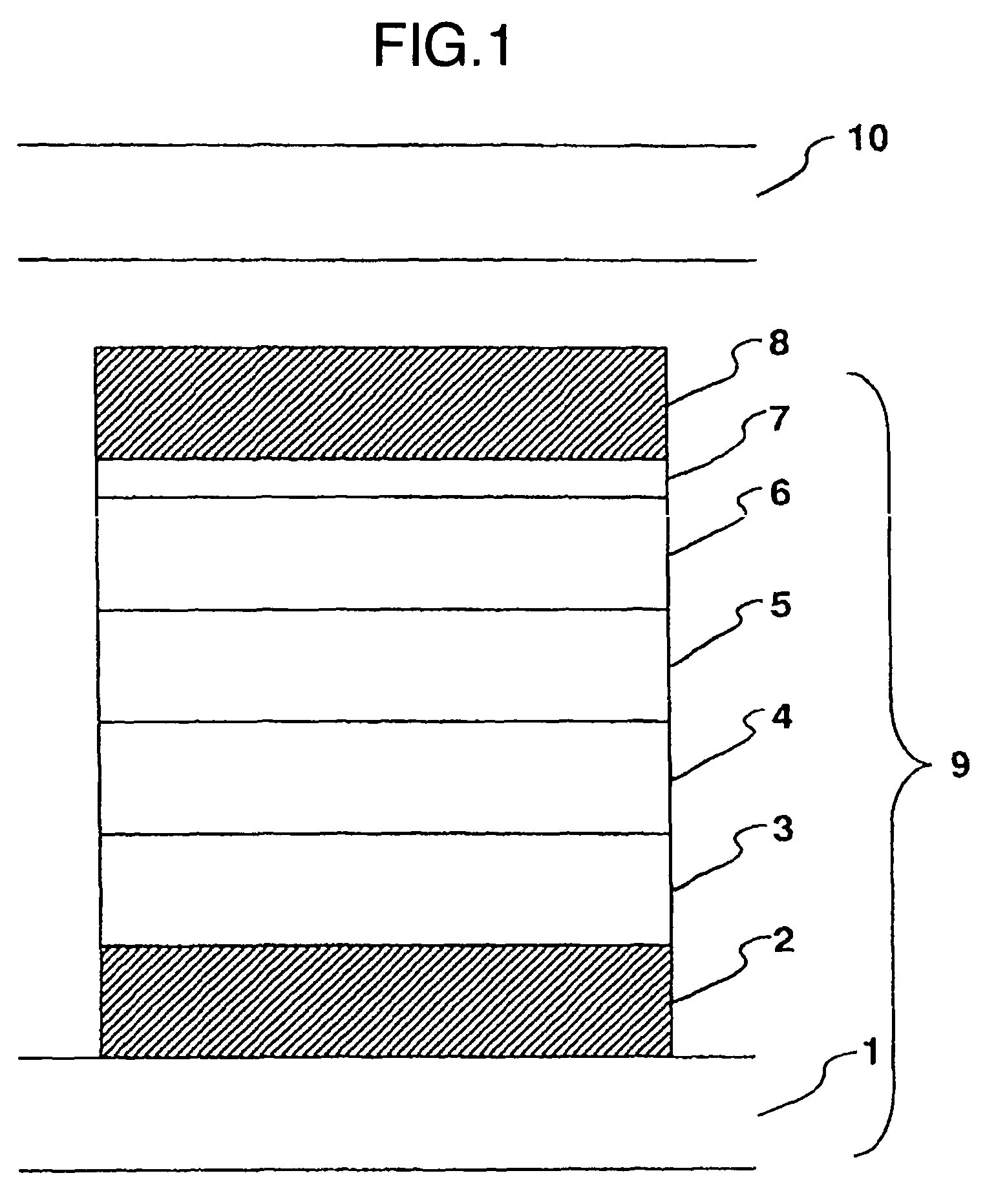

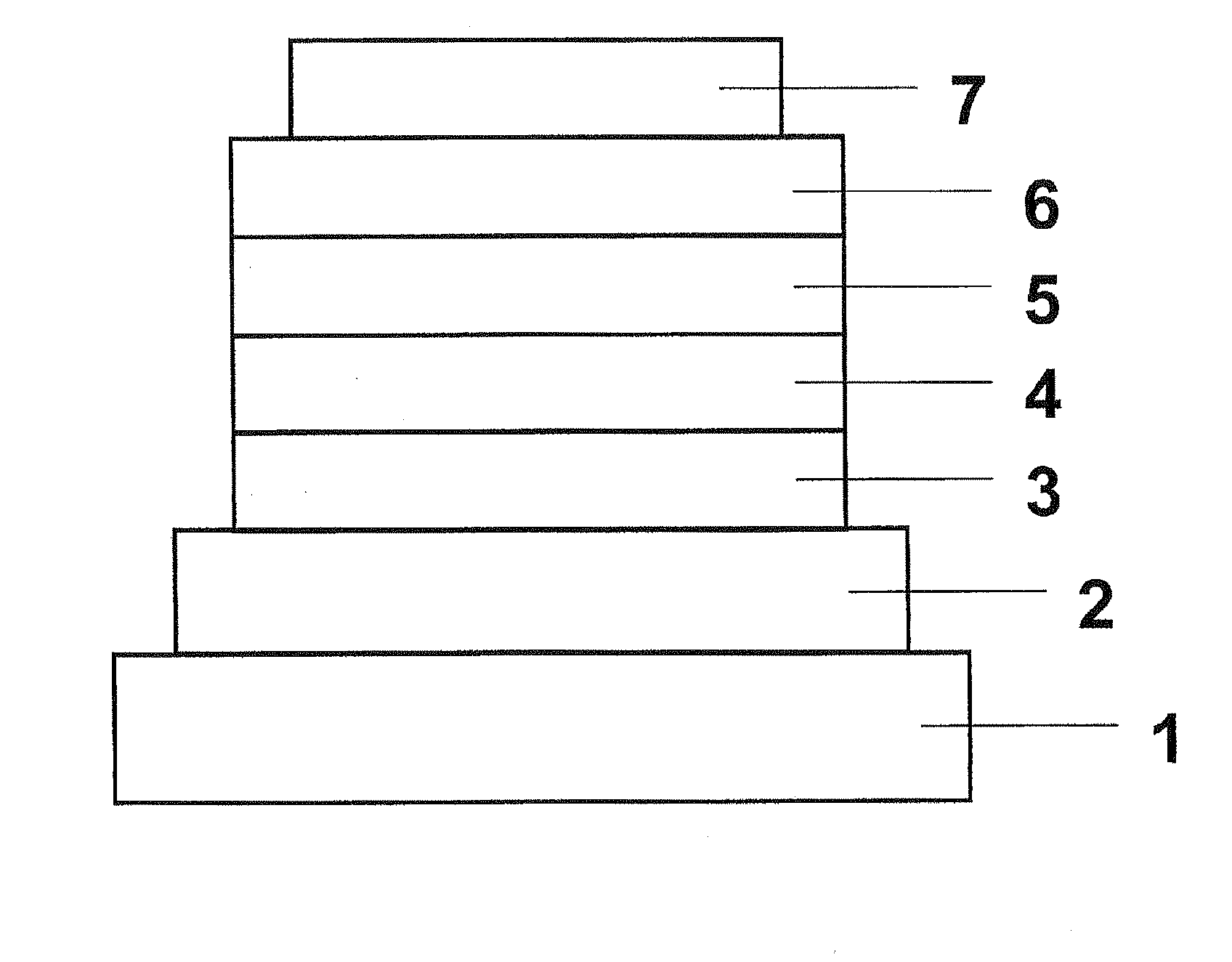

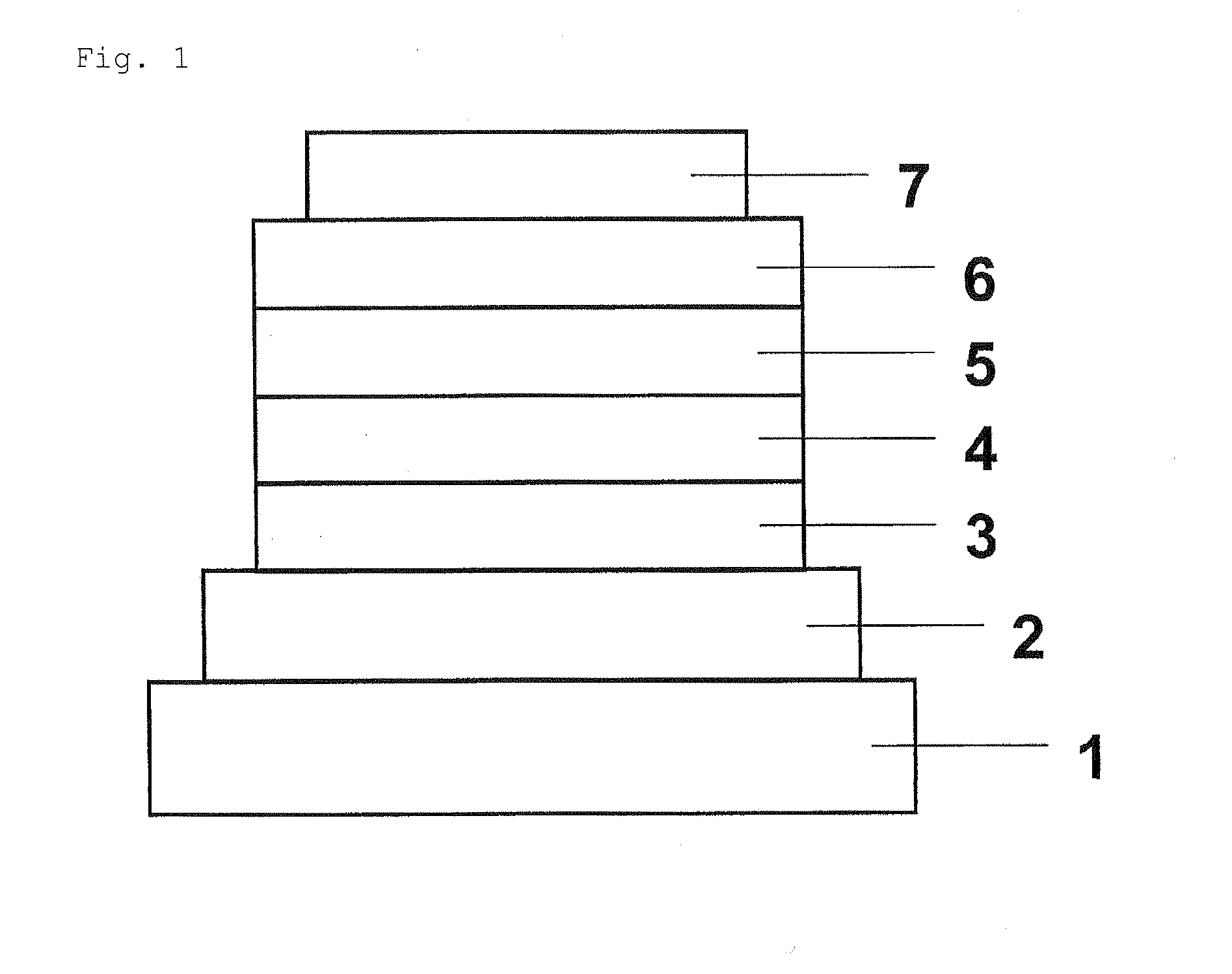

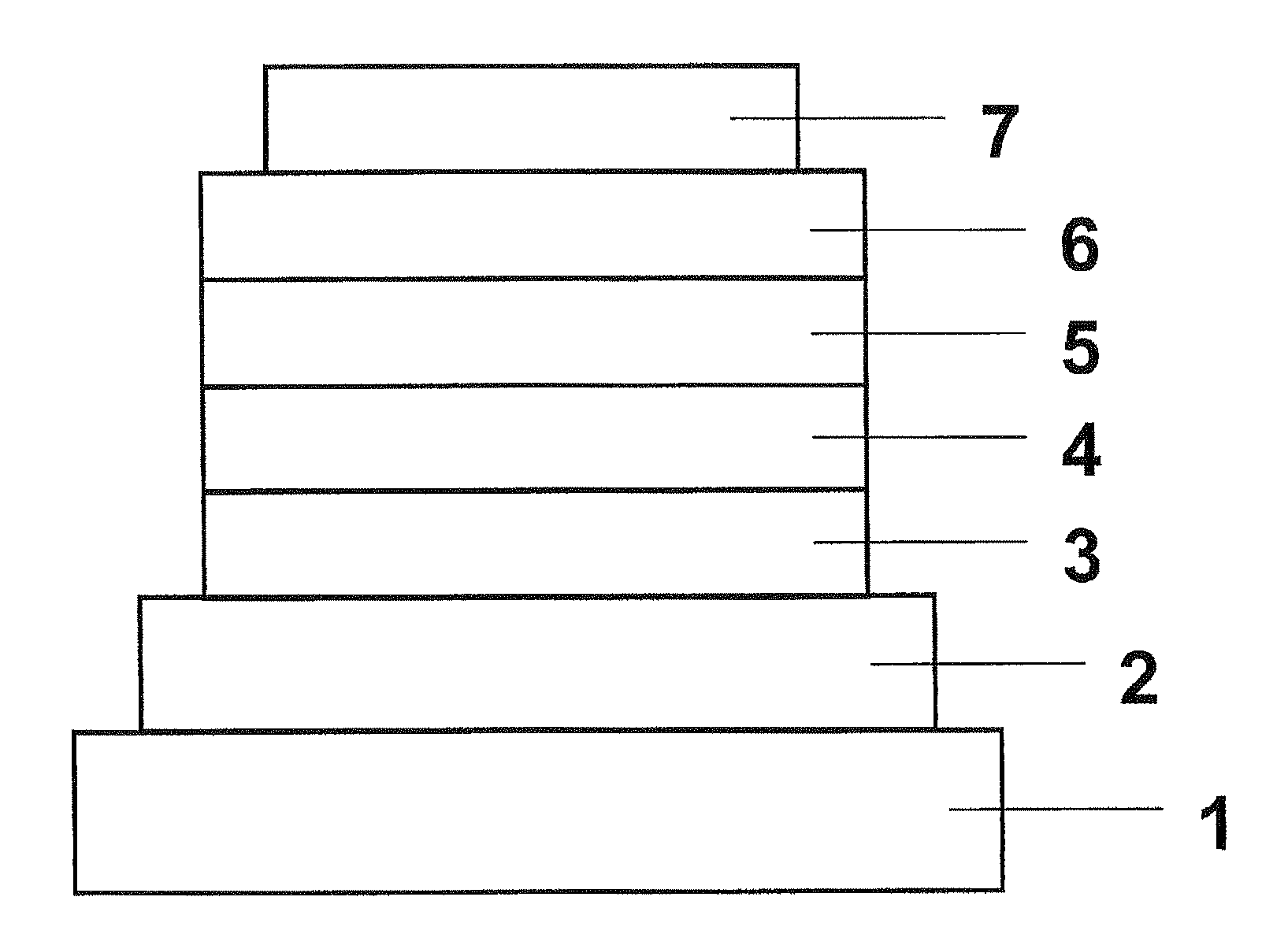

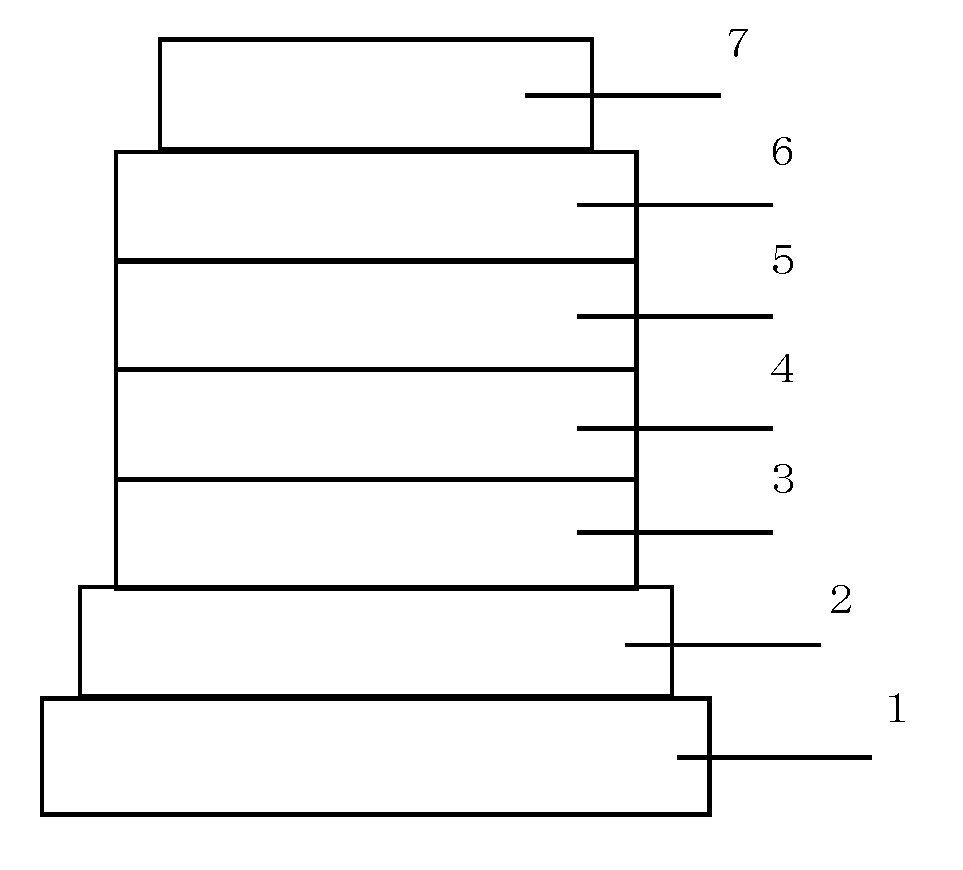

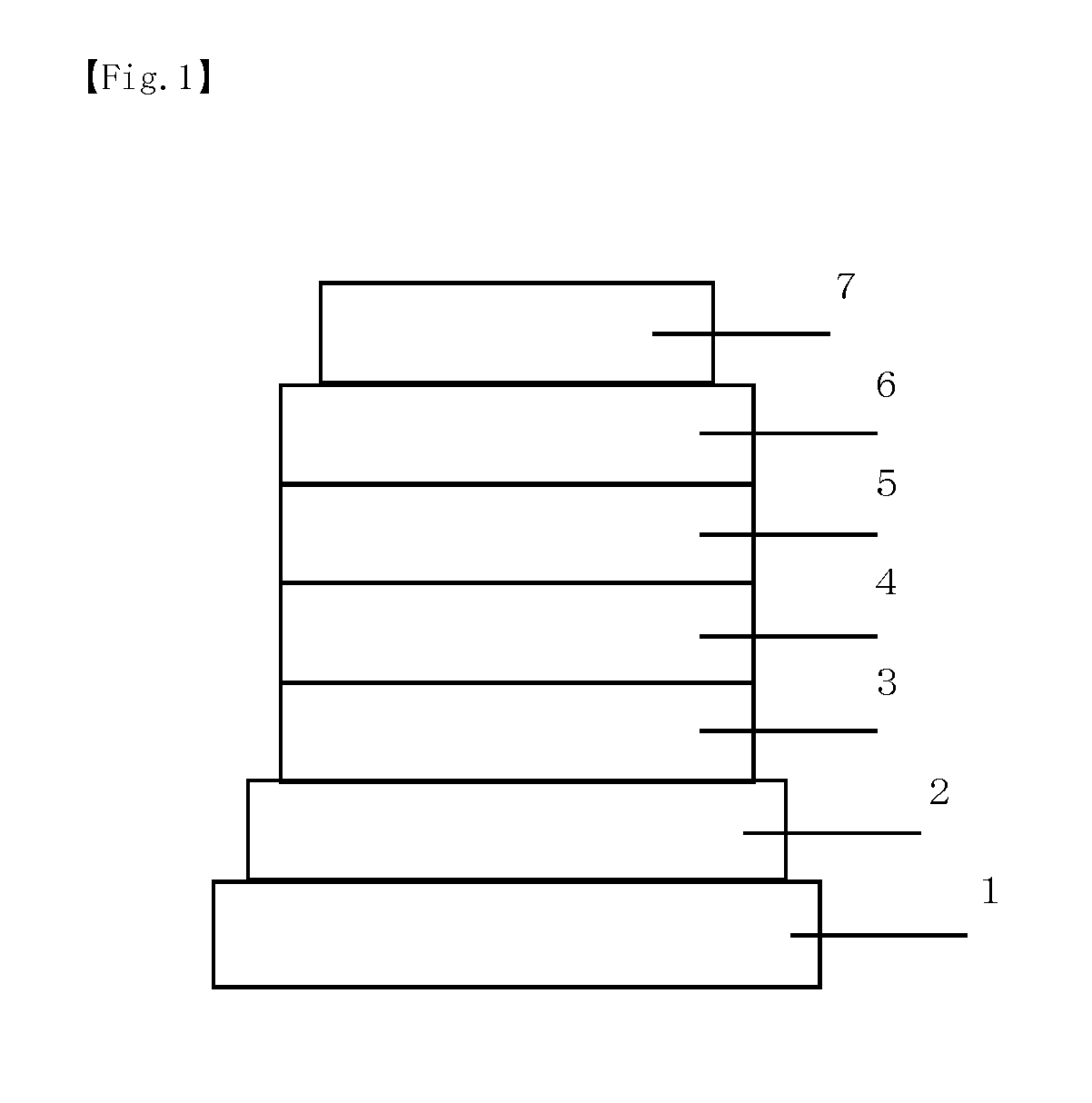

Organic light-emitting element, image display device and production method thereof

ActiveUS20050221121A1High structural reliabilityLight interference effectSolid-state devicesSemiconductor/solid-state device manufacturingDopantElectron

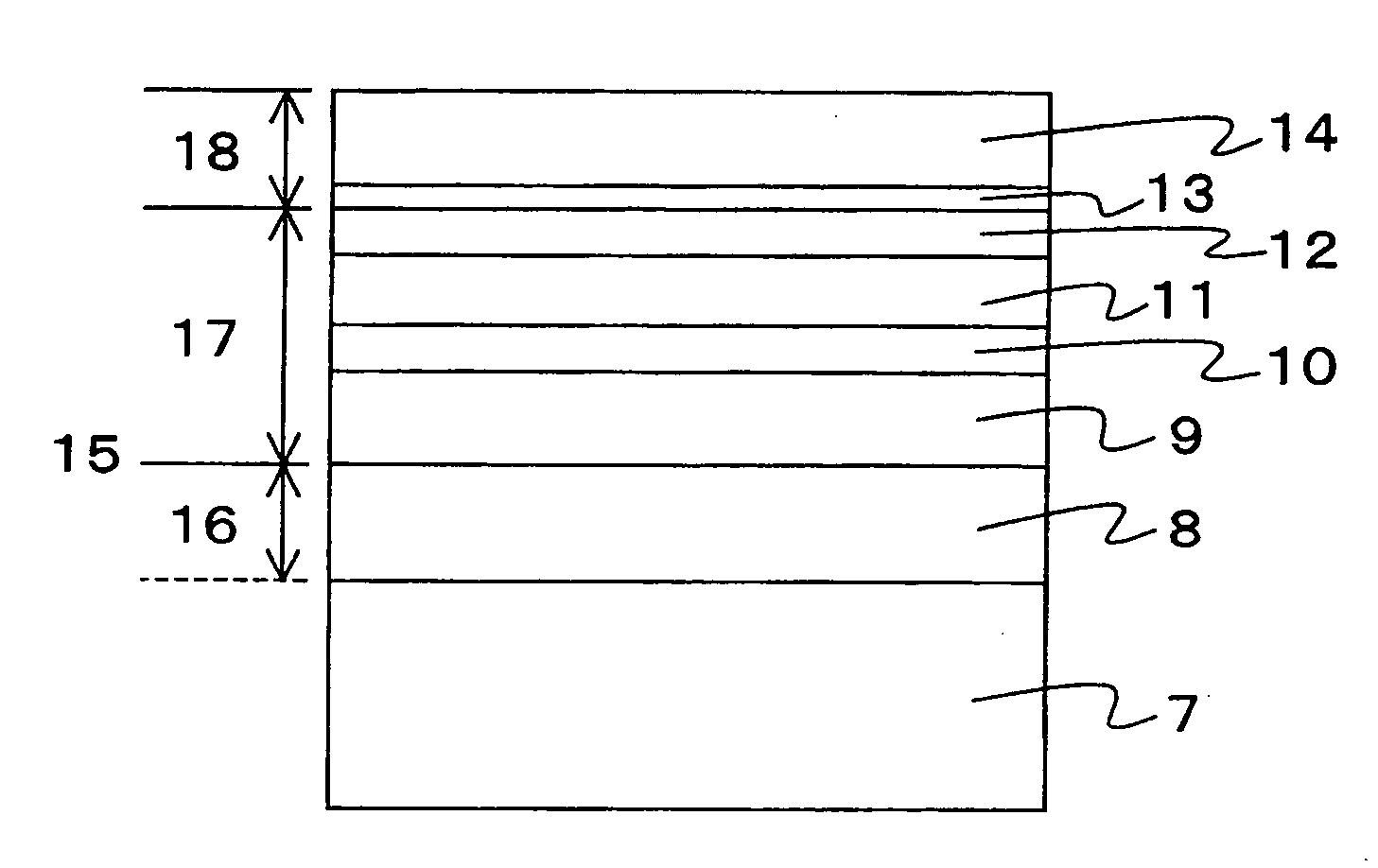

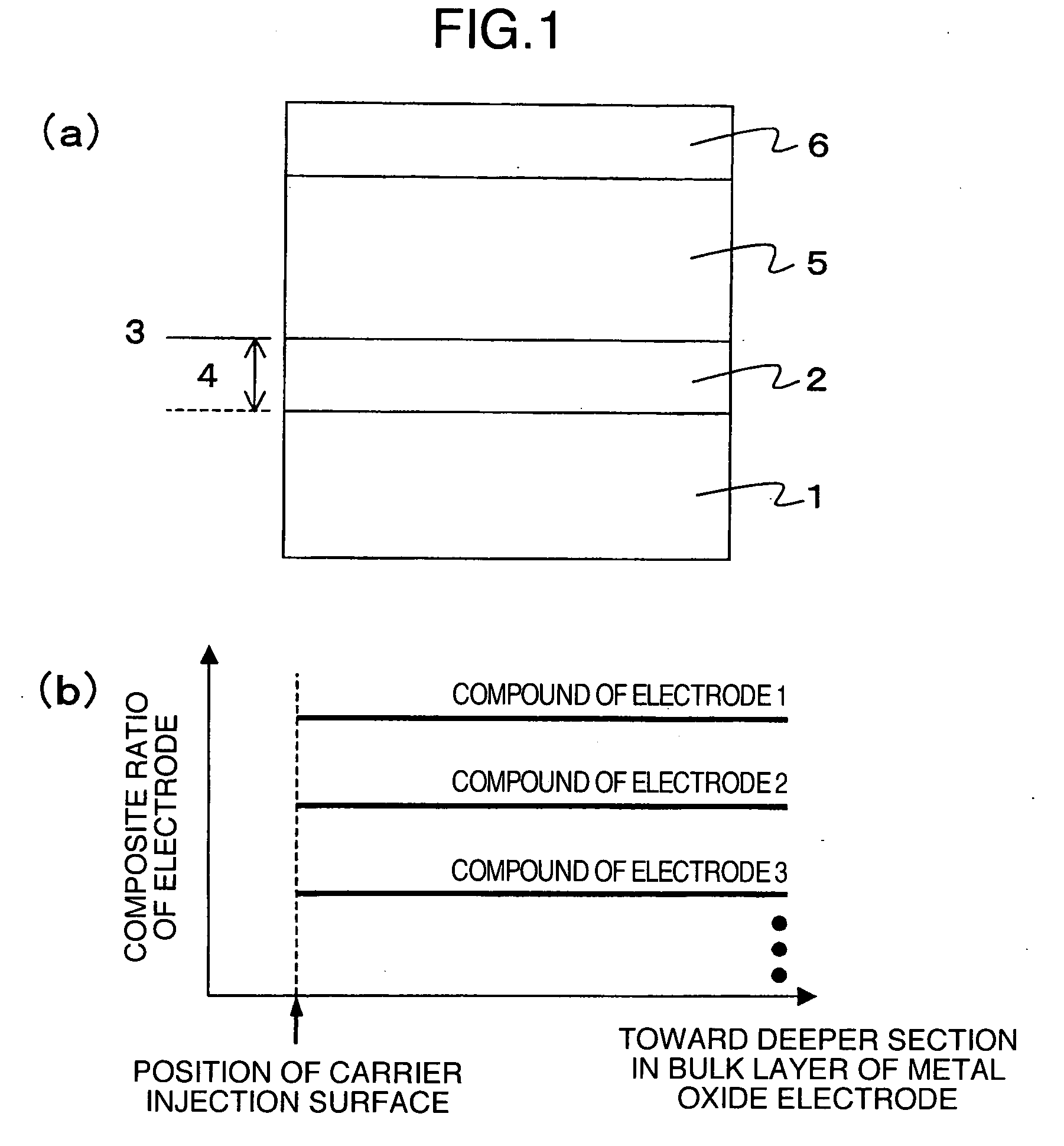

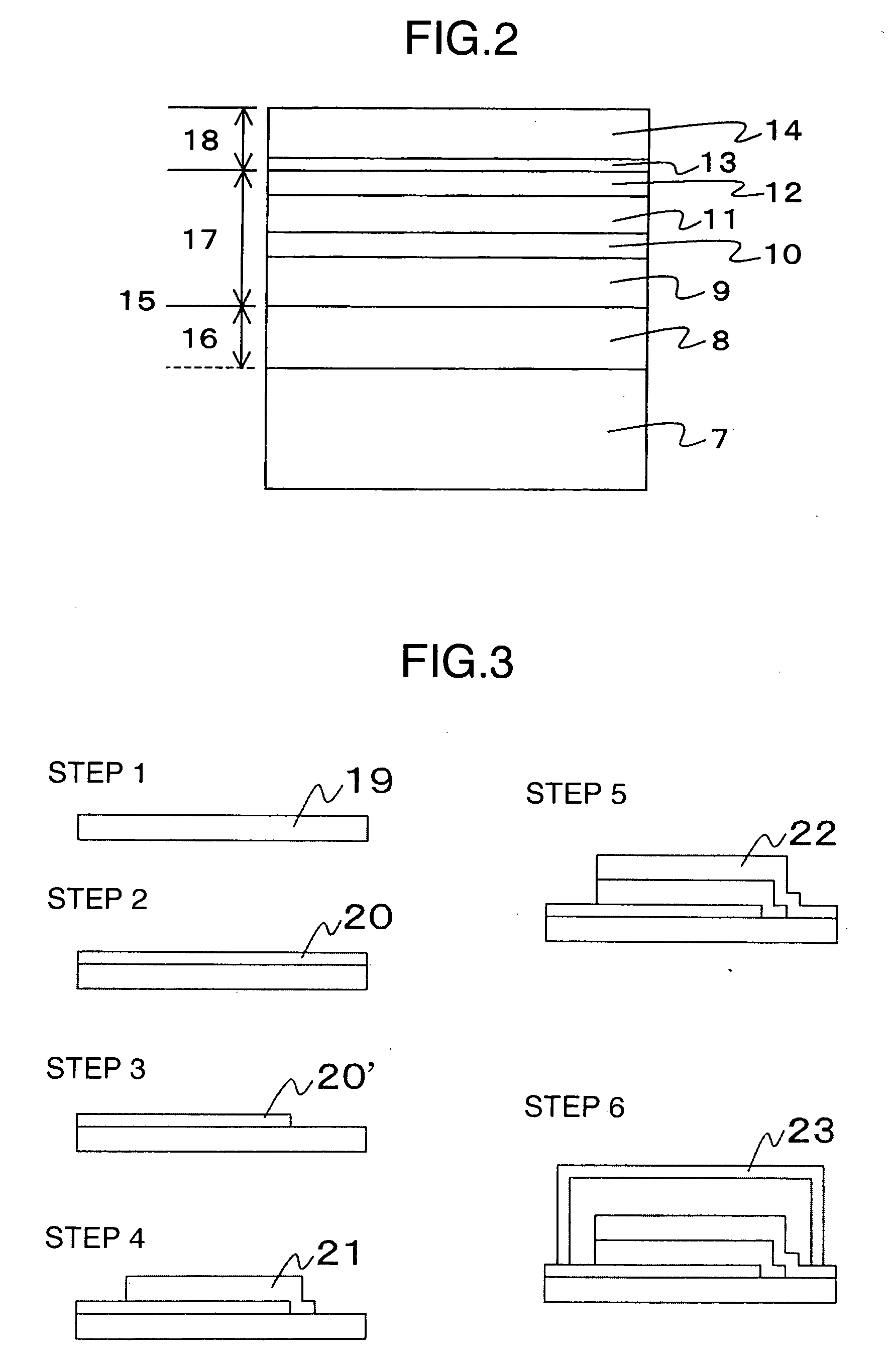

It is an object to provide an organic light-emitting element having two or more light-emitting layers, wherein degradation of each constituent material for the light-emitting layer is reduced to improve reliability of the element. The present invention provides an organic light-emitting element having a laminated structure with a first mixed light-emitting layer 4 composed of a hole transport material, an electron transport material and a dopant which determines a color of an emitted light, and a second mixed light-emitting layer 5 composed of a hole transport material, an electron transport material and a dopant which determines a color of an emitted light, and also provides an image display device which uses the organic light-emitting element.

Owner:SAMSUNG DISPLAY CO LTD +1

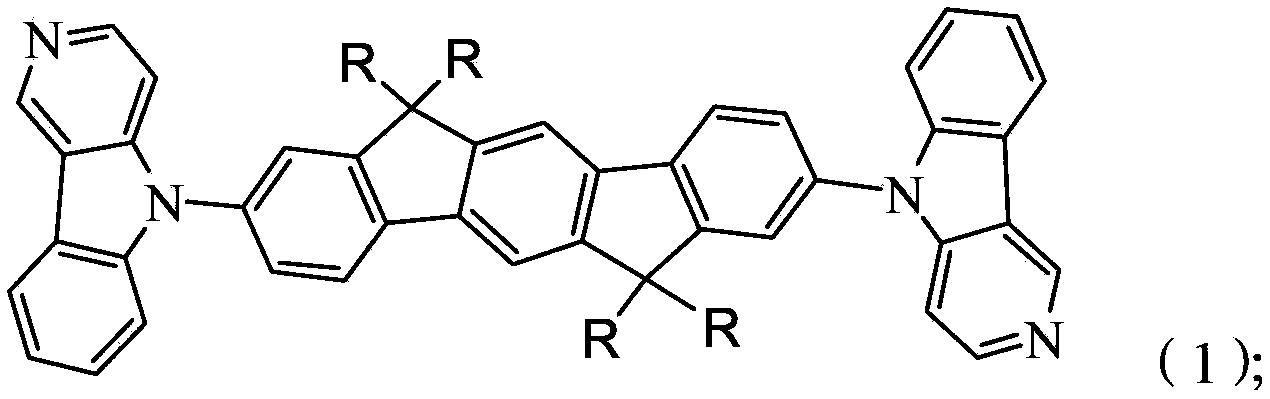

Novel materials for organic electroluminescent devices

ActiveCN101490207ALow LUMOFacilitates electron injectionStyryl dyesGroup 4/14 element organic compoundsHost materialOrganic electroluminescence

The invention relates to the compounds of formulae (1) to (6) and to organic electroluminescent devices, especially blue-emitting devices, in which these compounds are used as the host material or doping agent in the emitting layer and / or as the hole transport material and / or as the electron transport material.

Owner:MERCK PATENT GMBH

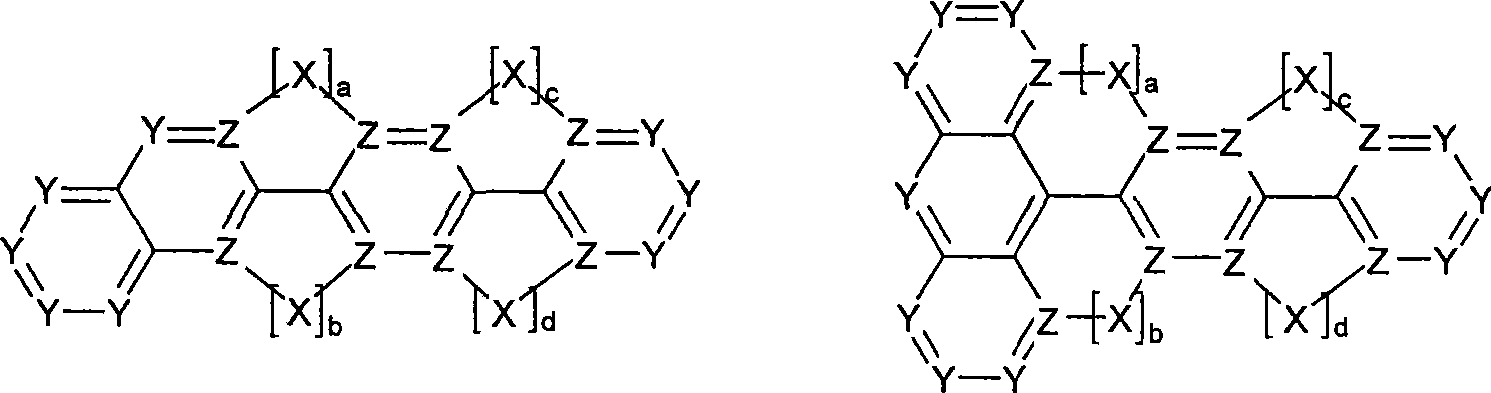

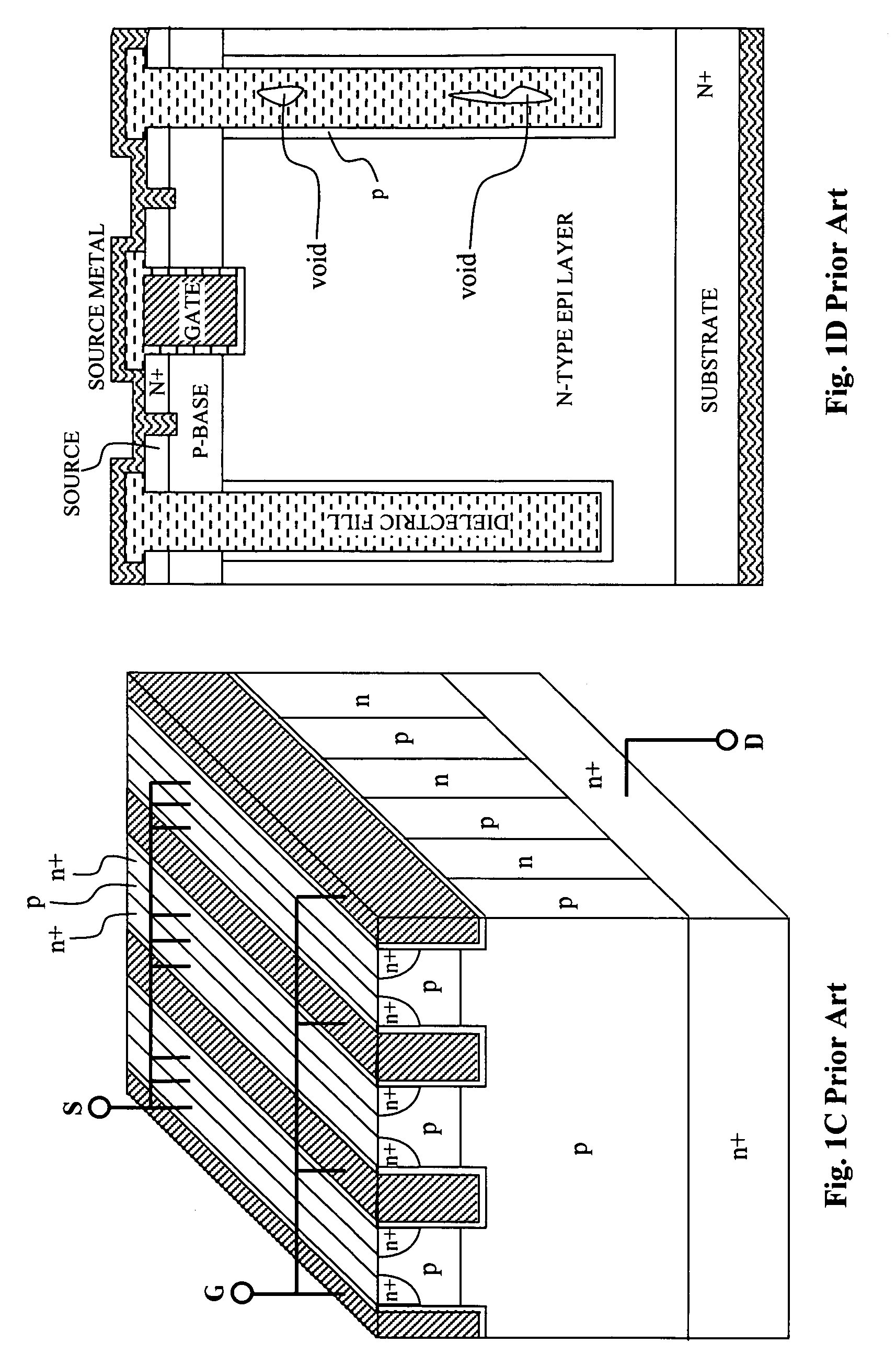

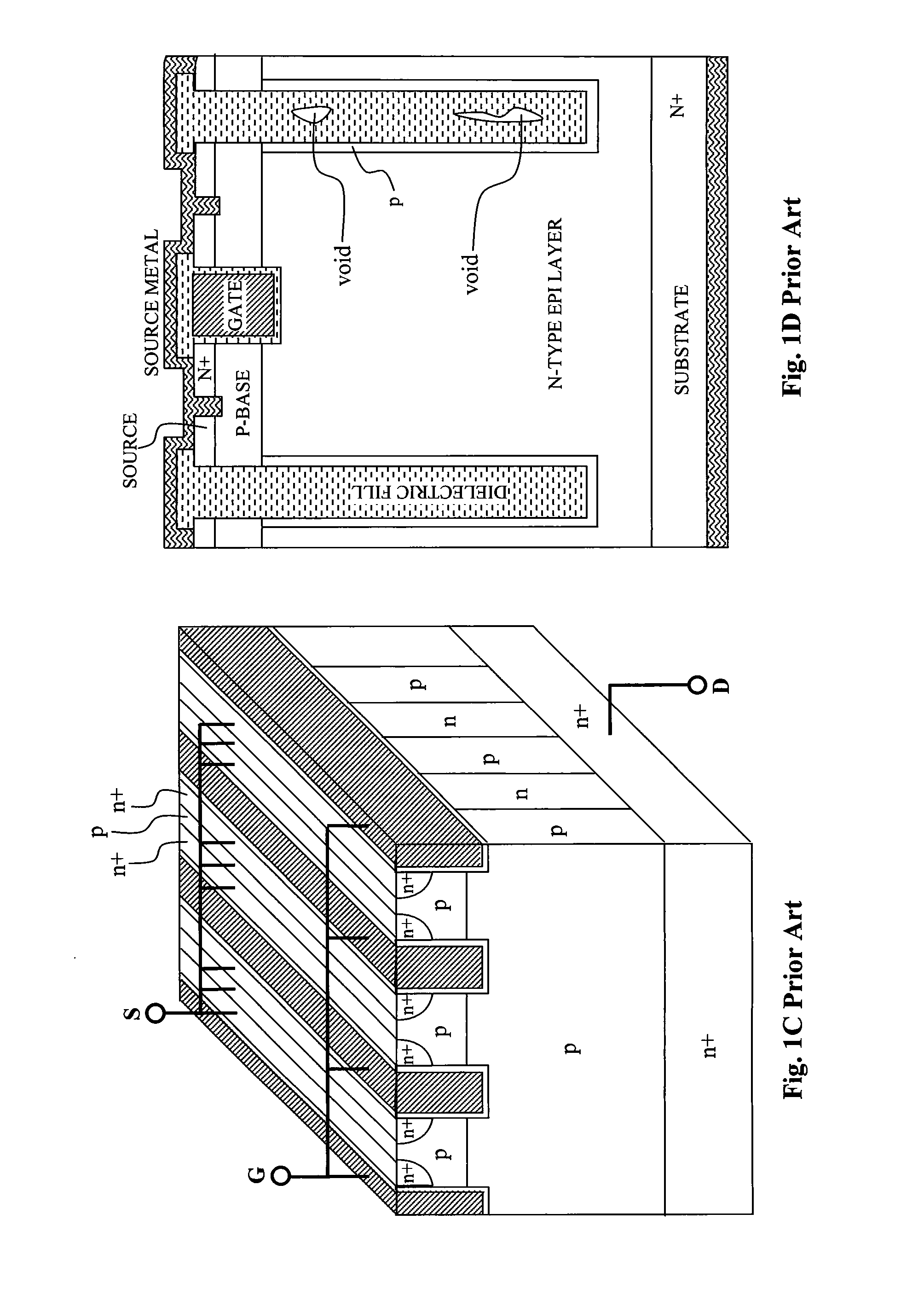

Nano-tube mosfet technology and devices

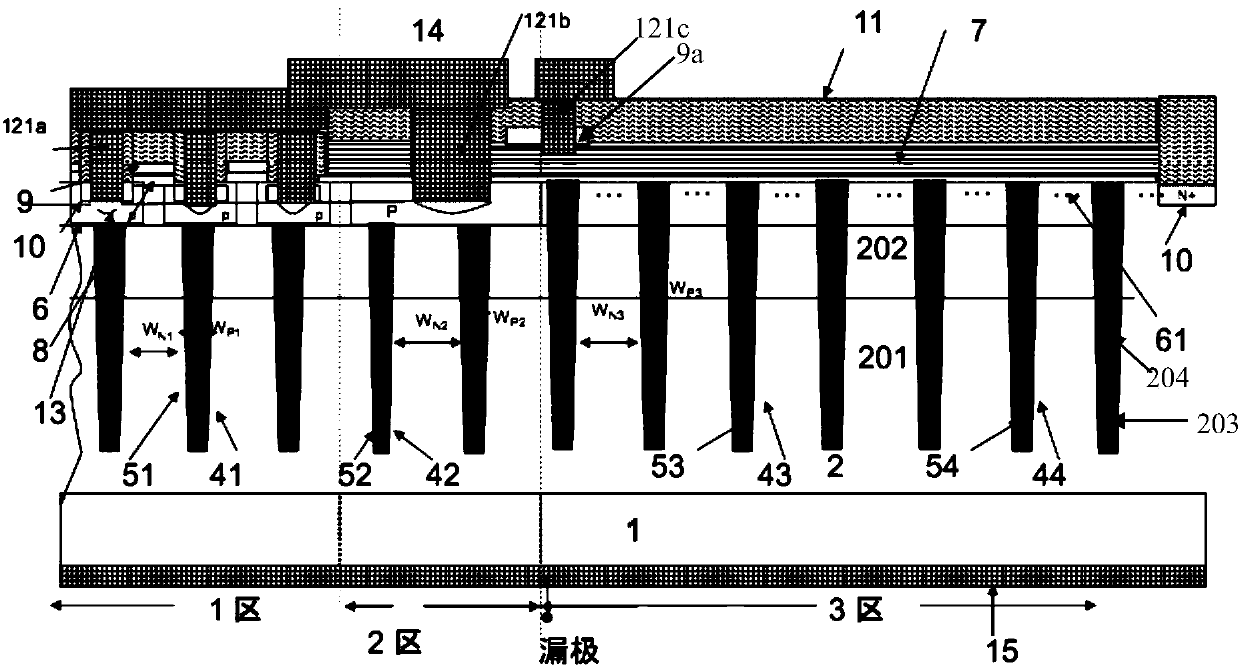

ActiveUS20100163846A1Simple and convenient processing stepEasy to carrySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDielectric layer

This invention discloses a semiconductor power device disposed in a semiconductor substrate and the semiconductor substrate has a plurality of trenches. Each of the trenches is filled with a plurality of epitaxial layers of alternating conductivity types constituting nano tubes functioning as conducting channels stacked as layers extending along a sidewall direction with a “Gap Filler” layer filling a merging-gap between the nano tubes disposed substantially at a center of each of the trenches. The “Gap Filler” layer can be very lightly doped Silicon or grown and deposited dielectric layer. In an exemplary embodiment, the plurality of trenches are separated by pillar columns each having a width approximately half to one-third of a width of the trenches.

Owner:ALPHA & OMEGA SEMICON INC

Organic electroluminescence device and organic electroluminescence system

ActiveUS20060255722A1Solution to short lifeReduce total powerDischarge tube luminescnet screensElectroluminescent light sourcesPhysicsOrganic electroluminescence

An organic electroluminescence device is provided which employs a metal oxide electrode having particular composition distribution of elements to extend the life. A conventional approach for extending the life of an electroluminescence device is not provided by considering the degradation mechanism of how the organic electroluminescence device is degraded by the driving with electric current. The composite ratio of compounds of an electrode made of metal oxide forming part of the organic electroluminescence device is substantially uniform from a surface through which the carriers are injected from the electrode toward a deeper section in a bulk layer of the electrode. Thus, the electrode has stoichiometrically stable composition to prevent the degradation of electrode materials and diffusion into the organic layer, thereby providing a longer life.

Owner:SAMSUNG DISPLAY CO LTD +1

Organic light emitting device

InactiveUS20070285010A1Improve charge balanceImprove efficiencyDischarge tube luminescnet screensElectroluminescent light sourcesHole injection layerOrganic light emitting device

Provided are an organic light emitting device (OLED) comprising: a first electrode; a second electrode; a hole injection layer (HIL), a hole transporting layer (HTL), and an emitting layer sequentially formed between the first electrode and the second electrode, wherein the work function, the IP or the absolute value of the highest occupied molecular orbital (HOMO) level of the HIL is greater than or equal to the absolute value of HOMO level of the HTL. In the OLED, the energy relationships between organic layers are controlled to facilitate hole injection and optimize the charge balance. Thus the efficiency of the OLED improves and the lifetime of the OLED increases.

Owner:SAMSUNG MOBILE DISPLAY CO LTD

Organic light-emitting element, image display device and production method thereof

ActiveUS8026662B2High structural reliabilityLight interference effectDischarge tube luminescnet screensElectroluminescent light sourcesDopantElectron

It is an object to provide an organic light-emitting element having two or more light-emitting layers, wherein degradation of each constituent material for the light-emitting layer is reduced to improve reliability of the element. The present invention provides an organic light-emitting element having a laminated structure with a first mixed light-emitting layer 4 composed of a hole transport material, an electron transport material and a dopant which determines a color of an emitted light, and a second mixed light-emitting layer 5 composed of a hole transport material, an electron transport material and a dopant which determines a color of an emitted light, and also provides an image display device which uses the organic light-emitting element.

Owner:SAMSUNG DISPLAY CO LTD +1

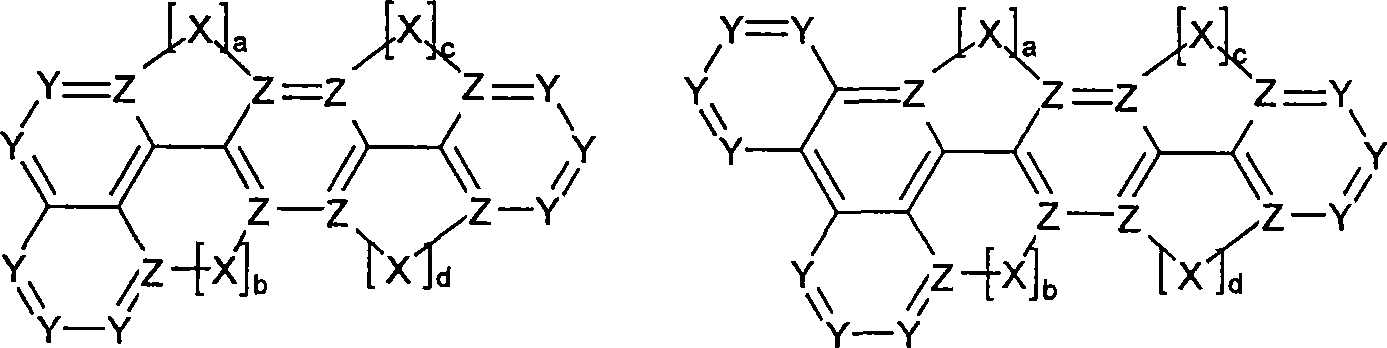

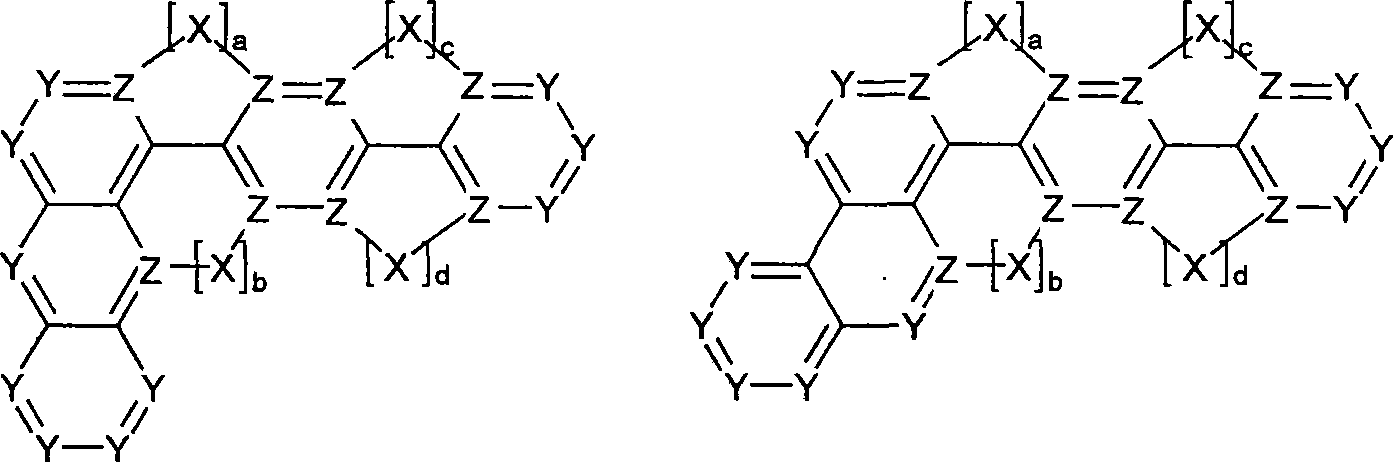

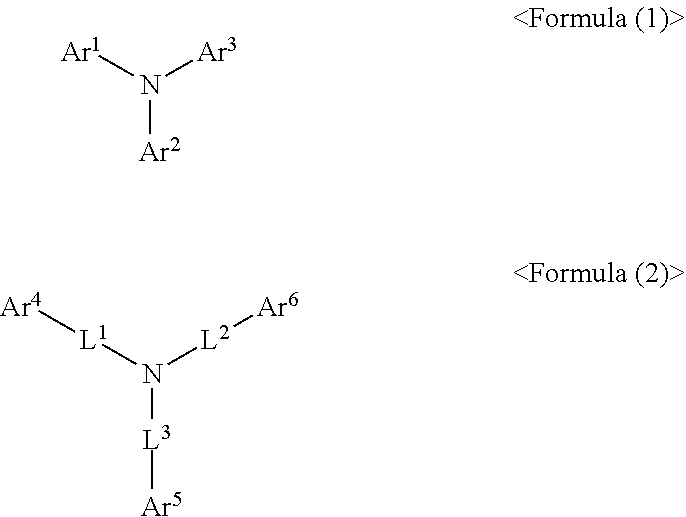

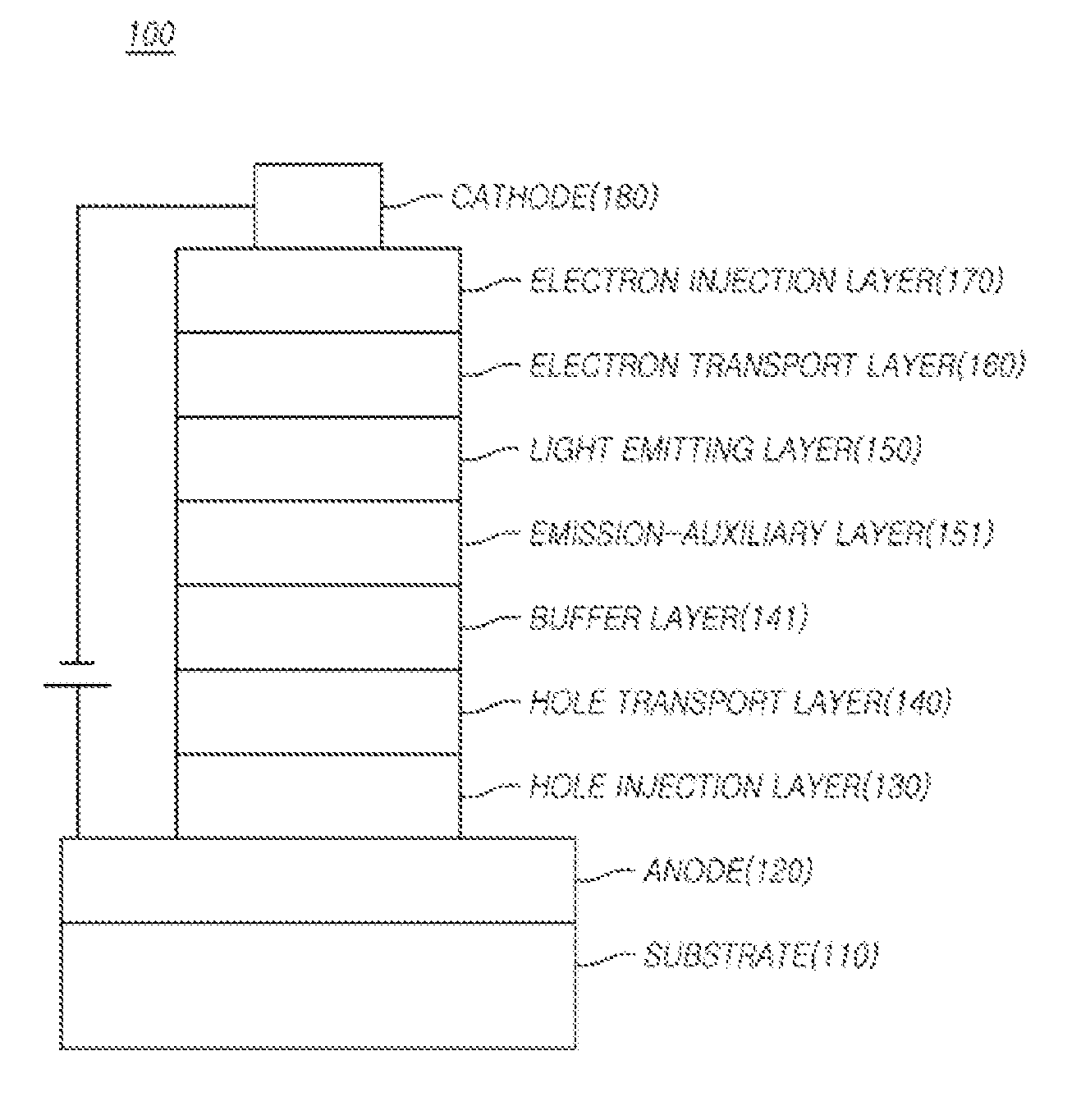

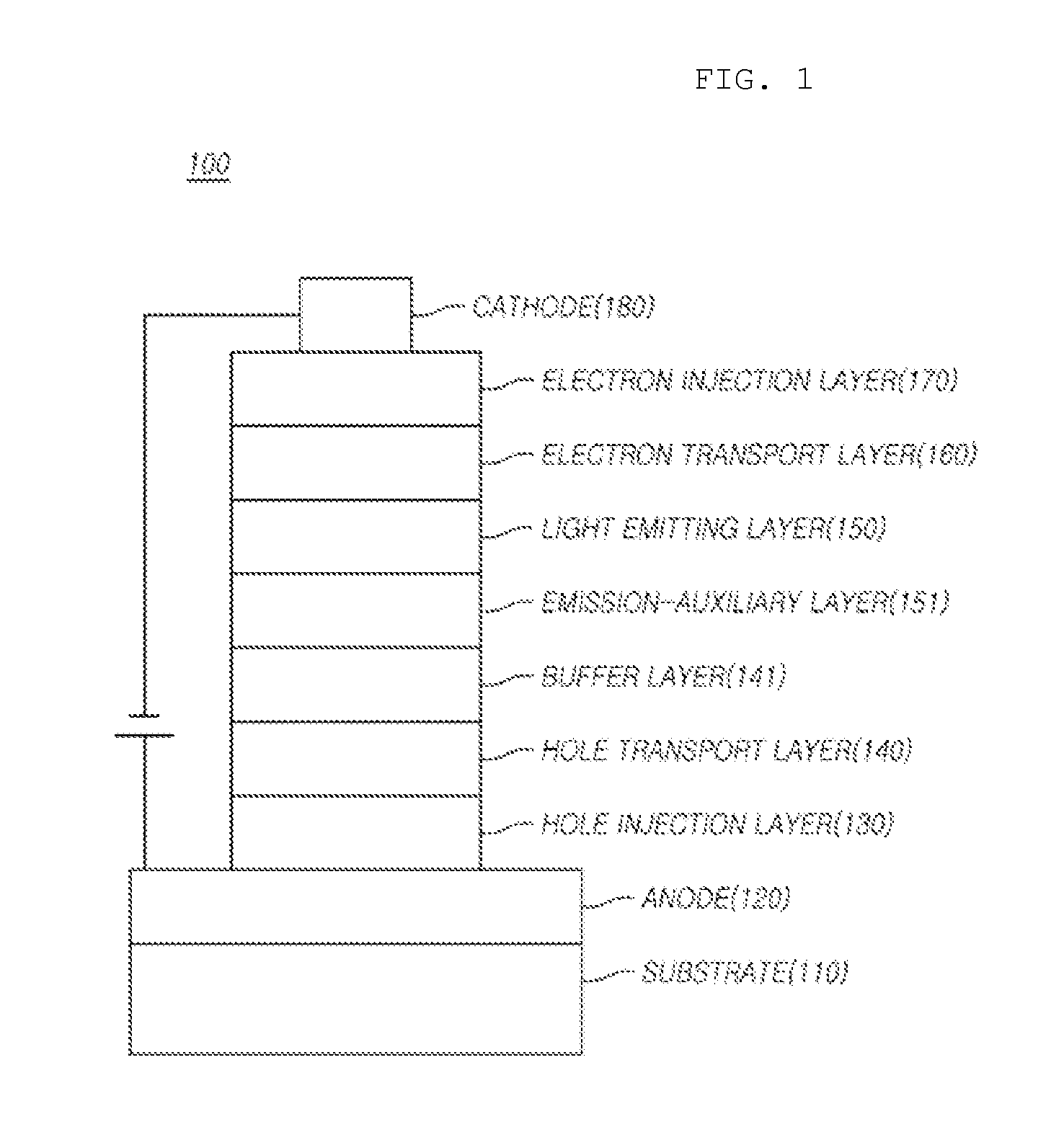

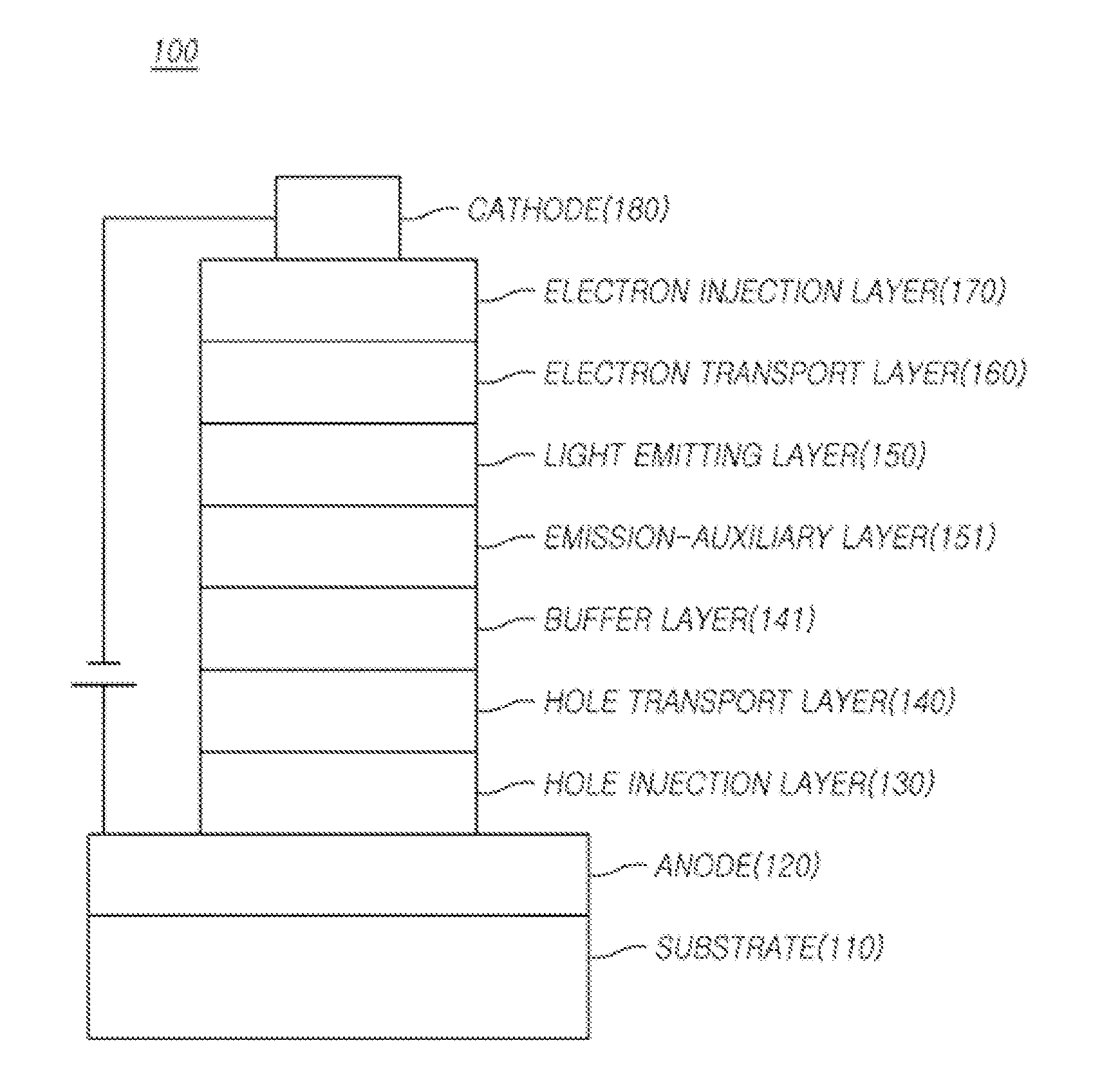

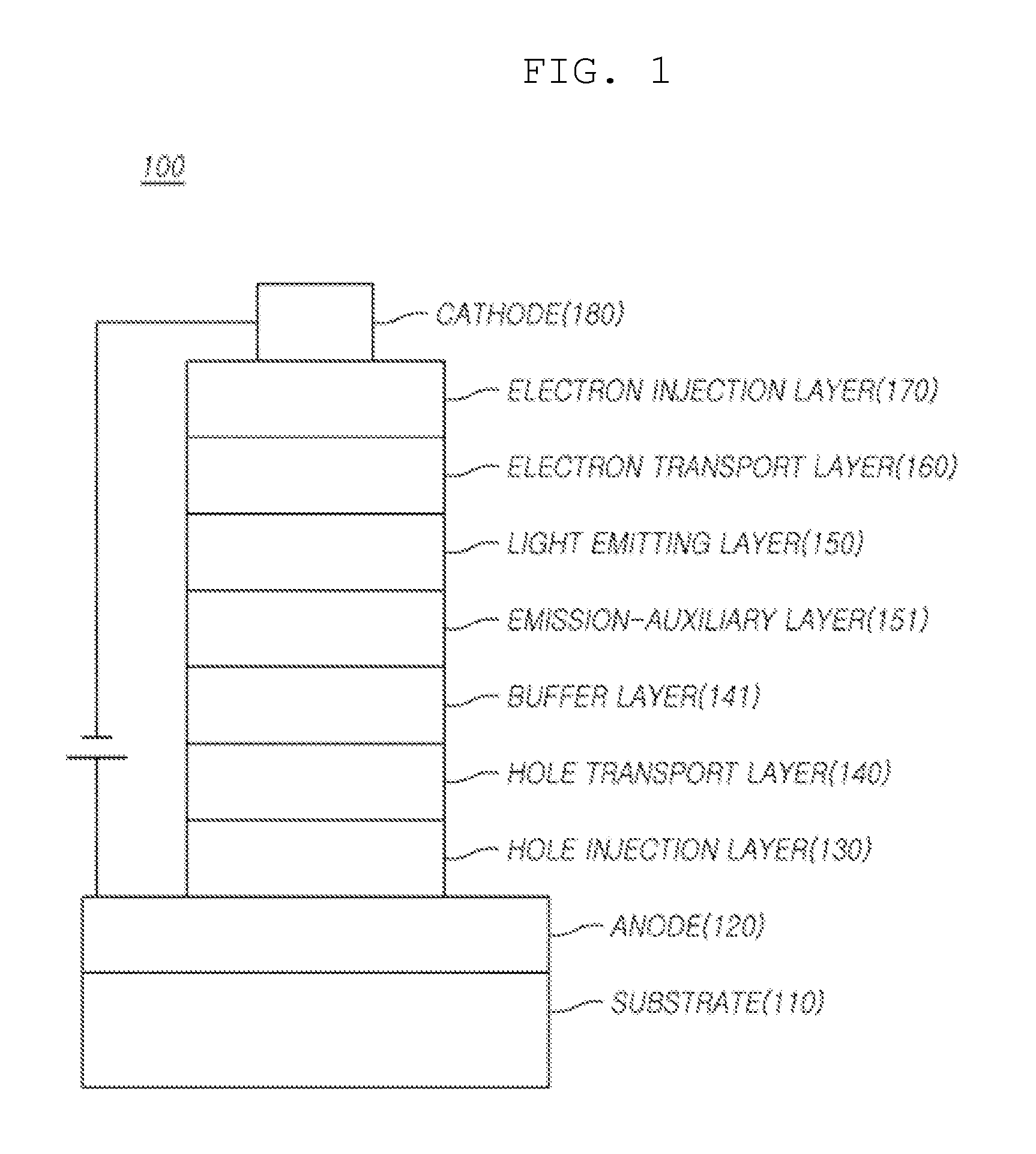

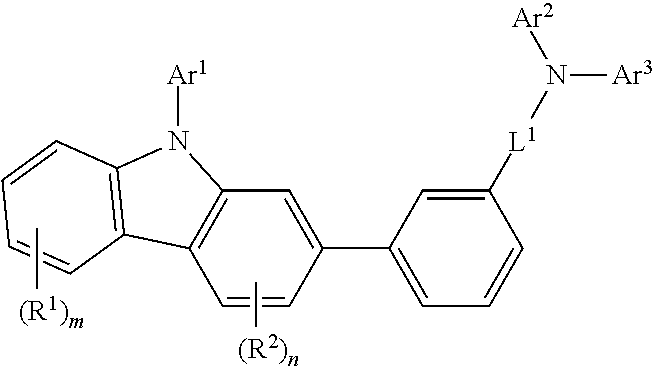

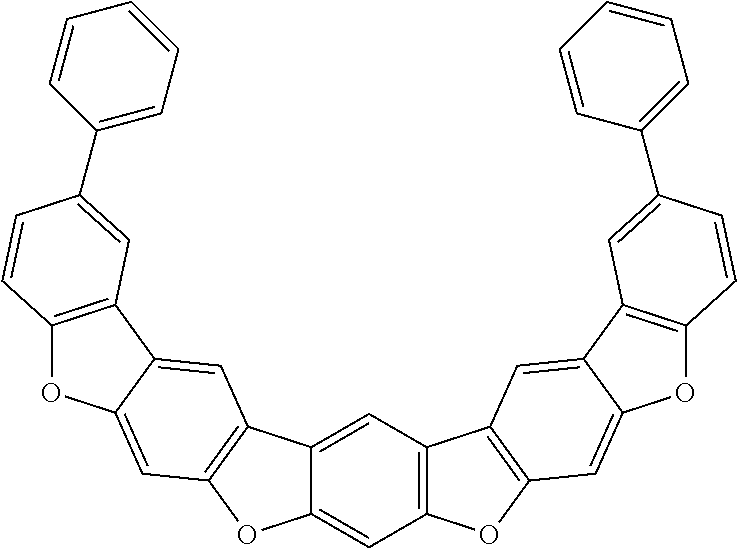

Compound for organic electronic element, organic electronic element using the same, and an electronic device

ActiveUS20170244047A1Improve charge balanceDeterioration of interface is preventedOrganic chemistryElectroluminescent light sourcesHigh electronHole transport layer

Provided is an organic electronic element comprising a hole transport layer containing a compound of Formula (1) and an emitting auxiliary layer containing a compound of Formula (2), capable of improving the light emitting efficiency, stability, and life span of an electronic device using the same.

Owner:DUK SAN NEOLUX

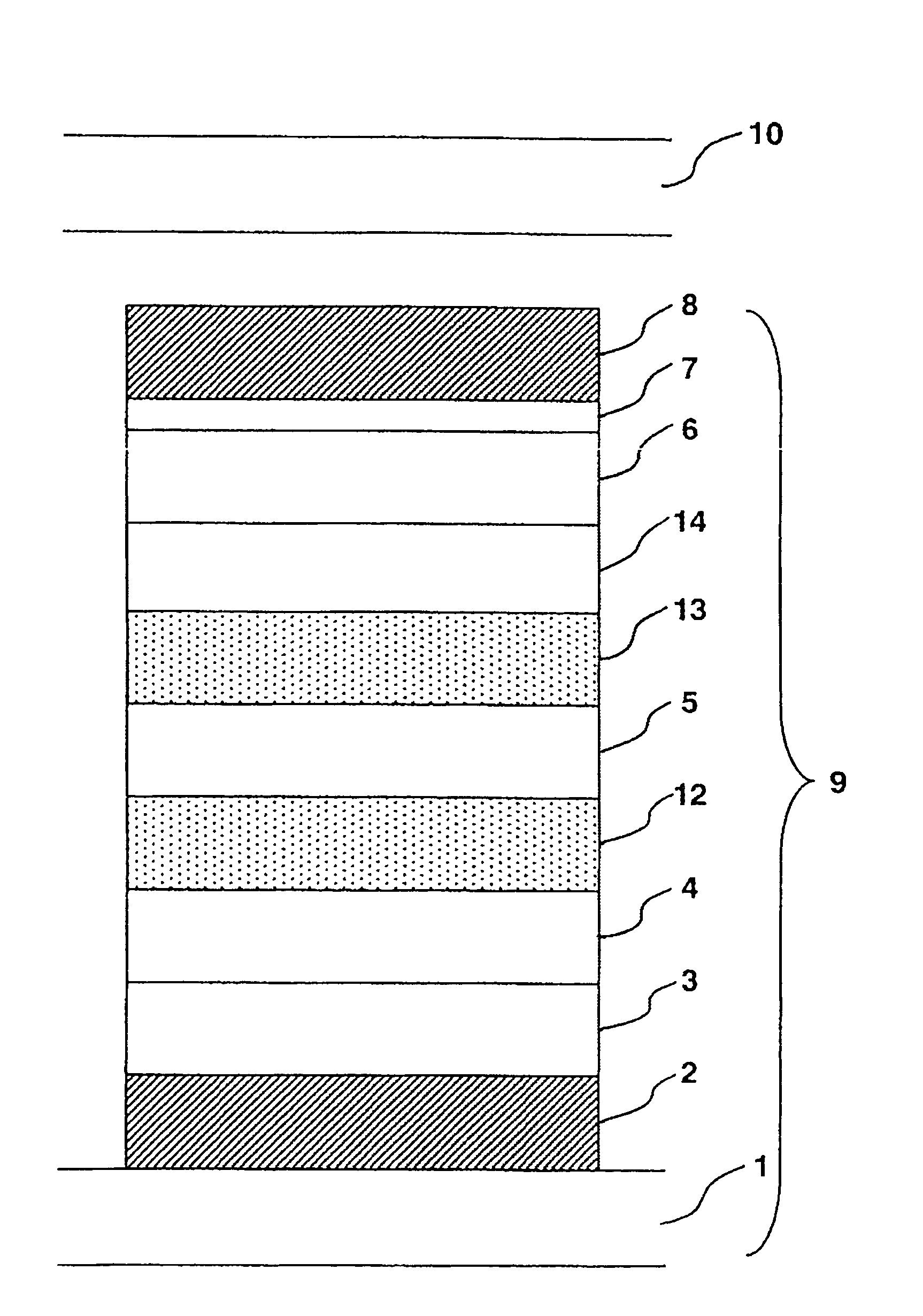

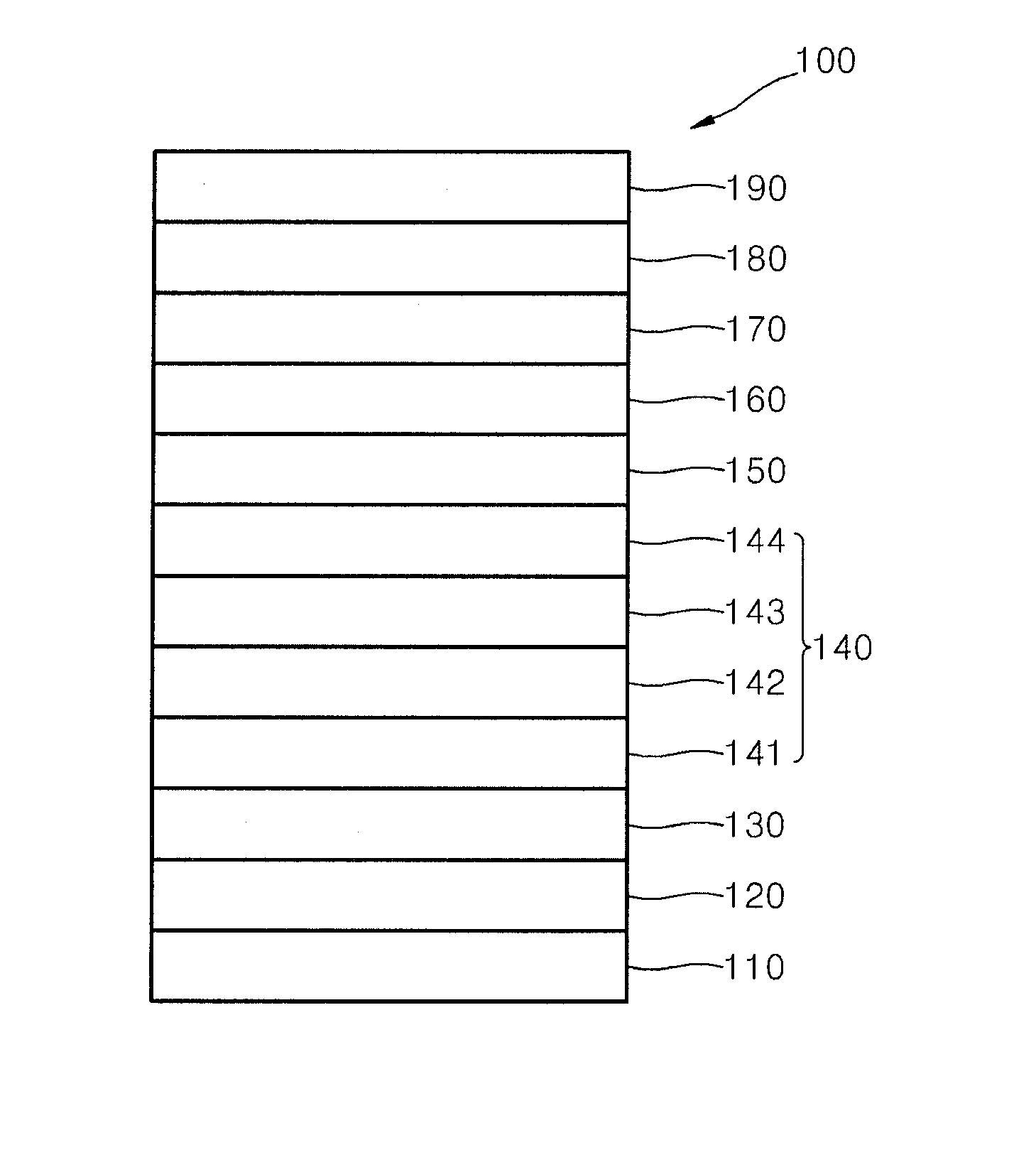

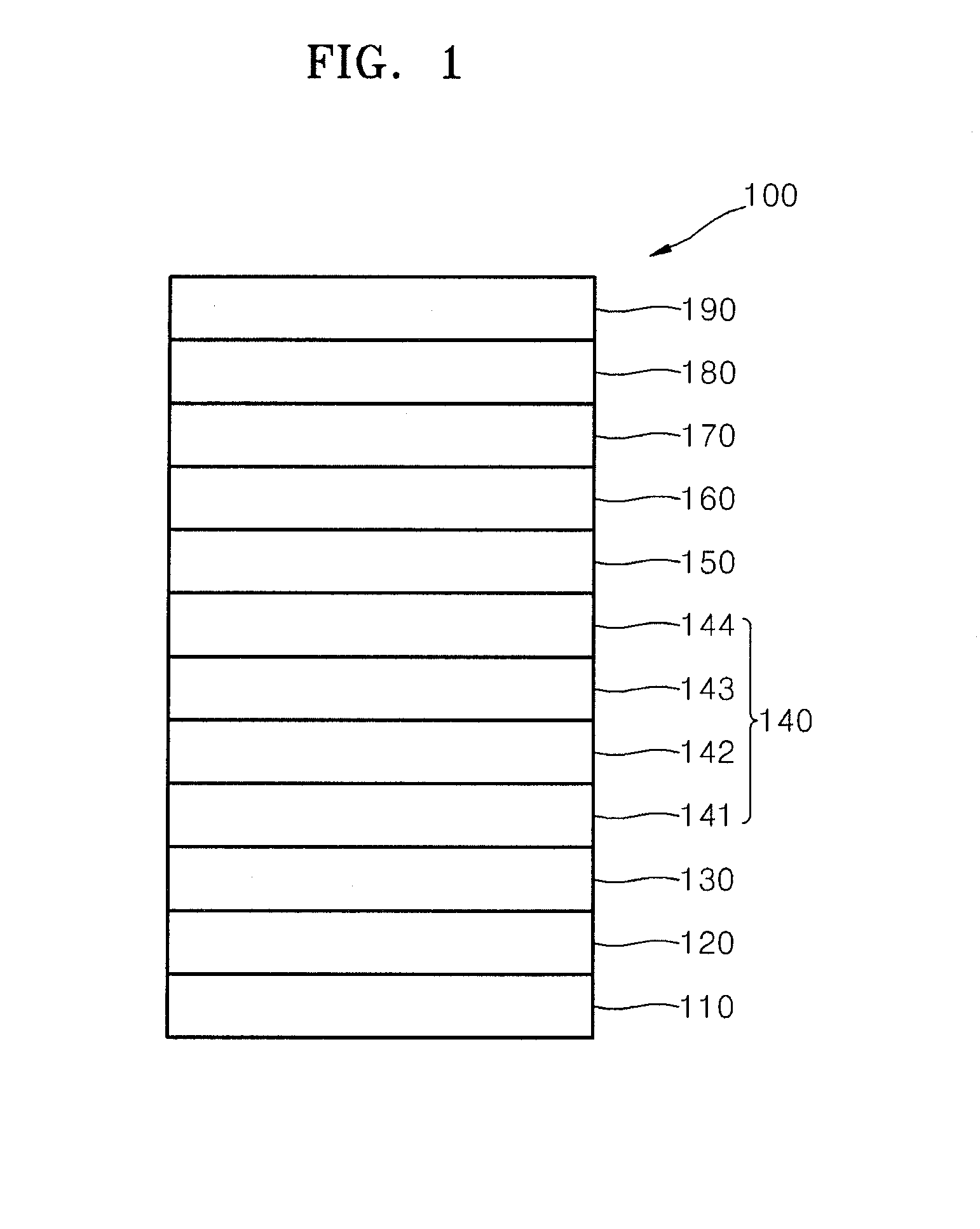

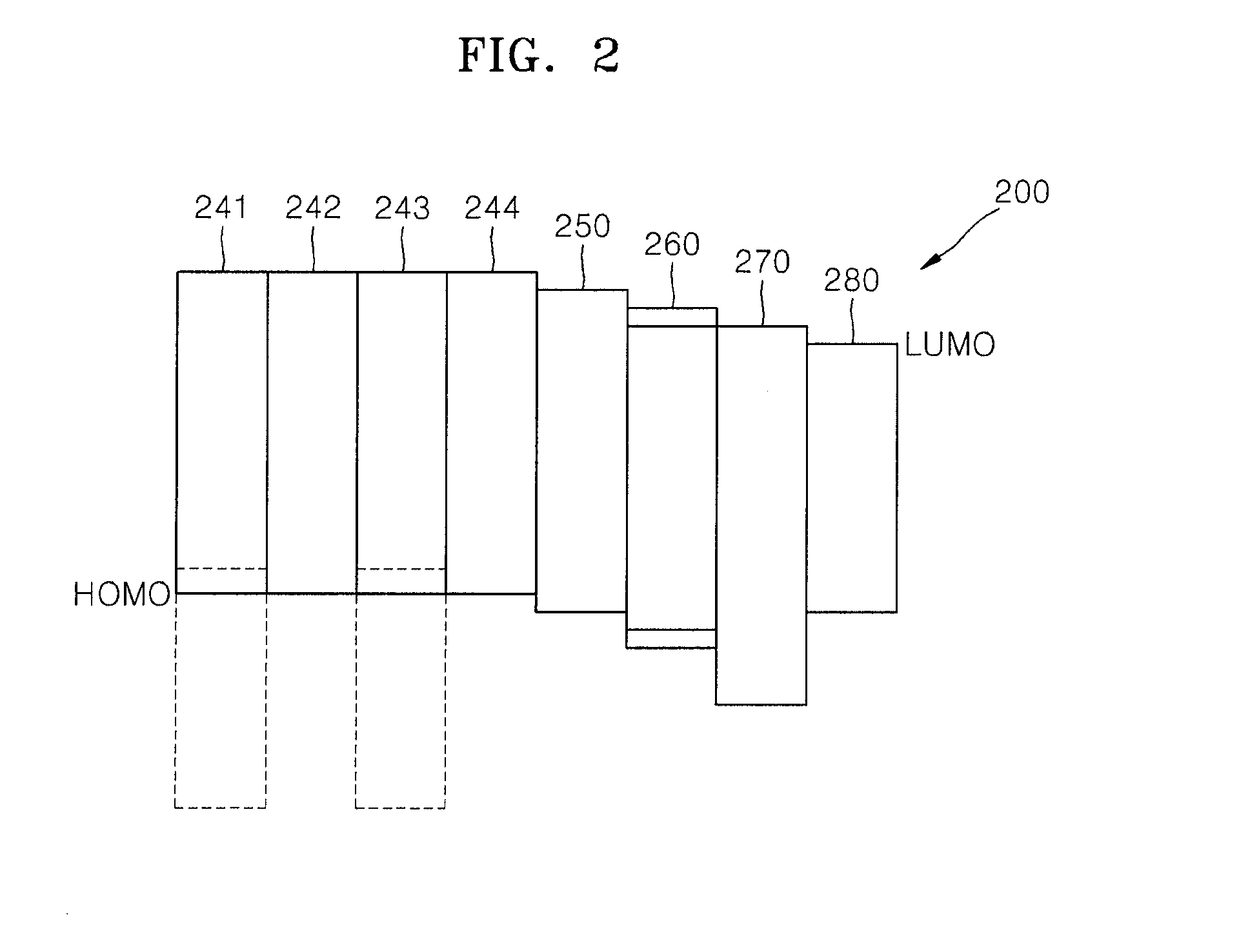

Organic light-emitting diode including multi-layered hole transporting layer, and flat display device including the organic light-emitting diode

ActiveUS20130140530A1Improve efficiencyExtend the lifespanOrganic chemistrySolid-state devicesDisplay deviceCharge generation

An organic light-emitting diode including: a first mixed layer between an emission layer and a first electrode and including first and second compounds; a second mixed layer between the emission layer and the first mixed layer and including third and fourth compounds; a first charge generation layer between the first mixed layer and the first electrode and including the first and second compounds and a first charge generation material; a second charge generation layer between the first mixed layer and the second mixed layer and including the third and fourth compounds and a second charge generation material; and a buffer layer between the emission layer and the second mixed layer, the first and the third compounds are each independently a compound represented by Formula 1 below, and the second compound and fourth compounds are each independently a compound represented by Formula 2 below:

Owner:SAMSUNG DISPLAY CO LTD

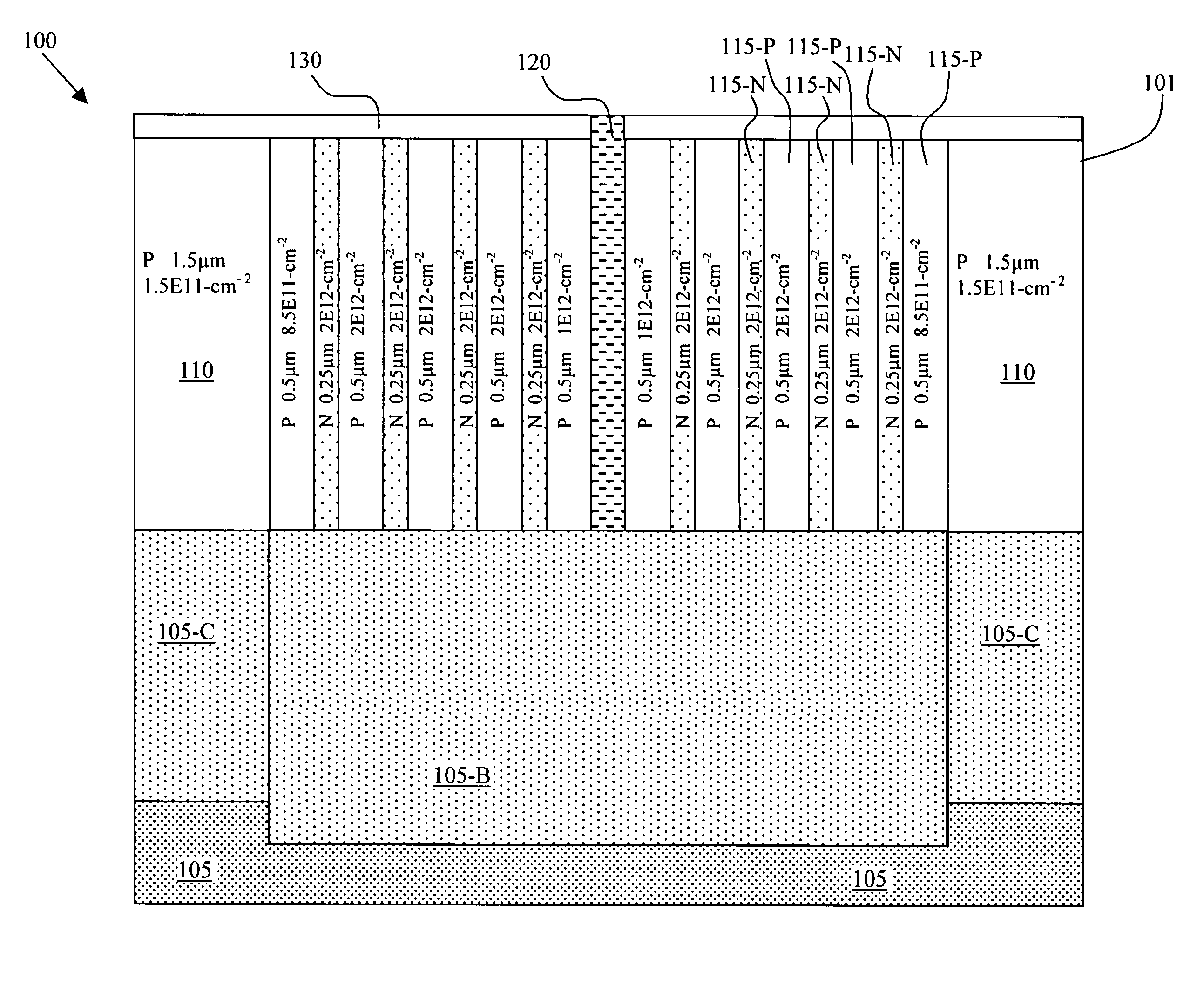

Nano-tube MOSFET technology and devices

ActiveUS7943989B2Improve charge balanceLow RDSSemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDielectric layer

This invention discloses a semiconductor power device disposed in a semiconductor substrate and the semiconductor substrate has a plurality of trenches. Each of the trenches is filled with a plurality of epitaxial layers of alternating conductivity types constituting nano tubes functioning as conducting channels stacked as layers extending along a sidewall direction with a “Gap Filler” layer filling a merging-gap between the nano tubes disposed substantially at a center of each of the trenches. The “Gap Filler” layer can be very lightly doped Silicon or grown and deposited dielectric layer. In an exemplary embodiment, the plurality of trenches are separated by pillar columns each having a width approximately half to one-third of a width of the trenches.

Owner:ALPHA & OMEGA SEMICON INC

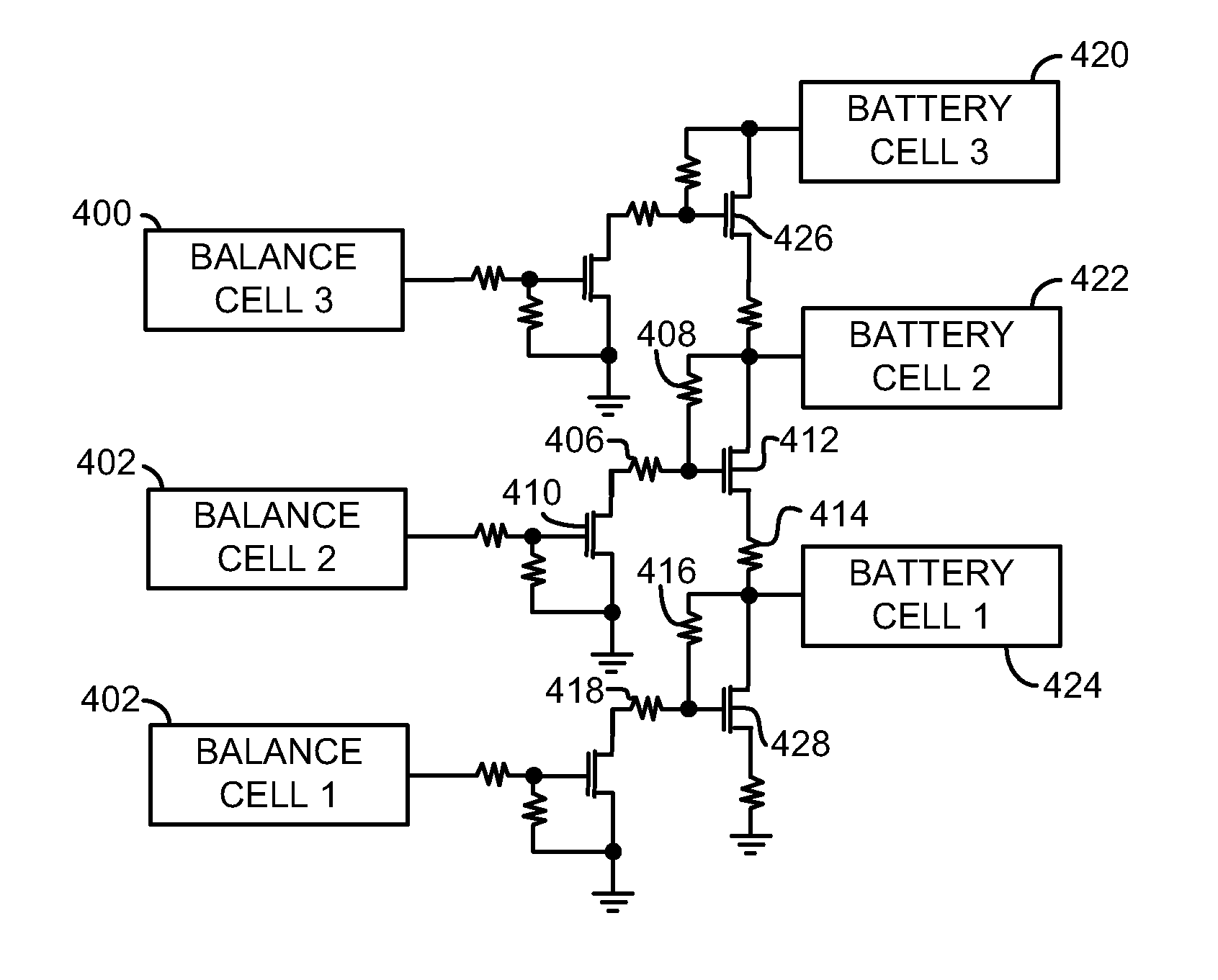

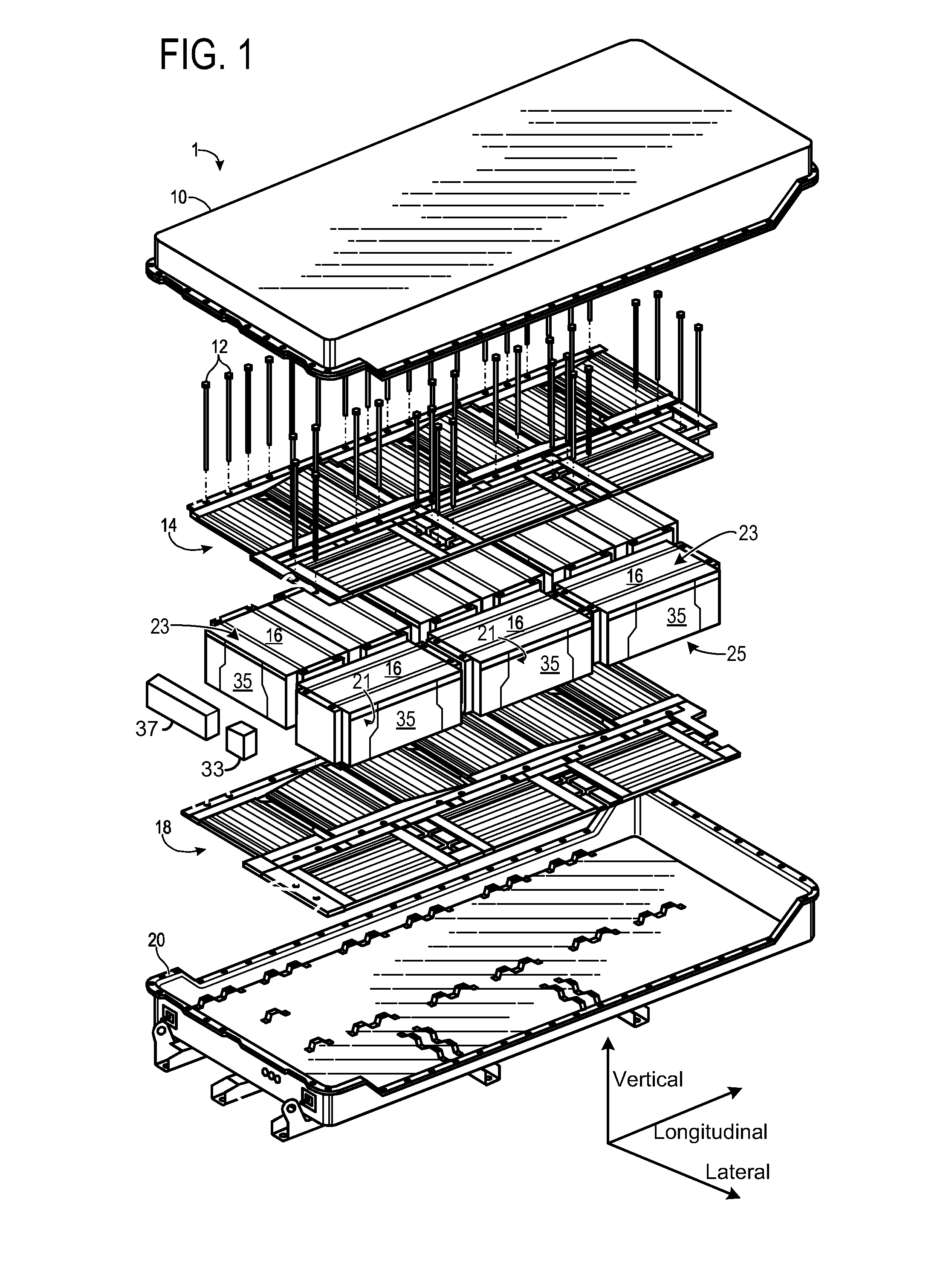

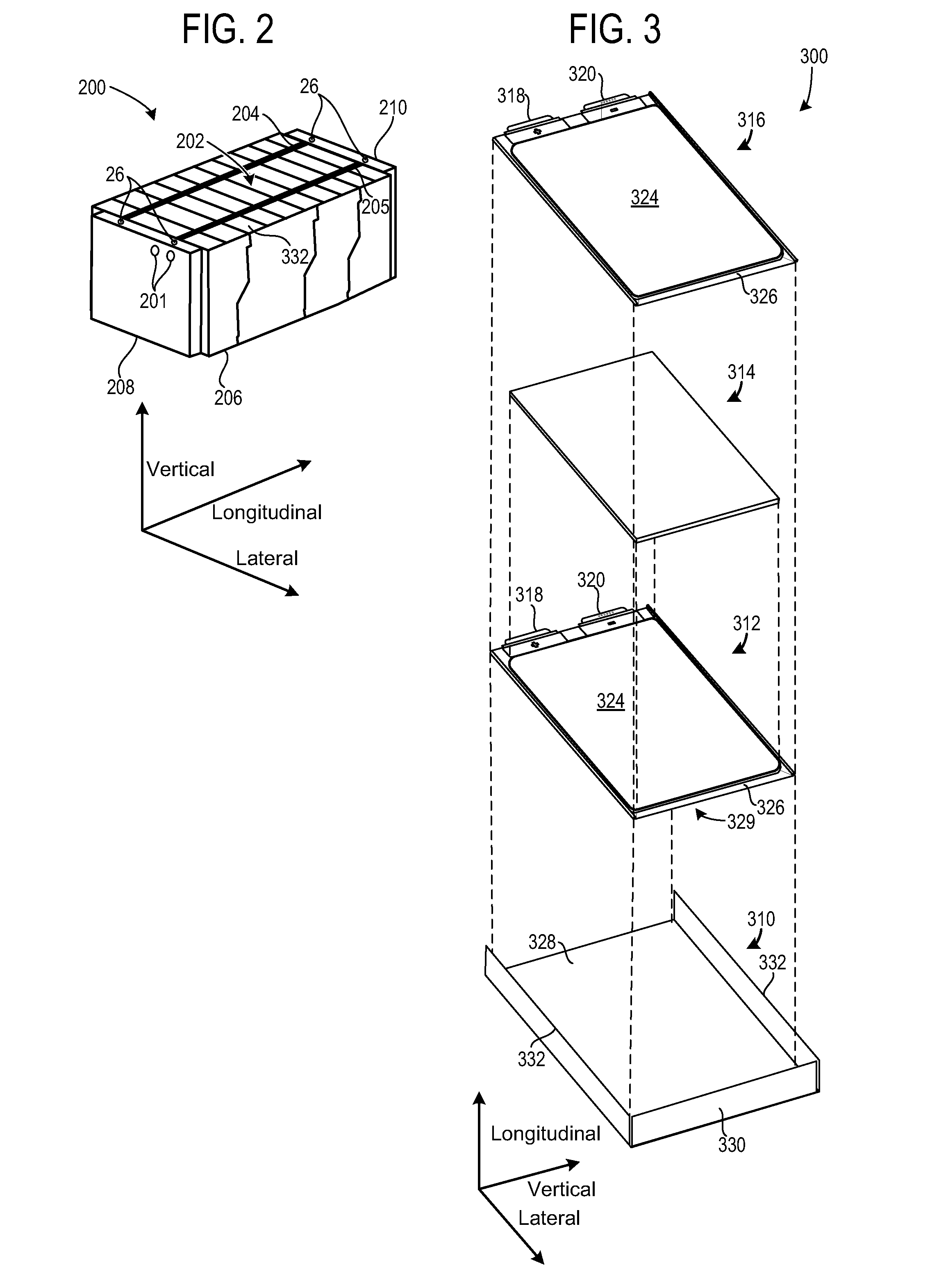

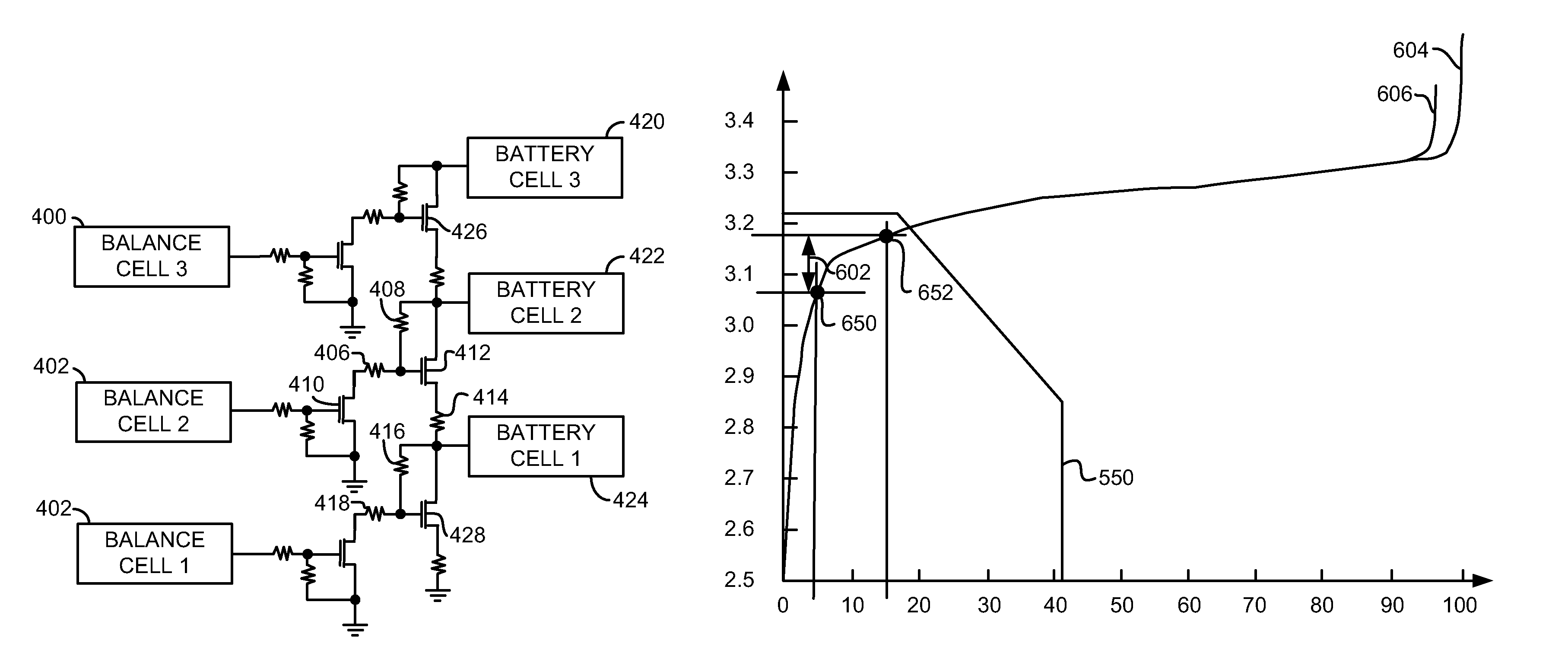

Method for Opportunistically Balancing Charge Between Battery Cells

ActiveUS20140049222A1Accurately determineAccurate balanceCharge equalisation circuitSecondary cellsImage resolutionEngineering

Systems and methods for balancing battery cells of a battery pack are disclosed. In one example, a charge imbalance is determined while battery cells operate in a high charge resolution voltage range. The charge imbalance determined during operation in the high charge resolution voltage range may be removed when the battery cells are operated in a low charge resolution voltage range. The system and method may be particularly useful for balancing battery cells that operate in the low charge resolution voltage range for a large portion of their operating time.

Owner:A123 SYSTEMS LLC

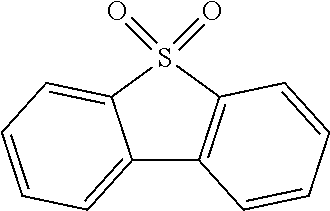

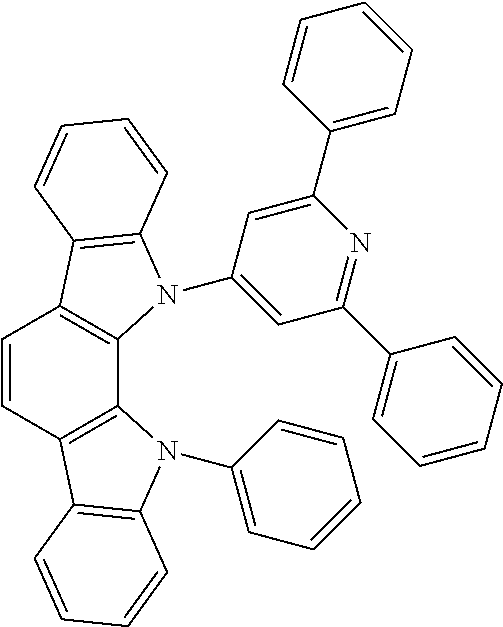

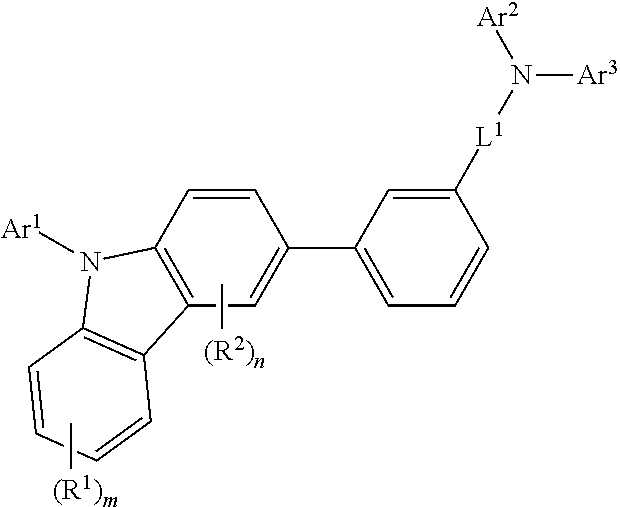

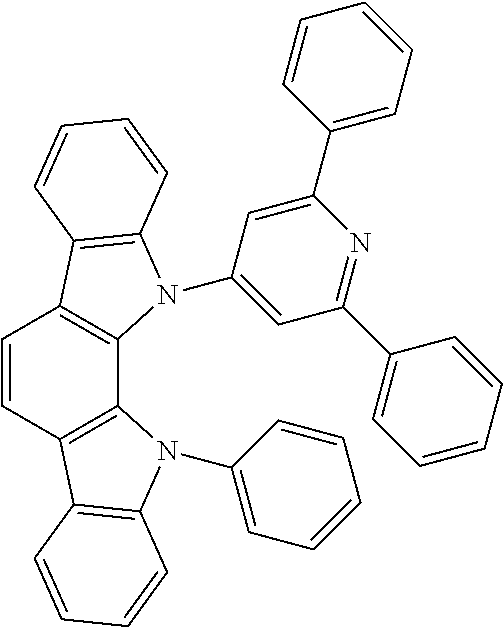

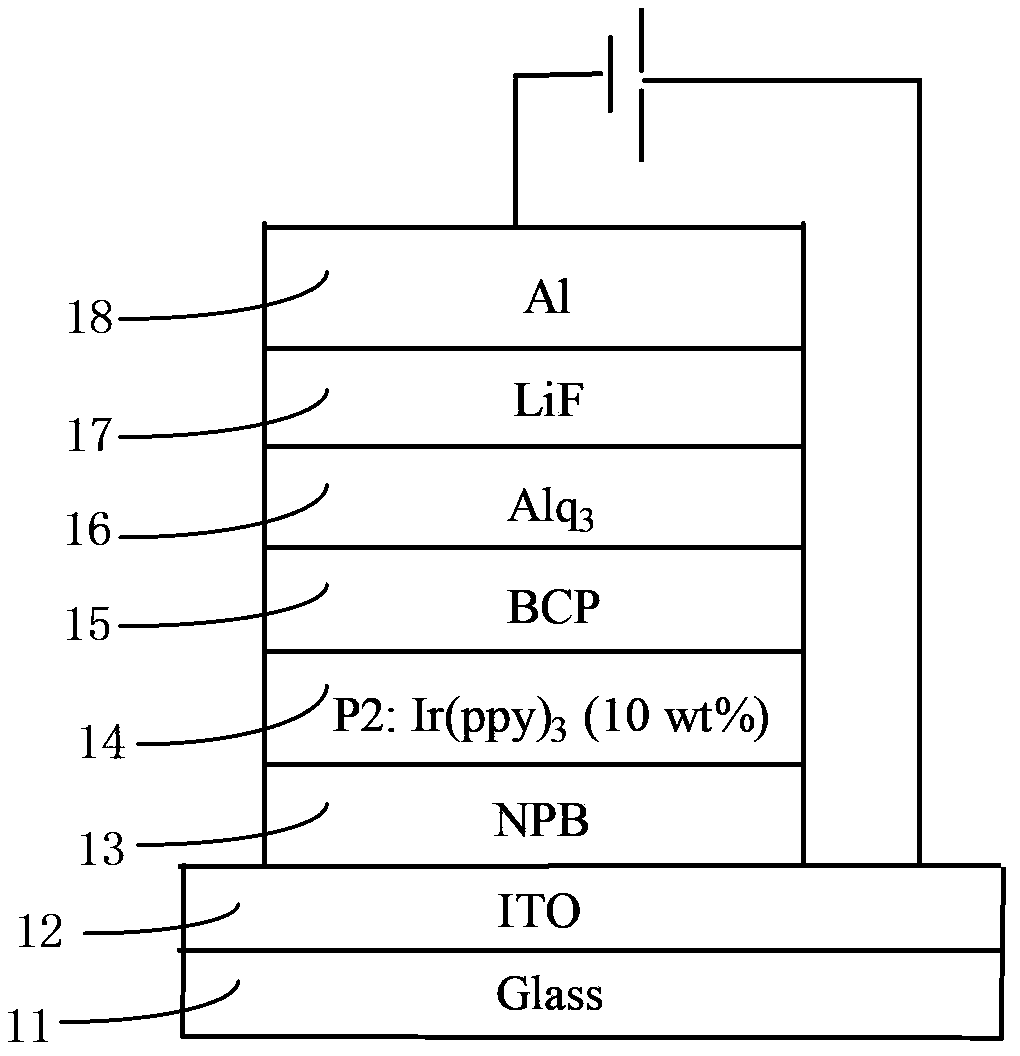

Organic Electroluminescent Device

ActiveUS20120305904A1Excellent characteristicsEasy injectionOrganic chemistryElectroluminescent light sourcesPolycyclic compoundCarbazole

Disclosed is an organic electroluminescent device (organic EL device) that is improved in luminous efficiency, sufficiently secures driving stability, and has a simple configuration. This organic EL device has a light-emitting layer between an anode and a cathode piled one upon another on a substrate and the said light-emitting layer contains a fused polycyclic compound in which seven or more rings are fused together as a host material. The aforementioned fused polycyclic compound has a structure formed by fusing two or more indole rings to a carbazole ring. A specific example thereof is the compound represented by the following formula.

Owner:NIPPON STEEL CHEMICAL CO LTD

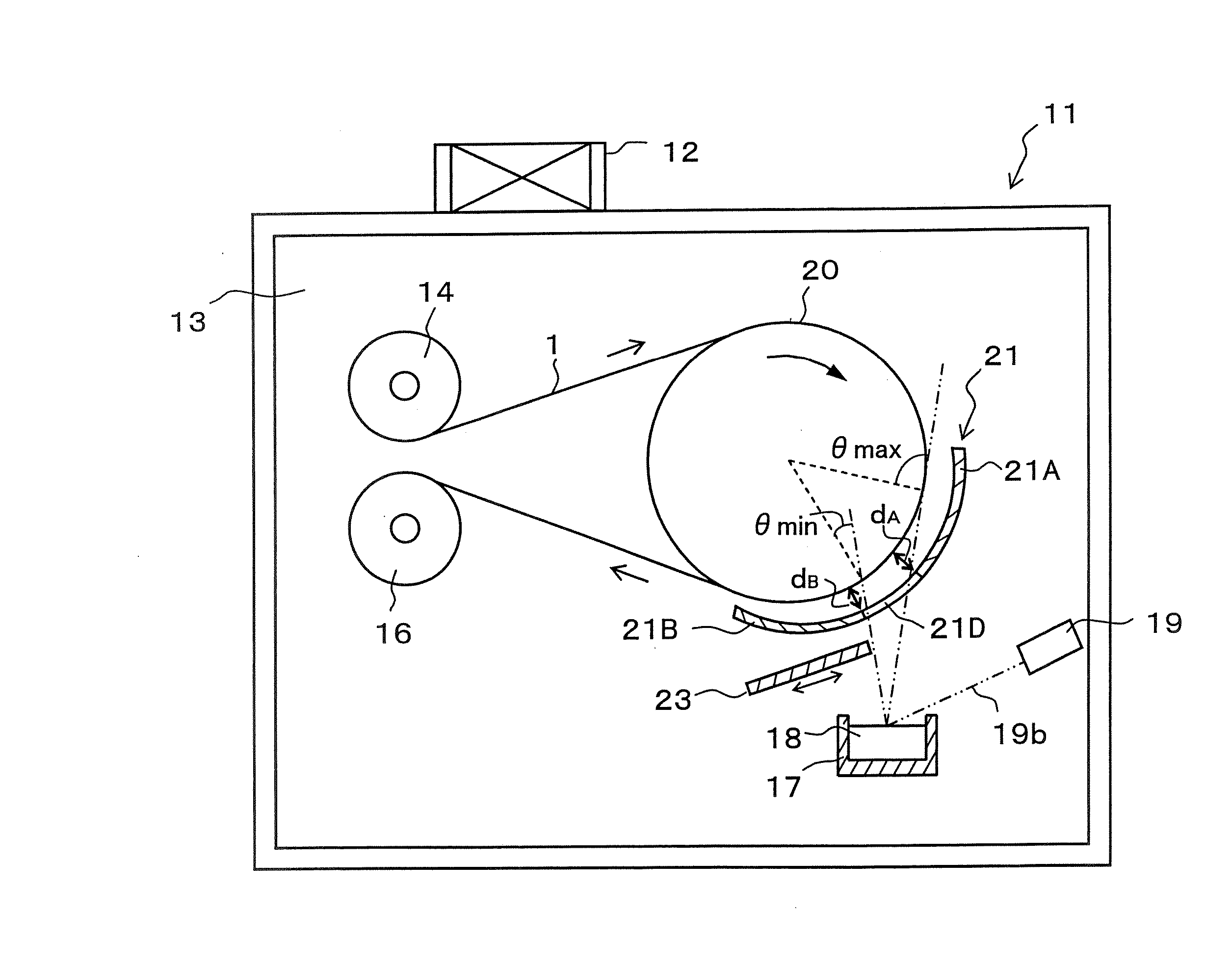

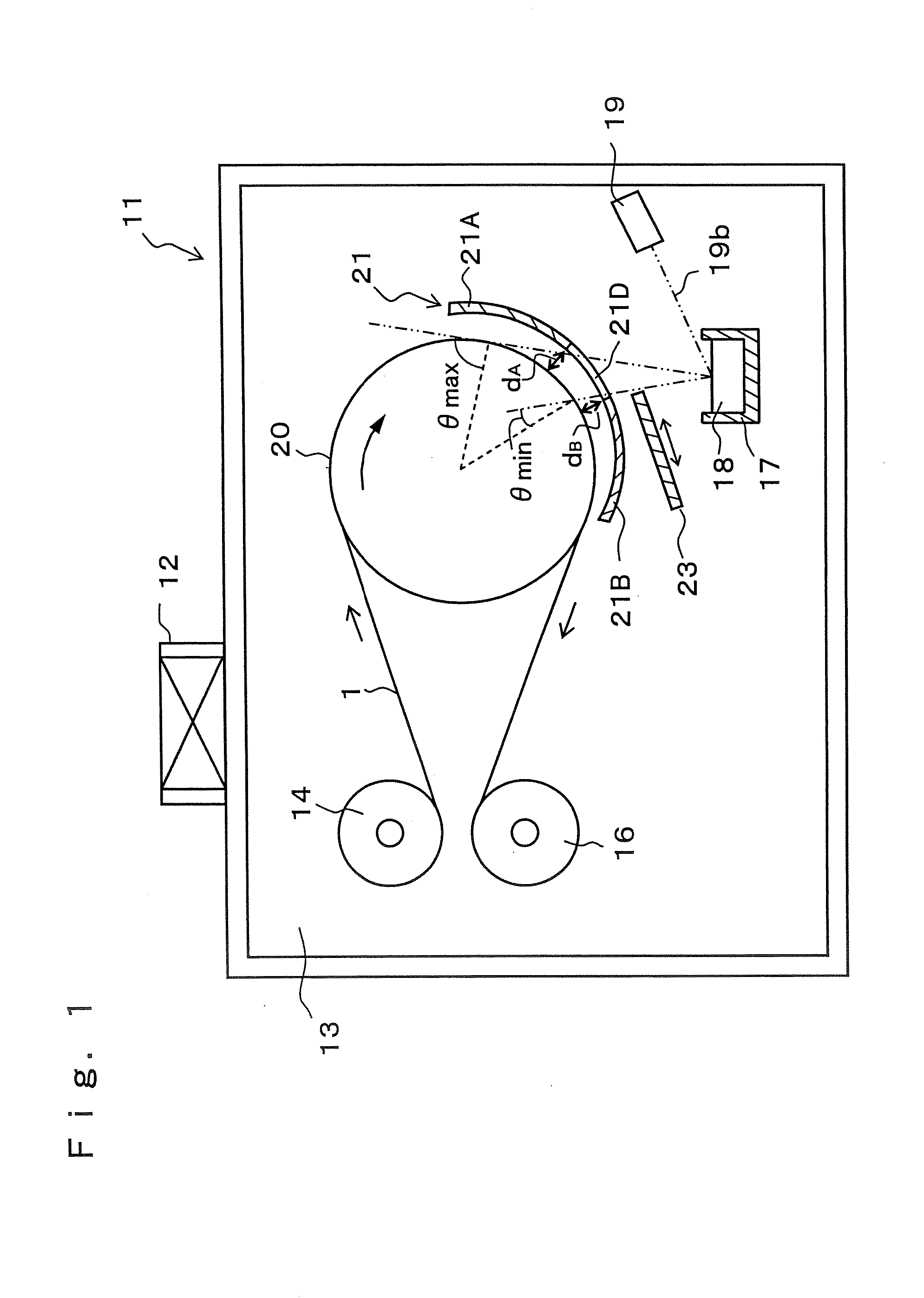

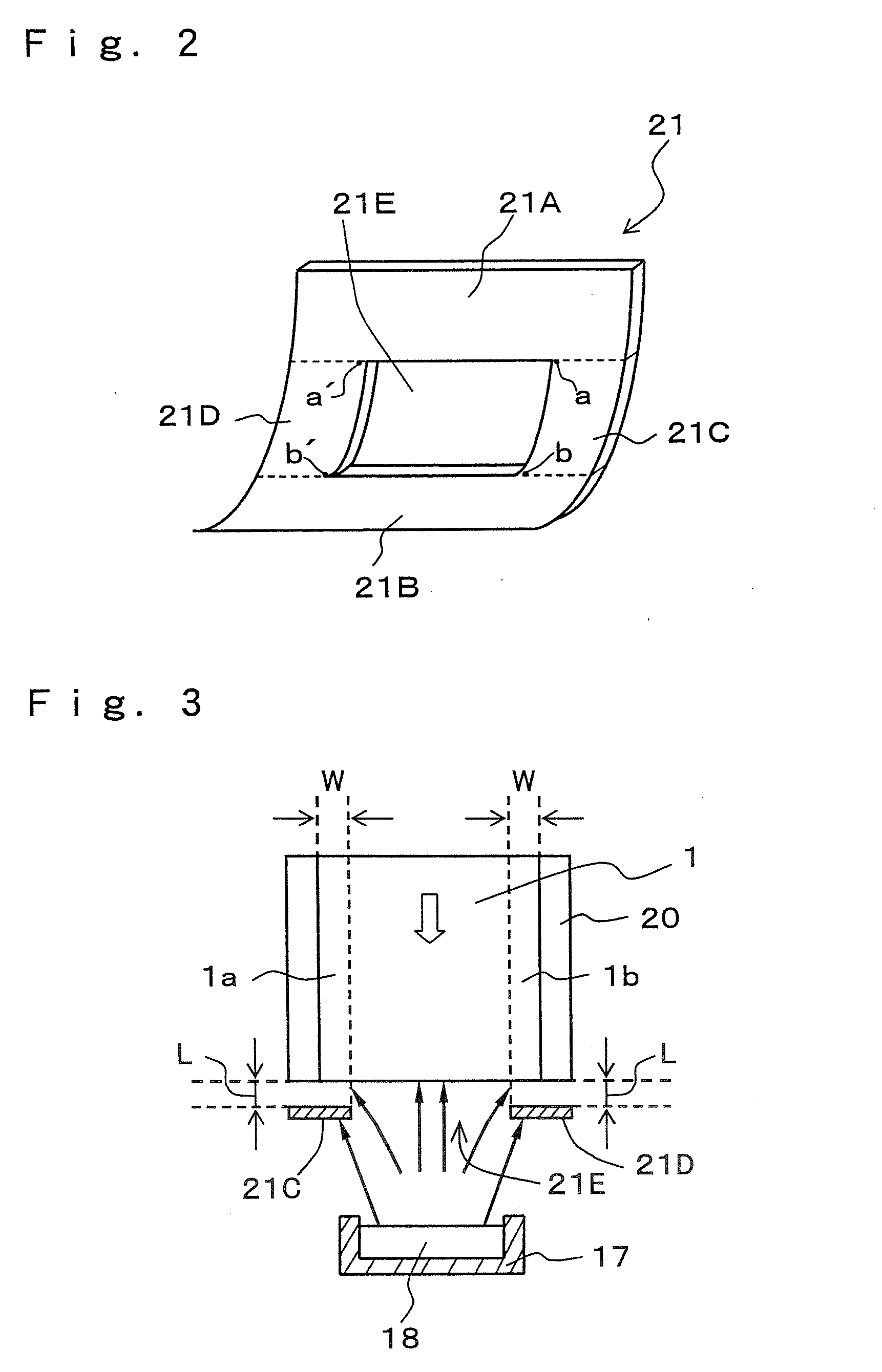

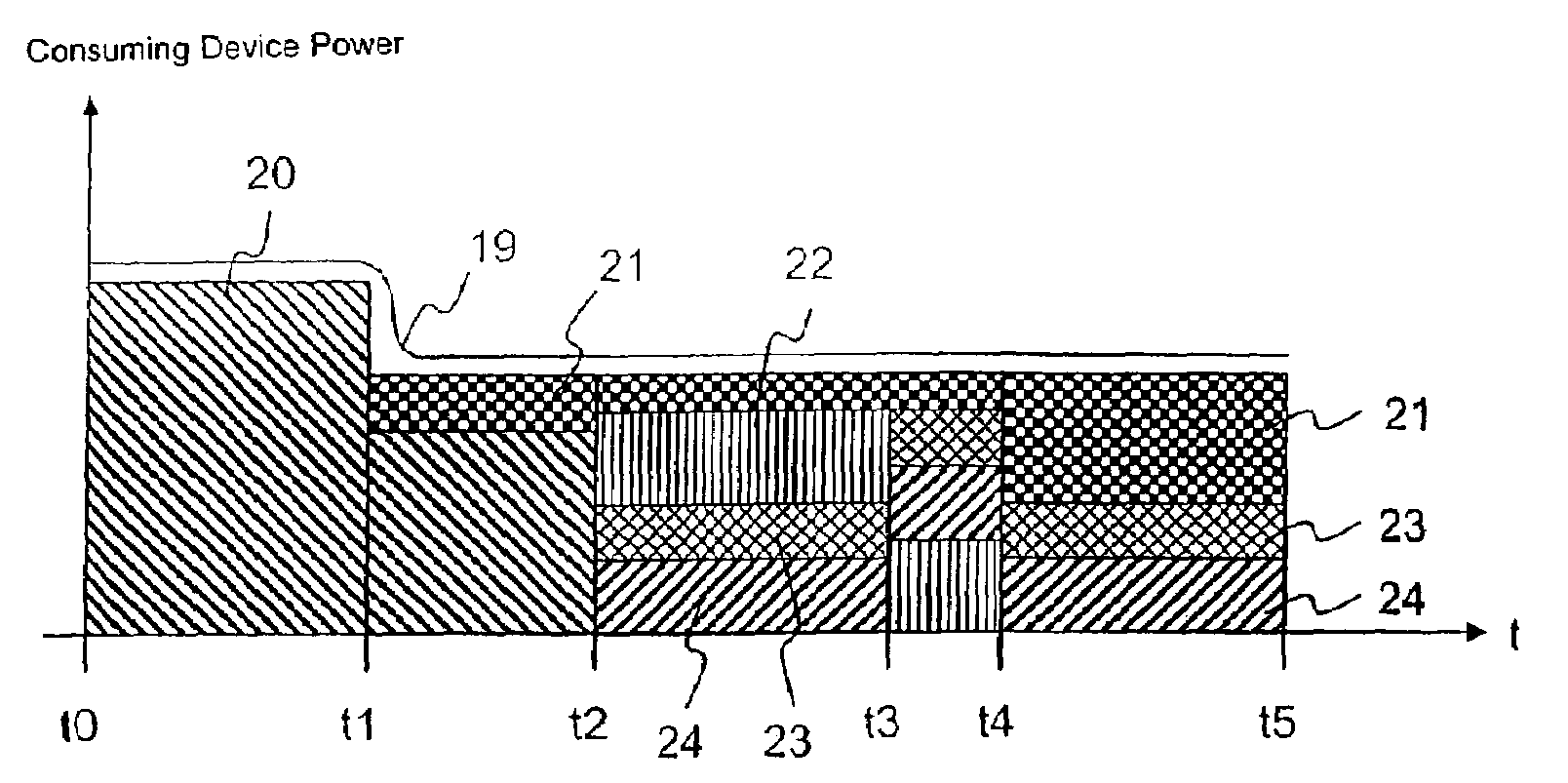

Apparatus and method for producing magnetic recording medium

InactiveUS20070026141A1Facilitate immigrationSuppress base film breakageVacuum evaporation coatingSputtering coatingGas phaseEngineering

The present invention provides an apparatus and a method for producing a magnetic recording medium, which are free from base film breakage, capable of running a base film stably during a vapor deposition preparation stage and a vapor deposition step, and excellent in production efficiency. The production apparatus comprises a supply roll 14 for delivering a non-magnetic substrate 1, a rotary cooling drum 20, a crucible 17 housing a vapor deposition material 18, a maximum incident angle regulating mask 21A for regulating a maximum incident angle of an evaporated vapor deposition material to the non-magnetic substrate, a minimum incident angle regulating mask 21B for regulating a minimum incident angle, a pair of edge portion regulating masks 21C and 21D for regulating deposition on both edges in a width direction of the non-magnetic substrate 1 surface, a shutter 23 capable of opening and closing an aperture among masks 21A, 21B, 21C, and 21D, and a winding roll 16, wherein the edge portion regulating masks 21C and 21D are provided in such a manner as to keep a distance dA between ends on upstream side of the edge portion regulating masks and the cooling drum 20 larger than a distance dB between ends on downstream side of the edge portion regulating masks and the cooling drum 20.

Owner:TDK CORPARATION

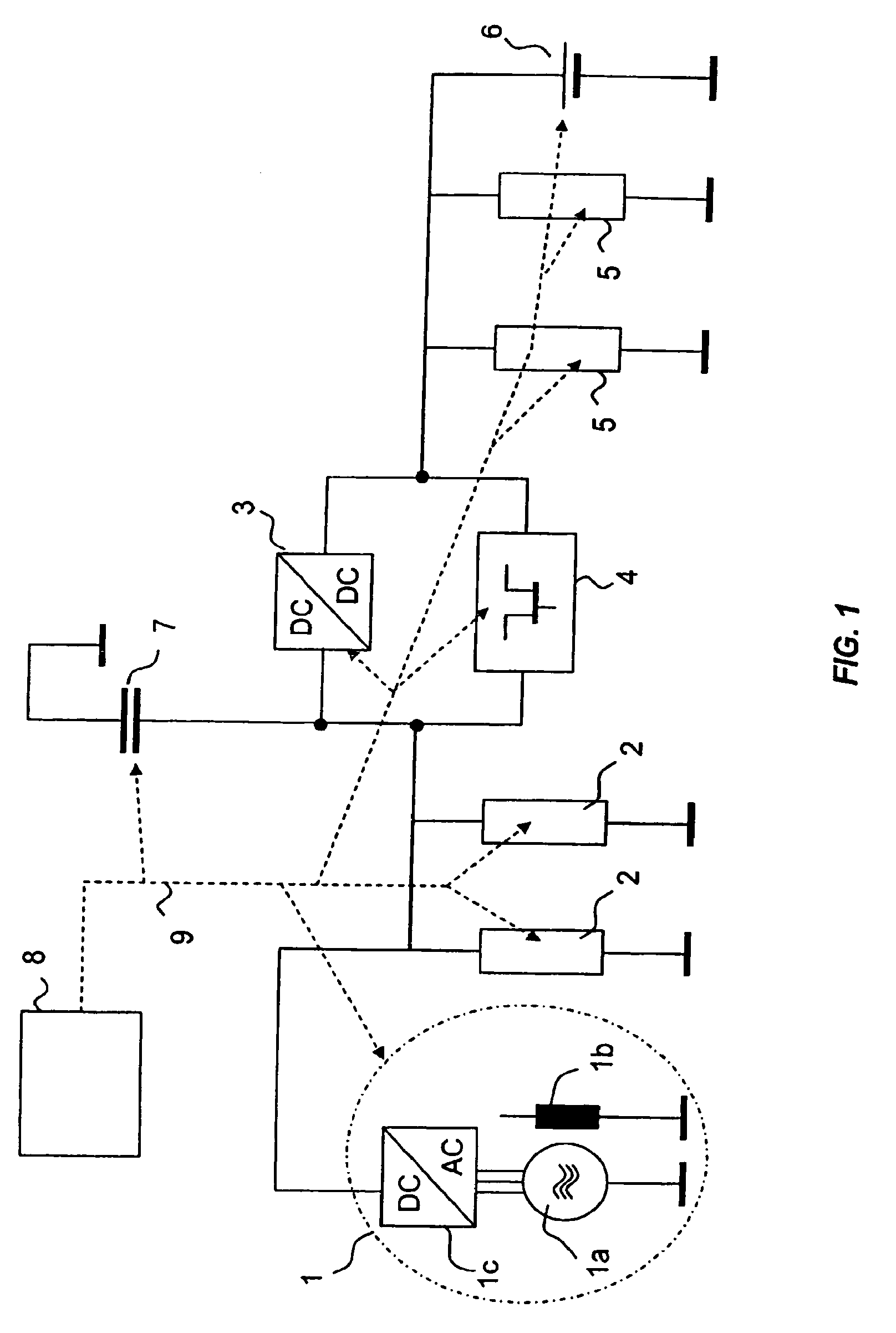

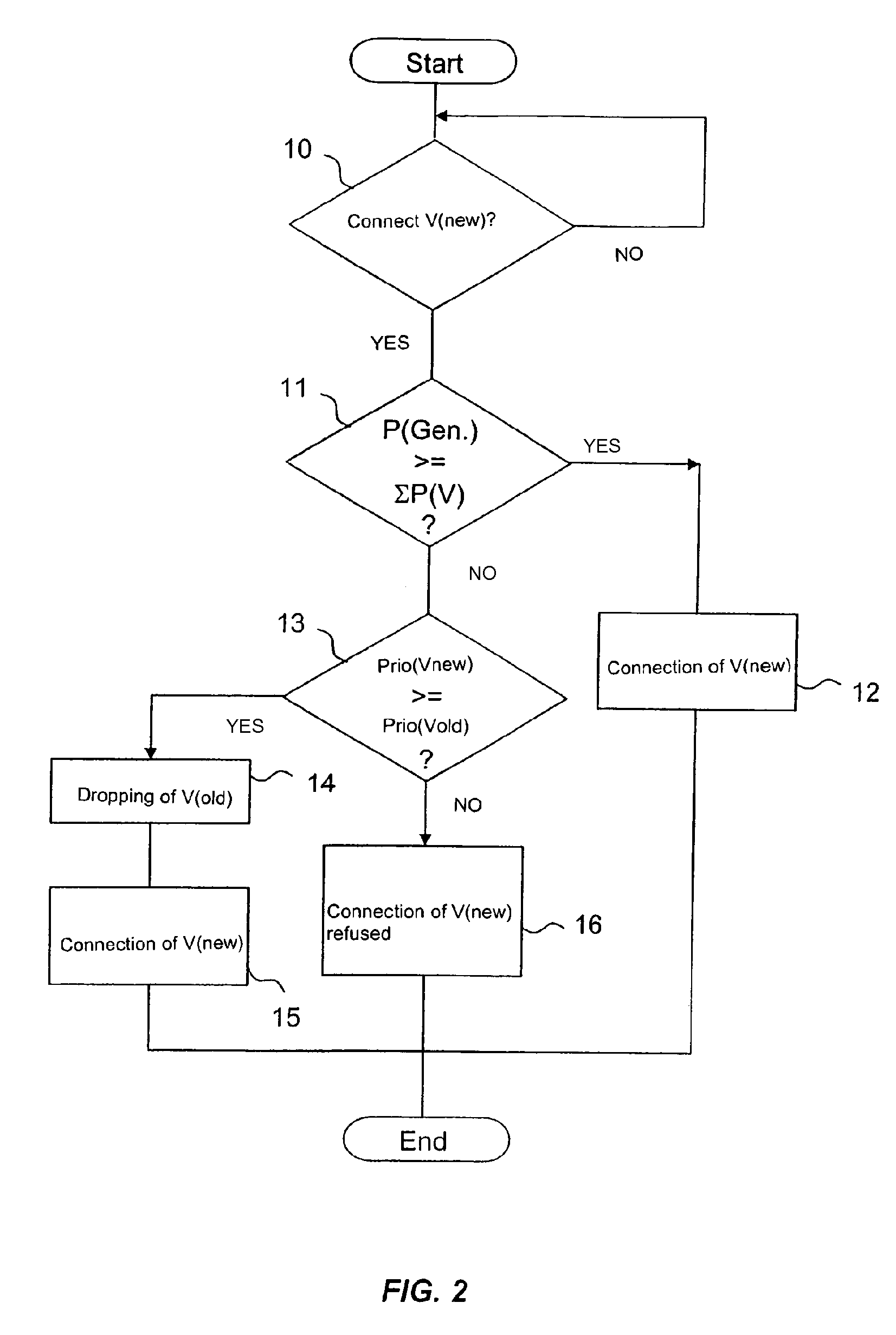

Method of controlling an onboard power supply system for a motor vehicle

InactiveUS7615879B2High temperature resistanceSmall and cost-effectiveEmergency protective circuit arrangementsLoad balancing in dc networkVoltage converterMobile vehicle

Owner:BAYERISCHE MOTOREN WERKE AG

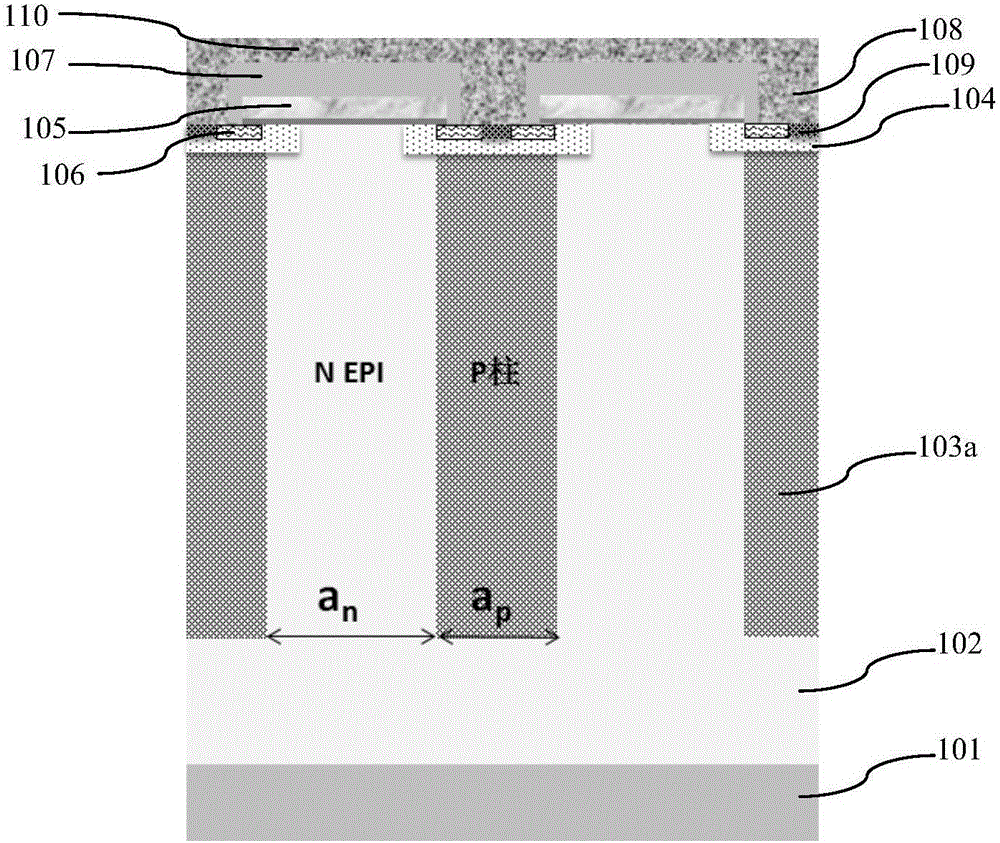

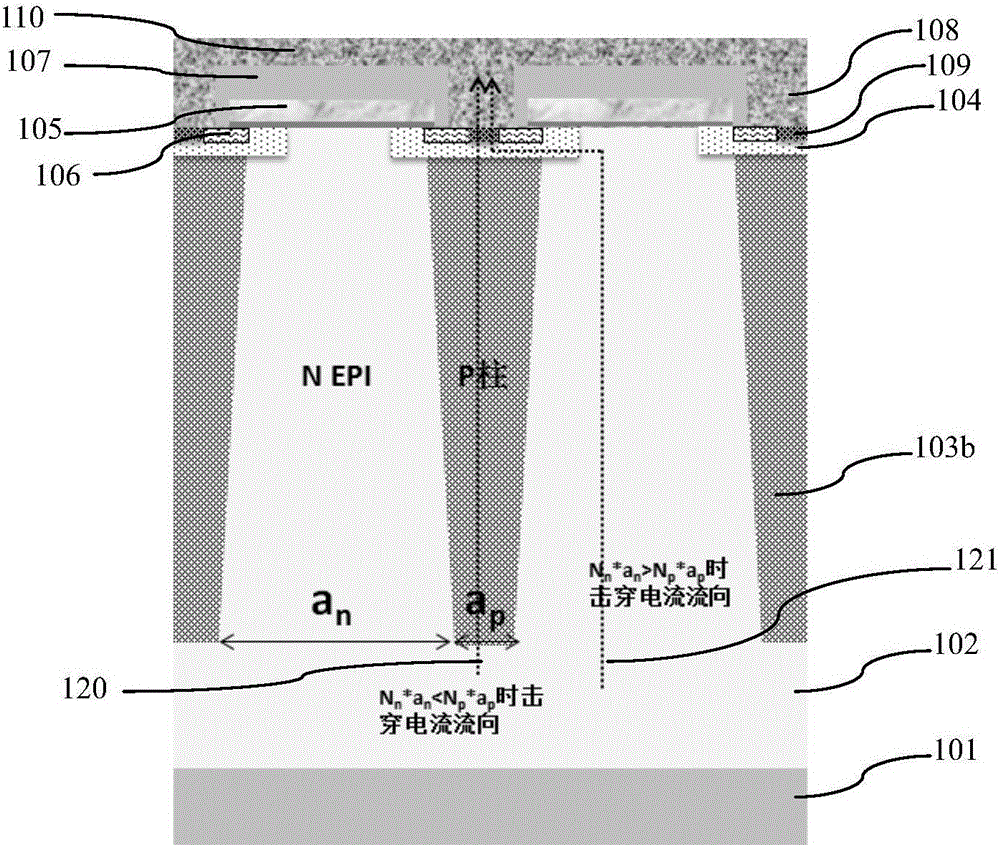

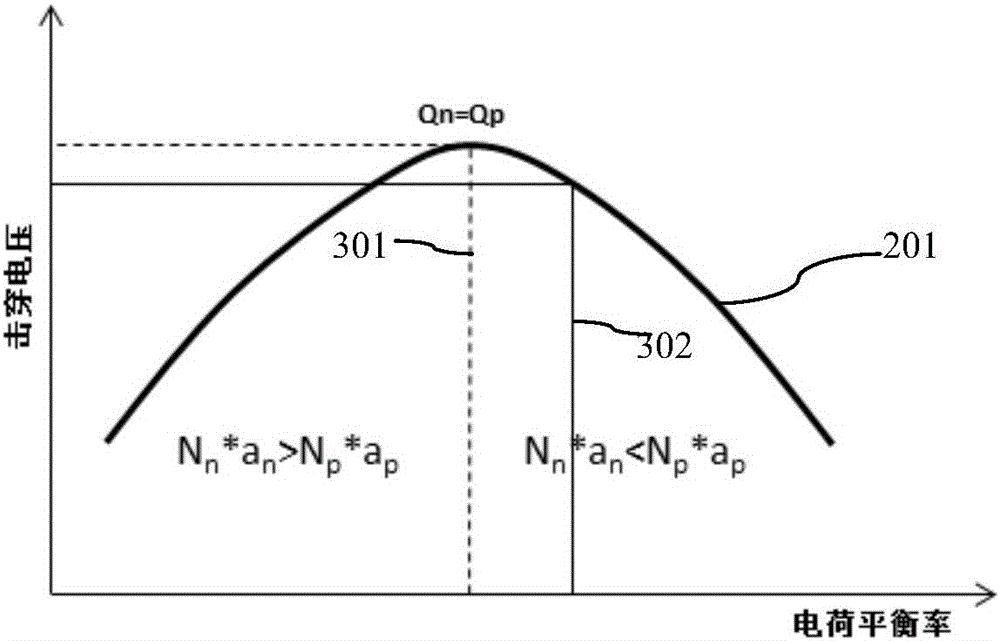

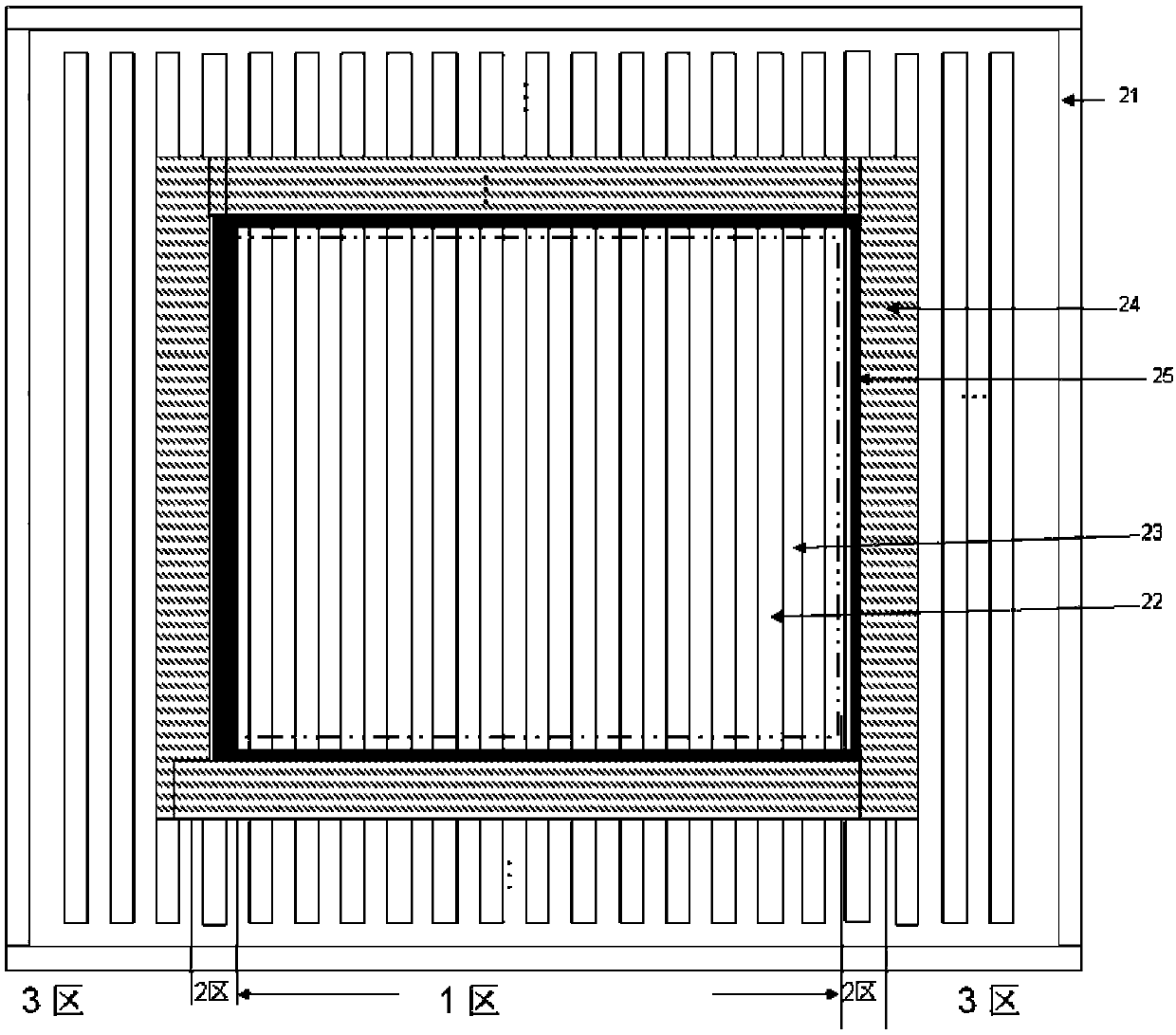

Super-junction power device and manufacturing method thereof

ActiveCN105957896AReduce filling defectsImprove stabilityTransistorSemiconductor/solid-state device manufacturingEtchingEngineering

The invention discloses a super-junction power device. A super-junction structure is formed on an N-type epitaxial layer; each groove is filled with a P-type post in the super-junction structure; the side surface of each groove is of an inclined structure to facilitate etching and filling of the groove; a doping compensation layer formed through ion implantation is formed on the side surface of each groove; and the doping concentration of each doping compensation layer in the direction from the top part of the corresponding groove to the bottom part is gradually changed for compensating the influence of the widths of the grooves at different depths on the charge balance of the P-type posts and N-type posts, so that the charge balance of the P-type posts at different depths of the grooves and the adjacent N-type posts is improved to improve the puncture voltage of the super-junction power device. The invention further discloses a manufacturing method of the super-junction power device. The puncture voltage of the super-junction structure with the inclined structures on the side surfaces of the grooves can be improved; and meanwhile, the device can also has good anti-impact ability.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Compound for organic electric element, organic electric element comprising the same and electronic device thereof

ActiveUS20150303379A1Solve low luminous efficiencyReduce the driving voltageOrganic chemistryStatic indicating devicesElectronic componentElectron

Owner:DUK SAN NEOLUX

Compound for organic electric element, organic electric element comprising the same and electronic device thereof

ActiveUS20150325795A1Increase valueWide bandgapOrganic chemistryStatic indicating devicesElectronMolecular physics

Owner:DUK SAN NEOLUX +1

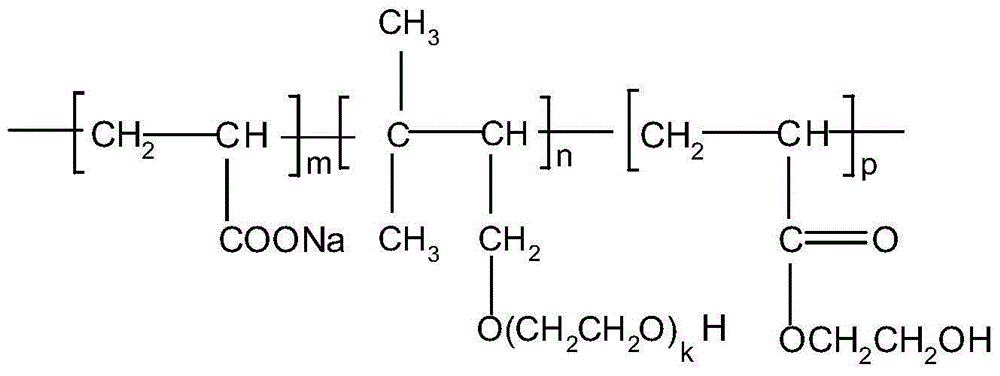

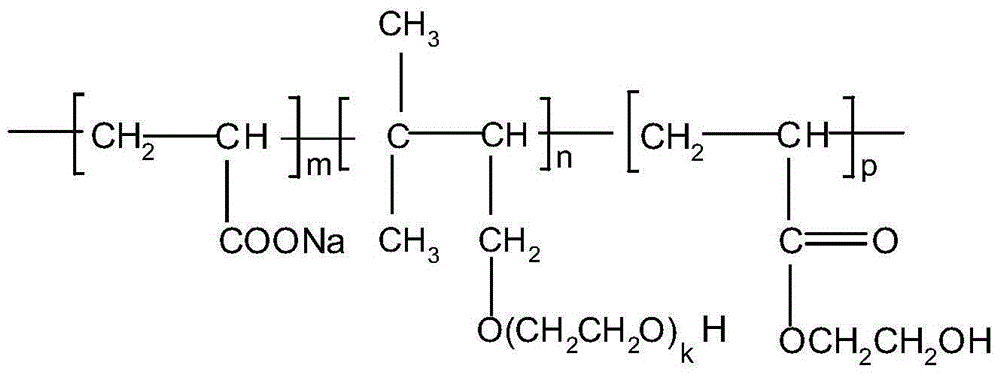

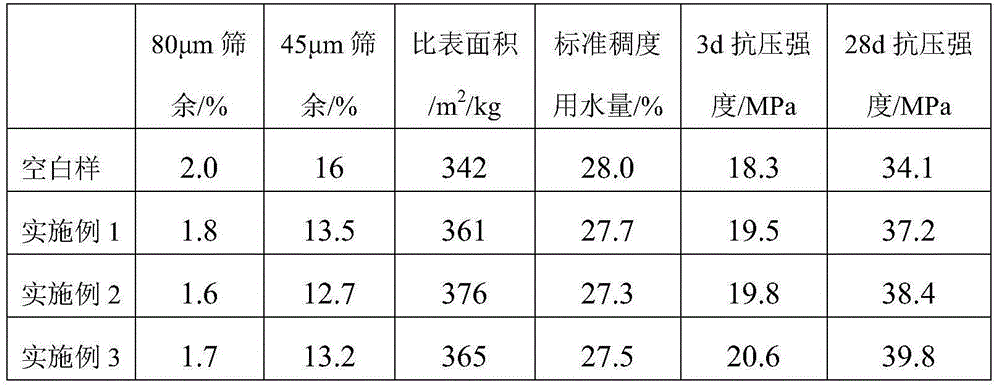

High-limestone-flour-adulterate-amount composite enhanced grinding aid for cement and preparation method of high-limestone flour-adulterate amount composite enhanced grinding aid

The invention relates to a high-limestone-flour-adulterate-amount composite enhanced grinding aid for cement and a preparation method of the high-limestone-flour-adulterate-amount composite enhanced grinding aid. The preparation method comprises the following steps that 1, materials including 18%-25% of triethanolamine, 8%-15% of triisopropanolamine, 20%-28% of ethanediol, 8%-12% of molasses, 4%-8% of polycarboxylate superplasticizer, 6%-10% of sodium sulfate, 5%-8% of glacial acetic acid and 2%-24% of water are taken; 2, the water is poured into an agitator kettle, and sodium sulfate is added to be stirred till sodium sulfate is completely dissolved; 3, glacial acetic acid is added to be completely dissolved, triethanolamine, triisopropanolamine, ethanediol, molasses and polycarboxylate superplasticizer are sequentially added after glacial acetic acid is dissolved, stirring continues to be carried out for 20-30 minutes, and the high-limestone flour-adulterate amount composite enhanced grinding aid is obtained. The high-limestone-flour-adulterate-amount composite enhanced grinding aid has the advantages that cement particles are prevented from clustering, and the cement particles are kept in a high homodisperse state; the strength of an interfacial transition zone is increased, and the strength of the cement is further increased; the grinding aiding efficiency of the grinding aid is improved.

Owner:WUHAN UNIV OF TECH

Organic electroluminescent device

ActiveUS9133205B2Improve featuresIncreased durabilityOrganic chemistryElectroluminescent light sourcesPolycyclic compoundCarbazole

Disclosed is an organic electroluminescent device (organic EL device) that is improved in luminous efficiency, sufficiently secures driving stability, and has a simple configuration. This organic EL device has a light-emitting layer between an anode and a cathode piled one upon another on a substrate and the said light-emitting layer contains a fused polycyclic compound in which seven or more rings are fused together as a host material. The aforementioned fused polycyclic compound has a structure formed by fusing two or more indole rings to a carbazole ring. A specific example thereof is the compound represented by the following formula.

Owner:NIPPON STEEL CHEMICAL CO LTD

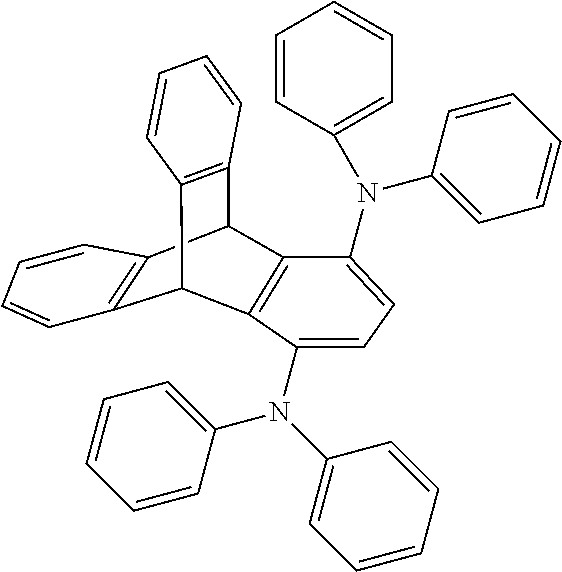

Organic electroluminescent device

InactiveUS20110272680A1Good hole transport propertiesImprove featuresOrganic chemistrySolid-state devicesArylElectron hole

Disclosed is a useful organic EL device which comprises a phosphorescent light-emitting layer and is endowed with improved luminous efficiency and high driving stability. Also disclosed is a hole-transporting material suitable for use in the phosphorescent light-emitting device. The hole-transporting material is a triptycene derivative which has substituents at the 9- and 10-positions and is substituted with an aromatic group containing at least one diarylamino group (—ArNAr2). The organic EL device contains the triptycene derivative in at least one organic layer selected from the group of a phosphorescent light-emitting layer, a hole-transporting layer, an electron-blocking layer, and an exciton-blocking layer. The diarylamino group (—NAr2) may be fused to form an aromatic heterocyclic group such as a carbazolyl group.

Owner:NIPPON STEEL CHEMICAL CO LTD

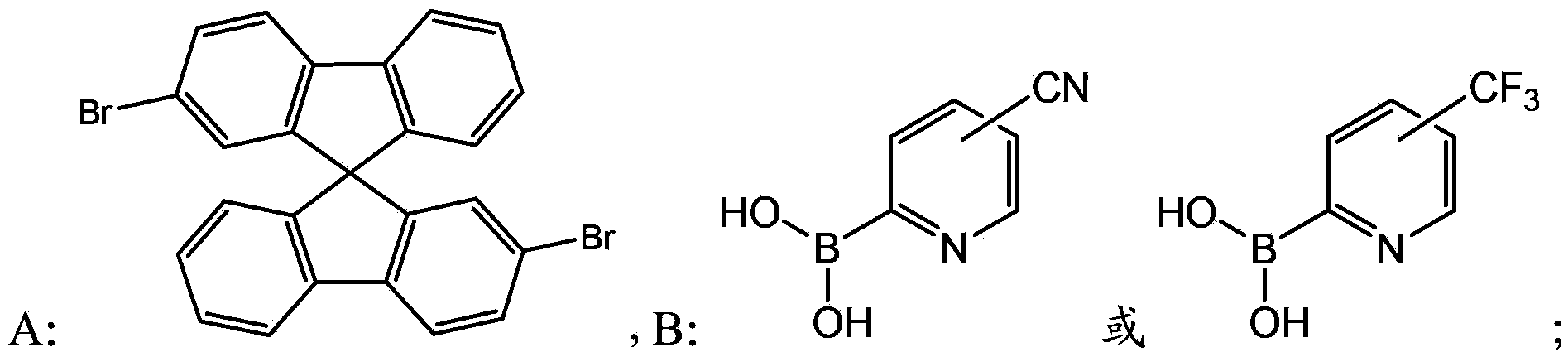

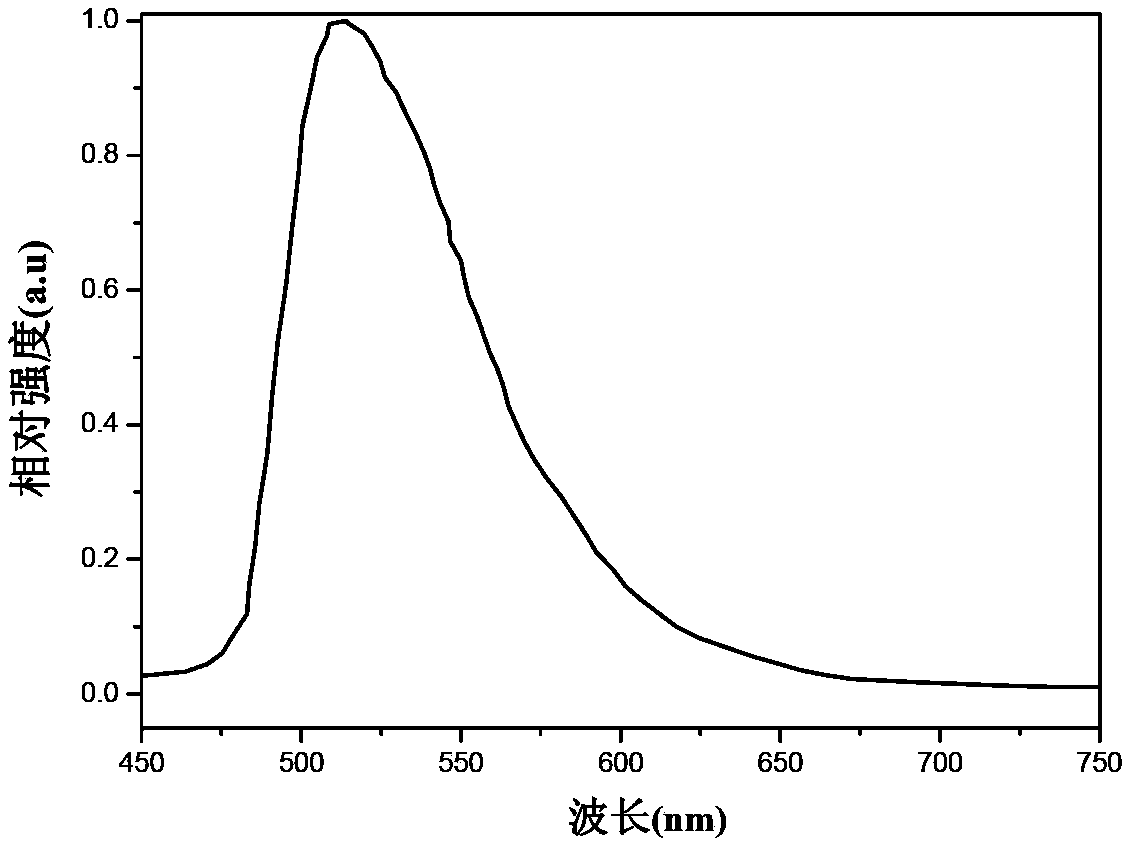

Electron transport material as well as preparation method and organic electroluminescence device thereof

InactiveCN104072405AImprove thermal stabilityEnhanced electron transport capabilitiesOrganic chemistrySolid-state devicesThermal stabilityStructural formula

The invention belongs to the field of photoelectrical materials, and in particular provides an electron transport material. The structural formula of the electron transport material is as shown in a formula (1) in the specification, and in the formula (1), Ar is as shown in the specification. The electron transport material is excellent in dissolving property, film-forming property and thermal stability, and is also excellent in electron transport property. The invention further provides a preparation method of the electron transport material and an organic electroluminescence device containing the electron transport material.

Owner:OCEANS KING LIGHTING SCI&TECH CO LTD +2

Organic electrophosphorescent main body material as well as preparation method thereof and organic electroluminescence device

InactiveCN104073246AEasy to processGood film-forming performanceOrganic chemistrySolid-state devicesOrganic electroluminescenceChemistry

The invention belongs to the field of photoelectric materials and specifically provides an organic electrophosphorescent main body material. A structural formula of the organic electrophosphorescent main body material is as shown in formula (1) in the specification, wherein R is H or C1-C6 alkyl. The organic electrophosphorescent main body material disclosed by the invention has excellent dissolving performance, film-forming performance and thermal stability, and has higher electron transporting performance. The invention further provides a preparation method of the organic electrophosphorescent main body material and an organic electroluminescence device containing the organic electrophosphorescent main body material.

Owner:OCEANS KING LIGHTING SCI&TECH CO LTD +2

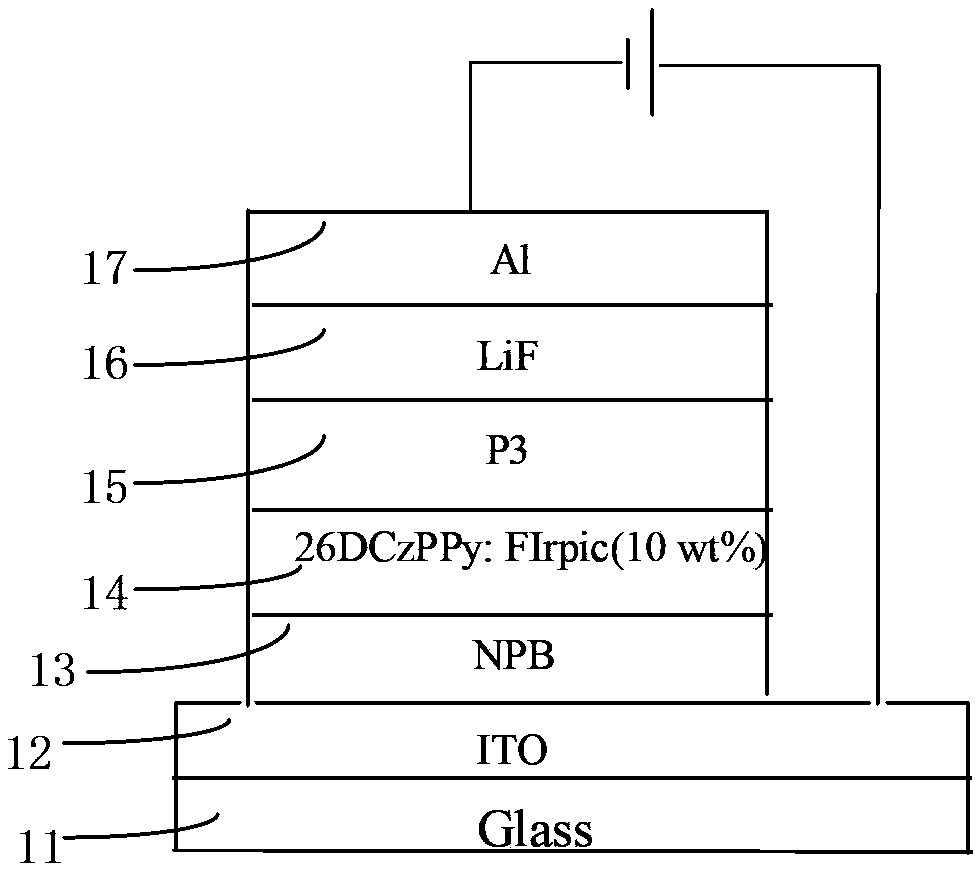

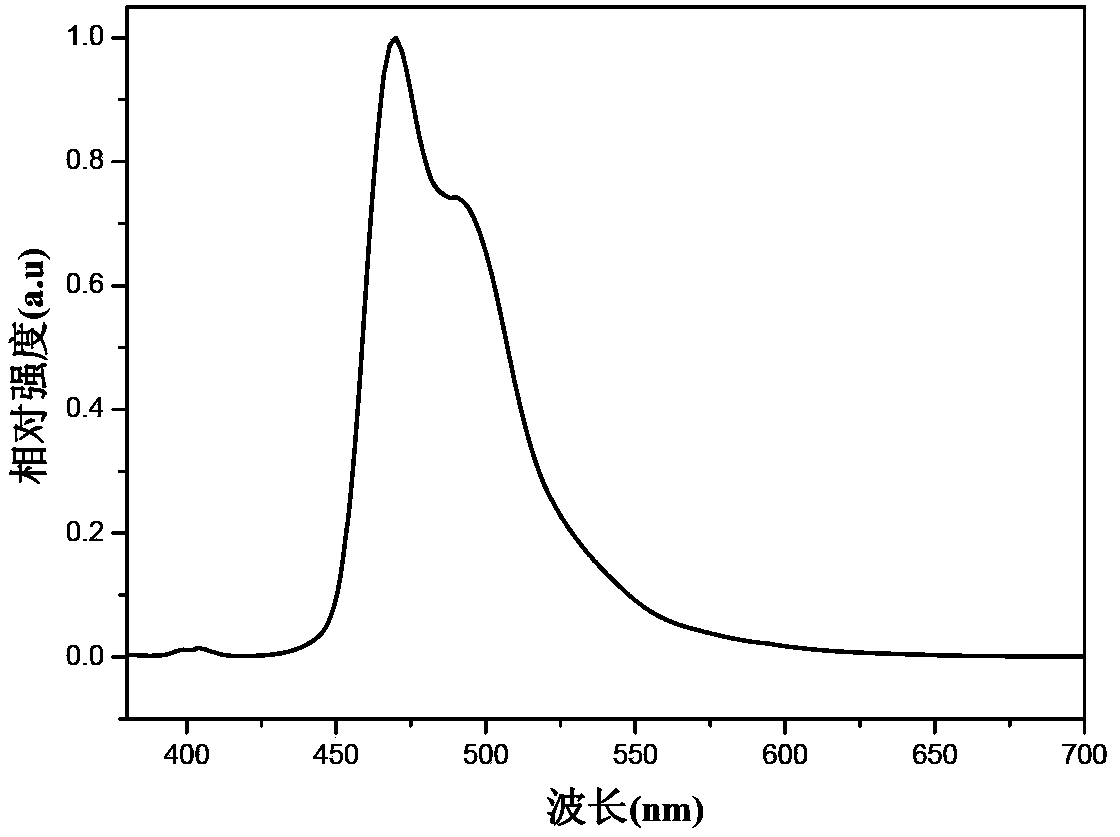

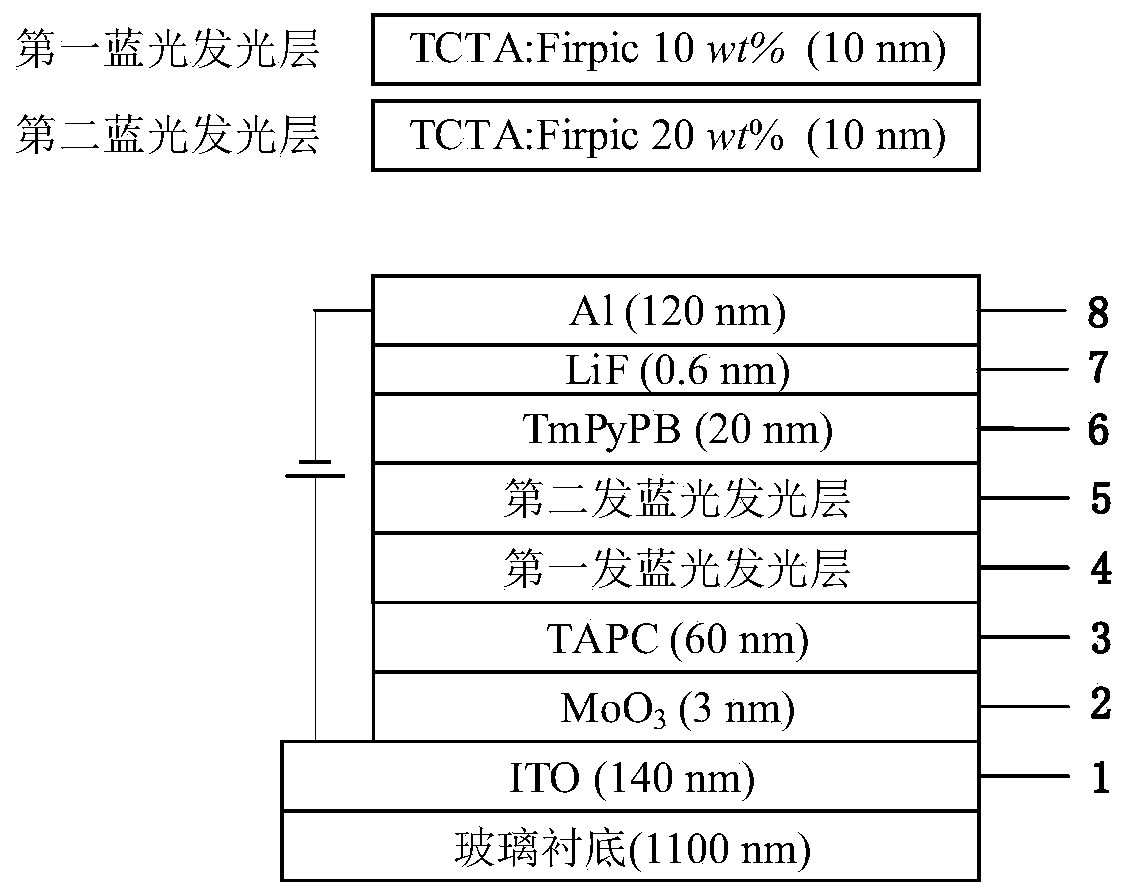

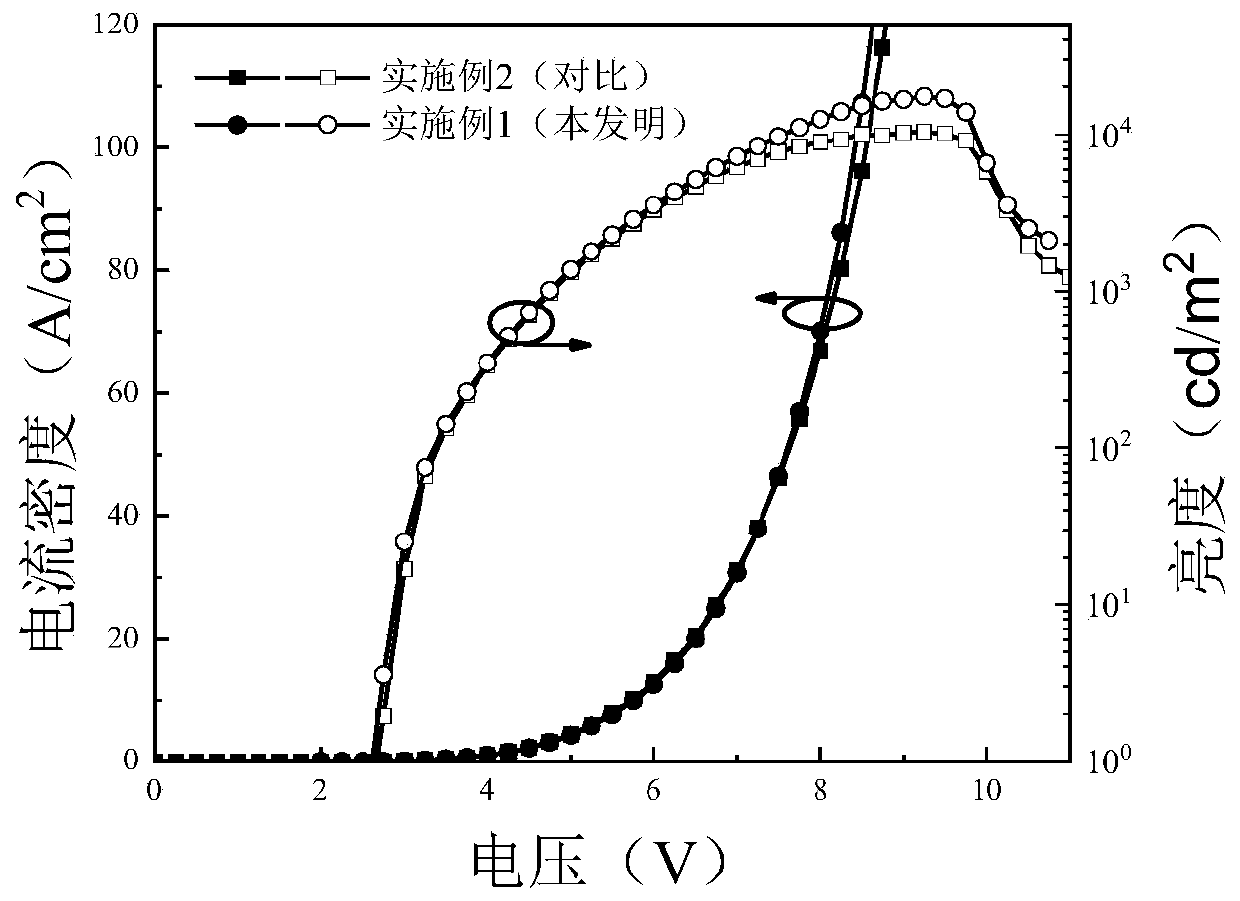

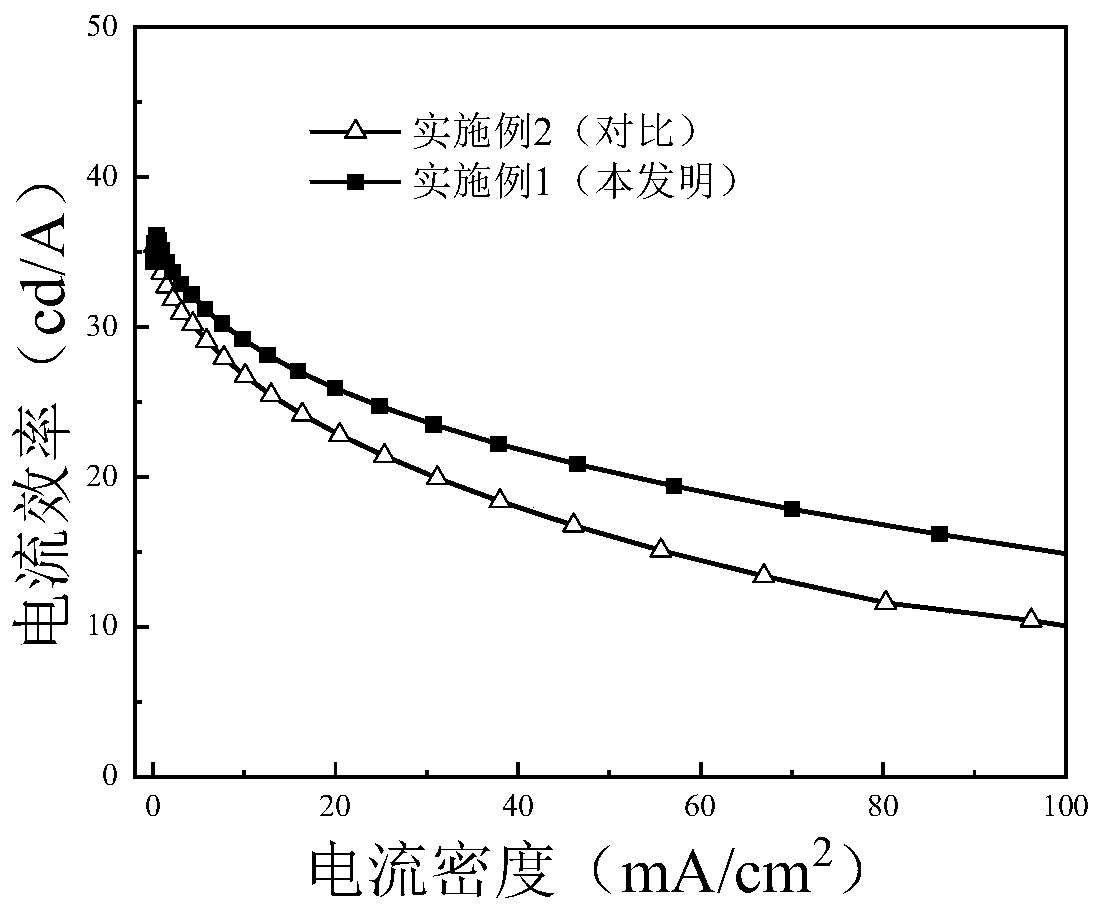

Dual-light emitting layer structure blue-light OLED and manufacturing process thereof

InactiveCN110265560ASimple preparation processLow costSolid-state devicesSemiconductor/solid-state device manufacturingElectronic transmissionHole injection layer

The invention requests and protects a dual-light emitting layer structure blue-light OLED device and a manufacturing process thereof. The device comprises a positive electrode substrate, a hole injection layer, a hole transmission layer, a first light-emitting layer, a second light-emitting layer, an electronic transmission layer, an electronic injection layer and a negative electrode, wherein the first light-emitting layer and the second light-emitting layer employ the same main body materials, same object material and same thickness, and the object doping concentration of the first light-emitting layer is not higher than 50% of the object doping concentration of the second light-emitting layer. The dual-light emitting layer structure provided by the technical scheme is simple, the exciton utilization rate and the composite region can be expanded, and the efficiency roll-off of the device is effectively improved.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

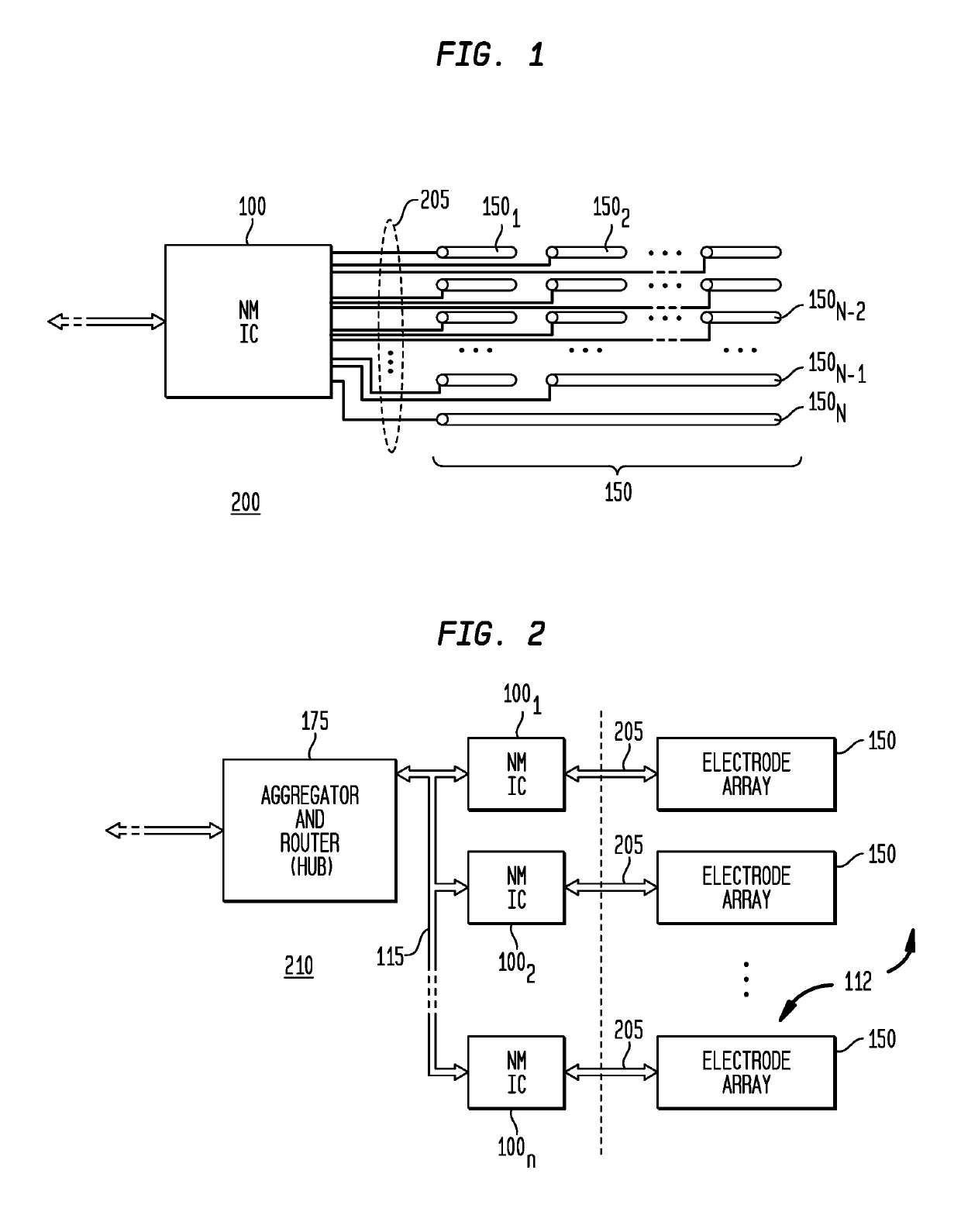

Neuromodulation apparatus, method and system

ActiveUS20190282817A1Minimizing chopper rippleFast recoveryDc network circuit arrangementsElectrotherapyStimulus controlSingle phase

Representative methods, apparatus and systems are disclosed for providing concurrent electrical stimulation and electrical recording in a human or non-human subject, such as for neuromodulation, with the apparatus coupleable to an electrode array. A representative apparatus is typically an integrated circuit including: stimulation circuits, recording circuits, and blocking circuits responsive to control signals to block the stimulation voltage or current on an electrode from a corresponding recording circuit, while other recording circuits may simultaneously record electrical signals from other electrodes and generate recorded data. A representative stimulation circuit may include current sources; a first multiplexer for current source selection; a second multiplexer for electrode selection; a switchable voltage offset circuit; a switchable grounding circuit; and a stimulation controller providing control signals to provide the electrical stimulation, such as biphasic or monophasic stimulation, and bipolor or unipolar stimulation. Off-chip communication, control, along with power and voltage level control, are also provided.

Owner:NIA THERAPEUTICS INC

Super junction device and manufacturing method thereof

ActiveCN109755291AImprove vertical pressure resistanceImprove the ability to withstand voltage verticallySemiconductor/solid-state device manufacturingSemiconductor devicesEpoxyEngineering

The invention discloses a super junction device, grooves of a super junction structure are of a lateral inclined structure, the doping concentration of N-type epitaxial layers are distributed in a stepped mode, and P-type columns are formed of a plurality of layers of P-type epitaxial layers which are filled in the grooves in an overlapped mode; and the doping concentration of the P-type epitaxiallayers of the P-type columns is decreased successively from bottoms to tops of the grooves. A protective epoxy film wraps around the circumferential side of a current flow region; and the N-type epitaxial layer at the interface of the protective epoxy film and the oxide film epitaxial layer of the N-type epitaxial layer of a terminal region internally comprises a top region with the reduced N-type doping concentration, and the top region can enhance the lateral depletion capacity of the N-type column at the interface of the oxide film epitaxial layer. The invention further discloses a manufacturing method of the super junction device. According to the super junction device, the charge balance between the P-type columns and N-type columns of the super junction structure with the inclined grooves can be improved, the longitudinal voltage endurance capability of the device is improved, and the source leakage breakdown voltage of the device is increased; and the lateral voltage bearing capacity of a device terminal can further be improved, and reliability of the device is improved.

Owner:SHENZHEN SANRISE TECH CO LTD

Nano-tube mosfet technology and devices

ActiveUS20160322459A1Simple and convenient processing stepEasy to carrySemiconductor/solid-state device manufacturingSemiconductor devicesMOSFETDielectric layer

This invention discloses a semiconductor power device disposed in a semiconductor substrate and the semiconductor substrate has a plurality of trenches. Each of the trenches is filled with a plurality of epitaxial layers of alternating conductivity types constituting nano tubes functioning as conducting channels stacked as layers extending along a sidewall direction with a “Gap Filler” layer filling a merging-gap between the nano tubes disposed substantially at a center of each of the trenches. The “Gap Filler” layer can be very lightly doped Silicon or grown and deposited dielectric layer. In an exemplary embodiment, the plurality of trenches are separated by pillar columns each having a width approximately half to one-third of a width of the trenches.

Owner:ALPHA & OMEGA SEMICON INC

Method for opportunistically balancing charge between battery cells

ActiveUS9450426B2Accurately determineAccurate balanceCharge equalisation circuitSecondary cells charging/dischargingImage resolutionEngineering

Systems and methods for balancing battery cells of a battery pack are disclosed. In one example, a charge imbalance is determined while battery cells operate in a high charge resolution voltage range. The charge imbalance determined during operation in the high charge resolution voltage range may be removed when the battery cells are operated in a low charge resolution voltage range. The system and method may be particularly useful for balancing battery cells that operate in the low charge resolution voltage range for a large portion of their operating time.

Owner:A123 SYSTEMS LLC

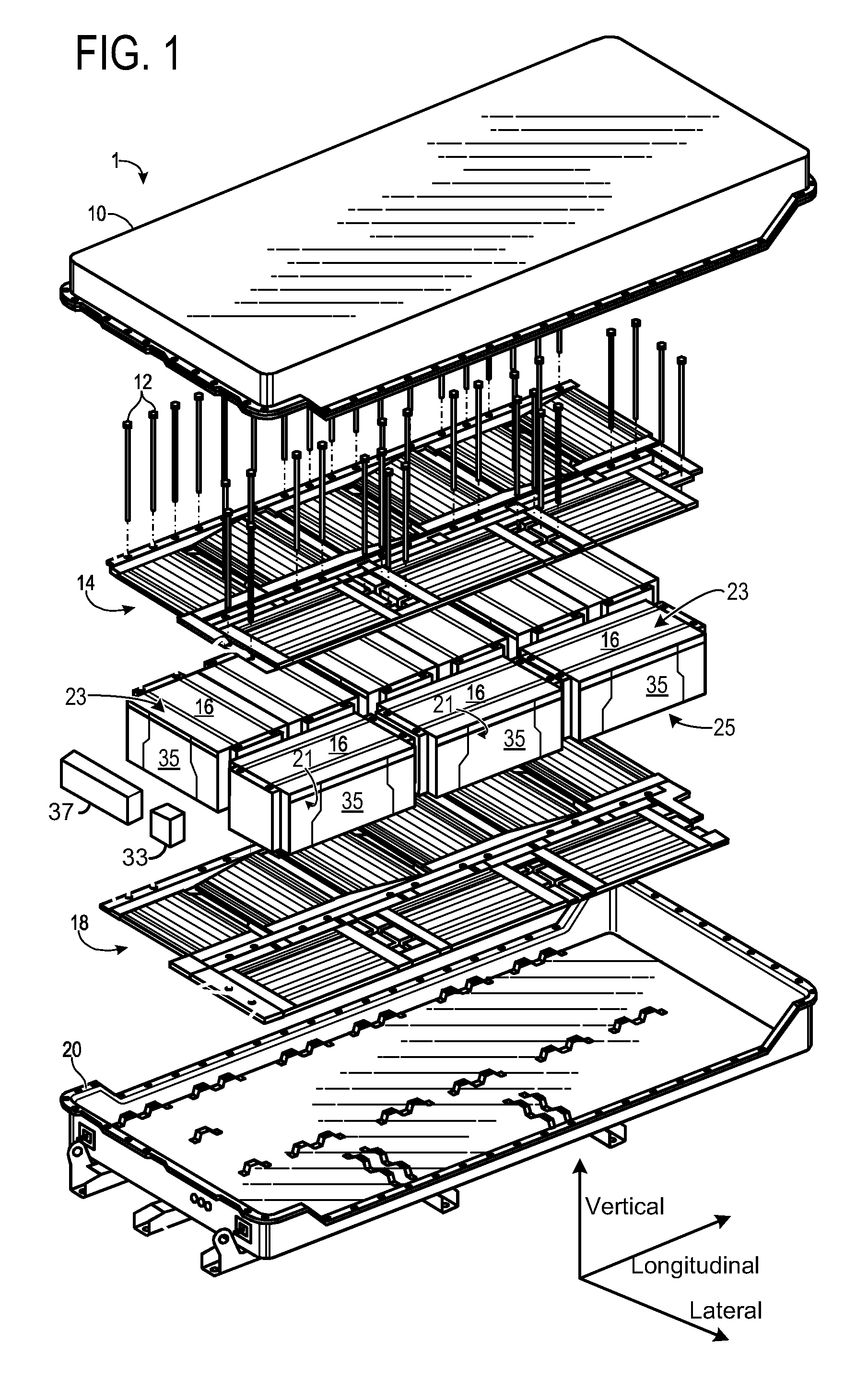

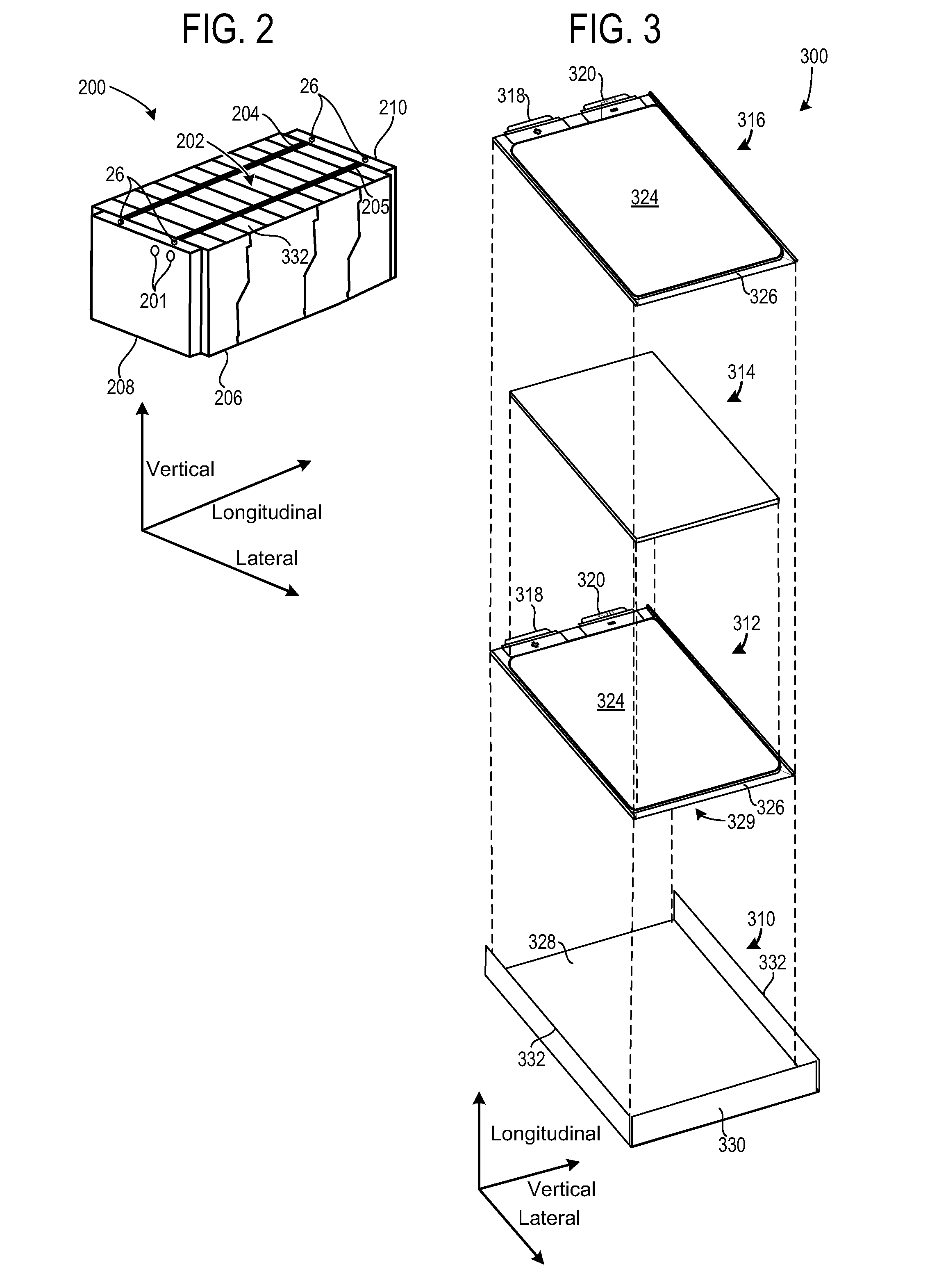

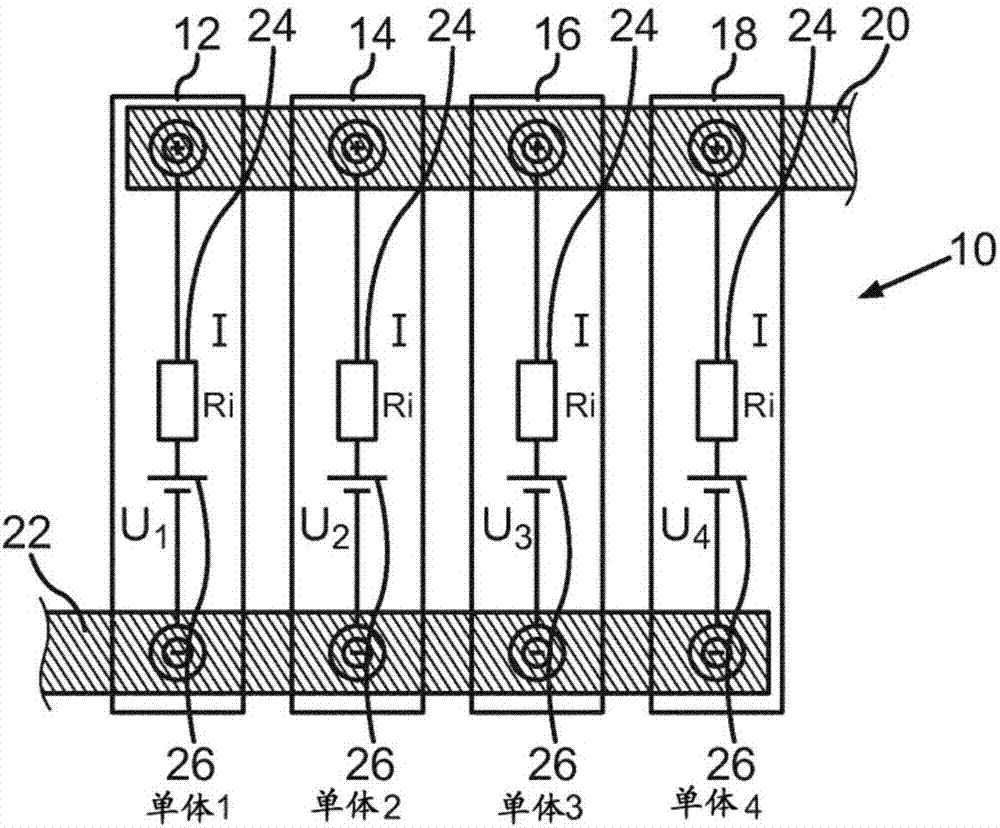

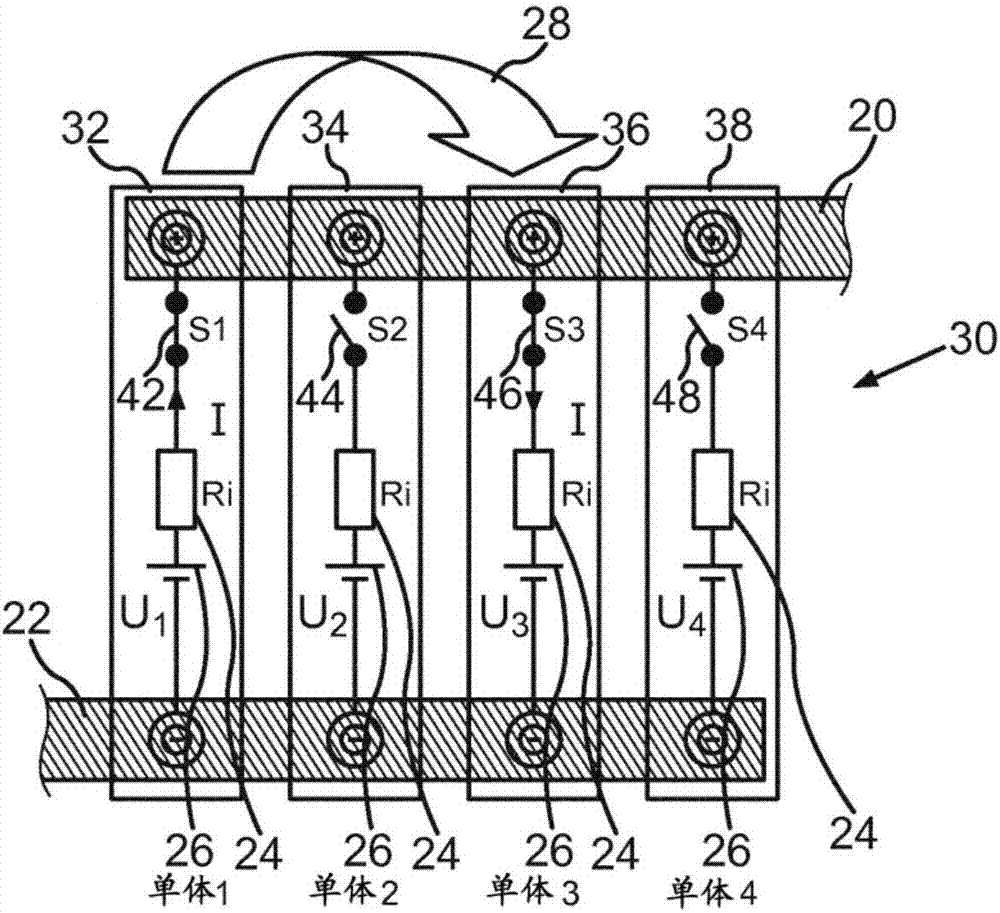

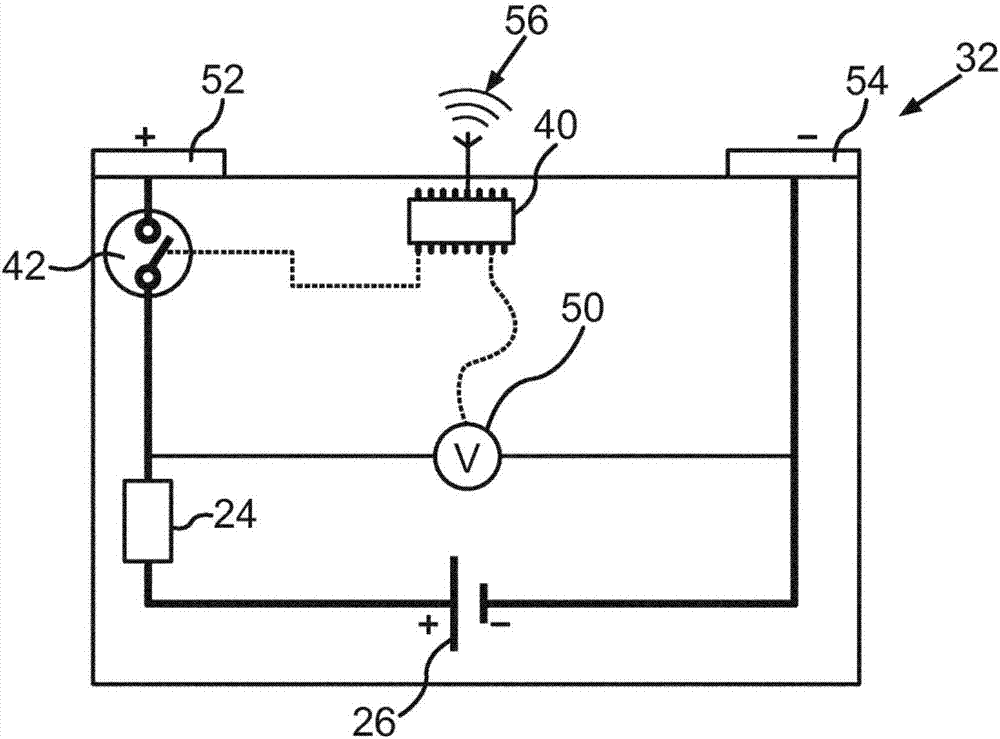

Adjustment of states of charge of battery cells

ActiveCN107258033AOptimize energy distributionImprove charge balanceParallel/serial switchingSecondary cells charging/dischargingState of chargeEngineering

The invention relates to a method for adjusting states of charge of battery cells which are electrically operated in a manner connected in parallel, having the following steps of: - determining the states of charge of the battery cells, - selecting those battery cells whose states of charge are intended to be adjusted according to a predefinable selection rule, - activating those battery cells which are adjusted using a semiconductor switch of the battery cells in each case, and deactivating the remaining battery cells using the semiconductor switches of the respective remaining battery cells, - adjusting the states of charge and monitoring the states of charge, and - ending the adjustment of the states of charge if a predefined state of charge is reached by the activated battery cells.

Owner:AUDI AG