Super junction device and manufacturing method thereof

A superjunction device, N-type technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of poor device EAS capability, poor BVds consistency, and insufficient BVds effect.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example approach

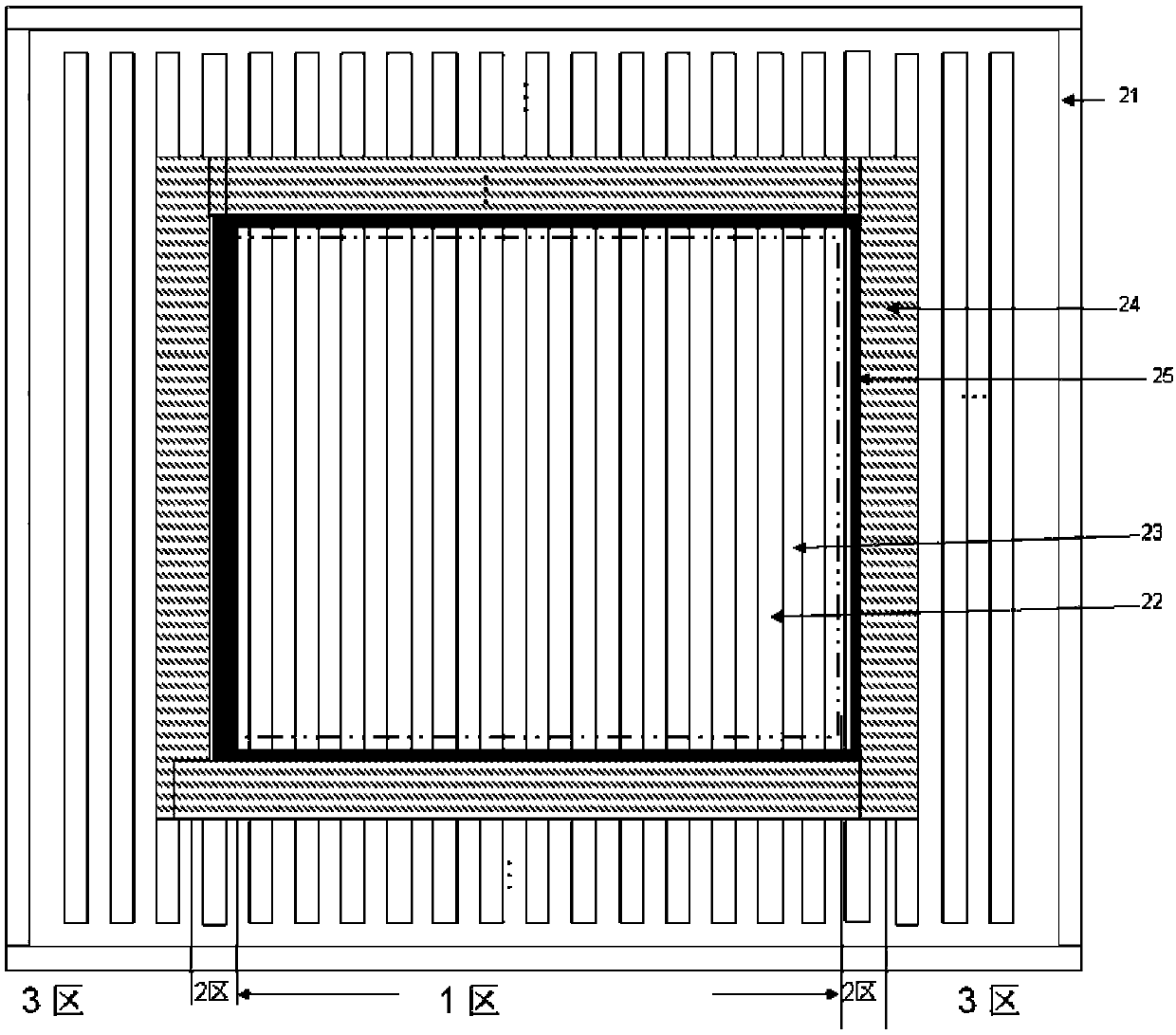

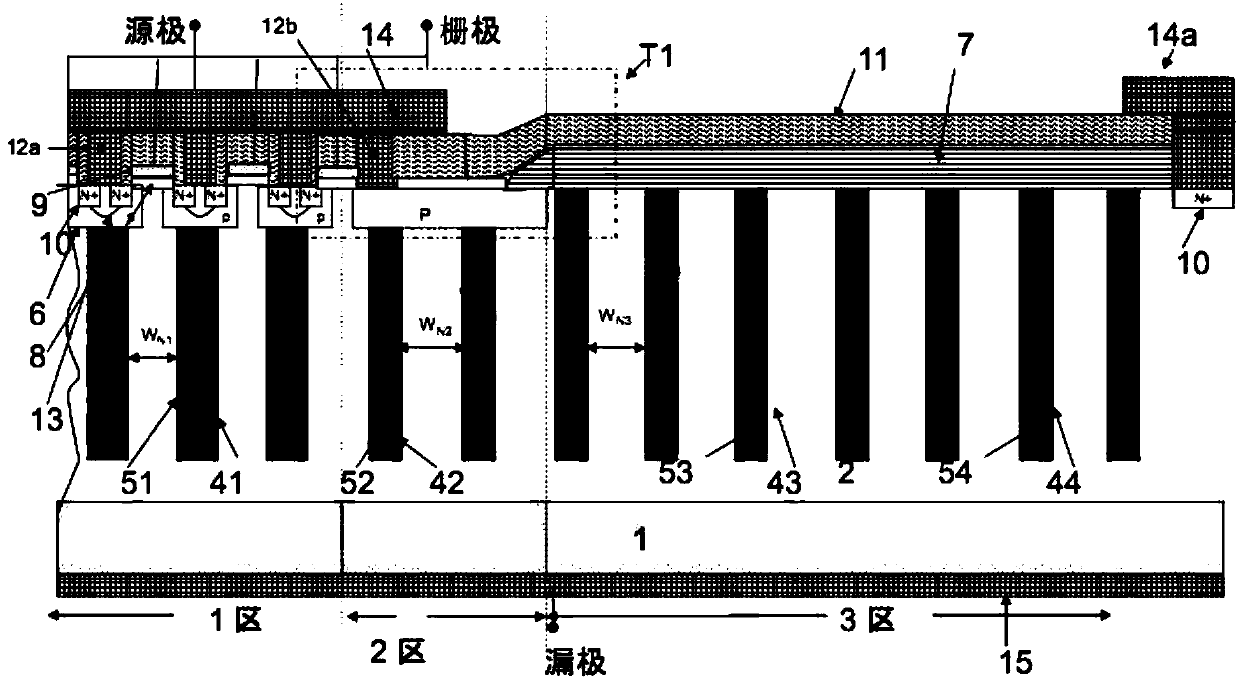

[0143] The manufacturing method of the super junction device according to the first embodiment of the present invention is to manufacture such as image 3 The superjunction device of the embodiment of the present invention is shown as an example for description, as Figure 5A to Figure 5H Shown is a schematic cross-sectional view of the device in each step of the manufacturing method of the super-junction device in the first embodiment of the present invention; in the manufacturing method of the super-junction device in the first embodiment of the present invention, the middle region of the super-junction device is the current flow region, that is, 1 zone, the terminal zone, that is, zone 3, surrounds the periphery of the current flow region, and the transition zone, that is, zone 2, is located between the current flow zone and the terminal zone; the structure of the top view of the super junction device can also refer to figure 1 shown. The method of the first embodiment of ...

no. 1 example

[0163] A P-type well 6 is formed on the top of each P-type column 51 in the current flow region, and each P-type well 6 extends to the N-type well 6 on both sides of the corresponding P-type column 51. surface of the column. In the method of the first embodiment of the present invention, one P-type well 6 is formed in the second region, and the P-type well 6 covers the two P-type pillars 52.

[0164] After the P-type ion implantation of the P-type well 6 is completed, it also includes performing an annealing process on the P-type well 6. The temperature of the annealing process is above 1000°C and the time is above 30 minutes.

[0165] In the method of the first embodiment of the present invention, the process conditions of the P-type well 6 need to meet the requirements of the threshold voltage of the device. For devices with a threshold voltage requirement of 2 volts to 4 volts, B 30-100KEV, 3-10 E13 can be used / cm2 process conditions, that is, the implanted impurity is bo...

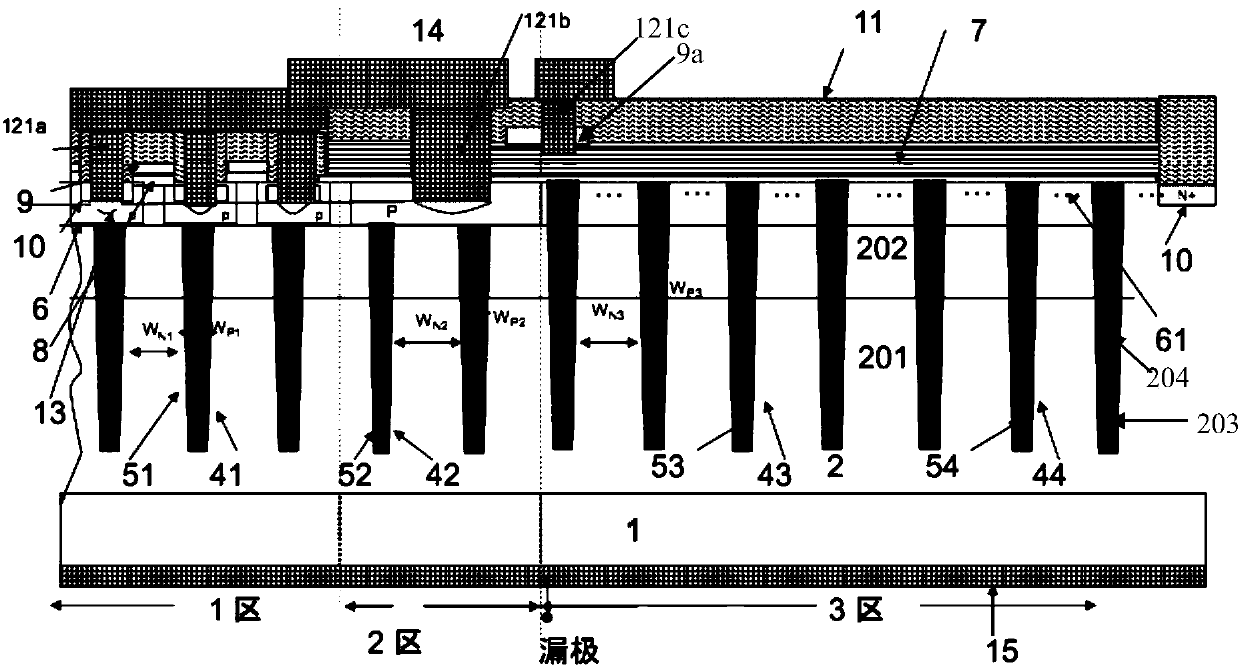

no. 2 example

[0214] A P-type well 6 is formed on the top of each P-type column 51 in the current flow region, and each P-type well 6 extends to the N-type well 6 on both sides of the corresponding P-type column 51. surface of the column. In the method of the second embodiment of the present invention, one P-type well 6 is formed in the second region, and the P-type well 6 covers the two P-type pillars 52.

[0215] After the P-type ion implantation of the P-type well 6 is completed, it also includes performing an annealing process on the P-type well 6. The temperature of the annealing process is above 1000°C and the time is above 30 minutes.

[0216] In the method of the second embodiment of the present invention, the process conditions of the P-type well 6 need to meet the requirements of the threshold voltage of the device. For devices with a threshold voltage requirement of 2 volts to 4 volts, B 30-100KEV, 3-10E13 / cm2 process conditions, that is, the implanted impurity is boron (B), th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More