Patents

Literature

121results about How to "Solve leakage current" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

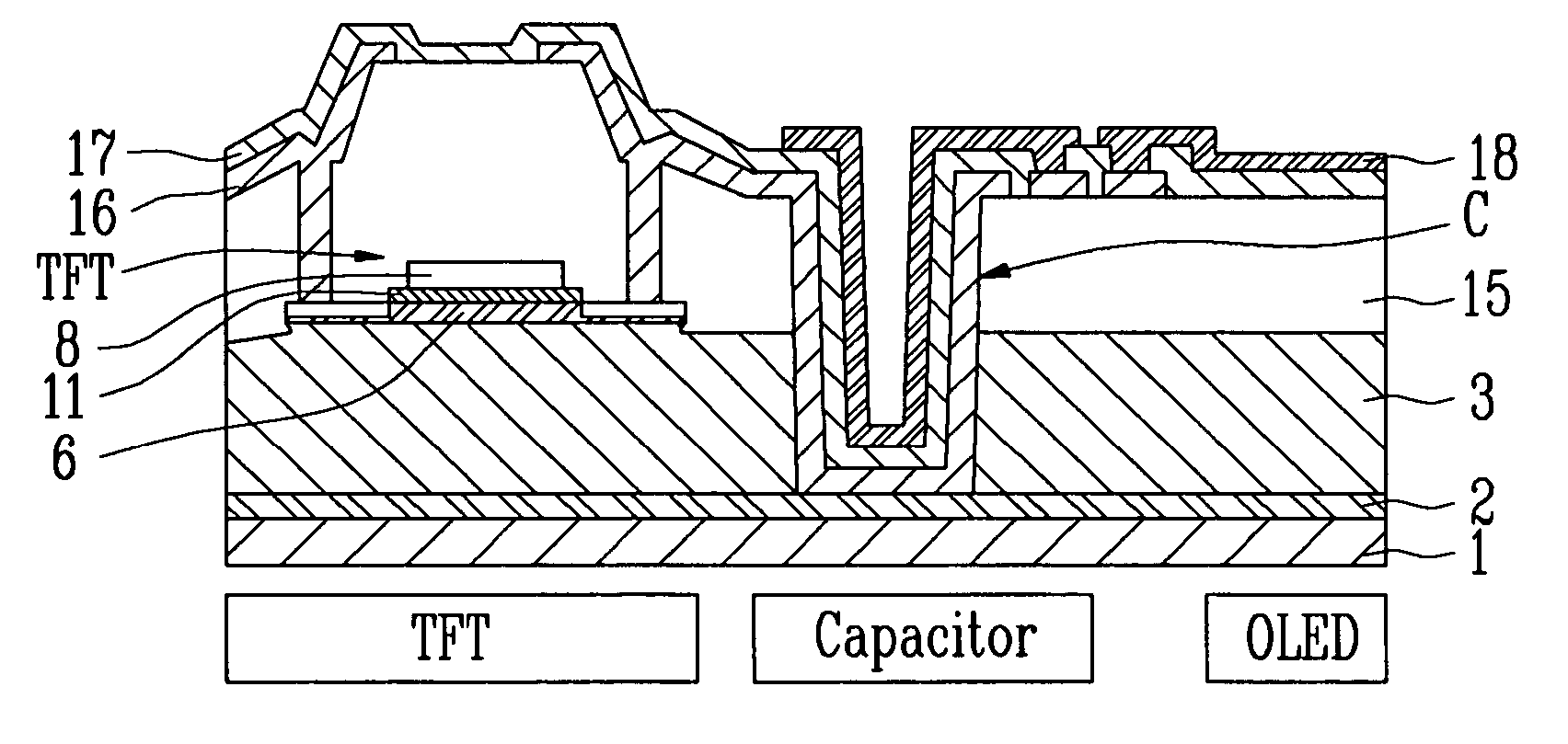

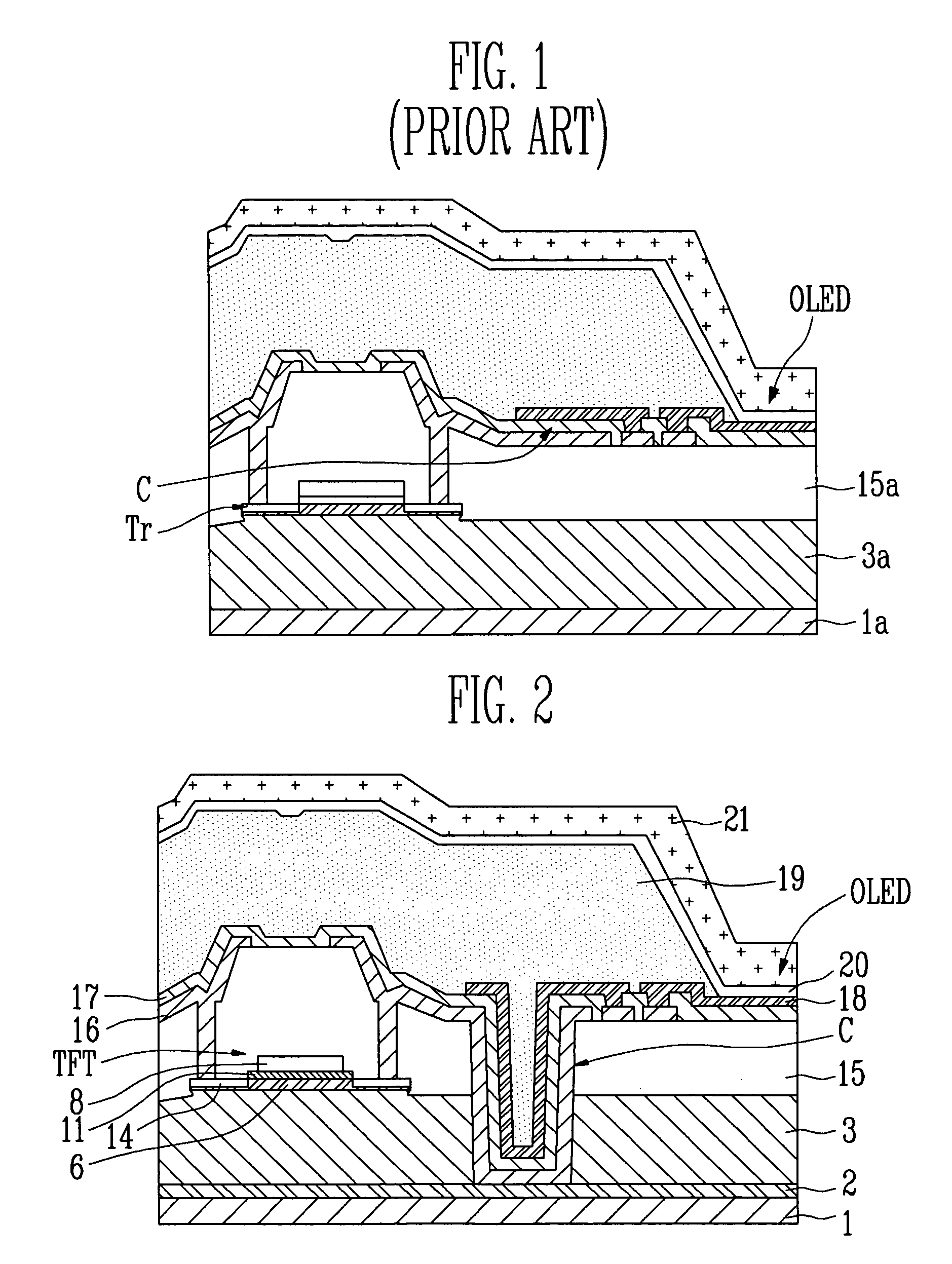

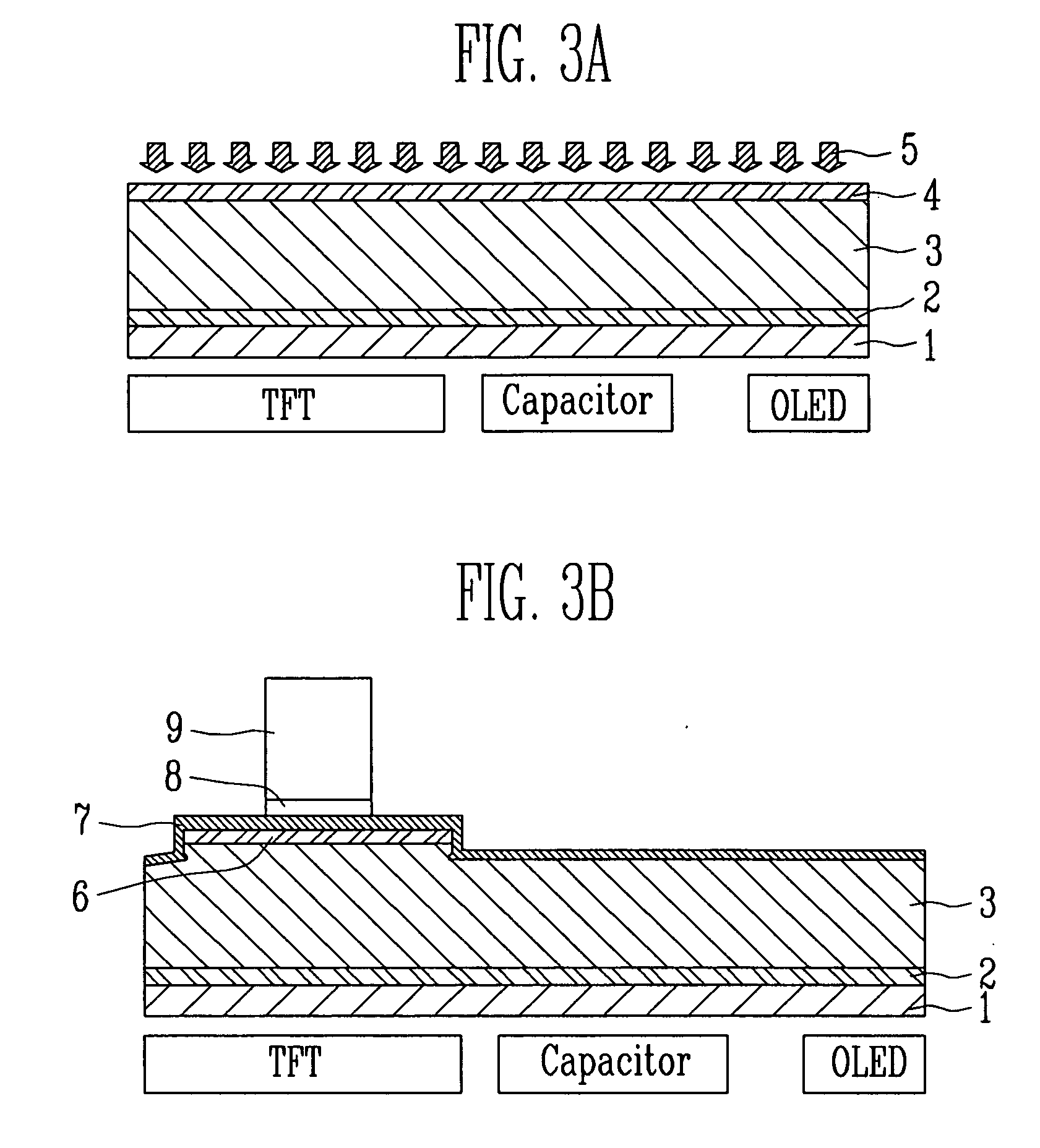

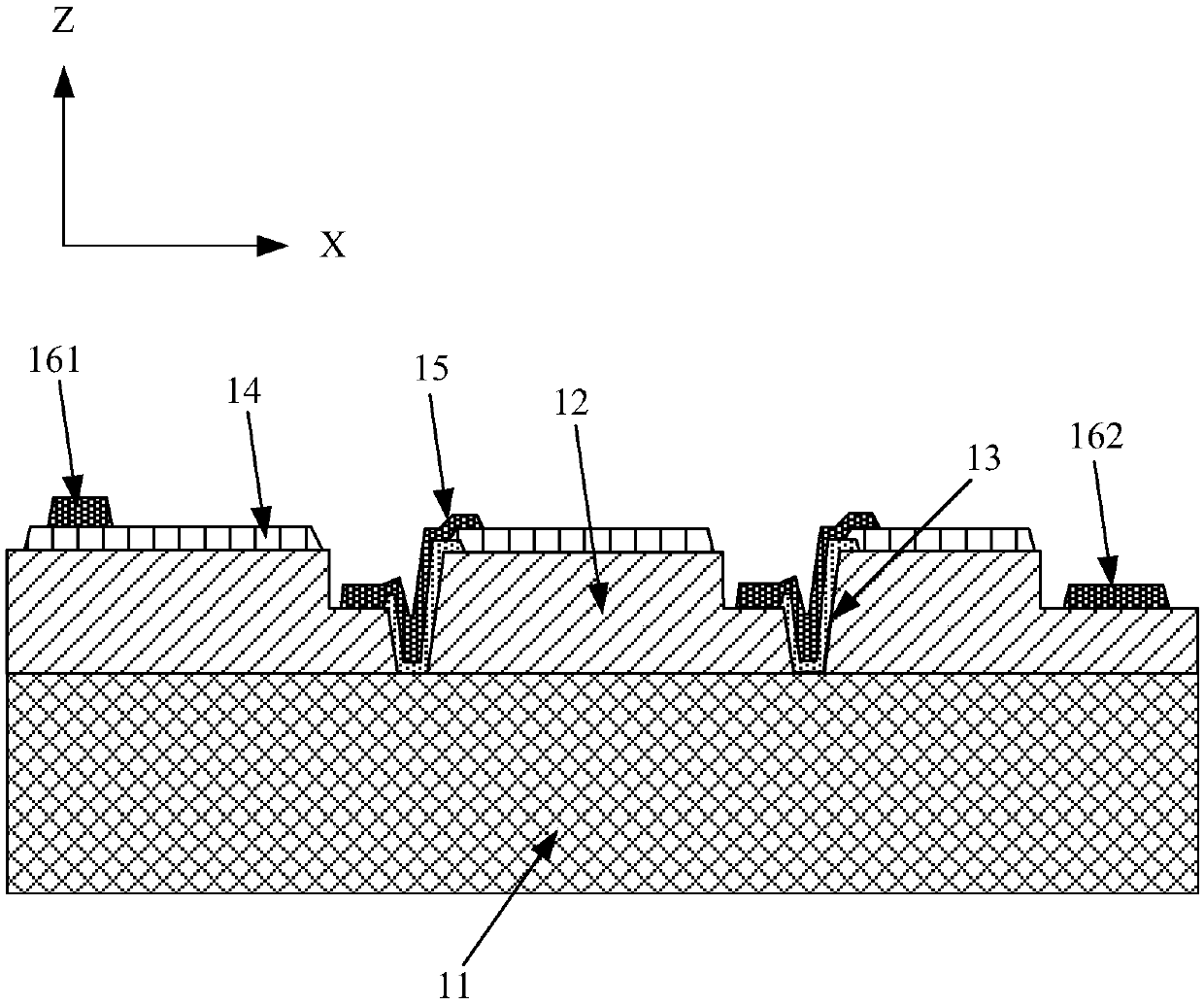

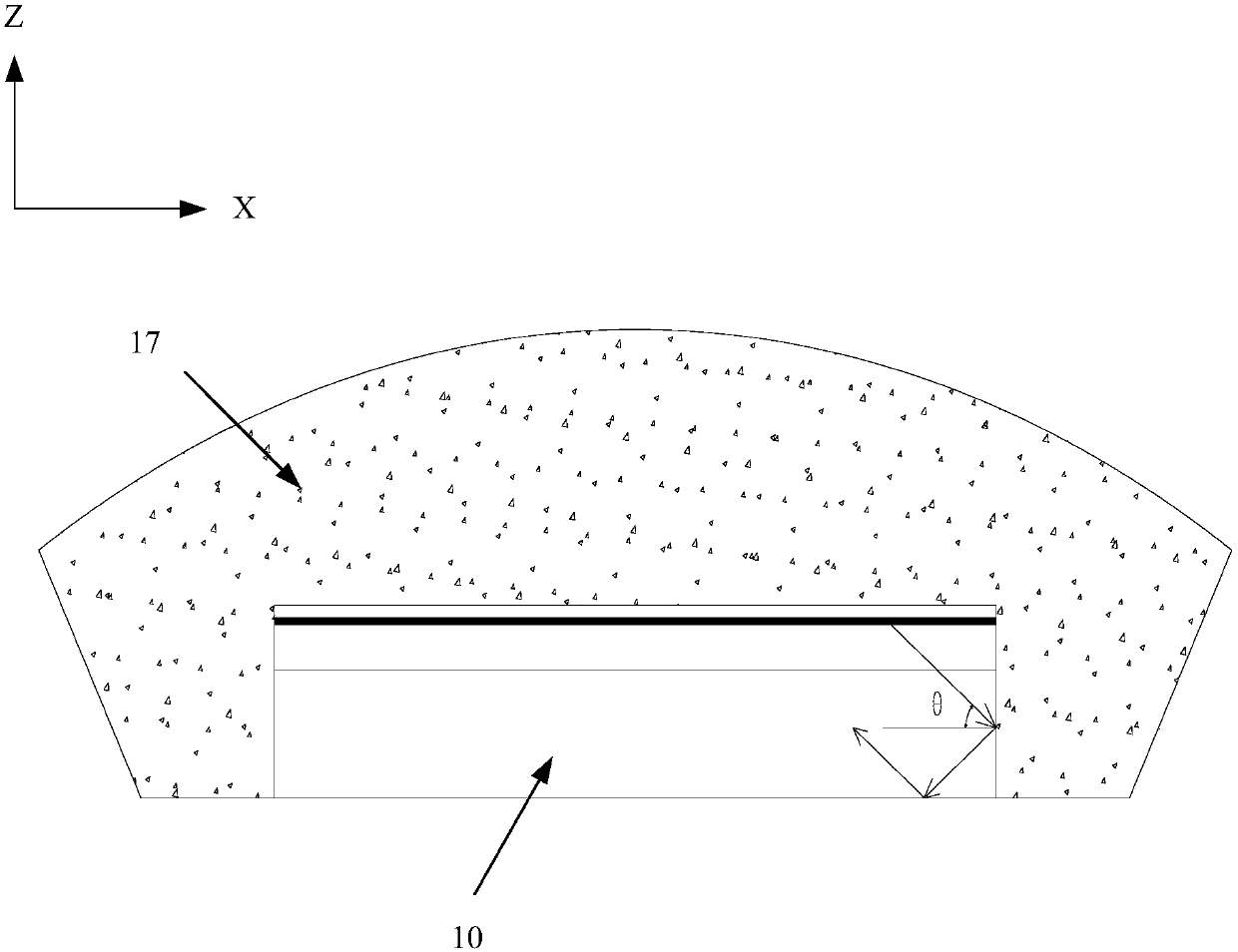

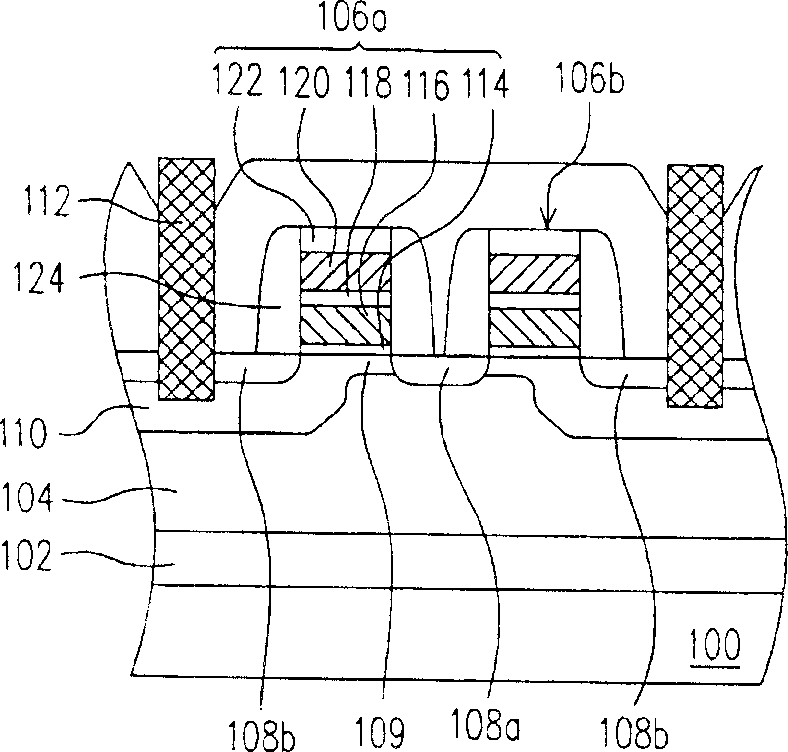

Low temperature active matrix display device and method of fabricating the same

InactiveUS20060138922A1Reduce aperture ratioIncrease capacitor areaElectric discharge tubesElectroluminescent light sourcesResistActive matrix

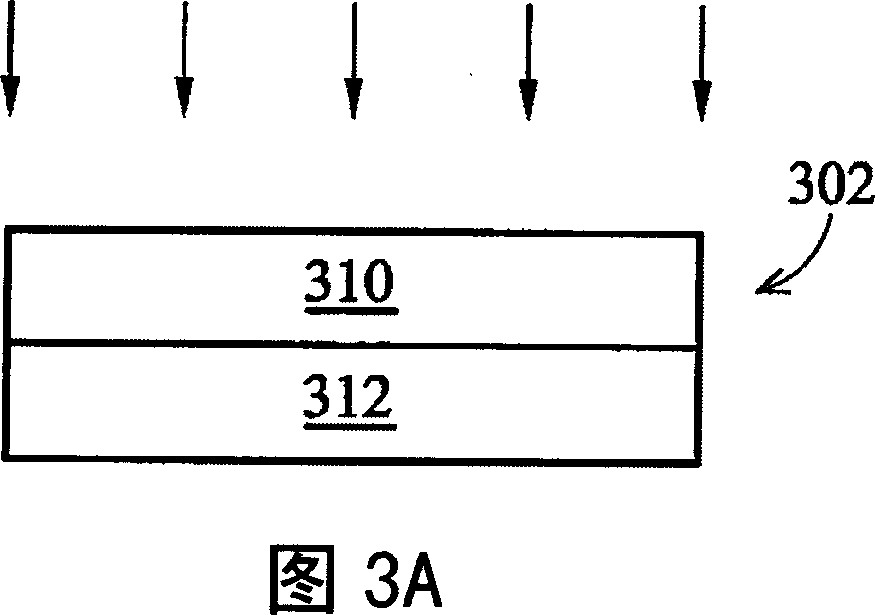

Provided are a low temperature active matrix display device using a plastic substrate and method of fabricating the same. The low temperature active matrix display device includes: a plastic substrate; a reflection layer disposed on the plastic substrate; a buffer layer disposed on the reflection layer; a thin film transistor disposed on the buffer layer in a first region of the plastic substrate; an interlayer dielectric layer disposed on the thin film transistor; a capacitor disposed in a trench formed in a second region of the plastic substrate and having a first electrode connected to a source electrode and a drain electrode of the thin film transistor, the trench extending from the interlayer dielectric layer to the reflection layer; and a display device having one electrode connected to a second electrode of the capacitor. The above-described structure includes photoresist spacers to decrease a leakage current from the TFT, includes a reflector to protect the plastic substrate from deformation due to laser irradiation, and employs a three-dimensional capacitor to increase an aperture ratio.

Owner:ELECTRONICS & TELECOMM RES INST

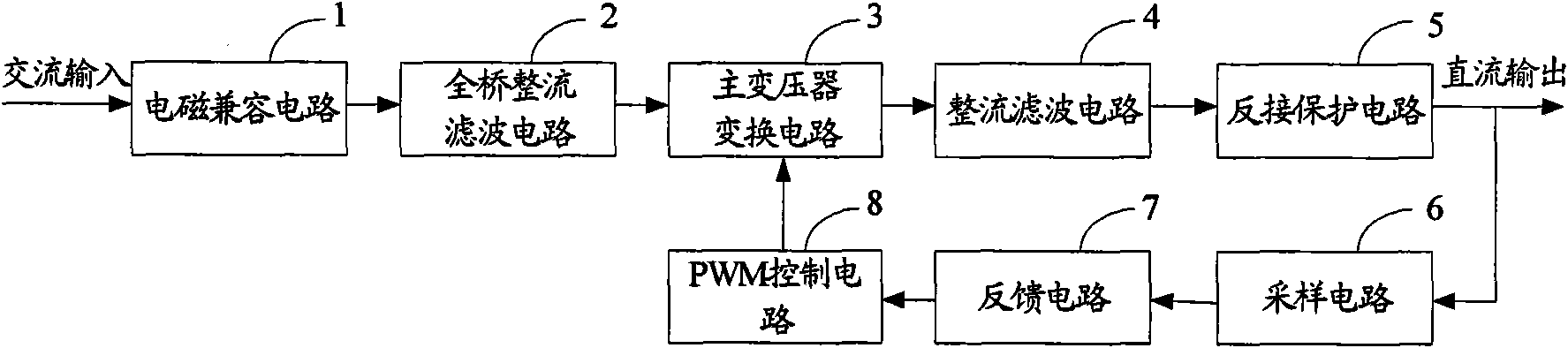

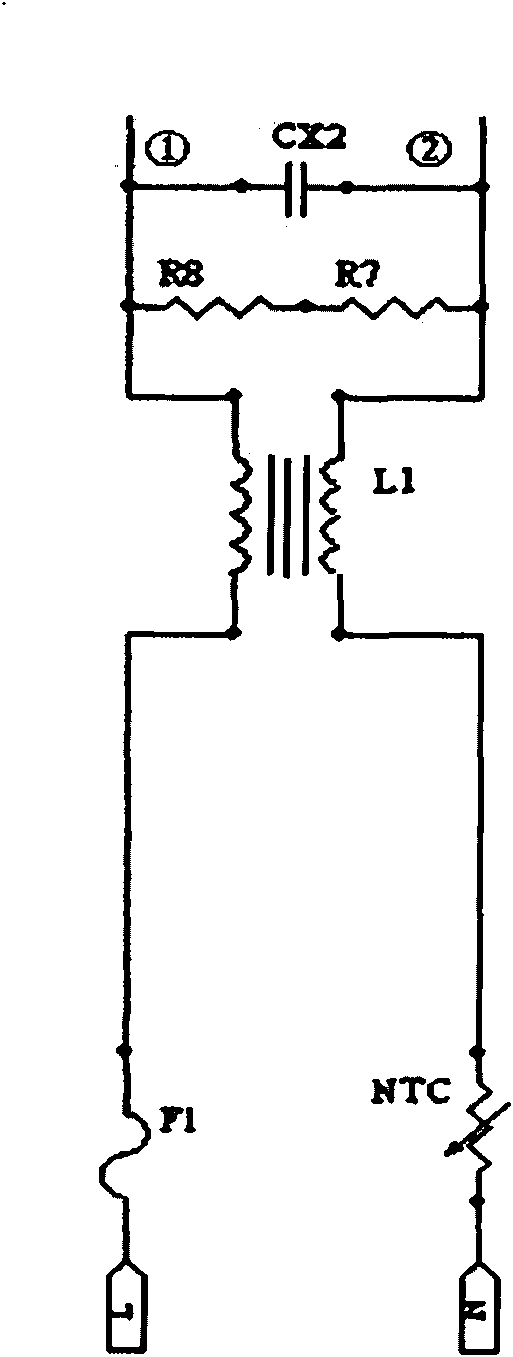

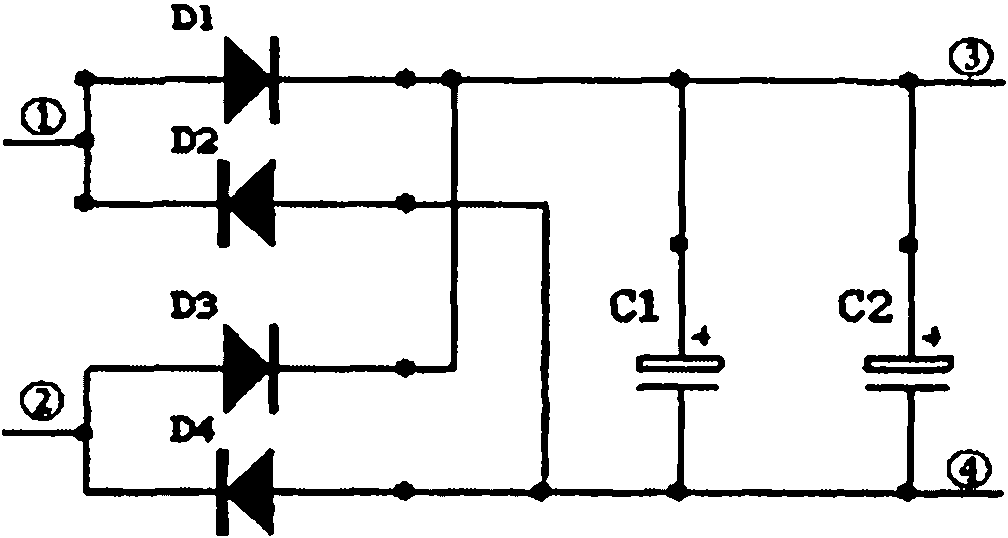

Charging circuit and charger

InactiveCN101867214ASolve leakage currentAddress serious damageBatteries circuit arrangementsEmergency protective circuit arrangementsControl signalFull bridge

The invention, which is applicable to the field of circuits, provides a charging circuit and a charger. The circuit comprises an electromagnetic compatibility circuit, a full-bridge rectifier and filter circuit, a main transformer transformation circuit, a rectifier and filter circuit, a reverse connection protection circuit, a sampling circuit, a feedback circuit and a PWM control circuit; the electromagnetic compatibility circuit is used for carrying out the high-frequency filtering of alternating-current input; the full-bridge rectifier and filter circuit is used for rectifying alternatingcurrent into pulsating direct current; the main transformer transformation circuit is used for storing and releasing electric energy according to PWM control signals; the rectifier and filter circuitis used for rectifying, filtering and outputting current; the reverse connection protection circuit is used for receiving regulated current and shutting off the charging circuit when the poles of a battery are reversely connected; the sampling circuit is used for acquiring voltage signal output; the feedback circuit is used for comparing the voltage signal with the reference voltage and then outputting a feedback signal; and the PWM control circuit is used for receiving the feedback signal and outputting a PWM control signal. By shutting off the charging circuit when the poles of the battery are reversely connected, the invention prevents the damage of the charger and the battery when the chargeable battery is reversely connected.

Owner:SHENZHEN RUIBIDA TECH

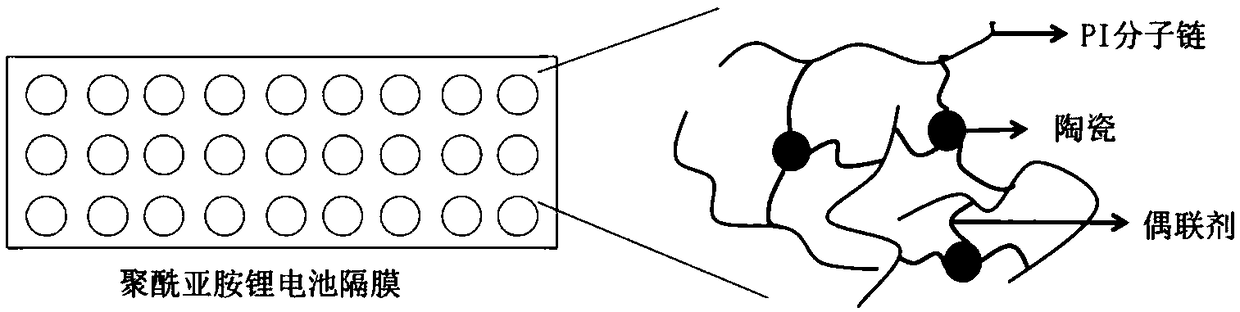

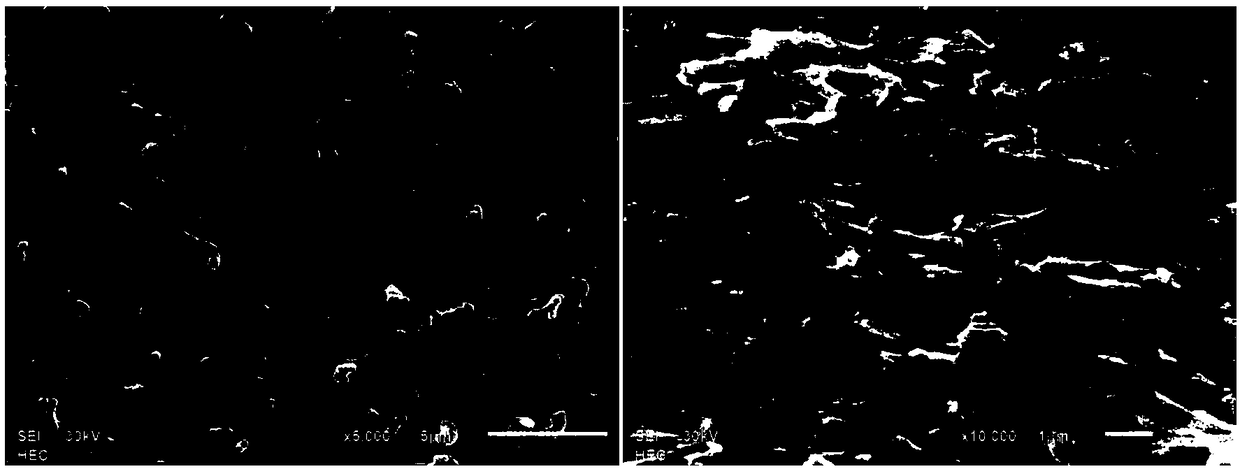

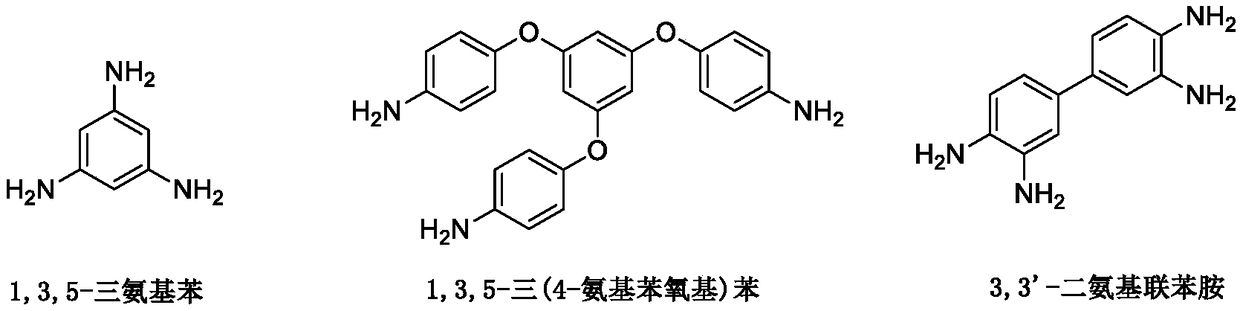

A polyimide lithium battery diaphragm, a preparation method thereof, and a lithium battery comprising the diaphragm

InactiveCN109119572AHigh mechanical strengthImprove puncture strengthCell component detailsCross-linkCoupling

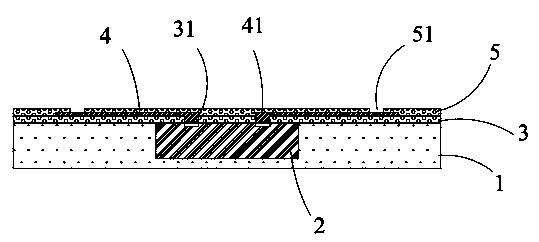

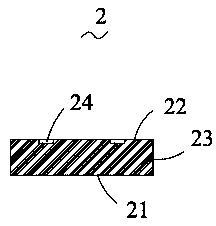

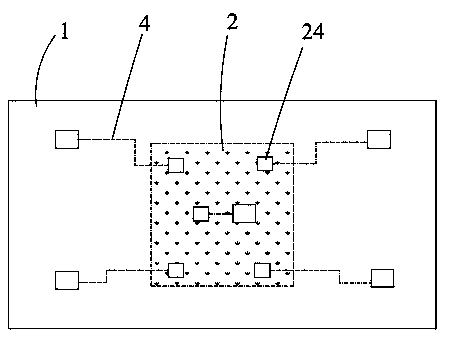

The present application relates to the field of lithium ion battery materials. Disclosed are a polyimide lithium battery diaphragm, a preparation method thereof, and a lithium battery comprising the diaphragm. The polyimide lithium battery diaphragm comprises: 30-50 parts of diorganic amine, 30-50 parts of dibasic organic anhydride, 2-5 parts of a polyamino crosslinking agent and 5-20 parts of polyimide formed by reaction of amino coupling agent surface modified ceramic powder and imidization. The polyimide diaphragm can form cross-linking between polymer molecular chains in the subsequent imidization process by adding polyamino crosslinking, which greatly enhances the mechanical strength; by ceramic powder added with the surface-modified coupling agent, the puncture strength of polyimidediaphragm can be greatly improved, and the pore size of diaphragm can be ensured to be small, the distribution is uniform, and the leakage current problem of a battery can be solved. At the same time,the polyimide lithium battery diaphragm has high production efficiency and is favorable for industrial large-scale production.

Owner:RUYUAN DONGYANG LIGHT FLUORINE RESIN CO LTD

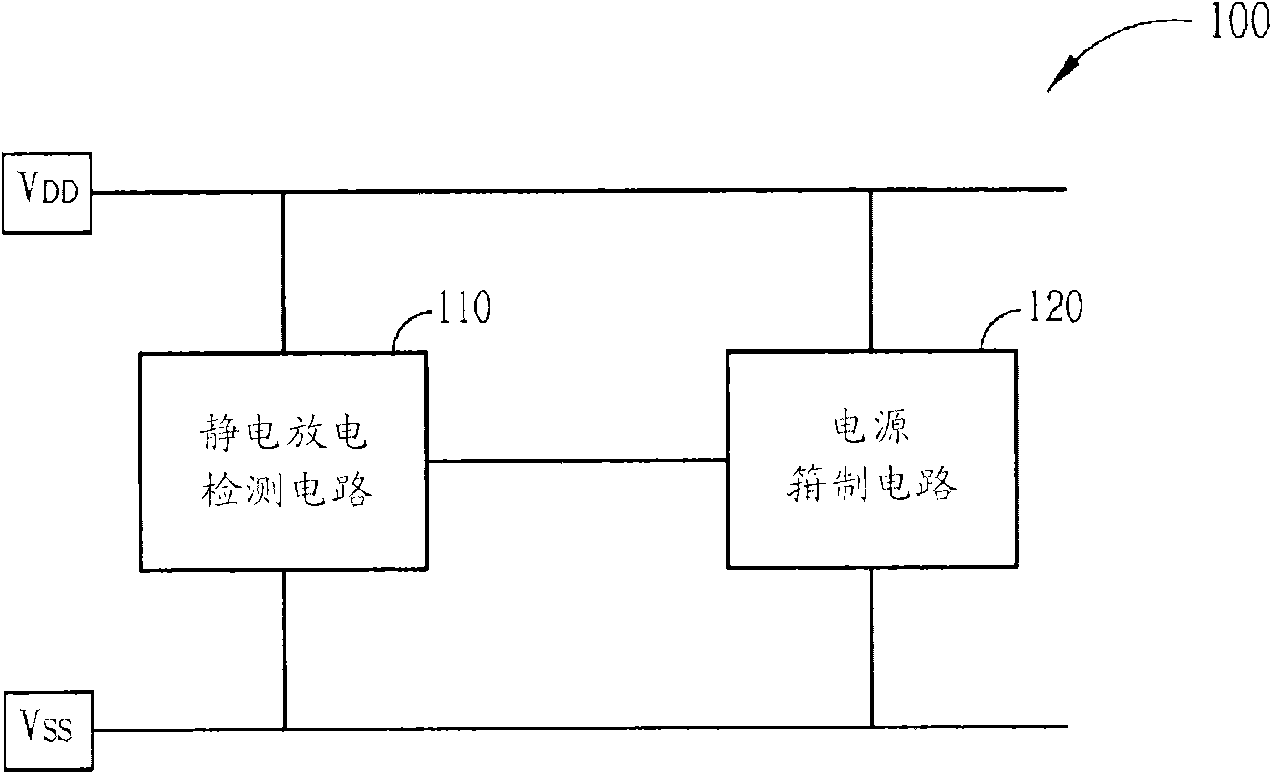

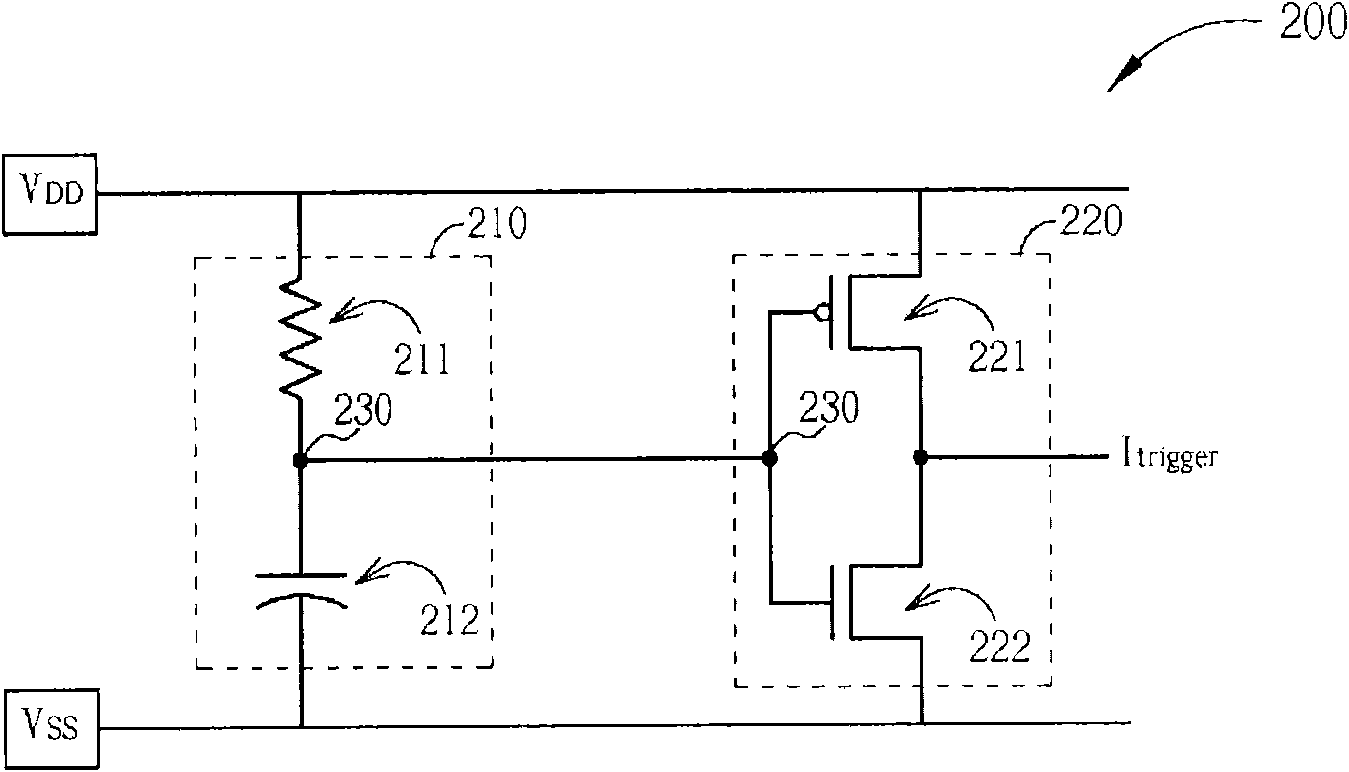

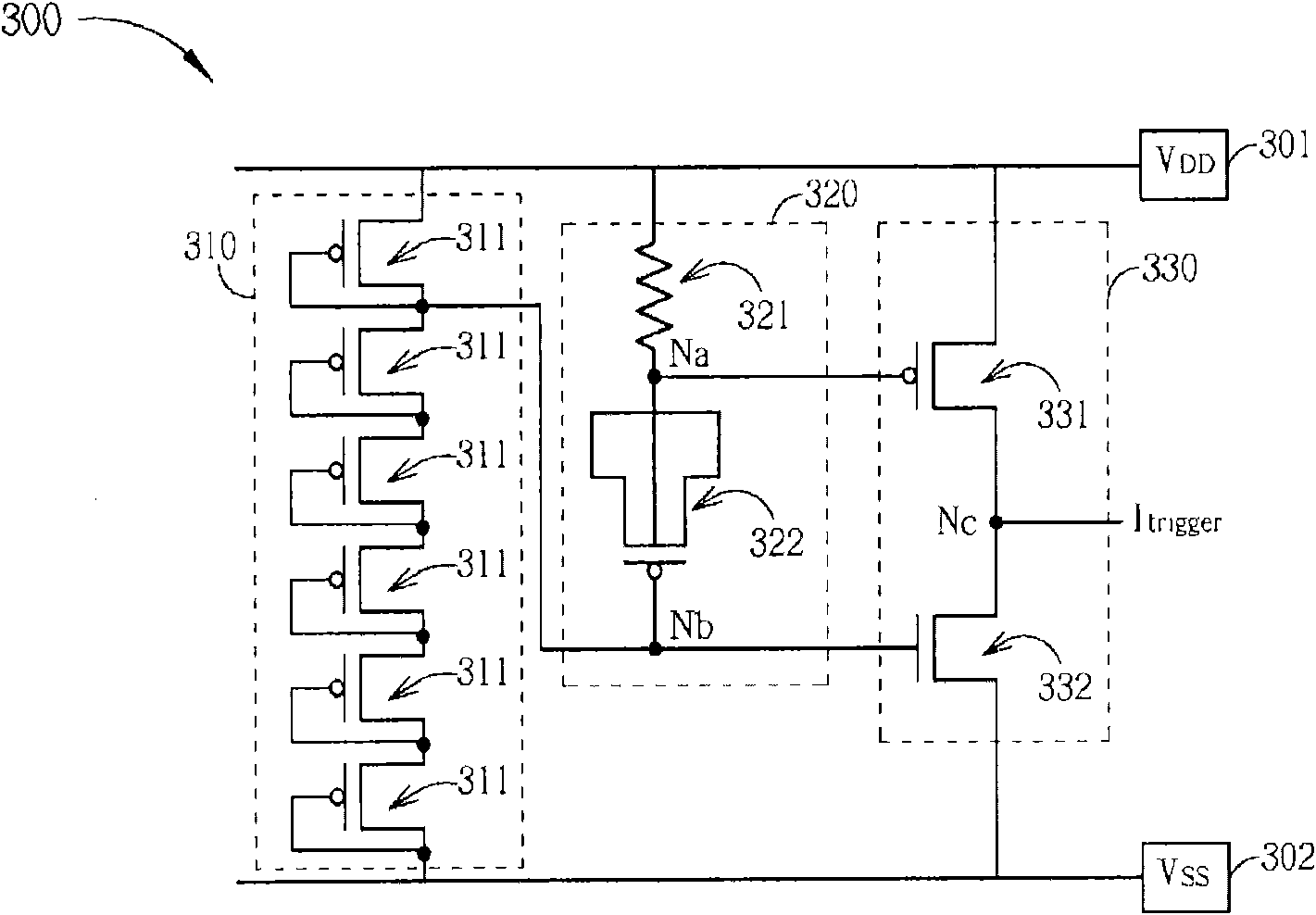

Electrostatic discharge testing circuit and correlated method thereof

The invention relates to an electrostatic discharge testing circuit and a correlated method thereof. The electrostatic discharge testing circuit comprises a first power source bonding pad, a second power source bonding pad, an RC circuit, a trigger circuit and a bias circuit, wherein the RC circuit comprises a resistor element and a capacitor element; the first power source bonding pad receives a first supply voltage; the second power source bonding pad is used for receiving a second supply voltage different from the first supply voltage; the resistor element is coupled between the first power source bonding pad and a first terminal, and the capacitor element is coupled between the first terminal and a second terminal; the trigger circuit is used for generating an electrostatic discharge triggering signal according to a voltage level between the first terminal and the second terminal; and the bias circuit is used for supplying a bias voltage to the second terminal.

Owner:FARADAY TECH CORP

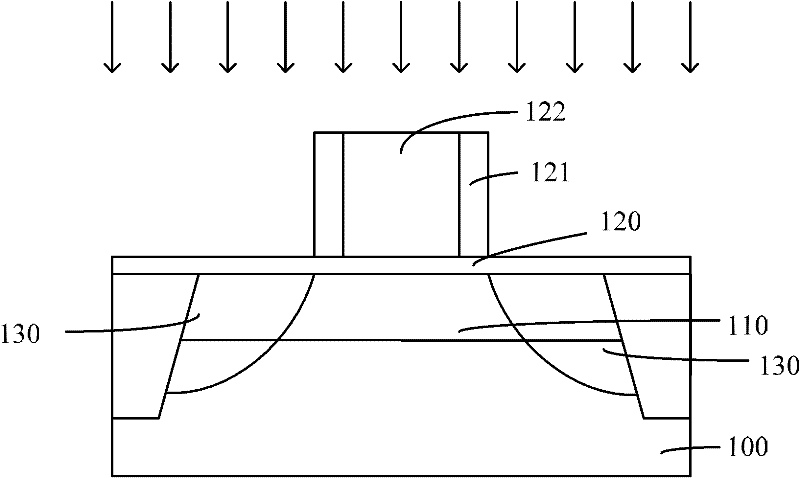

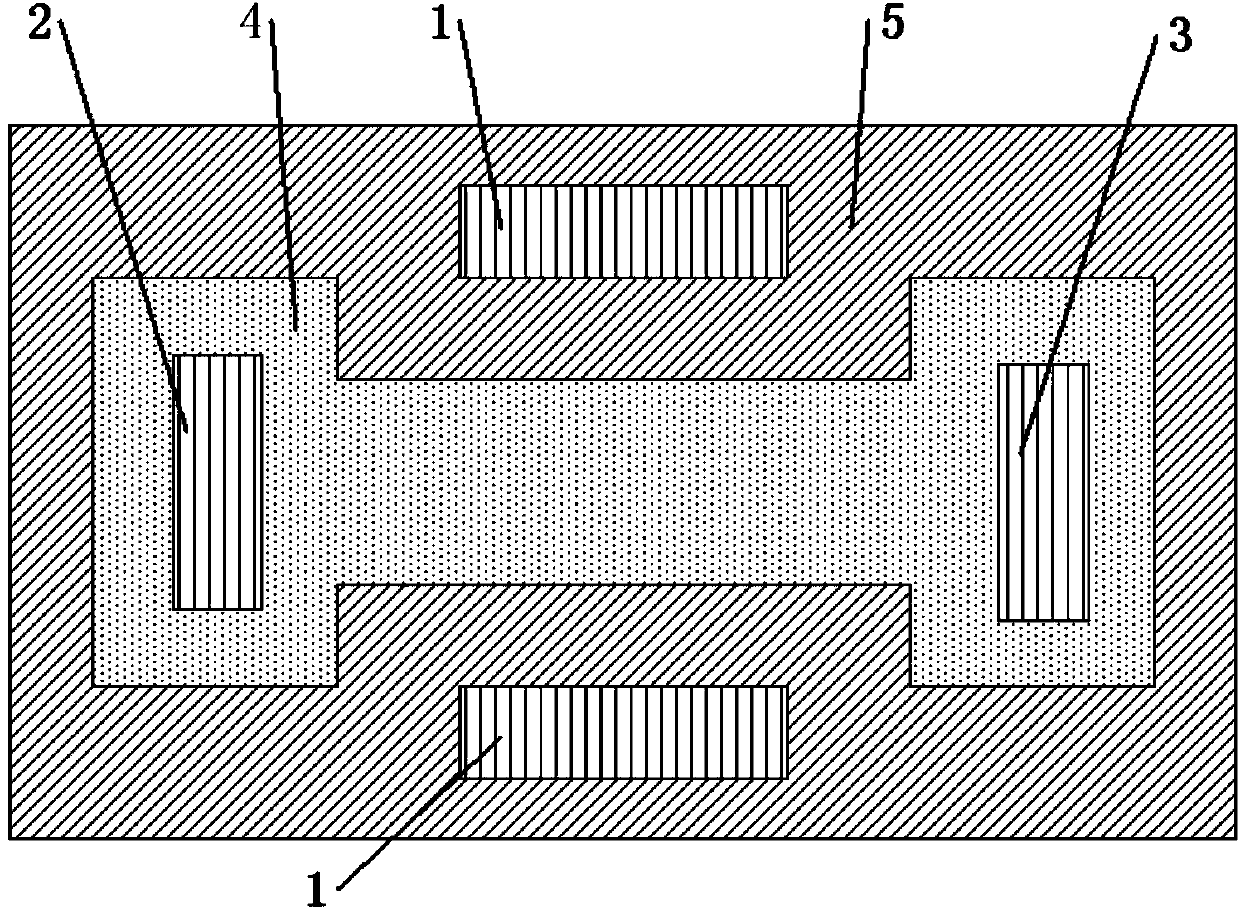

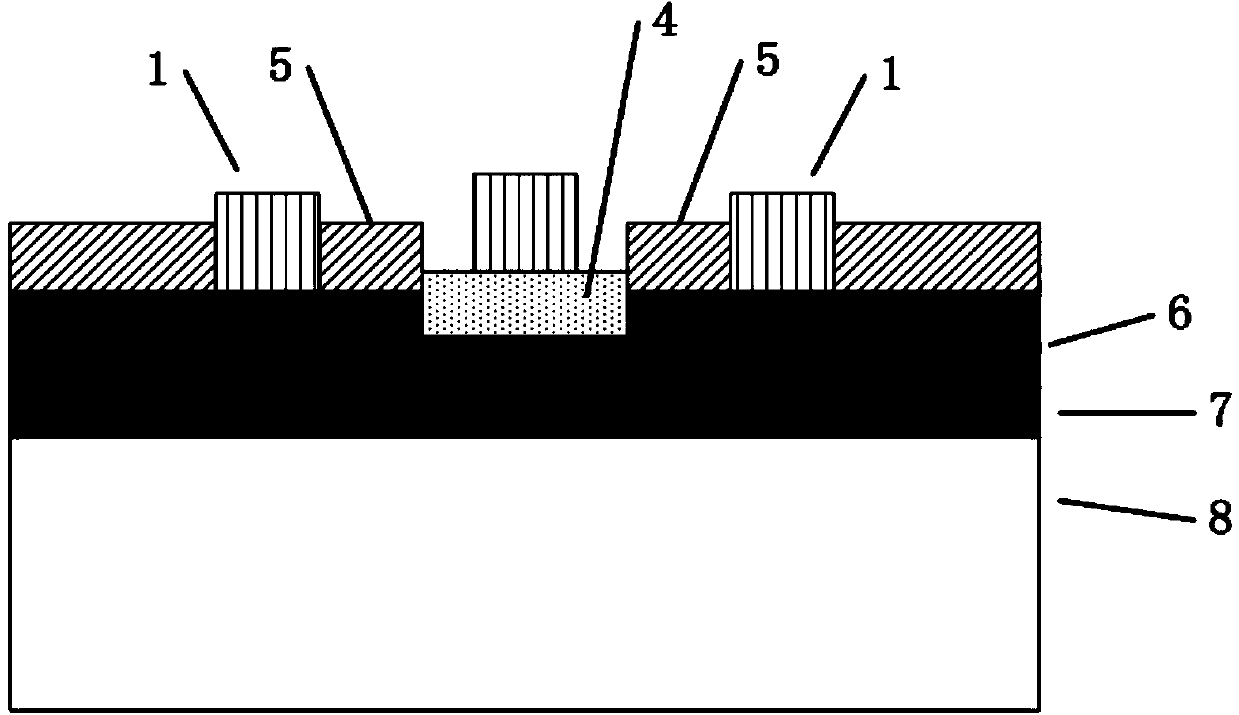

High-low voltage device for plasma display driving chip and preparation method

ActiveCN101714552ALow costReduce power consumptionStatic indicating devicesSolid-state devicesManufacturing technologyLow voltage

The invention provides a high-low voltage device for a plasma display driving chip and a preparation method. The device comprises a high-voltage N-type lateral isolation gate bipolar type transistor, a high-voltage P-type lateral double diffused metal oxide semiconductor field effect transistor, a high-voltage N-type lateral double diffused metal oxide semiconductor field effect transistor, a high-voltage diode and a low-voltage device. The preparation method comprises the following steps of: making a buried oxide layer and depositing a P-type epitaxial layer on the P-type substrate; making a high-voltage N-well and a high-voltage P-well of the high-voltage device on the P-type epitaxial layer; then making P-type body areas of the high-voltage N-type lateral isolation gate bipolar type transistor and the high-voltage P-type lateral double diffused metal oxide semiconductor field effect transistor on the P-type epitaxial layer; and making all low-voltage wells on the P-type epitaxial layer. The chip structure in the invention has the advantages of low chip power consumption, small chip area and high reliability, and can be compatible with manufacture technology of a standard low-voltage complementary type metal oxide semiconductor field effect transistor.

Owner:SUZHOU POWERON IC DESIGN

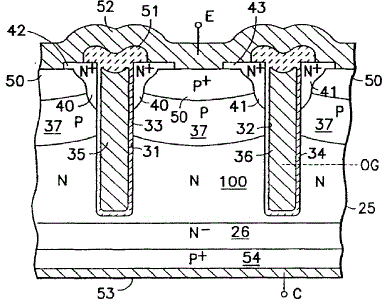

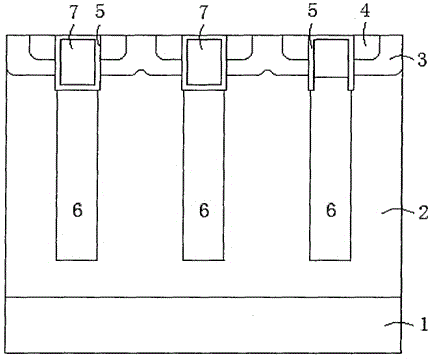

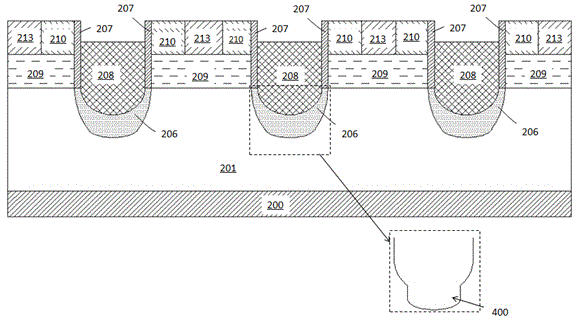

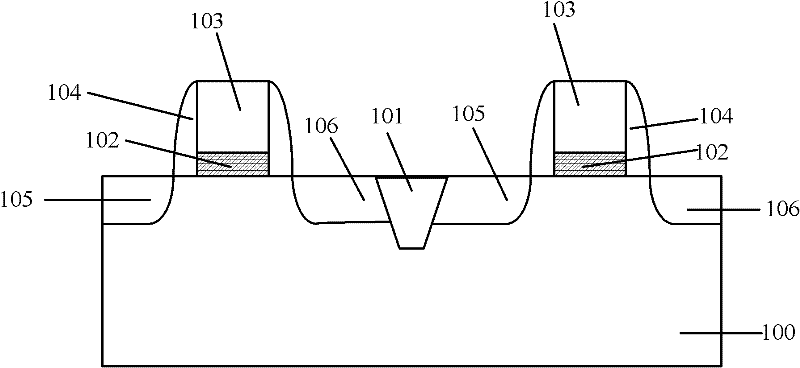

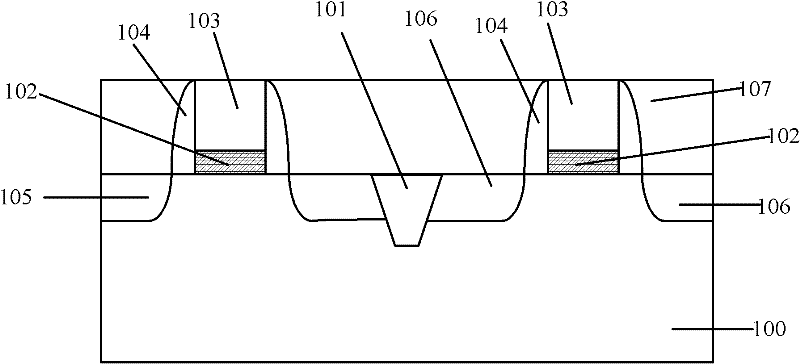

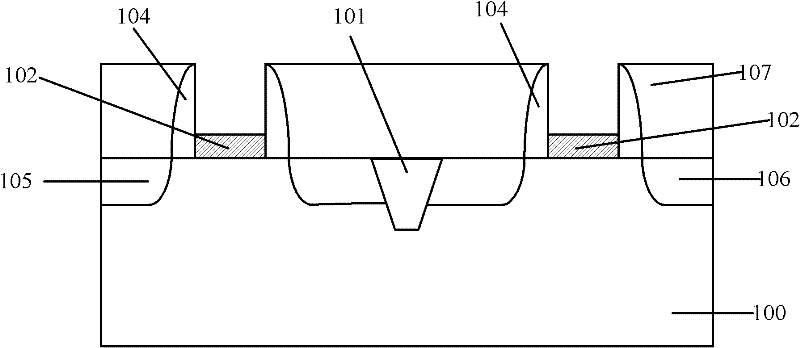

Trench type insulated gate field effect transistor and manufacture method thereof

InactiveCN104103694AImprove breakdown voltageReduce parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesParasitic capacitanceEngineering

The invention belongs to the technical field of insulated gate field effect transistors and particularly relates to a trench type insulated gate field effect transistor and a manufacture method thereof. According to the trench type insulated gate field effect transistor, a thick insulating medium layer is arranged at the bottom of a grid trench so as to increase breakdown voltage of the insulated gate field effect transistor and reduce stray capacitance of the insulated gate field effect transistor; meanwhile, a small groove is formed in the bottom of the grid trench, so that a field oxidation stress transition area is extended, the problem of current leakage caused by field oxidation stress is well solved, and reliability of devices is improved. According to the trench type insulated gate field effect transistor and the manufacture method thereof, by means of a self-alignment process, the groove in the bottom of the grid trench is formed, the process is simple, and the trench type insulated gate field effect transistor is easy to control.

Owner:SUZHOU ORIENTAL SEMICONDUCTOR CO LTD

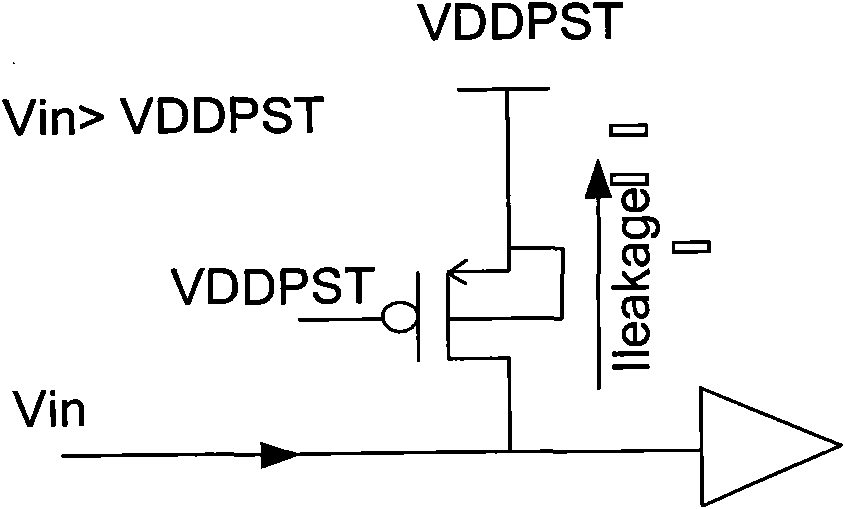

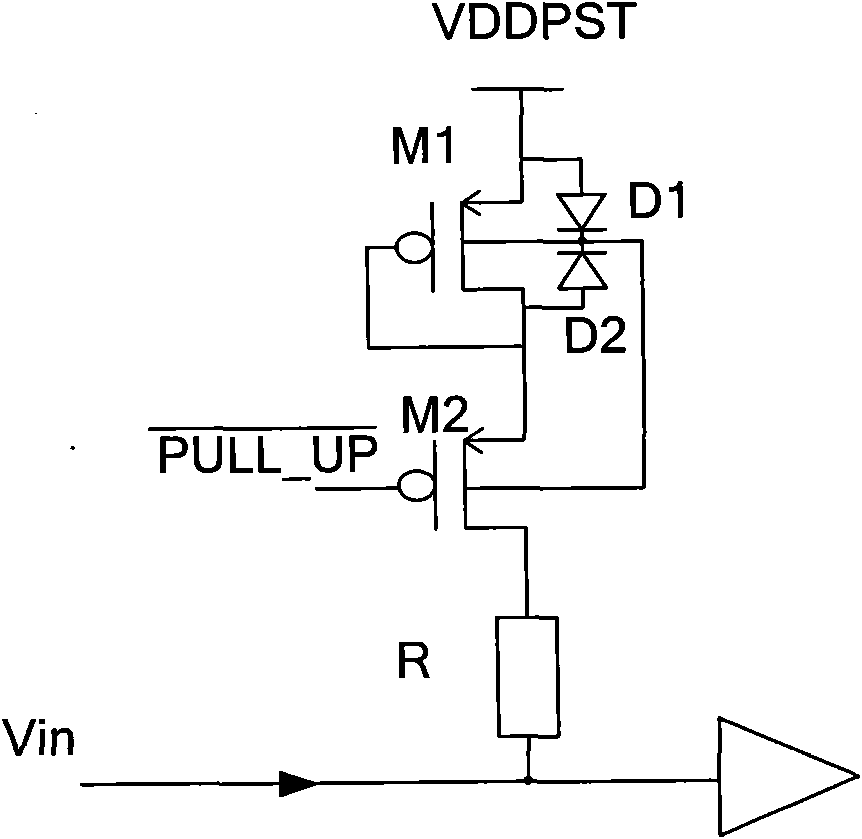

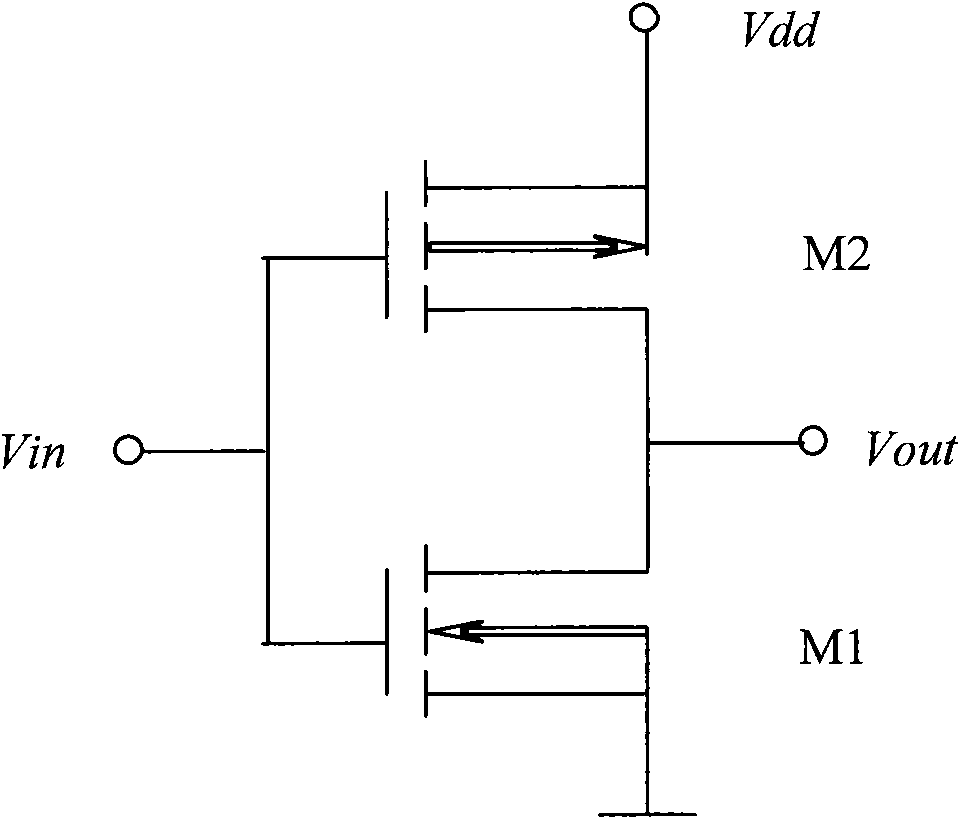

Wide-input voltage range zero-leakage current input pull-up circuit

ActiveCN101840908ANo delayFull pull upSemiconductor/solid-state device detailsSolid-state devicesDrain currentVoltage range

The invention relates to a wide-input voltage range zero-leakage current input pull-up circuit belonging to the field of microelectronics. The prior art has the problems of leakage current, froward resistance value and the like. The current output electrode of a switch MOS (Metal Oxide Semiconductor) tube of the input pull-up circuit connected with the signal input level of a chip by a controllable resistance value element; the grid electrode of the switch MOS tube is a pull-up signal input end; the current input electrode of the switch MOS tube is connected with the highest input level of the chip by a reverse cut-off circuit; and when the signal input level of the chip is higher than the highest input level, the reverse cut-off circuit is cut off. Pulling up is realized by adopting a method for dynamically changing and pulling up the MOS tube substrate to be offset and additionally arranging a diode, meanwhile, the leakage current is avoided when the input level is higher than the highest voltage of the chip.

Owner:SHANGHAI MOUNTAIN VIEW SILICON

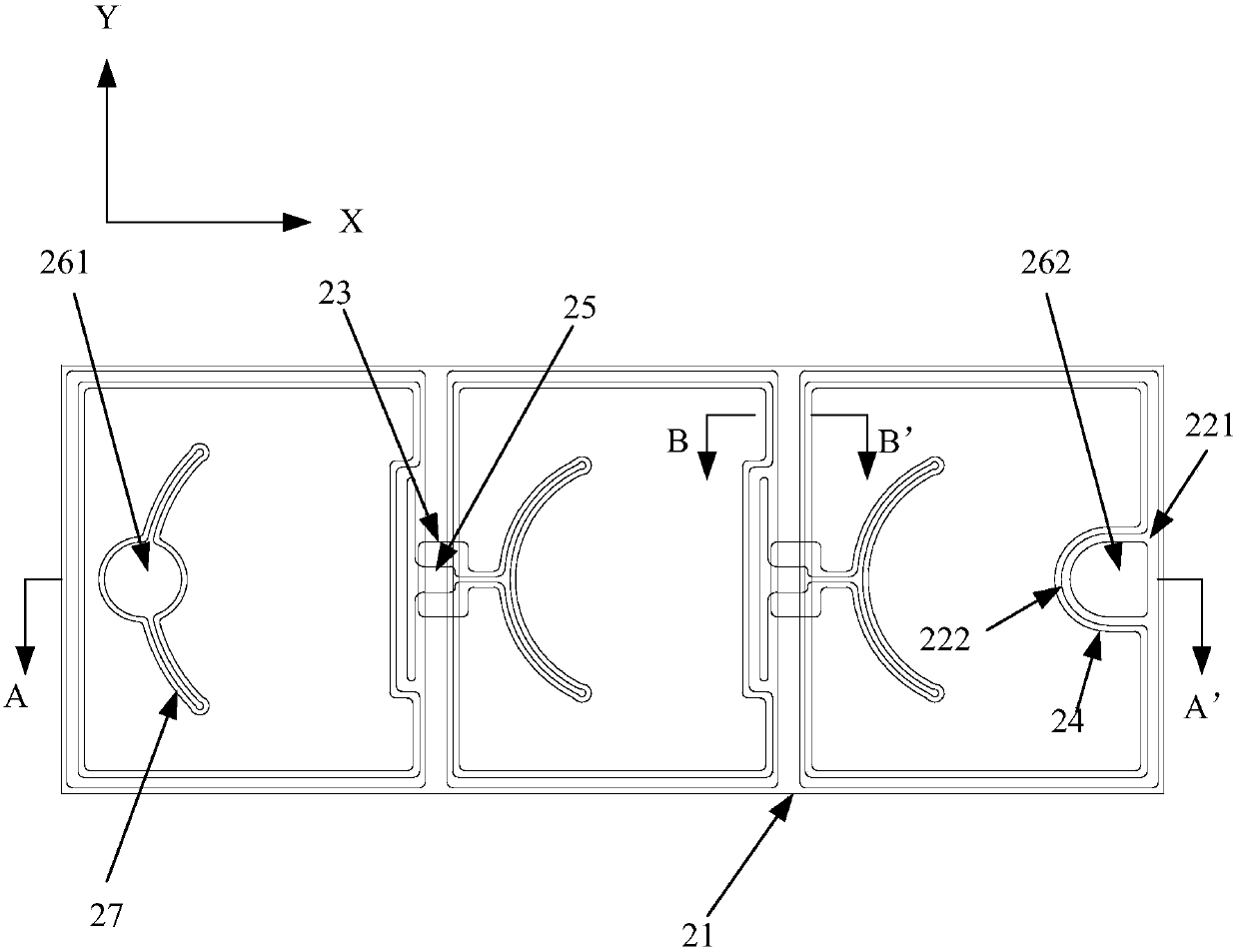

LED chip and production method thereof

ActiveCN107689407AReduce leakage currentImprove stabilitySemiconductor devicesQuantum efficiencyElectricity

The invention discloses an LED chip and a production method thereof. The LED chip comprises a substrate and an extension structure arranged on the substrate, wherein the extension structure is dividedinto a plurality of LED primitive cells; peripheral side walls of the extension structure are provided with a side wall groove, and the side wall groove is used for reducing the total emission of thelight in the LED primitive cells; a primitive cell groove is formed between two adjacent LED primitive cells, the substrate is exposed by virtue of the bottom of the primitive cell groove, and the primitive cell groove reduces the total emission of the light in the LED primitive cells as well as the leak current; an insulation layer is arranged in the primitive cell groove; and a connection electrode covers the insulation layer, and the connection electrode electrically connects two adjacent LED primitive cells. In the technical scheme of the invention, the total emission of the light in theLED primitive cells is reduced by virtue of the side wall groove, the total emission of the light in the LED primitive cells and the leak current can be reduced by virtue of the primitive cell groove,so that the light emitting efficiency can be improved, the current leakage rate is reduced, and the external quantum efficiency can be improved.

Owner:XIAMEN CHANGELIGHT CO LTD

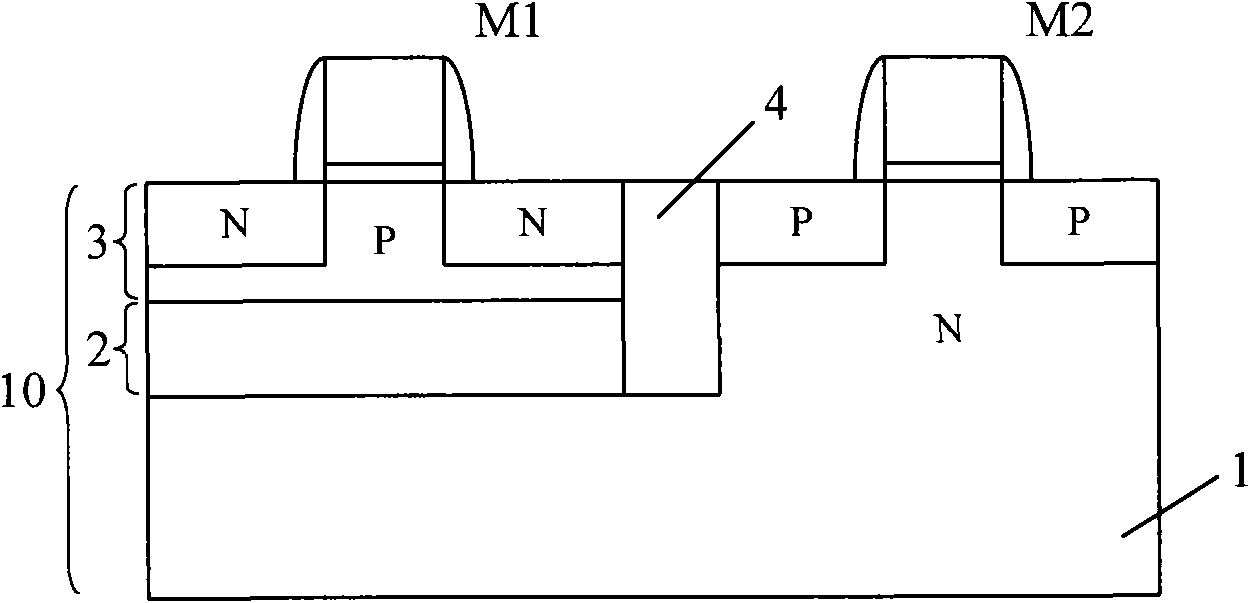

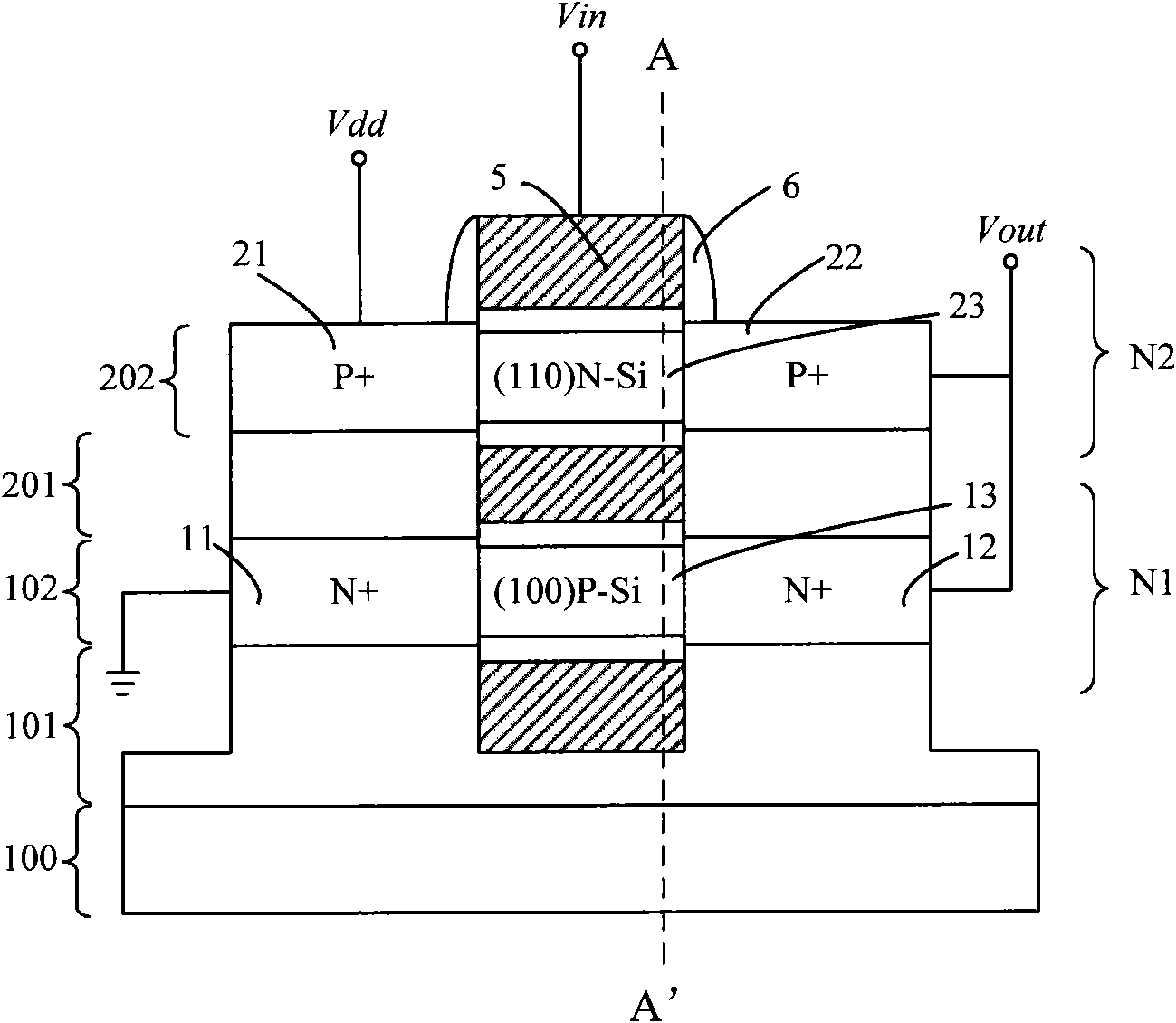

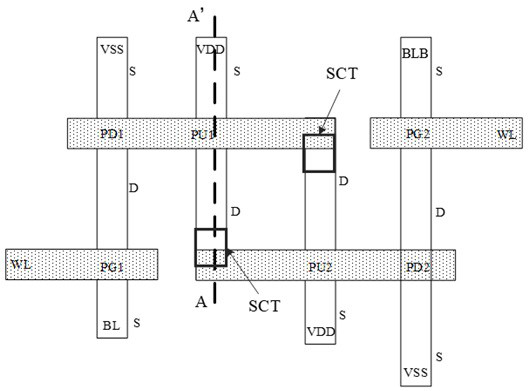

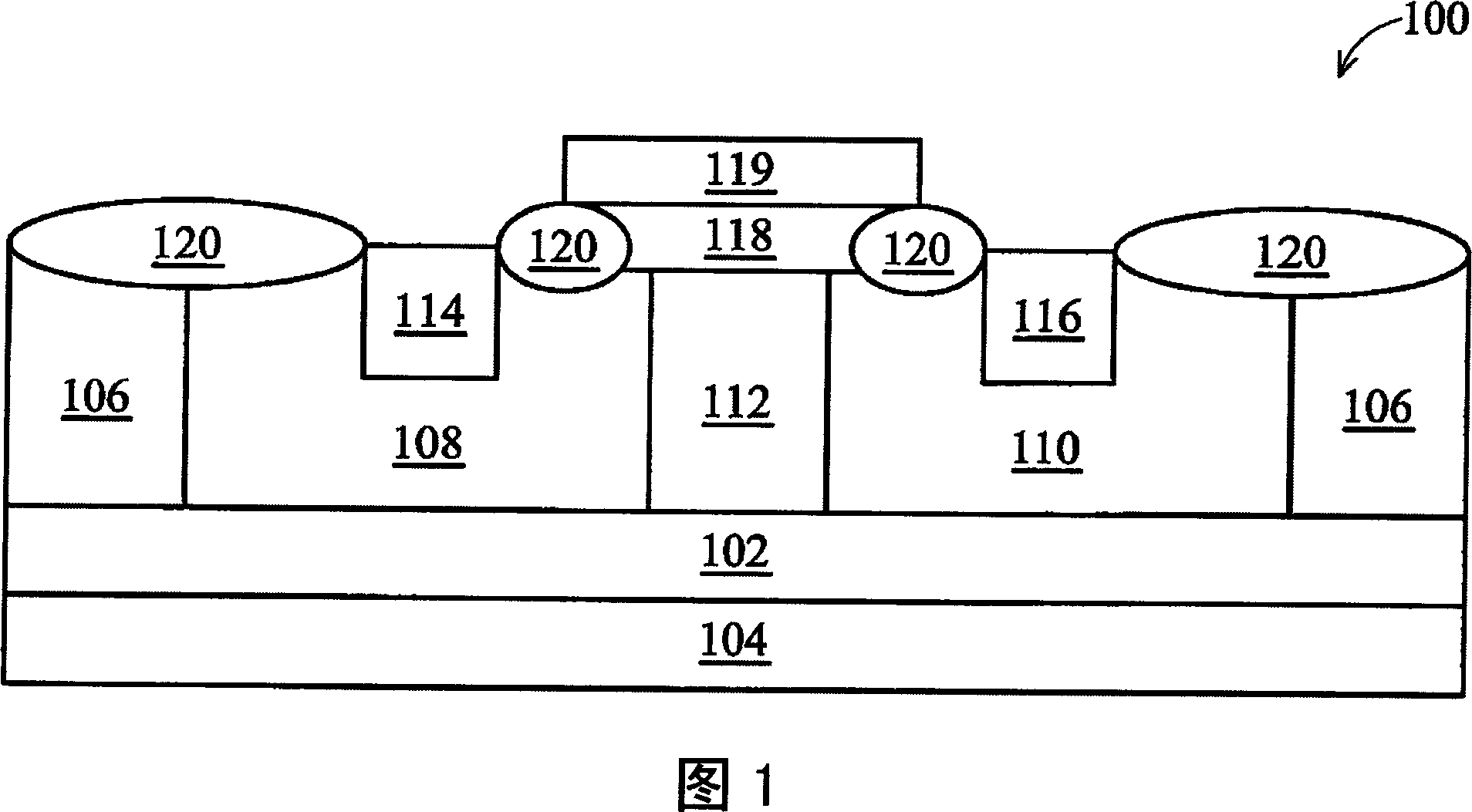

CMOS (Complementary Metal Oxide Semiconductor) device and manufacturing method thereof

InactiveCN101958328AQuick responseImprove mobilitySolid-state devicesSemiconductor/solid-state device manufacturingCMOSField-effect transistor

The invention relates to a CMOS (Complementary Metal Oxide Semiconductor) device and a manufacturing method thereof. The CMOS device comprises a silicon substrate, as well as a first buried oxide layer, first top layer silicon, a second buried oxide layer and second top layer silicon which are arranged on the silicon substrate in sequence, wherein the first top layer silicon and the second top layer silicon are different in 3.3 crystallographic orientation; a first field effect transistor is formed on the first top layer silicon used as a substrate, a second field effect transistor is formed on the second top layer silicon used as a substrate and is aligned to the first field effect transistor, and the conduction types of the first field effect transistor and the second field effect transistor are different. In the provided CMOS device, the crystallographic orientations of substrates of conducting channels formed by NMOS (N-Channel Metal Oxide Semiconductor) transistors and PMOS (P-Channel Metal Oxide Semiconductor) transistors are respectively (100) and (110), so that the mobility of respective current carrier is increased, and the response speed of the CMOS device is increased. The problem of current leakage of the substrates is solved by insulating the substrate of each transistor through stacking the transistors and using multiple buried oxide layers.

Owner:SEMICON MFG INT (SHANGHAI) CORP

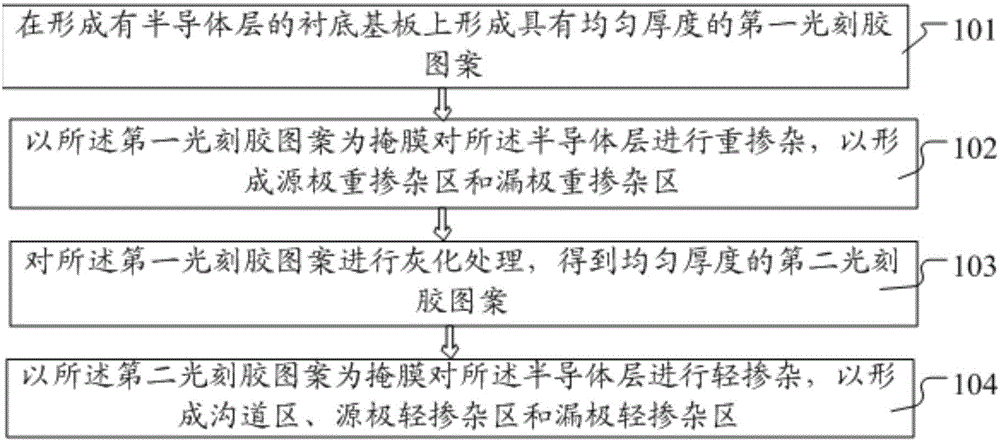

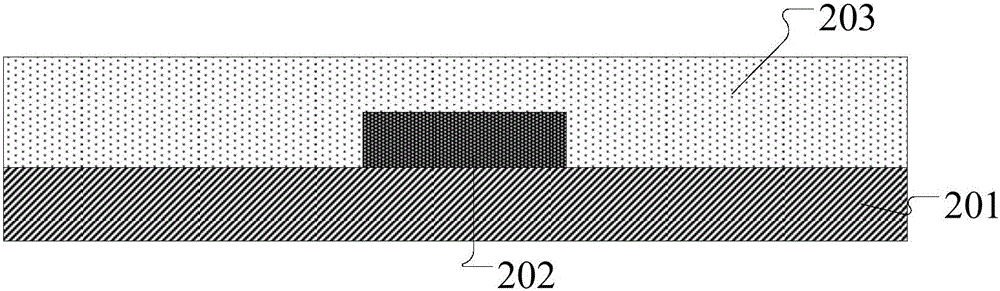

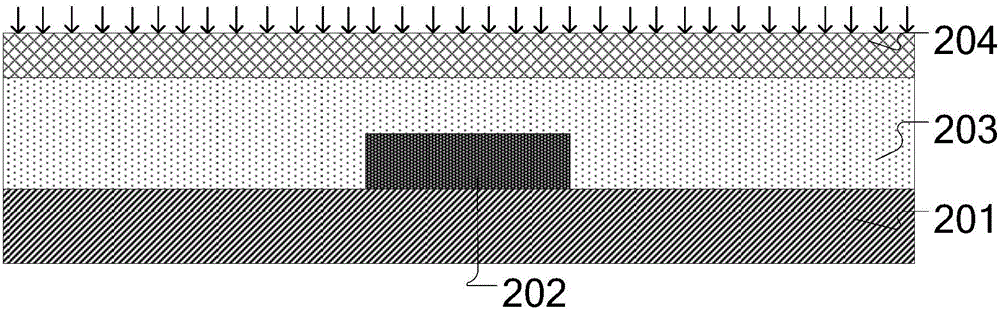

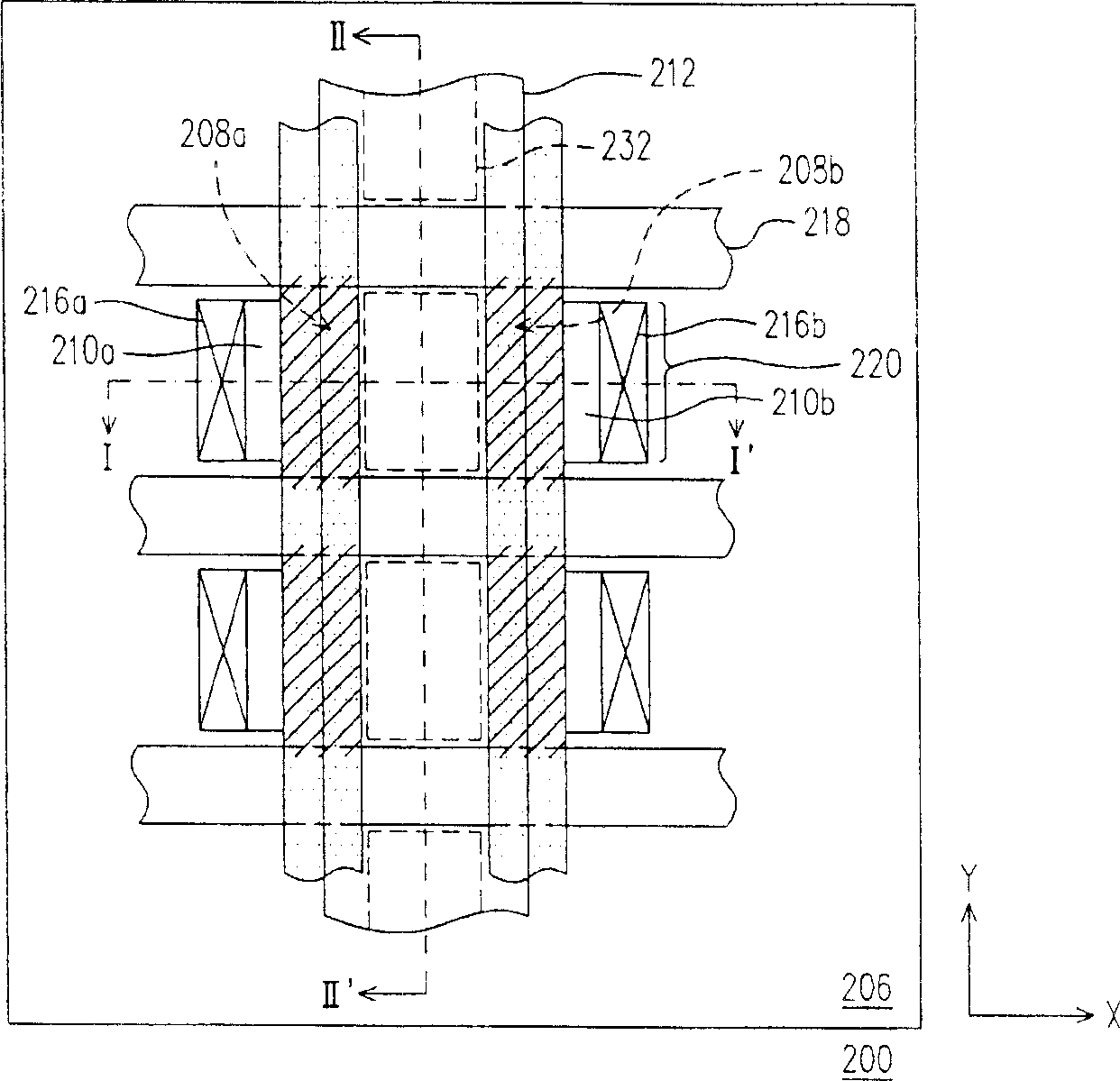

Preparation methods of thin film transistor and array substrate, array substrate and display device

InactiveCN106024633AFewer steps in the preparation processControl critical dimensionsTransistorSolid-state devicesDisplay devicePhotoresist

The invention provides preparation methods of a thin film transistor and an array substrate, the array substrate and a display device. The preparation method of the thin film transistor comprises the steps of: forming a first photoresist pattern with a uniform thickness on a substrate formed with a semiconductor layer; carrying out heavy doping on the semiconductor layer employing the first photoresist pattern as a mask to form a source heavily-doped region and a drain heavily-doped region; carrying out ashing treatment on the first photoresist pattern to obtain a second photoresist pattern with the uniform thickness; and carrying out light doping on the semiconductor layer employing the second photoresist pattern as the mask to form a channel region, a source lightly-doped region and a drain lightly-doped region. By the method, a photoresist can be fully utilized; the critical sizes of the source lightly-doped region and the drain lightly-doped region are accurately and efficiently controlled; and the product uniformity is ensured.

Owner:BOE TECH GRP CO LTD +1

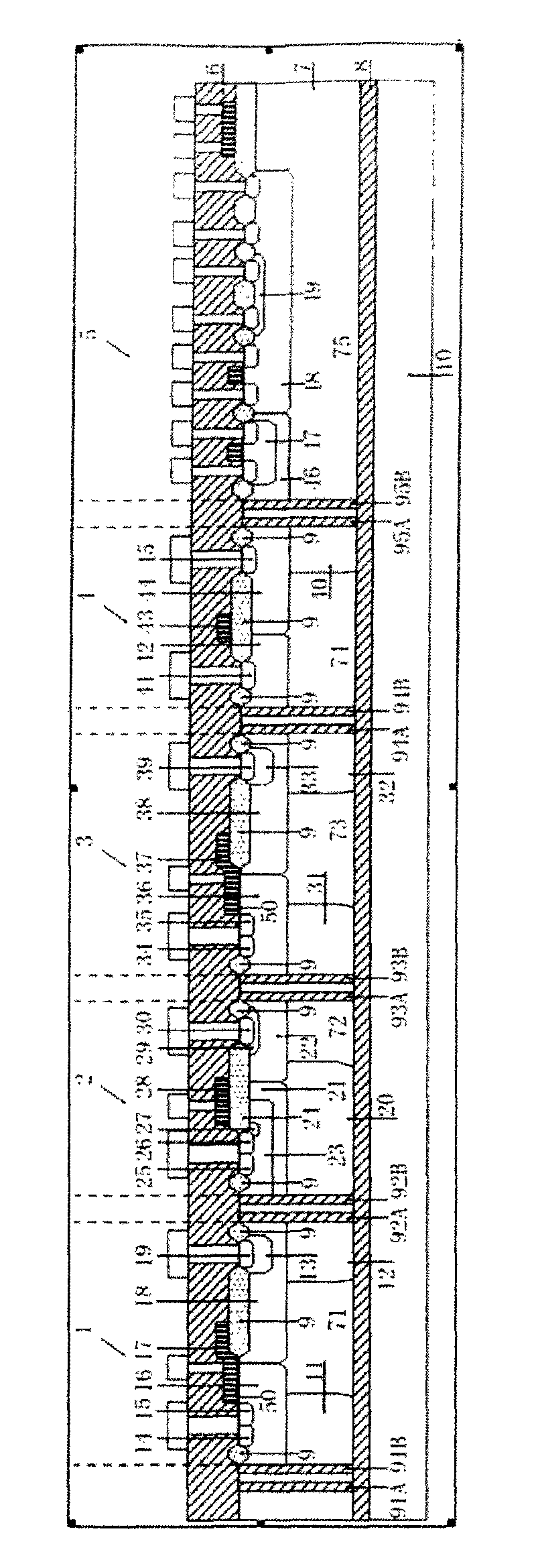

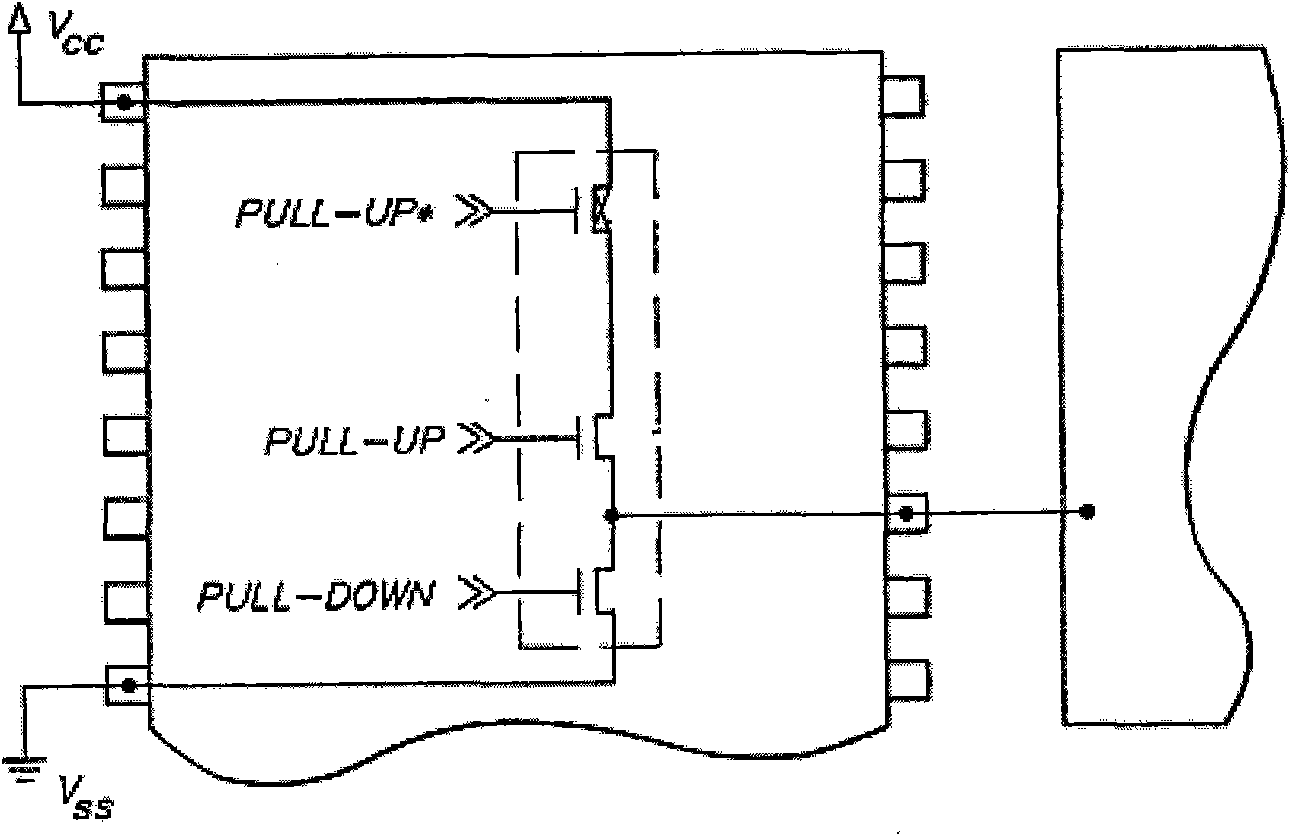

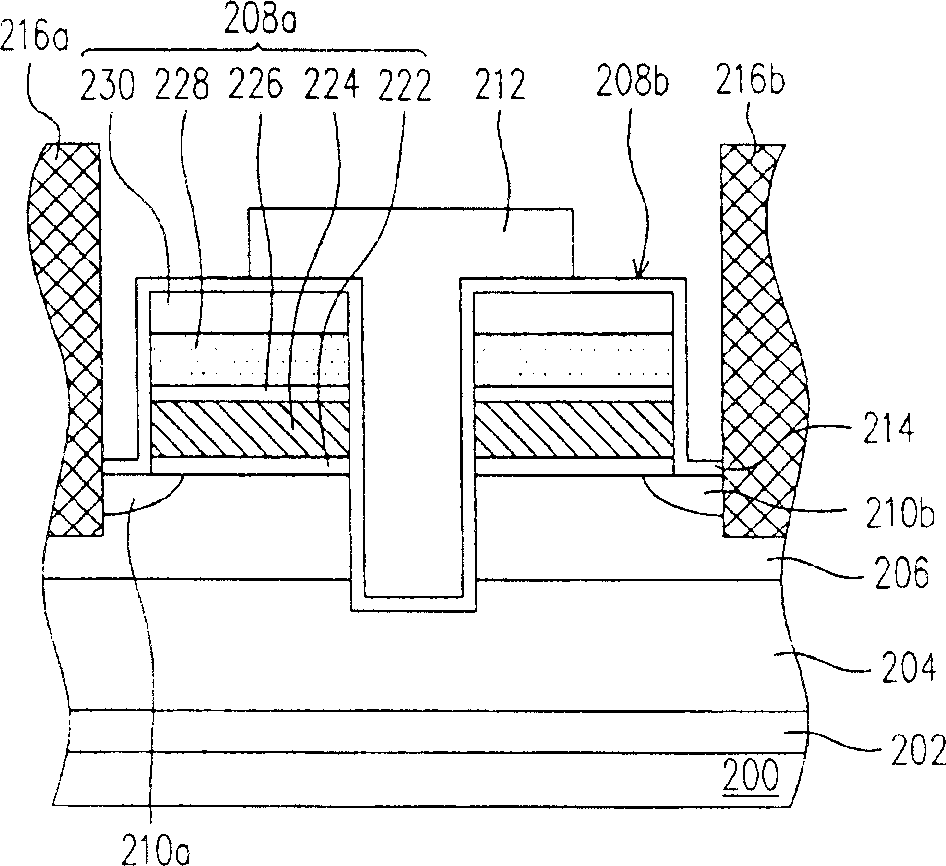

Panel display driving chip based on silicon on insulator (SOI) and preparation method thereof

InactiveCN101964344ASolve leakage currentReduce power consumptionSolid-state devicesSemiconductor/solid-state device manufacturingHigh voltage transistorsDisplay device

The invention provides a panel display driving chip based on a silicon on insulator (SOI) material, which is composed of a high-voltage P-type transverse metal oxide transistor, a high-voltage N-type transverse metal oxide transistor, a high-voltage N-type transverse insulated gate bipolar transistor and a low-voltage device, wherein each high-voltage device is isolated by a double-groove structure filled with silicon dioxide, which starts from the oxygen buried layer and ends at the field oxide on the device surface via the N-type buried layer and the N-type epitaxial layer; and the connection region of the epitaxial layer and the oxygen buried layer is provided with the N-type buried layer. The preparation method comprises the following steps: making the oxygen buried layer, the N-type buried layer and the deposition epitaxial layer on the P-type substrate; making the high-voltage P wells of the high-voltage N-type transverse metal oxide transistor and the high-voltage N-type transverse insulated gate bipolar transistor, the P-type drift region of the high-voltage P-type transverse metal oxide transistor, the buffer layer of the high-voltage transistor, the low-voltage well of the low-voltage transistor, the source and drain regions and the contact holes; and evaporating aluminium, photoetching aluminium in a reversed mode, forming electrodes and metal field plates, and passivating.

Owner:SOUTHEAST UNIV

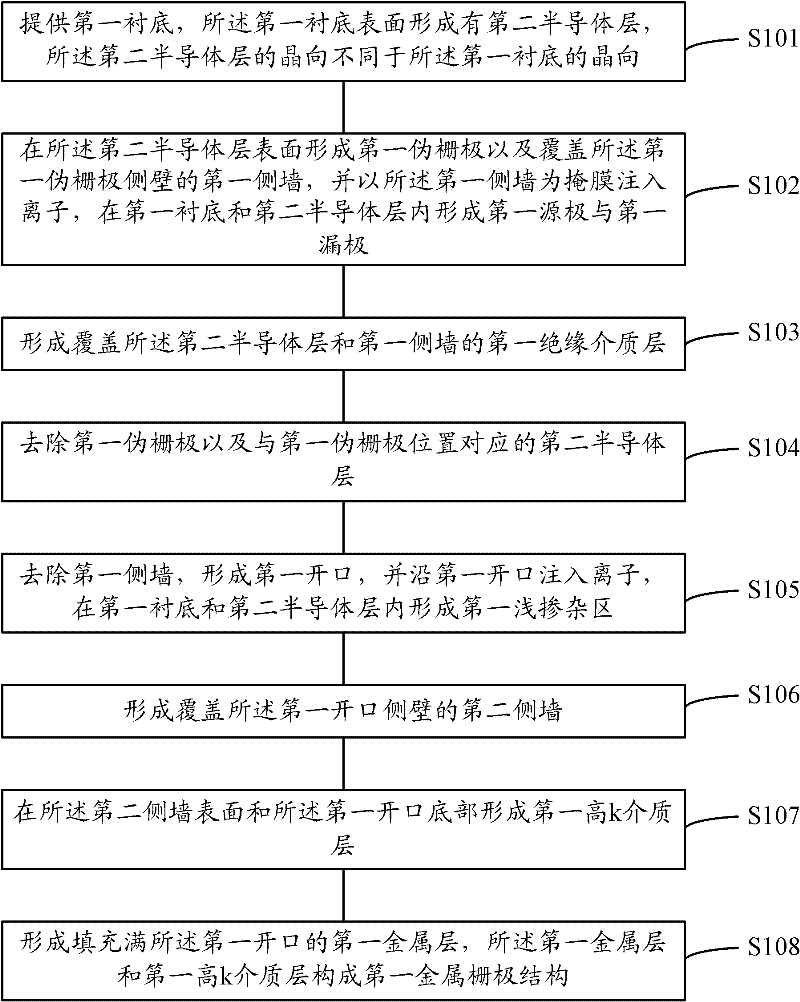

Method for manufacturing transistor

ActiveCN102479722AQuality improvementSolve leakage currentSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricEngineering

The invention provides a method for manufacturing a transistor. The method comprises: a semiconductor substrate is provided; sacrificial layers are formed on the semiconductor substrate, wherein the sacrificial layers are formed by utilizing a deposition technology; dummy grids are formed on the sacrificial layers; source regions and drain regions are formed in portions of the semiconductor substrate, wherein the portions are at two sides of the dummy grids and the sacrificial layers; interlayer dielectric layers that are flush with the dummy grids are formed; wherein the interlayer dielectric layers covers the source regions and the drain regions; the dummy grids and the sacrificial layers are removed as well as grooves that are exposed outside the semiconductor substrate are formed in the interlayer dielectric layers; gate dielectric layers are formed at the bottom of the grooves; high K dielectric layers are formed at sidewalls and the bottoms of the grooves; and metal grids are formed on the high K dielectric layers, wherein the grooves are filled with the metal grids and are flush with the interlayer dielectric layers. According to the invention, a leakage current problem of a transistor can be solved as well as the performance of the transistor can be improved.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

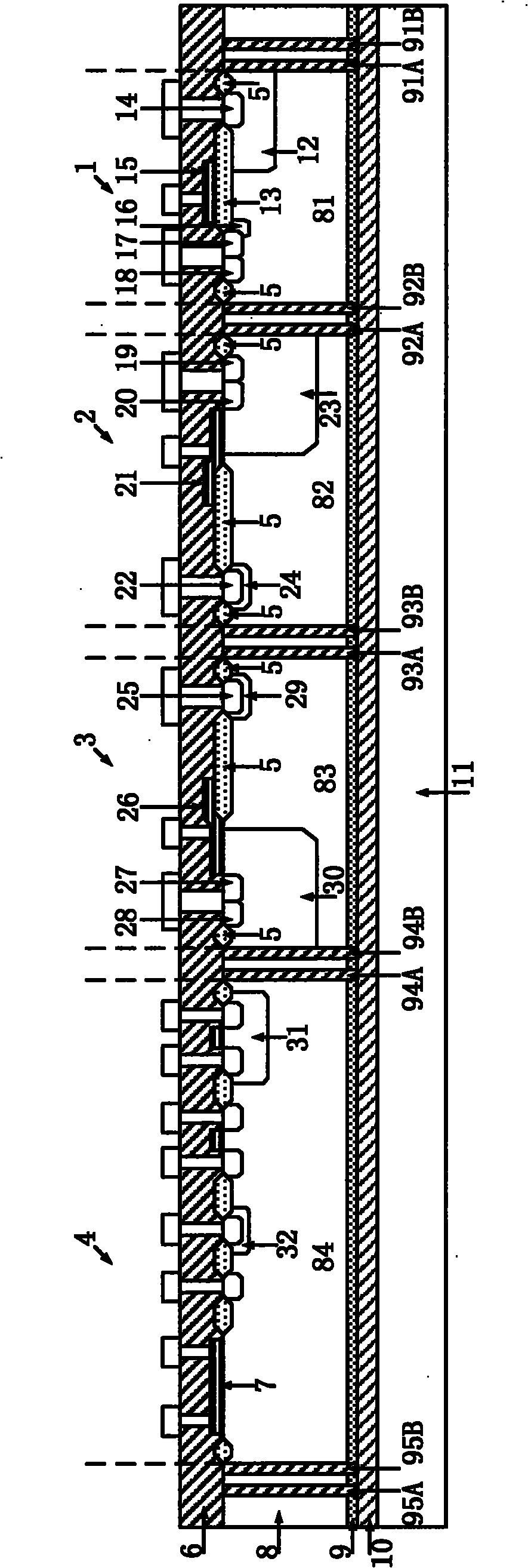

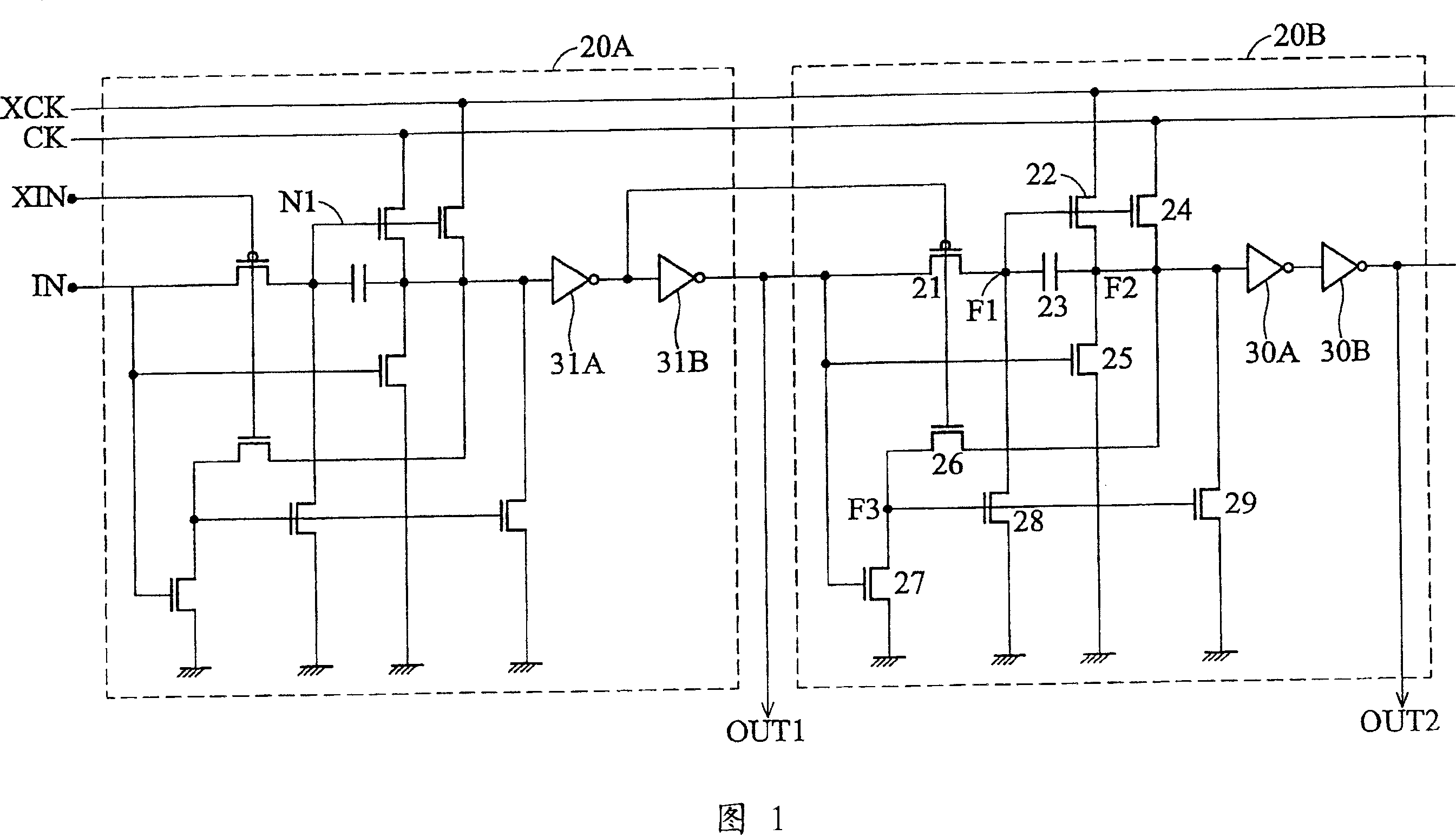

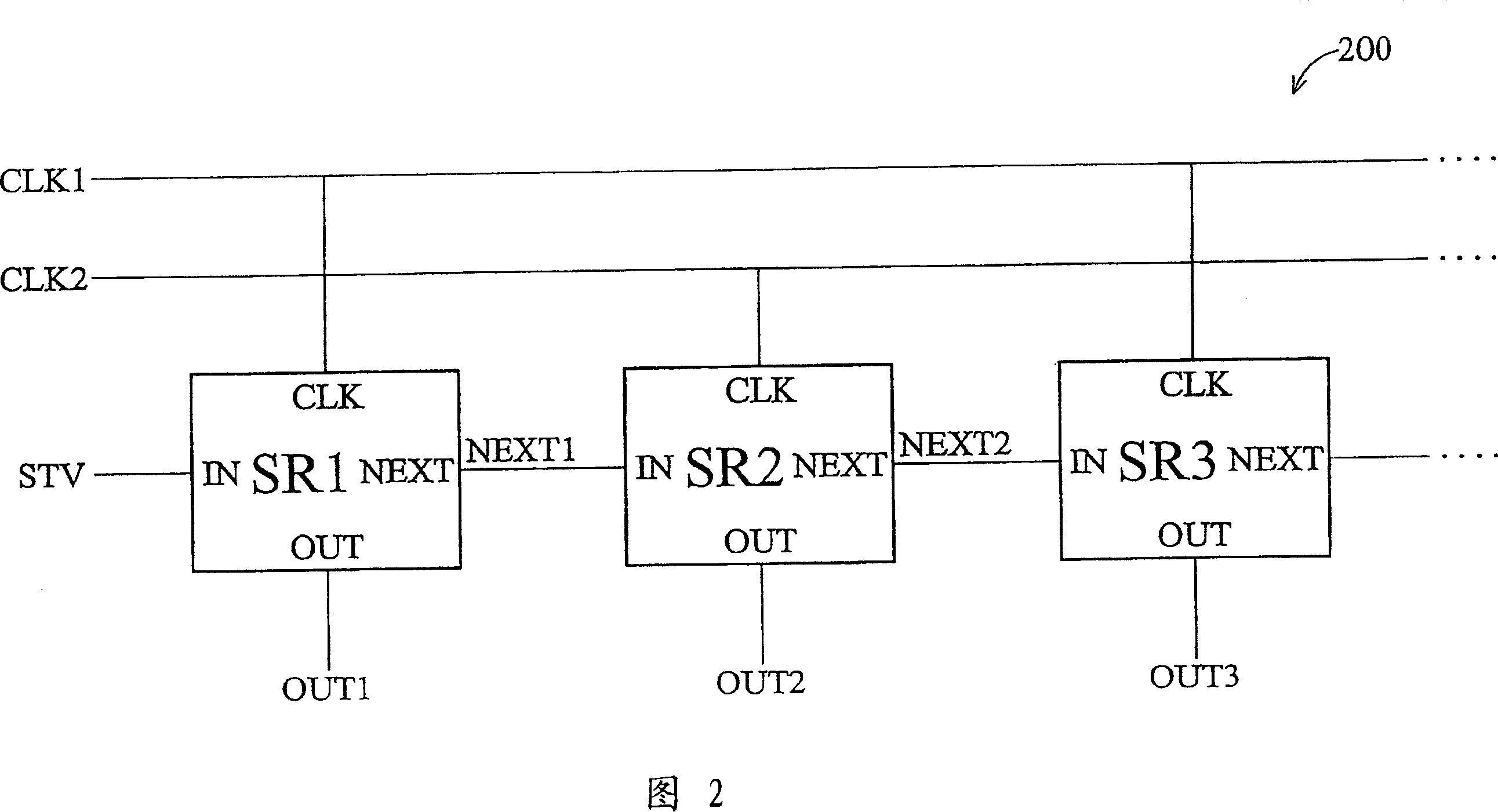

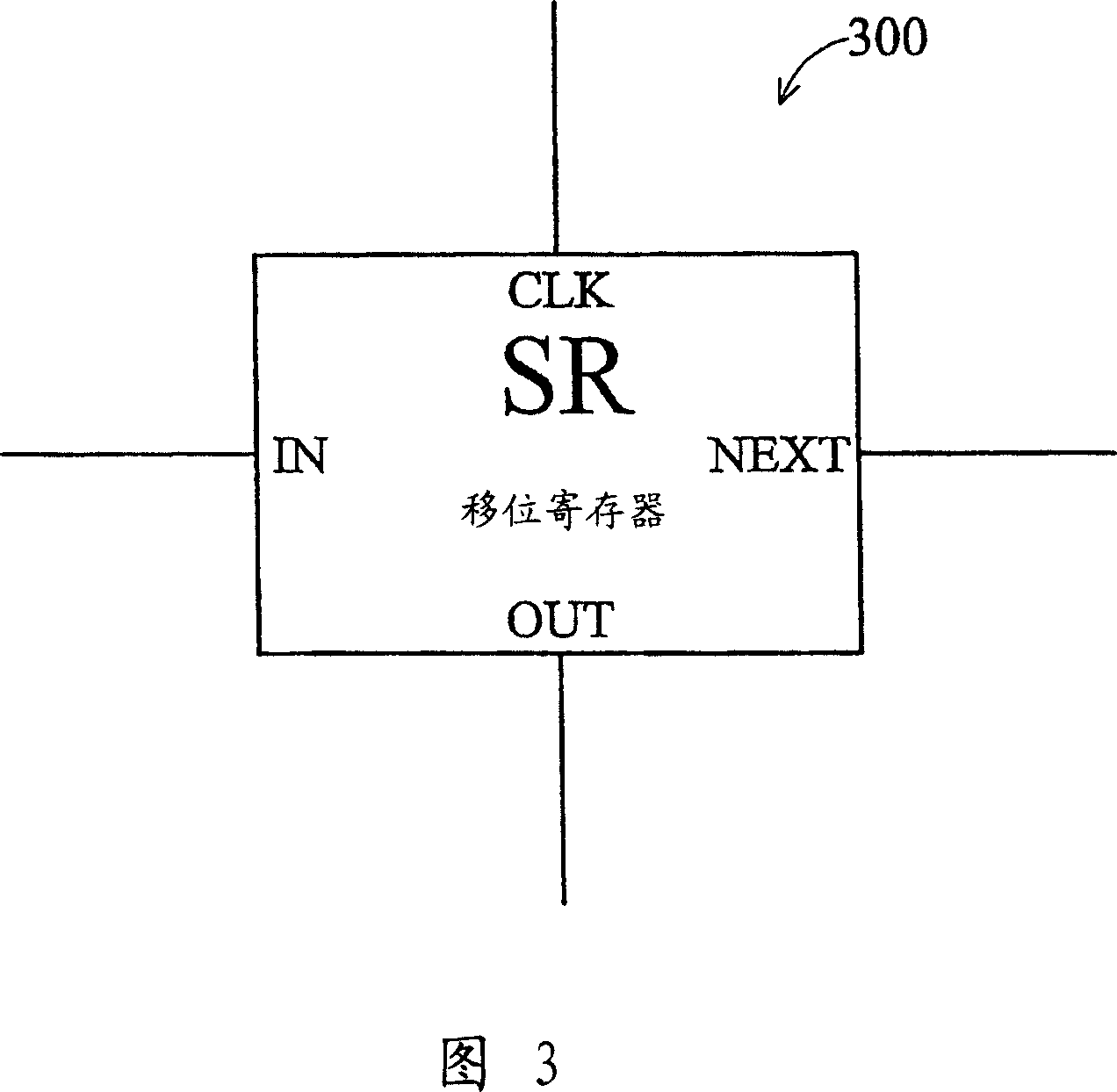

Image display system and method for driving display component

The invention provides an image display system which comprises a signal drive circuit, wherein, the signal drive circuit comprises a plurality of tandem shift registers which are controlled by a first clock signal and a second clock signal to generate corresponding drive signal in turn according to a start pulse signal; each shift register comprises a first clock input end, an input end, an output end and a drive end; the first clock input end is used to receive one of the first clock signal and the second clock signal; the input end receives a first pulse signal; the output end generates an output signal; the drive end generates a drive signal according to the received clock signal to drive a sublevel shift register; moreover, the output signal and the drive signal are generated at different time intervals.

Owner:INNOLUX CORP

Semiconductor device and preparation method thereof

ActiveCN114783947AAvoid short circuitWill not cause food and clothingTransistorSemiconductor/solid-state device detailsMetal interconnectDevice material

The invention provides a semiconductor device and a preparation method thereof. According to the method, an etching stop layer is not grown on the surface of a device, but a first interlayer dielectric layer is directly deposited, and a grinding barrier layer is directly formed on the first interlayer dielectric layer without grinding, so that grinding depression is avoided. The surface topography of the first interlayer dielectric layer and the surface topography of the grinding barrier layer are in a fluctuating state and fit with the surface topography of the device. And when the contact hole is etched, the morphology after etching in unit time is still matched with the surface morphology of the device. The first interlayer dielectric layer does not remain at the bottom of the contact hole, and over-etching is not needed, so that a film layer of the device cannot be broken through, and current leakage is avoided. And a second interlayer dielectric layer is also formed on the grinding barrier layer to serve as a grinding sacrificial layer. Therefore, in the grinding process, under the combined action of the sacrificial layer and the grinding barrier layer, the problem of grinding depression can be effectively relieved, so that the phenomenon that a metal interconnection structure formed subsequently collapses, and consequently a metal connection line is short-circuited is avoided, and the product yield is increased.

Owner:晶芯成(北京)科技有限公司 +1

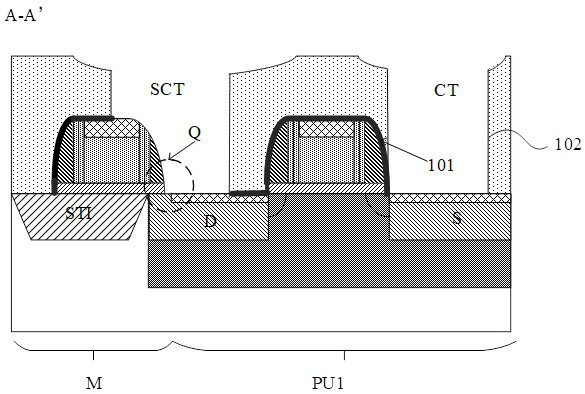

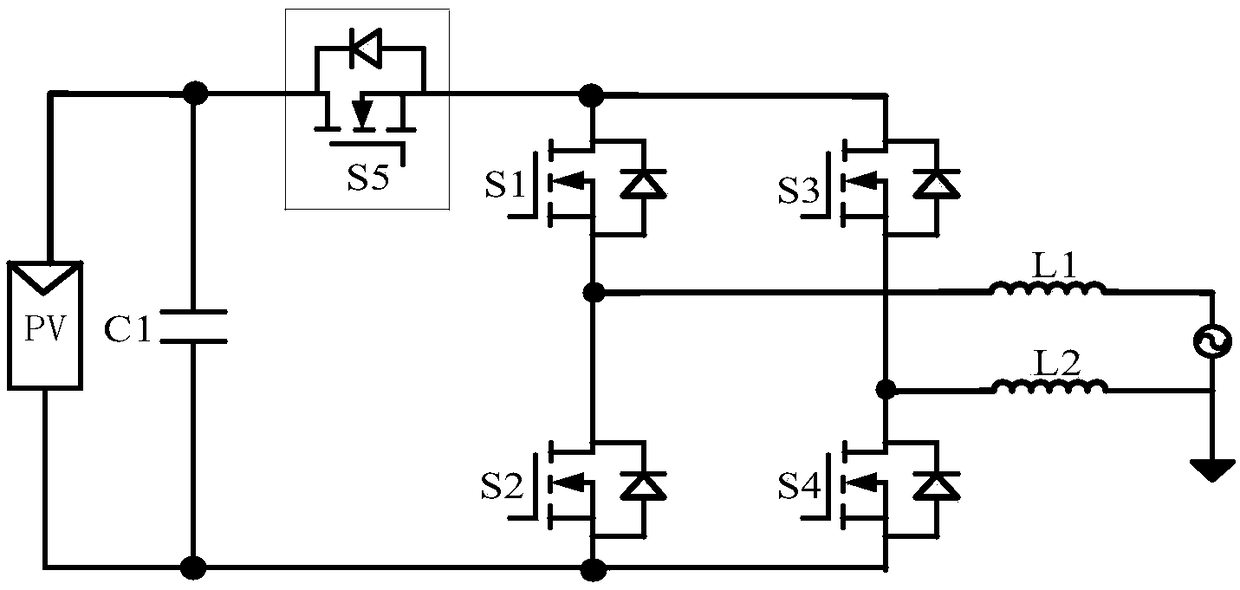

Epitaxial preparation method of gallium nitride LED

The invention discloses an epitaxial preparation method of a gallium nitride LED. The method comprises the following steps of growing a gallium nitride buffer layer on a sapphire substrate; annealingthe gallium nitride buffer layer shape to form at least one crystal nucleus island-buffer layer; and transversely growing the gallium nitride layer on the basis of the crystal nuclear island until allthe crystal nuclear islands are connected with each other, so as to form an integral two-dimensional crystal layer-3D crystal nucleus layer. According to the preparation method, a buffer insertion layer is grown in the middle of an active region. The buffer insertion layer is formed by alternately laminating a first sub-layer, a second sub-layer and a third sub-layer. The first sub-layer is madeof P-type gallium nitride, the second sub-layer is made of P-type indium gallium nitrogen, and the third sub-layer is made of N-type aluminum gallium nitrogen. According to the technical scheme, the functions of electronic deceleration and uniform expansion are achieved through consumption, blocking and emission effects. The problem of leakage current of positive conduction is solved, and the problem that the light emitting efficiency of the conventional gallium nitride LED epitaxial structure is lowered along with the increasing of the current density is solved.

Owner:贵州杰芯光电科技有限公司

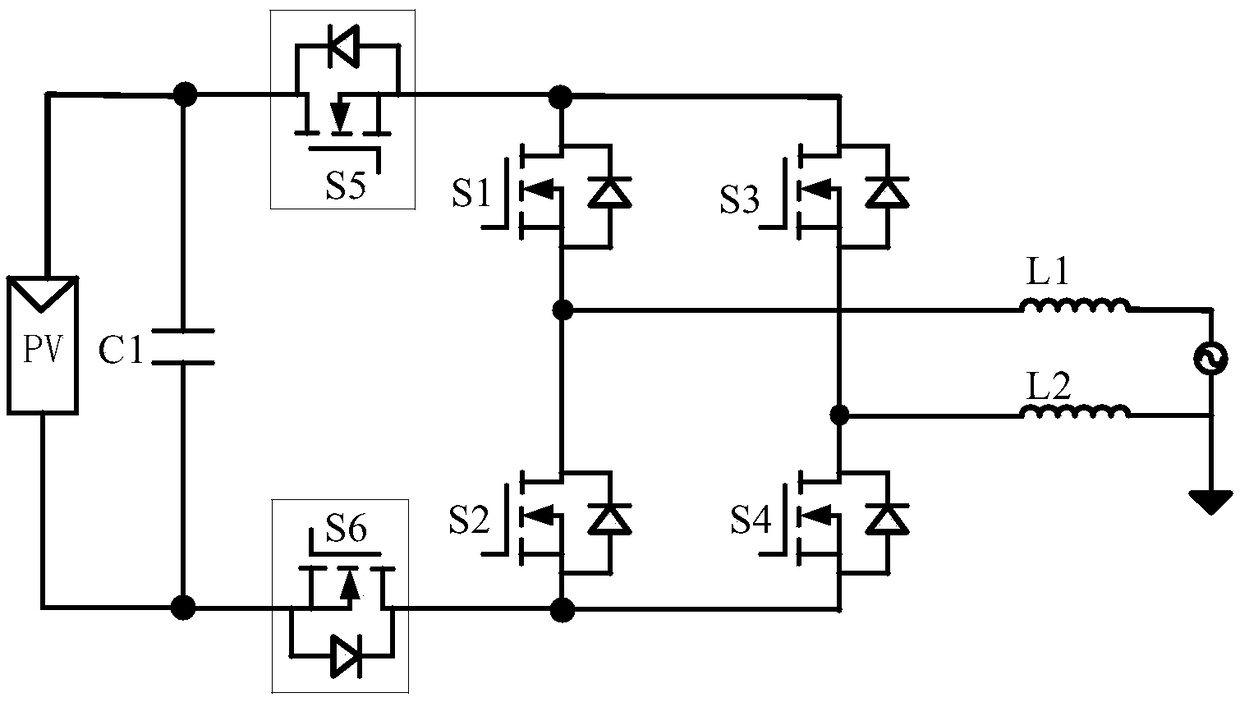

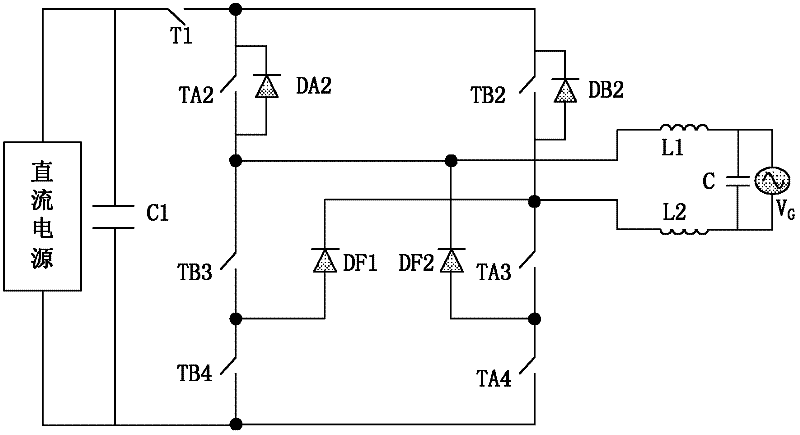

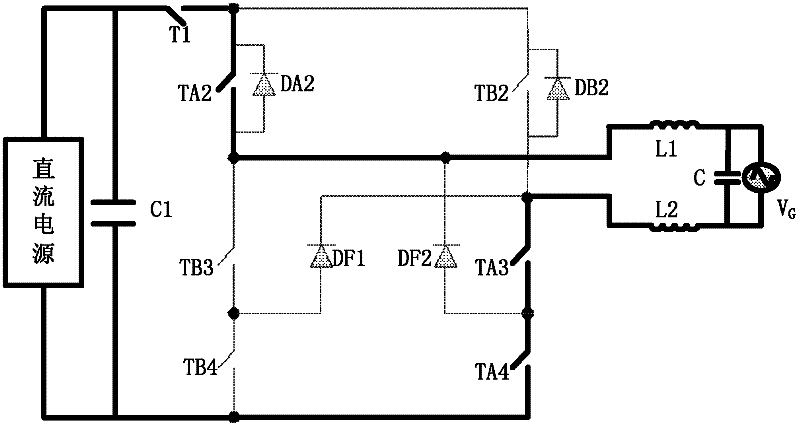

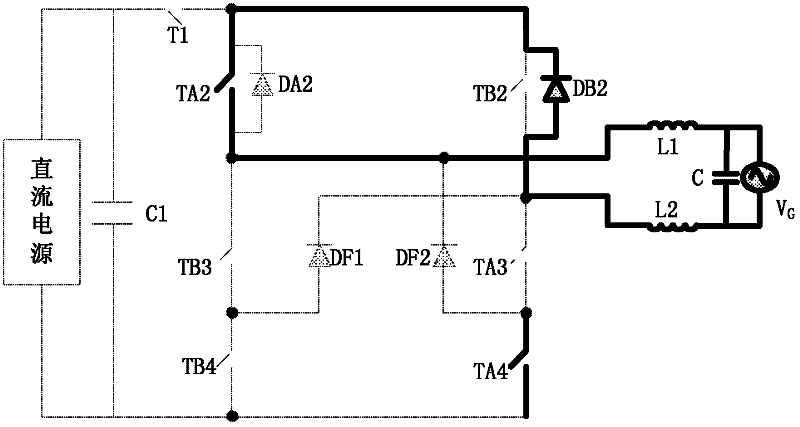

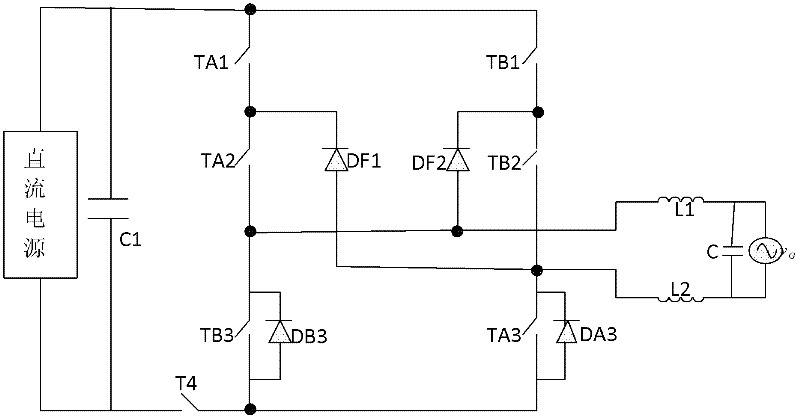

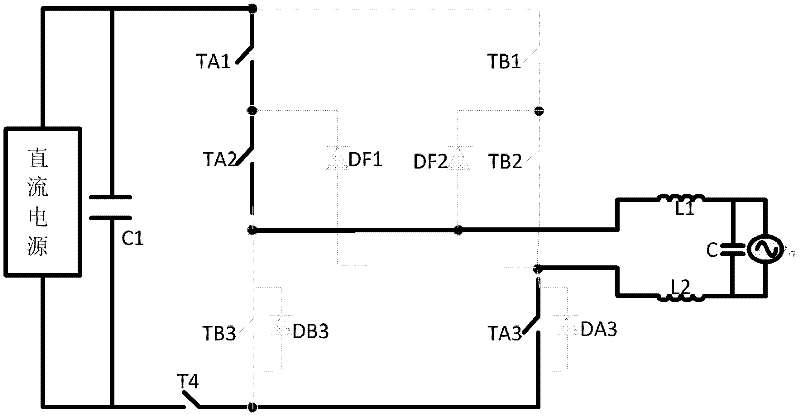

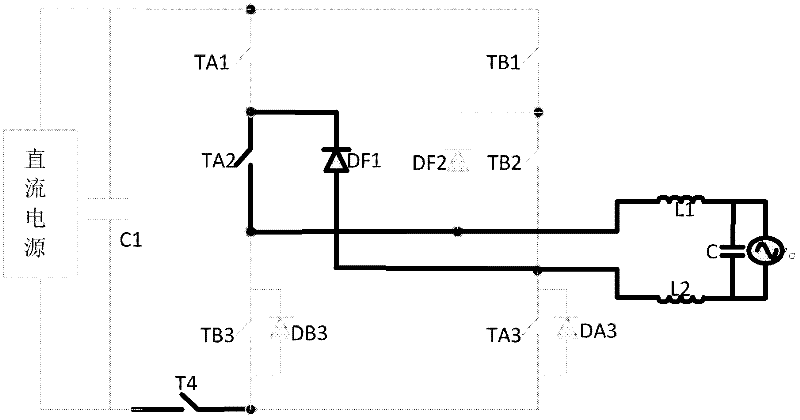

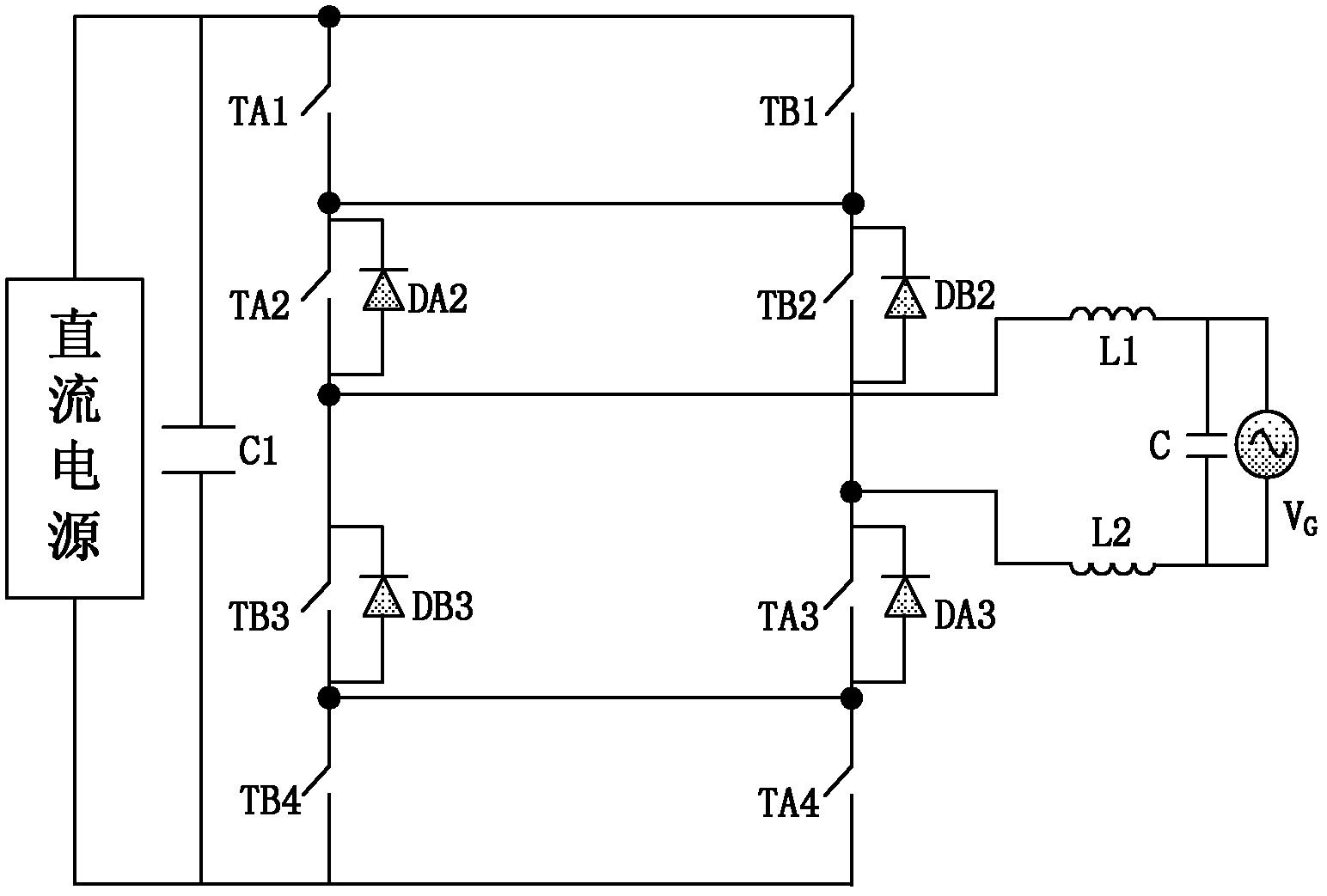

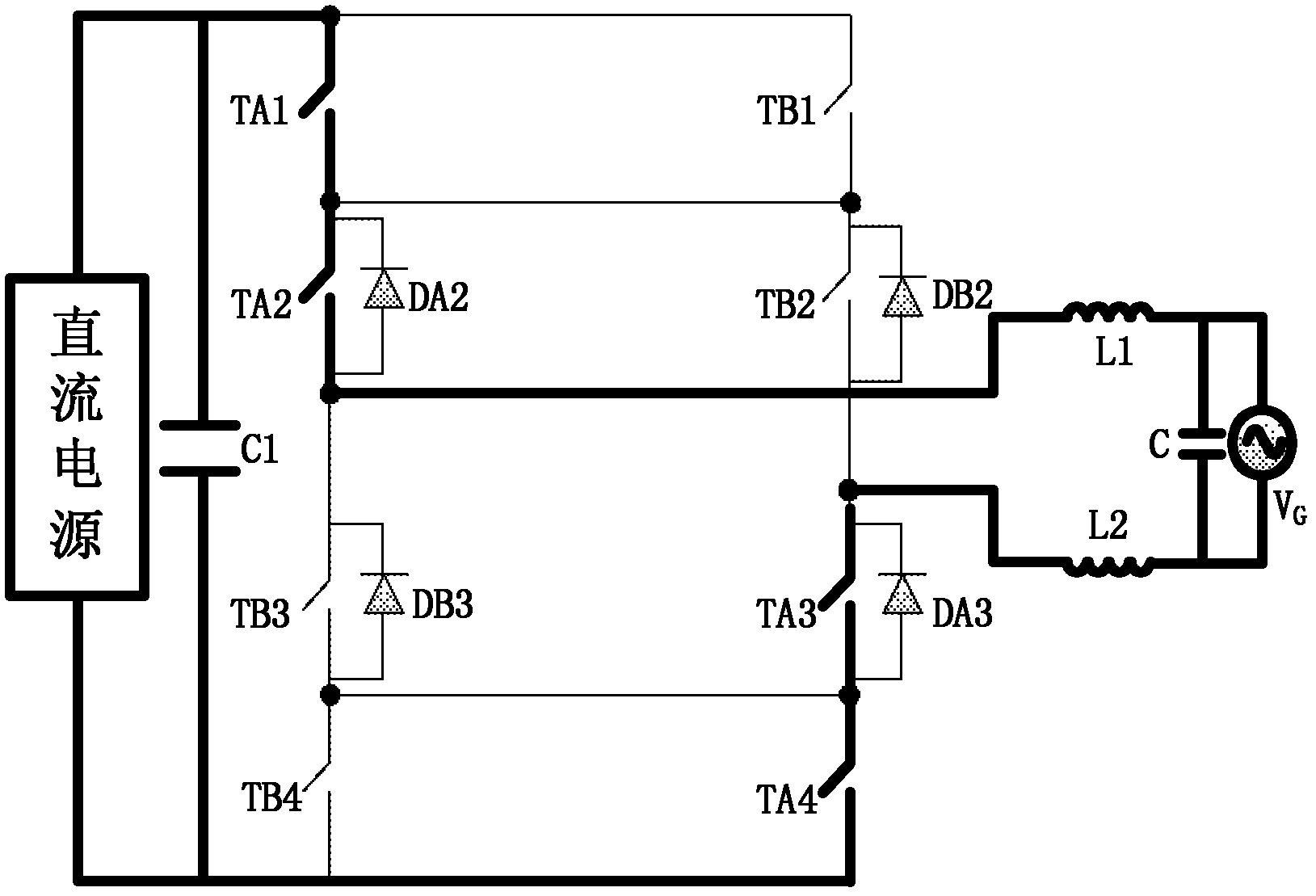

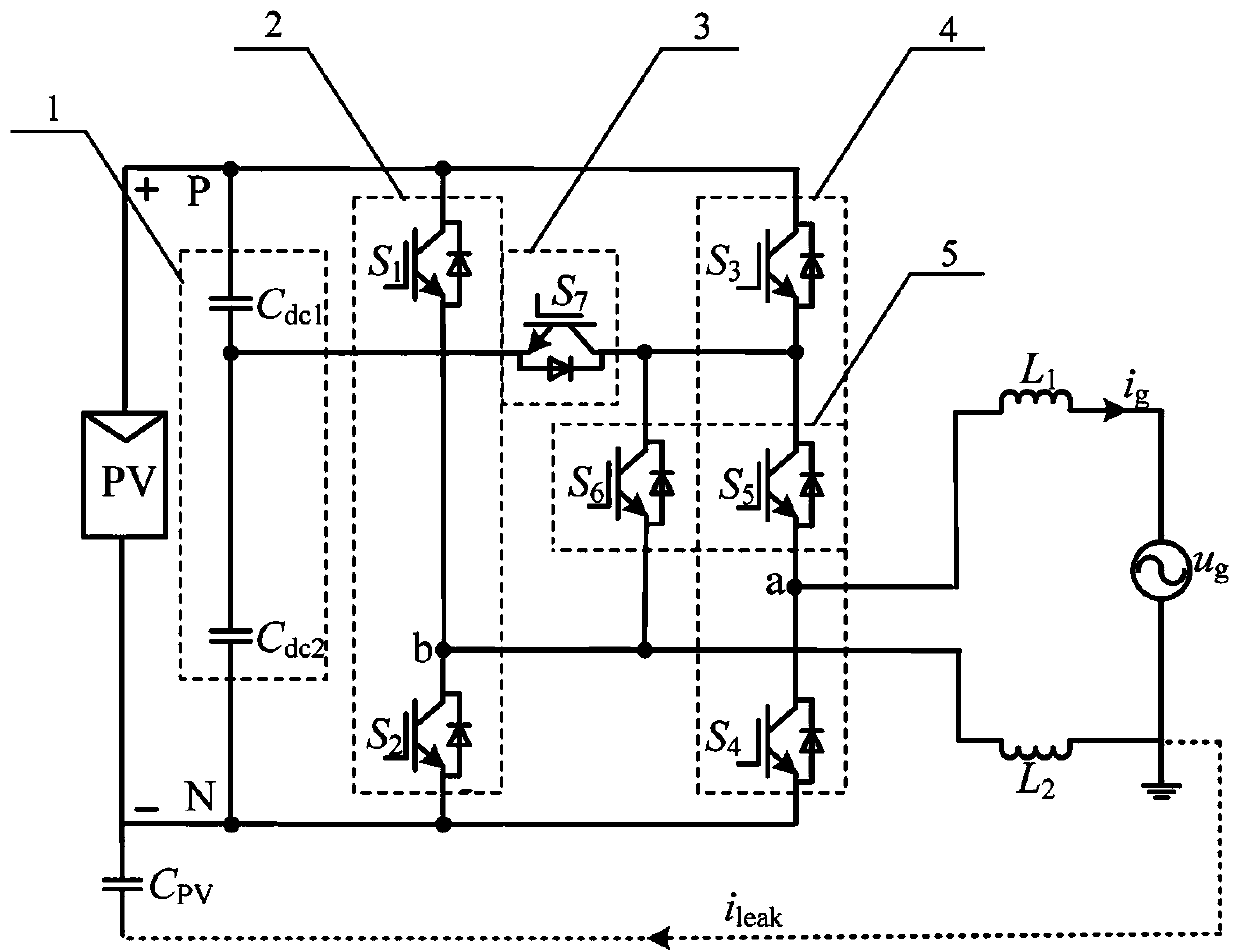

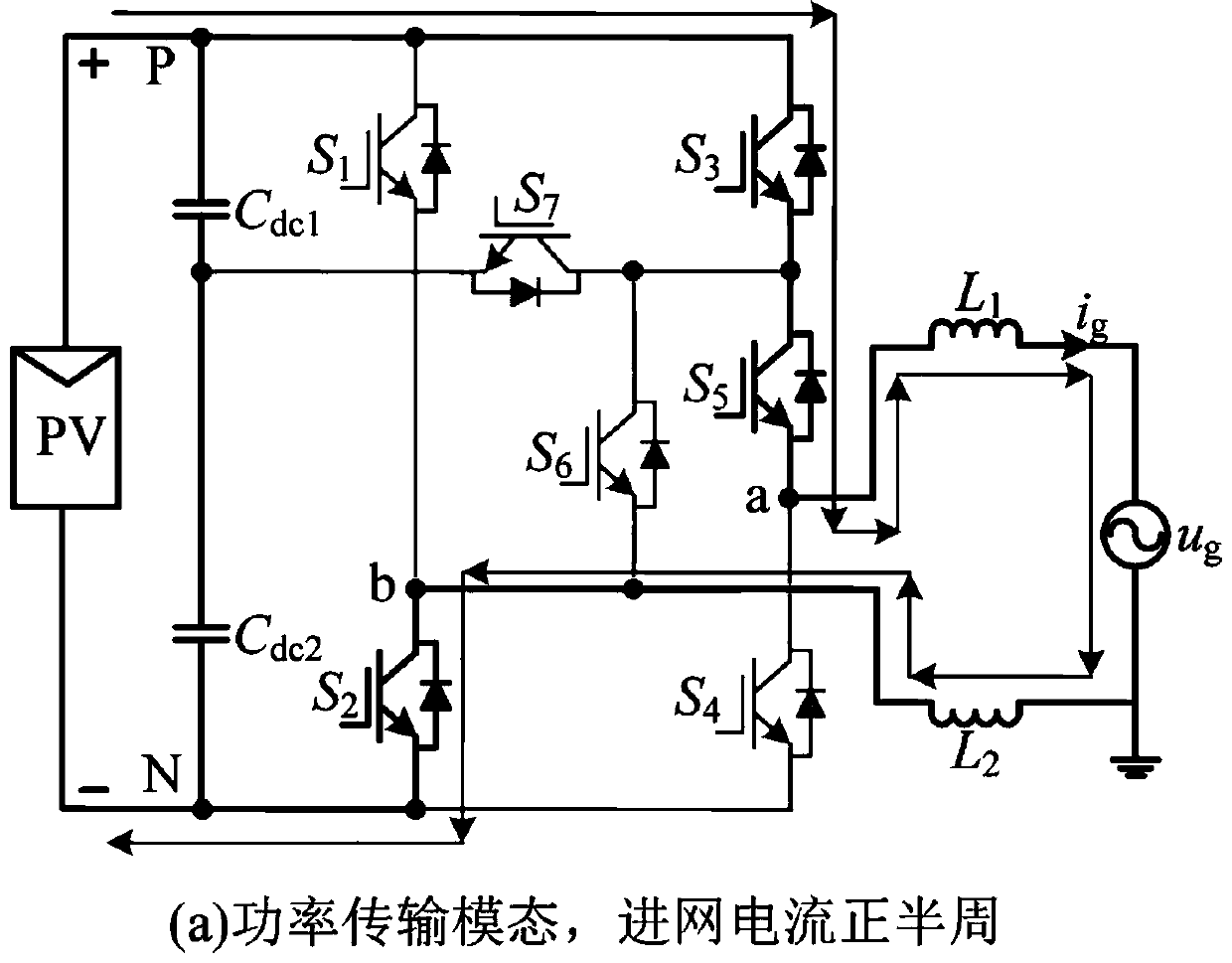

A new non-isolated five-level inverter

ActiveCN109167525ASolve leakage currentTroubleshoot voltage balance issuesAc-dc conversionSingle network parallel feeding arrangementsEngineeringBalance problems

The invention provides a novel non-isolated five-level inverter. The non-isolated five-level inverter includes: a first end of the first bridge arm circuit is connected with the positive electrode ofthe battery; a second end of the first bridge arm circuit is connected with the negative electrode of the battery; The first end of the second bridge arm circuit is connected with the positive electrode of the battery, and the second end of the second bridge arm circuit is connected with the negative electrode of the battery. The first freewheeling circuit is respectively connected with the firstbridge arm circuit and the connecting circuit, and the second freewheeling circuit is respectively connected with the second bridge arm circuit and the connecting circuit. After the first bridge arm circuit, the second bridge arm circuit, the first freewheeling circuit, the second freewheeling circuit and some switching devices in the connection circuit are turned on in each operation state, the current path formed can keep the common-mode voltage of the non-isolated five-level inverter constant. This embodiment solves the voltage balance problem of the clamping capacitor, thereby ensuring that the common-mode voltage of the non-isolated five-level inverter is constant.

Owner:HUNAN UNIV

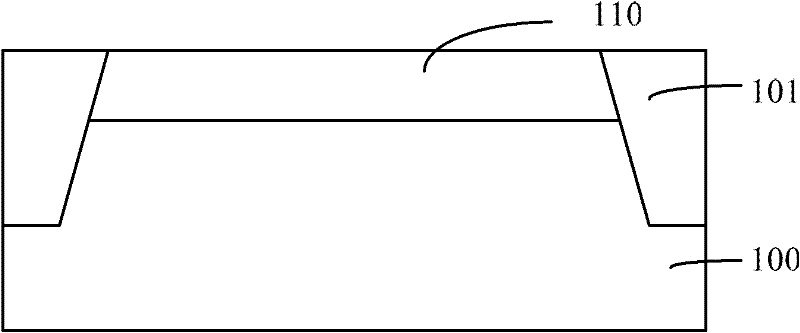

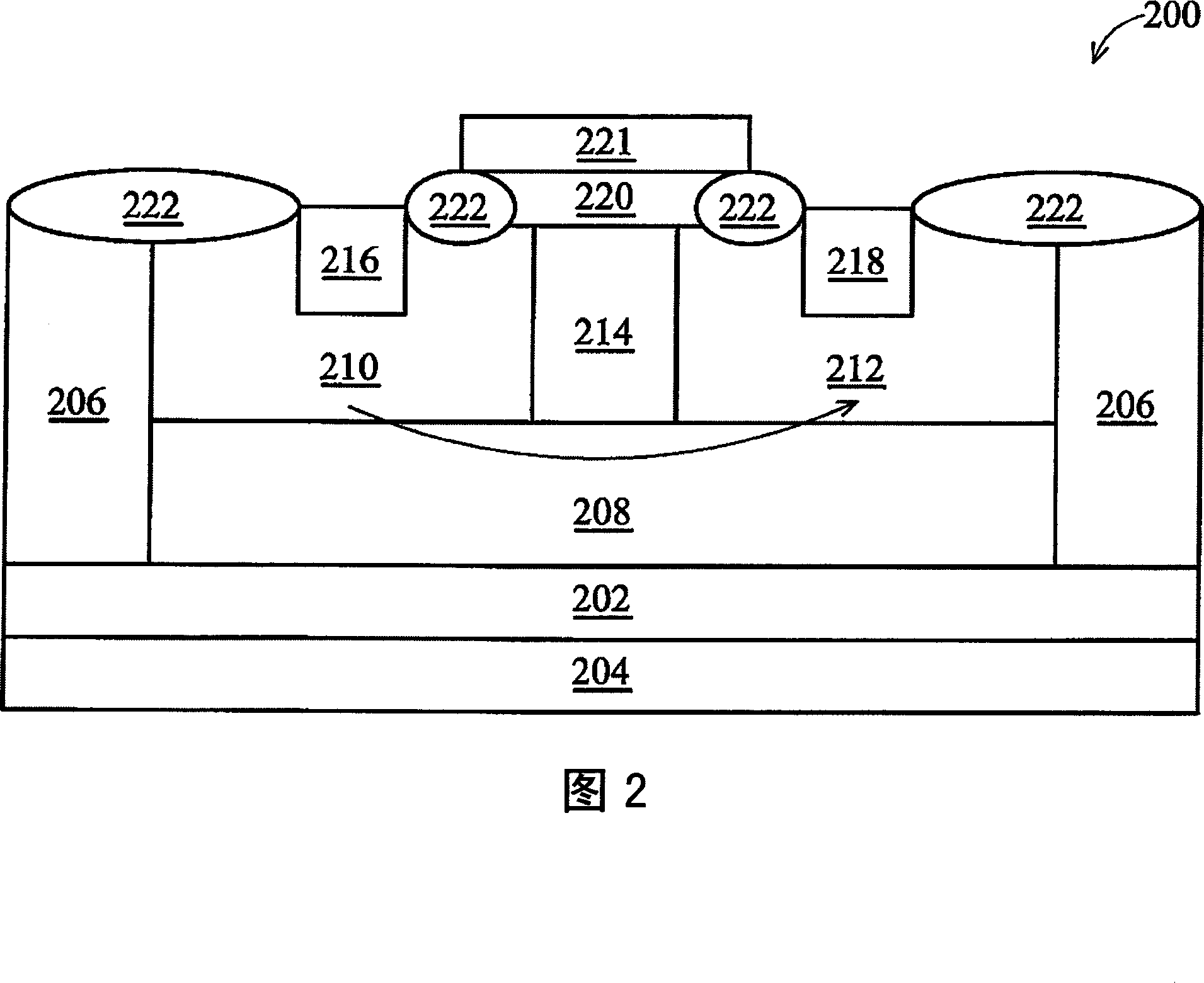

Metal oxide semiconductor device and forming method thereof

ActiveCN102544096AImprove mobilityImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricSemiconductor structure

The invention relates to a metal oxide semiconductor structure and a forming method thereof, in particular to the forming method of a complementary metal oxide semiconductor device. The forming method disclosed by the invention has the advantages that, (1) the performances of the semiconductor device are improved by forming a semiconductor layer which has different crystal orientation with a substrate on the surface of the substrate and improving carrier mobility by utilizing stress generated in the semiconductor layer with the different crystal orientation; (2) the carrier mobility is improved by forming the semiconductor layer which has the different crystal orientation with the substrate on the surface of the substrate, forming an NMOS (negative-channel metal oxide semiconductor) on the crystal surface of orientation (100) and forming a PMOS (positive-channel metal oxide semiconductor) on the crystal surface of orientation (110); (3) the leakage current problem in the conventional process is avoided by substituting a high-k gate dielectric for a traditional silicon dioxide gate dielectric; and (4) the forming method has simple process and low cost.

Owner:SEMICONDUCTOR MANUFACTURING INTERNATIONAL (BEIJING) CORP

Single-phase inverter

ActiveCN102545682AImprove output power qualityIncrease the equivalent switching frequencyAc-dc conversionPower qualityPower inverter

The invention discloses a single-phase inverter. The positive terminal of a direct current power supply is connected with the first end of a first switching tube; the second end of the first switching tube is connected with the negative terminal of the direct current power supply through a second switching tube, a third switching tube and a fourth switching tube which are sequentially connected in series; the second end of the first switching tube is connected with the negative terminal of the direct current power supply through a fifth switching tube, a sixth switching tube and a seventh switching tube which are sequentially connected in series; a first clamping diode is connected between the common terminal of the third switching tube and the fourth switching tube and the common terminal of the fifth switching tube and the sixth switching tube; a second clamping diode is connected between the common terminal of the sixth switching tube and the seventh switching tube and the common terminal of the second switching tube and the third switching tube; an alternating current load is connected between the common terminal of the second switching tube and the third switching tube and the common terminal of the fifth switching tube and the sixth switching tube; and the second switching tube is reversely connected in parallel with a second diode, and the fifth switching tube is reversely connected with a fifth diode. The single-phase inverter provided by the embodiment of the invention can be used for improving the quality of output electric energy of the inverter.

Owner:SUNGROW POWER SUPPLY CO LTD

Single-phase inverter

ActiveCN102570878AImprove output power qualityIncrease the equivalent switching frequencyEfficient power electronics conversionReactive power adjustment/elimination/compensationPower qualitySingle phase

The invention discloses a single-phase inverter, which comprises seven switching tubes. The positive end of a direct current power supply is connected with the negative end of the direct current power supply through a first switching tube, a second switching tube, a seventh switching tube and a fourth switching tube, which are sequentially connected in series. The positive end of the direct current power supply is connected with the negative end of the direct current power supply through a fifth switching tube, a sixth switching tube, a third switching tube and the fourth switching tube, which are sequentially connected in series. A first clamping diode is connected between the second end of the sixth switching tube and the second end of the first switching tube. A second clamping diode is connected between the second end of the second switching tube and the second end of the fifth switching tube. The second end of the second switching tube and the second end of the sixth switching tube are the alternating current ends of the single-phase inverter. The third switching tube is reversely connected in parallel with a third diode. The seventh switching tube is reversely connected in parallel with a seventh diode. According to the single-phase inverter in the embodiment of the invention, the quality of electric energy output by the inverter can be improved.

Owner:SUNGROW POWER SUPPLY CO LTD

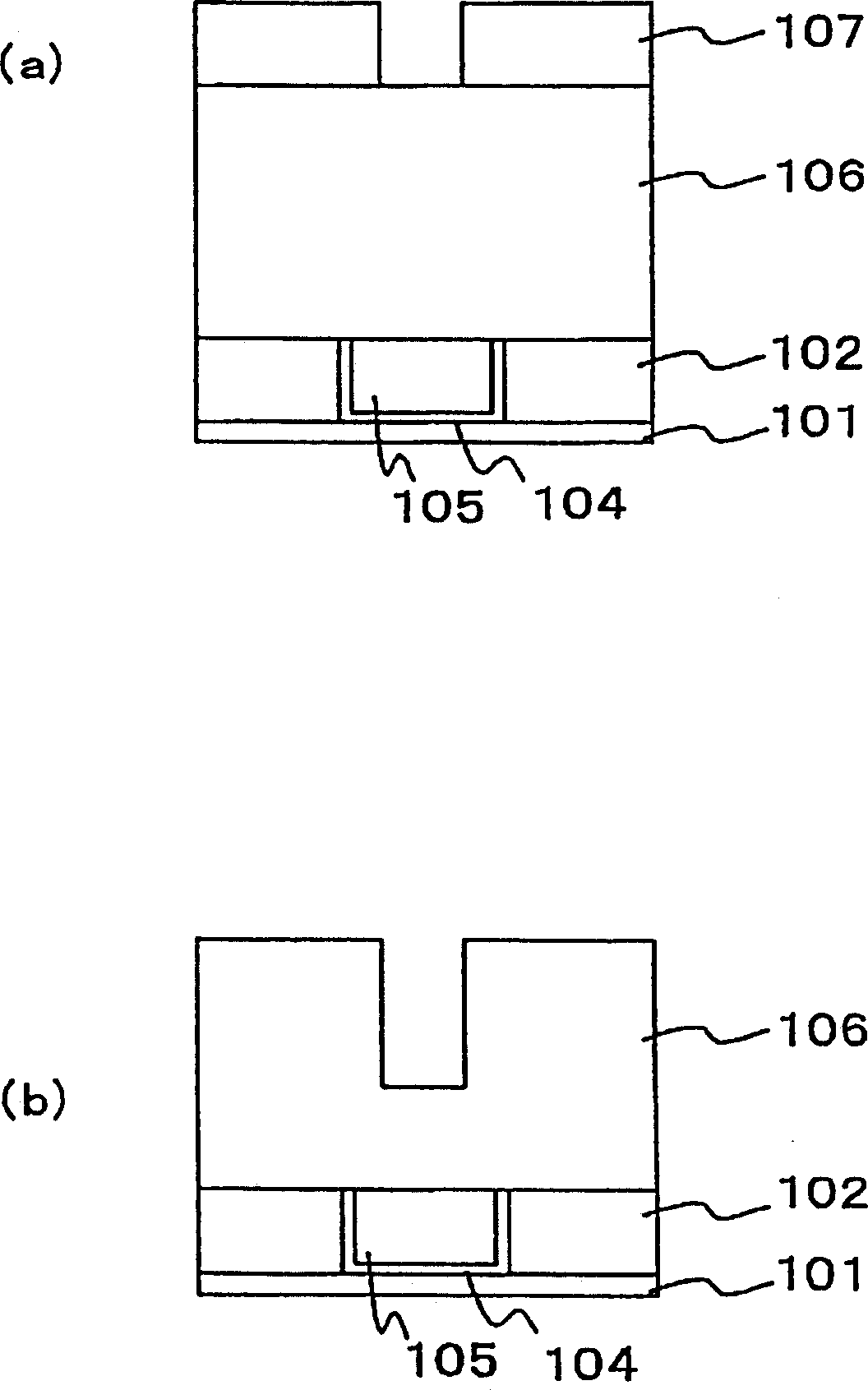

Non-volatile memory, its production and operation

InactiveCN1855499ASolve leakage currentImprove reliabilityTransistorSolid-state devicesGate stackEngineering

The well region of the non-volatile memory cell is formed at a substrate. A shallow well region is formed at said well region. At least two gate stacks are located on the substrate. The drain region is formed in the gate stack proximate the outer edge of said shallow well. The auxiliary gate layer is formed on the substrate between said two gate stacks, and passes through partial substrate. The dielectric layer is formed between said dielectric layer and substrate and between said auxiliary gate layer and gate stacks. The conducting plug is formed on said substrate, and extended down to said shallow well and said drain region therein.

Owner:POWERCHIP SEMICON CORP

Semiconductor structure and its forming method, transverse diffusion p-type mos device

ActiveCN1967870ASolve leakage currentTransistorSolid-state devicesSemiconductor structureMaterials science

The present invention discloses a semiconductor structure. A buried layer of a first polarity type is constructed on a semiconductor substrate. A first epitaxial layer of a second polarity type is formed on the buried layer. A second epitaxial layer of the second polarity type is formed on the buried layer. An isolation structure of the first polarity type is formed between the first and second epitaxial layers on the buried layer. A first well of the second polarity type is formed on the first epitaxial layer. A second well of the second polarity type is formed on the second epitaxial layer. A third well of the first polarity type is formed between the first and second wells, on the isolation structure. The isolation structure interfaces with the buried layer and the third well, thereby substantially blocking a leakage current path between the first and the second wells.

Owner:TAIWAN SEMICON MFG CO LTD

Encapsulation method for chip fan-out encapsulation structure

InactiveCN103489790ASimple processReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingDielectric layerElectrical and Electronics engineering

The invention relates to an encapsulation method for a chip fan-out encapsulation structure. The encapsulation method includes the following steps that S1, a chip assembly is provided and comprises a chip and a plastic package shell encapsulated on the chip, the chip comprises a first surface, a second surface and an electrode bonding pad, the first surface and the second surface are oppositely arranged, the electrode bonding pad is exposed outwards from the second surface, the plastic package shell at least encapsulates the first surface, and the electrode bonding pad is not encapsulated by the plastic package shell; S3, a substrate ink line is formed and provided with an electrical connecting end connected with the electrode bonding pad; S4, a first thin film dielectric layer is formed, covers the substrate ink line and is provided with a first opening part enabling the substrate ink line to be partially exposed. Ink leading is adopted in the encapsulation method, so chip encapsulation is achieved. Compared with the prior art, the encapsulation method has the advantages of being simple in process, low in manufacturing cost and short in production cycle and protecting the environment, and meanwhile the problem of current leakage can be solved.

Owner:GERAD TECH SUZHOU

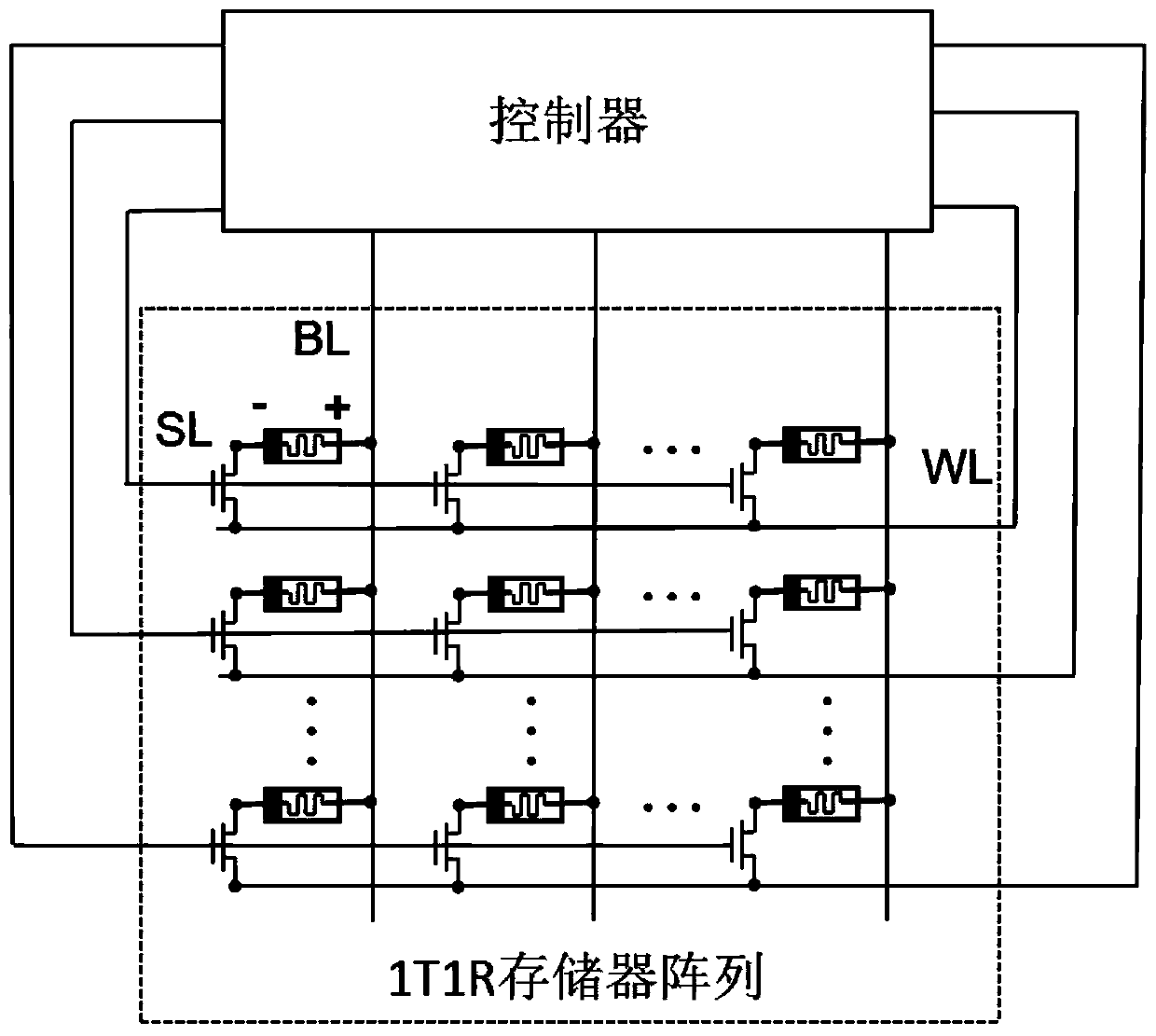

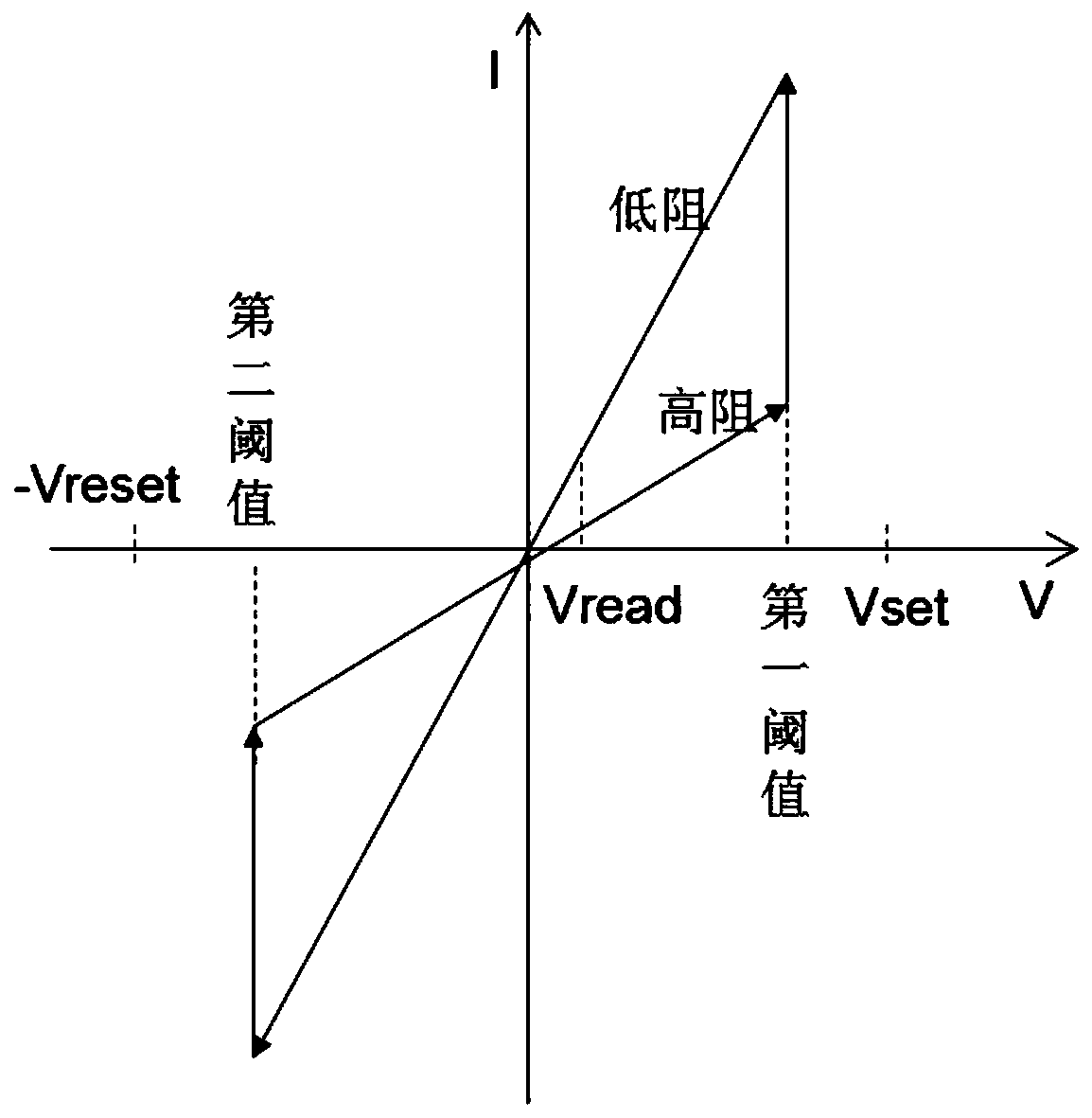

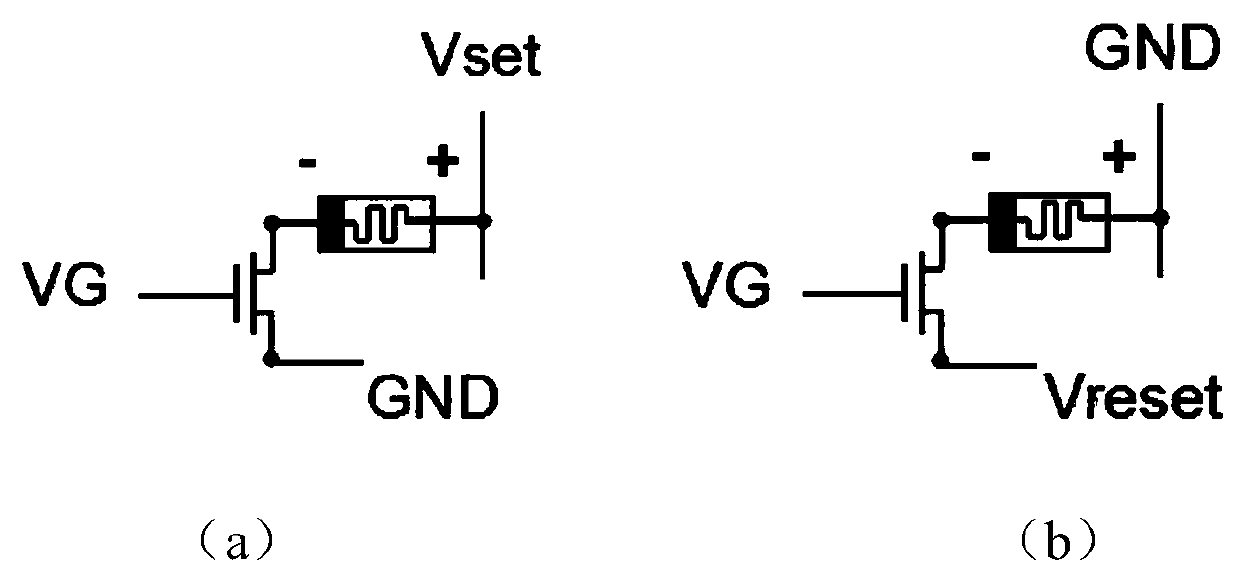

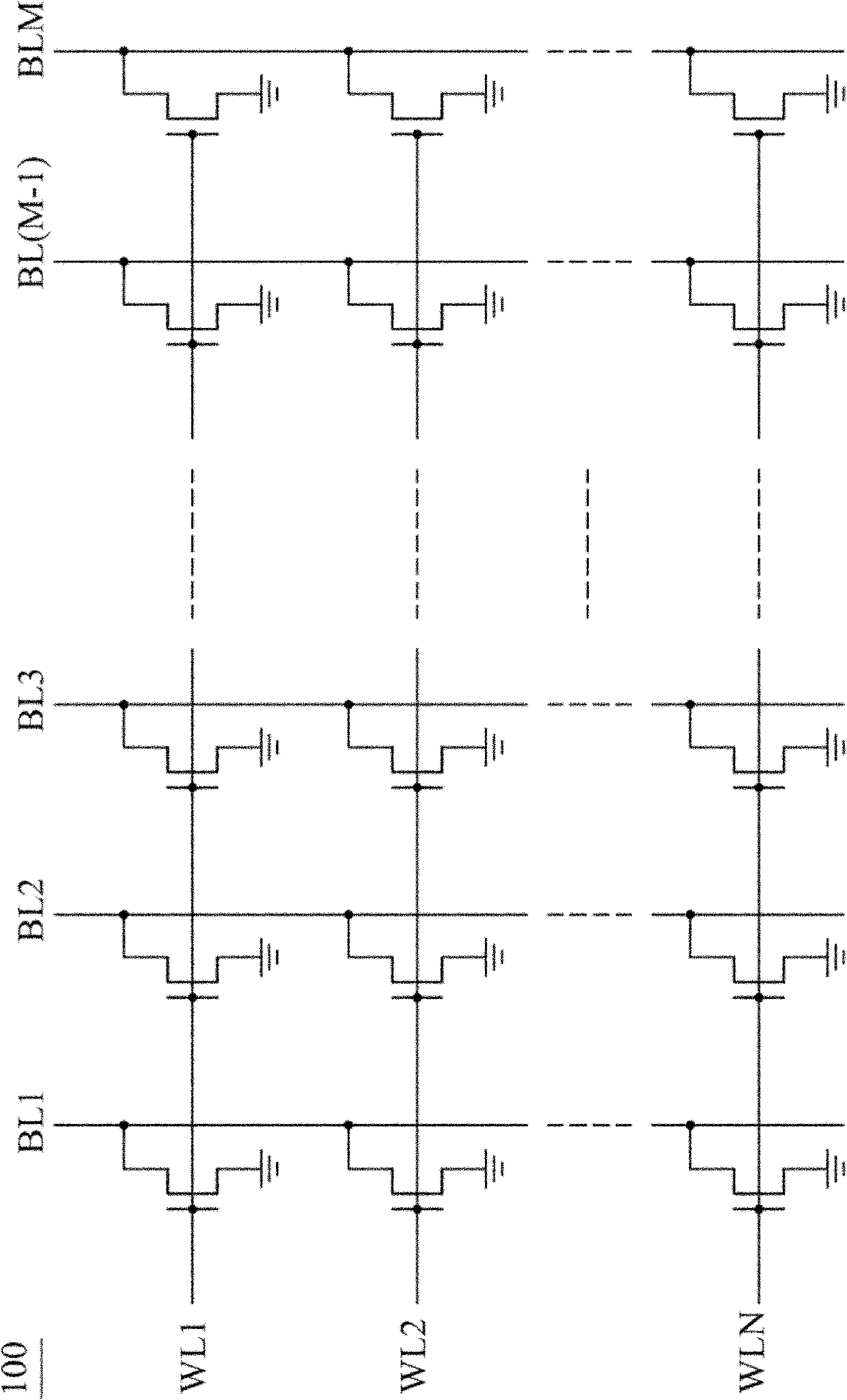

Convolution calculation accelerator based on 1T1R memory array and operation method of convolution calculation accelerator

ActiveCN110569962ASolve leakage currentResolution delay is largeNeural architecturesPhysical realisationParallel computingComputation process

The invention discloses a convolution calculation accelerator based on a 1T1R memory array and an operation method of the convolution calculation accelerator, the convolution calculation accelerator adopts a 1T1R memory array structure, and the problem of leakage current in the array is solved; different voltages are input into a word line, a bit line and a selection line of a 1T1R memory array according to input numbers for convolution operation, AND logic operation and total current reading are achieved, multiplication and addition operation steps in convolution operation are completed, andtherefore convolution operation is achieved, and the calculation process is simplified. According to the method, the binary multiplication operation is realized in parallel, the multiplication operation of all data of the convolution kernel is completed in one step, and the operation result can be read in parallel, so that the processing efficiency is greatly improved. In addition, by adopting the1T1R memory array, the fusion of storage and calculation is realized, the energy consumption and the calculation time are greatly saved, and the problem of relatively large delay caused by separationof storage and calculation in a calculation architecture in the prior art is solved.

Owner:HUAZHONG UNIV OF SCI & TECH

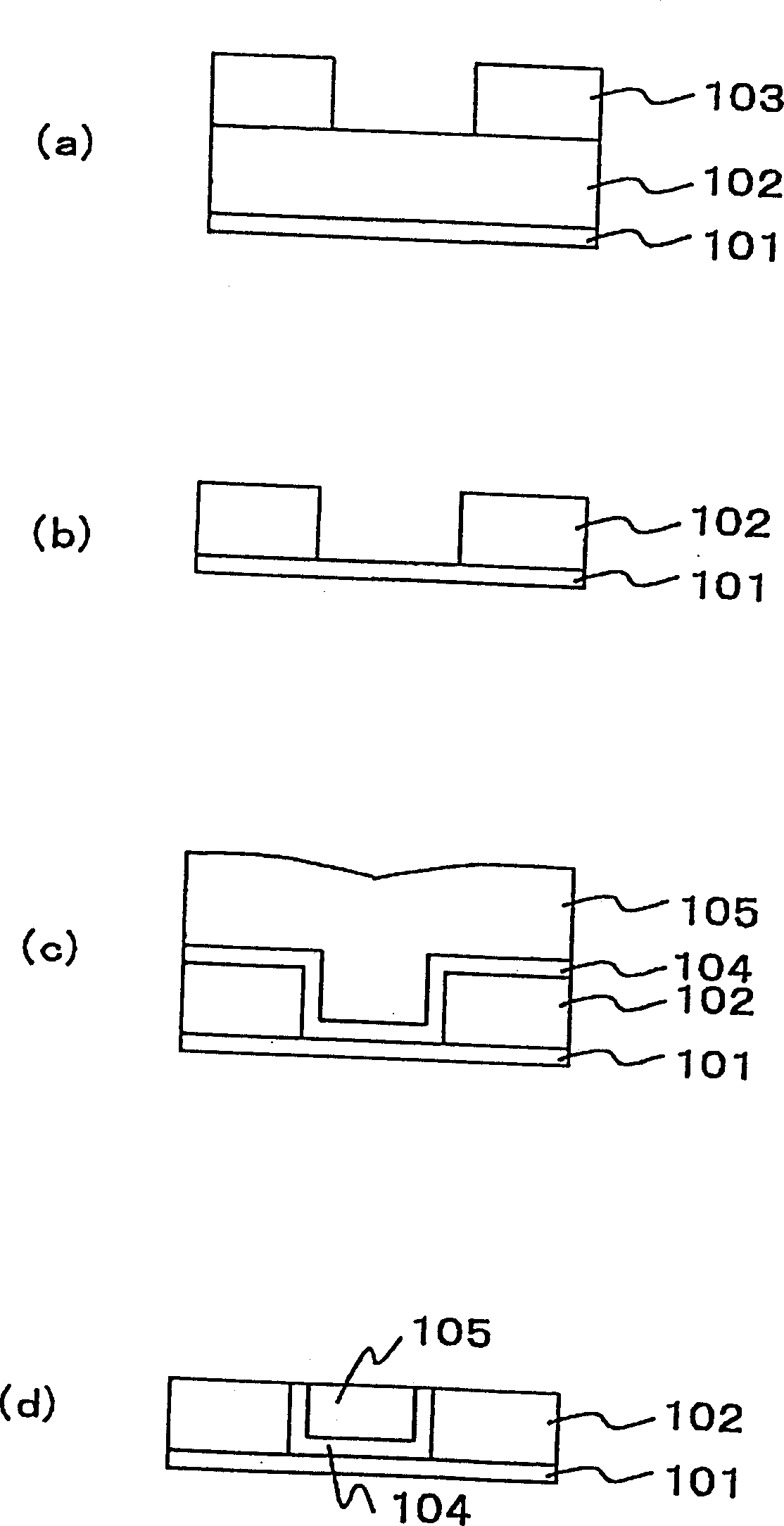

Method for producing semiconductor apparatus

InactiveCN1181532CEfficient removalSolve leakage currentSemiconductor/solid-state device detailsSolid-state devicesInterconnectionEngineering

In a method of manufacturing a semiconductor device having a multi-layer interconnection, after a via hole has been formed, the inside of the via hole is cleaned using a cleaning solution containing a complexing agent capable of forming a complex with contaminants of copper type metals.

Owner:RENESAS ELECTRONICS CORP

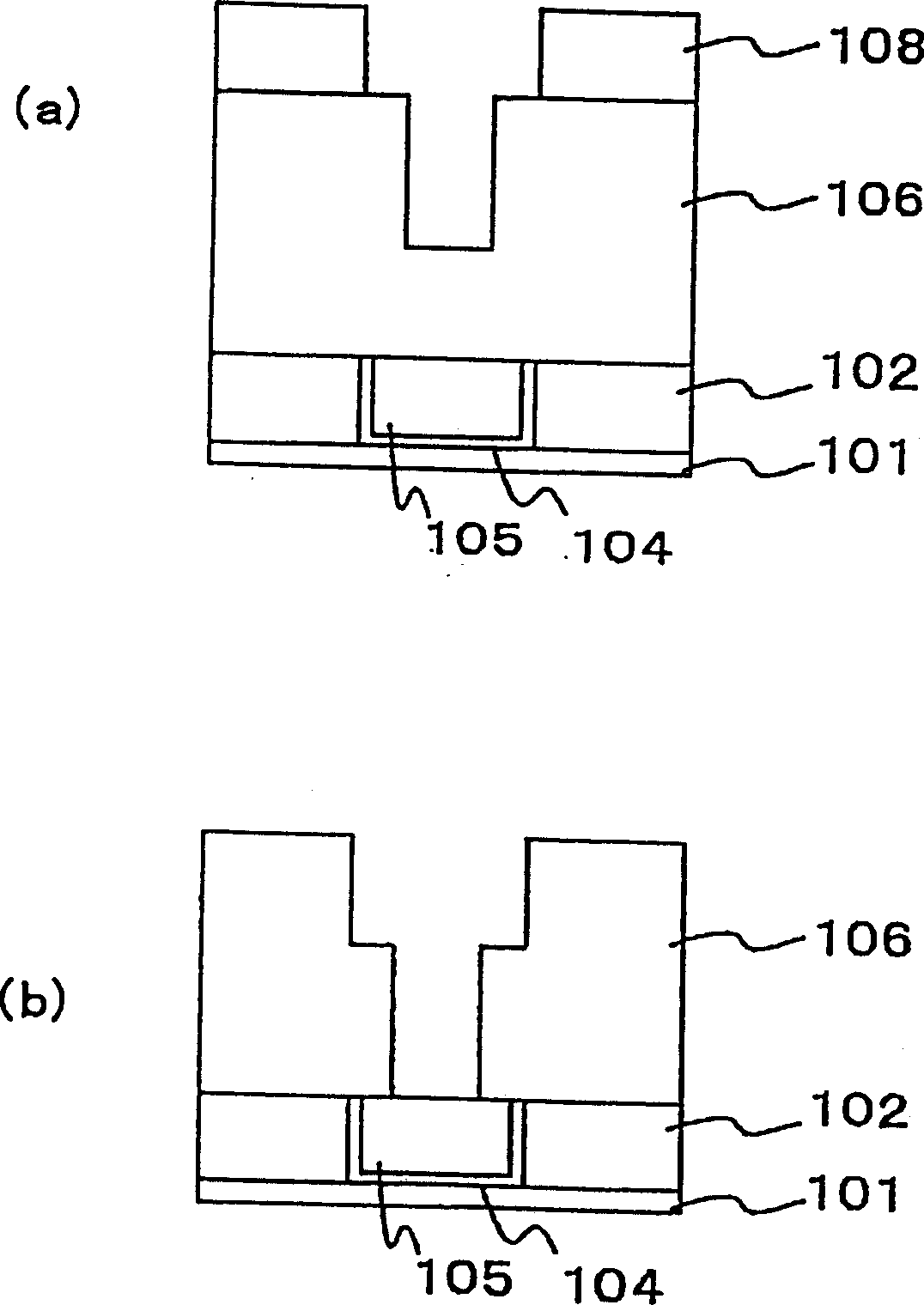

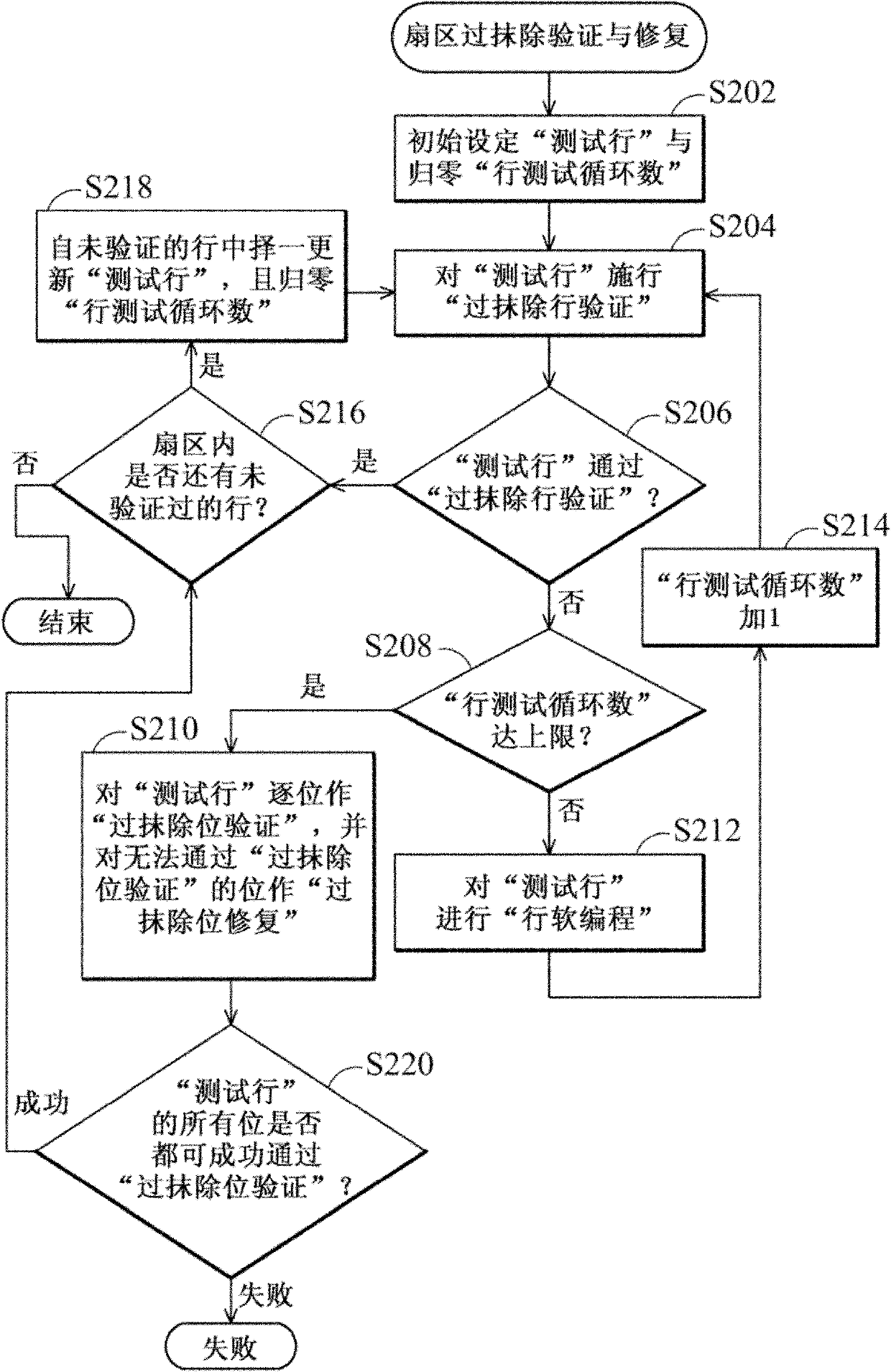

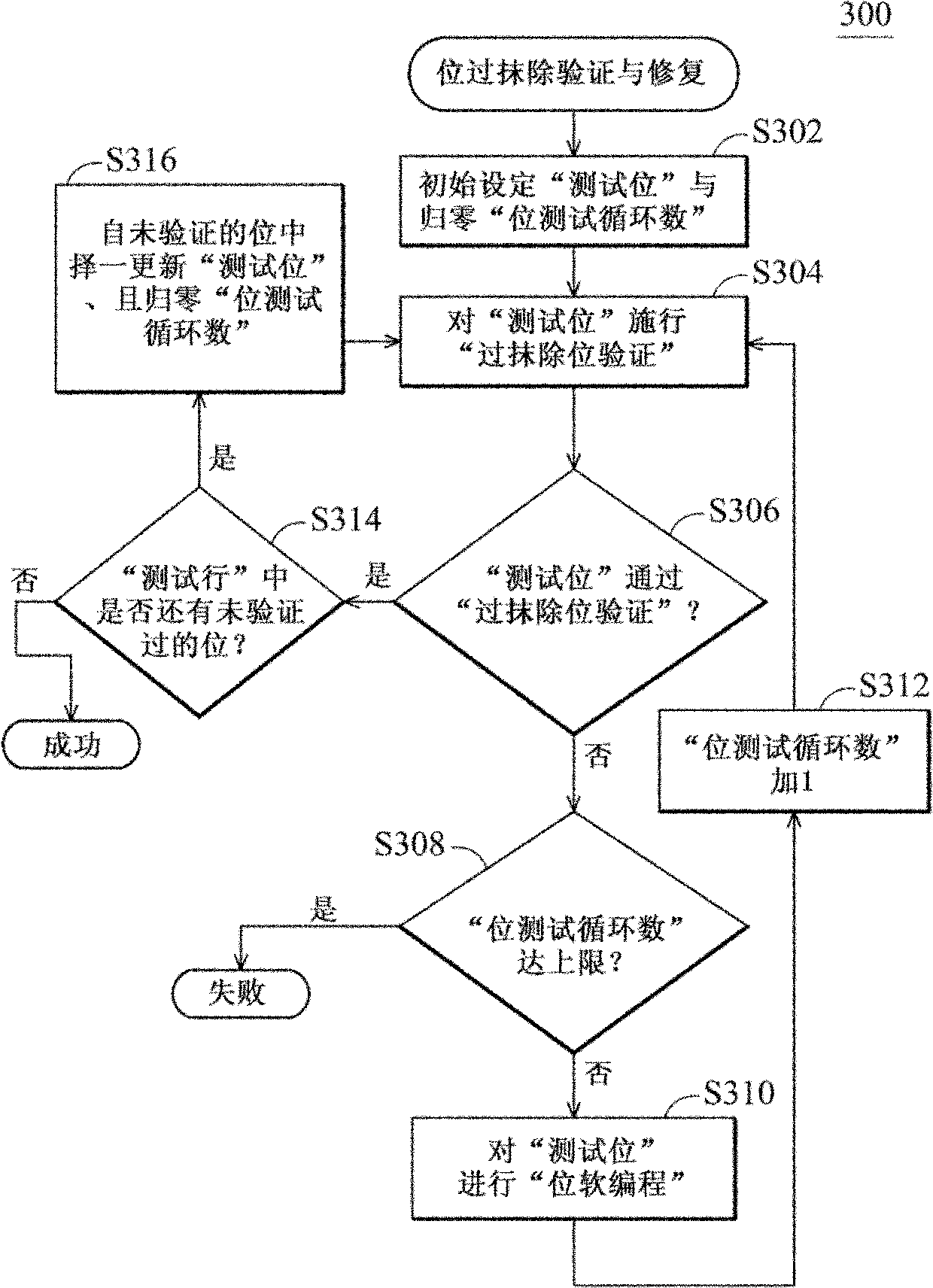

NOR type stack flash and over-erased verification and restoration method thereof

The invention discloses an NOR type stack flash and an over-erased verification and restoration method thereof. A sector of the NOR type stack flash is applied with over-erased column verification by the method for each column, and columns which cannot pass through the over-erased column verification undergo over-erased column restoration. Additionally, the columns which cannot pass through the over-erased column restoration and pass through the over-erased column verification are applied with over-erased bit verification for each bit, and bits which cannot pass through the over-erased bit verification undergo over-erased bit restoration. The NOR type stack flash and the over-erased verification and restoration method in the embodiment of the invention can solve a current leakage problem generated by over erase.

Owner:WINBOND ELECTRONICS CORP

Single-phase inverter

InactiveCN102427303AImprove output power qualityIncrease the equivalent switching frequencyDc-ac conversion without reversalPower inverterPower quality

Embodiments of the invention provide a single-phase inverter. The single-phase inverter is characterized in that: a positive terminal of a direct current power supply is connected with a negative terminal of the direct current power supply through a first, a second, a seventh and an eighth switch tubes, wherein the first, the second, the seventh and the eighth switch tubes are connected in series successively; the positive terminal of the direct current power supply is connected with the negative terminal of the direct current power supply through a fifth, a sixth, a third and a fourth switch tubes, wherein the fifth, the sixth, the third and the fourth switch tubes are connected in series successively; a second terminal of the first switch tube forms a short circuit with the second terminal of the fifth switch tube; the second terminal of the third switch tube forms the short circuit with the second terminal of the seventh switch tube; the second terminal of the second switch tube and the second terminal of the sixth switch tube are an alternating-current output terminal of the single-phase inverter; the second switch tube is parallelly connected with a second diode in a reverse direction; the third switch tube is parallelly connected with a third diode in the reverse direction; the sixth switch tube is parallelly connected with a sixth diode in the reverse direction; the seventh switch tube is parallelly connected with a seventh diode in the reverse direction. By using the single-phase inverter in the embodiments of the invention, an output power quality of the inverter can be increased.

Owner:SUNGROW POWER SUPPLY CO LTD

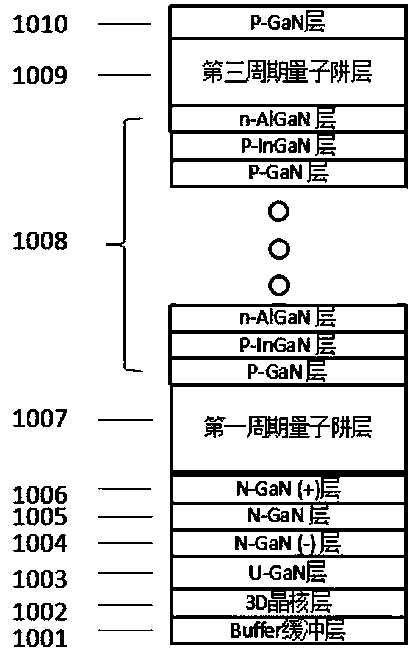

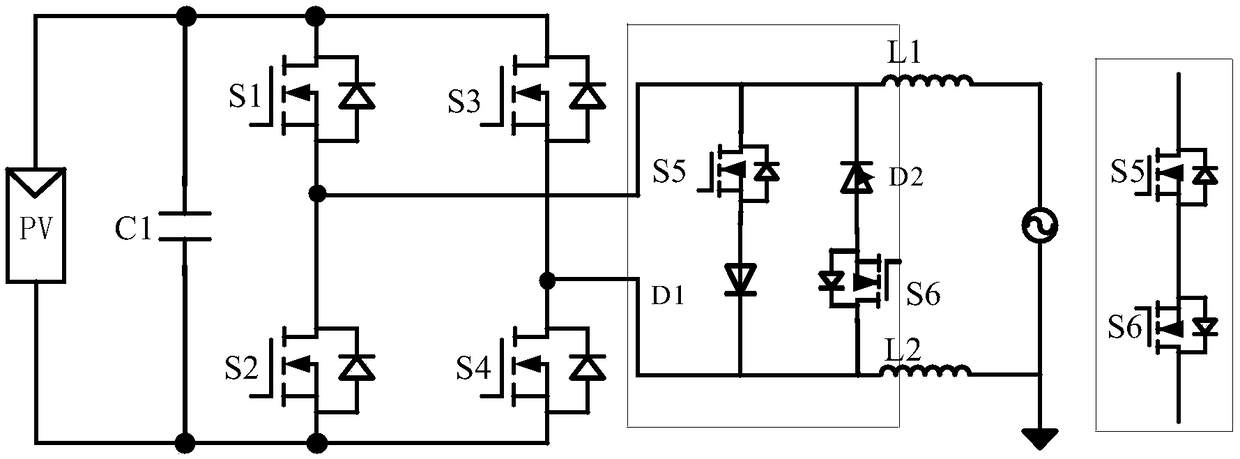

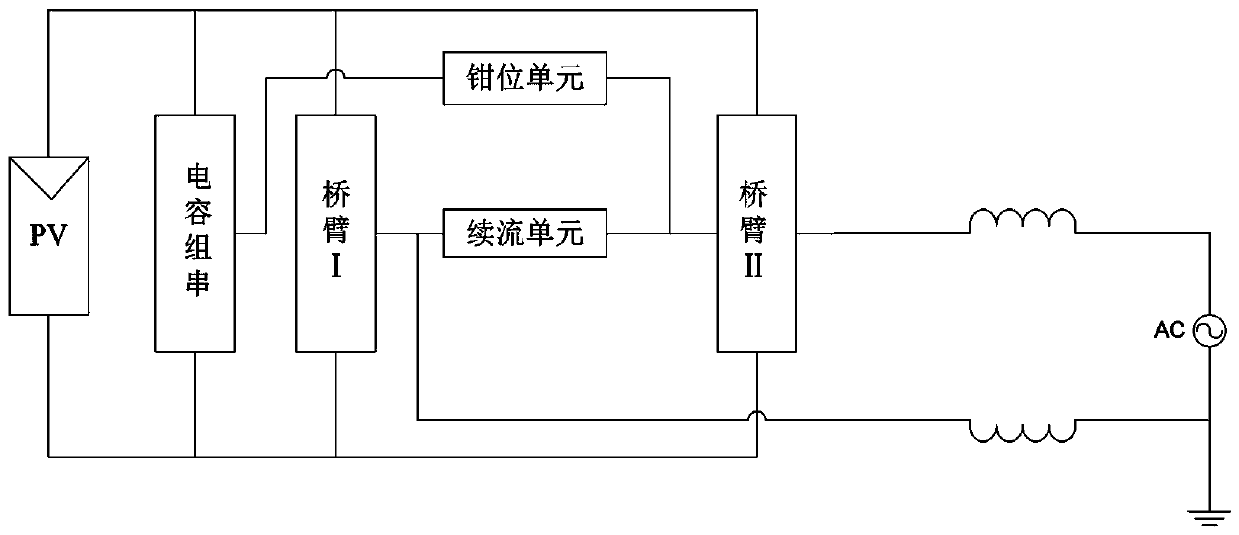

Non-isolated intermediate-point clamping photovoltaic grid connected inverter and modulation method thereof

ActiveCN110011556ASolve leakage currentCapability to suppress leakage currentAc-dc conversionSingle network parallel feeding arrangementsCapacitanceGrid connected inverter

The invention provides a non-isolated intermediate-point clamping photovoltaic grid connected inverter and a modulation method thereof. The non-isolated intermediate-point clamping photovoltaic grid connected inverter is arranged between a photovoltaic array output unit and an AC power grid, and comprises a capacitor bank, a clamping unit, a freewheeling unit and first and second legs; the first leg is in parallel connection with the capacitor bank, second leg and photovoltaic array output unit; the positive end of the clamping unit is connected with the freewheeling unit and the second leg, and the negative end of the clamping unit is connected to the intermediate point of the capacitor bank; one end of the freewheeling unit is connected with the positive end of the clamping unit, and theother end of the freewheeling unit is connected with the intermediate point of the first leg; and a point a of the first leg and a point b of the second leg form an AC voltage output end of the non-isolated intermediate-point clamping photovoltaic grid connected inverter. Thus, common-mode voltage oscillation caused by a switch junction capacitance parameter can be eliminated, and common-mode grounding leakage current caused by the switch junction capacitor is inhibited effectively.

Owner:ZHENGZHOU UNIV

Double-gate graphene transistor with silicon substrate and aluminium oxide gate dielectric, and preparation method

ActiveCN103811556ALarge physical thicknessSolve leakage currentTransistorSemiconductor/solid-state device manufacturingCarbon filmGate dielectric

The invention discloses a double-gate graphene transistor with a silicon substrate and an aluminium oxide gate dielectric, and a preparation method, which are mainly used for solving the problems of low channel carrier mobility and carrier scattering of a graphene transistor prepared by the prior art. The preparation method comprises the following realization steps of: depositing a layer of Al2O3 on an epitaxial 3C-SiC surface on a Si substrate, and photoetching a double-gate graph; placing the etched sample in a quartz tube, generating a carbon film by reacting Cl2 with SiC, then placing the carbon film sample in Ar gas and annealing to generate graphene; etching off Al2O3 at the both sides of the graphene sample and 60-400 nm away from a conductive channel to form a double-gate groove; finally depositing a metal layer on the graphene sample and etching to form transistor metal contact. The double-gate graphene transistor provided by the preparation method disclosed by the invention has the advantages of being high in carrier mobility, good in scattering effect suppression performance, and capable of regulating a channel carrier concentration, as well as can be used for producing a large-scale integrated circuit.

Owner:XIDIAN UNIV

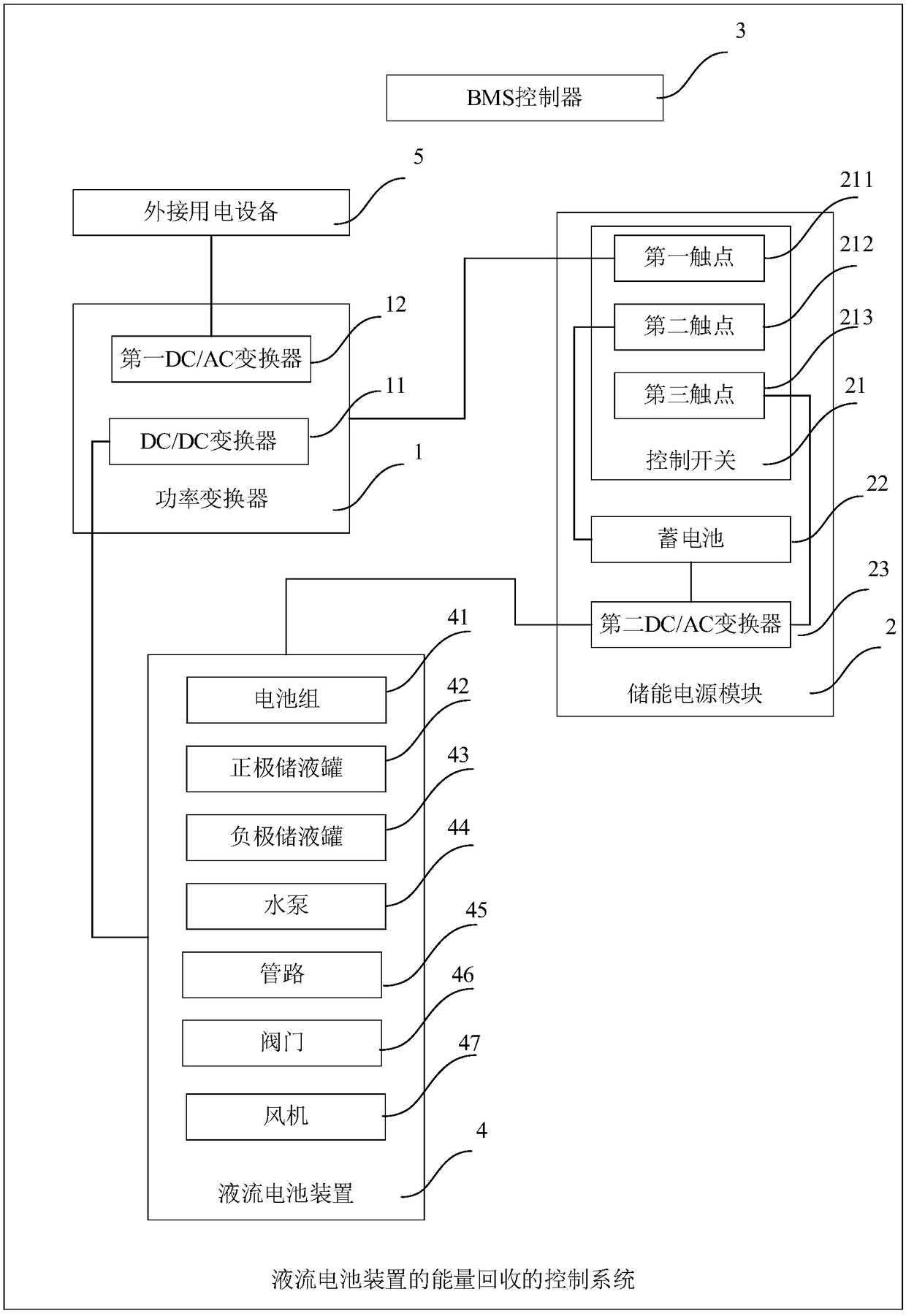

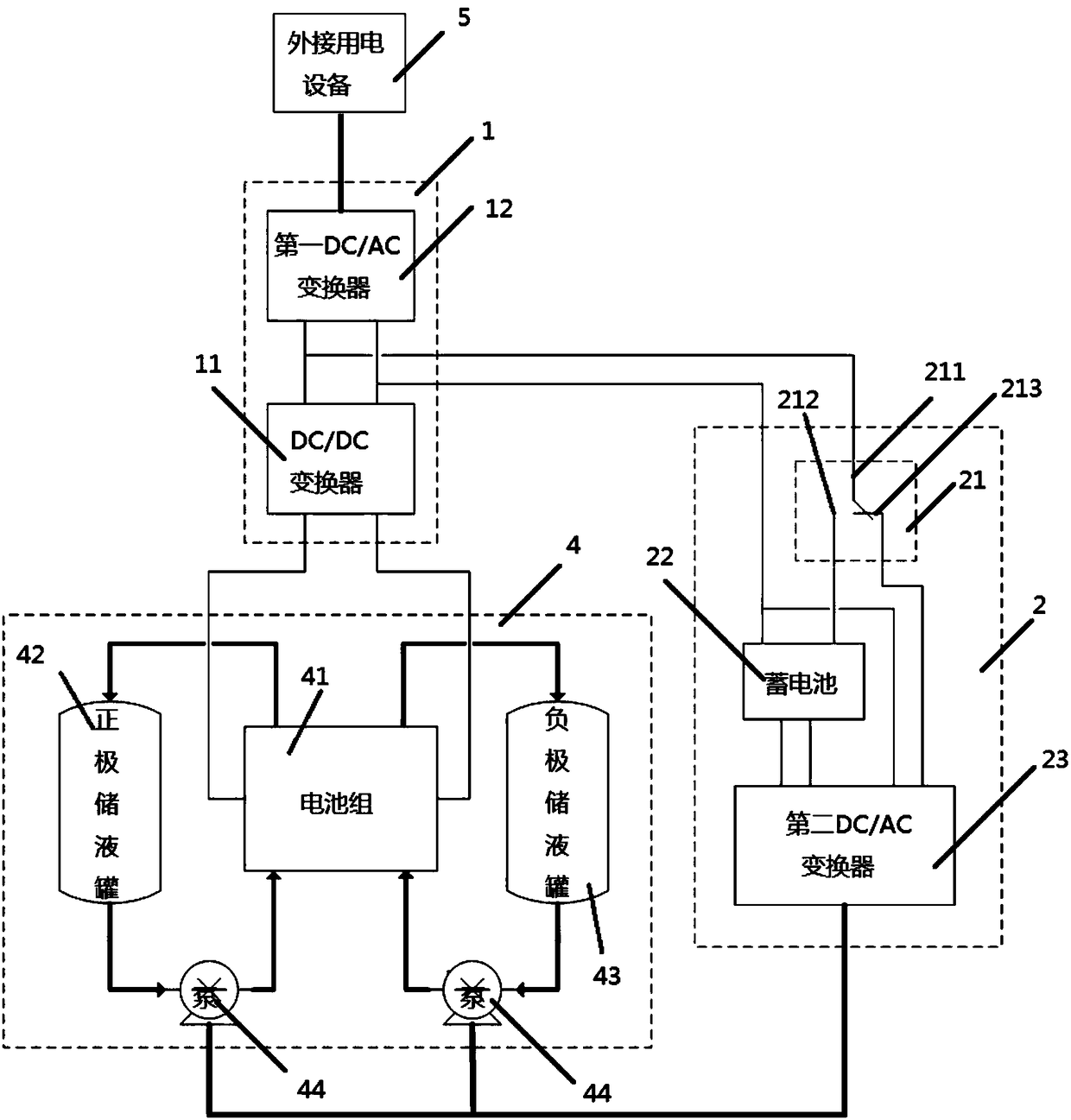

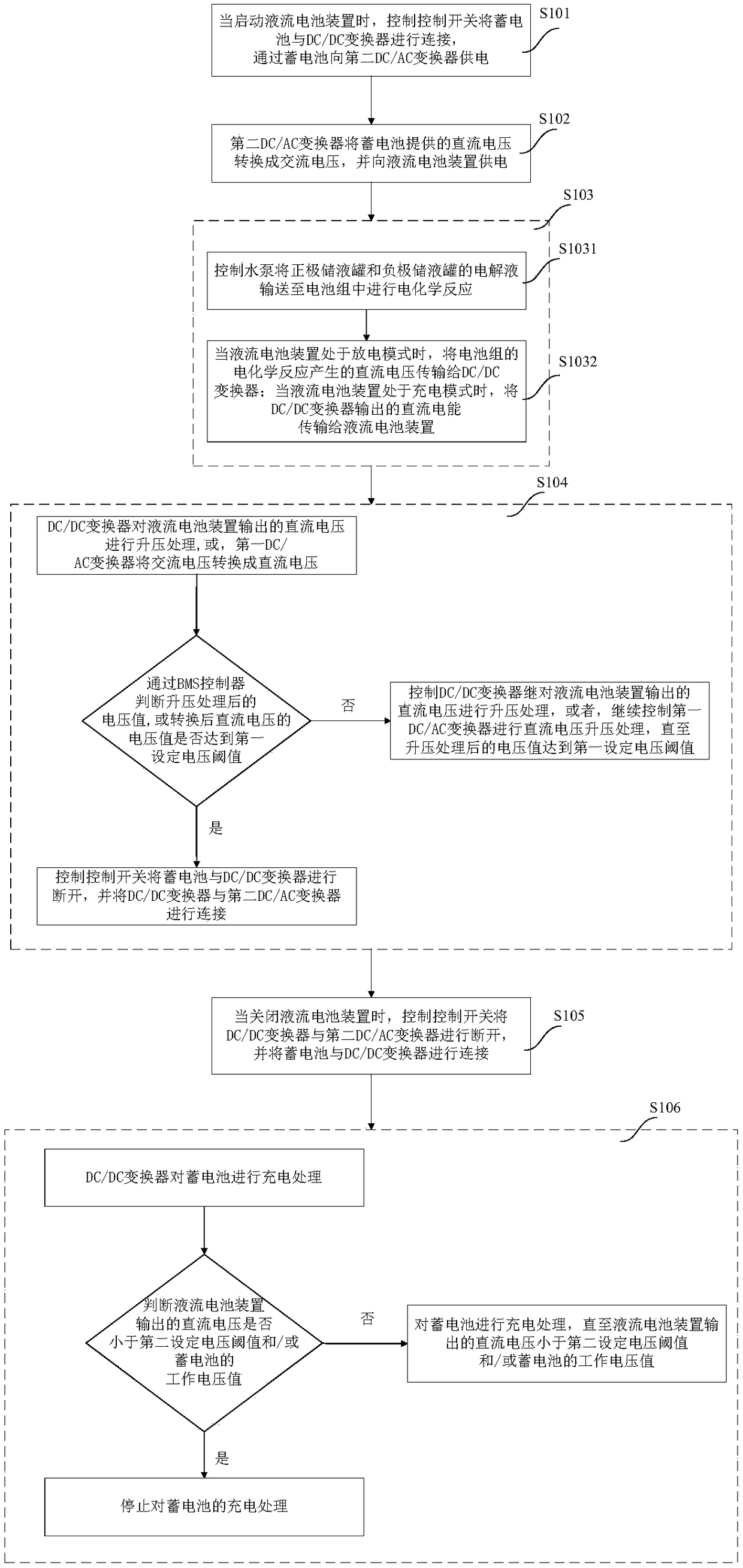

Control system and method for energy recovery of flow battery device

ActiveCN108110826ASolve leakage currentAvoid defectsReactant parameters controlRegenerative fuel cellsControl systemEnergy recovery

The invention discloses a control system and method for energy recovery of a flow battery device. The control system comprises a power converter, an energy storage power supply module and a BMS controller. The power converter is used for boosting a DC voltage outputted by a flow battery device and supplying power to an external device. The BMS controller is used for switching the working mode of the energy storage power supply module. The energy storage power supply module is used for self-charging, and also supplies power to the flow battery device. The control system and method of the invention complete the recovery of the remaining energy in a battery pack, and solve the leakage current problem existing in the existing flow battery device; and can achieve the continuous operation of theflow battery device through a storage battery when the flow battery device is stopped and achieve the black start of the flow battery device through the storage battery when the flow battery device is in a shutdown state, and overcome the defects of a plurality of modules included in the power supply module in the existing flow battery device, thereby reducing the equipment size and reducing theinvestment cost.

Owner:SHANGHAI ELECTRICGROUP CORP

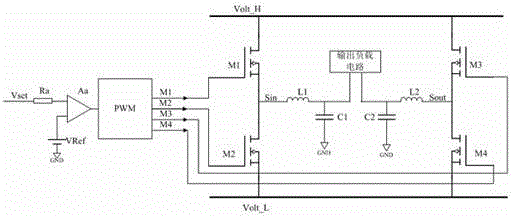

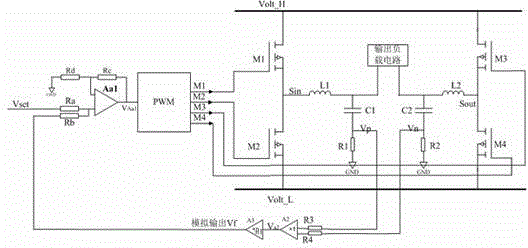

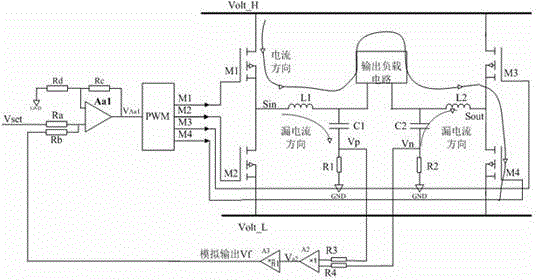

Motor drive circuit eliminating output leakage current

The invention discloses a drive circuit sampling and amplifying a leakage current measured by a measuring circuit and passing through a C (capacitor) in an LC filter circuit and further sending the leakage current signal to a pre-stage Vset circuit in a feedback way. The motor drive circuit eliminating an output leakage current comprises a pre-stage input circuit, a PWM output circuit, a rectifying circuit, an output filter circuit and a feedback circuit which are sequentially connected. The feedback circuit is arranged between the output filter circuit and the pre-stage input circuit. The feedback circuit which comprises a leakage current sampling circuit and a signal amplifying circuit is used for sampling the leakage current of the output filter circuit and further sending the leakage current to the pre-stage input circuit as feedback.

Owner:SHANGHAI MICRO ELECTRONICS EQUIP (GRP) CO LTD