Encapsulation method for chip fan-out encapsulation structure

A packaging method and packaging structure technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of long preparation period, difficult metal corrosion, high pollution, etc., and achieve the problem of leakage current and production cycle. The effect of environmental protection and short production cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

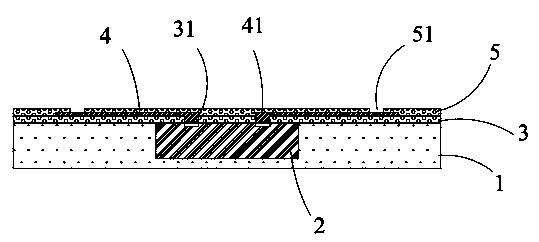

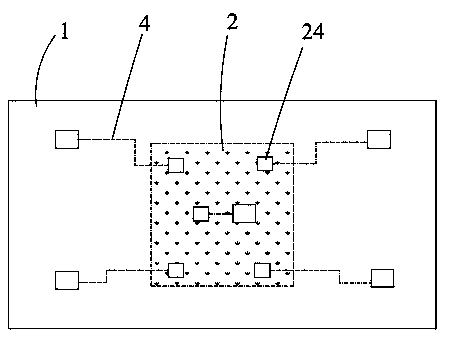

[0038] See Figures 1 to 3 The chip fan-out packaging structure in an embodiment of the present invention includes a chip 2, a plastic casing 1 encapsulated on the chip 2, a second insulating medium layer 3 arranged on the chip 2 and the plastic casing 1, and a second insulating medium layer 3 arranged on the second Several ink traces 4 on the second insulating medium layer 3 , and a first insulating medium layer 5 arranged on the ink traces 4 . The above-mentioned parts and the interrelationships between the parts will be described in detail below.

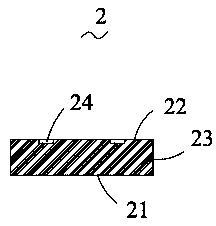

[0039] The chip 2 has a first surface 21 and a second surface 22 opposite to each other, a third surface 23 connecting the first surface 21 and the second surface 22 , and an electrode pad 24 exposed from the second surface 22 . The chip 2 can also be replaced by a combination (not shown) of a chip and passive components.

[0040] The plastic package 1 is encapsulated on the first surface 21 and the third surface 23 of the chip...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More