Patents

Literature

54results about How to "Increase capacitor area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

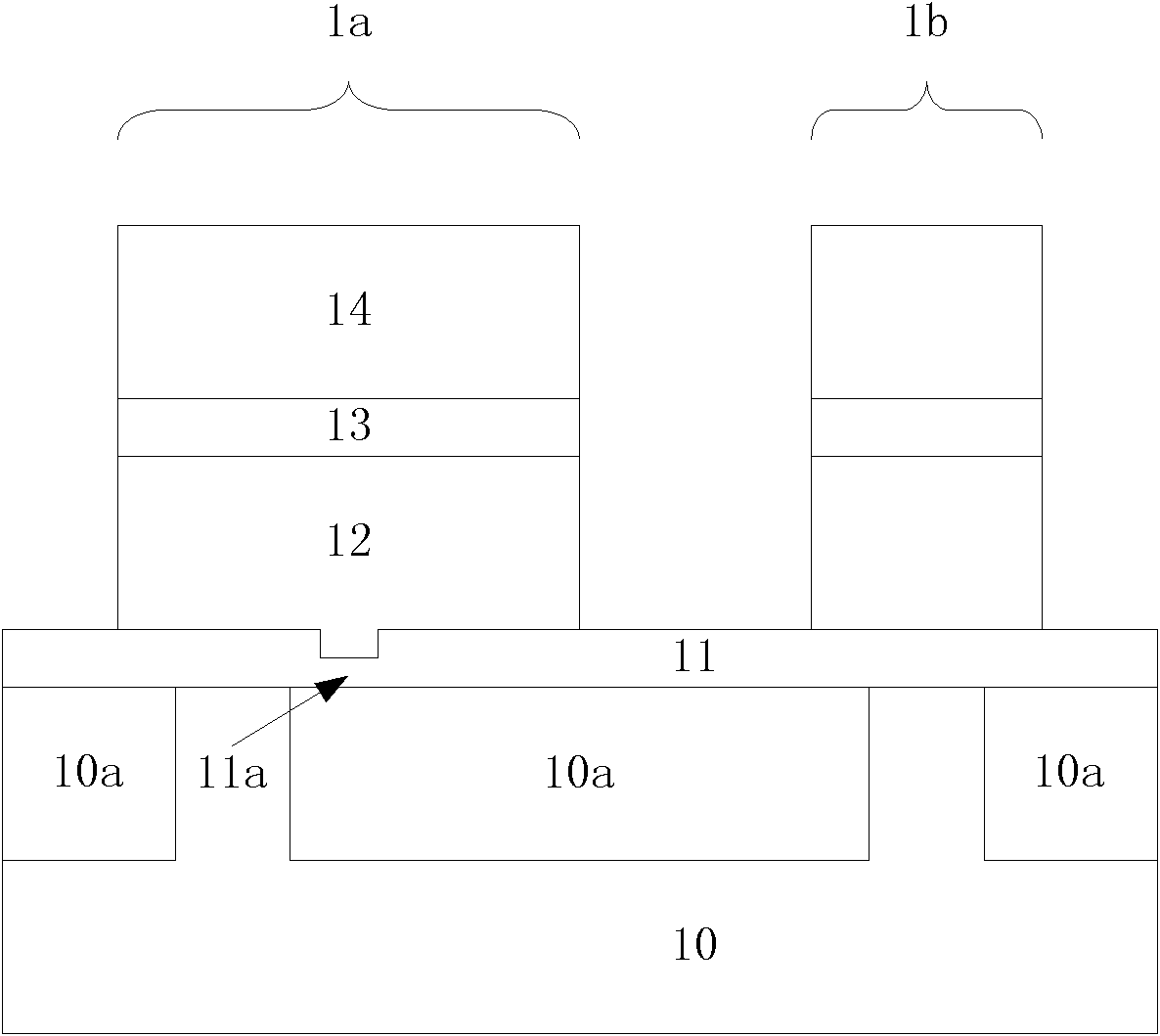

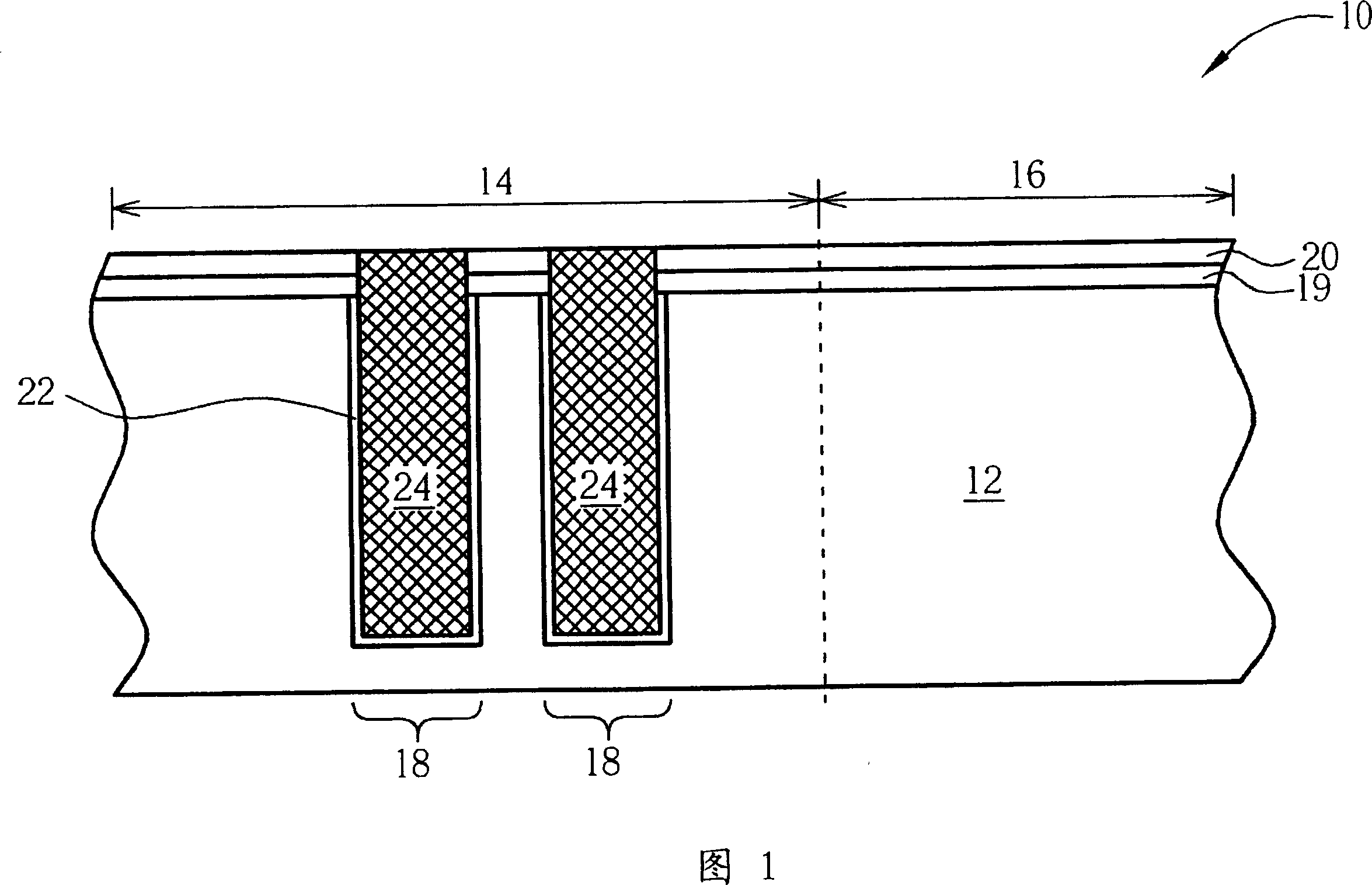

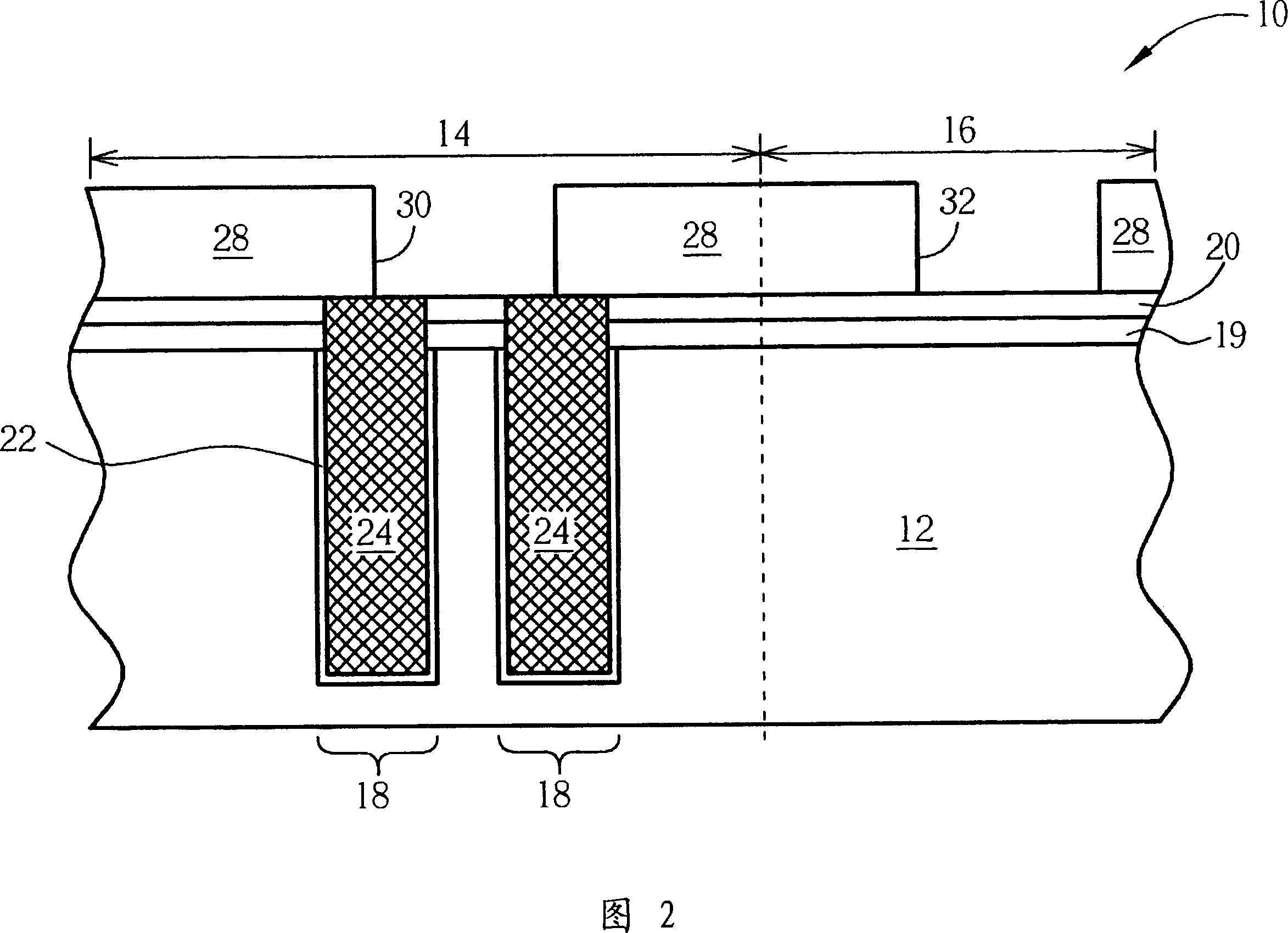

Low temperature active matrix display device and method of fabricating the same

InactiveUS20060138922A1Reduce aperture ratioIncrease capacitor areaElectric discharge tubesElectroluminescent light sourcesResistActive matrix

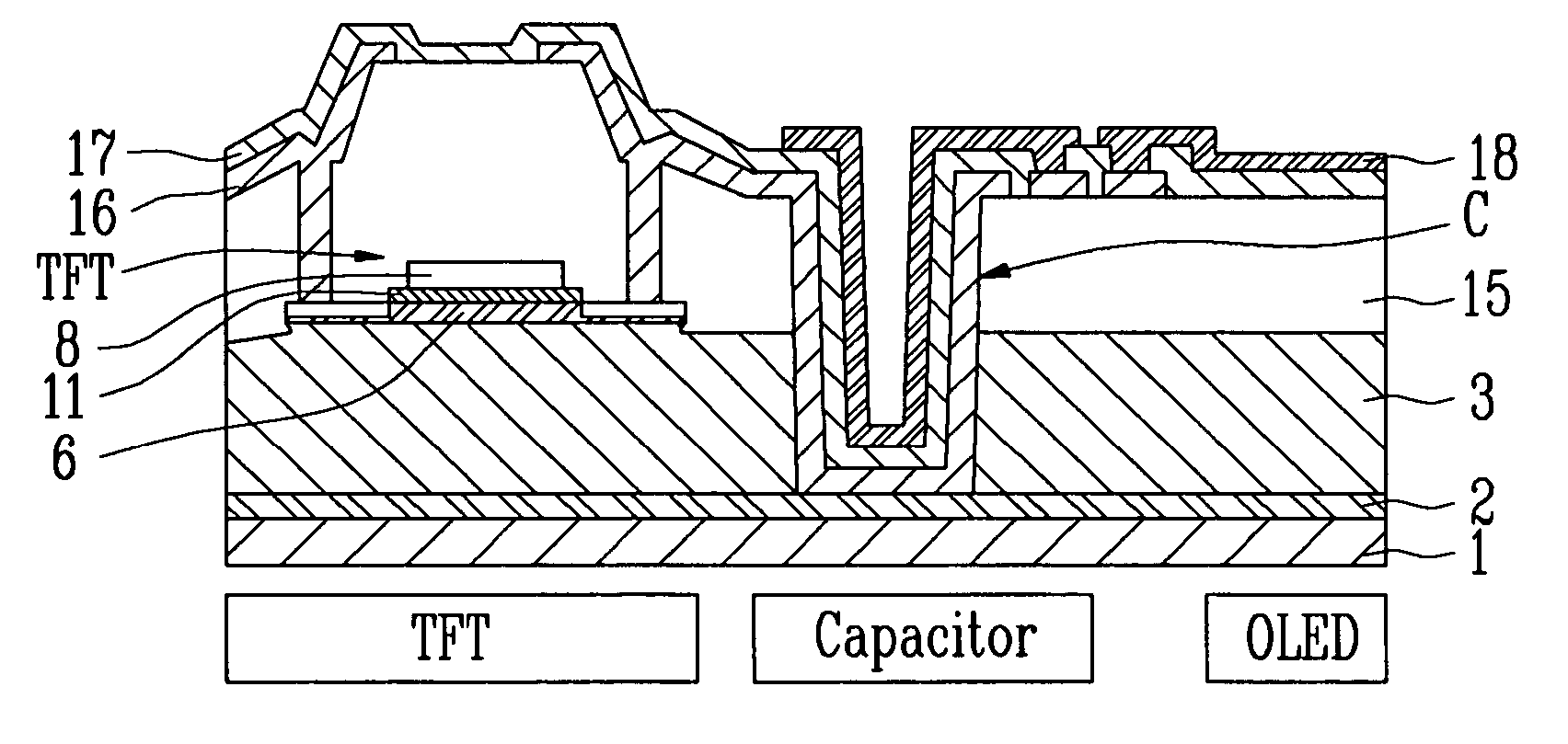

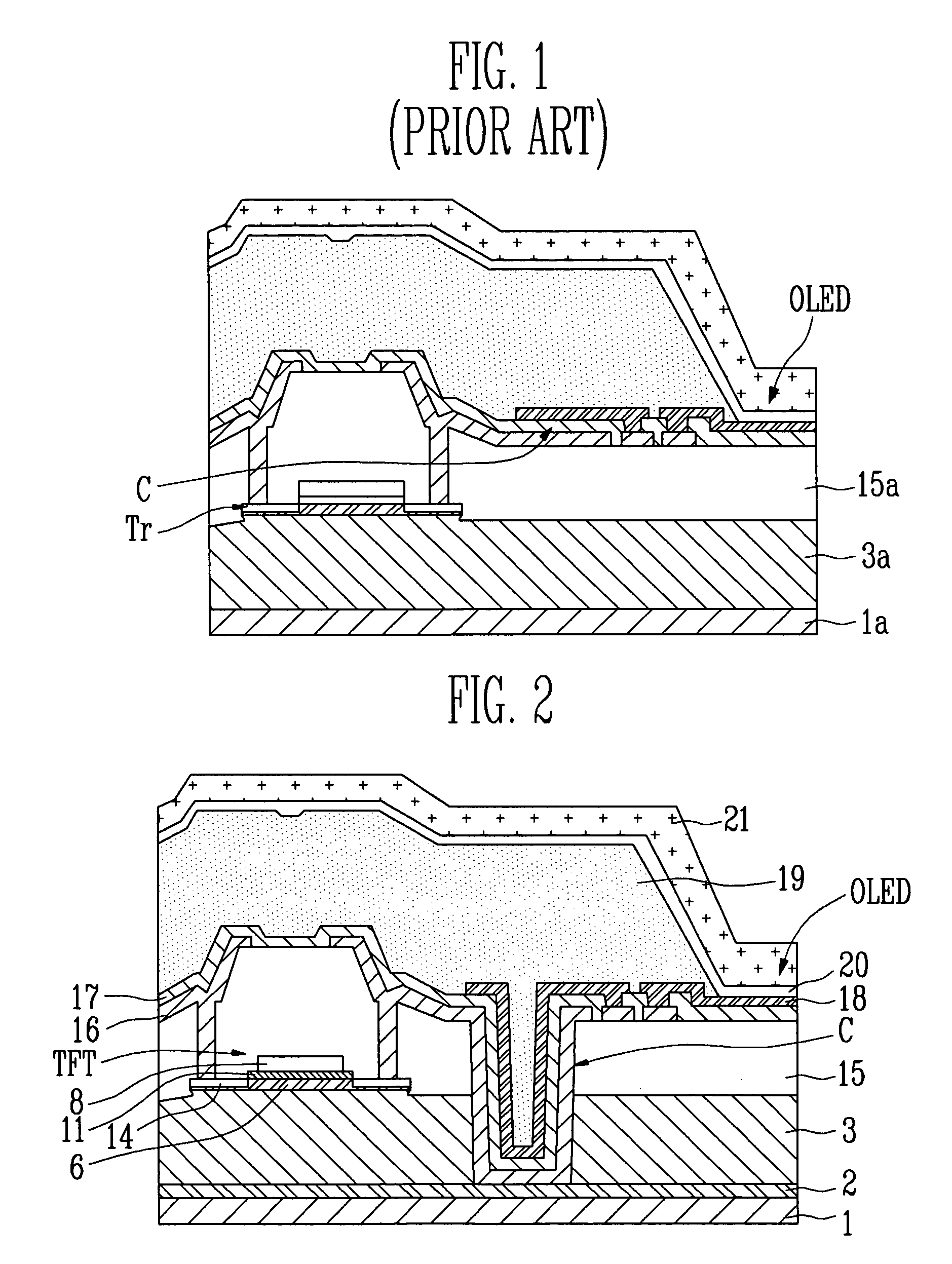

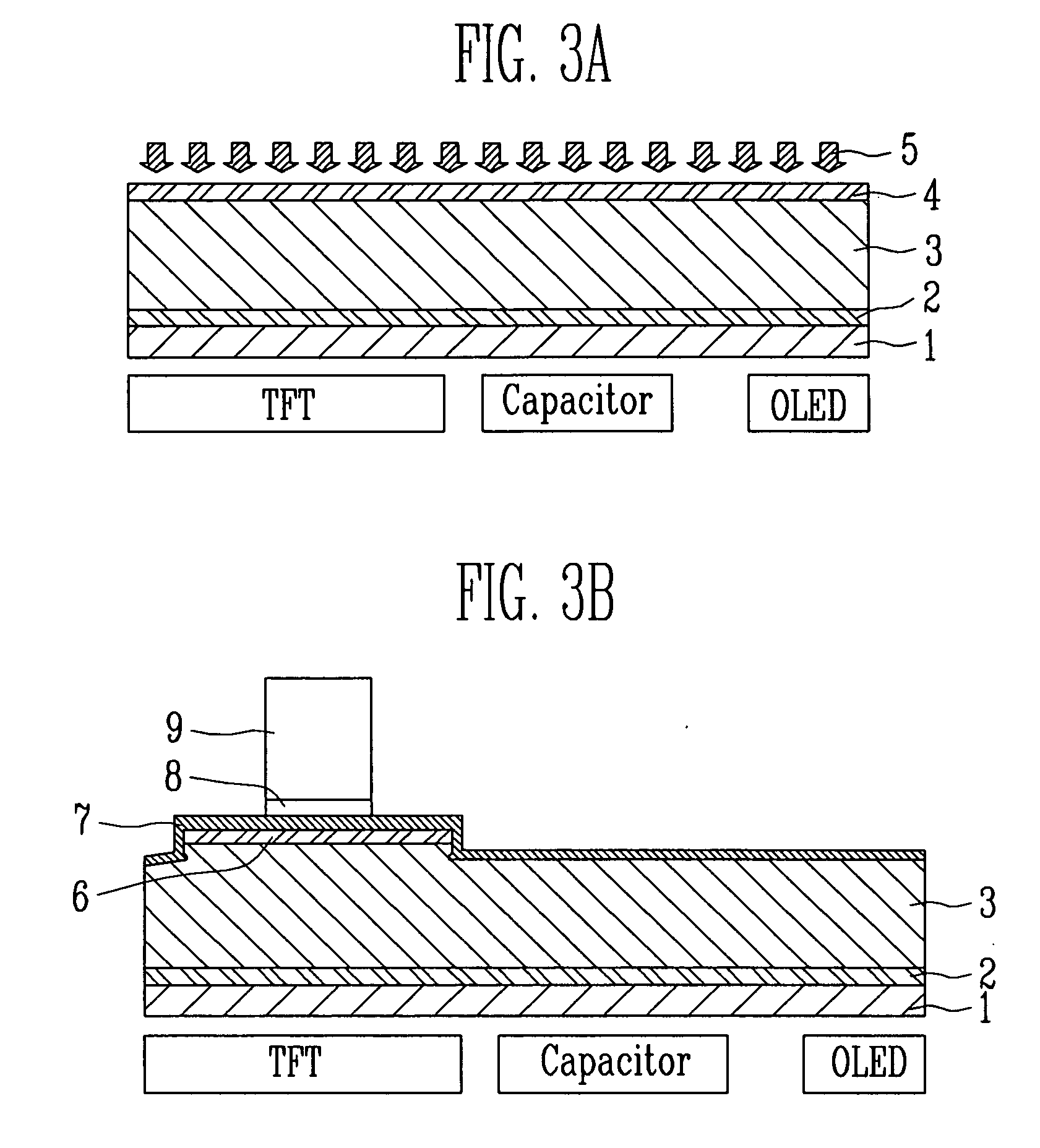

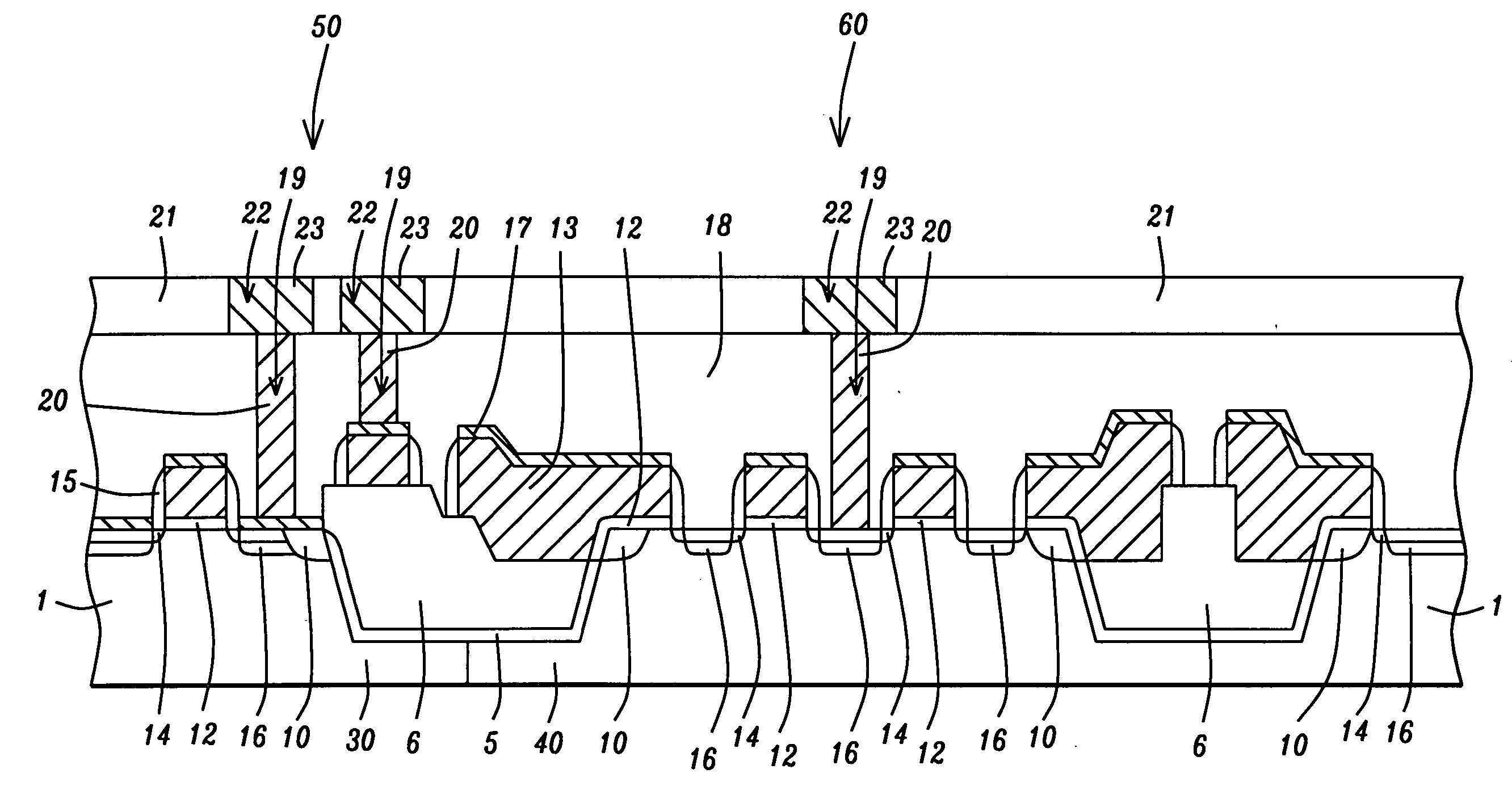

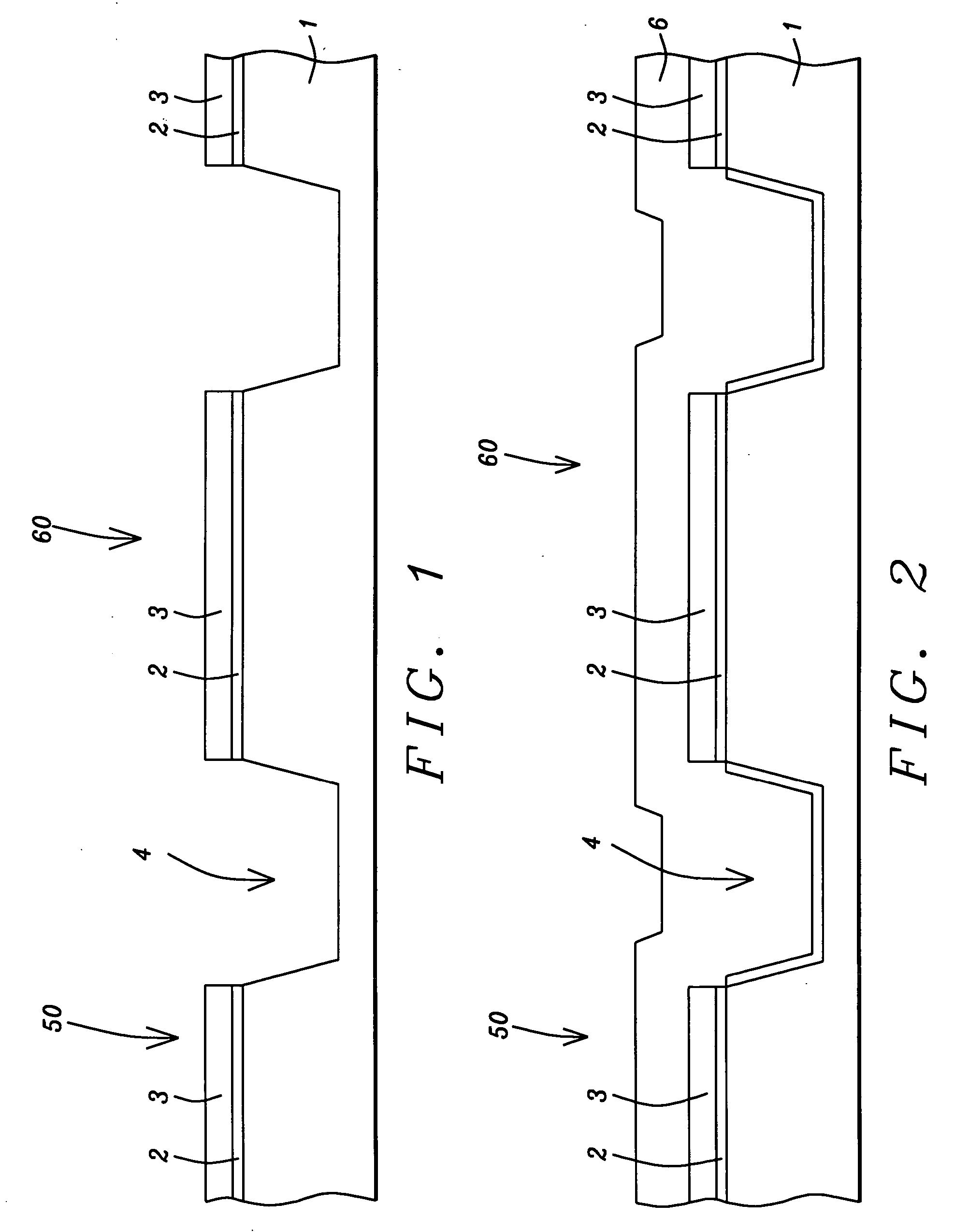

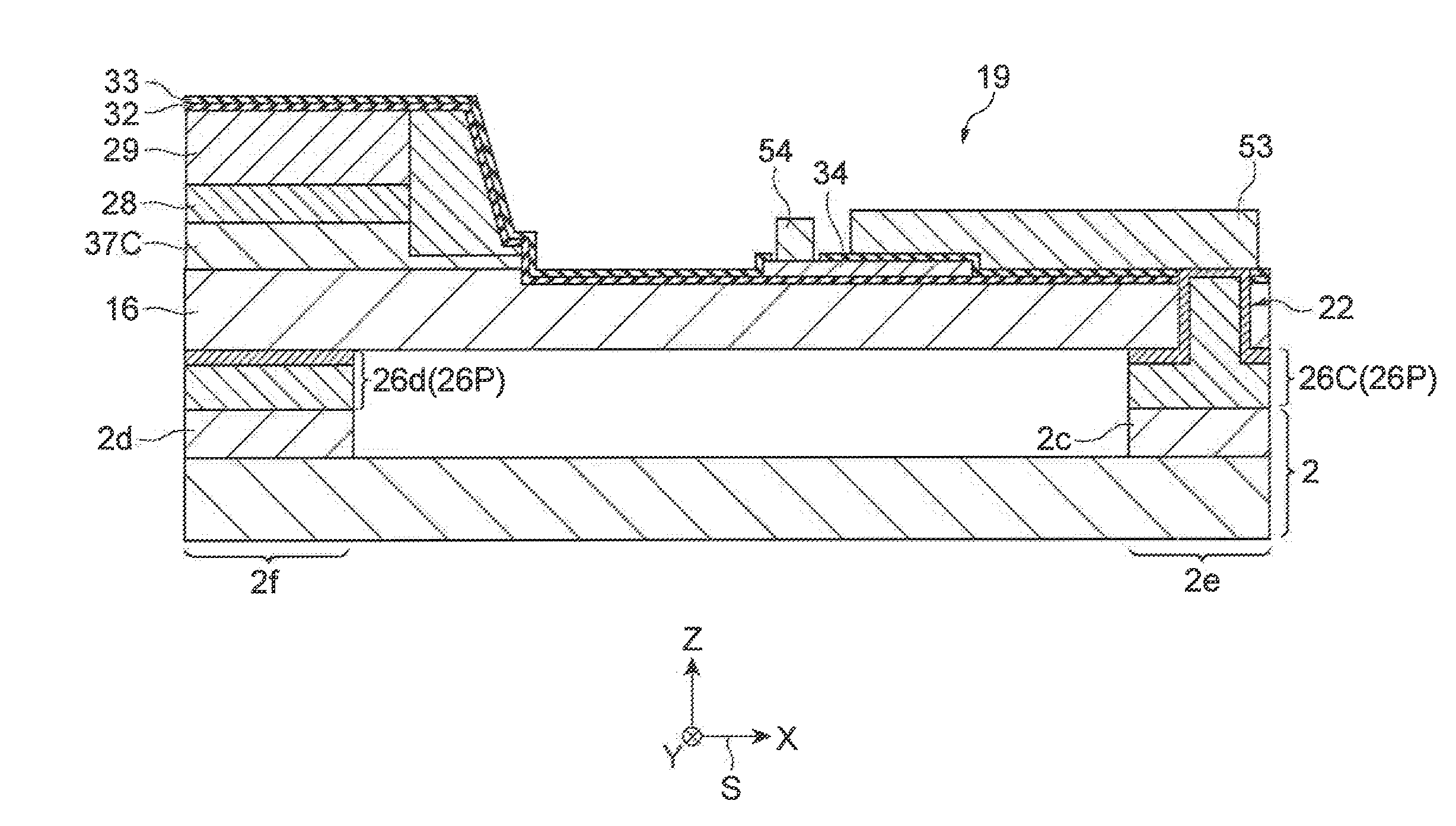

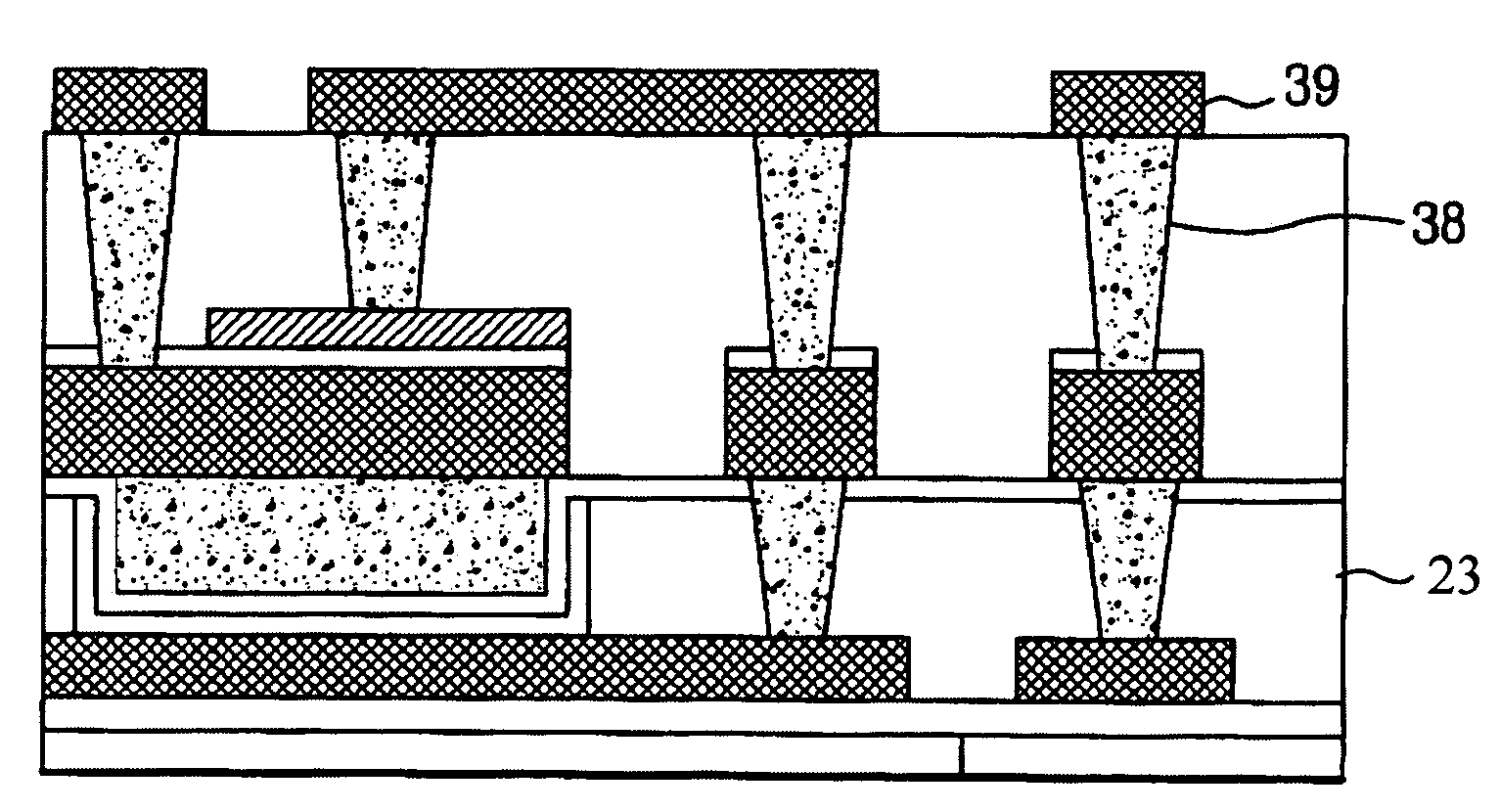

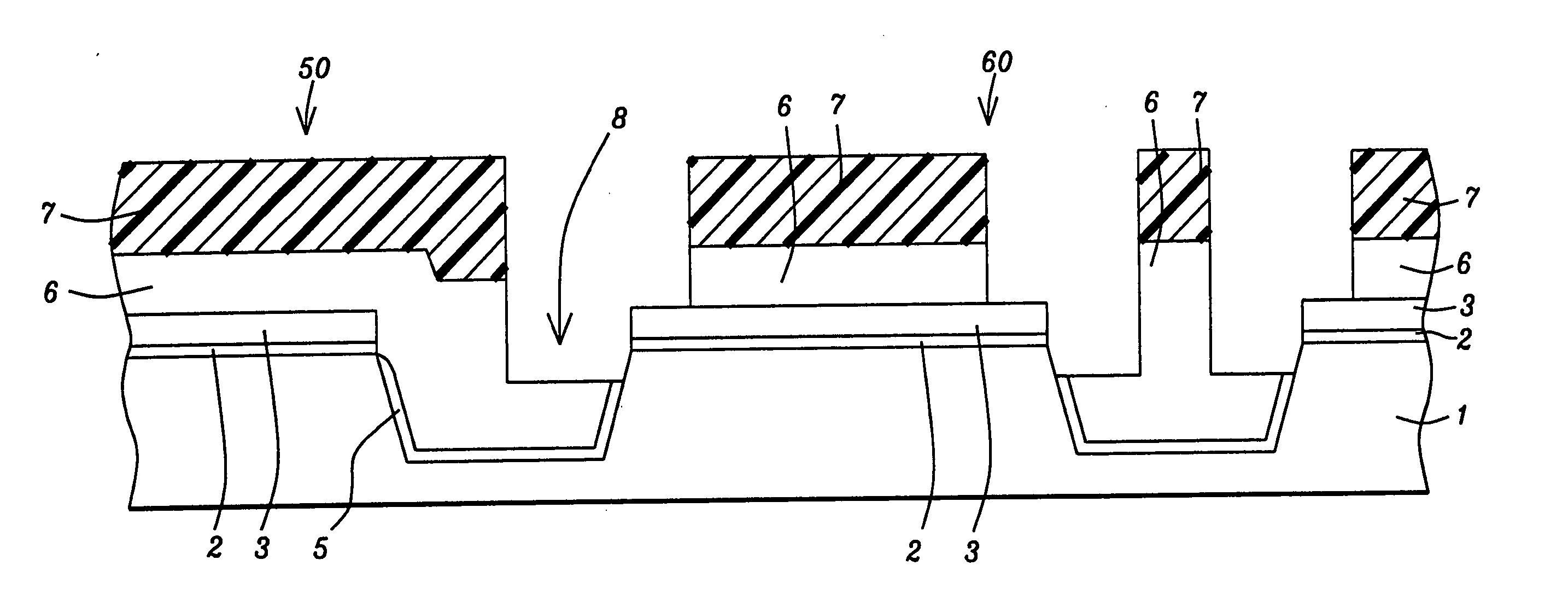

Provided are a low temperature active matrix display device using a plastic substrate and method of fabricating the same. The low temperature active matrix display device includes: a plastic substrate; a reflection layer disposed on the plastic substrate; a buffer layer disposed on the reflection layer; a thin film transistor disposed on the buffer layer in a first region of the plastic substrate; an interlayer dielectric layer disposed on the thin film transistor; a capacitor disposed in a trench formed in a second region of the plastic substrate and having a first electrode connected to a source electrode and a drain electrode of the thin film transistor, the trench extending from the interlayer dielectric layer to the reflection layer; and a display device having one electrode connected to a second electrode of the capacitor. The above-described structure includes photoresist spacers to decrease a leakage current from the TFT, includes a reflector to protect the plastic substrate from deformation due to laser irradiation, and employs a three-dimensional capacitor to increase an aperture ratio.

Owner:ELECTRONICS & TELECOMM RES INST

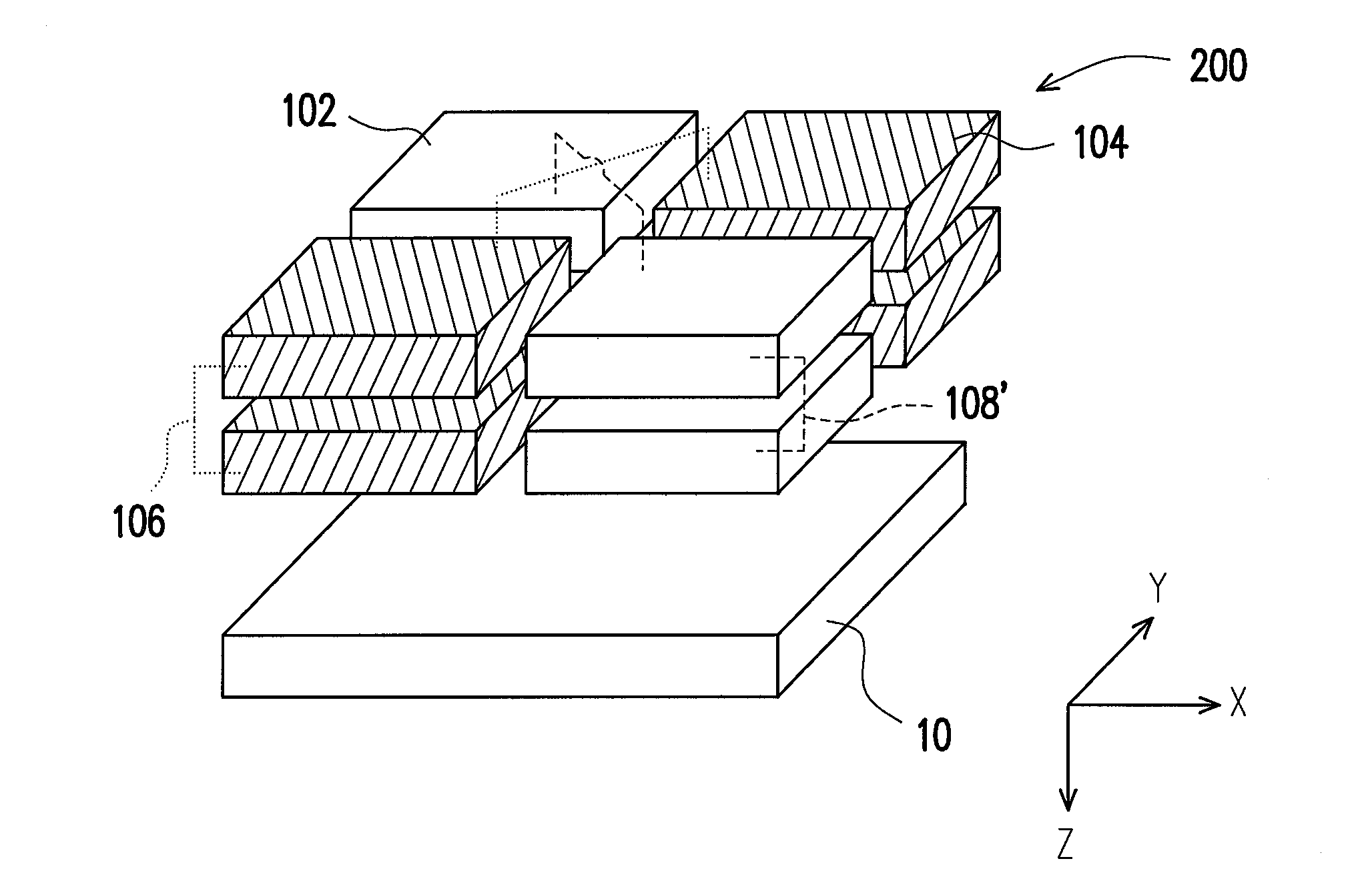

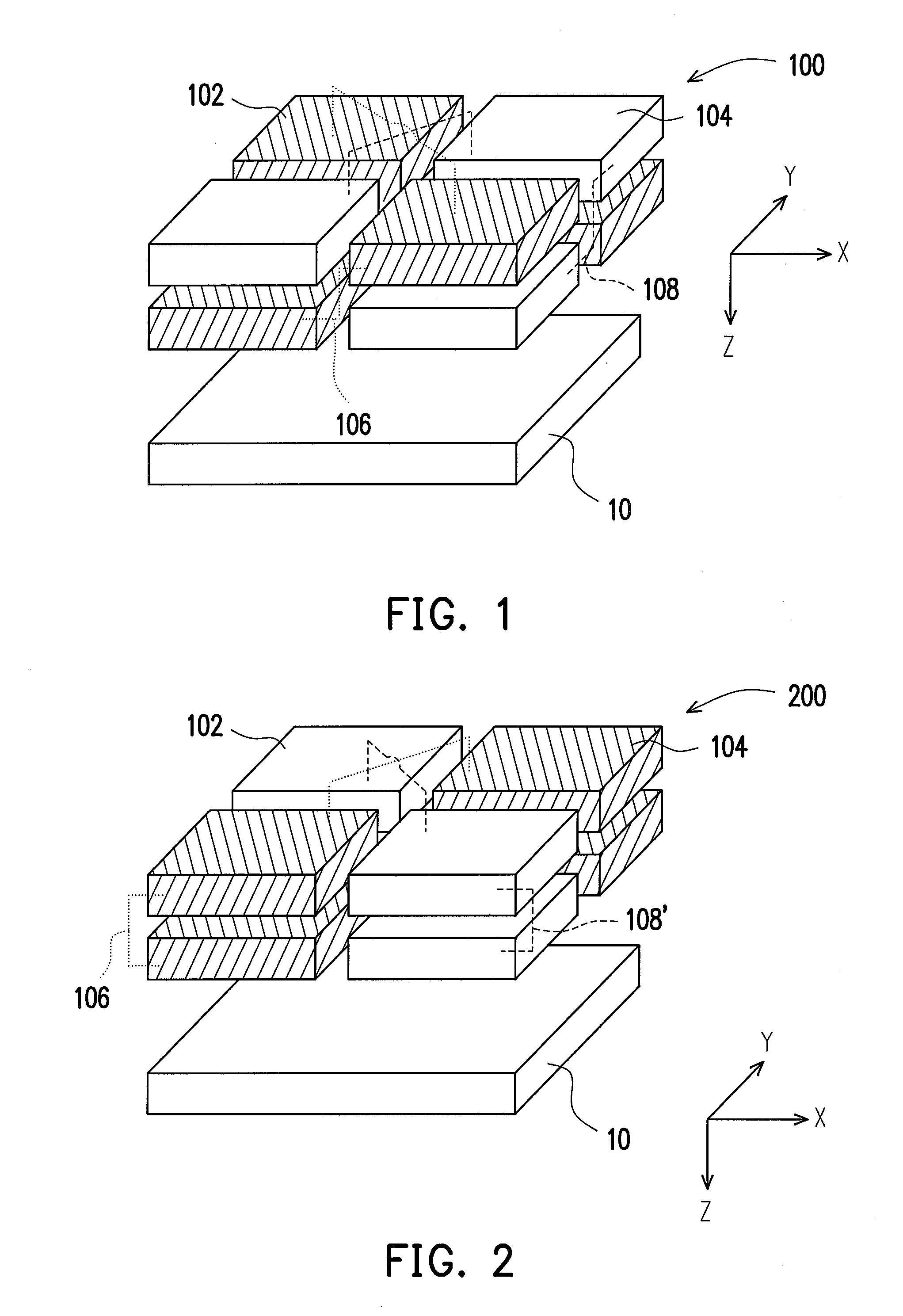

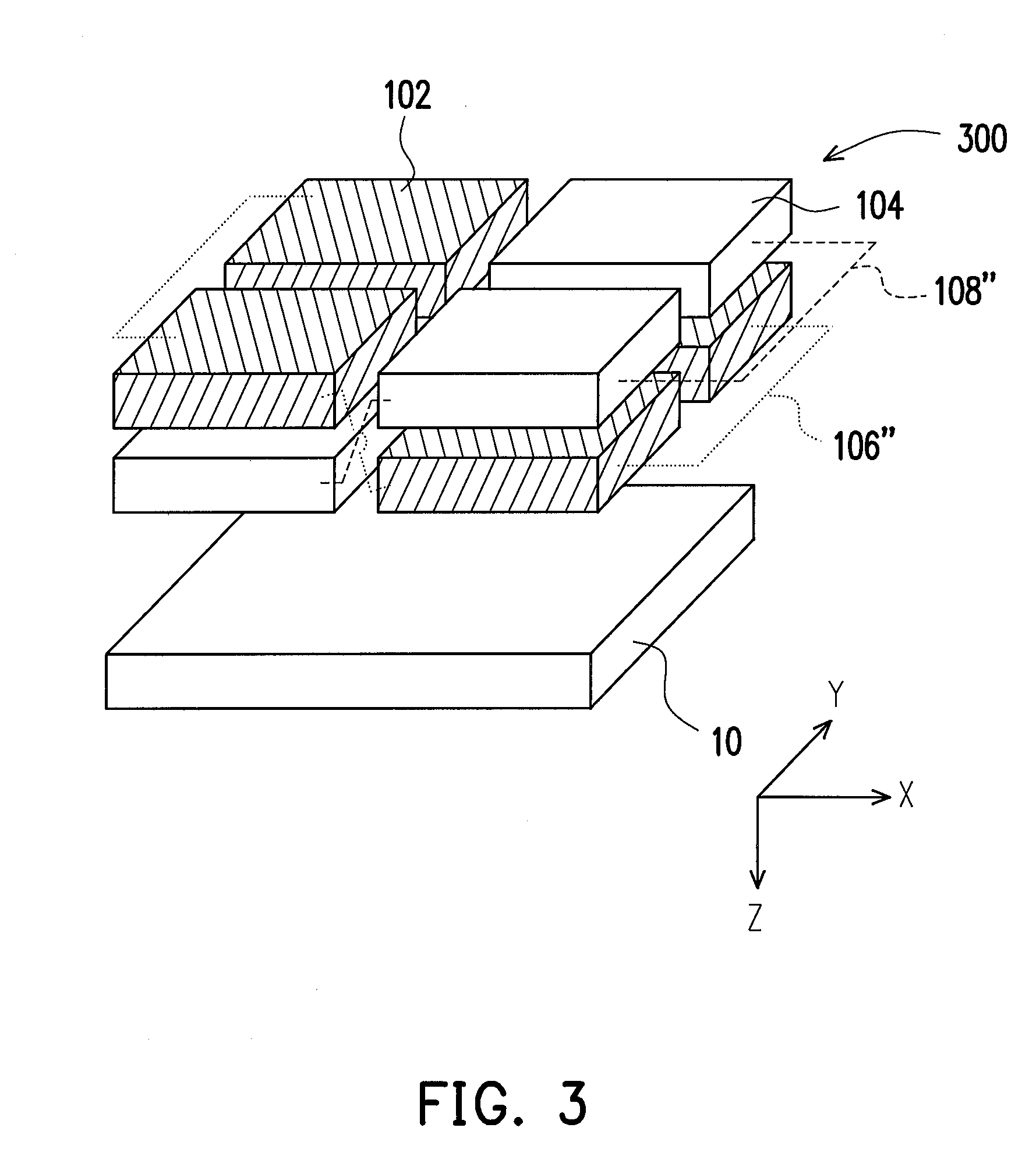

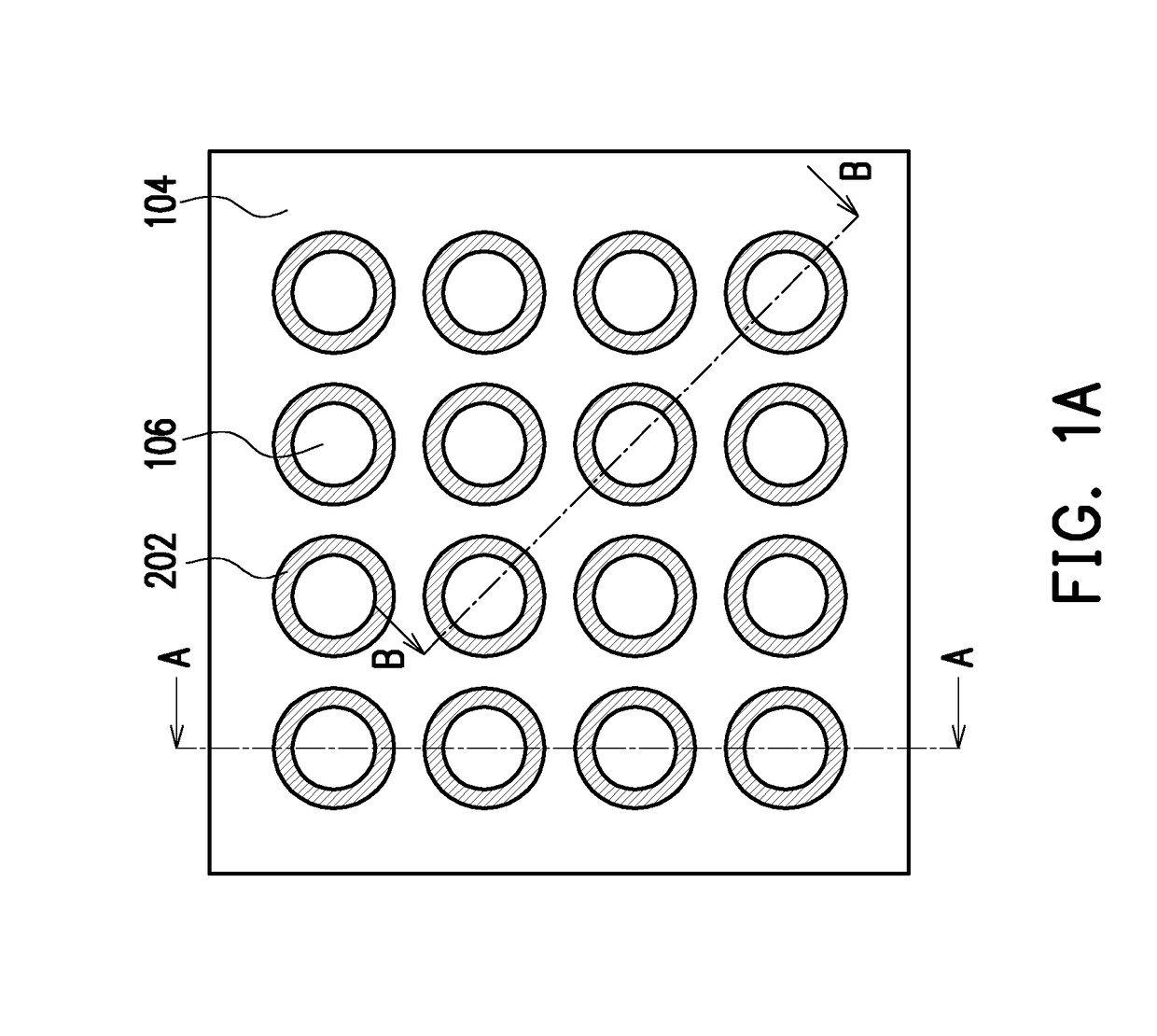

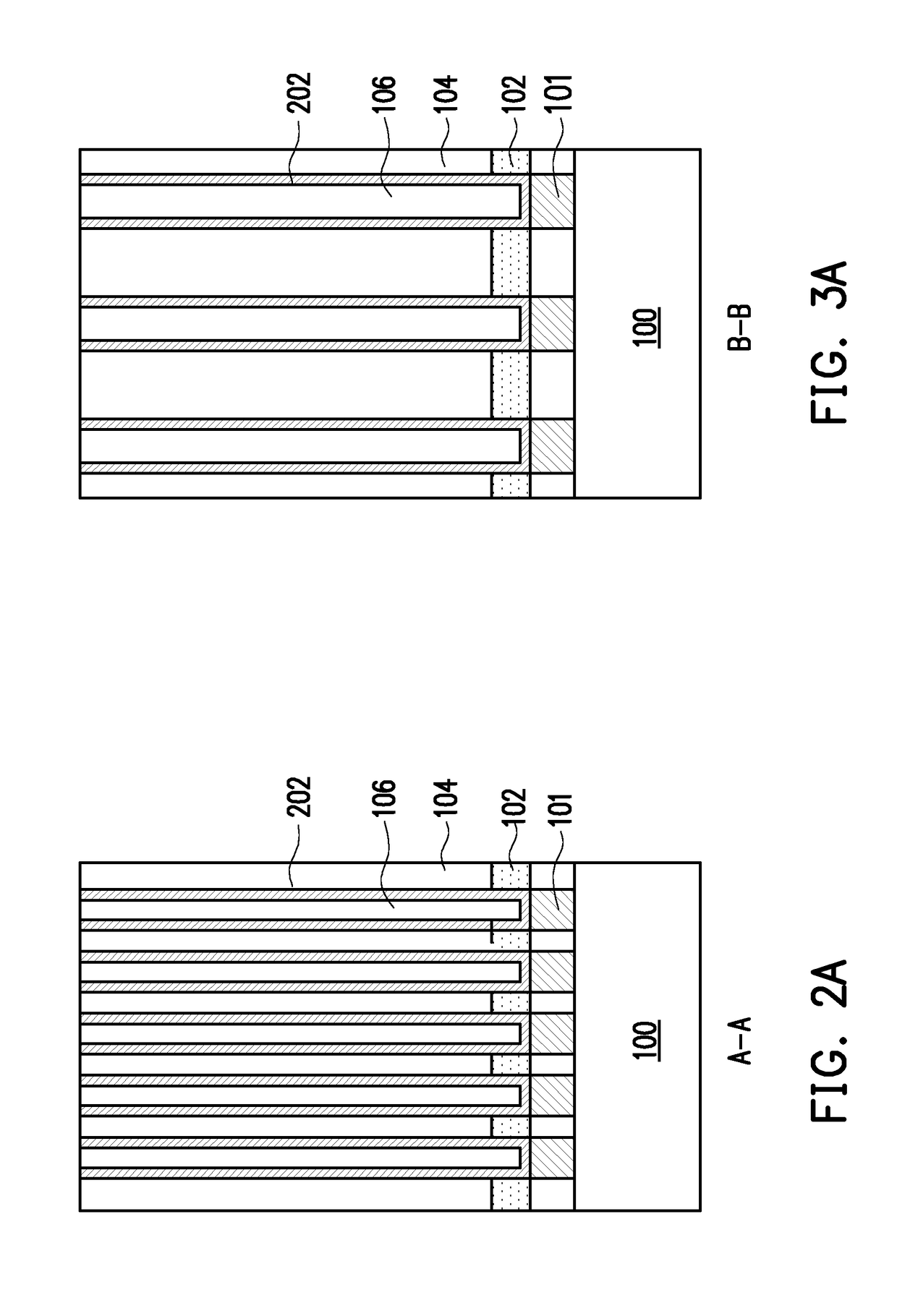

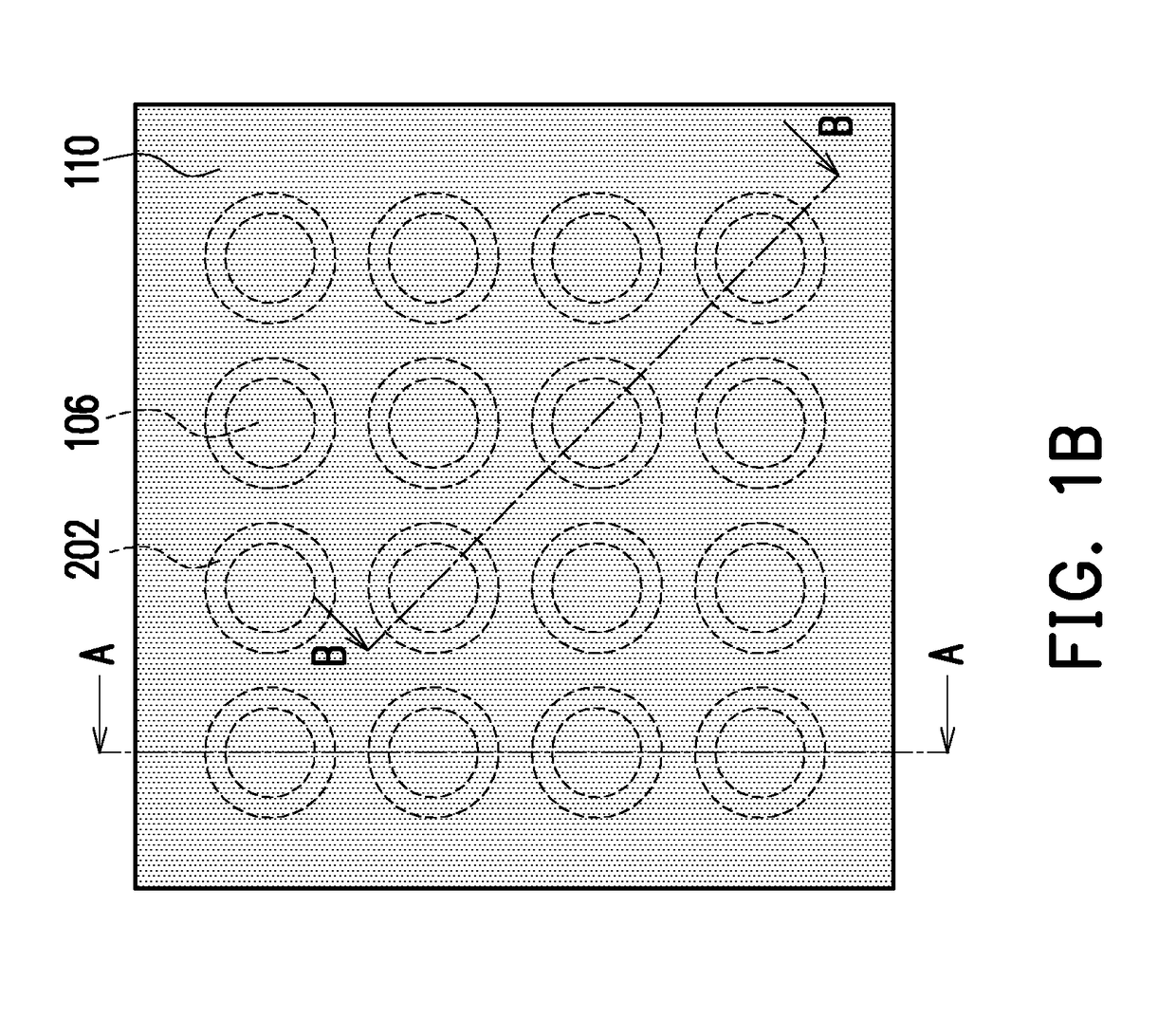

Structure of capacitor set and method for reducing capacitance variation between capacitors

ActiveUS20080012092A1Reduce Capacitance VariationIncrease production capacitySemiconductor/solid-state device detailsSolid-state devicesCapacitanceCapacitor

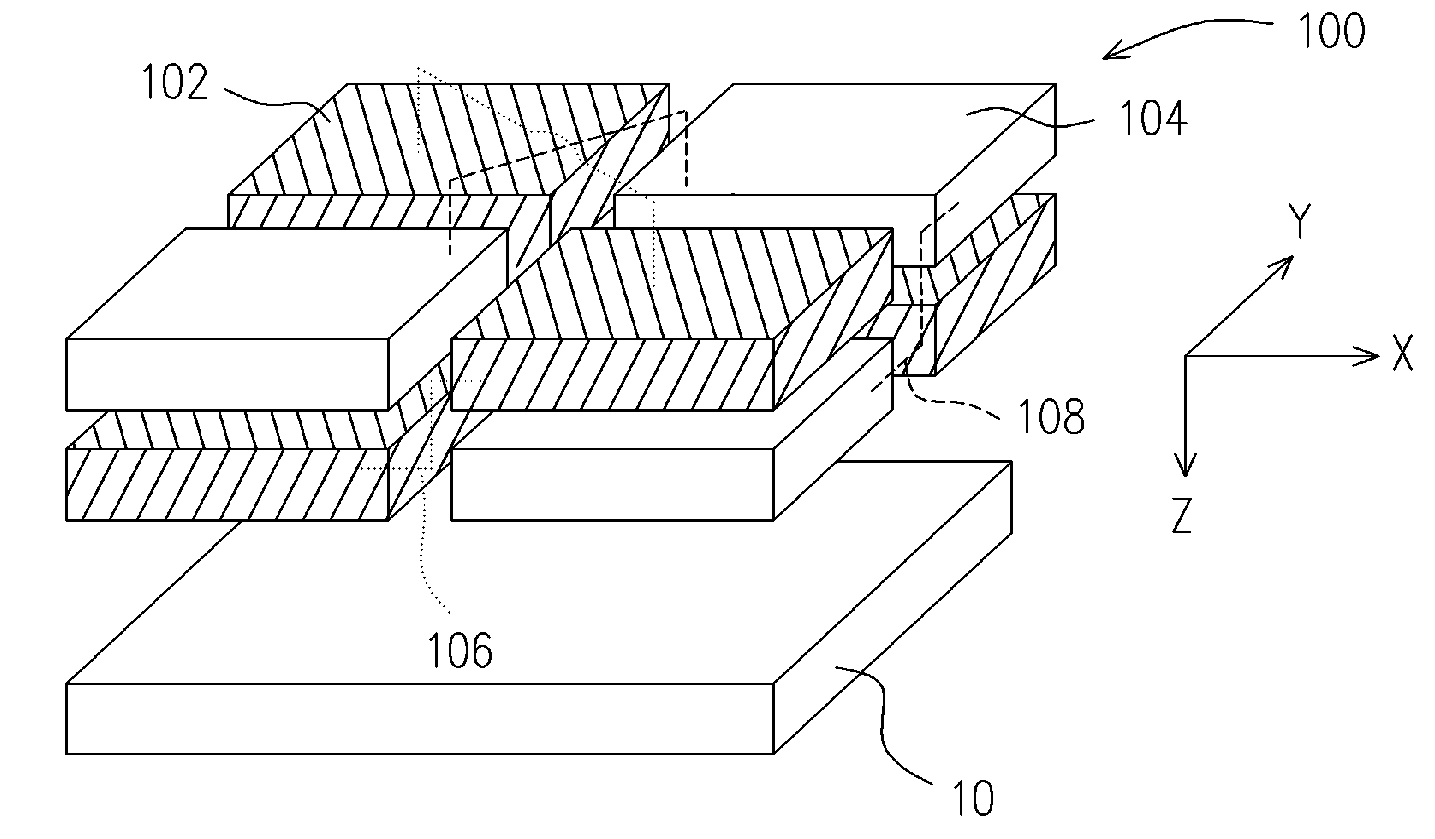

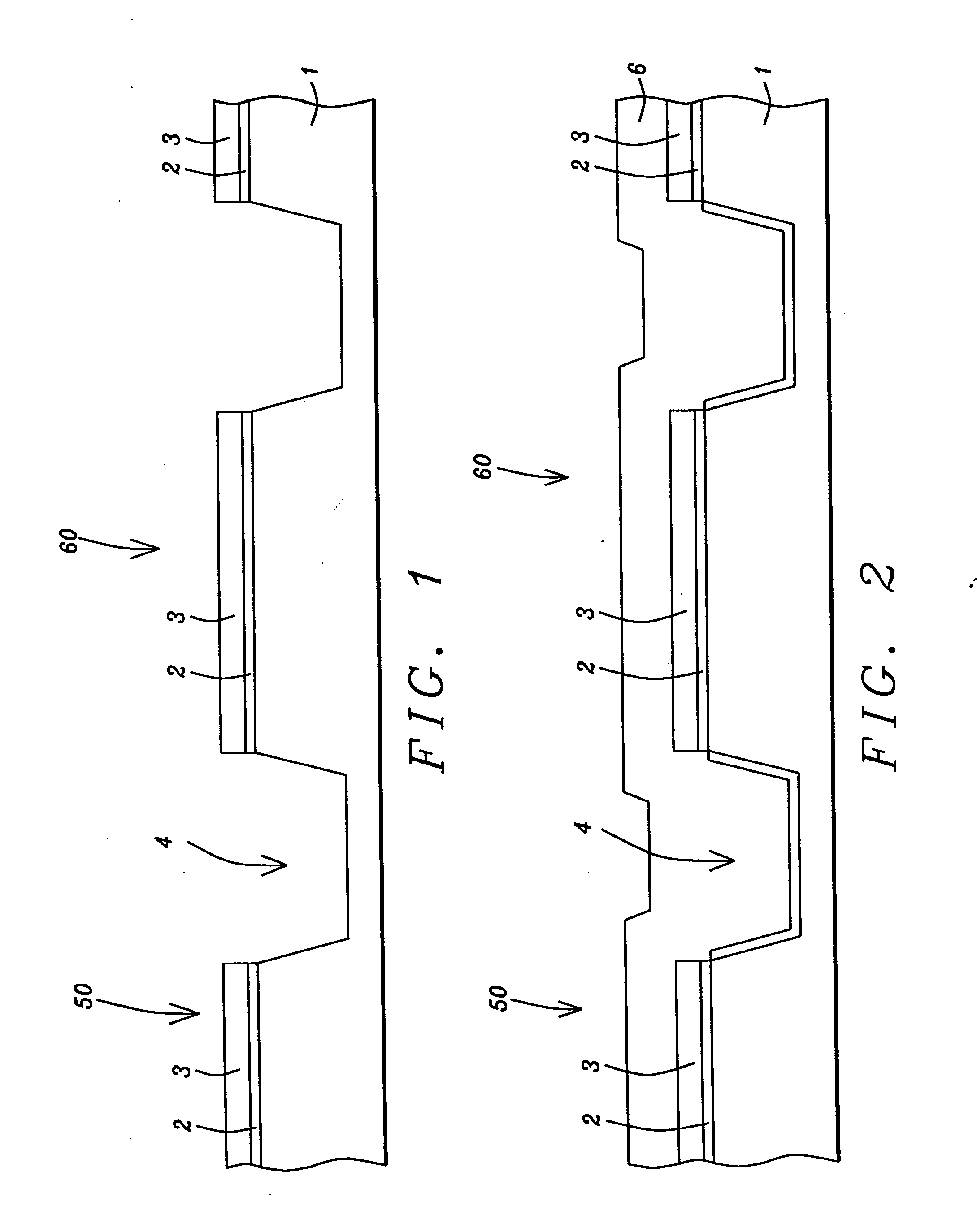

A structure of a capacitor set is described, including at least two capacitors that are disposed at the same position on a substrate and include a first capacitor and a second capacitor. The first capacitor includes multiple first capacitor units electrically connected with each other in parallel. The second capacitor includes multiple second capacitor units electrically connected with each other in parallel. The first and the second capacitor units are arranged spatially intermixing with each other to form an array.

Owner:MARLIN SEMICON LTD

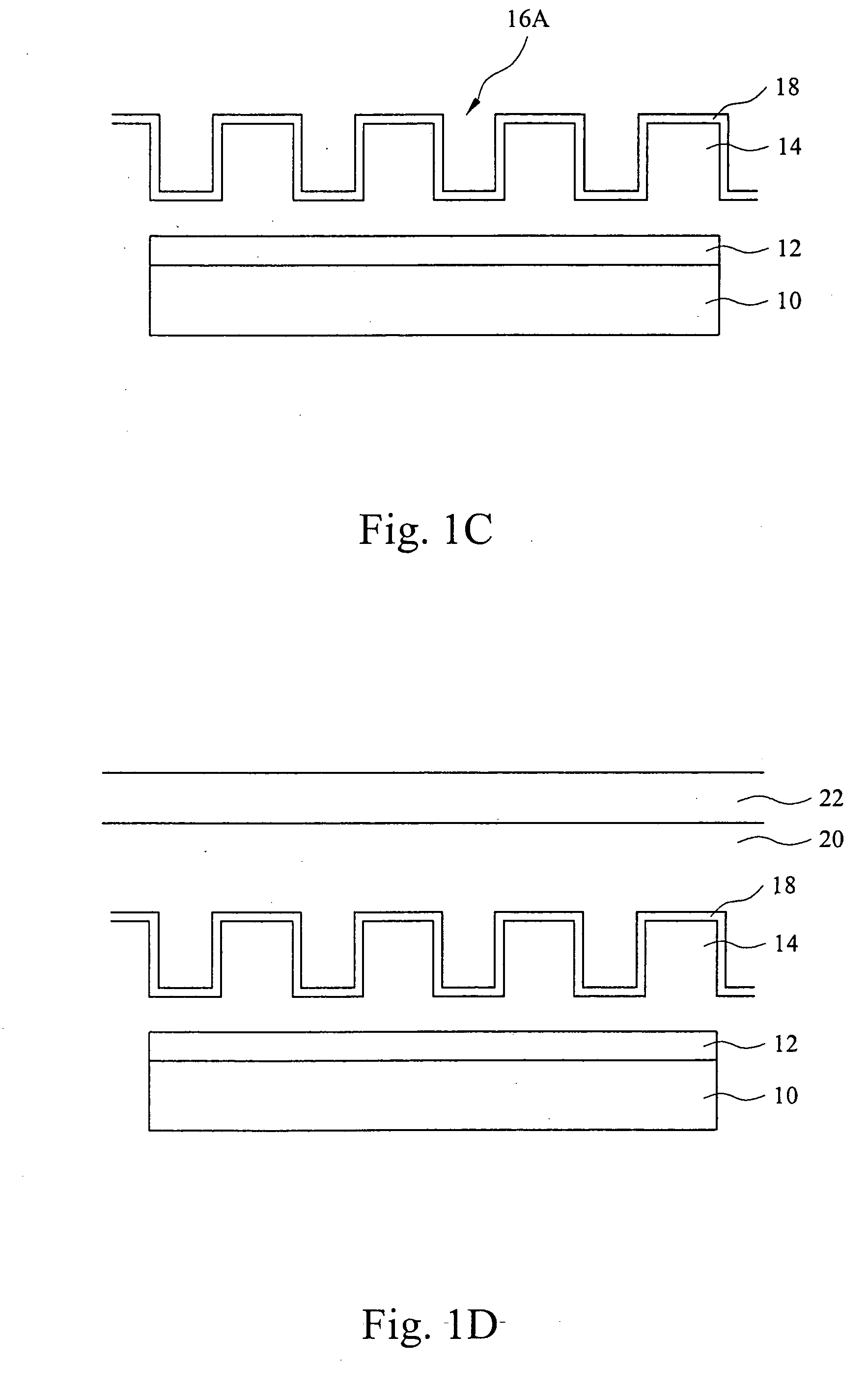

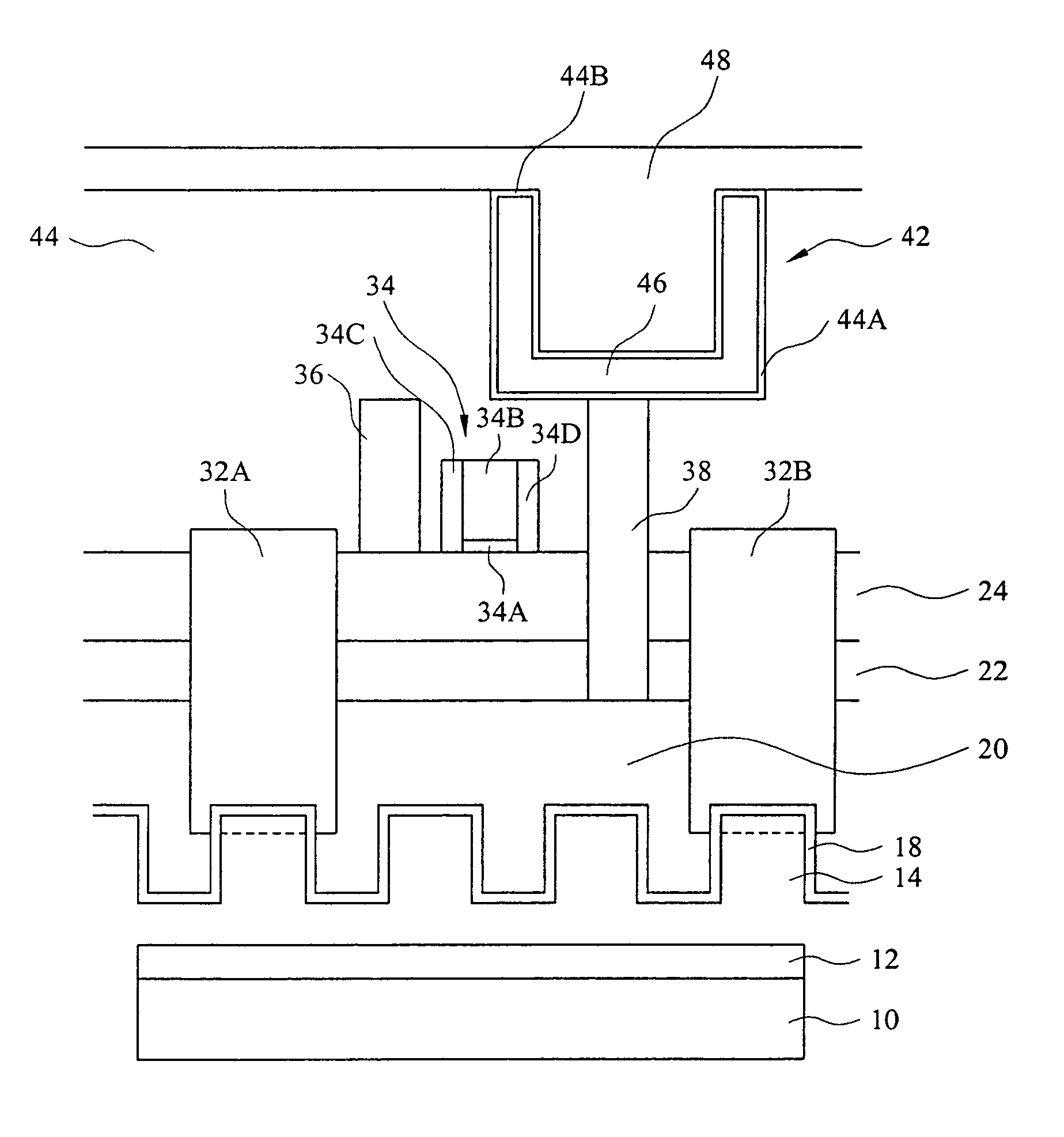

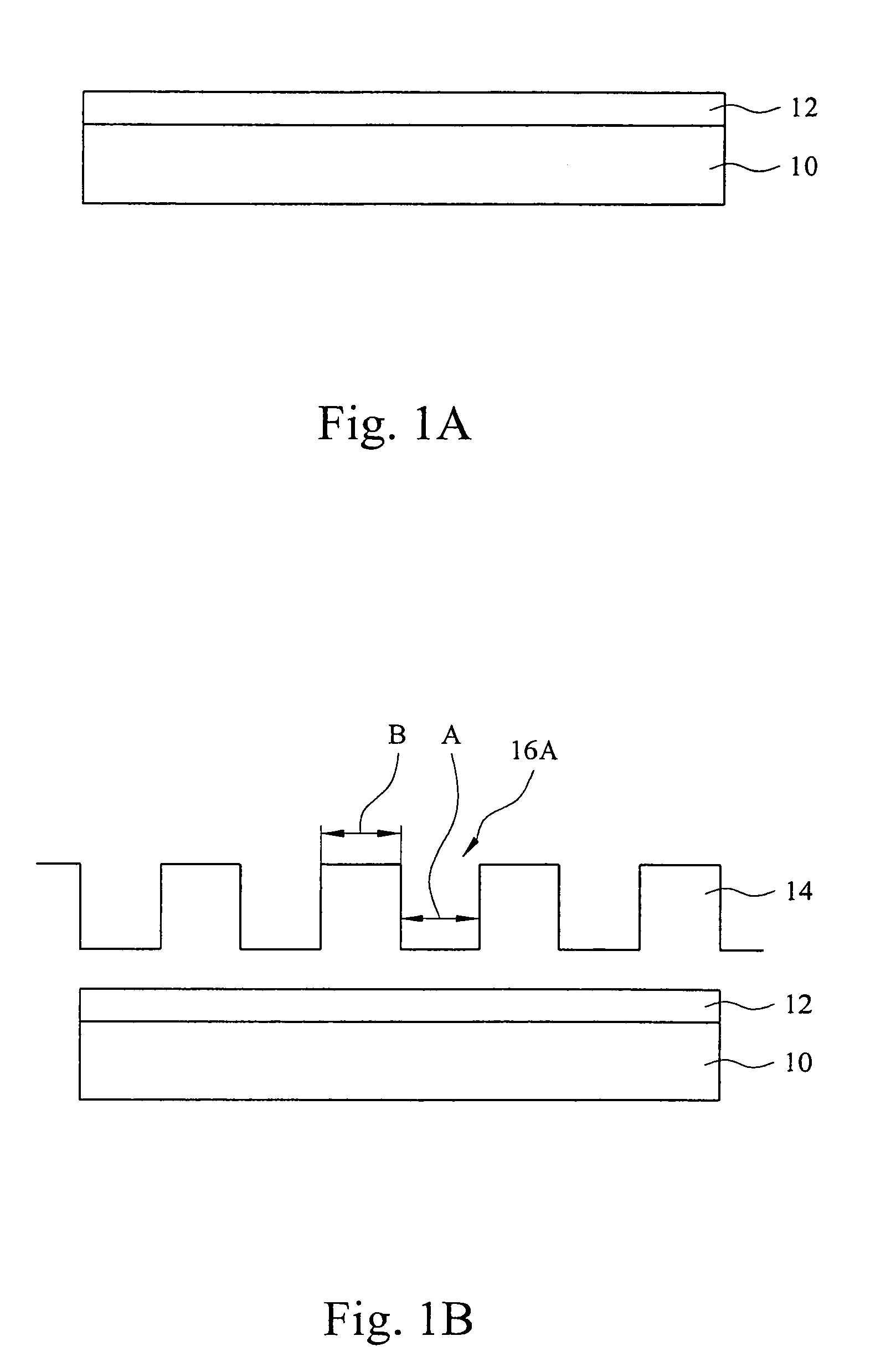

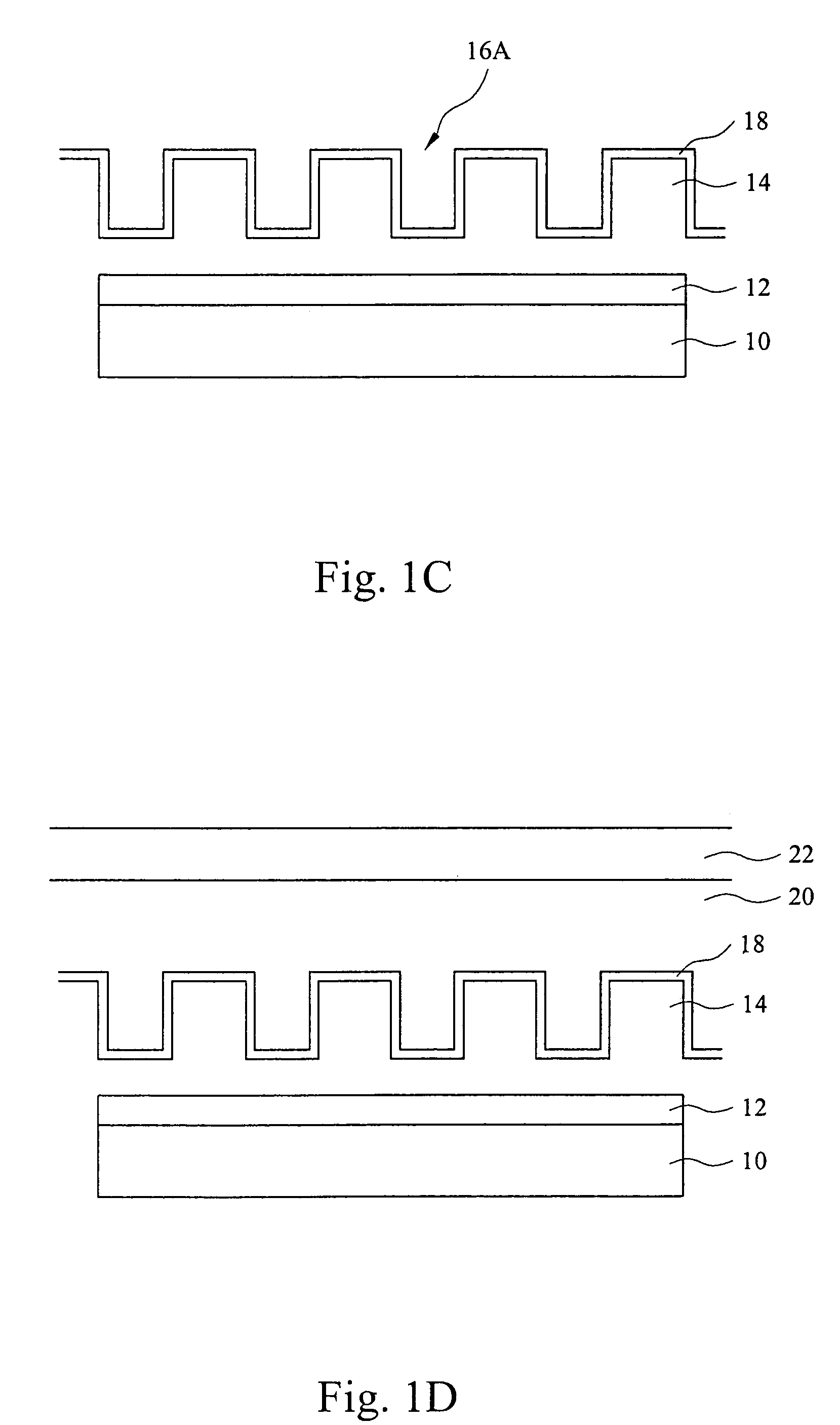

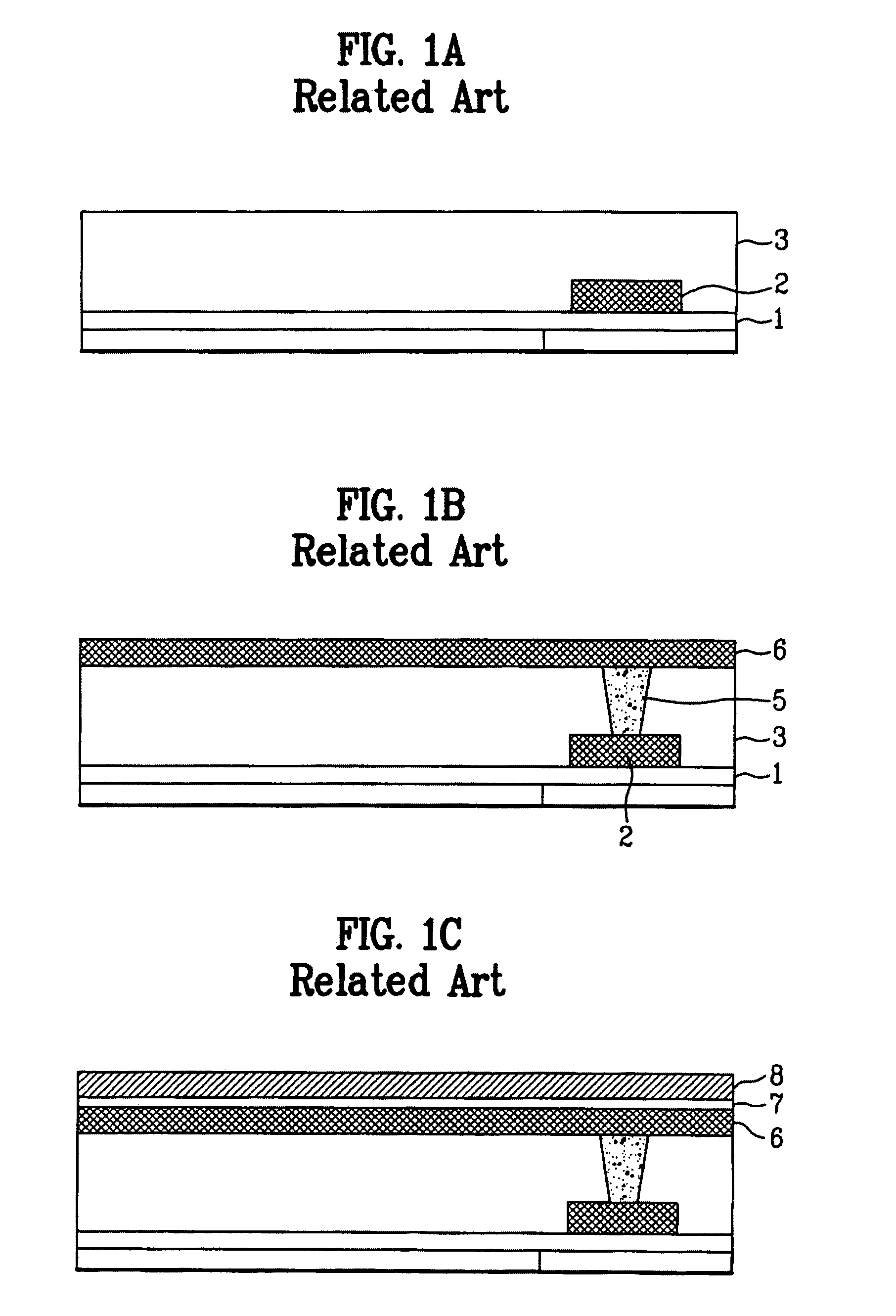

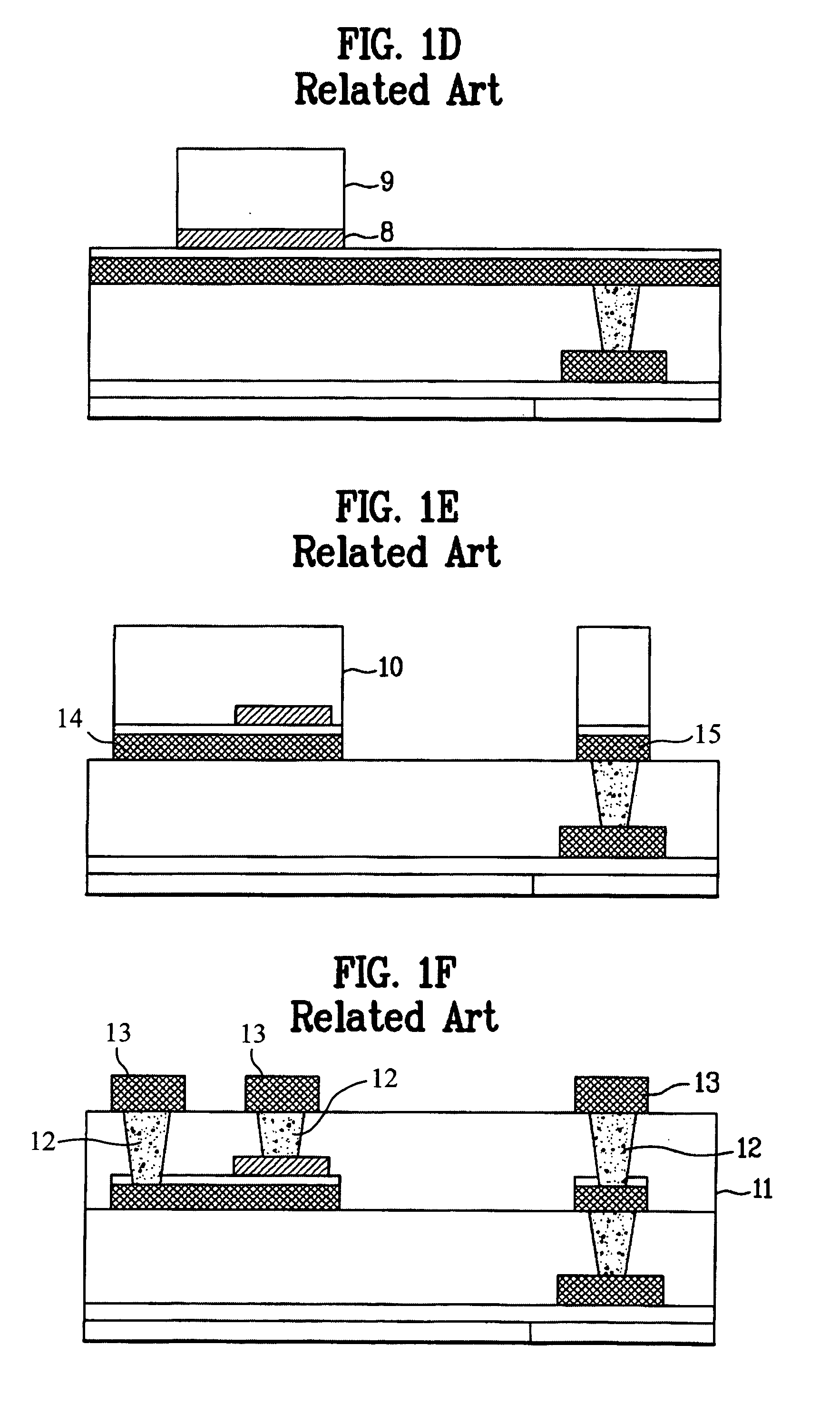

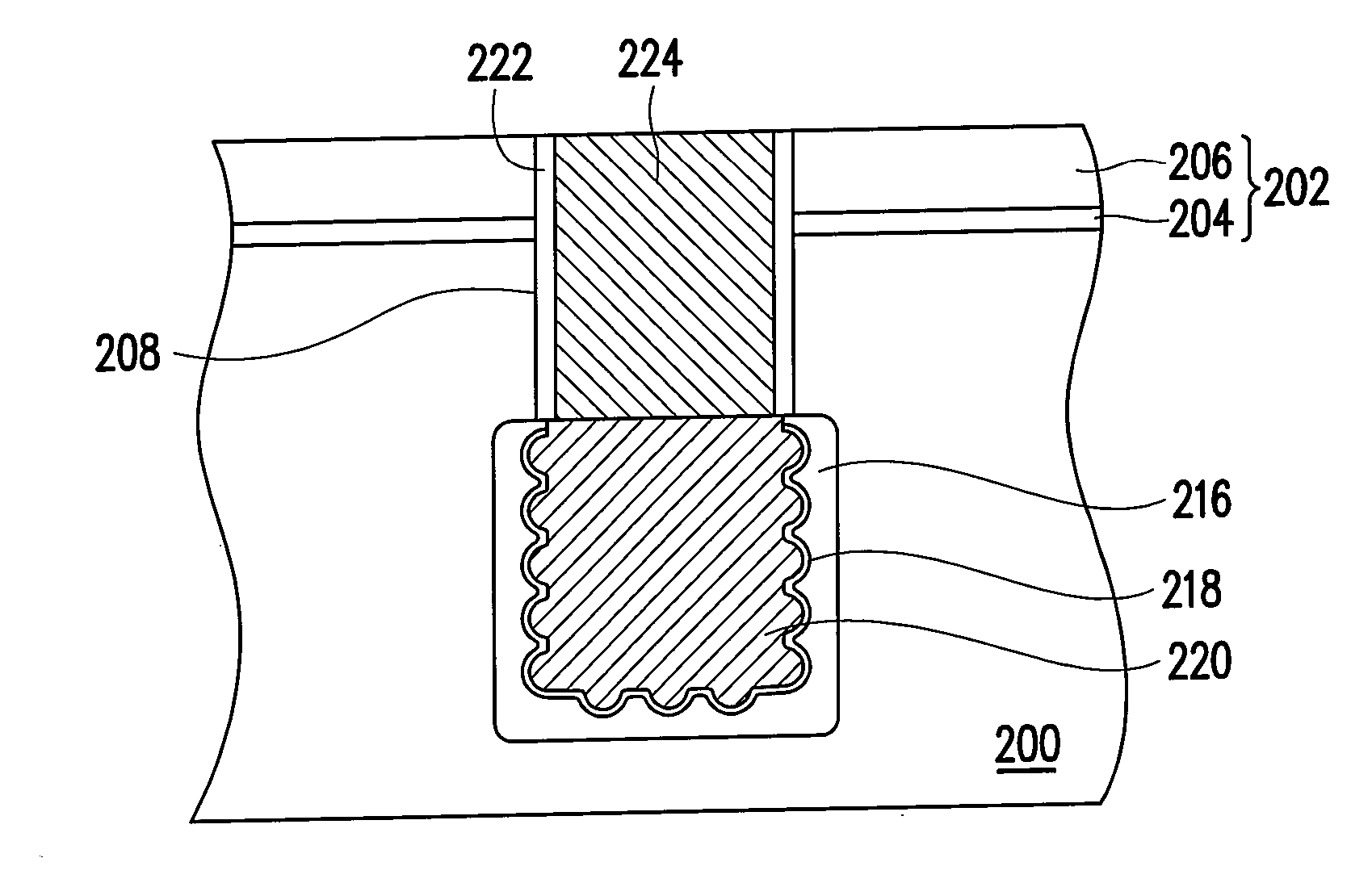

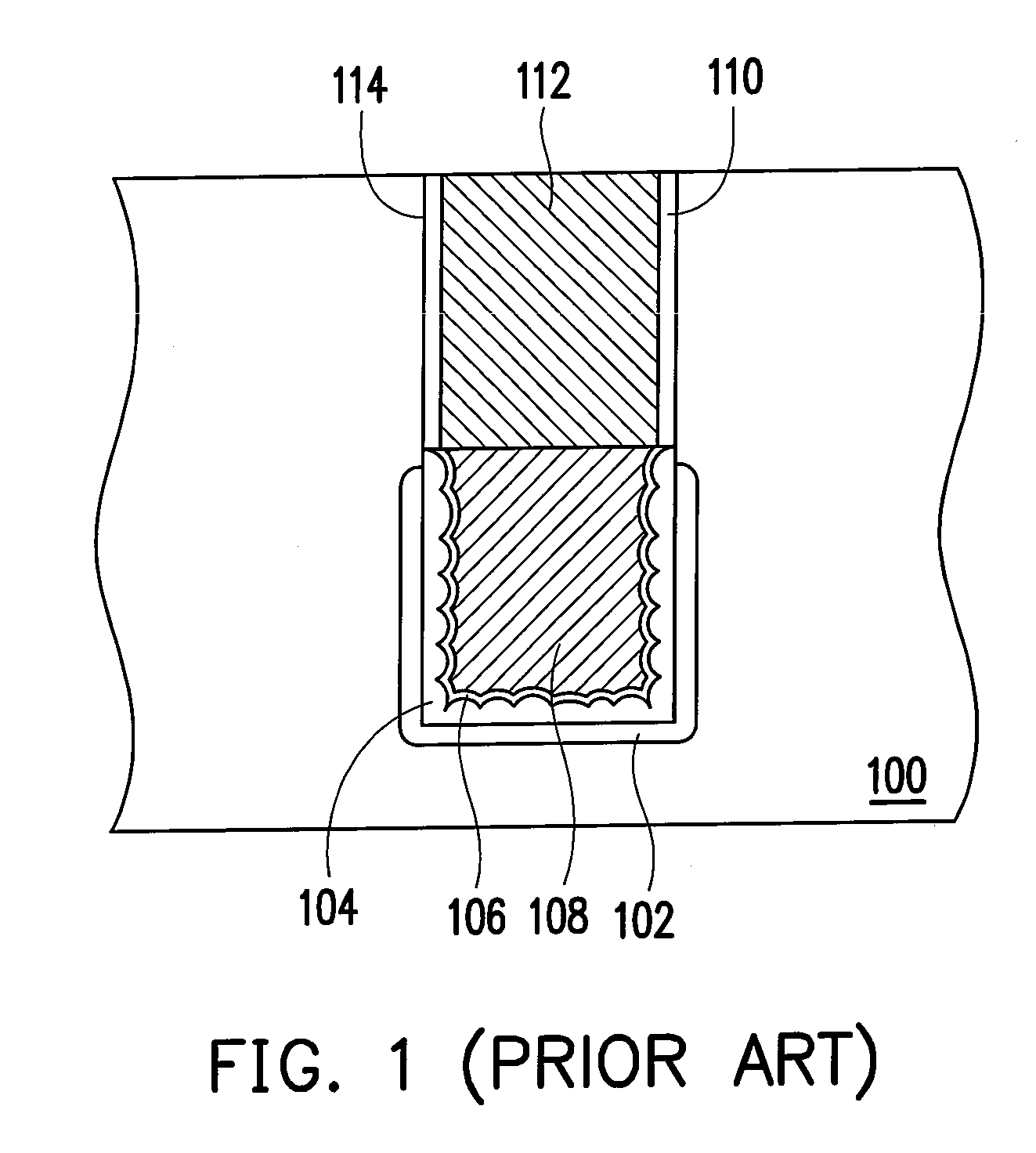

Semiconductor device substrate with embedded capacitor

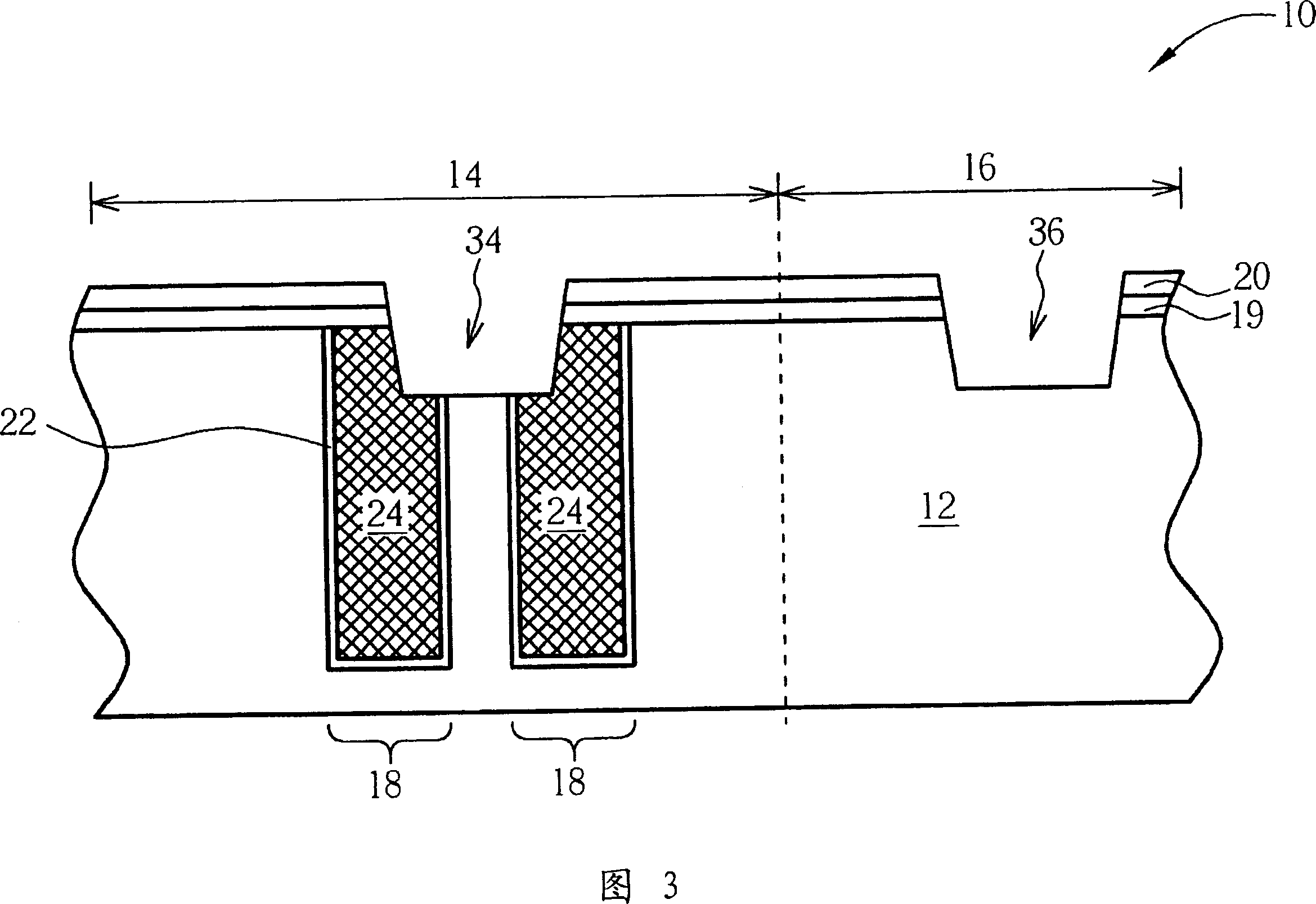

InactiveUS20060003522A1Increase capacitor areaSpace utilizationSolid-state devicesSemiconductor/solid-state device manufacturingDevice materialSoi substrate

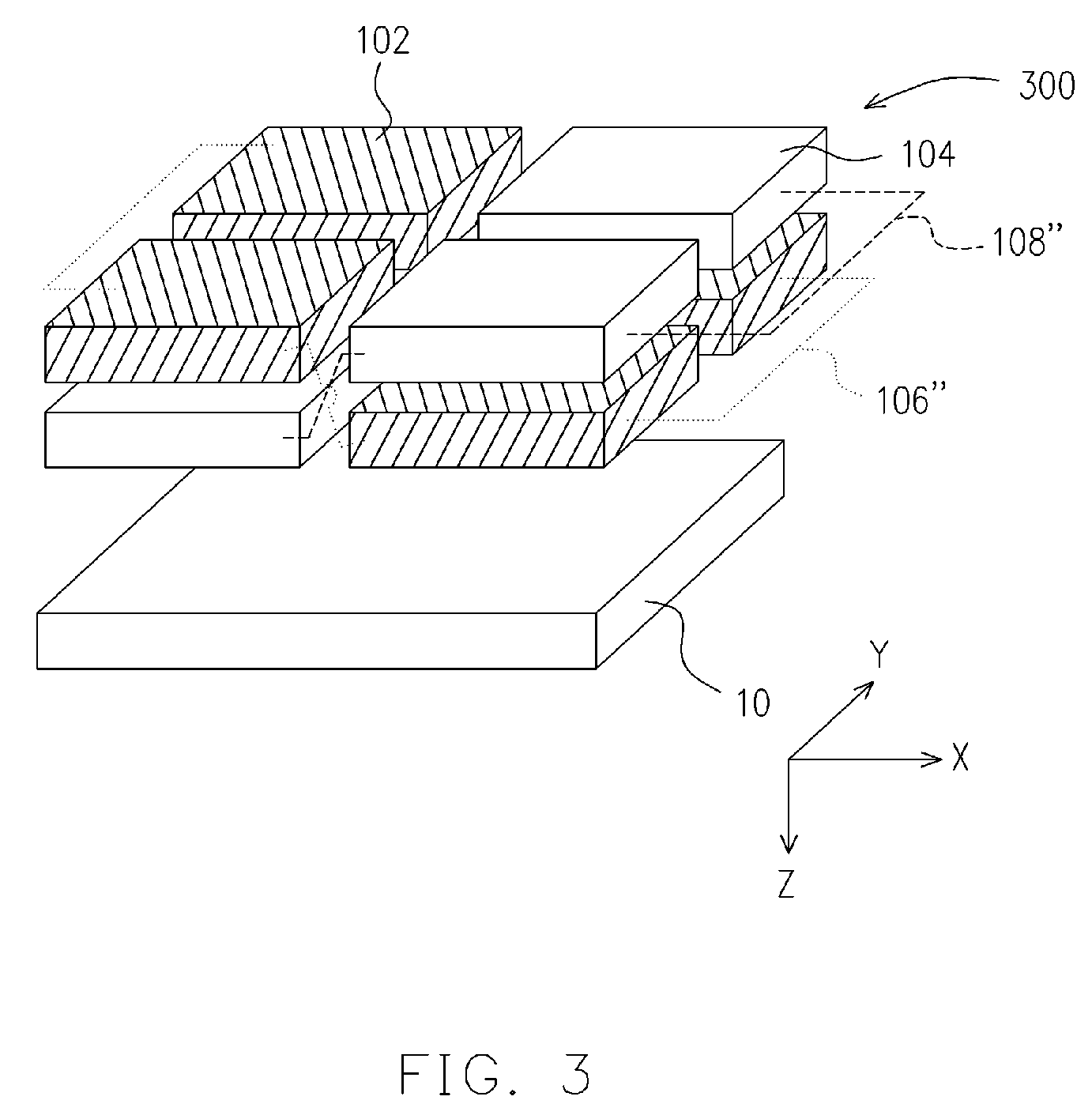

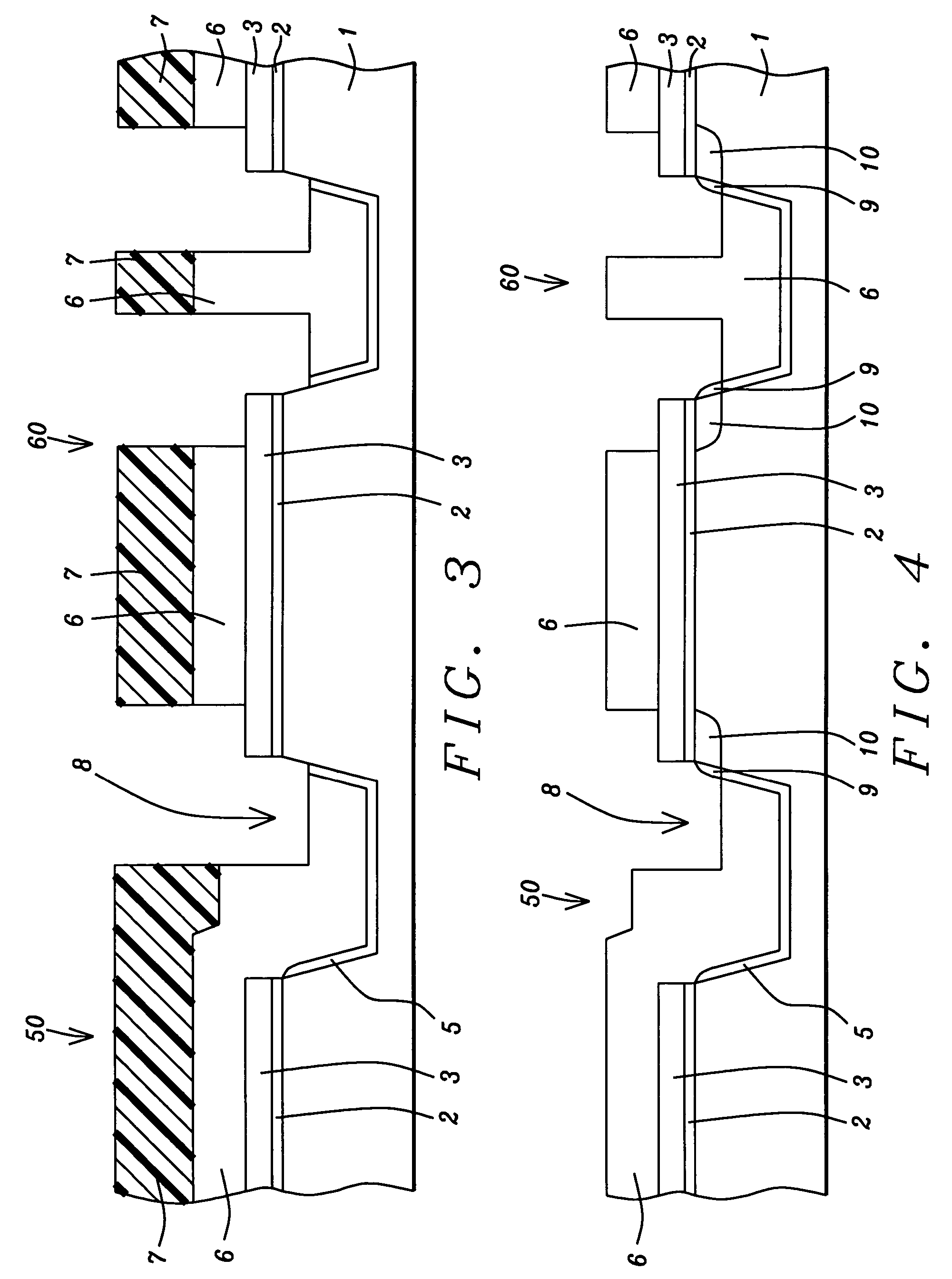

A method for forming a semiconductor device including a DRAM cell structure comprising a silicon on insulator (SOI) substrate with an embedded capacitor structure including providing a substrate comprising an overlying first electrically insulating layer; forming a first electrically conductive layer on the first electrically insulating layer to form a first electrode; forming a capacitor dielectric layer on the first electrode; forming a second electrically conductive layer on the capacitor dielectric layer to form a second electrode; forming a second electrically insulating layer on the second electrode; and, forming a monocrystalline silicon layer over the second electrode to form an SOI substrate comprising a first capacitor structure.

Owner:TAIWAN SEMICON MFG CO LTD

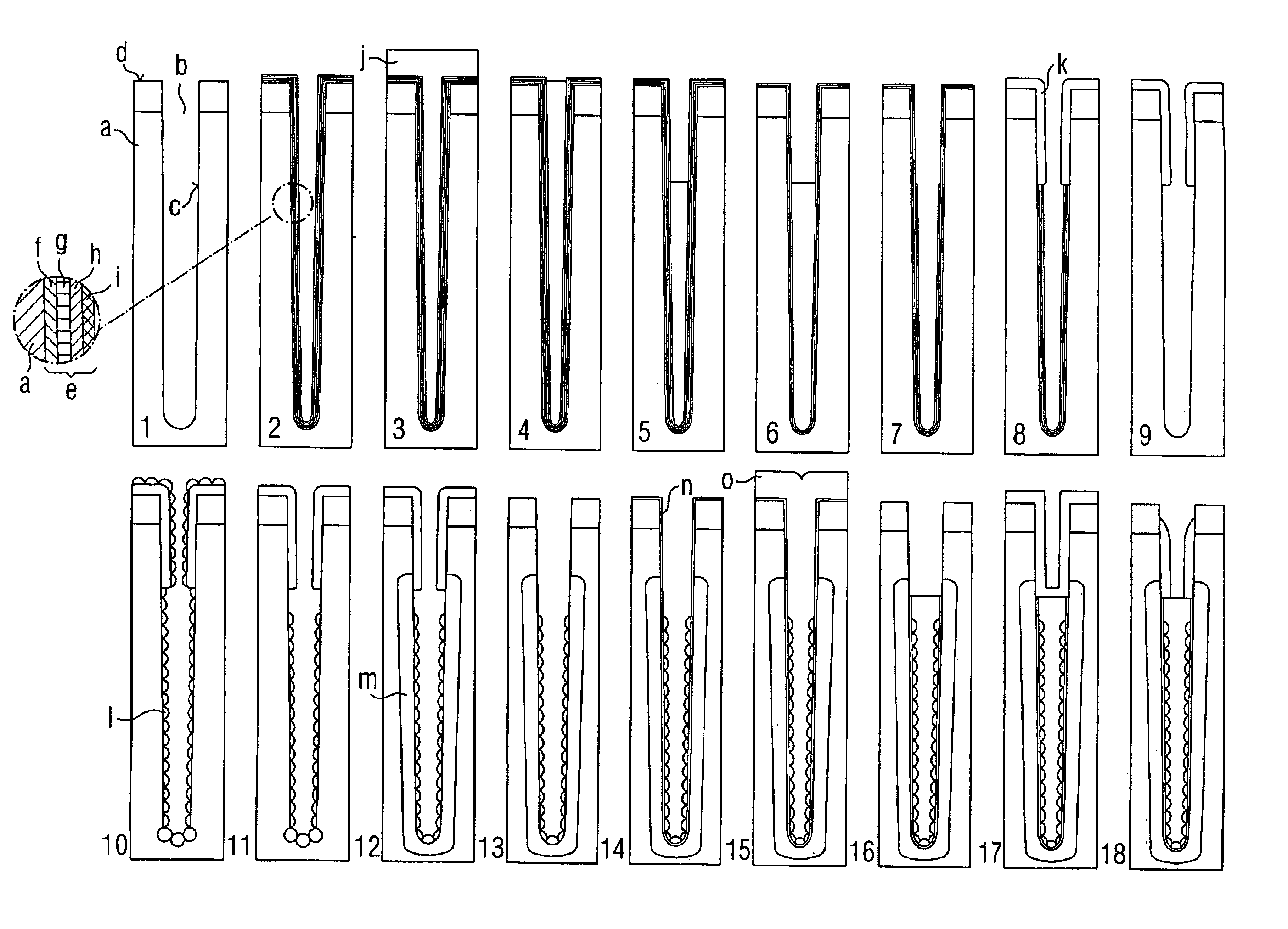

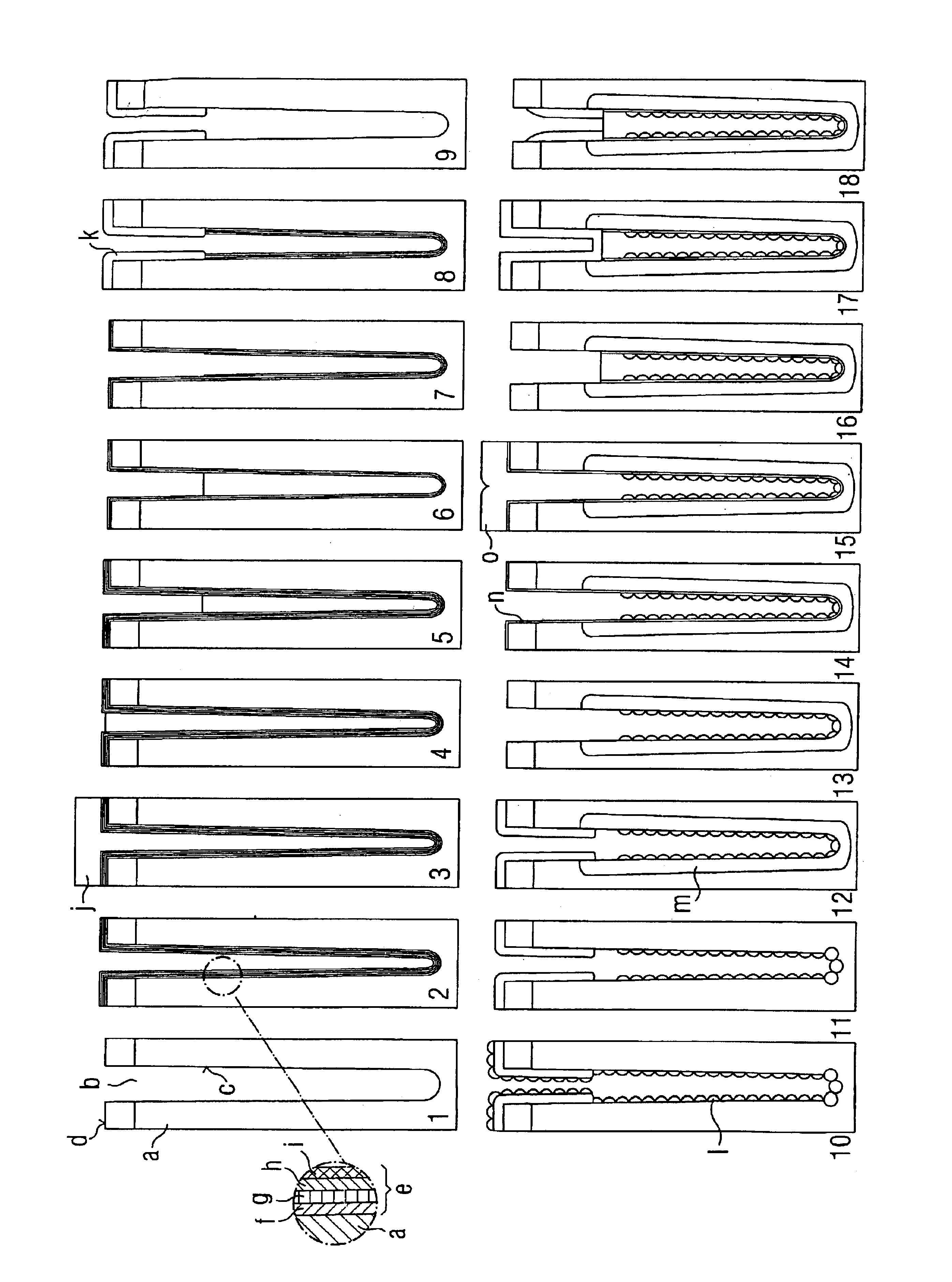

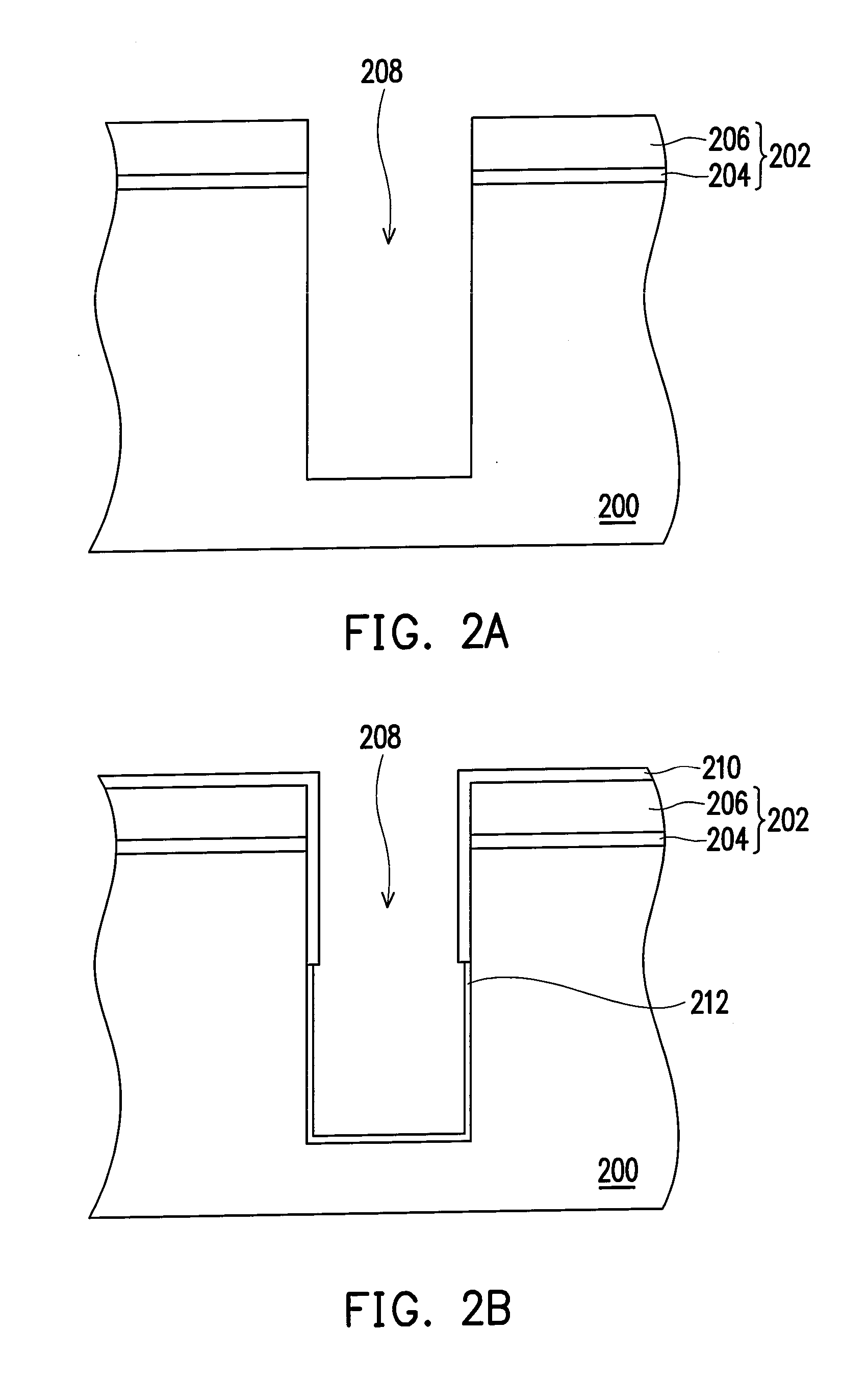

Method for fabricating a deep trench capacitor for dynamic memory cells

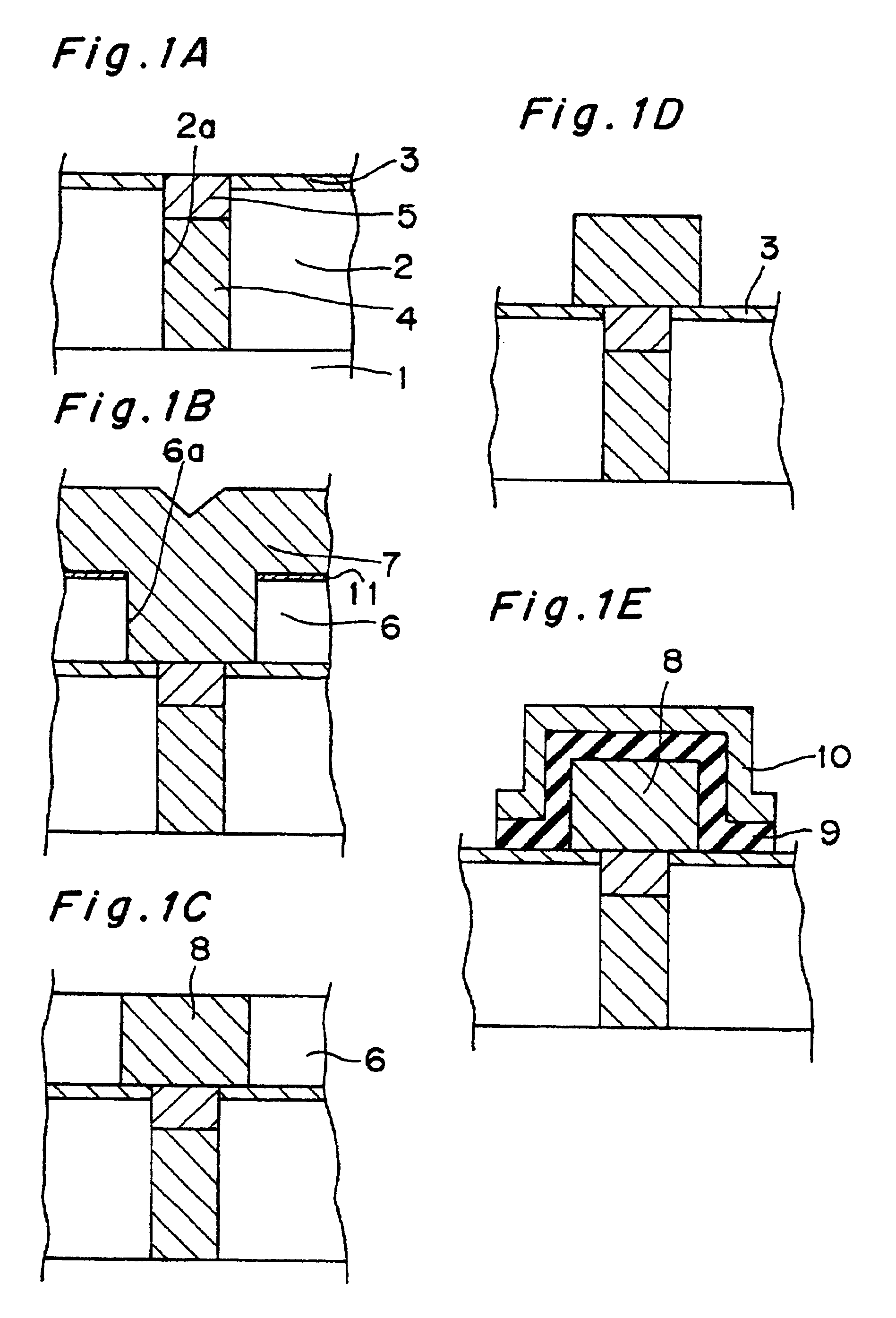

InactiveUS6841443B2Reduce process complexityMask is durableTransistorSolid-state devicesDielectricEngineering

A method for fabricating a deep trench capacitor for dynamic memory cells in which a trench is etched into the depth of a semiconductor substrate, and wherein the interior of the trench is provided with a doping and a dielectric and is filled with a conductive material as an inner electrode. The inner electrode and the dielectric are etched back within a collar region, and a collar is formed using a collar process comprising a collar oxide deposition and etching back of the collar oxide on the substrate surface and in the trench as far as the inner electrode, after which the inner electrode is completed by further steps of depositing and etching back conductive layers. Prior to the doping a masking layer is applied to the collar region of the trench, and this masking layer is removed again before the collar process. Before the dielectric is applied the surface of the lower regions of the trench outside the collar region a layer of grains of conductive material is applied.

Owner:POLARIS INNOVATIONS

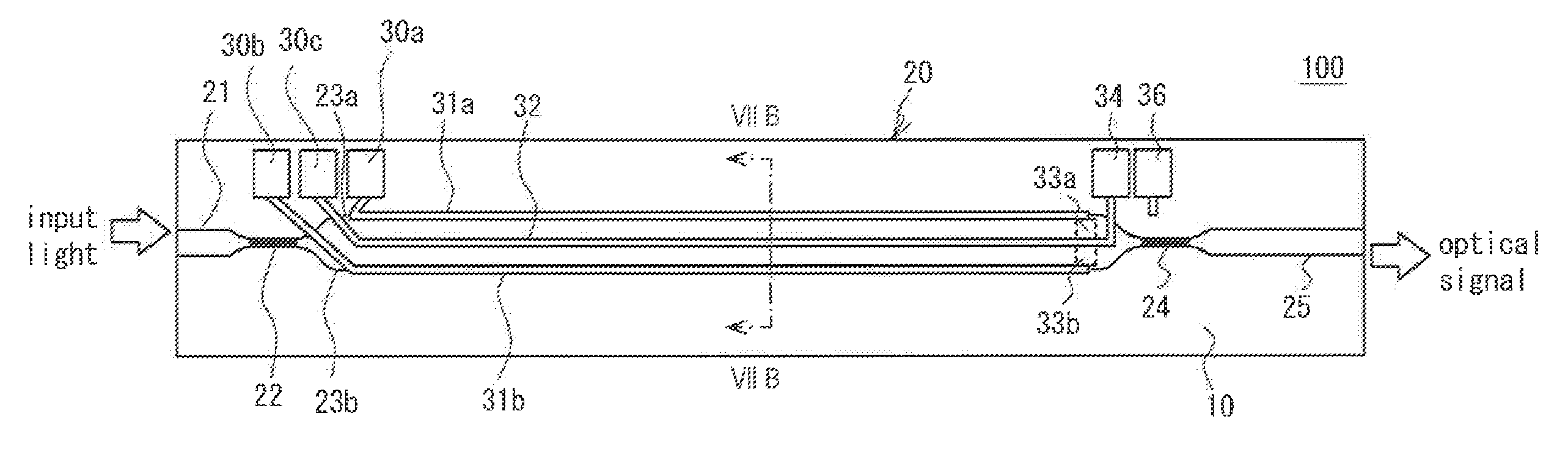

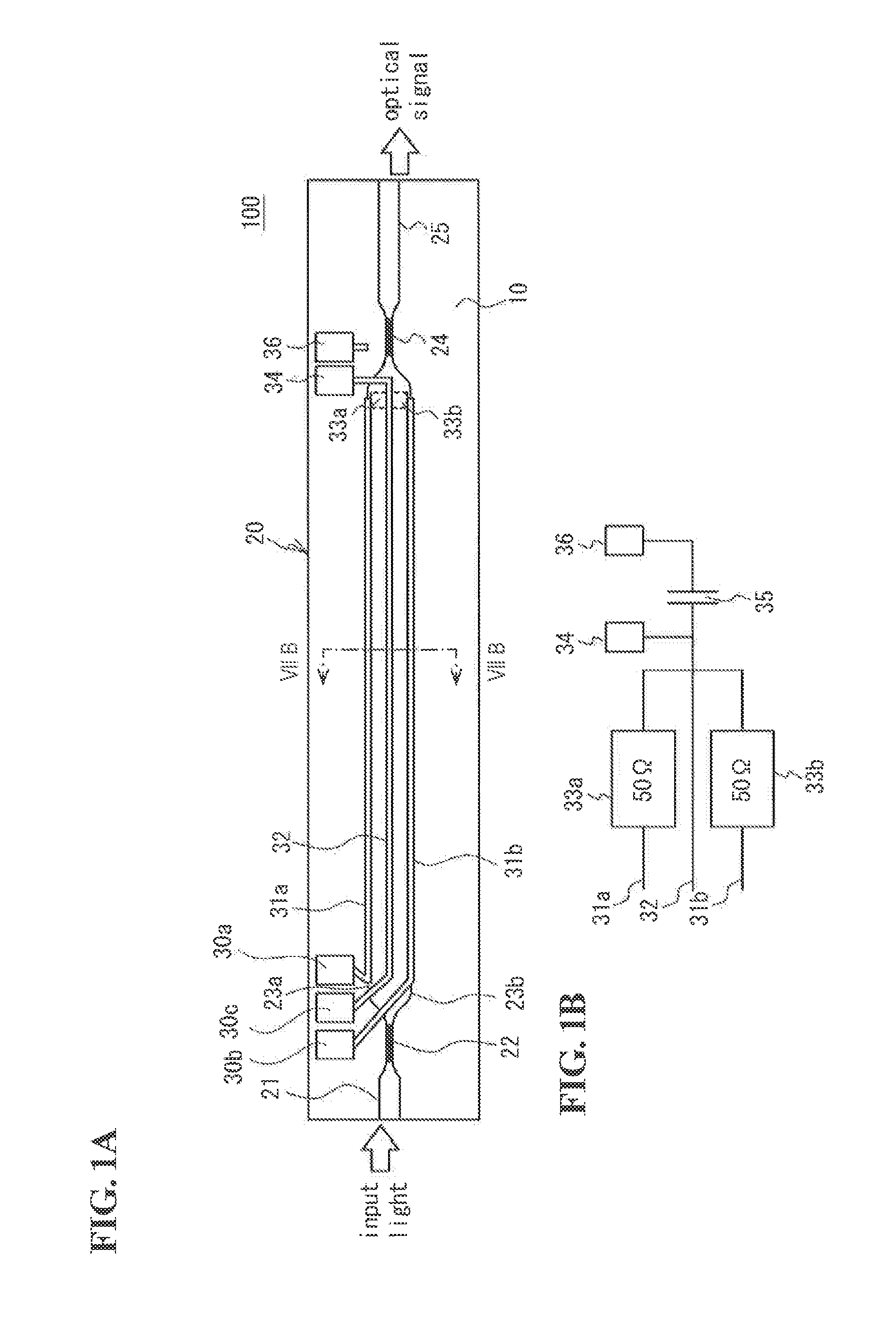

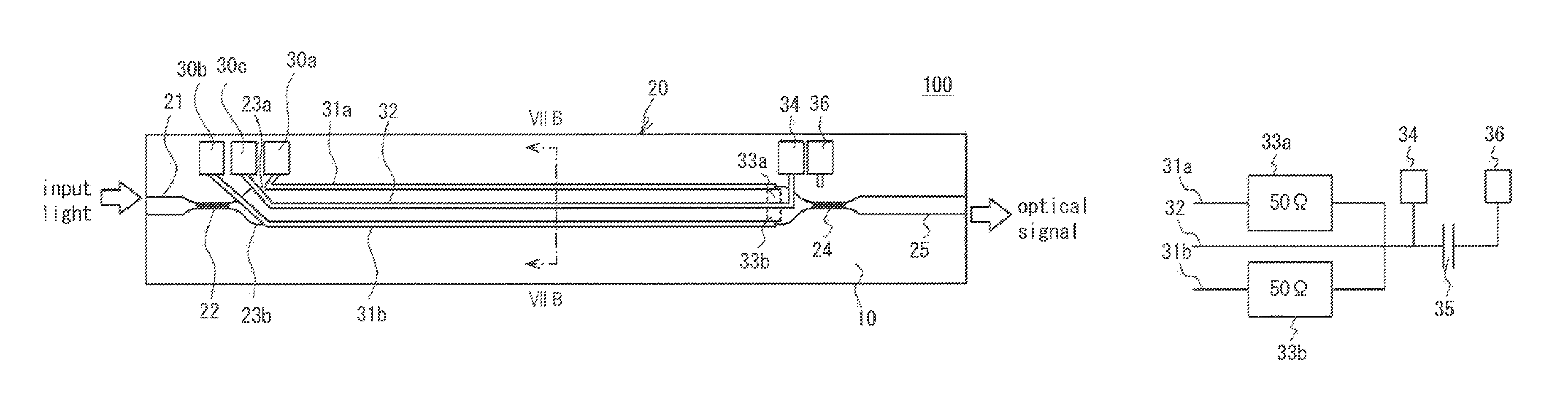

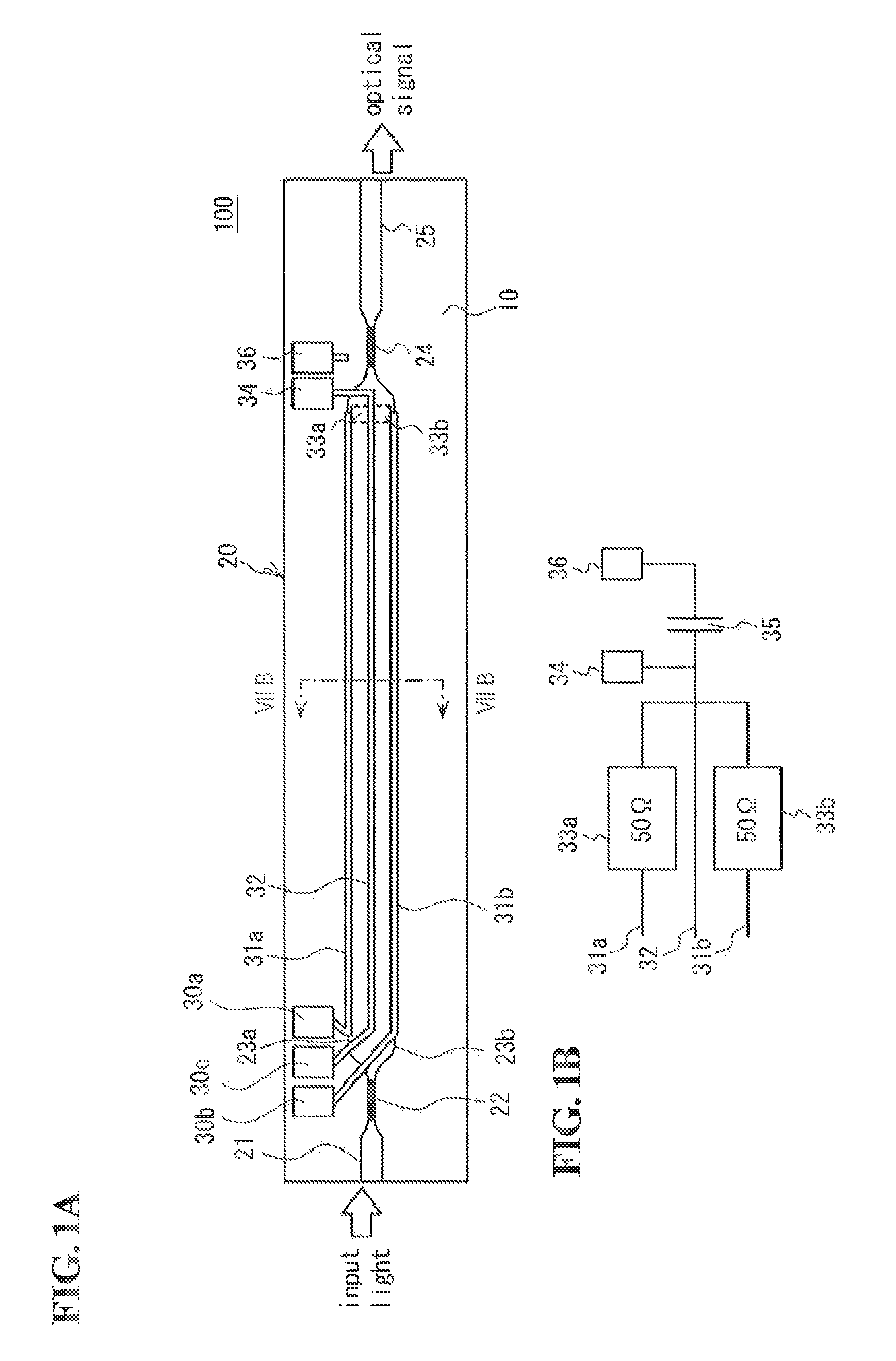

Optical semiconductor device and method of producing the same

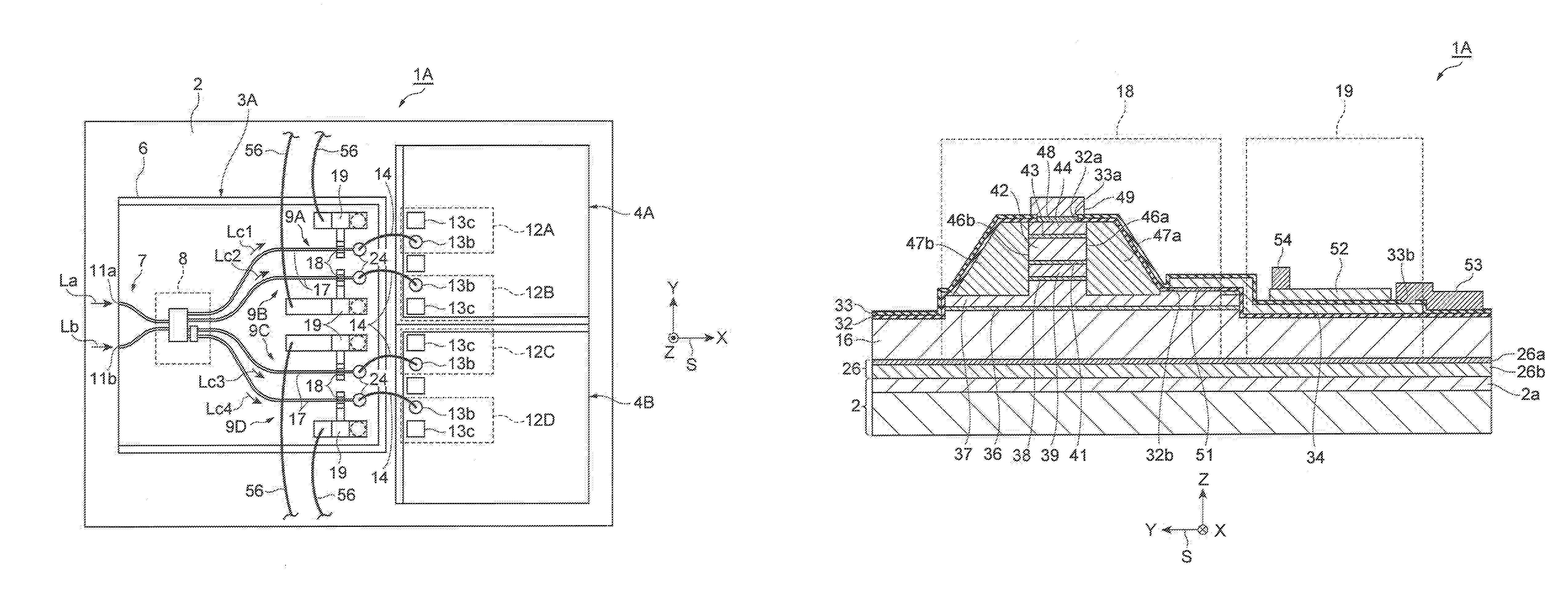

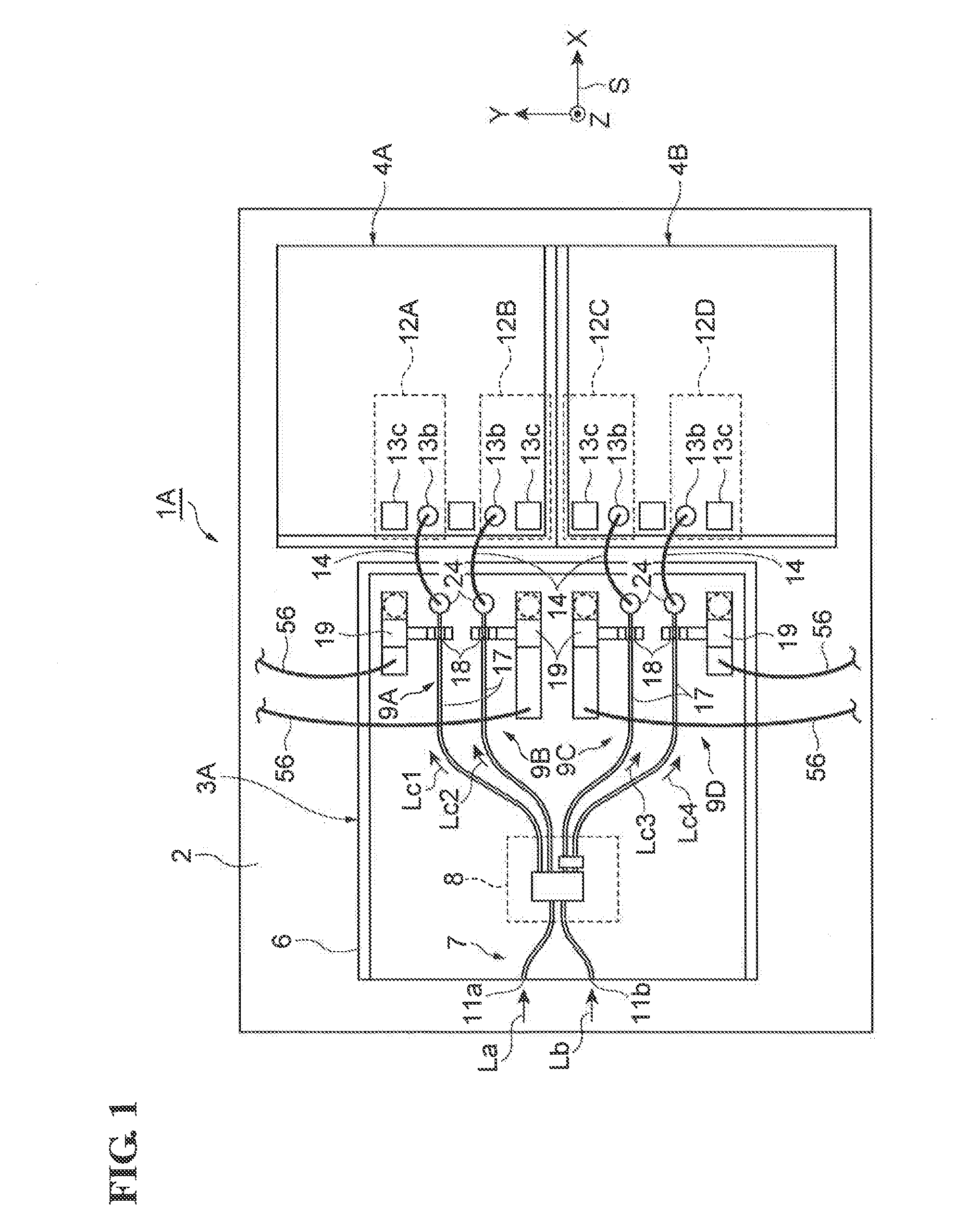

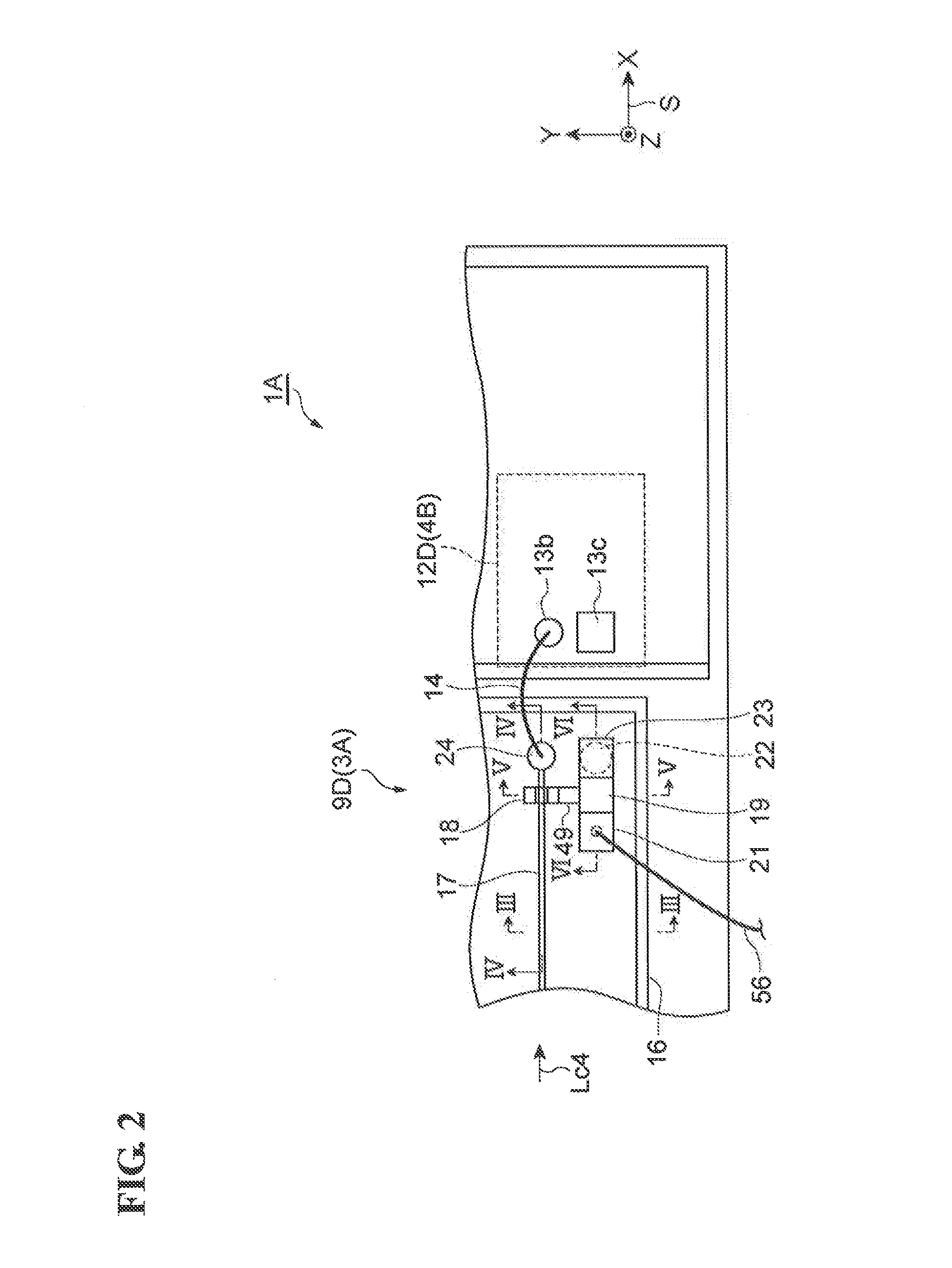

ActiveUS20160026064A1Increase areaReduce areaSemiconductor/solid-state device manufacturingOptical light guidesLight waveSemiconductor

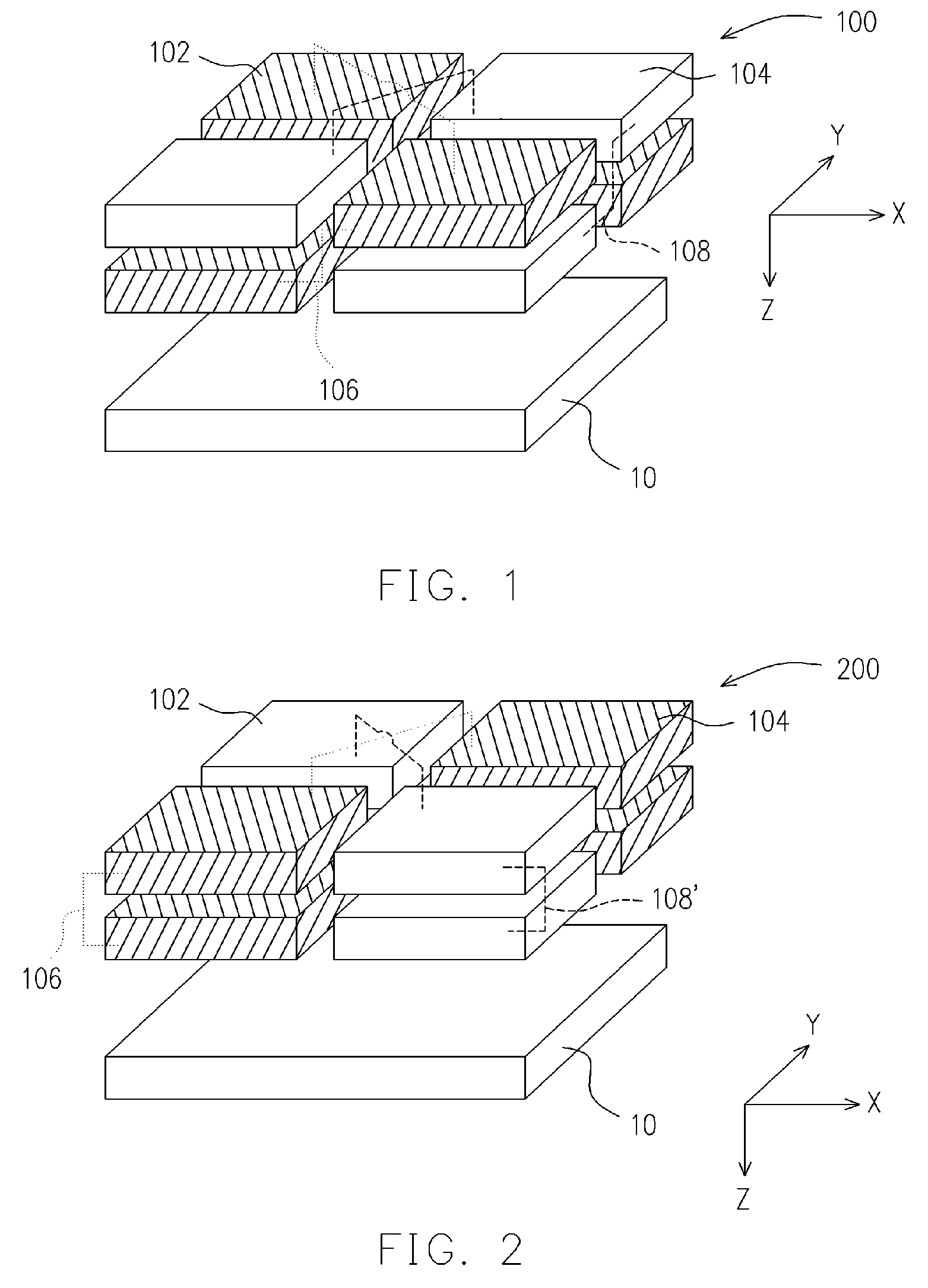

An optical semiconductor device including: a substrate having a principal surface; a first and a second optical waveguides disposed on the principal surface of the substrate, the first and second optical waveguides extending in a first direction, the second optical waveguide being arranged adjacent to the first optical waveguide in a second direction intersecting with the first direction; a first and a second signal electrodes disposed on the first and second optical waveguides; a resistor disposed on the principal surface, the resistor being arranged between the first optical waveguide and the second optical waveguide, the resistor being electrically connected to the first signal electrode and the second signal electrode; a resin layer disposed on the principal surface, top surfaces of the first and second signal electrodes, and the resistor; and a capacitor disposed on the resin layer, the capacitor being electrically connected to the resistor through an opening of the resin layer.

Owner:SUMITOMO ELECTRIC IND LTD

Floating gate type EEPROM (Electrically Erasable Programmable Read Only Memory) device and manufacturing method thereof

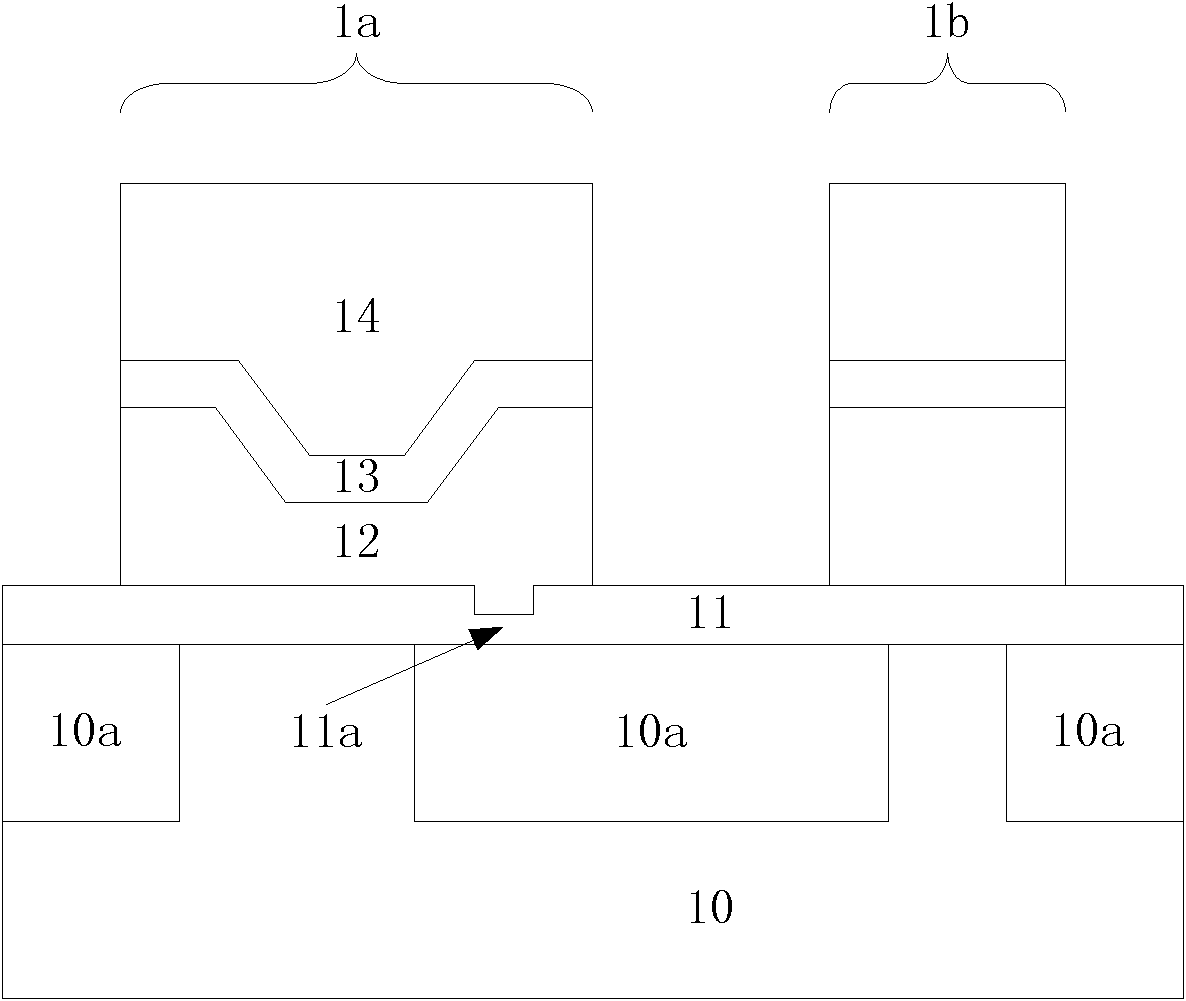

InactiveCN102760737AIncrease capacitor areaIncreased Voltage Coupling EfficiencyTransistorSolid-state devicesCoupling efficiencyEtching

The invention discloses a floating gate type EEPROM (Electrically Erasable Programmable Read Only Memory) device. A memory cell of the EEPROM device comprises a memory transistor and a selection transistor, wherein the memory transistor comprises a floating gate positioned at the lower part and a control gate positioned at the upper part; and a dielectric layer is arranged between the floating gate and the control gate, and is in a curved surface shape. The invention further discloses a manufacturing method of the device, which mainly comprises the step that the floating gate is subjected to shallow trench etching, so that the dielectric layer is in the concave curved surface shape. Compared with the traditional flat dielectric layer, the capacitance area is increased; and the increased capacitance is proportional to the depth of a shallow trench, so that the voltage coupling efficiency and the coupled voltage are increased, and the area of the existing device can be kept or even reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Method to reduce a capacitor depletion phenomena

A method of integrating the fabrication of a capacitor cell and a logic device region, wherein the surface area of a capacitor region is increased, and the risk of a capacitor depletion phenomena is reduced, has been developed. After formation of insulator filled STI regions featuring tapered sides, a portion of the insulator layer in an STI region is recessed below the top surface of the semiconductor substrate exposing a bare, tapered side of the semiconductor substrate. Ion implantation into the tapered side of the portion of semiconductor substrate exposed in the recessed STI portion, as well as into a top portion of semiconductor substrate located adjacent to the recessed STI portion, results in formation of a capacitor region now greater in surface area than a counterpart capacitor region which is formed via implantation into only a top portion of semiconductor substrate. Growth of a gate insulator layer and definition of gate structures in the logic device region, also simultaneously forms a capacitor dielectric layer on the underlying capacitor region, as well as a capacitor plate structure in the capacitor cell region.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor device substrate with embedded capacitor

InactiveUS7235838B2Increase capacitor areaSpace utilizationTransistorSolid-state devicesSoi substrateDielectric layer

A method for forming a semiconductor device including a DRAM cell structure comprising a silicon on insulator (SOI) substrate with an embedded capacitor structure including providing a substrate comprising an overlying first electrically insulating layer; forming a first electrically conductive layer on the first electrically insulating layer to form a first electrode; forming a capacitor dielectric layer on the first electrode; forming a second electrically conductive layer on the capacitor dielectric layer to form a second electrode; forming a second electrically insulating layer on the second electrode; and, forming a monocrystalline silicon layer over the second electrode to form an SOI substrate comprising a first capacitor structure.

Owner:TAIWAN SEMICON MFG CO LTD

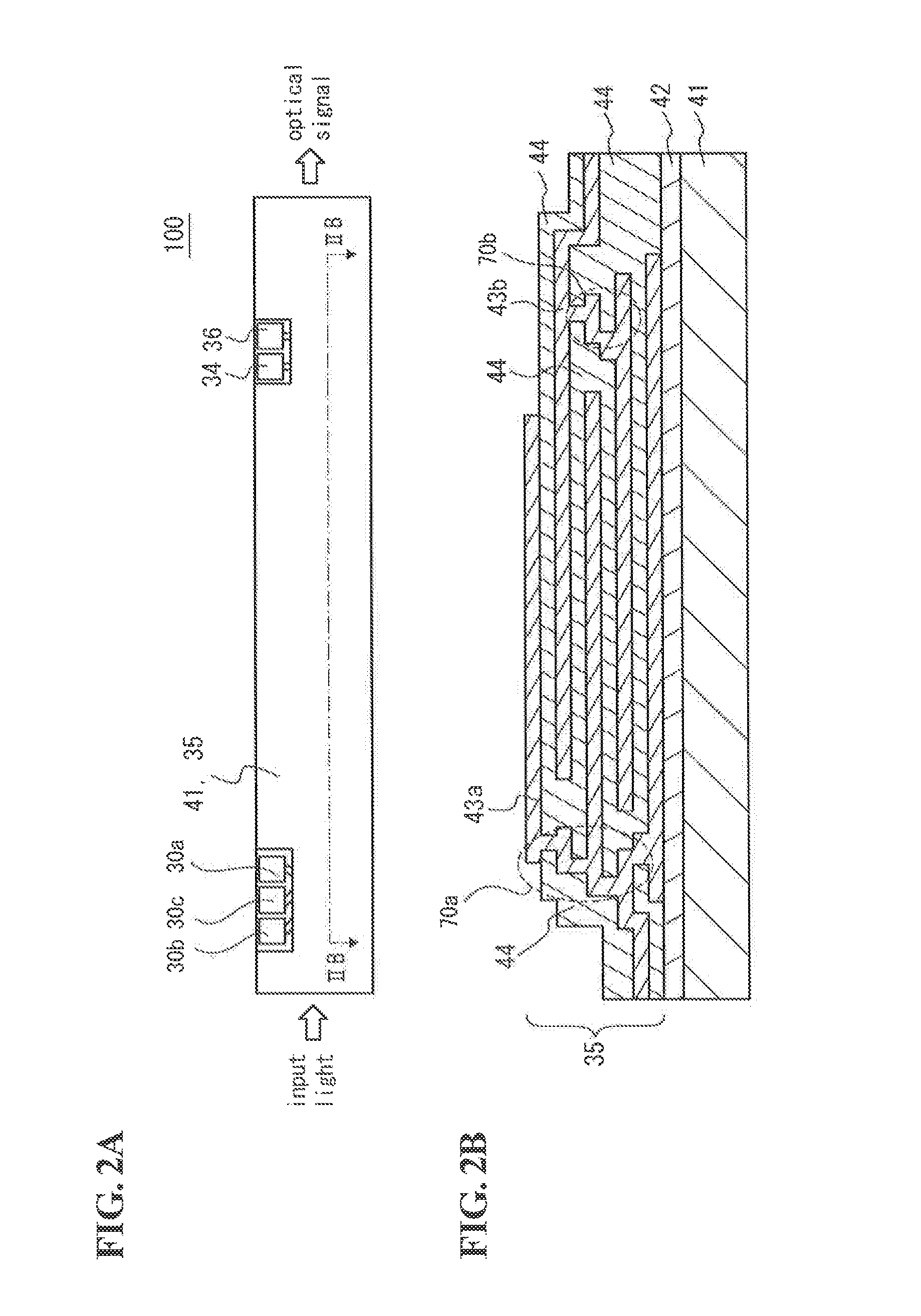

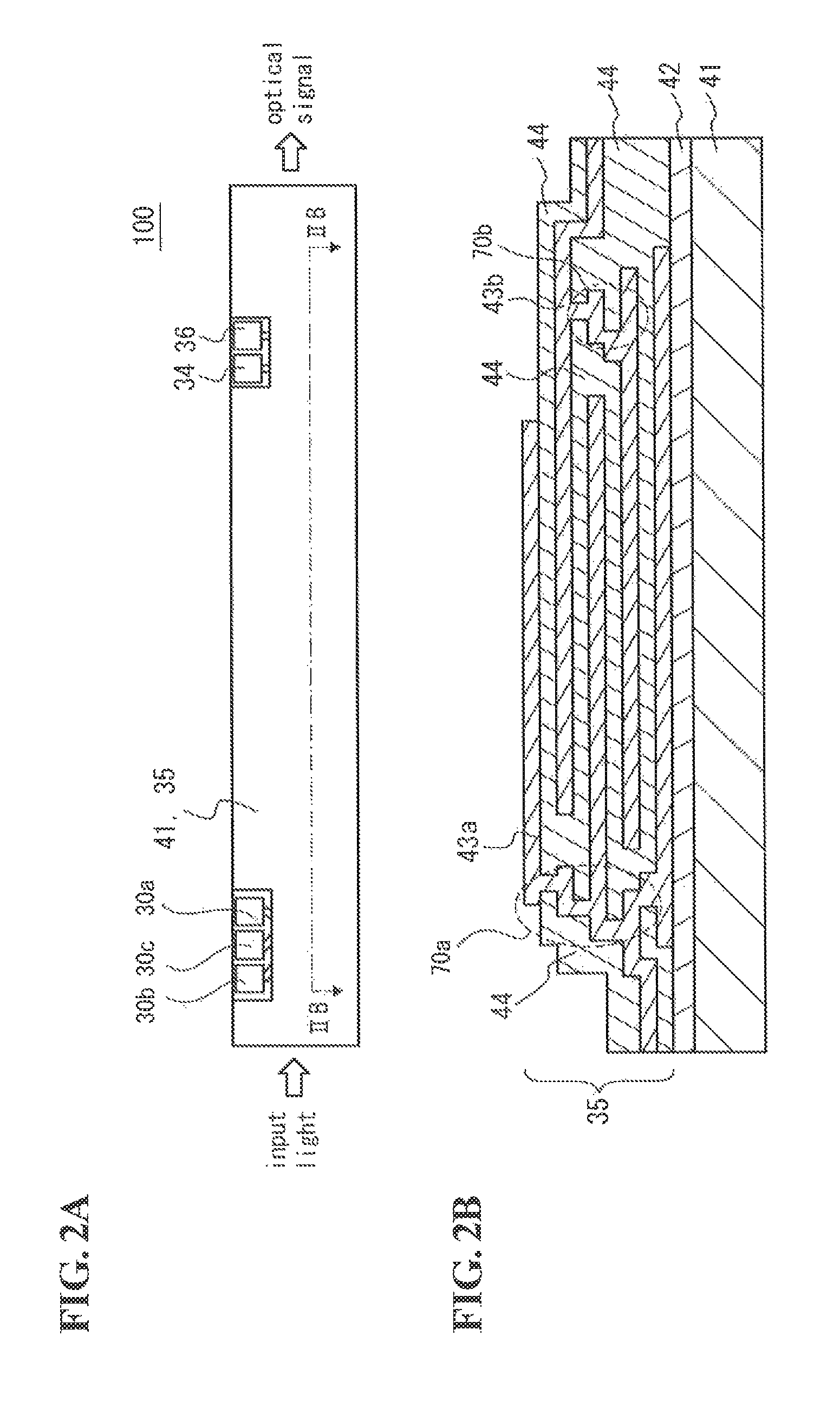

Optical-to-electrical converter unit and semiconductor light-receiving device

ActiveUS20140246746A1Parasitic capacitance is generatedReduce parasitic capacitanceOptical light guidesSemiconductor devicesElectricityCapacitance

An optical-to-electrical converter unit includes a substrate having front and back surfaces; an optical waveguide unit; and an optical-to-electrical converter. The optical-to-electrical converter includes a light-receiving element optically coupled to the optical waveguide unit; a capacitance element including first and second conductive layers and an insulating layer disposed between the first and second conducive layers; an electrode pad electrically connected to the light-receiving element; a back electrode formed on the back surface of the substrate; and a via electrode extending from the front surface to the back surface of the substrate. The optical waveguide unit, the light-receiving element, the capacitance element, and the electrode pad are formed on the front surface. The first conductive layer of the capacitance element is electrically connected to the light-receiving element and the electrode pad. The second conductive layer of the capacitance element is electrically connected to the back electrode through the via electrode.

Owner:SUMITOMO ELECTRIC IND LTD

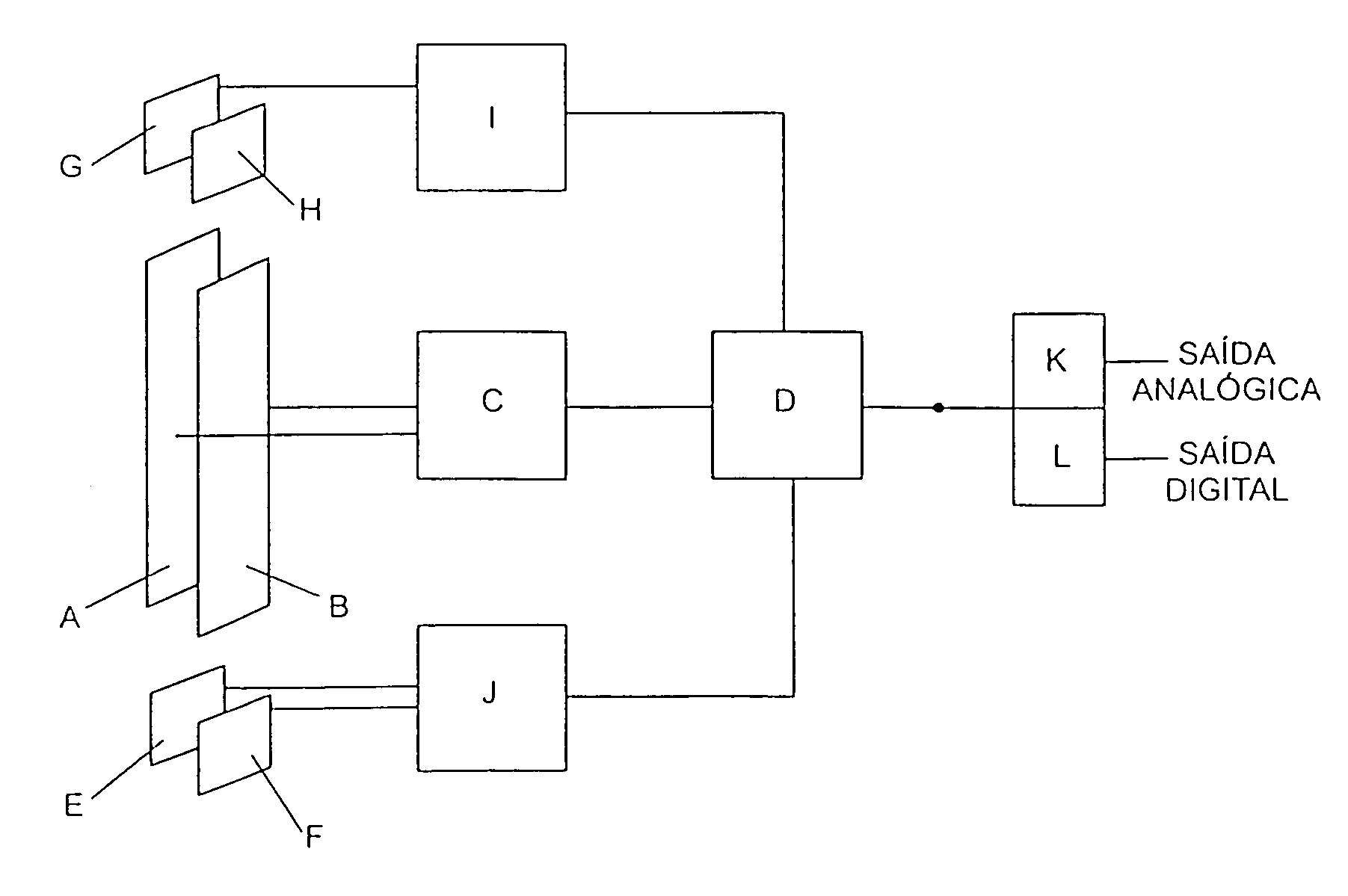

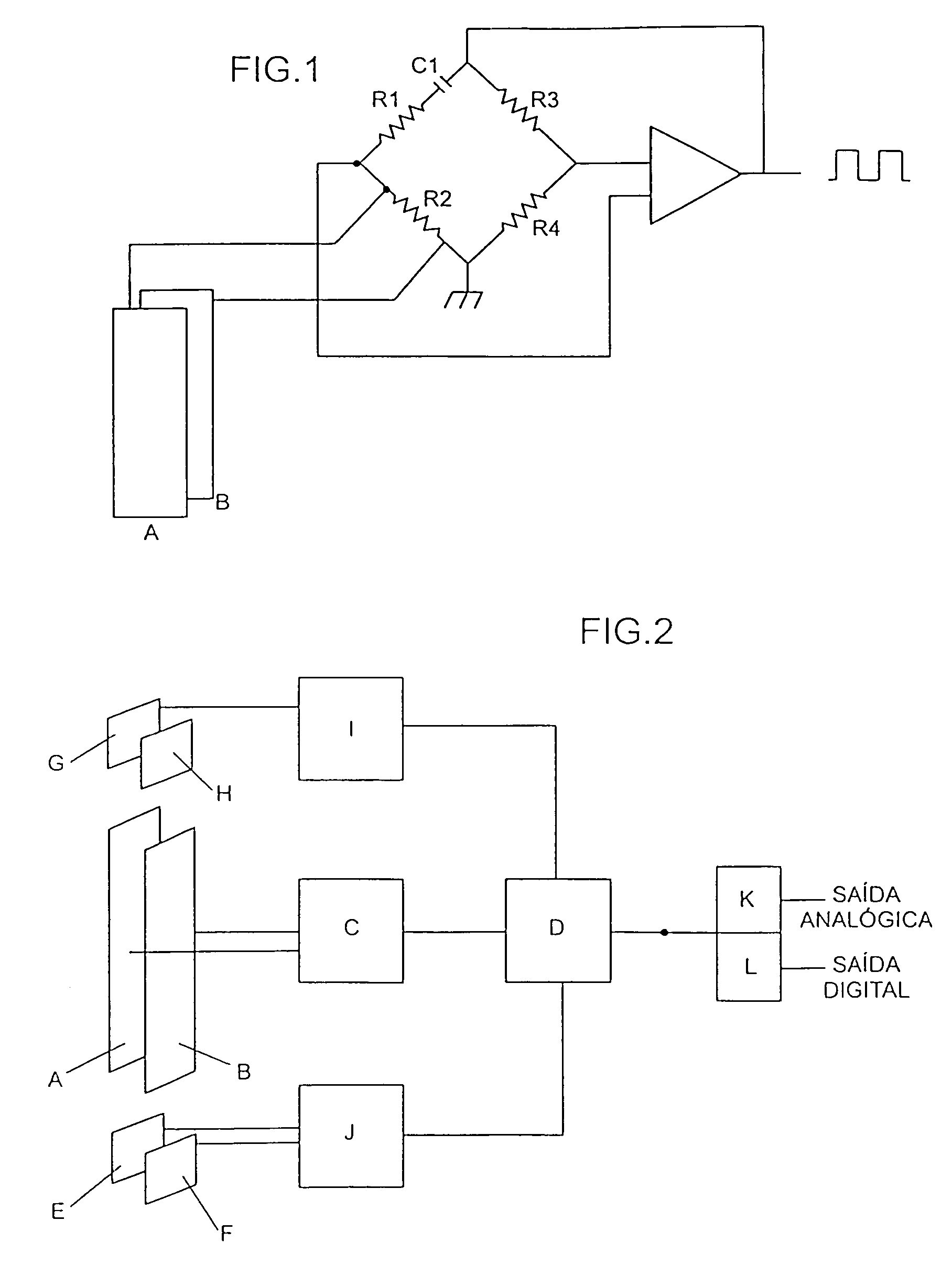

Apparatus for measuring and indicating the level and/or volume of a liquid stored in a container

InactiveUS7441455B2Increase capacitor areaReduce distanceMachines/enginesAlarmsBiomedical engineeringCapacitor

Owner:INDEBRAS IND ELETROMECANICA BRASILEIRA

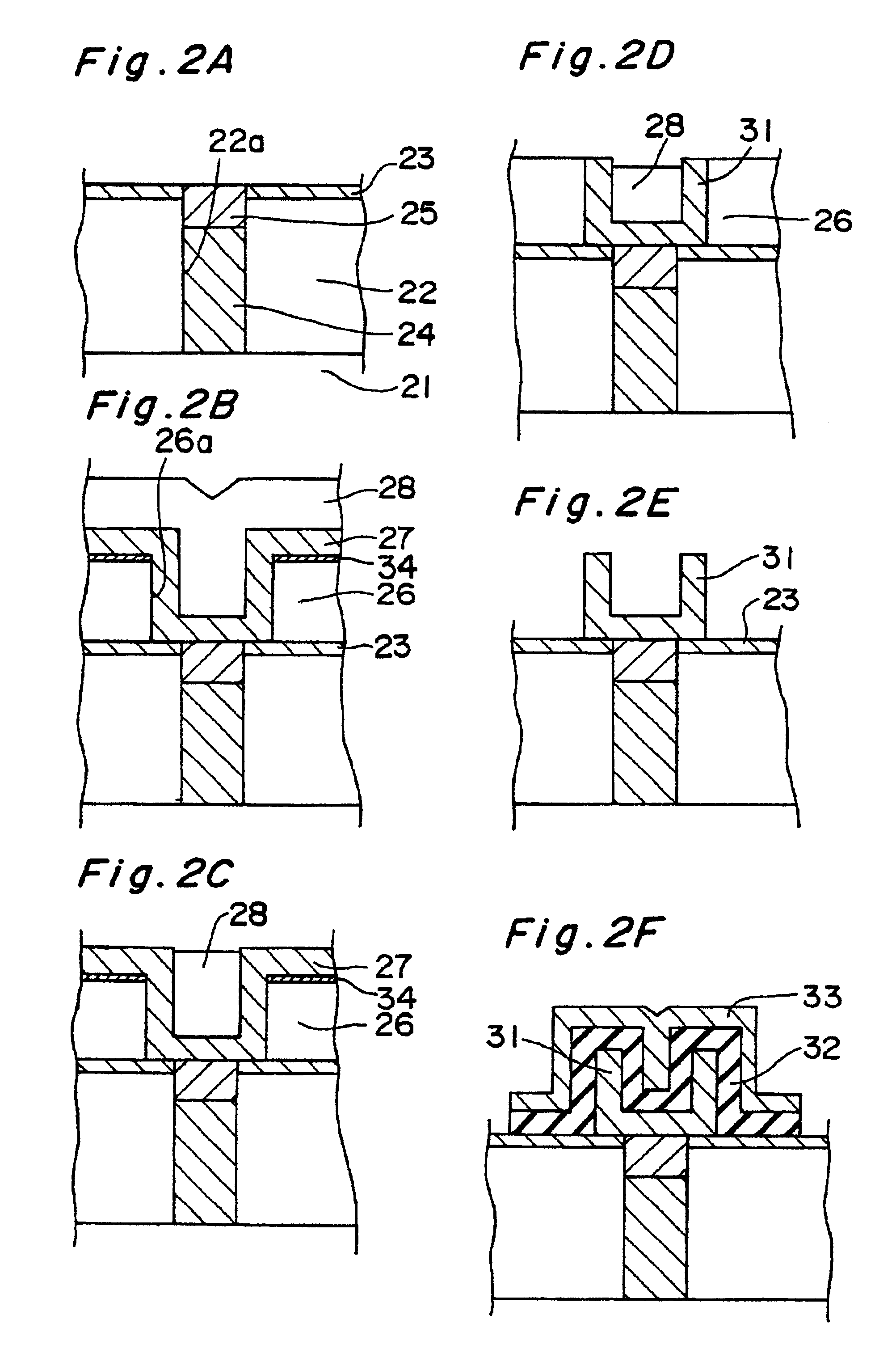

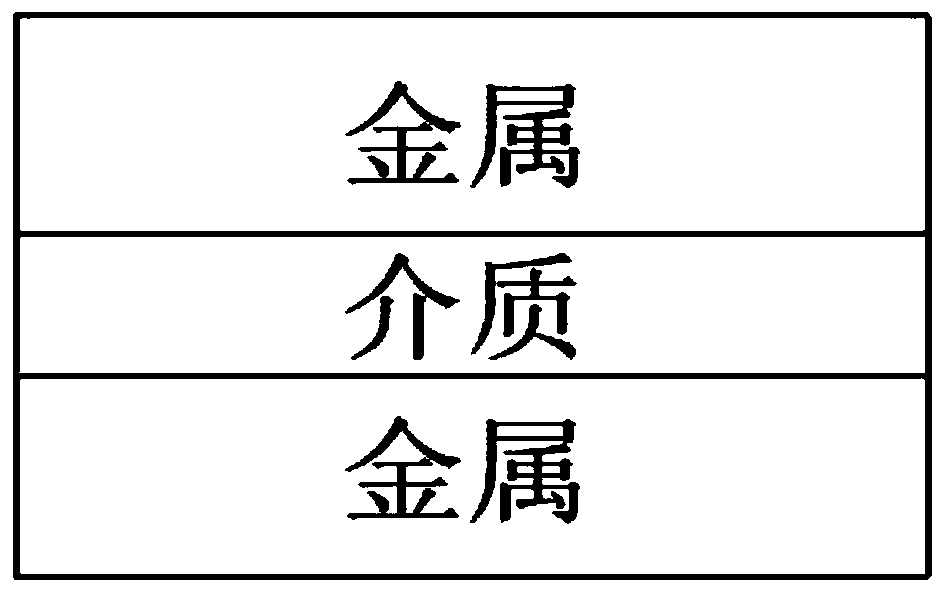

Method of fabricating MIM capacitor

InactiveUS7235453B2Increase capacitanceIncrease capacitor areaTransistorSemiconductor/solid-state device detailsCapacitanceHigh capacitance

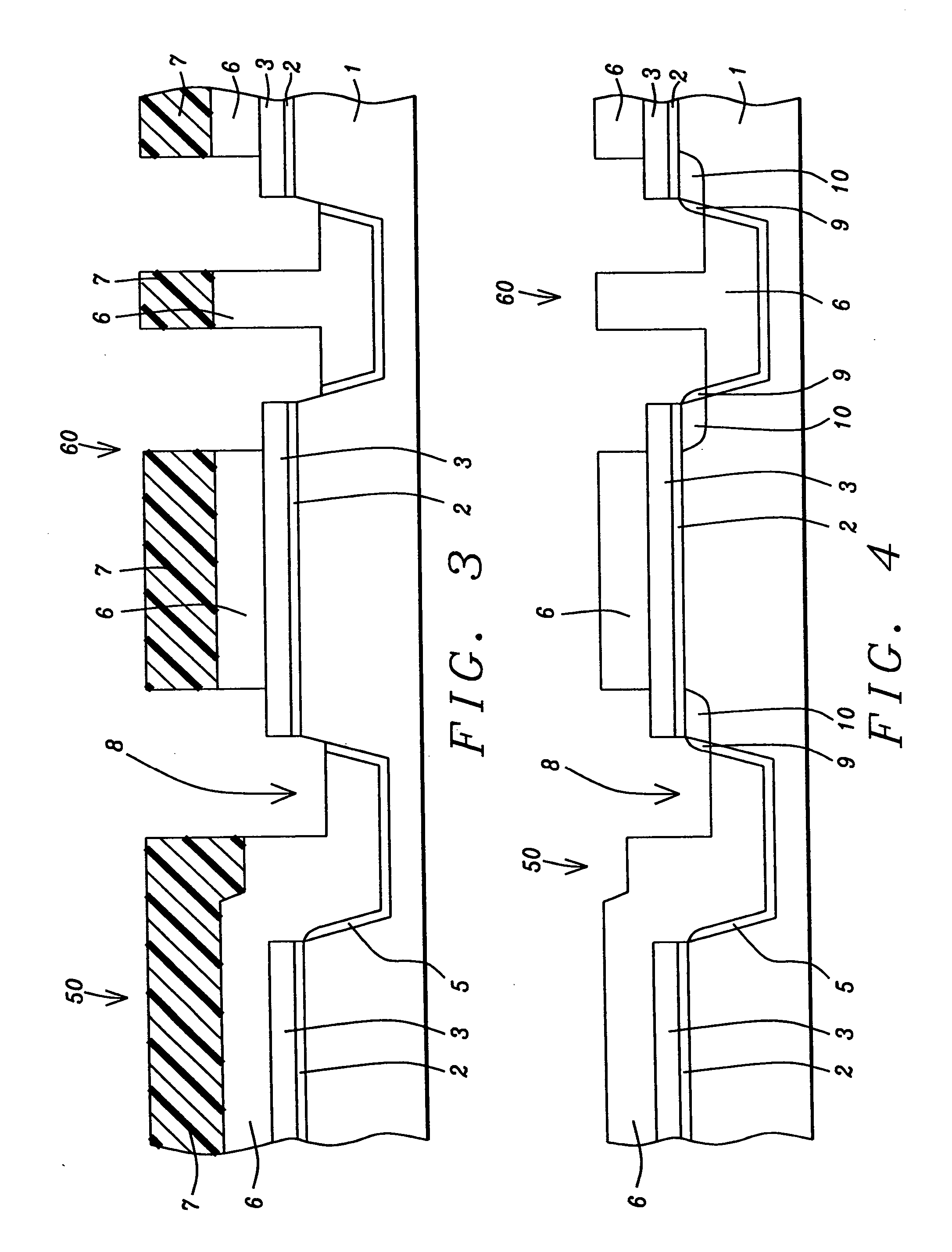

A method of fabricating an MIM capacitor is provided, by which higher capacitance can be secured per unit volume or area by forming a dual-stack type capacitor to increase an effective area of the capacitor. The method includes patterning a first metal layer, forming a planarized second insulating layer having a trench exposing a portion of the patterned first metal layer, forming a second metal layer within the trench, forming a first dielectric layer on the second metal layer, forming first via holes exposing the patterned first metal layer, forming first plugs filling the trench and first via holes, forming a third metal layer thereover, forming a second dielectric layer on the third metal layer, forming a patterned fourth metal layer on the second dielectric layer, patterning the second dielectric layer and the third metal layer, forming a planarized third insulating layer having second via holes therein, and forming a patterned fifth metal layer on the third insulating layer.

Owner:DONGBU ELECTRONICS CO LTD

Method to reduce a capacitor depletion phenomena

A method of integrating the fabrication of a capacitor cell and a logic device region, wherein the surface area of a capacitor region is increased, and the risk of a capacitor depletion phenomena is reduced, has been developed. After formation of insulator filled STI regions featuring tapered sides, a portion of the insulator layer in an STI region is recessed below the top surface of the semiconductor substrate exposing a bare, tapered side of the semiconductor substrate. Ion implantation into the tapered side of the portion of semiconductor substrate exposed in the recessed STI portion, as well as into a top portion of semiconductor substrate located adjacent to the recessed STI portion, results in formation of a capacitor region now greater in surface area than a counterpart capacitor region which is formed via implantation into only a top portion of semiconductor substrate. Growth of a gate insulator layer and definition of gate structures in the logic device region, also simultaneously forms a capacitor dielectric layer on the underlying capacitor region, as well as a capacitor plate structure in the capacitor cell region.

Owner:TAIWAN SEMICON MFG CO LTD

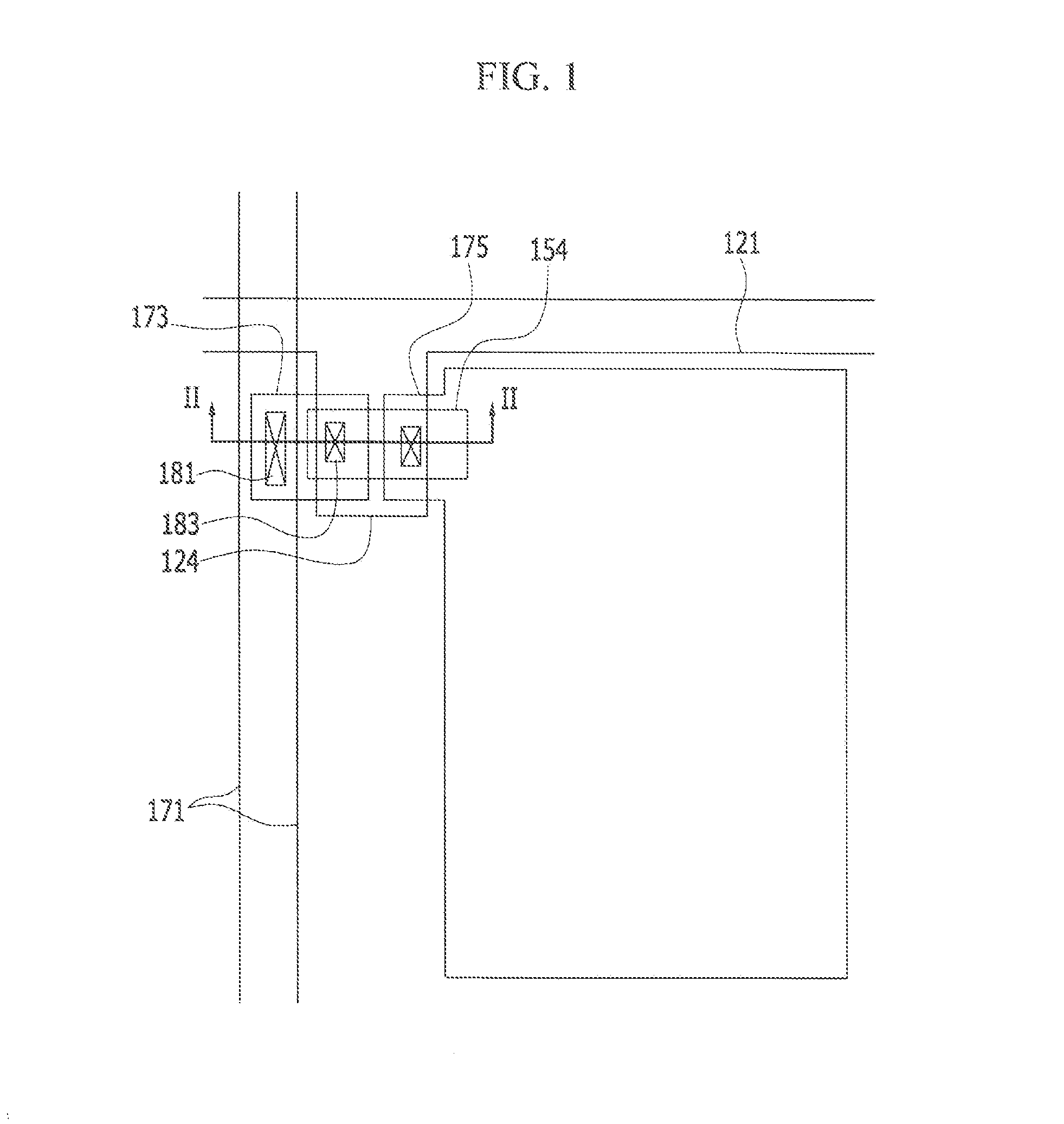

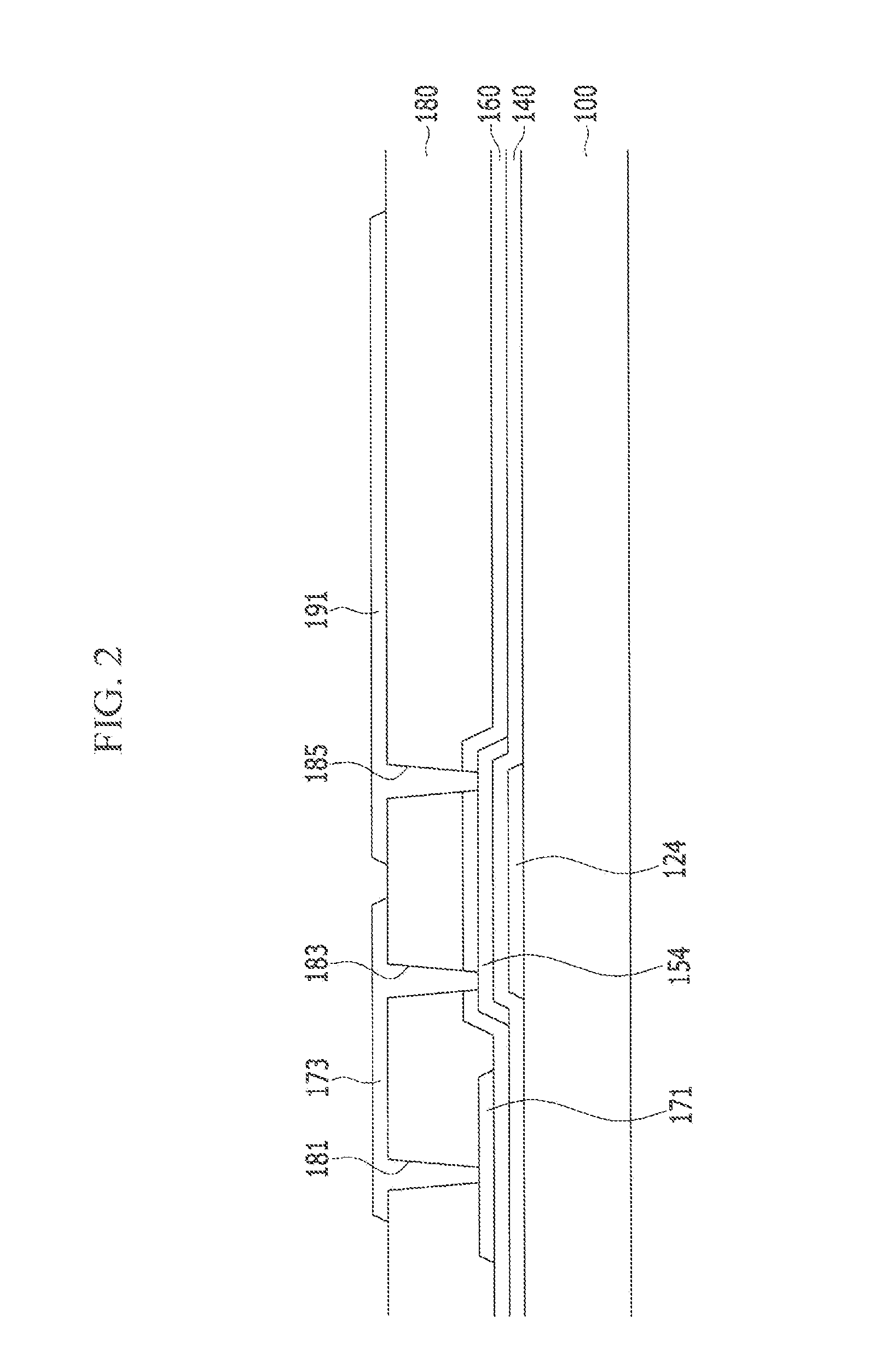

Thin film transistor array panel and organic light emitting diode display including the same

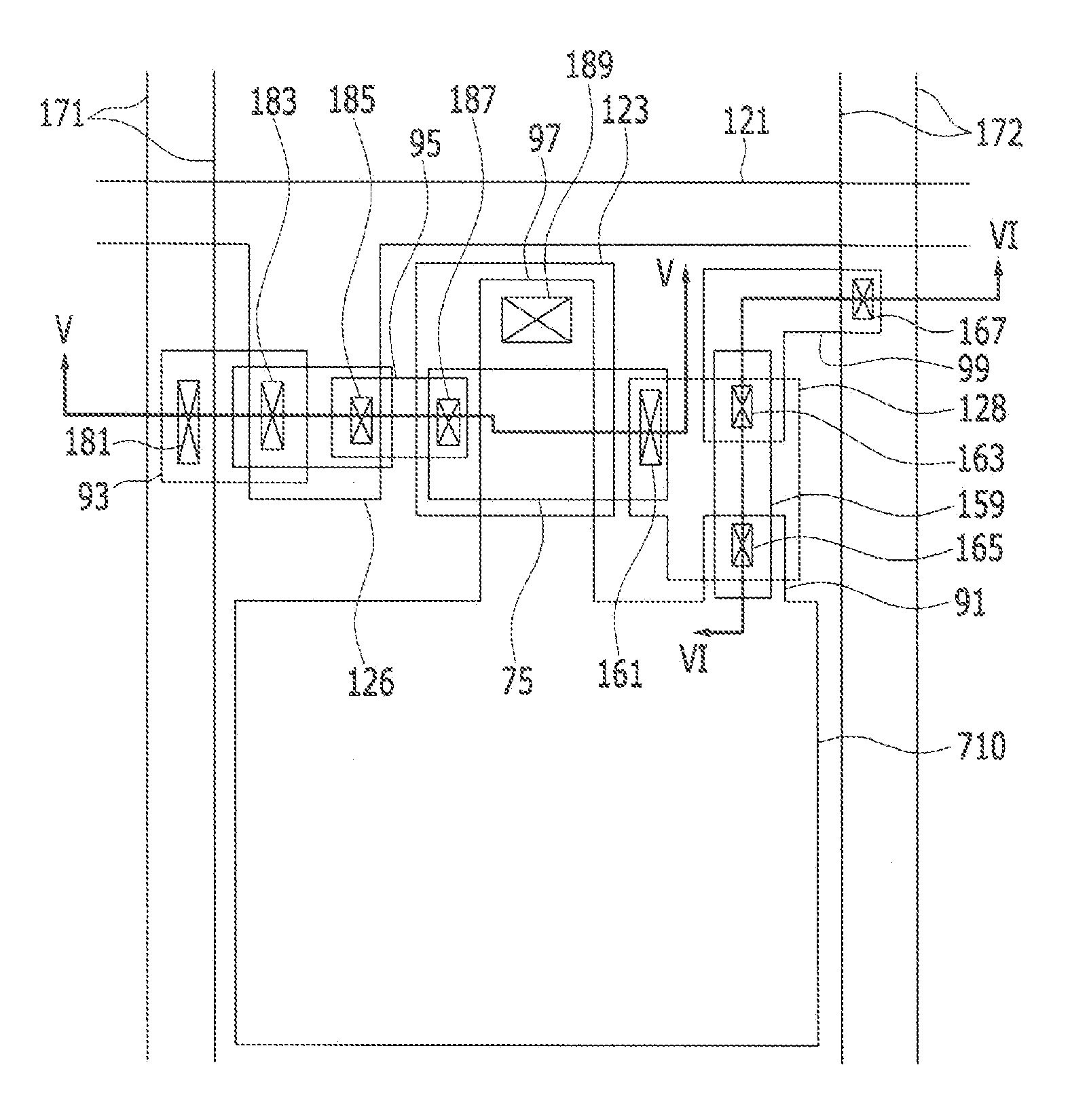

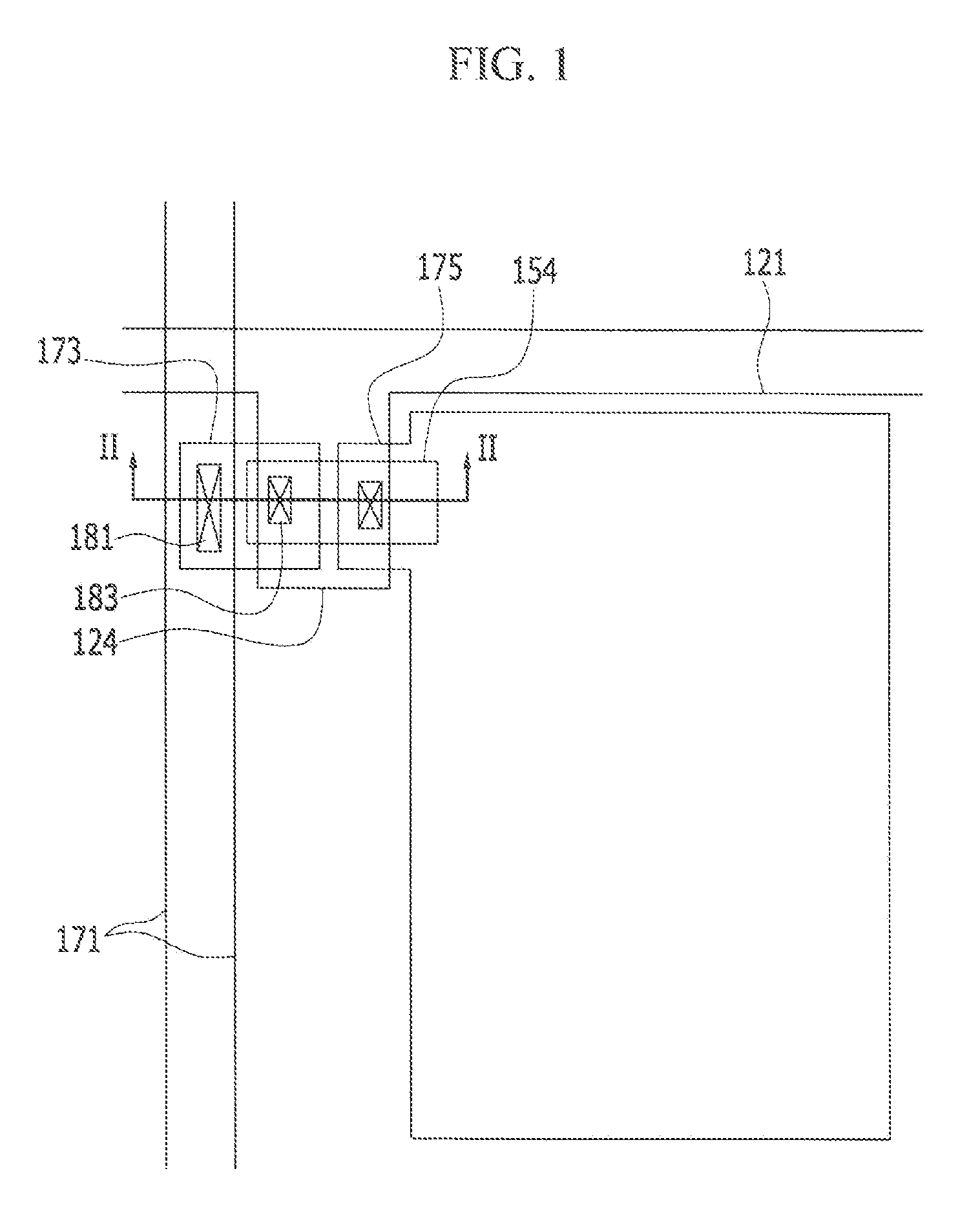

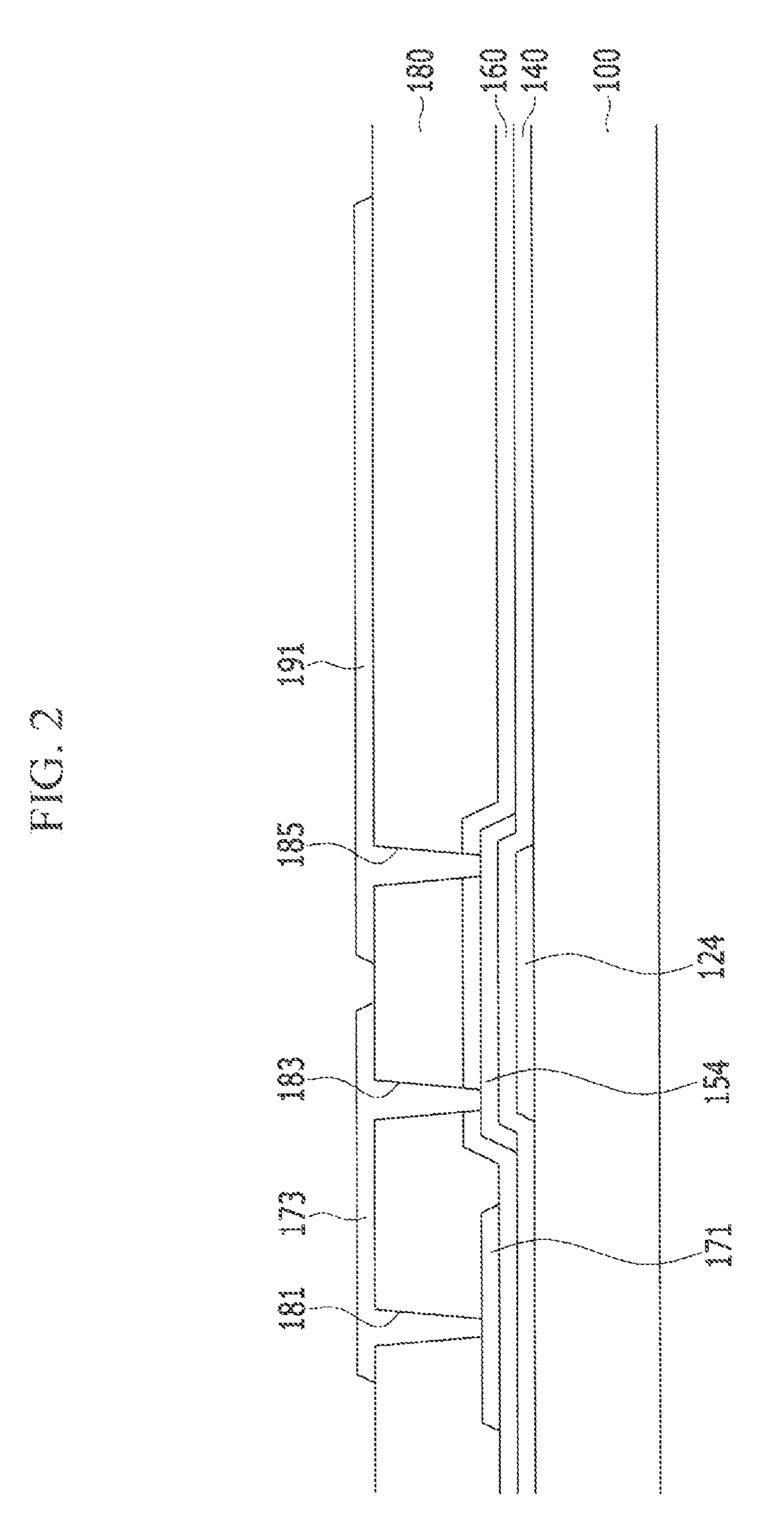

ActiveUS20140103317A1Reduce sizeIncrease the aperture ratioTransistorSolid-state devicesPhysicsOxide semiconductor

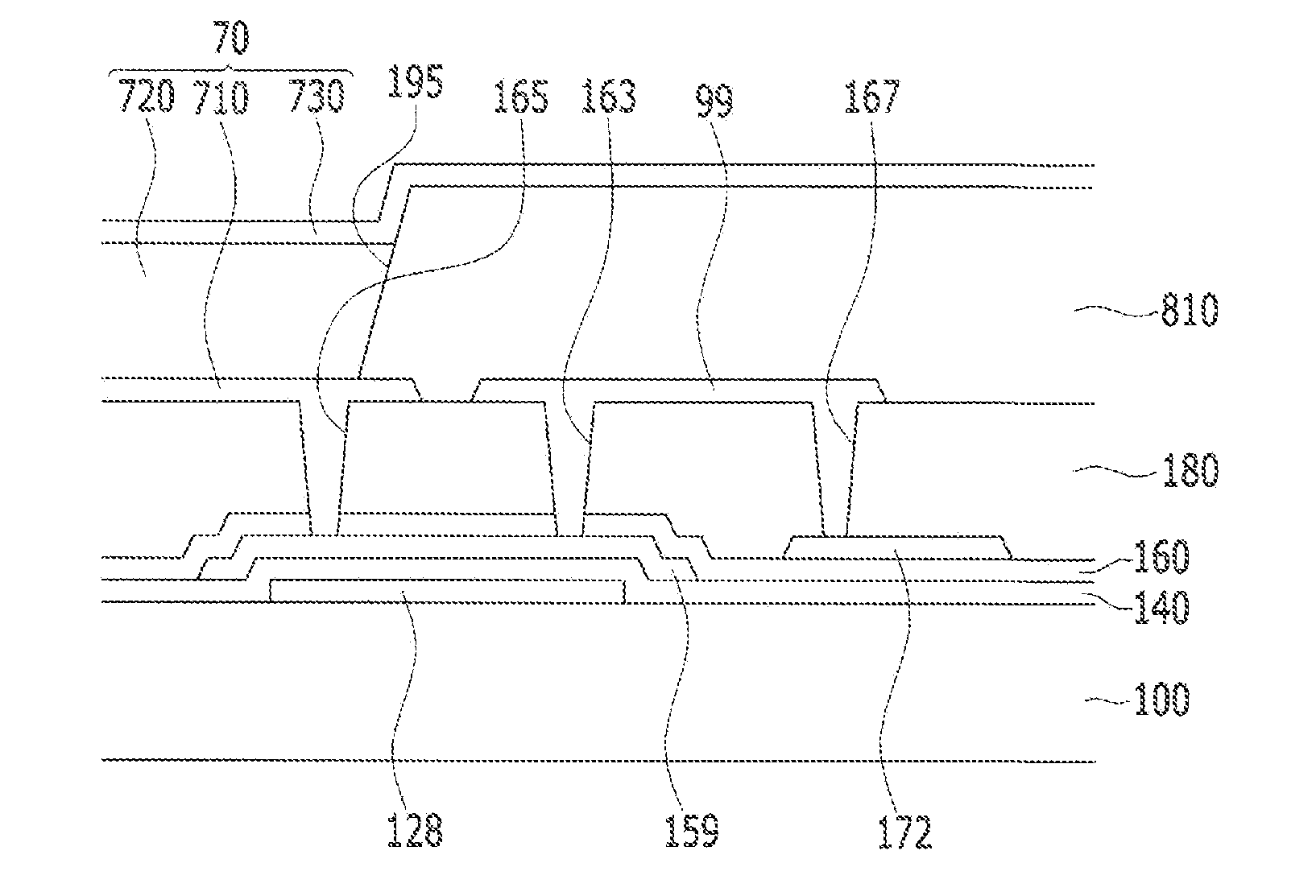

A thin film transistor substrate according to an exemplary embodiment includes: a substrate; a gate electrode disposed on the substrate; a gate insulating layer disposed on the gate electrode; an oxide semiconductor disposed on the gate insulating layer; a first interlayer insulating layer disposed on the oxide semiconductor; a data line disposed on the first interlayer insulating layer; a second interlayer insulating layer disposed on the data line; a source electrode disposed on the second interlayer insulating layer and connected with the oxide semiconductor and the data line through a first contact hole through the second interlayer insulating layer; and a drain electrode disposed on the second interlayer insulating layer and connected with the semiconductor through a second contact hole through the second interlayer insulating layer.

Owner:SAMSUNG DISPLAY CO LTD

Deep trench and fabricating method thereof, trench capacitor and fabricating method thereof

InactiveUS20080305604A1Increase capacitanceIncrease the areaSemiconductor/solid-state device manufacturingCapacitorsSiliconSubstrate surface

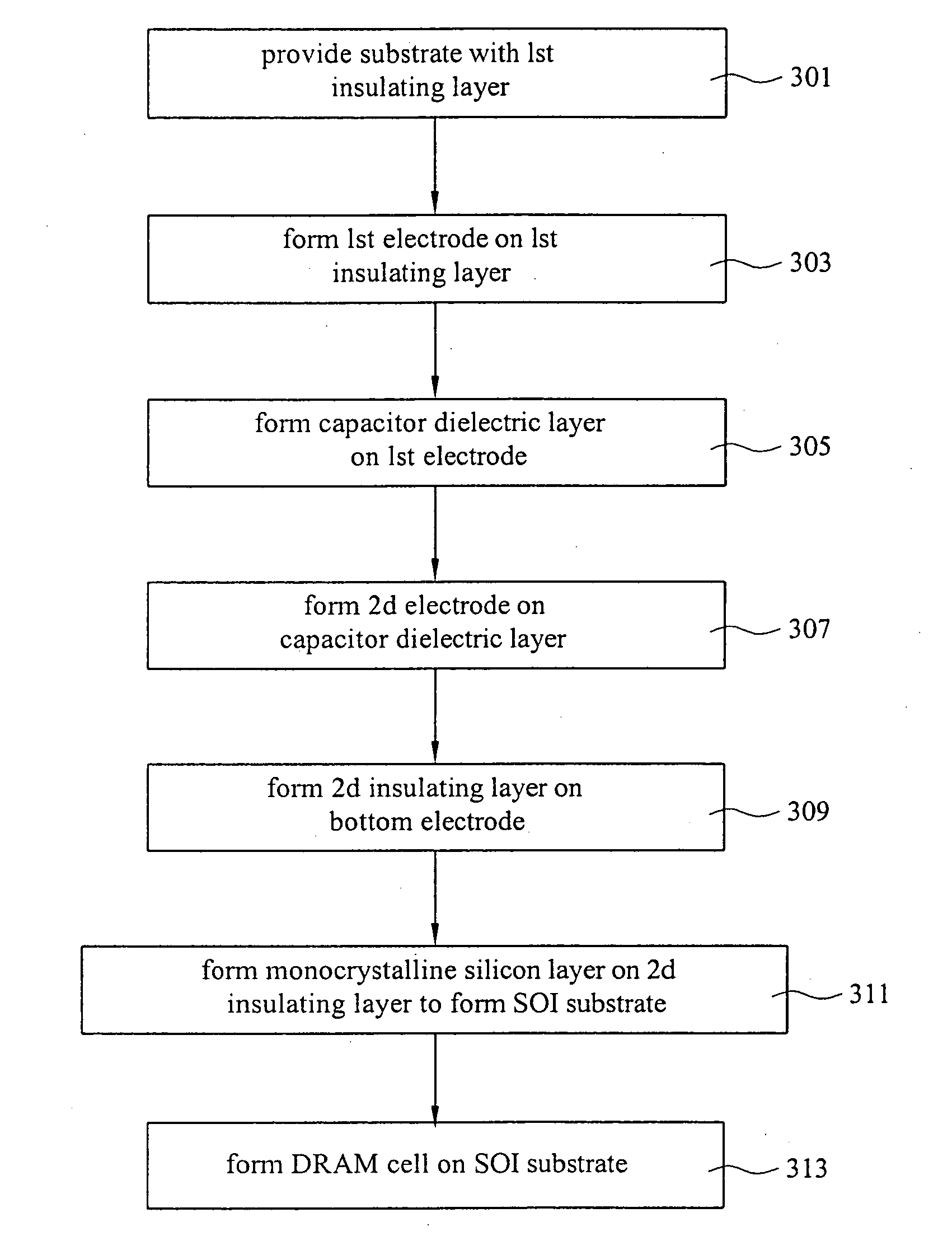

A method of fabricating a deep trench is provided, by which a trench is formed in the substrate initially. Then, a block layer is formed on the substrate surface of the upper portion of the trench. After that, a pad oxide layer is formed on the substrate surface of the lower portion of the trench. Next, a plurality of hemispherical silicon grains is formed on the substrate and exposes a portion of the pad oxide layer. Then, by using the hemispherical silicon grains as a mask, a portion of the pad oxide layer is removed so as to form a patterned pad oxide layer. Continually, the hemispherical silicon grains and the substrate exposed by the patterned pad oxide layer are removed. Finally, the patterned pad oxide layer is removed.

Owner:NAN YA TECH

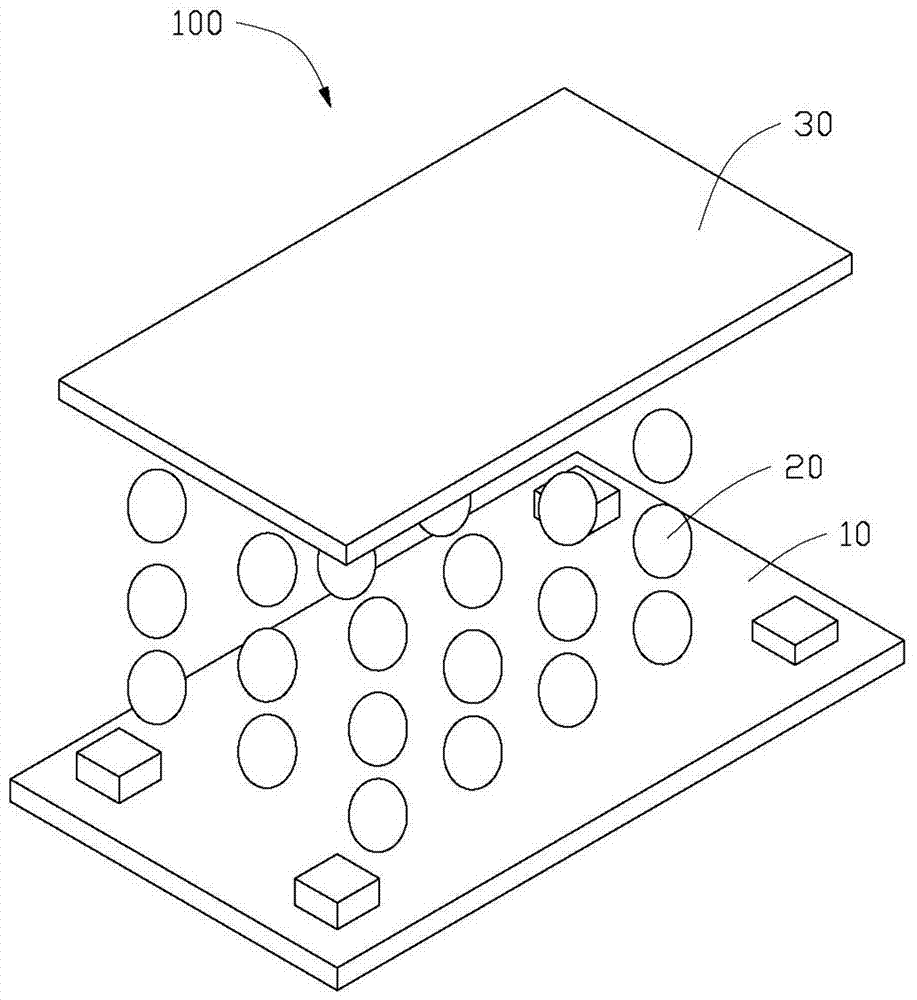

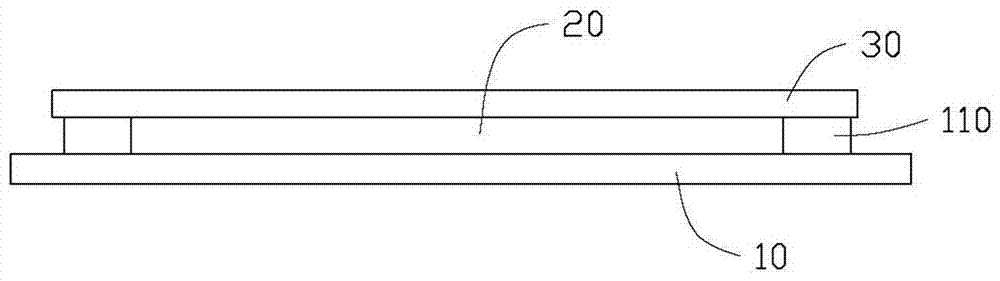

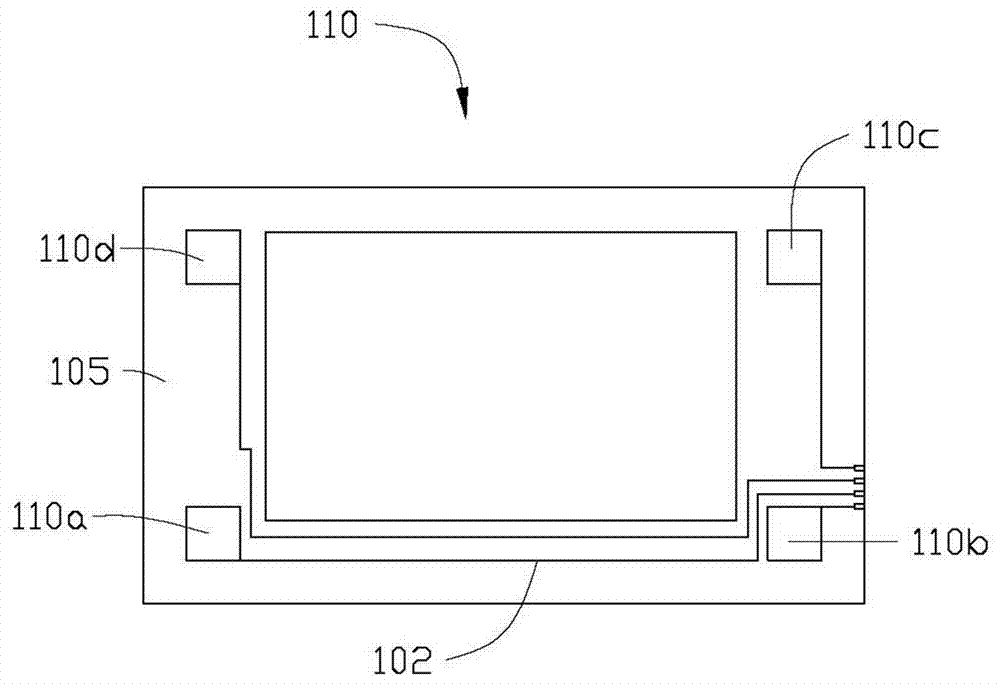

Pressure sensing module and touch display substrate

InactiveCN107340897AIncrease capacitor areaHigh sensitivityInput/output processes for data processingMicro structureBiochemical engineering

The invention relates to a pressure sensing module and a touch display substrate provided with the pressure sensing module. The pressure sensing module comprises a base, an elastic layer, a first electrode layer, a piezoelectric material layer and a second electrode layer, wherein the base, the elastic layer and the first electrode layer are sequentially arranged in a stacked mode; the elastic layer comprises multiple micro-structures which form a concavo-convex surface; the first electrode layer, the piezoelectric material layer and the second electrode layer cooperate to form a pressure sensing module body; and the pressure sensing module body is arranged on the elastic layer and used for sensing pressure exerted on the pressure sensing module.

Owner:HONG FU JIN PRECISION IND (SHENZHEN) CO LTD +1

Method for improving metal-insulator-metal capacitor reliability and process structure thereof

ActiveCN102683176AReduce electric field strengthImprove reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesMetal-insulator-metalCapacitance

The invention discloses a method for improving metal-insulator-metal (MIM) capacitor reliability. The method comprises the following steps of sequentially depositing a first metal dielectric layer, a metal layer, a corrosion stopping layer and a second metal dielectric layer on a substrate; forming a first through hole and a second through hole in the second metal dielectric layer and covering a bottom anti-reflex layer on the surface of the second metal dielectric layer; manufacturing a multilayer groove on the second through hole and forming a laminated groove with gradually-increased bottom width; manufacturing the bottom portion of the multilayer groove into a first chamfer, enabling the first through hole to be contacted with the second metal dielectric layer, and manufacturing a connection position between the top end and the multilayer groove into a second chamfer; and etching the first through hole and the second through hole to the surface of the first metal dielectric layer and sequentially forming a top electrode, an insulating film and a bottom electrode on the surface of the second metal dielectric layer from top to bottom. The invention further discloses a process structure of the method for improving the metal-insulator-metal MIM capacitor reliability. The method and the process structure can improve reliability of MIM capacitor devices.

Owner:SHANGHAI HUALI MICROELECTRONICS CORP

Semiconductor device producing method and semiconductor device

InactiveUS6881643B2High bulk densityThe implementation process is simpleTransistorSolid-state devicesCapacitorSemiconductor

In a semiconductor device producing method, a plug is formed within a contact hole formed in a barrier film and an interlayer insulating film on a semiconductor substrate. Then, an insulation film is formed on the plug and barrier film, and a hole is made in the insulation film such that an upper surface of the plug is exposed. A first conductive film is formed on the insulation film so as to fill the hole, and then etched by a CMP method to form a lower electrode within the hole. The insulation film is removed and the lower electrode is left in a protuberant manner. A dielectric film made of a ferroelectric or high-dielectric-constant substance and a second conductive film are sequentially formed over the lower electrode and the barrier film, and then patterned simultaneously to thereby form a capacitor dielectric film and an upper electrode.

Owner:SHARP KK

Method for manufacturing deep channel capacitor and etching deep channel opening

ActiveCN101000894AIncrease capacitor areaSimple processSemiconductor/solid-state device manufacturingCapacitanceNitride

The invention relates to a substrate, which contains an oxide silicon layer, a first nitride silicon layer, a shallow channel isolate, and the second nitride silicon layer. It forms a designed multicrystalline layer on the second nitride silicon layer, and etches the designed multicrystalline layer to form the deep ditch shedding, and then it removes the multicrystalline layer and simultaneously etches the substrate to deepen the deep channel shedding by etching method and to fill a capacitor structure into the deep channel.

Owner:UNITED MICROELECTRONICS CORP

Thin film transistor array panel and organic light emitting diode display including the same

ActiveUS9391212B2Increase the aperture ratioSmall sizeTransistorSolid-state devicesDisplay deviceLight-emitting diode

A thin film transistor substrate according to an exemplary embodiment includes: a substrate; a gate electrode disposed on the substrate; a gate insulating layer disposed on the gate electrode; an oxide semiconductor disposed on the gate insulating layer; a first interlayer insulating layer disposed on the oxide semiconductor; a data line disposed on the first interlayer insulating layer; a second interlayer insulating layer disposed on the data line; a source electrode disposed on the second interlayer insulating layer and connected with the oxide semiconductor and the data line through a first contact hole through the second interlayer insulating layer; and a drain electrode disposed on the second interlayer insulating layer and connected with the semiconductor through a second contact hole through the second interlayer insulating layer.

Owner:SAMSUNG DISPLAY CO LTD

Structure of capacitor set

ActiveUS20100140741A1Increase production capacityReduce Capacitance VariationSemiconductor/solid-state device detailsSolid-state devicesEngineeringCapacitor

A structure of a capacitor set is described, including at least two capacitors that are disposed at the same position on a substrate and include a first capacitor and a second capacitor. The first capacitor includes multiple first capacitor units electrically connected with each other in parallel. The second capacitor includes multiple second capacitor units electrically connected with each other in parallel. The first and the second capacitor units are arranged spatially intermixing with each other to form an array.

Owner:MARLIN SEMICON LTD

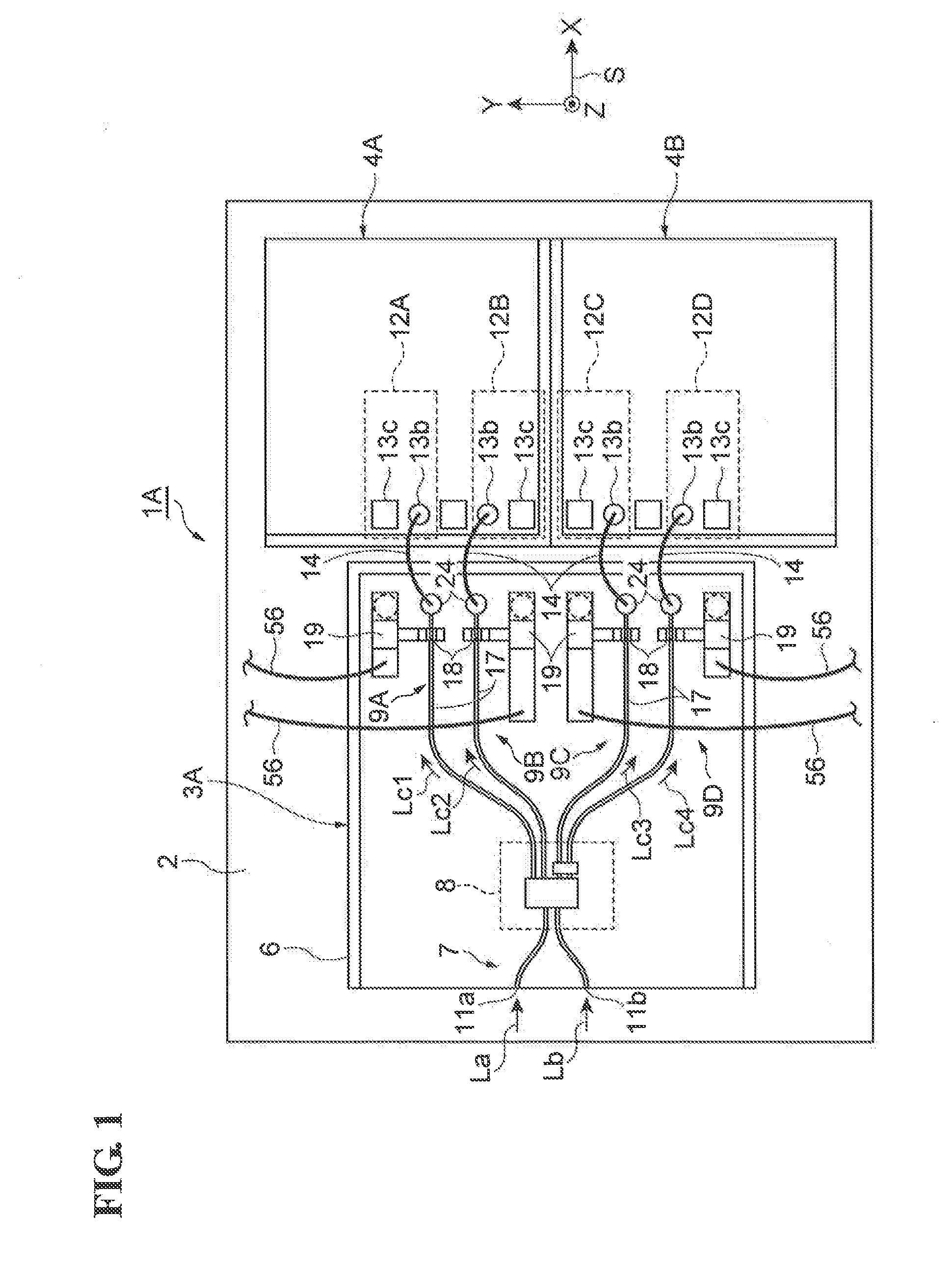

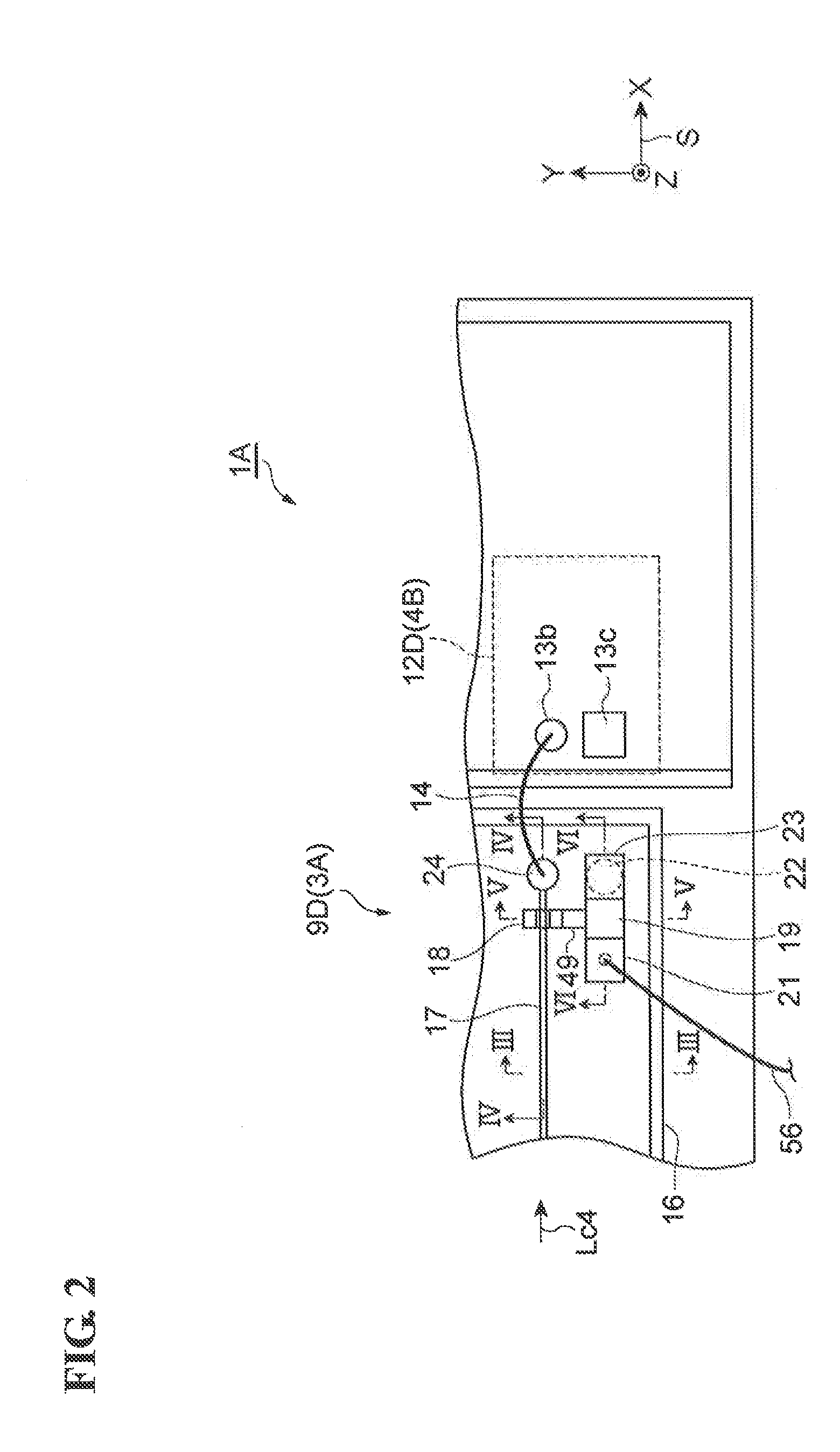

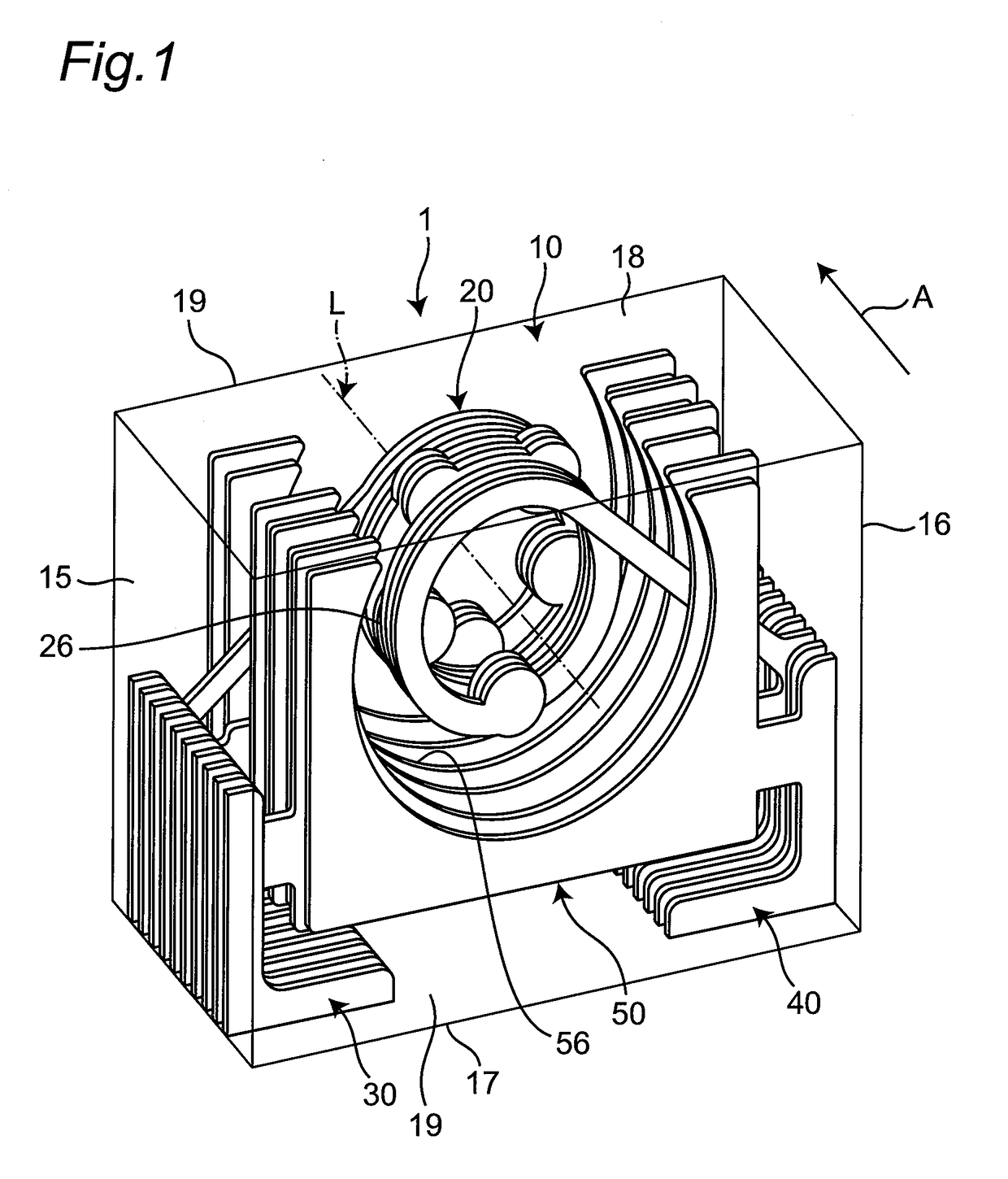

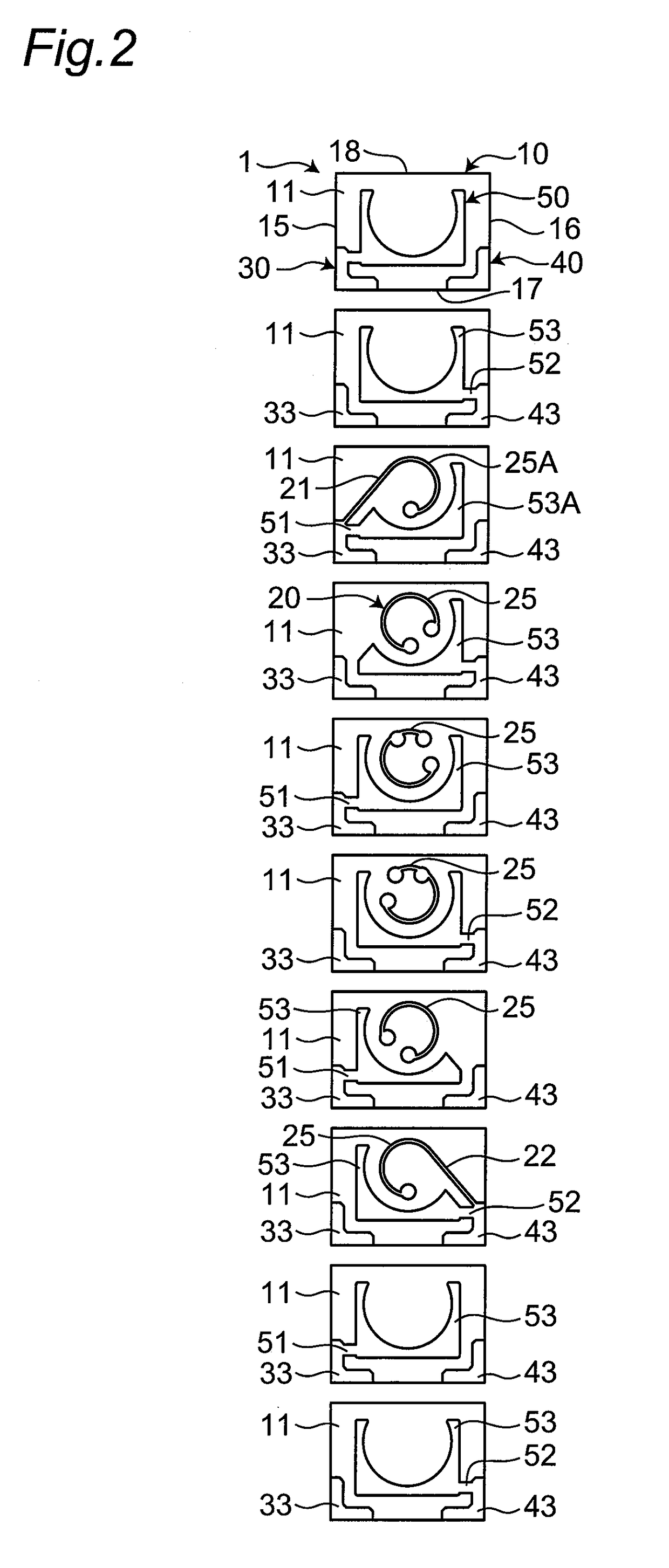

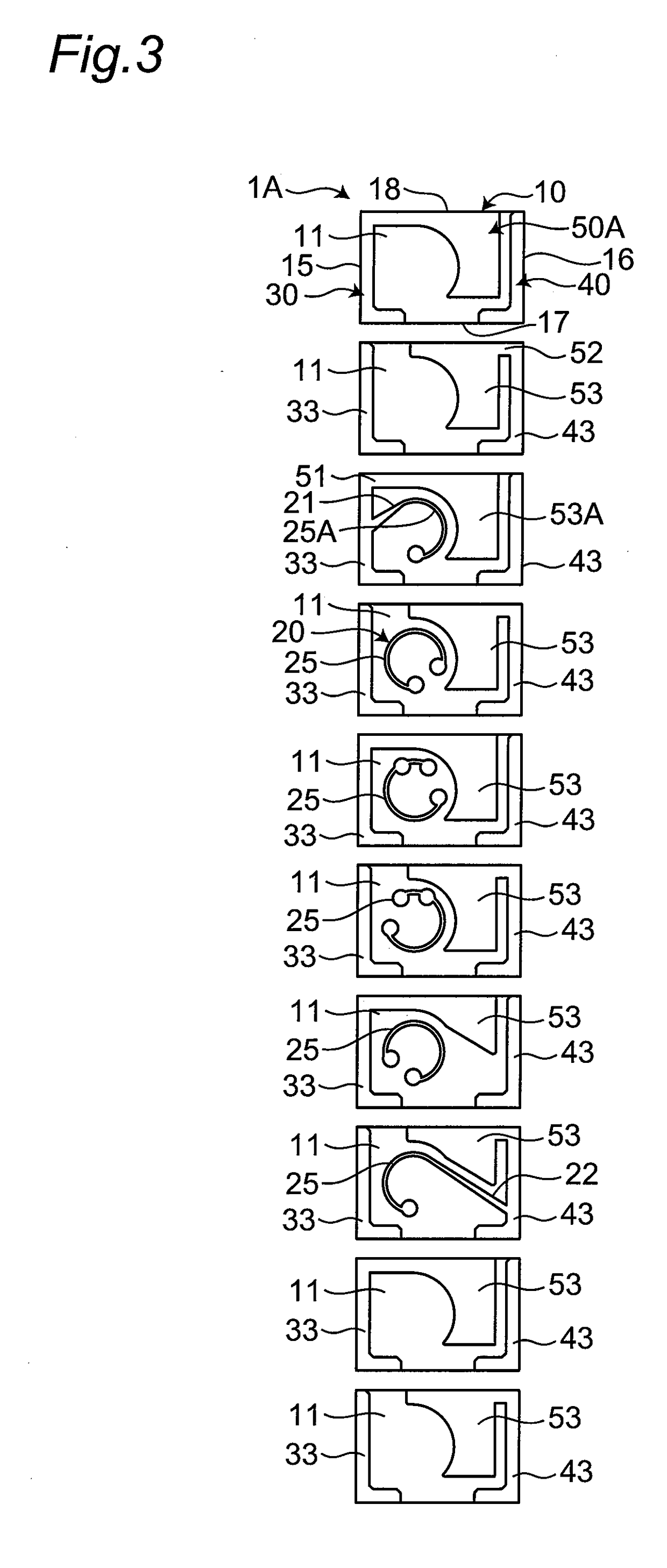

Lc composite component

ActiveUS20180351526A1Increase capacitor areaDecreasing acquisitionTransformers/reacts mounting/support/suspensionMultiple-port networksEngineeringCapacitor

An LC composite component comprising an element body, a helically wound coil disposed in the element body, and a capacitor disposed on an outer circumferential side of the coil in the element body. When viewed in an axial direction of the coil, the element body is rectangular, and the capacitor is disposed between at least two sides of the element body and the coil.

Owner:MURATA MFG CO LTD

Capacitor structure and method of manufacturing the same

ActiveUS20180358428A1High mechanical strengthIncrease capacitance valueSolid-state devicesCapacitorsEngineeringDielectric layer

Provided is a capacitor structure including a substrate, a cup-shaped lower electrode, a top supporting layer, a capacitor dielectric layer, and an upper electrode. The cup-shaped lower electrode is located on the substrate. The top supporting layer surrounds the upper portion of the cup-shaped lower electrode. The top supporting layer includes a high-k material. Surfaces of the cup-shaped lower electrode and the top supporting layer are covered by the capacitor dielectric layer. A surface of the capacitor dielectric layer is covered by the upper electrode.

Owner:WINBOND ELECTRONICS CORP

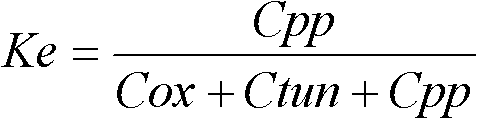

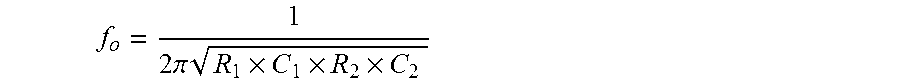

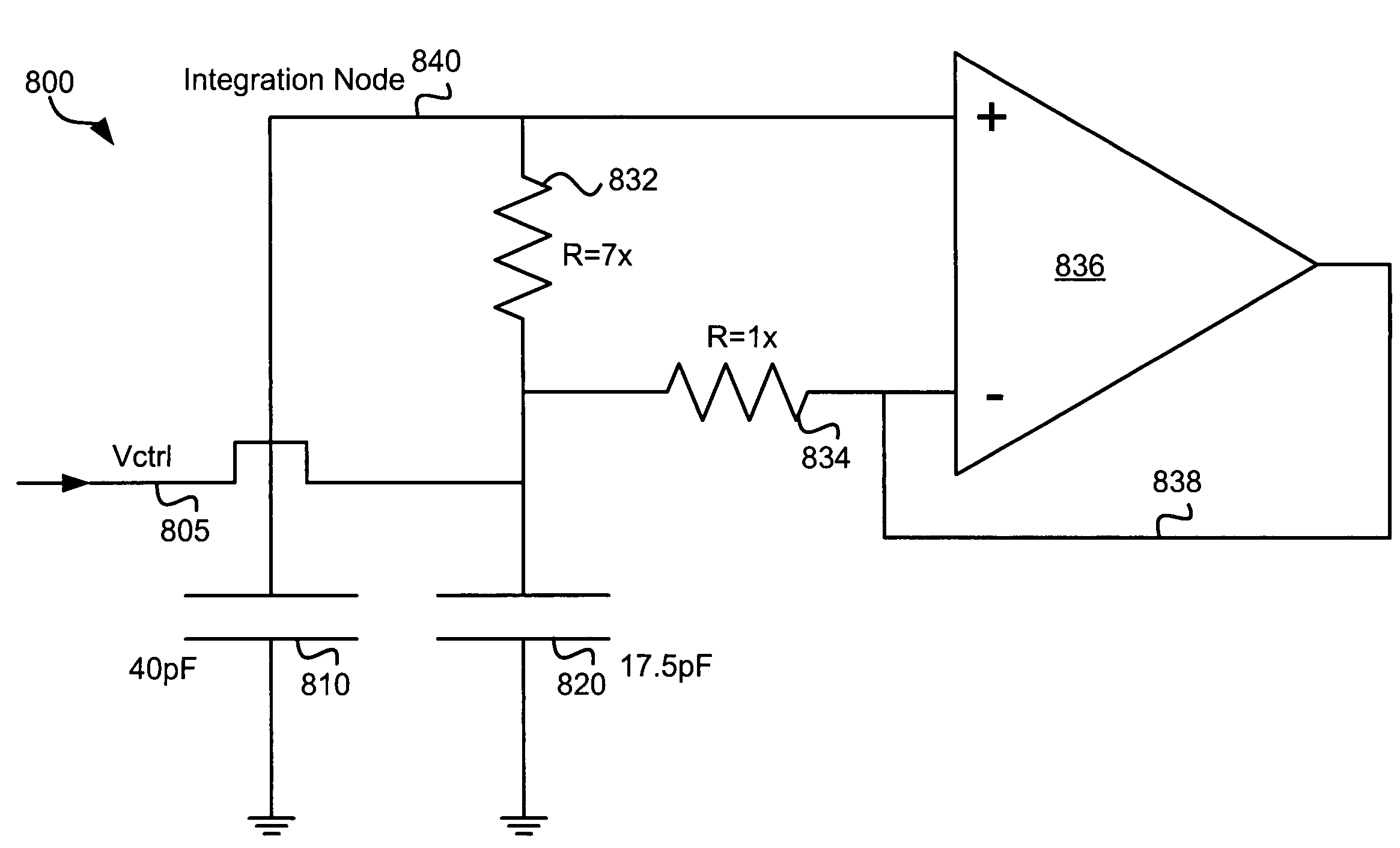

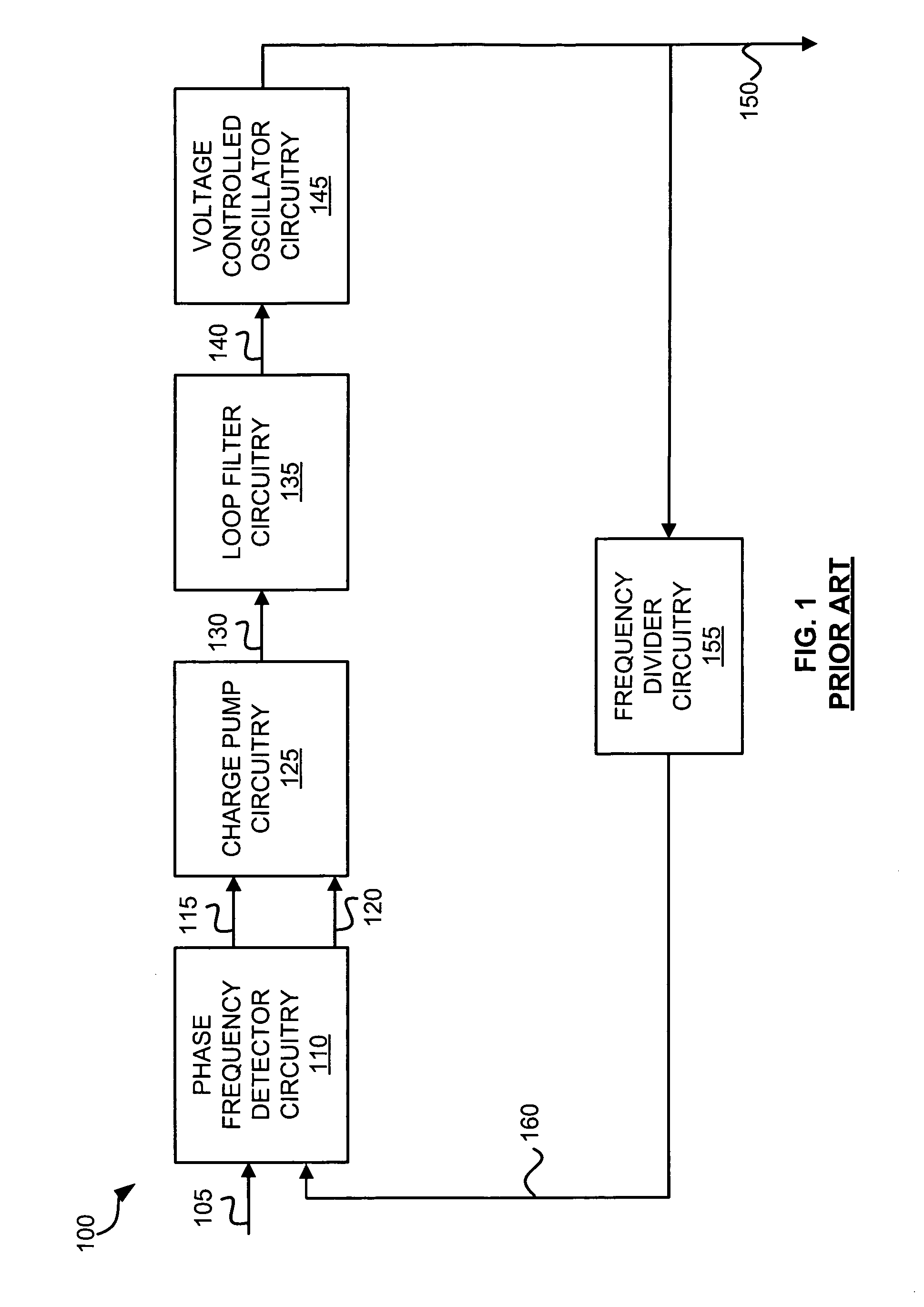

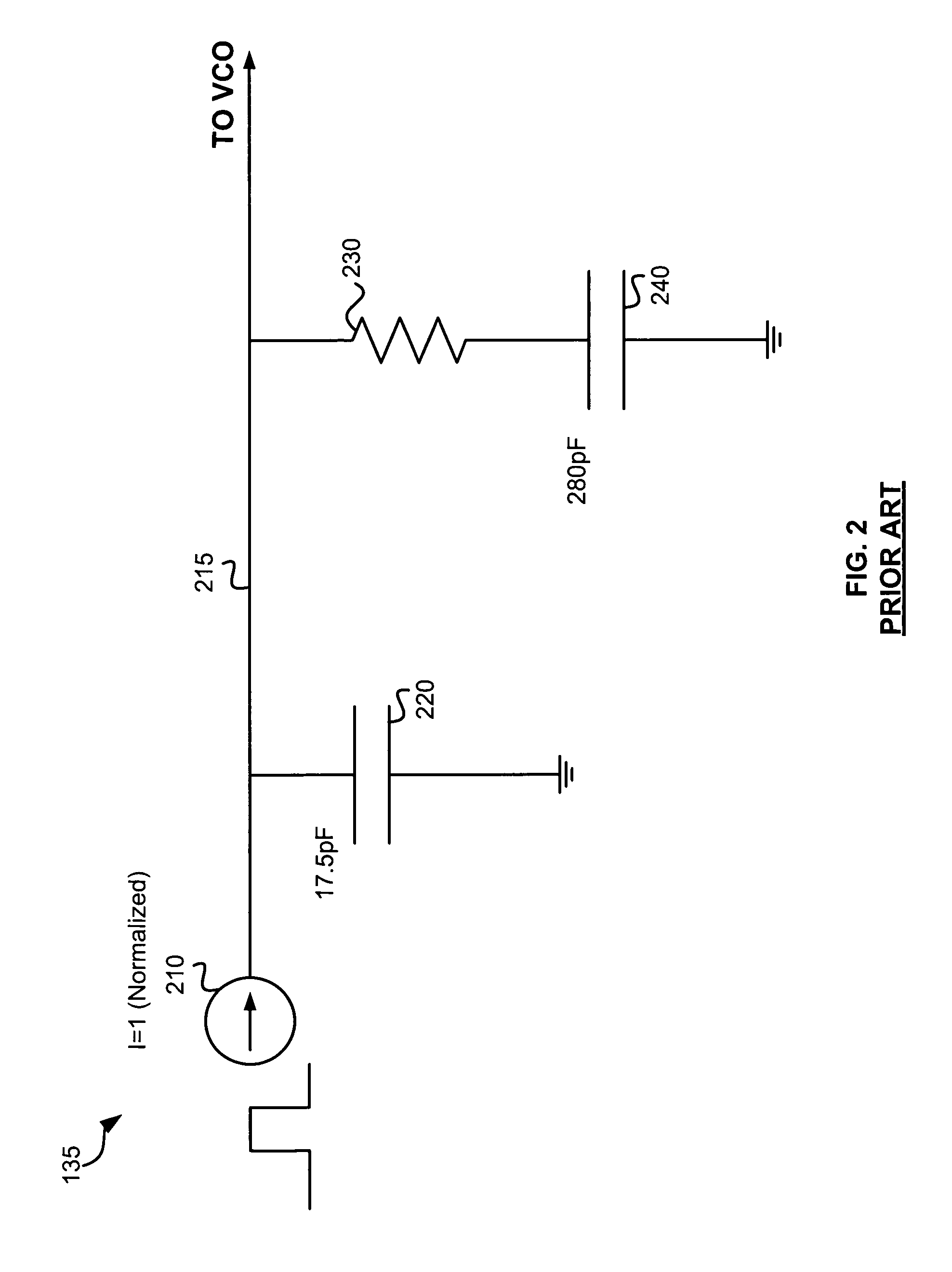

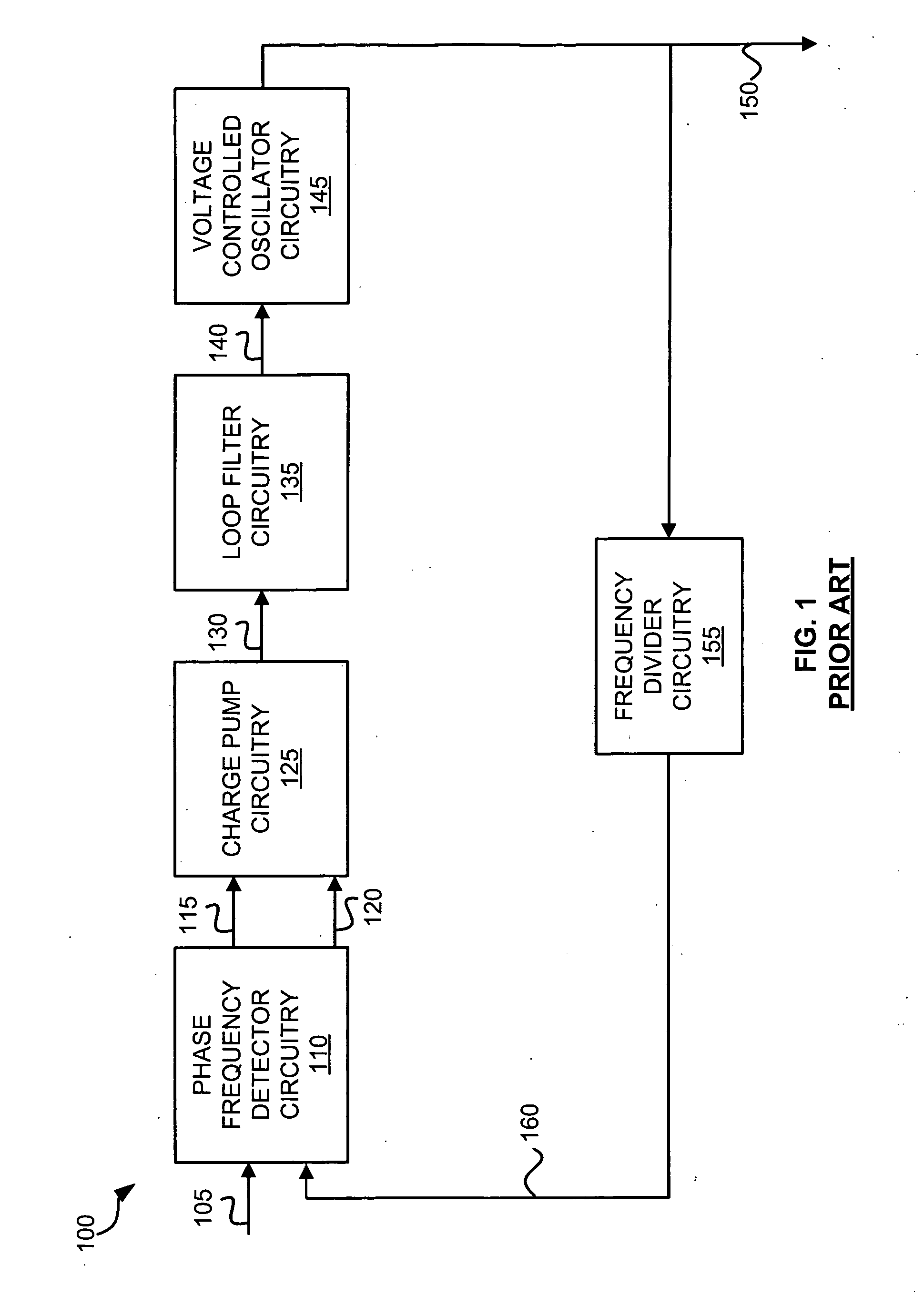

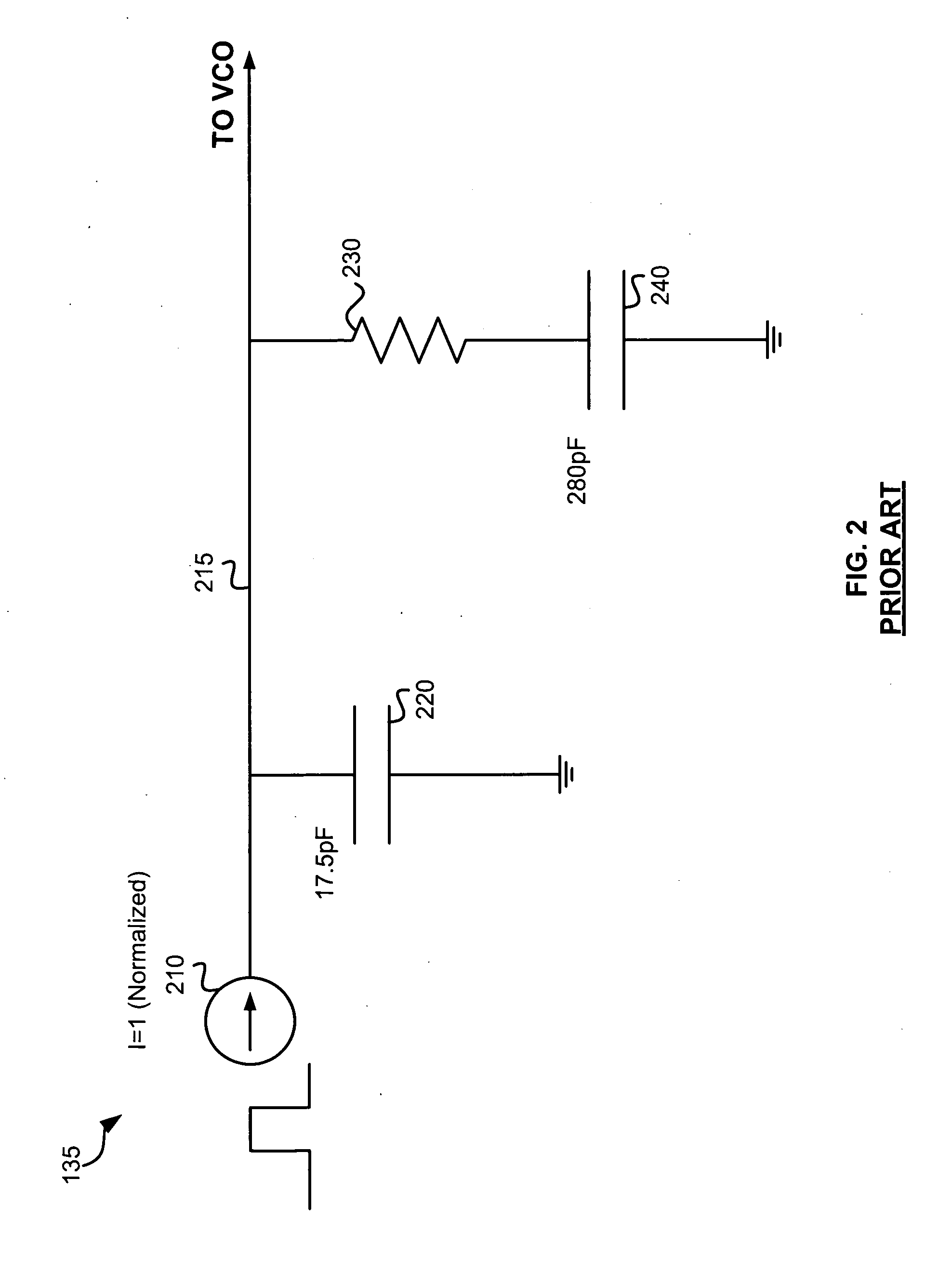

Phase-locked loop filter capacitance with a drag current

Phase-locked loop circuitry includes charge pump circuitry, loop filter circuitry, and drag current circuitry. The charge pump circuitry generates a charge pump current based on a phase of an input signal. The loop filter circuitry receives the charge pump current. The drag current circuitry generates a drag current to draw charge in the opposite direction from the charging current from a loop filter integration capacitor in the loop filter circuitry that does not include voltage sensing circuitry.

Owner:CONVERSANT INTPROP MANAGEMENT INC

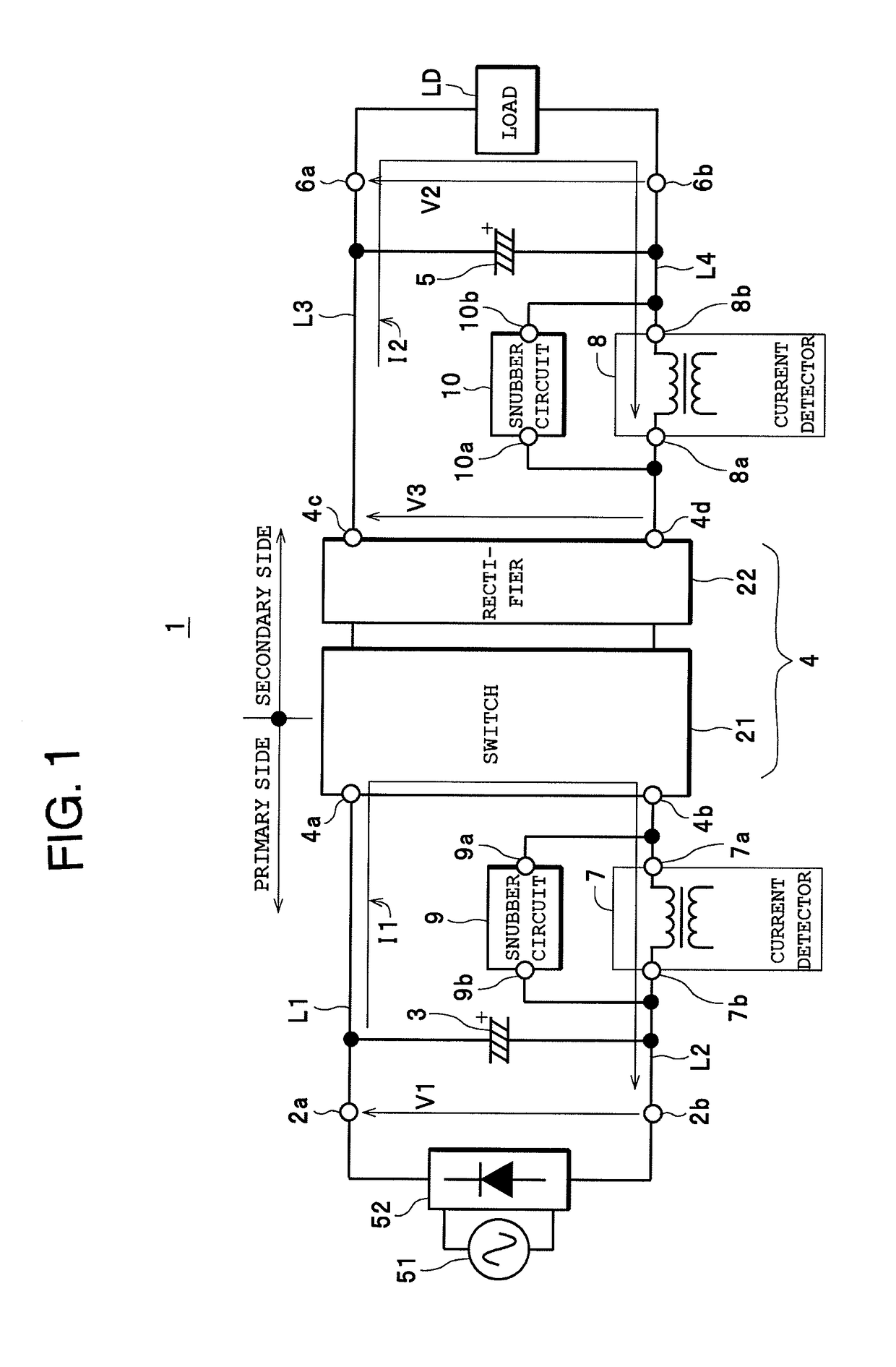

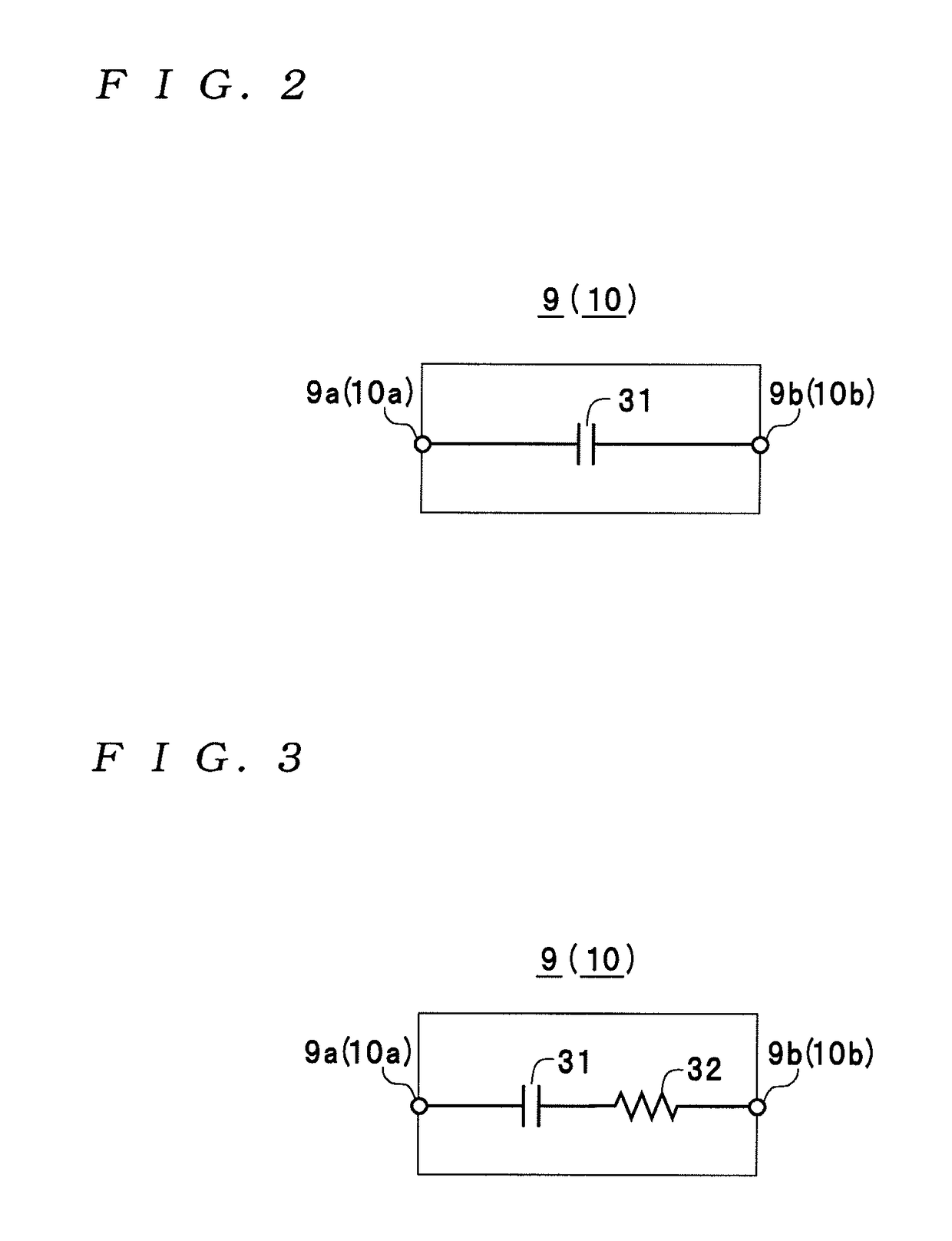

Electronic device

ActiveUS20190020265A1Increase capacitanceIncrease capacitor areaEfficient power electronics conversionApparatus with intermediate ac conversionSnubberEngineering

An electronic device includes a power converter and a current detector that is disposed at at least one position out of a primary-side position and a secondary-side position for the power converter and detects a current flowing at the at least one position. A snubber circuit including a capacitor is directly connected in parallel to both ends of the current detector.

Owner:TDK CORPARATION

Back capacitor structure and manufacturing method

ActiveCN110752207AImprove area utilizationSmall sizeSemiconductor/solid-state device detailsSolid-state devicesCapacitanceHigh capacitance

The invention discloses a back capacitor structure and a manufacturing method. The method comprises the following steps of arranging a nitride layer on the front of a semiconductor substrate and arranging a hole, directly facing the nitride layer, in the back of the semiconductor substrate, wherein the nitride layer is arranged at the bottom of the hole; arranging first metal layers on the inner wall of the hole and the back of the semiconductor substrate; arranging dielectric layers on the inner wall of the hole and the back of the semiconductor substrate, wherein the dielectric layers coverthe first metal layers; arranging through holes in the dielectric layer above the first metal layers of the semiconductor substrate; and manufacturing a hole in the back of the semiconductor substrate. The capacitor structure in the manufactured hole is capable of greatly improving the capacity area, thereby improving the area utilization rate of an epitaxy structure; the occupied planar space issmaller, so that benefit is provided to reduce the device size; and the back capacitor is manufactured without changing the original manufacturing process, so that the process cost is saved.

Owner:福建省福联集成电路有限公司

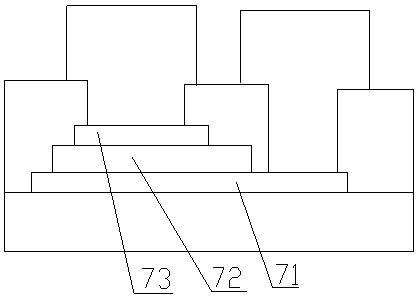

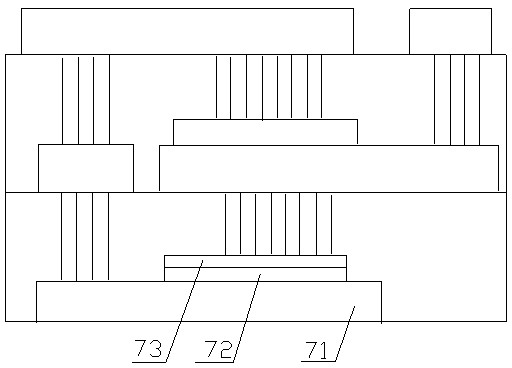

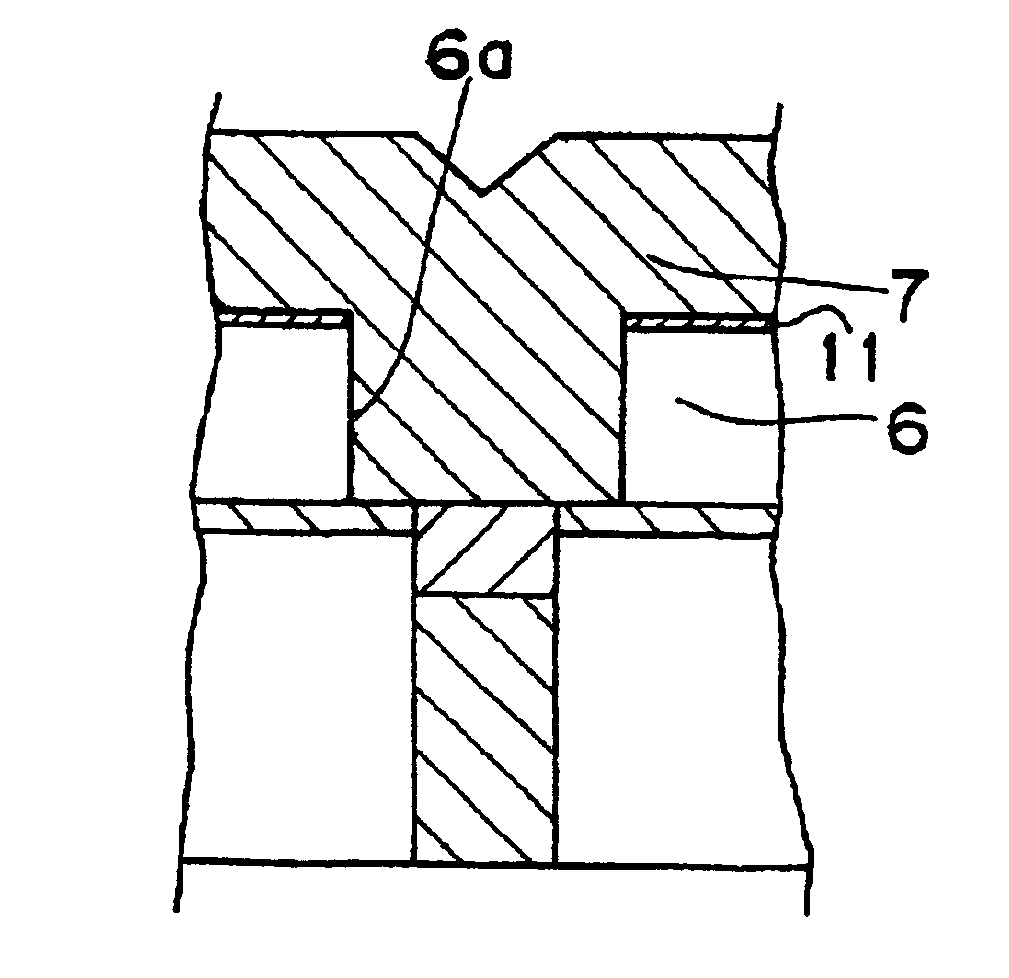

Preparation method of three-dimensional ferroelectric random access memory and three-dimensional ferroelectric random access memory

PendingCN111524892AImprove integration densityReduce manufacturing costSolid-state devicesSemiconductor devicesCapacitanceRandom access memory

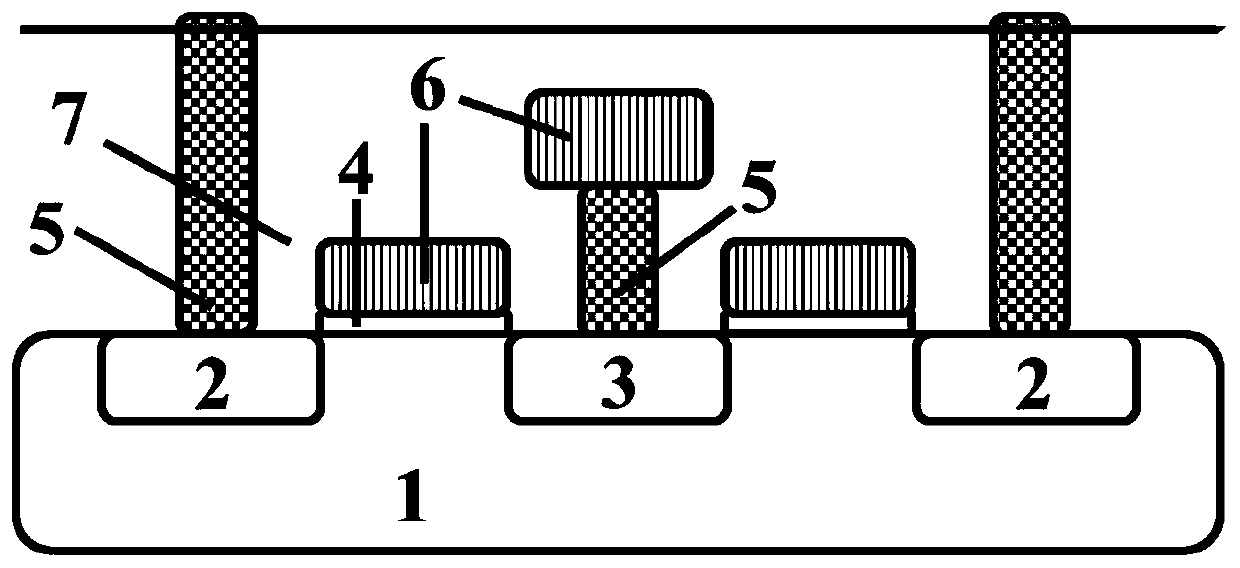

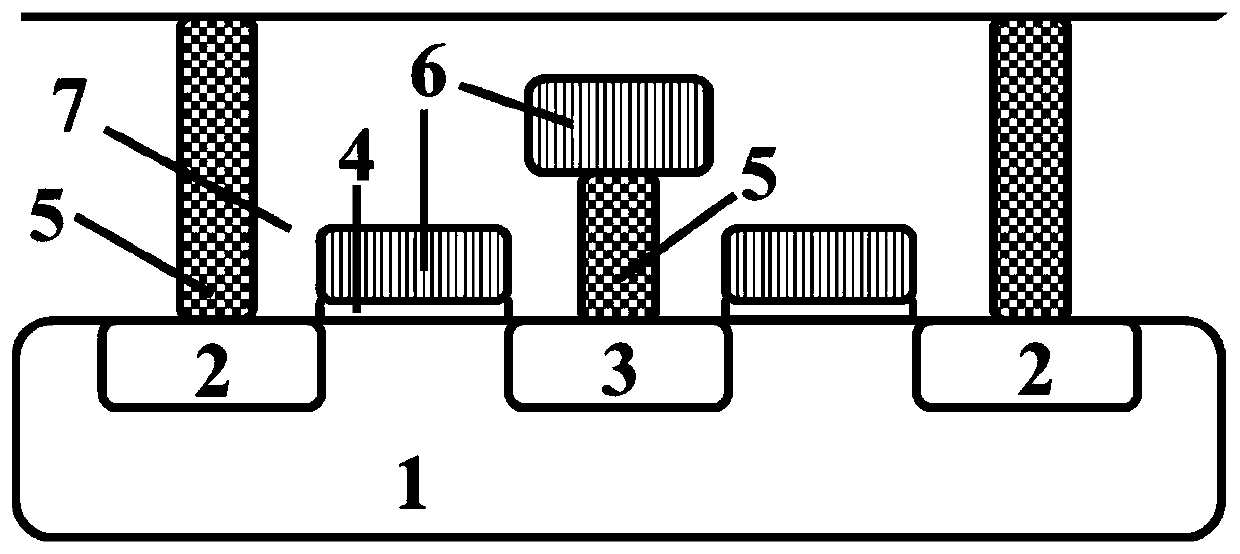

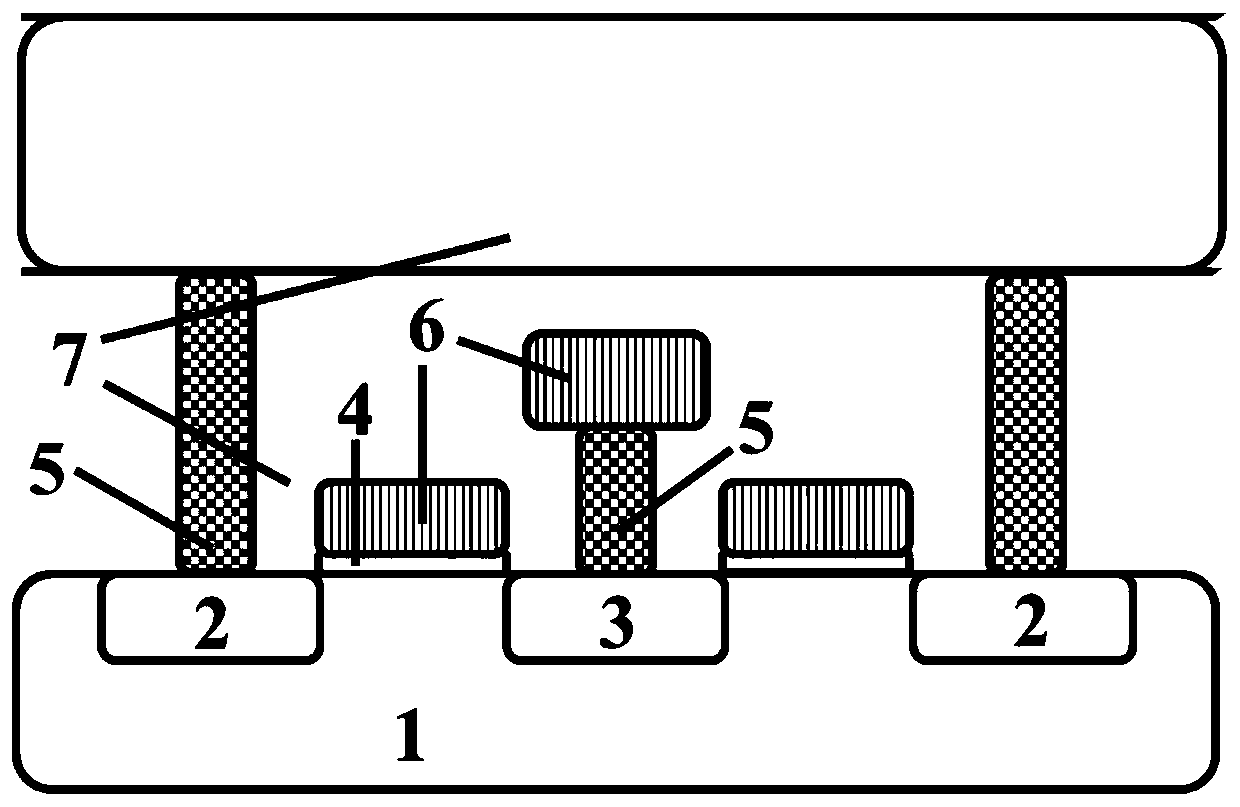

The invention provides a preparation method of a three-dimensional ferroelectric random access memory and the three-dimensional ferroelectric random access memory. The preparation method comprises thefollowing steps: while preparing a transistor based on a CMOS process, vertically integrating each ferroelectric storage unit of a three-dimensional ferroelectric capacitor on the transistor in sequence to obtain the three-dimensional ferroelectric random access memory. The ferroelectric storage unit of the three-dimensional ferroelectric capacitor sequentially comprises an interlayer medium (7),a capacitor bottom electrode (9), a ferroelectric film (10) and a capacitor top electrode (11) which are vertically deposited. A ferroelectric capacitor is integrated into a complementary metal oxidesemiconductor (CMOS), and a capacitor structure is converted from a plane to a three-dimensional structure to increase a capacitor area, so that higher storage density is realized, and the size of astorage unit is further reduced on the premise of not reducing storage charges.

Owner:XIANGTAN UNIV

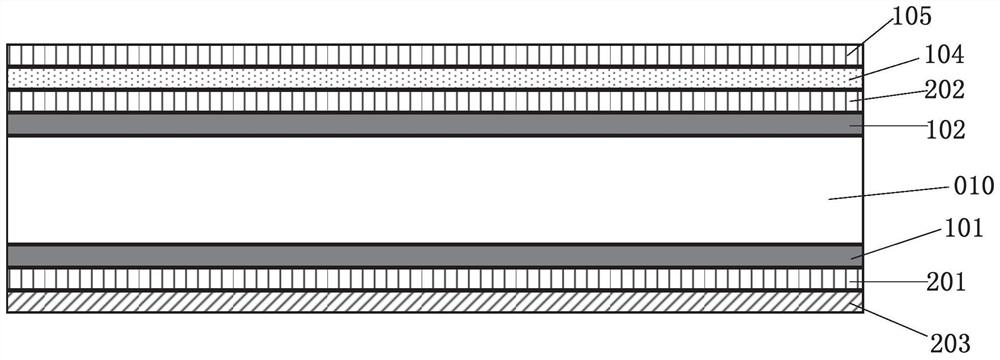

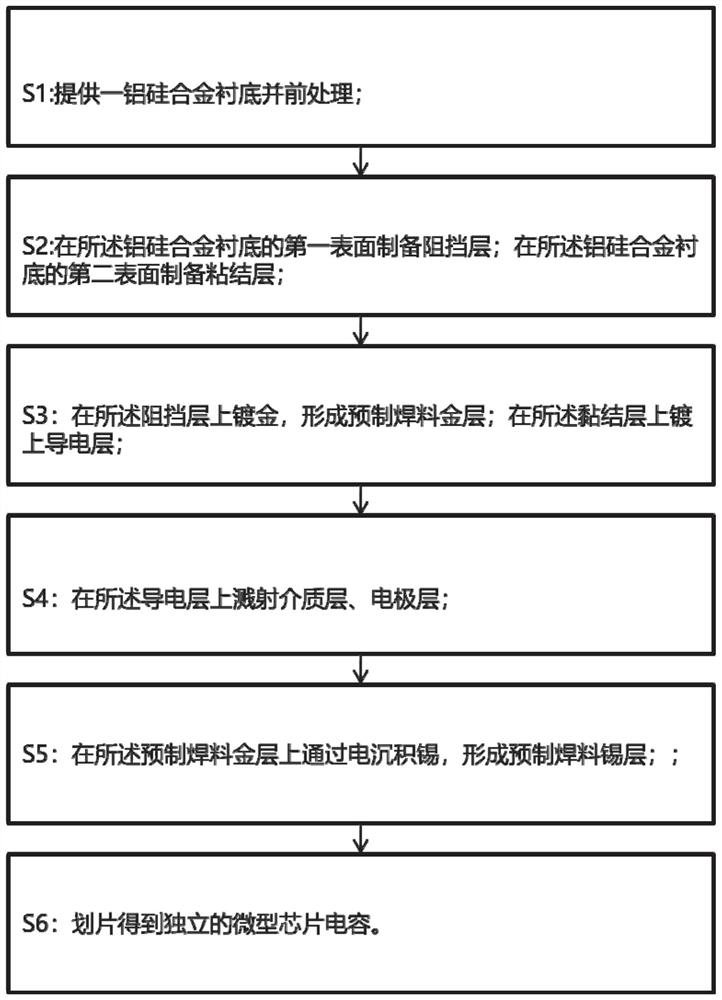

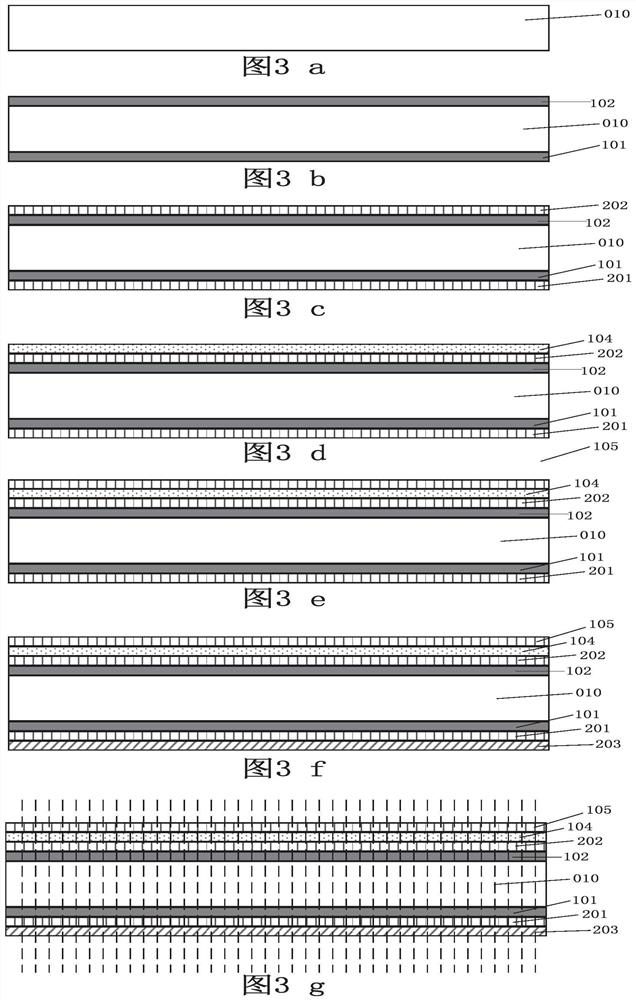

Microchip capacitor and manufacturing method thereof

PendingCN112151512AIncrease capacitor areaShort production cycleSemiconductor/solid-state device detailsSolid-state devicesElectrically conductiveCapacitance

The invention discloses a microchip capacitor and a manufacturing method thereof. The chip capacitor comprises a prefabricated solder tin layer, a prefabricated solder gold layer, a barrier layer, analuminum-silicon alloy substrate, a bonding layer, a conductive layer, a dielectric layer and an electrode layer which are stacked in sequence. The manufacturing method comprises the following steps:S1, providing an aluminum-silicon alloy substrate and carrying out pretreatment; S2, preparing a barrier layer on the first surface of the aluminum-silicon alloy substrate, and preparing a bonding layer on the second surface of the aluminum-silicon alloy substrate; S3, plating gold on the barrier layer to form a prefabricated solder gold layer, and plating a conductive layer on the bonding layer;S4, sputtering a dielectric layer and an electrode layer on the conductive layer; S5, forming a prefabricated solder tin layer on the prefabricated solder gold layer through tin electro-deposition; and S6, scribing to obtain the independent microchip capacitor. According to the invention, the aluminum-silicon alloy is used as the substrate, the substrate does not need to be polished or sputtered with a priming coat, the capacitor area is large, the manufacturing period is short, and the assembling difficulty of the microchip capacitor is reduced.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

Phase-locked loop filter capacitance with a drag current

InactiveUS20070247236A1Easy to manageReduce loop bandwidthPulse automatic controlLoop filterCapacitance

Phase-locked loop circuitry includes charge pump circuitry, loop filter circuitry, and drag current circuitry. The charge pump circuitry generates a charge pump current based on a phase of an input signal. The loop filter circuitry receives the charge pump current. The drag current circuitry generates a drag current to draw charge in the opposite direction from the charging current from a loop filter integration capacitor in the loop filter circuitry that does not include voltage sensing circuitry.

Owner:CONVERSANT INTPROP MANAGEMENT INC

Optical semiconductor device and method of producing the same

ActiveUS9563100B2Reduce areaReduce capacitanceOptical light guidesNon-linear opticsWaveguideSemiconductor

Owner:SUMITOMO ELECTRIC IND LTD

Optical-to-electrical converter unit and semiconductor light-receiving device

ActiveUS8969989B2Increase capacitor areaIncrease the areaOptical light guidesSemiconductor devicesCapacitancePhotoelectric conversion

An optical-to-electrical converter unit includes a substrate having front and back surfaces; an original waveguide unit; and an optical-to-electrical converter. The optical-to-electrical converter includes a light-receiving element optically coupled to the optical waveguide unit; a capacitance element including first and second conductive layers and an insulating layer disposed between the first and second conductive layers; an electrode pad electrically connected to the light-receiving element; a back electrode formed on the back surface of the substrate; and a via electrode extending from the front surface to the back surface of the substrate. The optical waveguide unit, the light-receiving element, the capacitance element, and the electrode pad are formed on the front surface. The first conductive layer of the capacitance element is electrically connected to the light-receiving element and the electrode pad. The second conductive layer of the capacitance element is electrically connected to the back electrode through the via electrode.

Owner:SUMITOMO ELECTRIC IND LTD