Floating gate type EEPROM (Electrically Erasable Programmable Read Only Memory) device and manufacturing method thereof

A manufacturing method and floating gate technology, which is applied in semiconductor/solid-state device manufacturing, electric solid-state devices, semiconductor devices, etc., can solve the problems of reducing size and performance, increase voltage coupling efficiency, maintain device area, and reduce device area Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

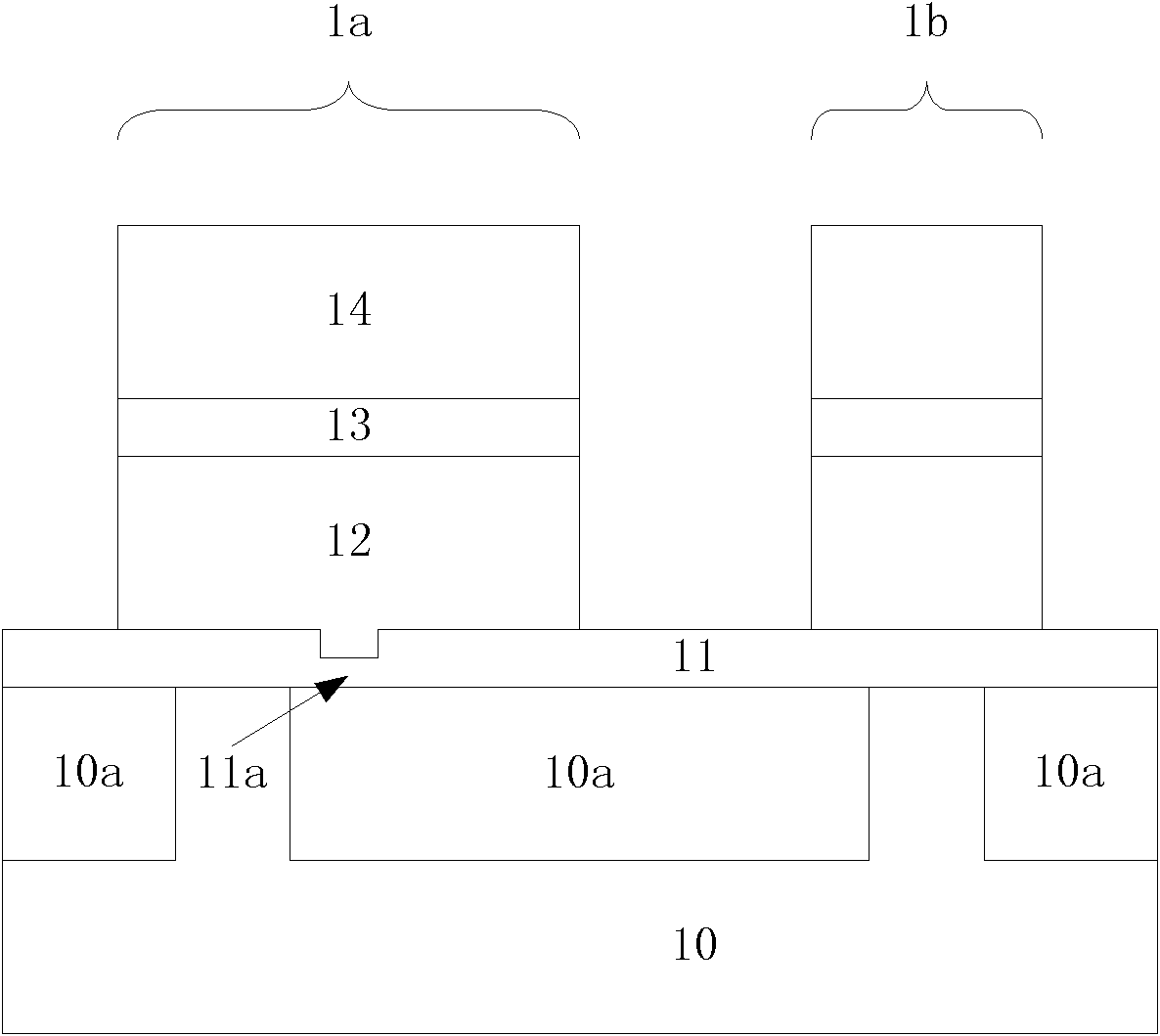

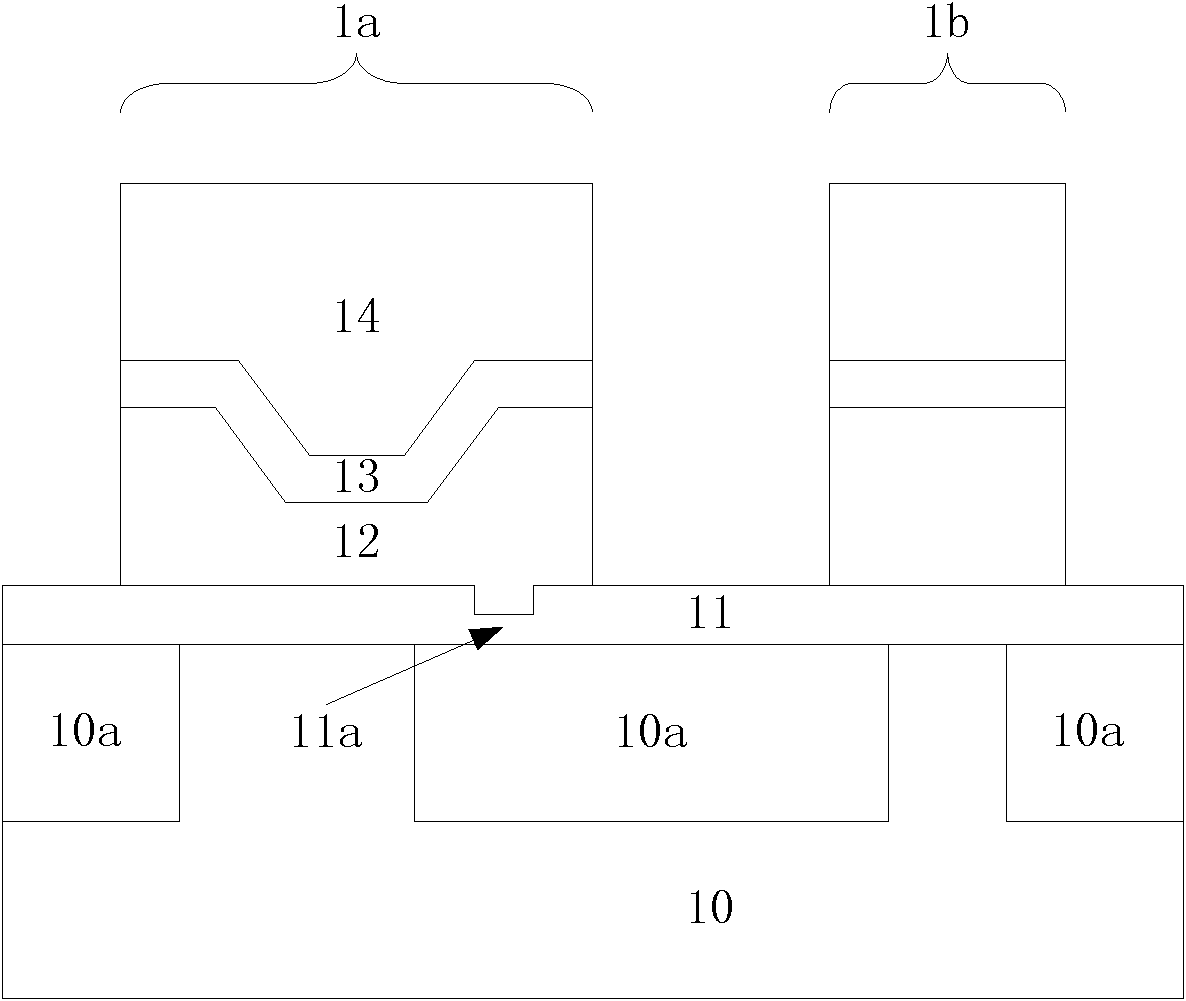

[0025] see figure 2 , which is a specific embodiment of the floating gate EEPROM device of the present invention. Wherein, each memory cell includes a storage transistor 1a and a selection transistor 1b, both transistors are fabricated on the substrate 10 and the gate oxide layer 11, and share a heavily doped source and drain region 10a. The storage transistor 1a is a floating gate transistor, including two gates, a polysilicon floating gate 12 located below and a polysilicon control gate 14 located above, and a dielectric layer 13 separates the two gates 12 and 14 . A small portion of the gate oxide layer 11 is thinner in the area of the storage transistor 1a, which is called the tunnel oxide layer 11a.

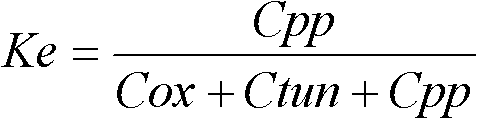

[0026] Such as figure 1 As shown, in the existing floating gate type EEPROM device, the upper and lower surfaces of the dielectric layer 13 are flat planar shapes. The floating gate 12 is in contact with the lower surface of the dielectric layer 13, and the contact sur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More