Method to reduce a capacitor depletion phenomena

a capacitor and depletion phenomenon technology, applied in the field of semiconductor devices, can solve the problems of deleterious depletion phenomena affecting the performance of capacitor cells, and achieve the effect of less risk of capacitor depletion phenomena

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

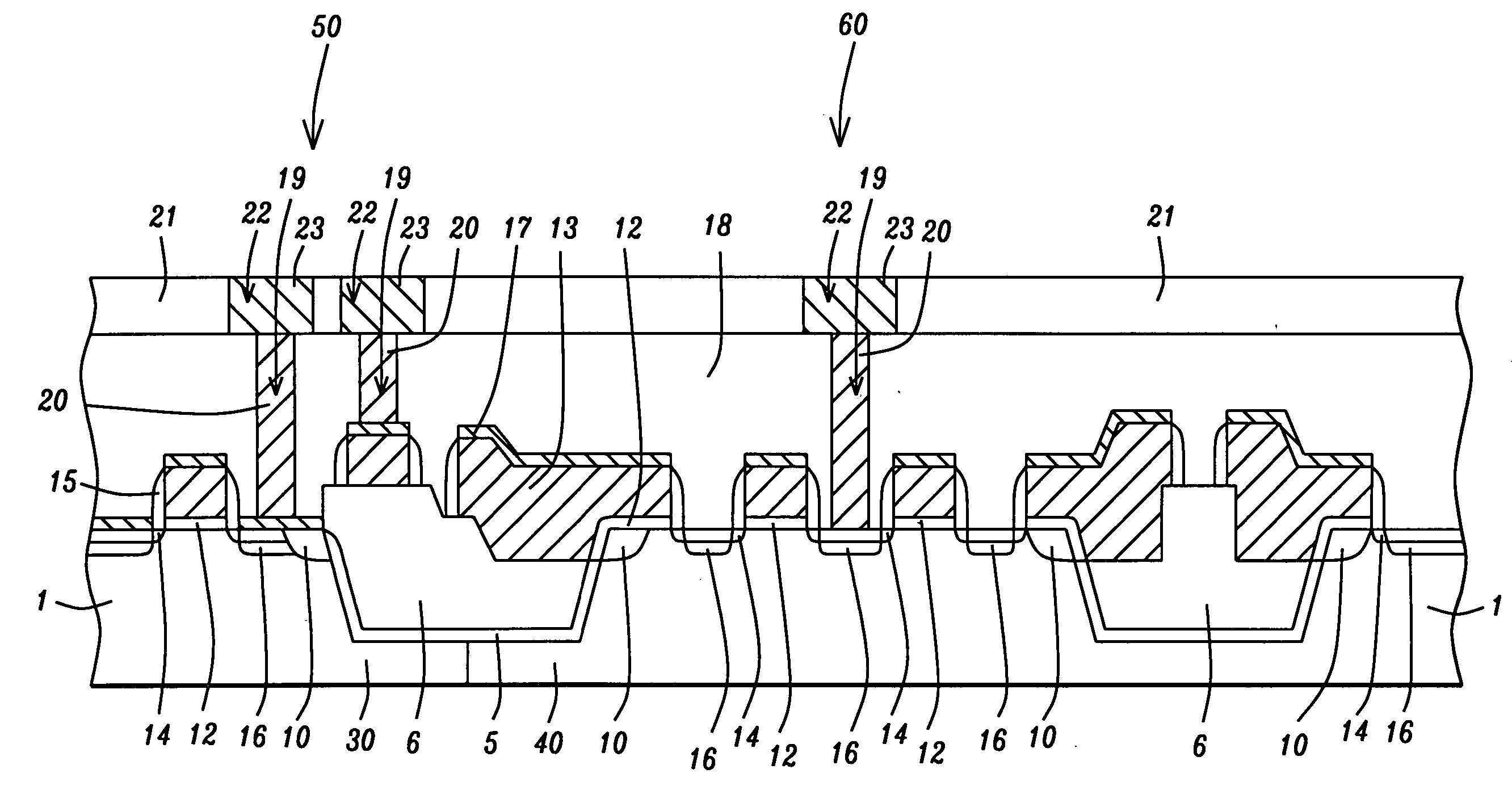

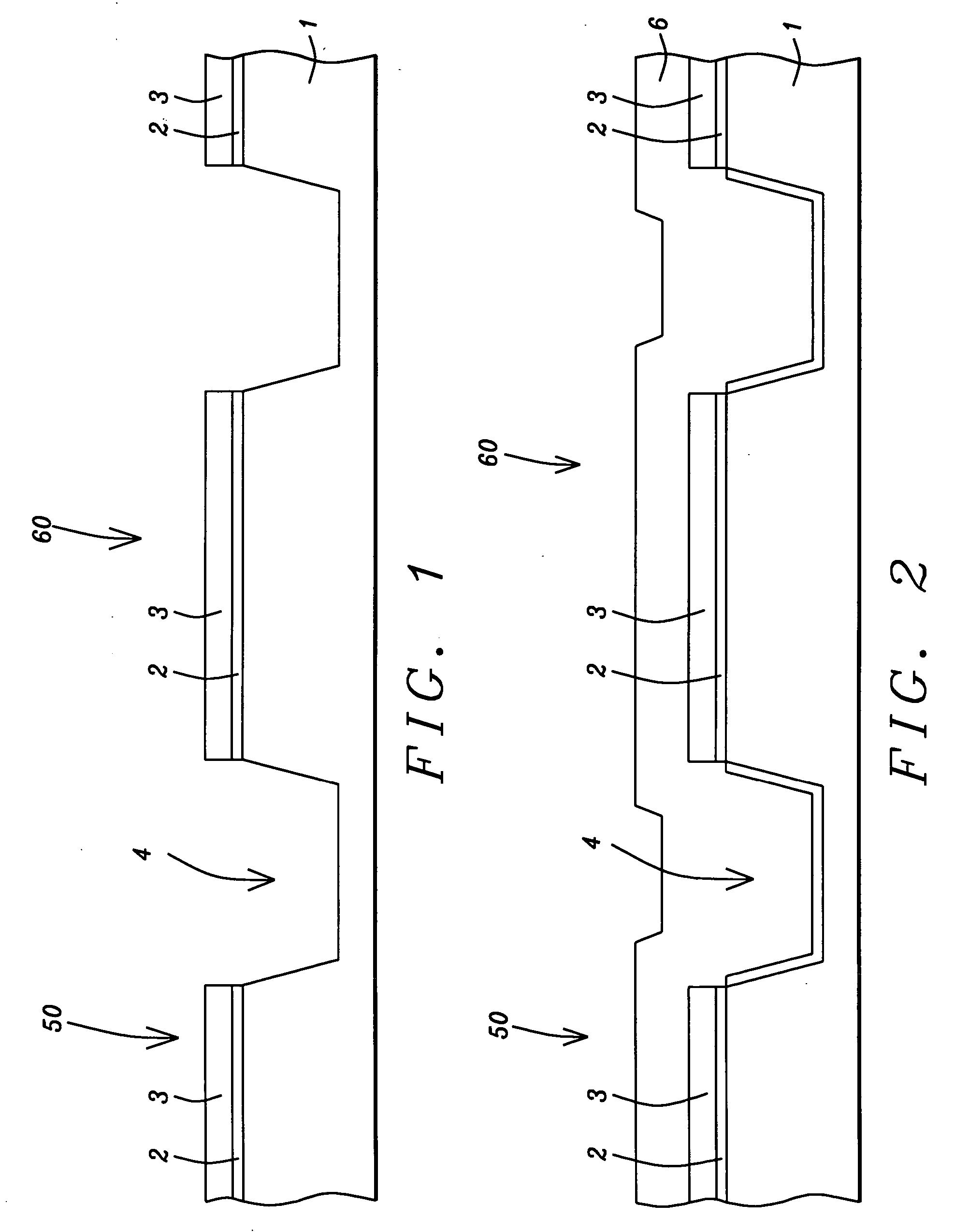

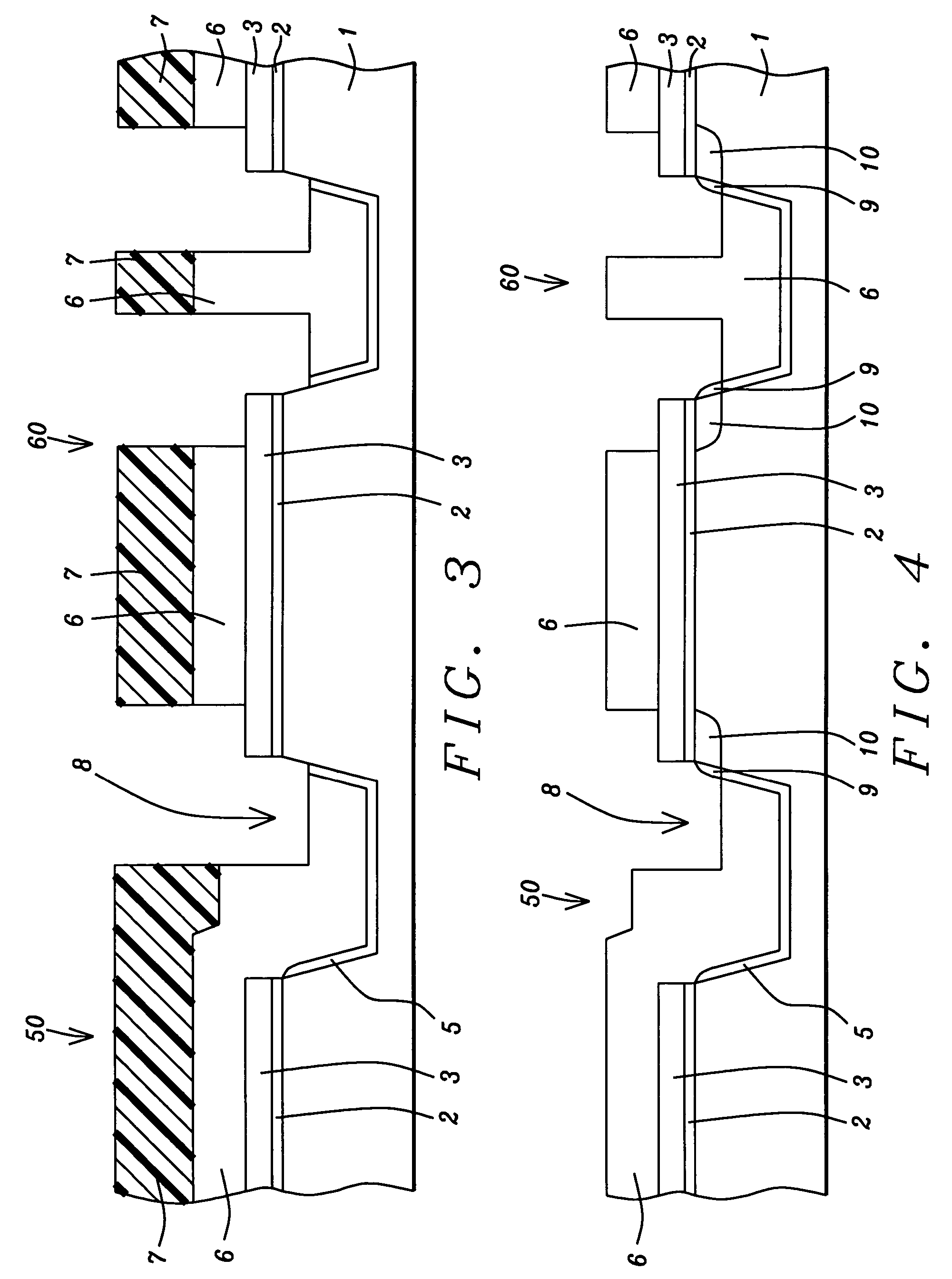

[0012] The method of integrating the fabrication of a capacitor cell in a logic process sequence wherein increased capacitor area and reduced risk of a capacitor depletion phenomena are realized via implantation of a capacitor region into a tapered silicon side wall exposed in an STI structure, will now be described in detail. Semiconductor substrate 1, comprised of P type single crystalline silicon, featuring a crystallographic orientation, is used and schematically shown in FIG. 1. The fabrication of a capacitor cell will be shown in region 60 of semiconductor substrate 1, integrated with the fabrication of logic devices in region 50 of semiconductor substrate 1. Pad oxide layer 2, comprised of silicon oxide is formed at a thickness between about 50 to 300 Angstroms, on the surface of semiconductor substrate 1, via thermal oxidation procedures, or via low pressure chemical vapor deposition (LPCVD) or plasma enhanced chemical vapor deposition (LPCVD) procedures. Silicon nitride la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More