High-low voltage device for plasma display driving chip and preparation method

A display drive, high and low voltage technology, applied in the field of row address driver chips and column address driver chips for ion displays, can solve problems such as insufficient reliability, achieve good reliability performance, high isolation reliability, and anti-latch performance Good results

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

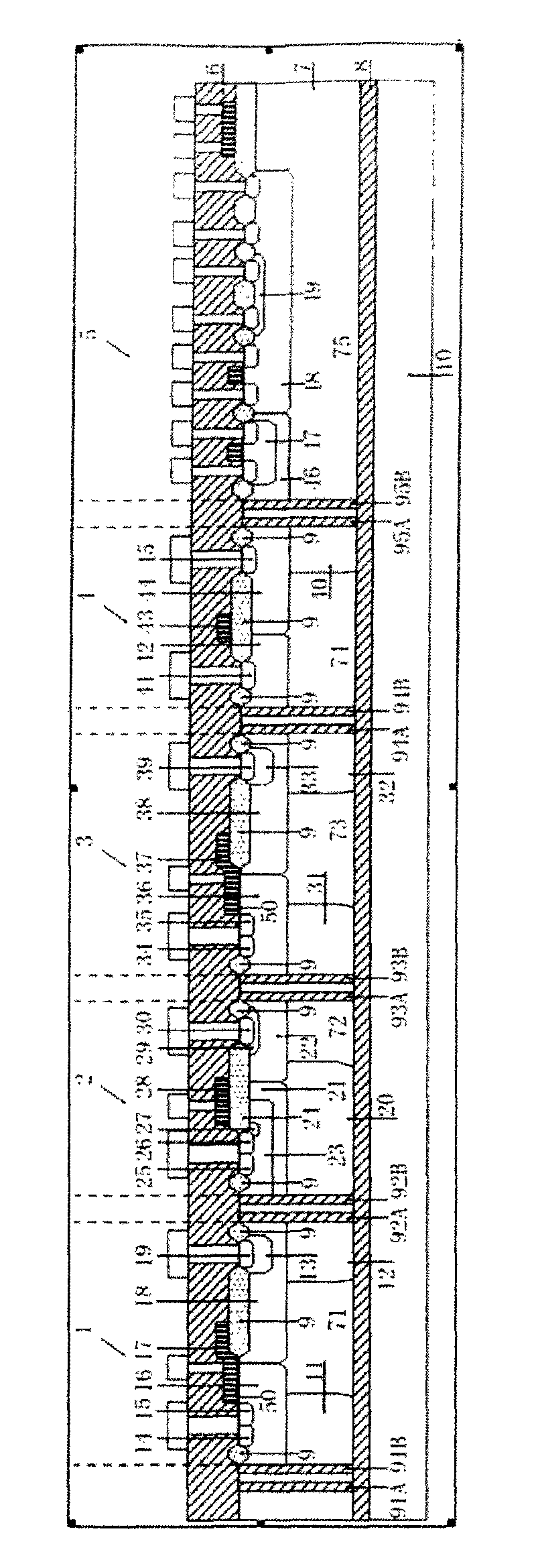

[0020] Below in conjunction with accompanying drawing, structure of the present invention is described in detail, as figure 1 As shown, a high and low voltage device for a plasma display driver chip includes a P-type substrate 10, a buried oxide layer 8 is arranged on the P-type substrate 10, and a high-voltage N-type lateral insulated gate double layer is arranged on the buried oxide layer 8. Pole type transistor 1, high-voltage P-type lateral double-diffused metal-oxide-semiconductor field-effect transistor 2, high-voltage N-type lateral double-diffused metal-oxide-semiconductor field-effect transistor 3, high-voltage diode 4 and low-voltage device 5, characterized in that the high-voltage N-type lateral The insulated gate bipolar transistor 1 is adjacent to the high-voltage P-type lateral double-diffused metal-oxide-semiconductor field-effect transistor 2, and the drain terminal of the high-voltage N-type lateral insulated-gate bipolar transistor 1 is connected to the high-v...

Embodiment 2

[0031] The preparation method of the high and low voltage device for the plasma display driver chip of the present invention is as follows:

[0032] The first step: take a P-type substrate 10 with an impurity concentration of 1.0e15cm-3, and pre-clean it as shown in Figure 2(a); prepare a buried oxide layer 8 on the P-type substrate 10 as shown in Figure 2(b ); then grow a P-type epitaxial layer 7 with an impurity concentration of 1e15cm-3 as shown in FIG. High voltage N well 12 of insulated gate bipolar transistor 1, high voltage N well 20 of high voltage P-type lateral double diffused metal oxide semiconductor field effect transistor 2, high voltage N well of high voltage N type lateral double diffused metal oxide semiconductor field effect transistor 3 The well 32 and the high-voltage N well 40 of the high-voltage diode 4, after a simple treatment of rapid thermal annealing, directly inject boron with a dose of 3e12cm-2 and high-temperature annealing to form a high-voltage ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More