Semiconductor structure and its forming method, transverse diffusion p-type mos device

A semiconductor and metal-oxide-semiconductor technology, applied in the field of metal-oxide-semiconductor components, can solve problems such as transistor failures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

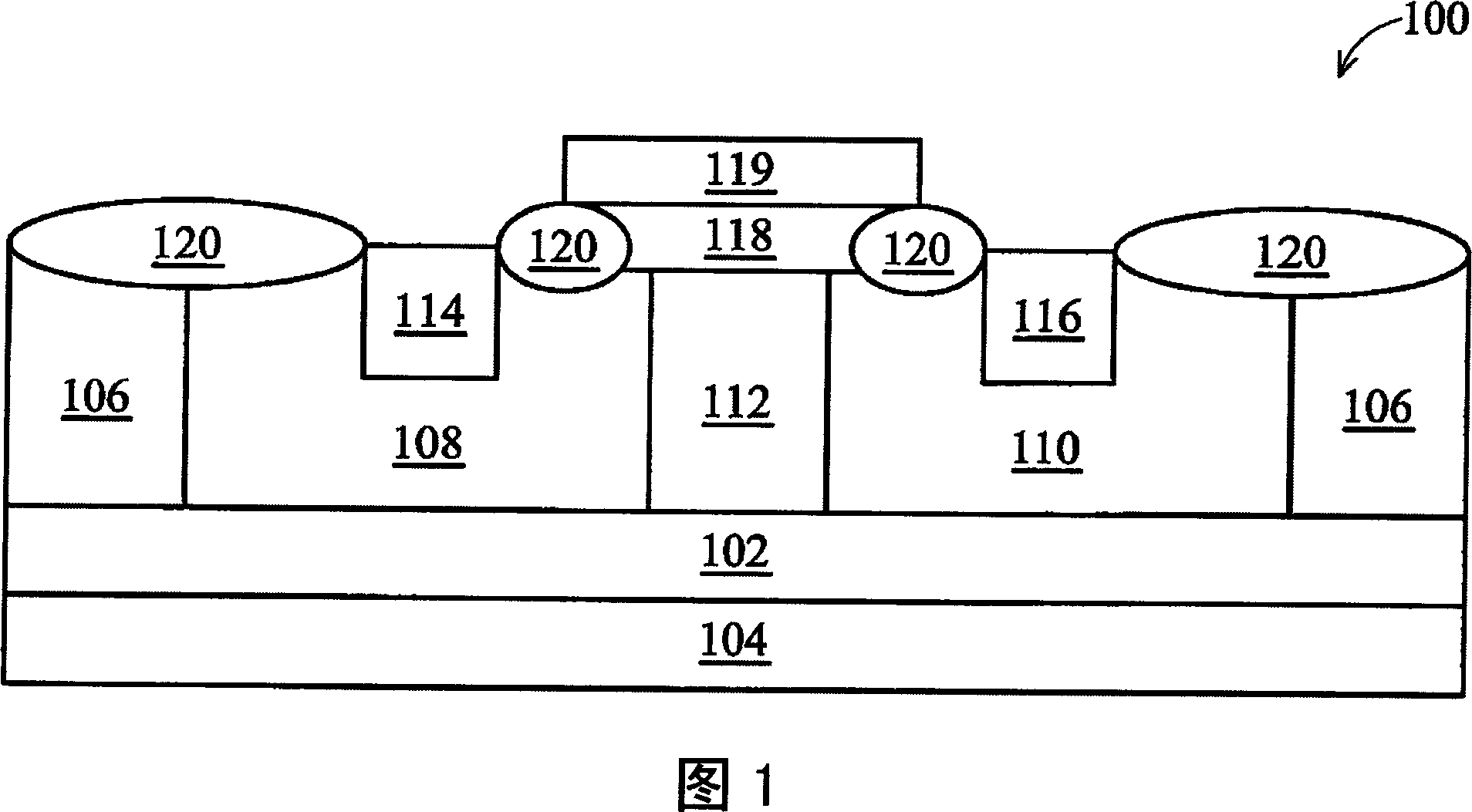

[0029] FIG. 1 is a cross-sectional view 100 of a symmetrical laterally diffused PMOS (hereinafter referred to as LDPMOS) transistor without an epitaxial layer in the prior art. The method of this LDPMOS transistor is as follows: first, an N-type buried layer 102 is formed on the P-type semiconductor substrate 104 , and then an N-type isolation ring 106 is formed on the N-type buried layer 102 . P-type well regions 108 and 110 are formed in the isolation ring 106 and separated by an N-type well region 112 . The drain (not shown) of the LDPMOS transistor is connected to P+ contact 114 and the source (not shown) is connected to P+ contact 116 . A gate oxide layer 118 is formed on the N-type well region 112 and part of the P-type well regions 108 and 110 . A gate structure 119 is then formed on the gate oxide layer 118, and an oxide layer 120 is selectively formed on the surface of the LDPMOS transistor.

[0030] Since this LDPMOS transistor does not have an epitaxial layer, a t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More