CMOS (Complementary Metal Oxide Semiconductor) device and manufacturing method thereof

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve problems such as affecting CMOS performance, serious bottom leakage current, etc., to improve mobility, improve response speed, and solve the problem of lining Effect of bottom leakage current problem

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

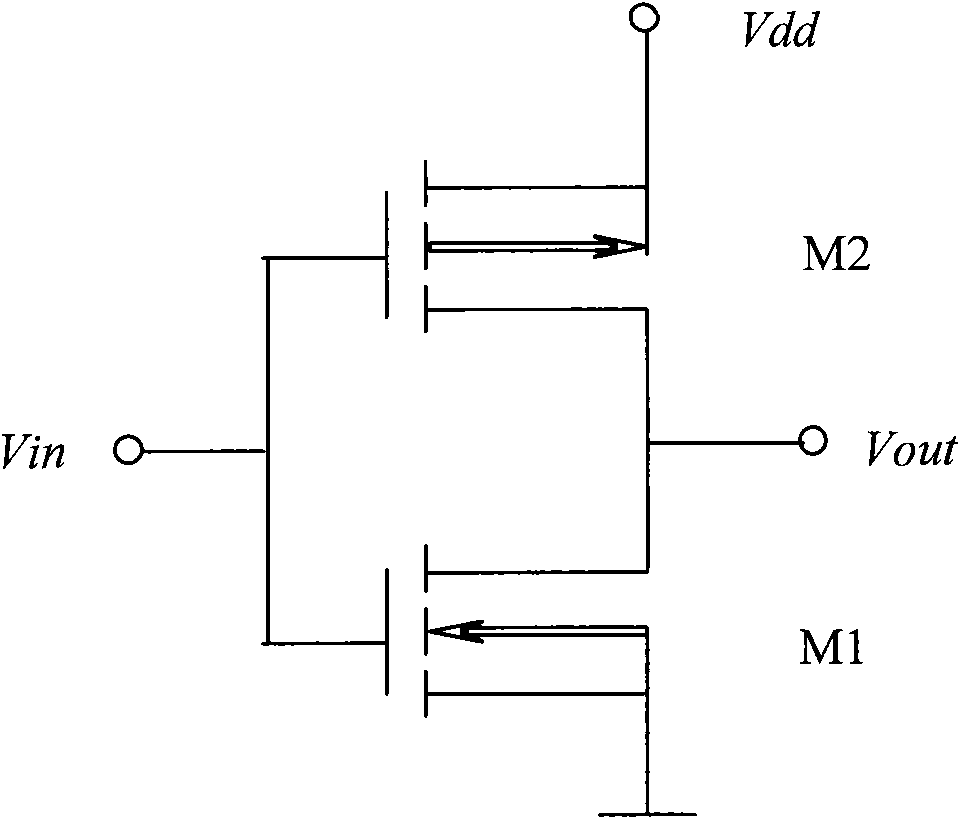

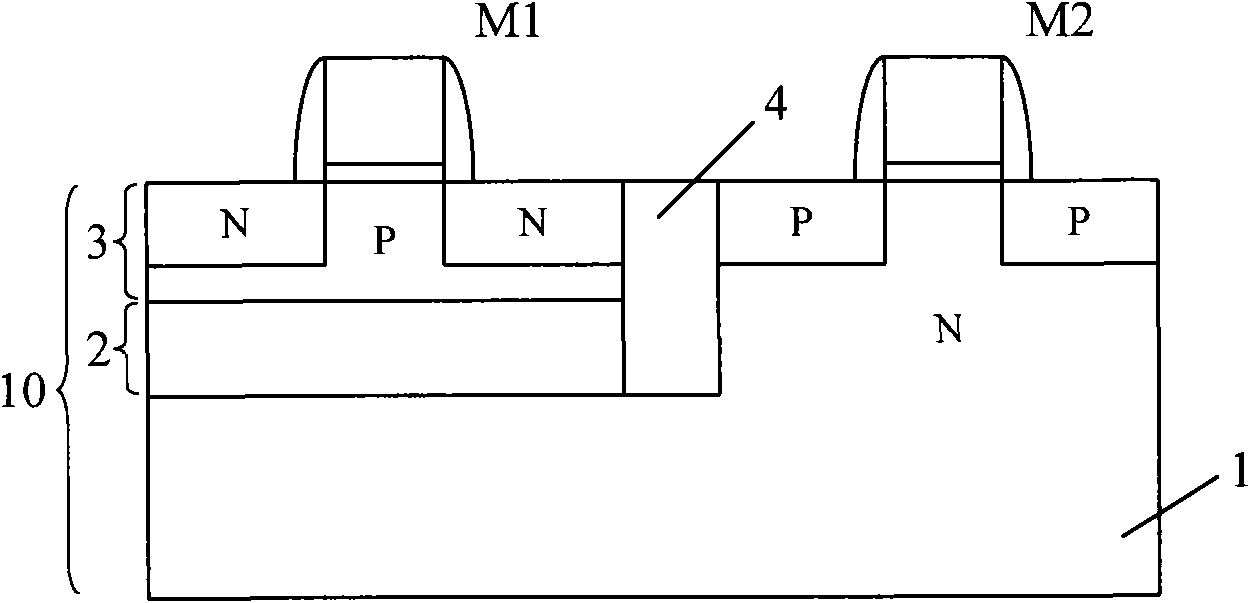

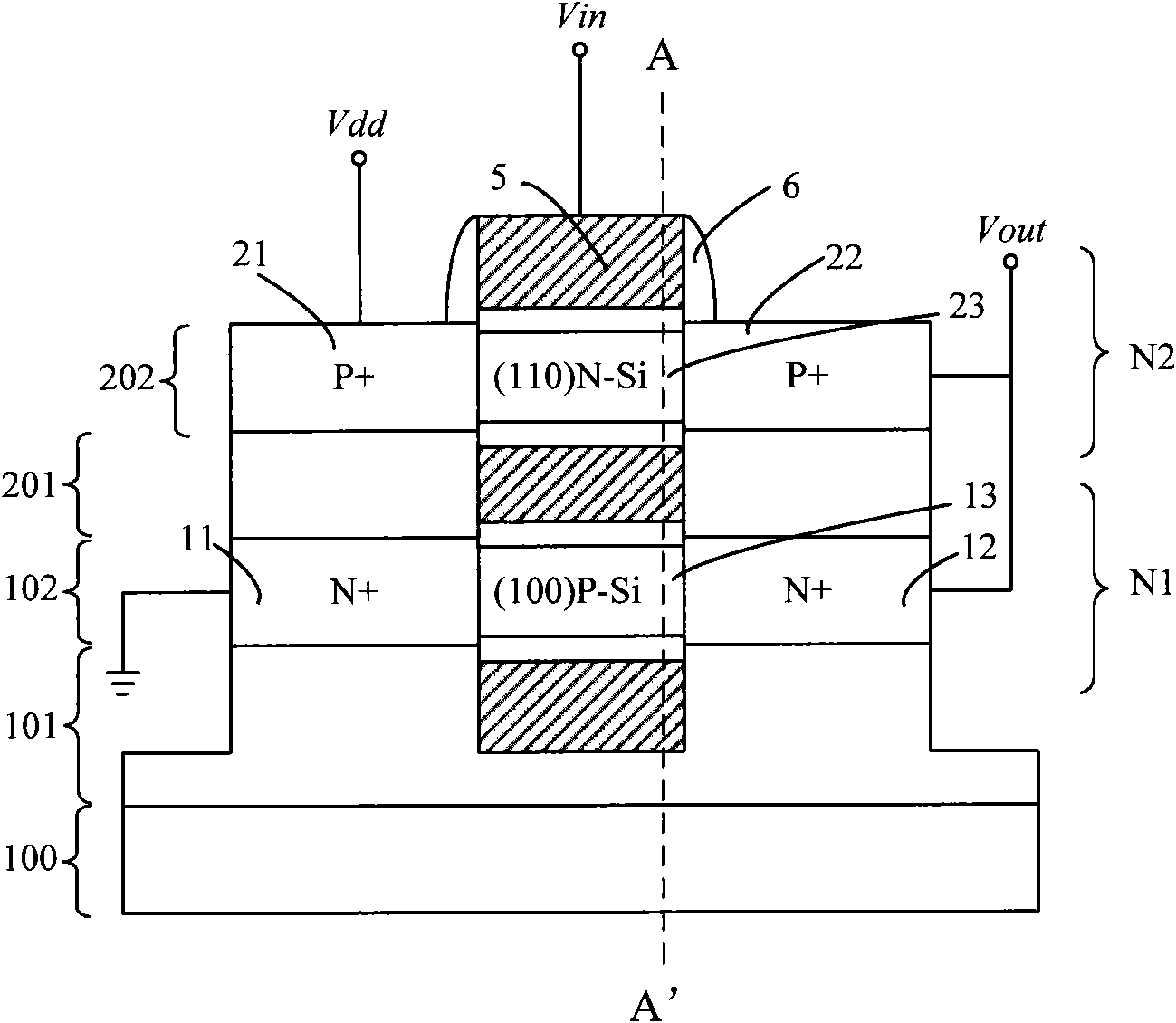

[0049] Existing composite substrate CMOS devices, because there is always a transistor directly formed on the silicon substrate, and the leakage current of the substrate is easy to occur, the CMOS device of the present invention stacks transistors on the silicon-on-insulator, and uses different The crystal orientation and layers of the top layer of silicon are used as the base of each transistor to form a conductive channel, supplemented by a multi-layer buried oxide layer to insulate the base, so as to solve the above-mentioned leakage current problem.

[0050] Such as image 3 Shown is the cross-sectional structure diagram of the CMOS device of the present invention, Figure 4 for along image 3 The cross-sectional schematic diagram of the A-A' section in the middle, combined with image 3 as well as Figure 4 , the CMOS device of the present invention specifically includes:

[0051] A silicon substrate 100, a first buried oxide layer 101, a first top layer silicon 102, ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More