Method for manufacturing transistor

A manufacturing method and transistor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as unstable device performance, improve quality, and avoid leakage current problems.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

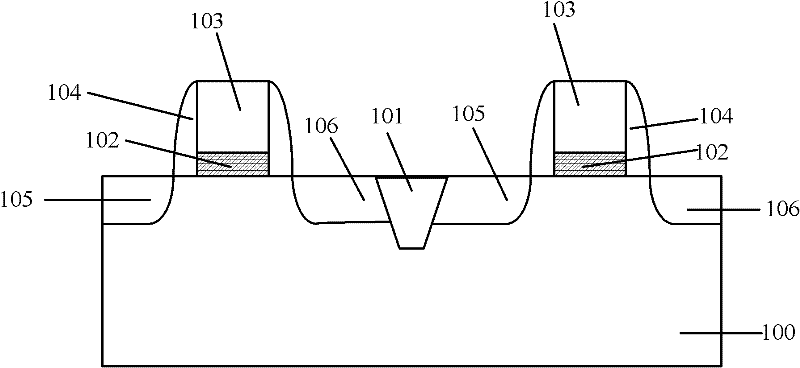

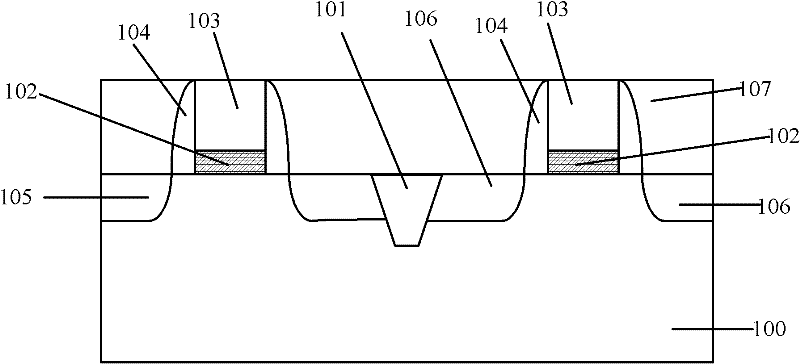

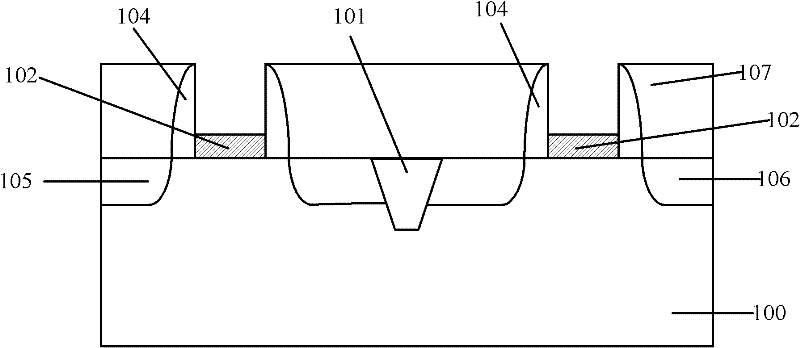

[0039] The transistors manufactured by the existing method using the high-K dielectric as the gate dielectric layer have leakage current, and the performance of the device is unstable. After research by the inventors, it is found that the leakage current of the transistor is caused by the damage of the gate dielectric layer by the etching process. Specifically, combined with image 3 , when performing an etching process to remove the dummy gate, using the dummy gate (made of polysilicon) and the interlayer dielectric layer (made of silicon oxide) 107 and the dummy gate and sidewalls (made of nitrogen) Silicon (Si) 104 has an etching selectivity, so there is no need to set a mask layer on the interlayer dielectric layer 107 and the sidewall 104, so that the surface of the interlayer dielectric layer 107 is exposed. However, the above etching process damages the gate dielectric layer 103 under the dummy gate, thus causing leakage current of the transistor.

[0040] The invento...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More