Preparation methods of thin film transistor and array substrate, array substrate and display device

A thin-film transistor and thin-film technology, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, and electric solid-state devices, can solve the problems of increasing manufacturing process steps, increasing production costs, and reducing product yields.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

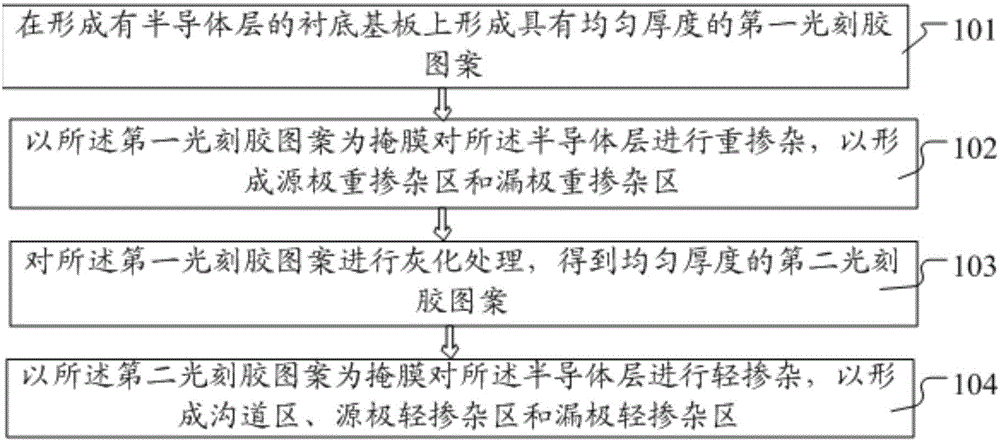

[0034] At least one embodiment of the present invention provides a method for manufacturing a thin film transistor, comprising: forming a first photoresist pattern with a uniform thickness on a base substrate formed with a semiconductor layer; using the first photoresist pattern as a mask pair The semiconductor layer is heavily doped to form a heavily doped source region and a heavily doped drain region; ashing the first photoresist pattern to obtain a second photoresist pattern with a uniform thickness; The resist pattern is used as a mask to lightly dope the semiconductor layer to form a channel region, a lightly doped source region and a lightly doped drain region.

[0035] The "half-exposure process" in the present disclosure refers to exposing the photoresist layer using, for example, a gray-tone mask or a half-tone mask. The areas of the photoresist that are exposed by the gray or half-tone areas are called half-exposed areas.

[0036] In the present invention, it is on...

Embodiment 1

[0039] This embodiment provides a method for manufacturing a thin film transistor. For example, figure 1 A process flow chart of a thin film transistor manufacturing method provided in this embodiment. include:

[0040] Step 101: forming a first photoresist pattern with a uniform thickness on the substrate on which the semiconductor layer is formed;

[0041] Step 102: using the first photoresist pattern as a mask to heavily dope the semiconductor layer to form a heavily doped source region and a heavily doped drain region;

[0042] Step 103: Perform ashing treatment on the first photoresist pattern to obtain a second photoresist pattern with a uniform thickness;

[0043] Step 104: Lightly doping the semiconductor layer by using the second photoresist pattern as a mask to form a lightly doped source region and a lightly doped drain region of the channel region.

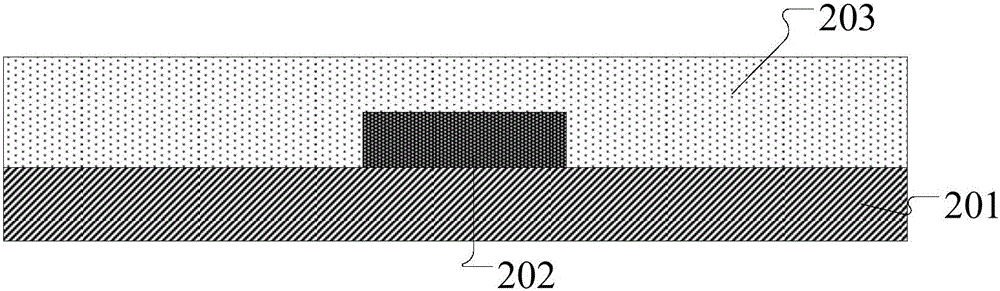

[0044] For example, in order to more clearly illustrate the fabrication process of thin film transistors, Figu...

Embodiment 2

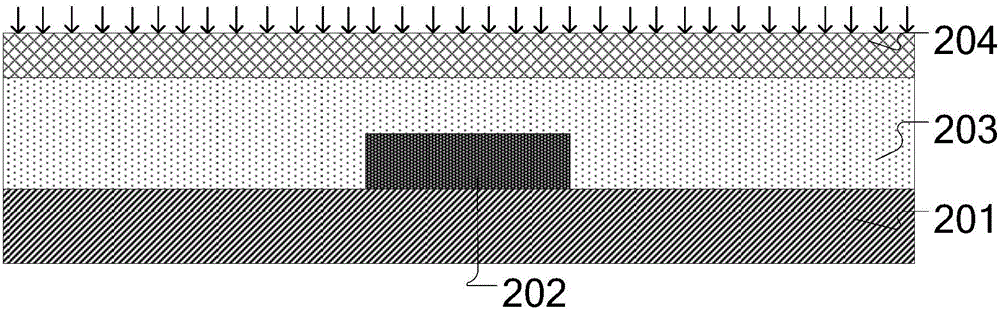

[0062] This embodiment provides a method for manufacturing a thin film transistor. Figure 3a-3h A schematic process flow diagram of another manufacturing method of a bottom-gate thin film transistor provided by an embodiment of the present invention is given.

[0063] For example, if Figure 3a As shown, a semiconductor layer thin film 204 is deposited on the first buffer layer 203, the semiconductor layer thin film 204 is doped and then coated with photoresist for patterning, so that the channel region to be formed is also doped. For example, the threshold voltage (threshold voltage, Vth) of the semiconductor layer thin film 204 is adjusted by using a doping process. For example, the doping process for adjusting the threshold voltage may be a boron ion or phosphorus ion doping implantation process for the semiconductor layer film 204 .

[0064] For example, if Figure 3b As shown, a photoresist (not shown) is coated on the semiconductor layer film, and the photoresist is ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More