Patents

Literature

830results about How to "Reduce conduction" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

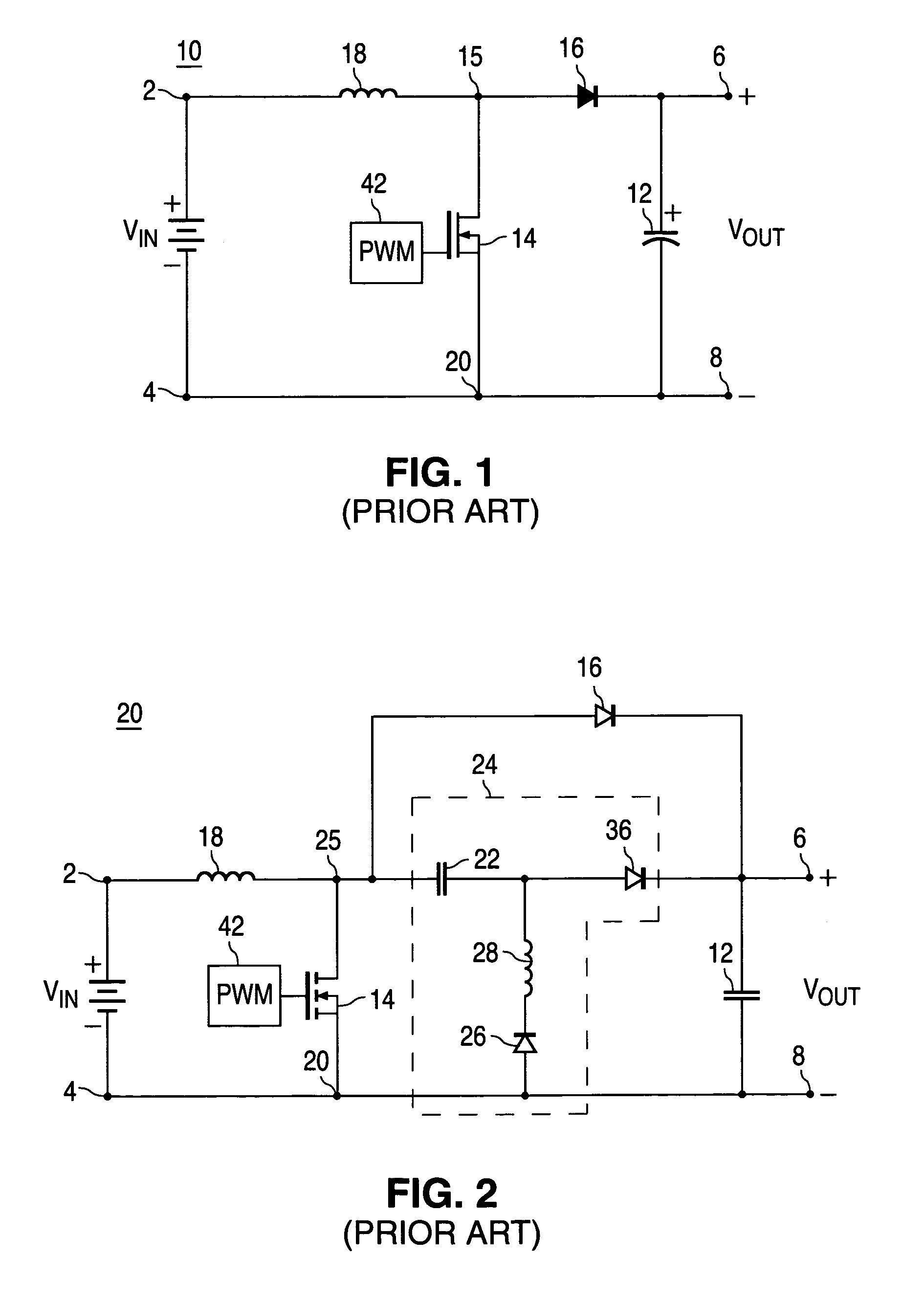

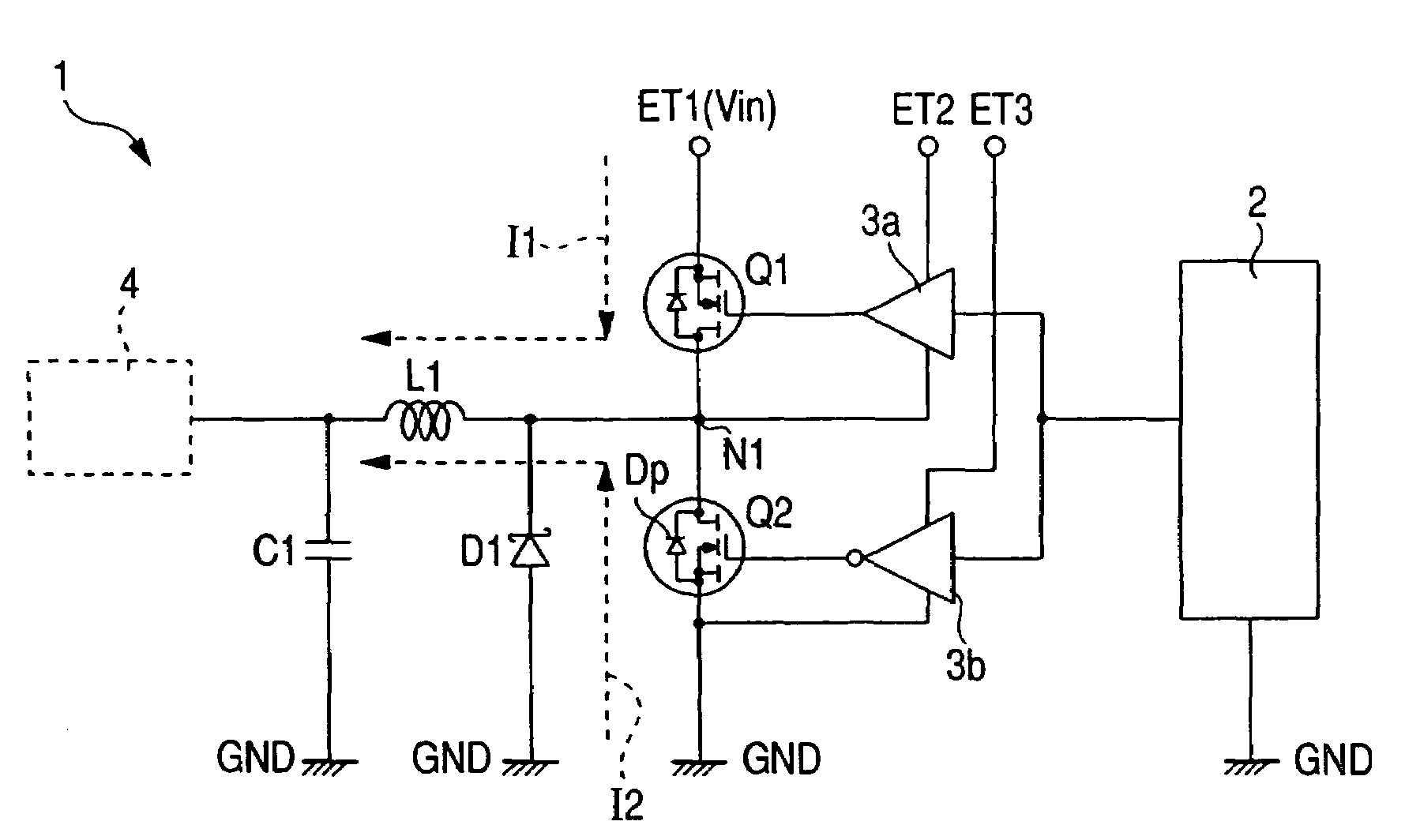

Snubber circuit for a power converter

InactiveUS7385833B2Easy to controlHigh voltageEfficient power electronics conversionDc-dc conversionTransverterEngineering

Owner:ASTEC INT LTD

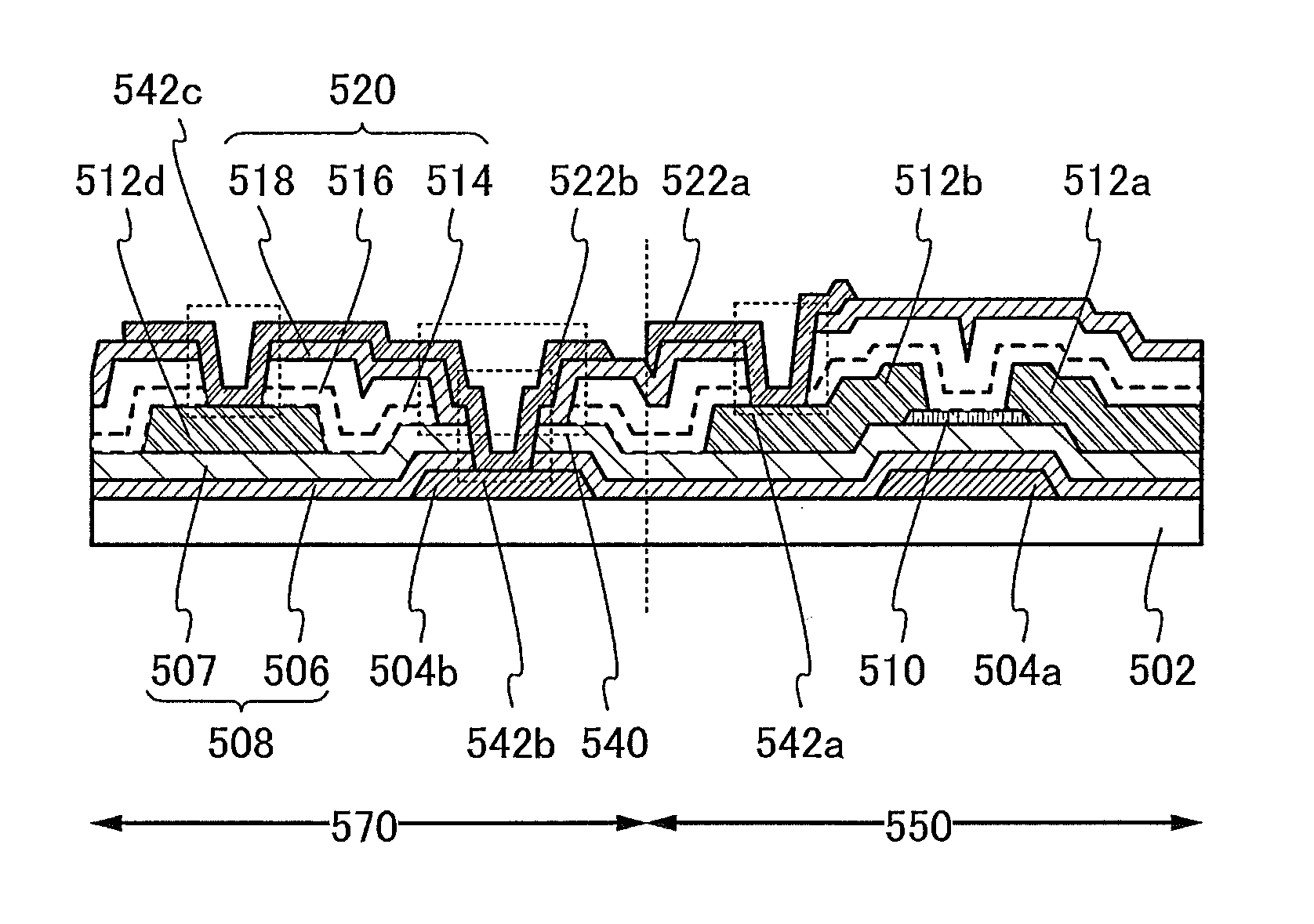

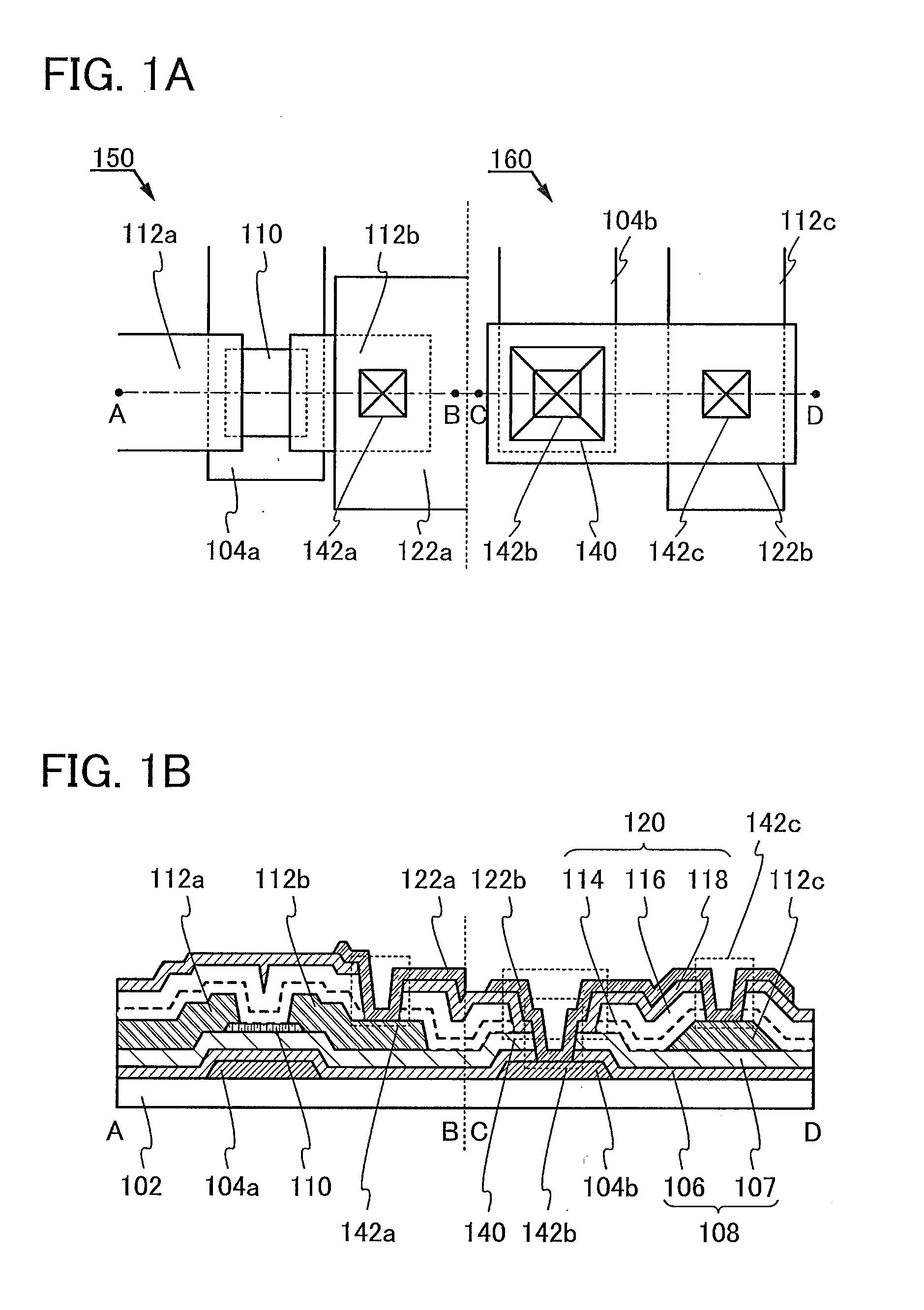

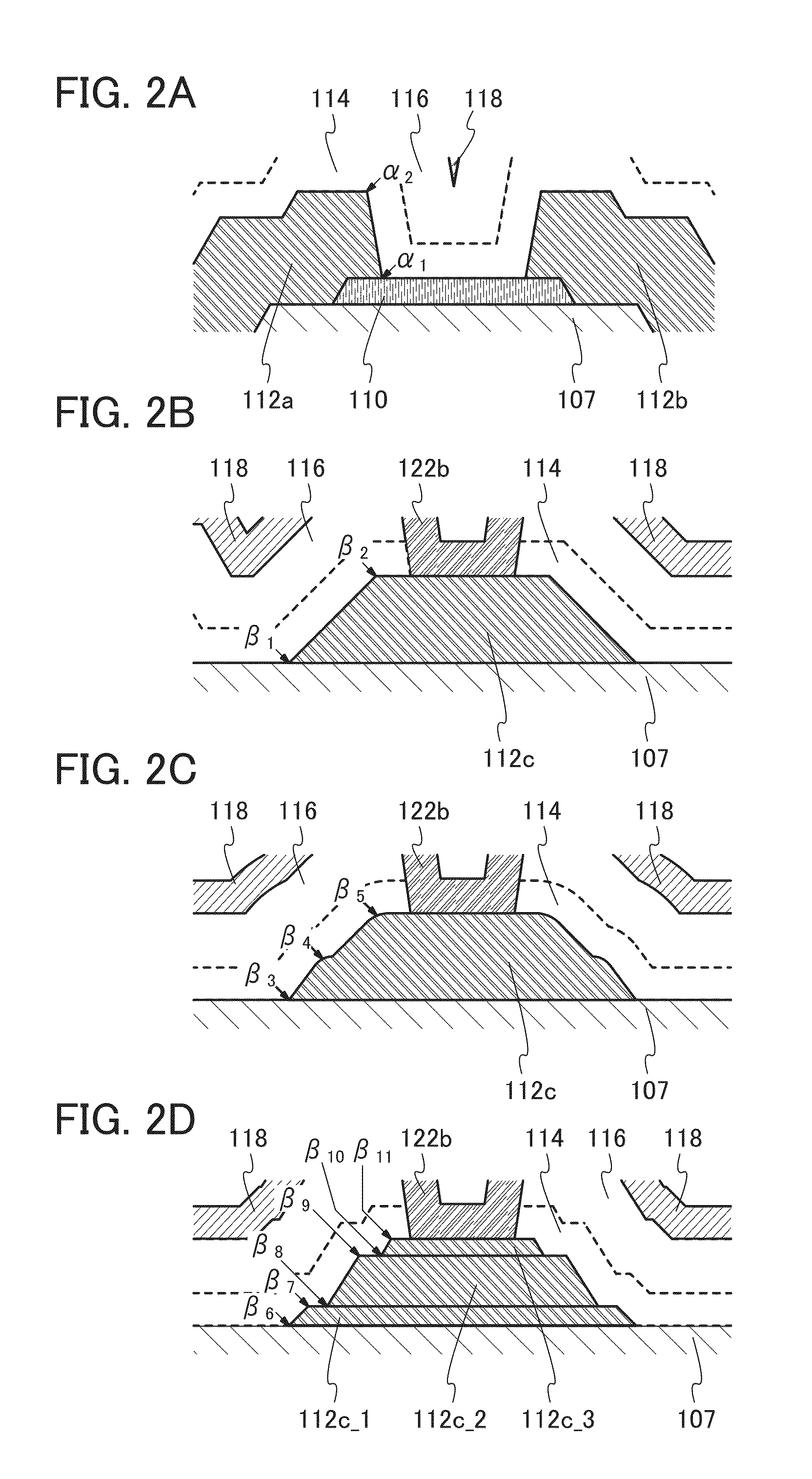

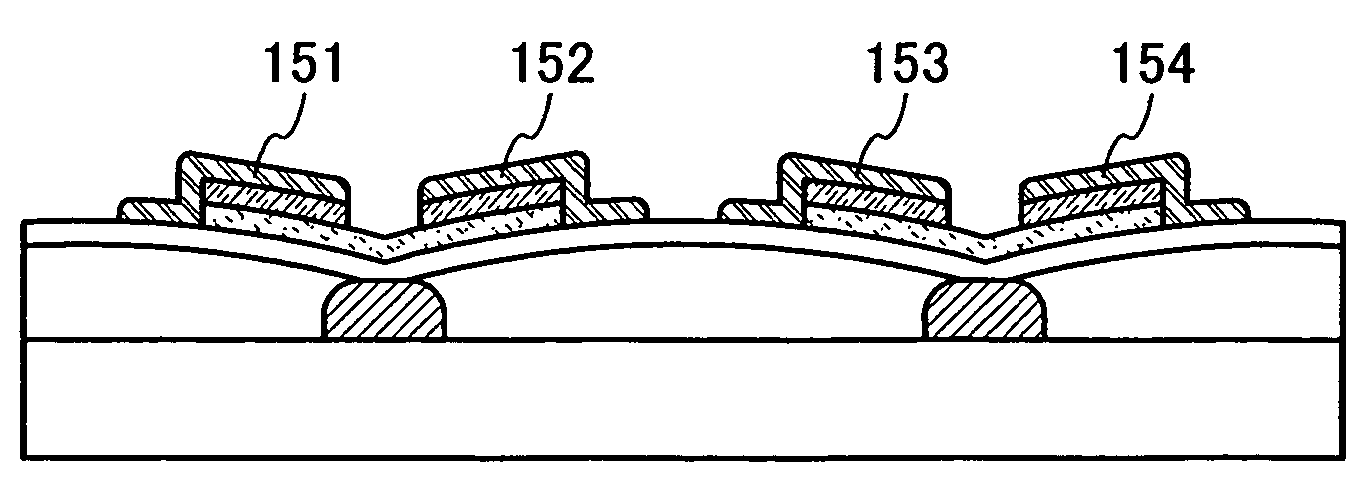

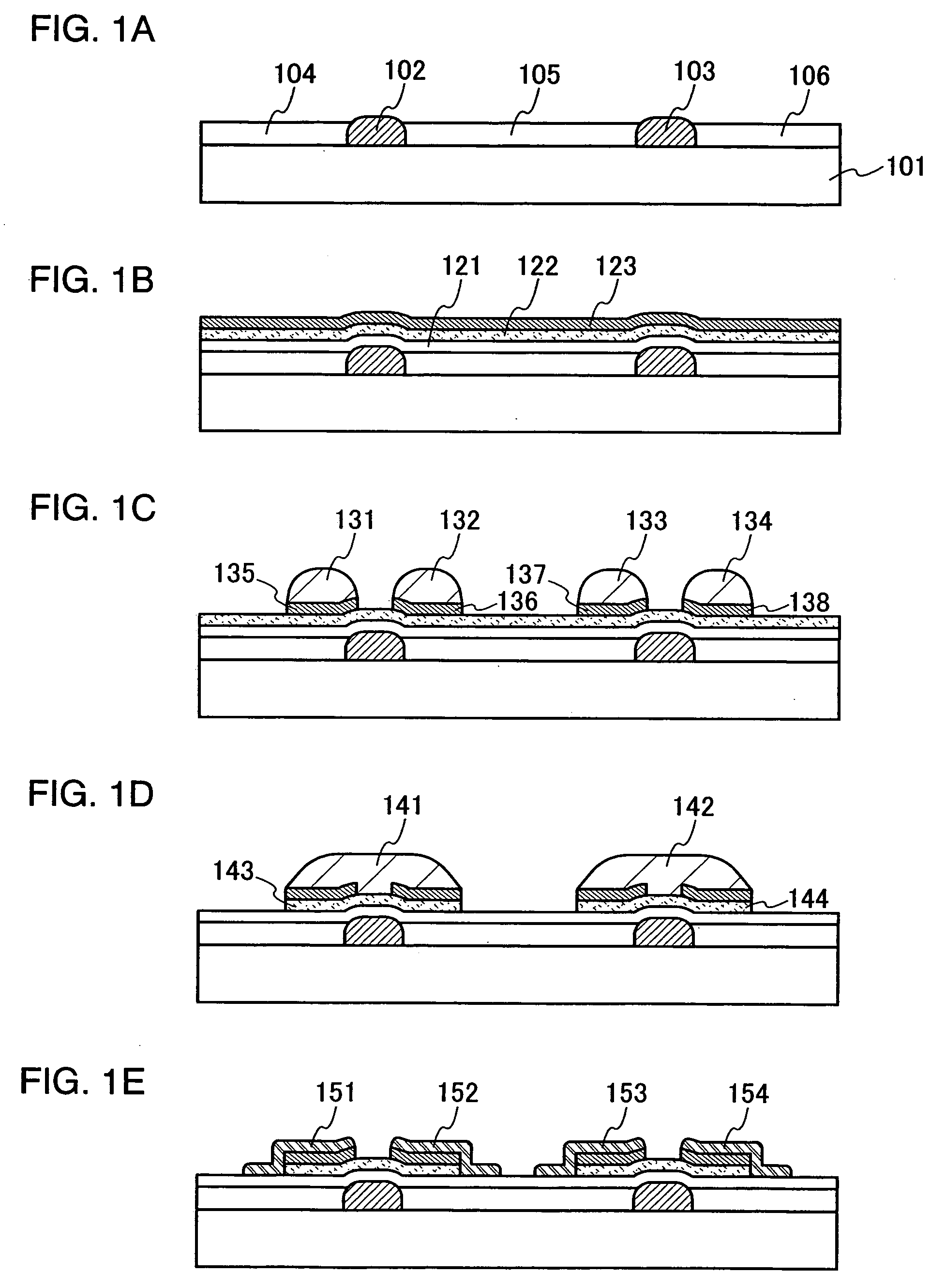

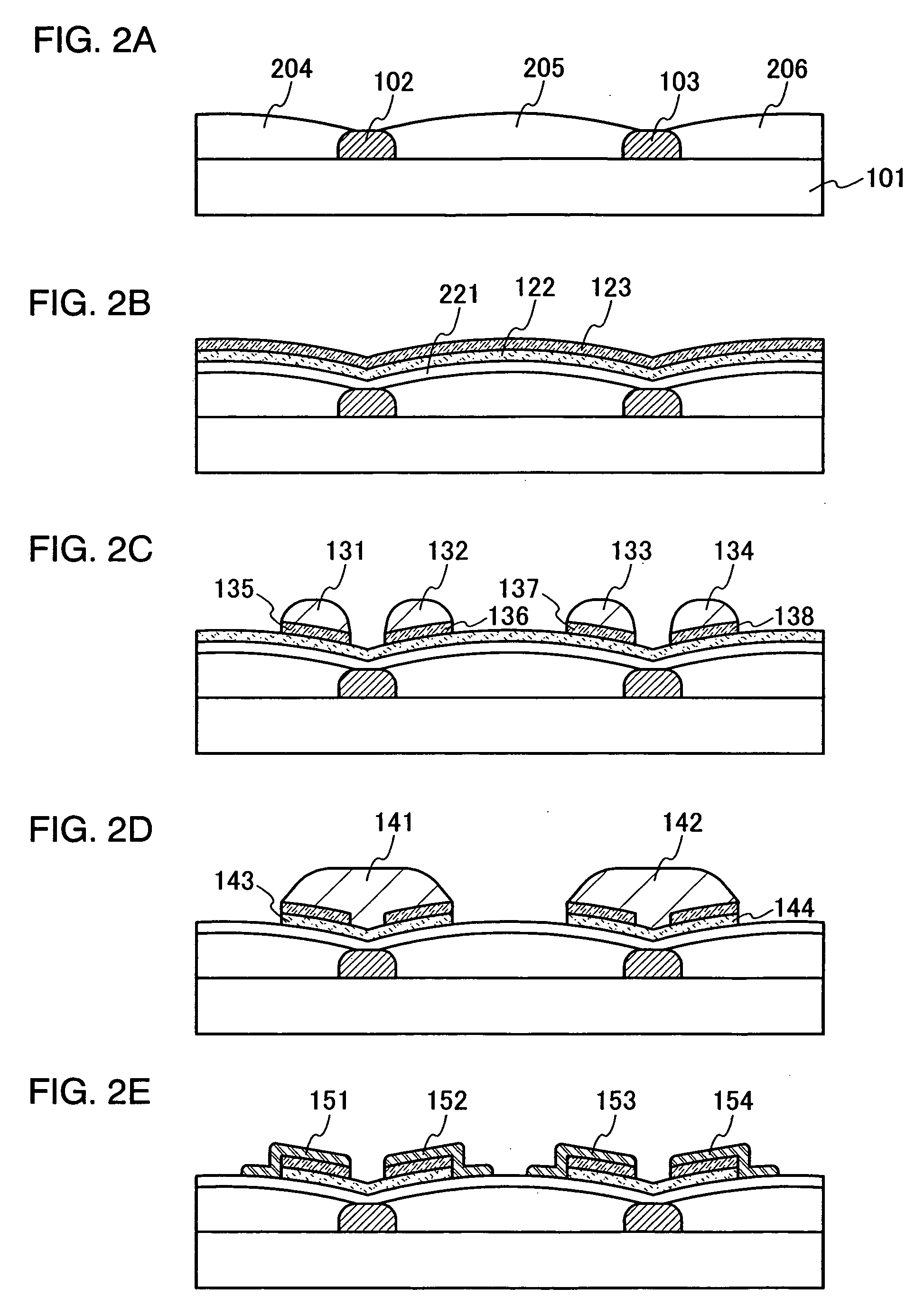

Semiconductor device and display device including the semiconductor device

ActiveUS20150014680A1Excellent electrical propertiesImprove featuresSolid-state devicesNon-linear opticsPower semiconductor deviceDisplay device

A semiconductor device including a transistor and a connection portion is provided. The transistor includes a gate electrode, a first insulating film over the gate electrode, an oxide semiconductor film over the first insulating film and at a position overlapping with the gate electrode, and source and drain electrodes electrically connected to the oxide semiconductor film; and the connection portion includes a first wiring on the same surface as a surface on which the gate electrode is formed, a second wiring on the same surface as a surface on which the source and drain electrodes are formed, and a third wiring connecting the first wiring and the second wiring. The distance between an upper end portion and a lower end portion of the second wiring is longer than the distance between an upper end portion and a lower end portion of each of the source and drain electrodes.

Owner:SEMICON ENERGY LAB CO LTD

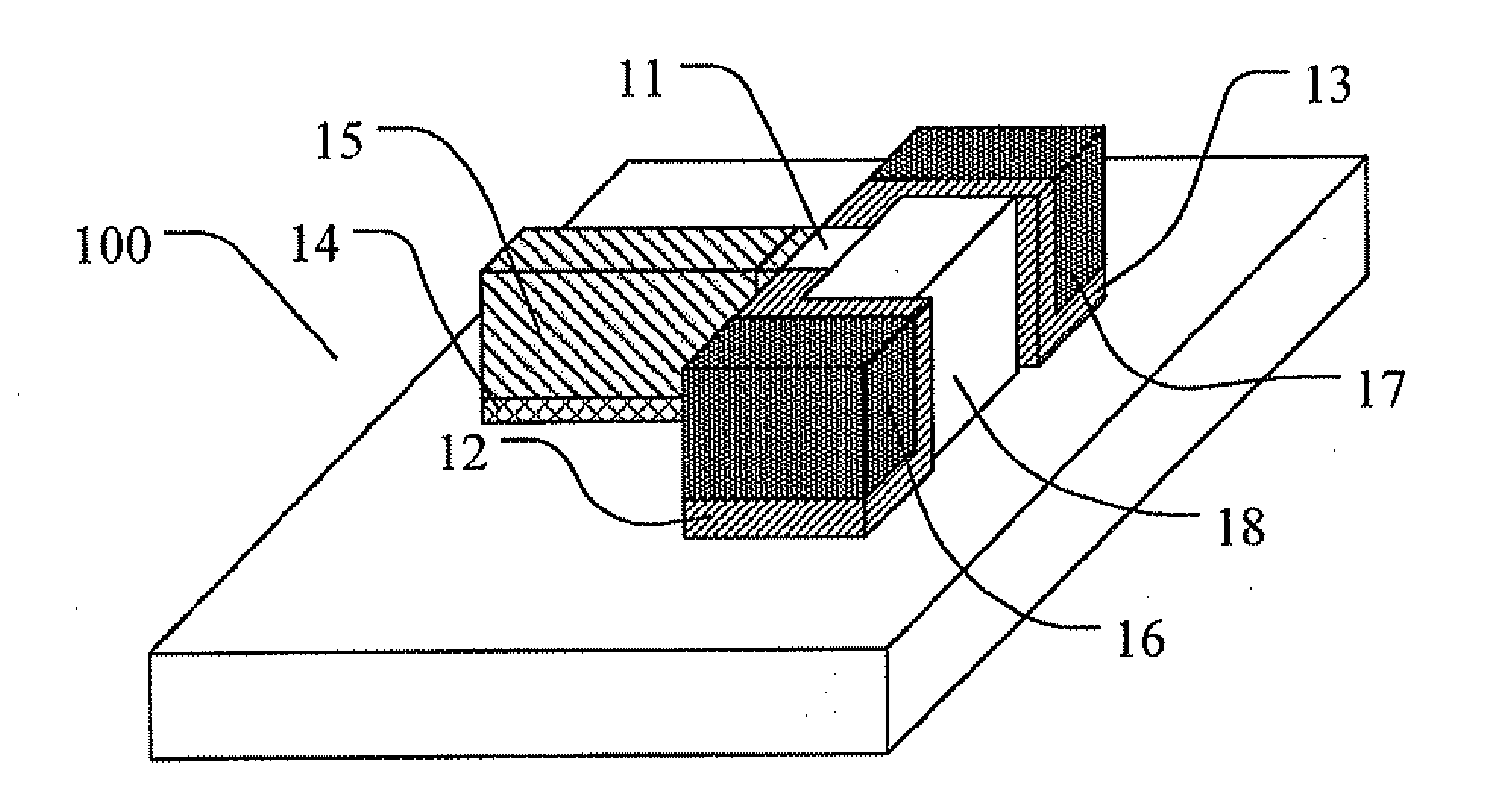

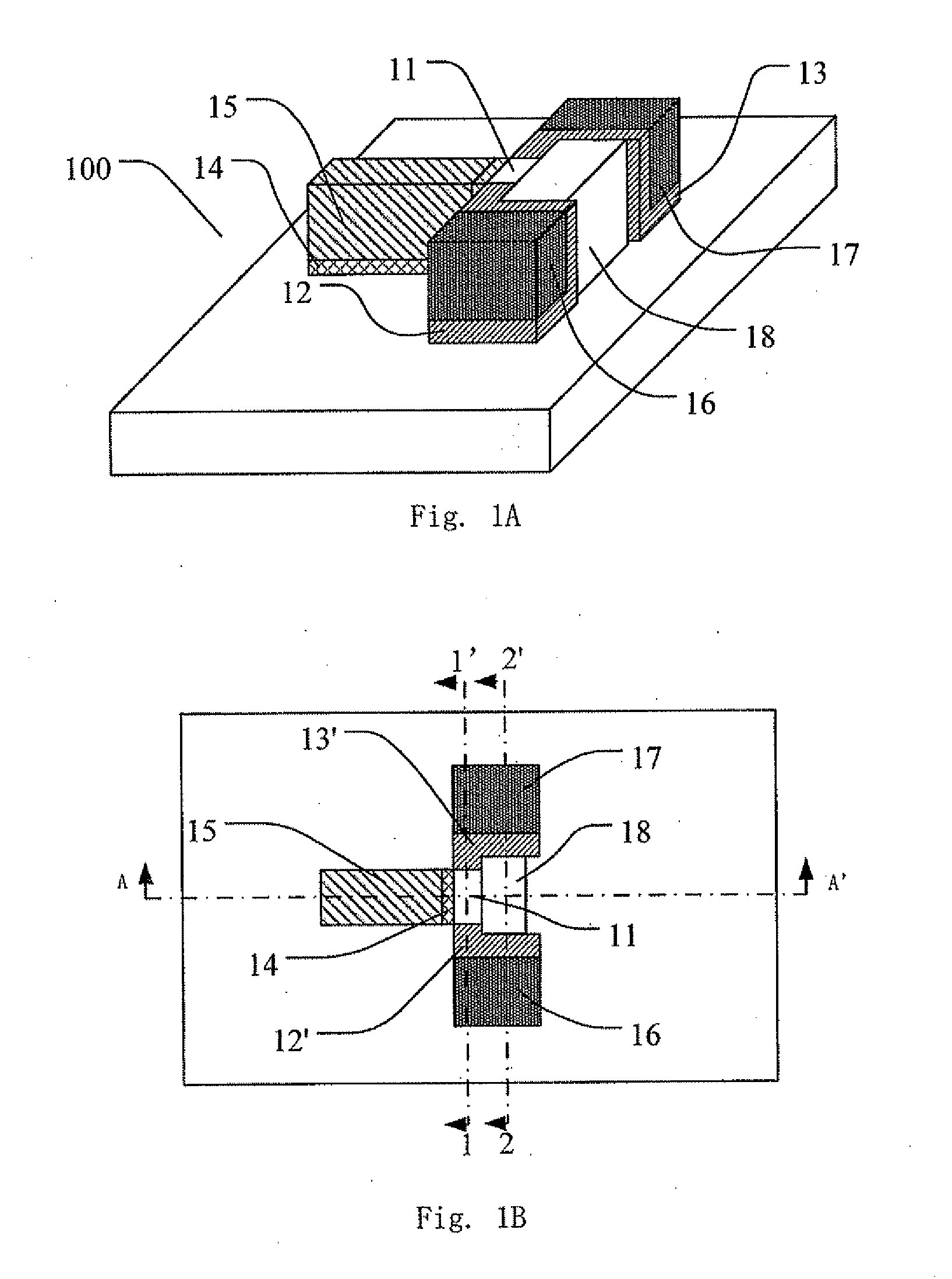

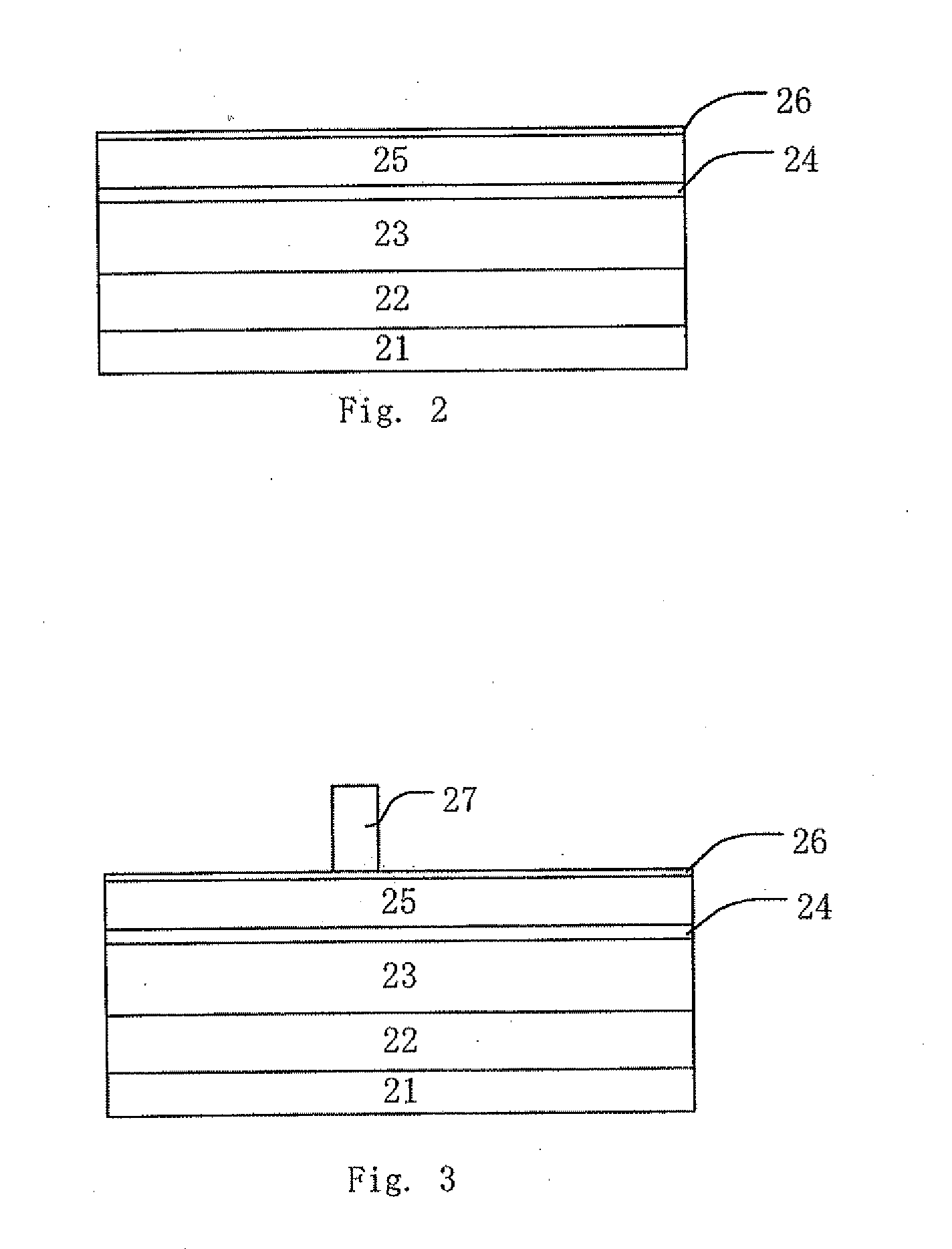

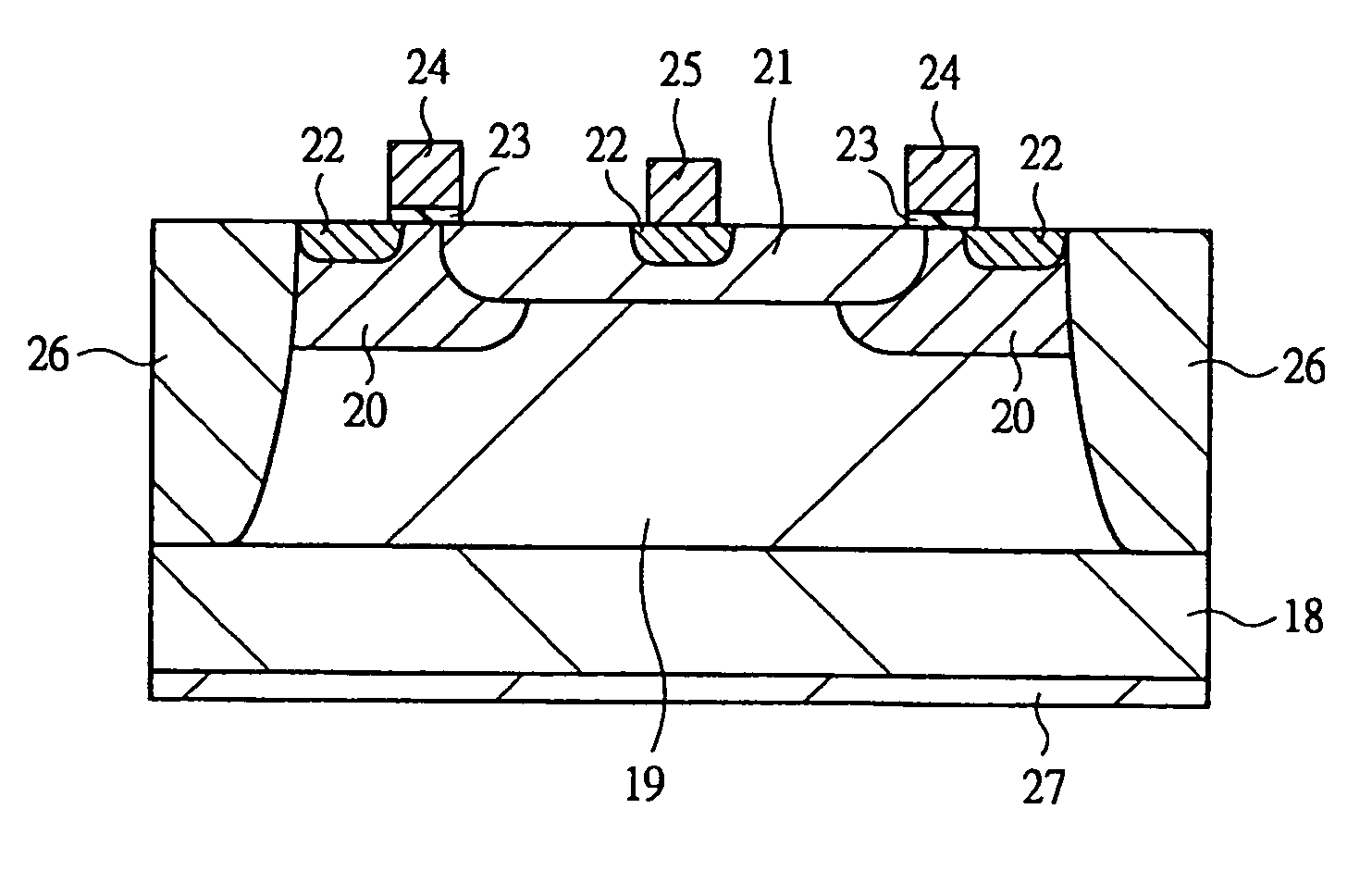

Semiconductor device and method for manufacturing the same

ActiveUS20110193164A1Reduce parasitic capacitanceLarge thicknessSolid-state devicesSemiconductor/solid-state device manufacturingPower semiconductor deviceGate dielectric

The present application discloses a semiconductor device formed on a SOI substrate which comprises a buried insulating layer and a semiconductor layer on the buried insulating layer and a method for manufacturing the same, wherein a fin of semiconductive material having two opposing sides perpendicular to a main surface of the SOI substrate is provided in the semiconductor layer, said semiconductor device comprising: a source region and a drain region provided at two ends of the fin respectively; a channel region provided at a central portion of the fin; and a stack of gate dielectric and gate conductor provided at one side of the fin, where the gate conductor is isolated from the channel region by the gate dielectric, wherein the gate conductor extends away from the one side of the fin in a direction parallel to the main surface of the SOI substrate. The semiconductor device has an improved short channel effect and a reduced parasitic capacitance and resistance, which contributes to an improved electrical property and facilitates scaling down of the transistor.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

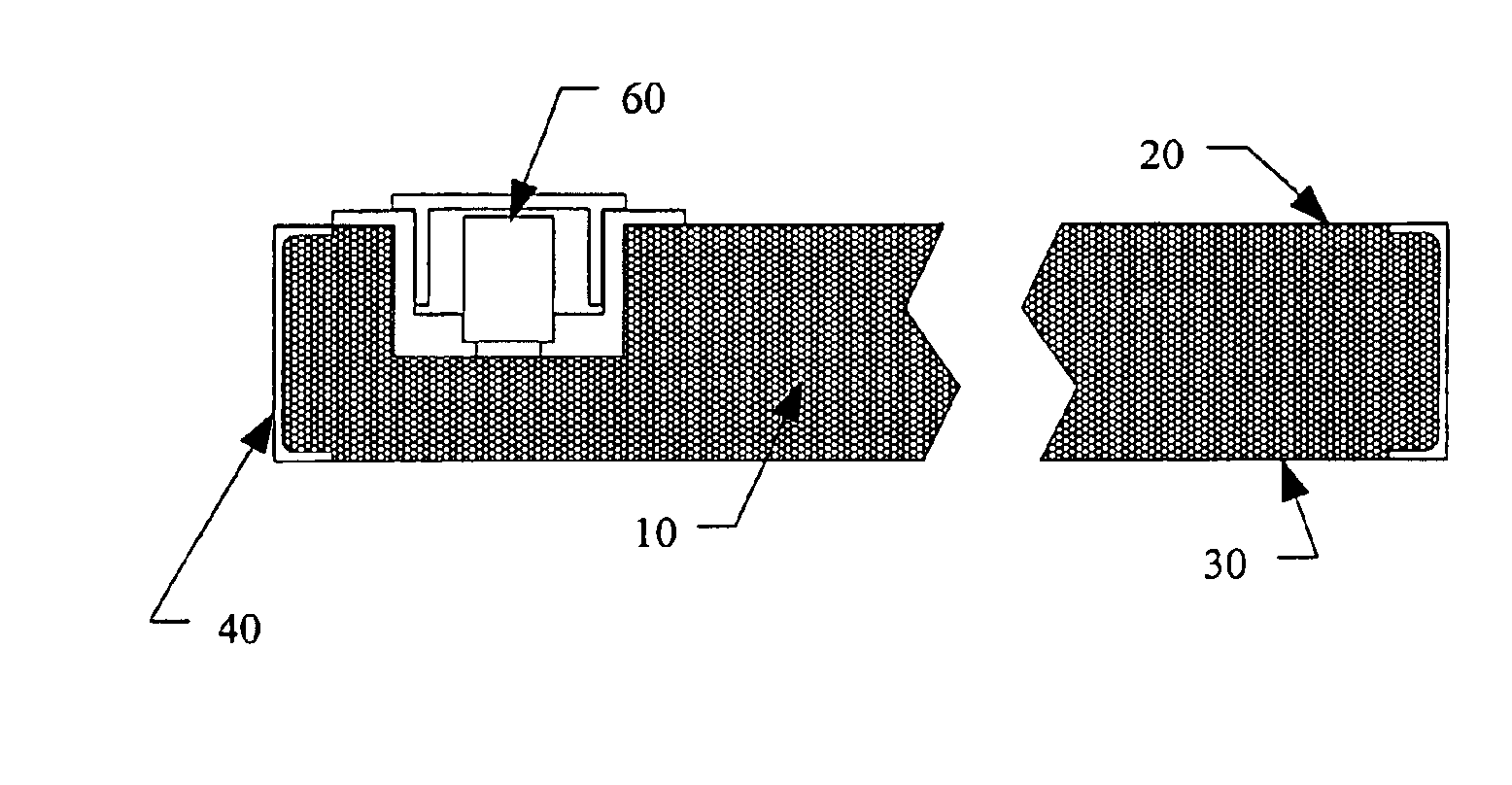

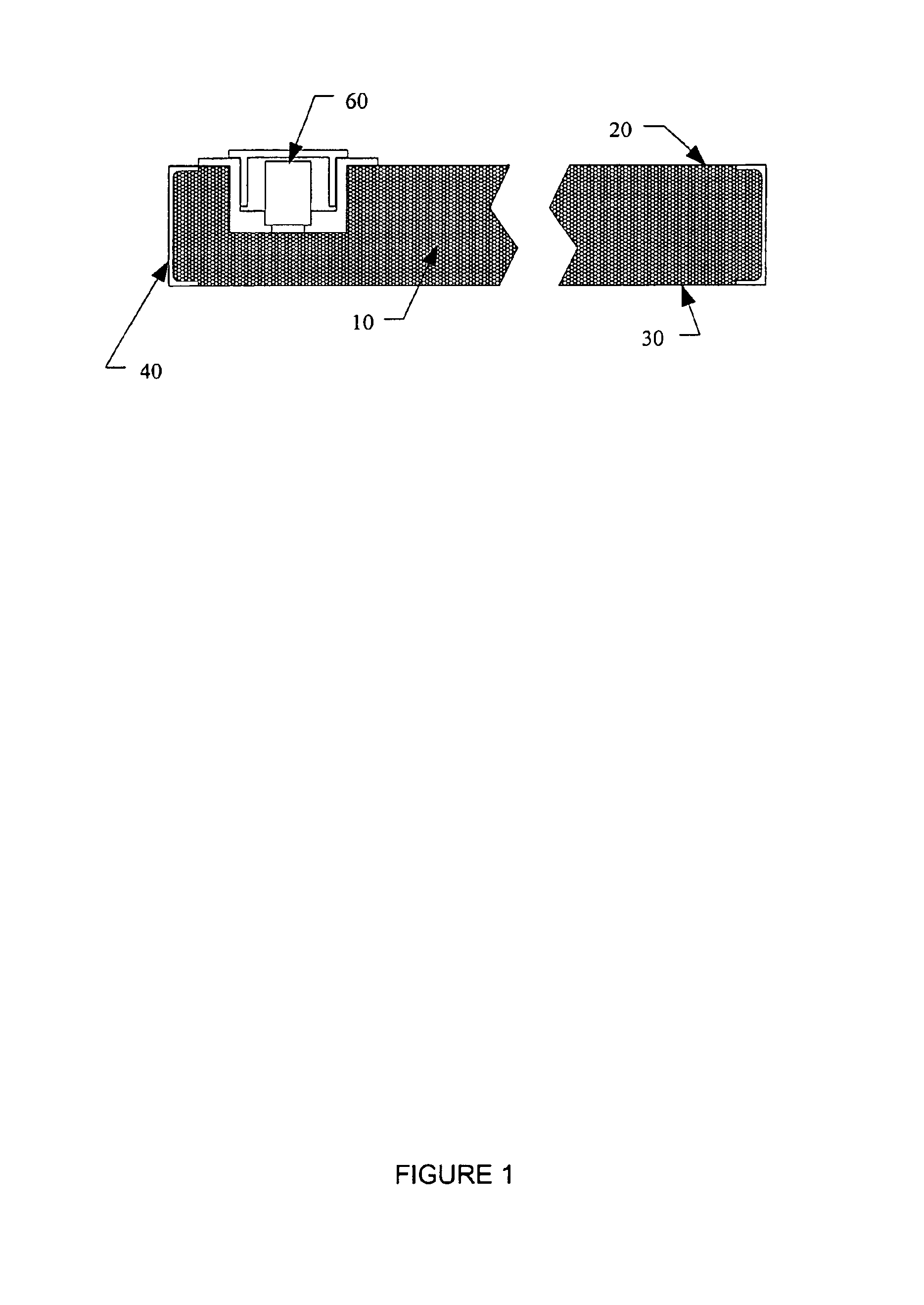

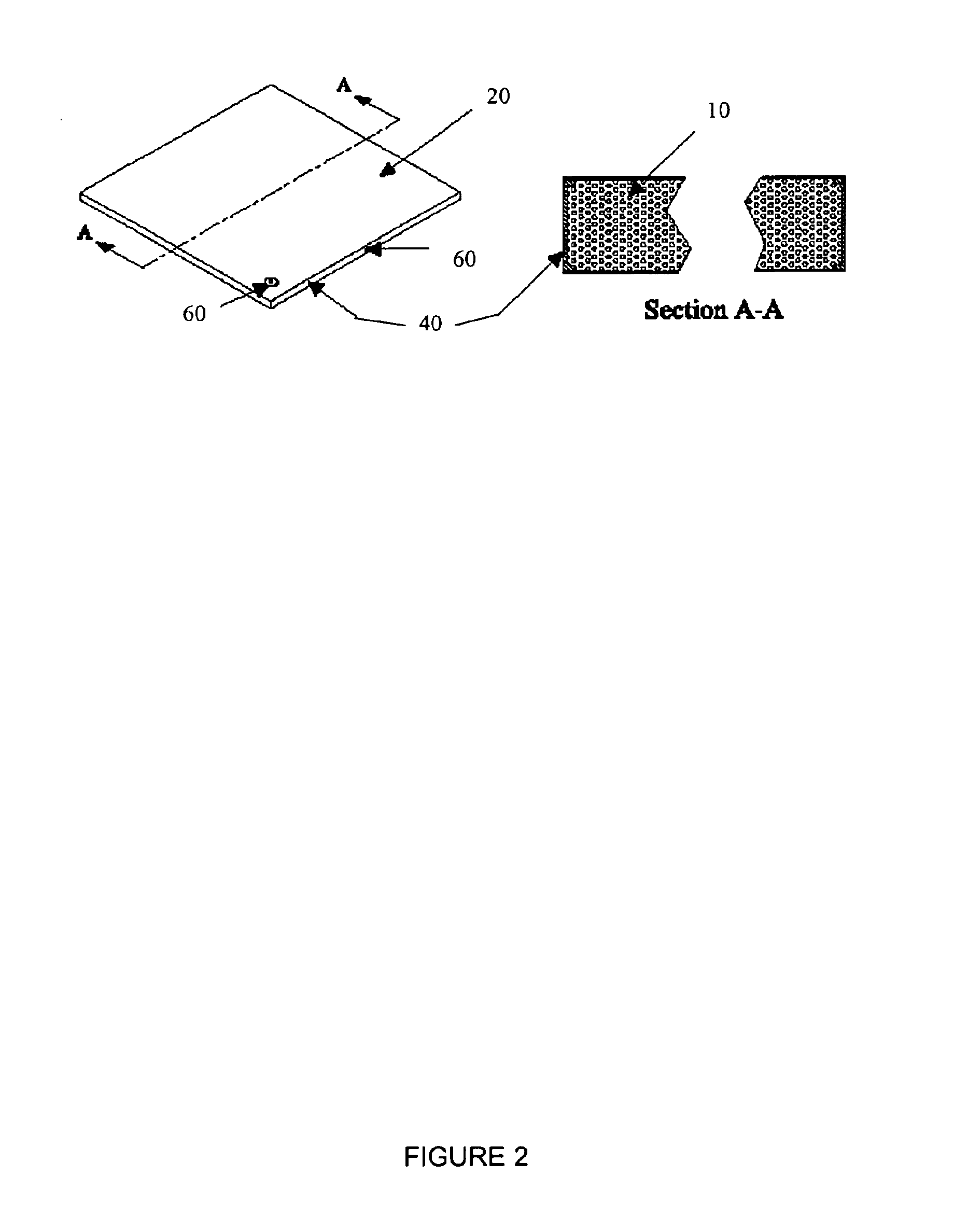

Microsphere insulation systems

InactiveUS6858280B2Reduce the impactIncreases insulation valueLayered productsContainer filling methodsMicrosphereEngineering

A new insulation system is provided that contains microspheres. This insulation system can be used to provide insulated panels and clamshells, and to insulate annular spaces around objects used to transfer, store, or transport cryogens and other temperature-sensitive materials. This insulation system provides better performance with reduced maintenance than current insulation systems.

Owner:TECH APPL

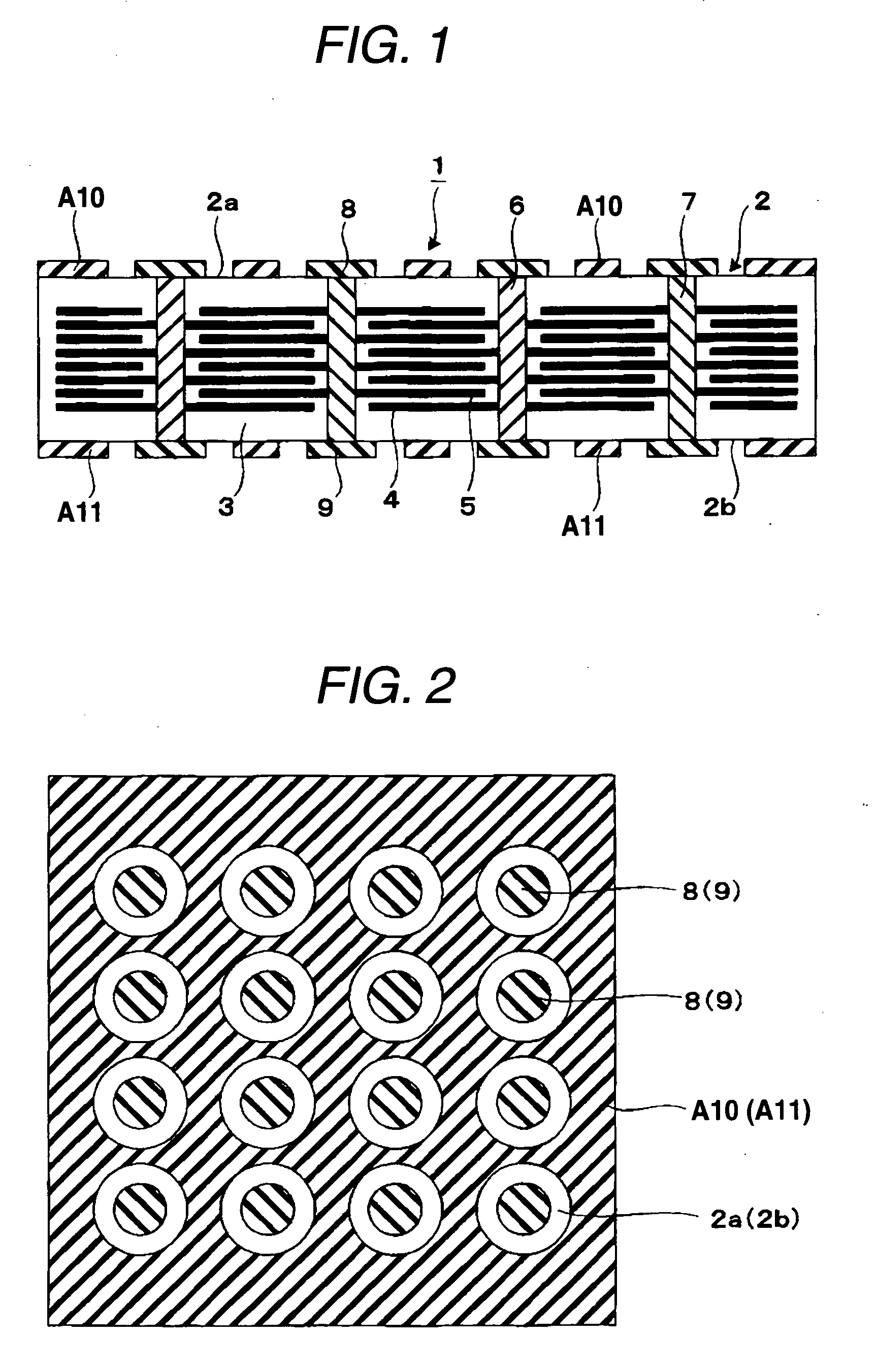

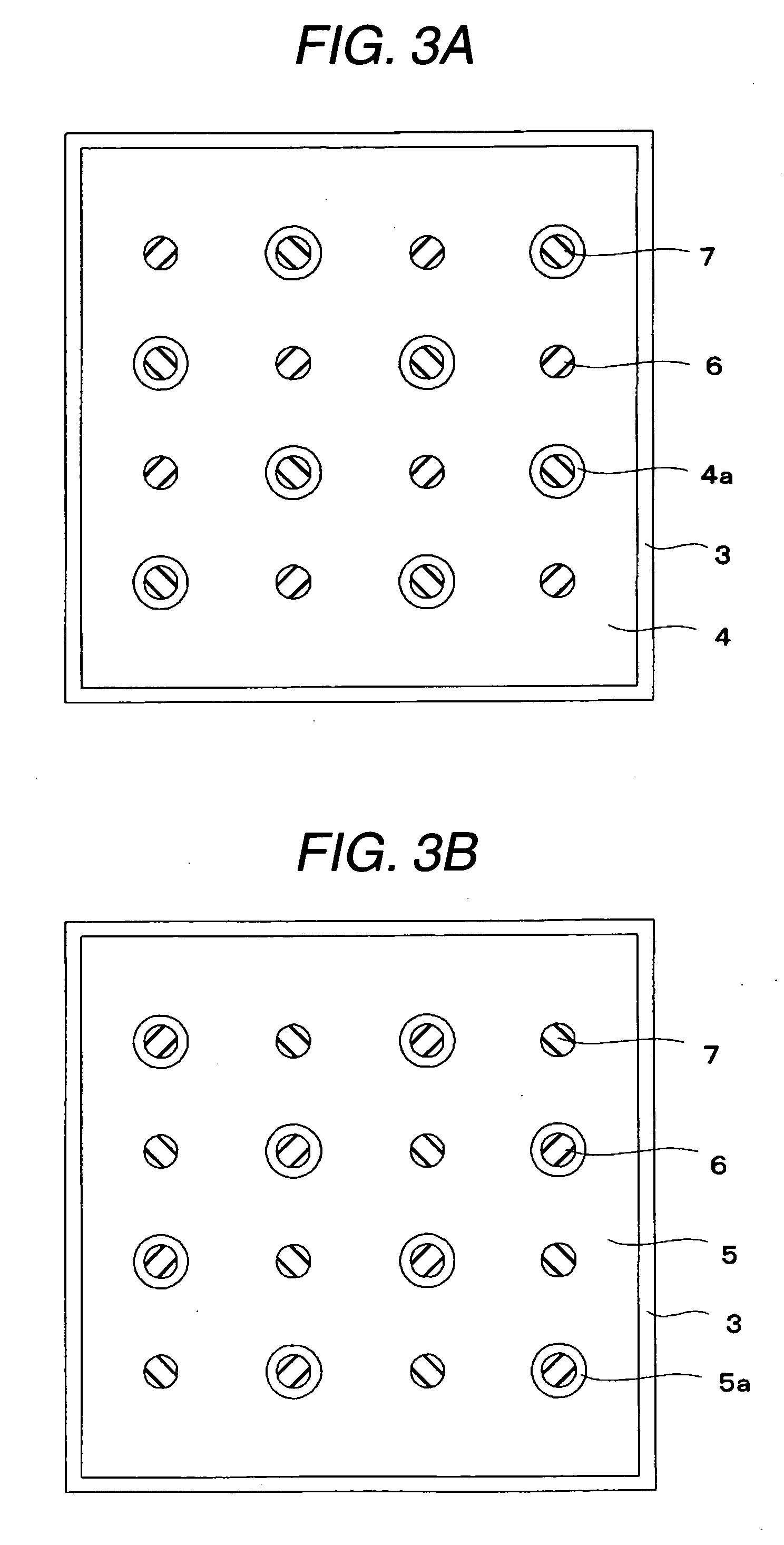

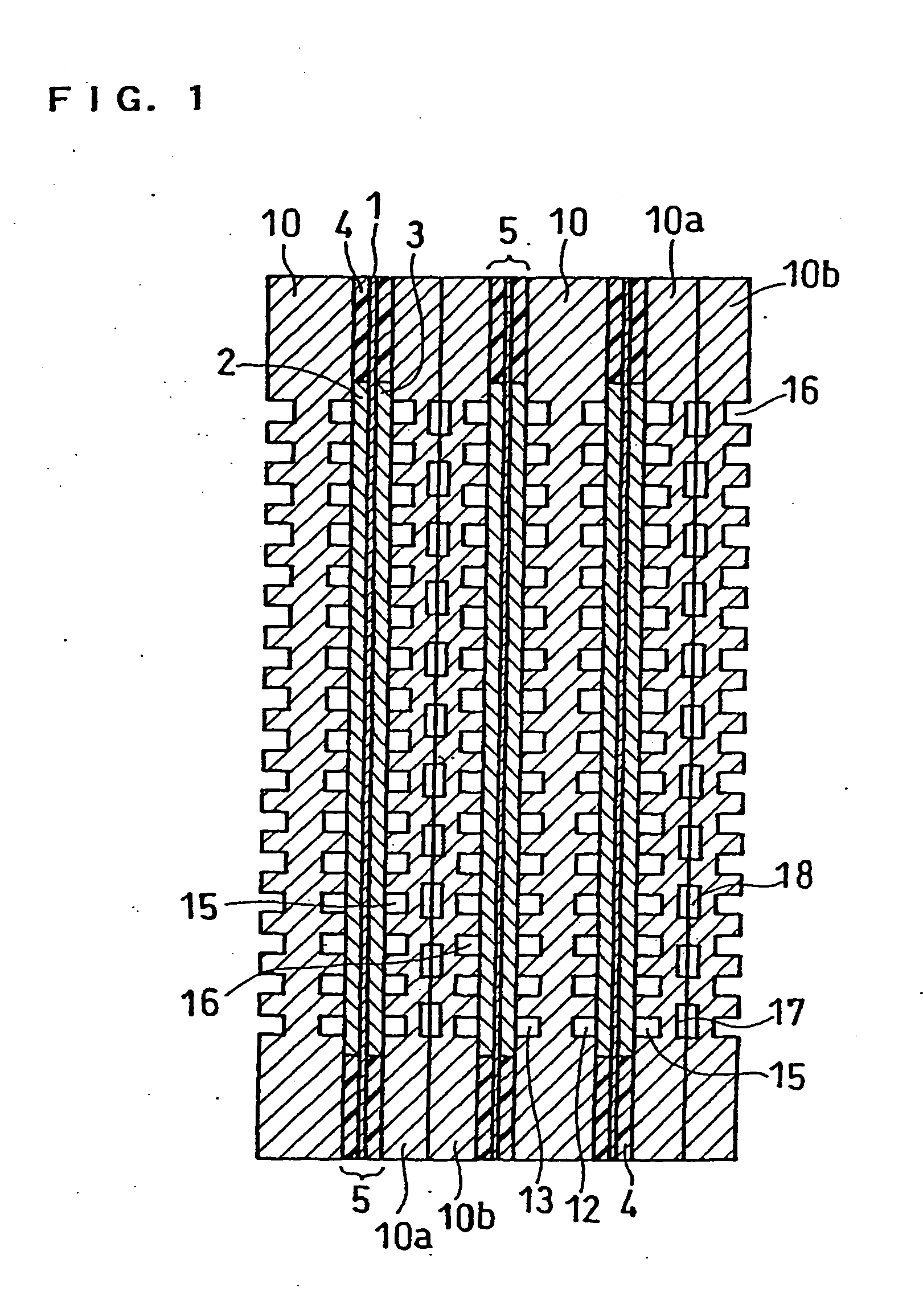

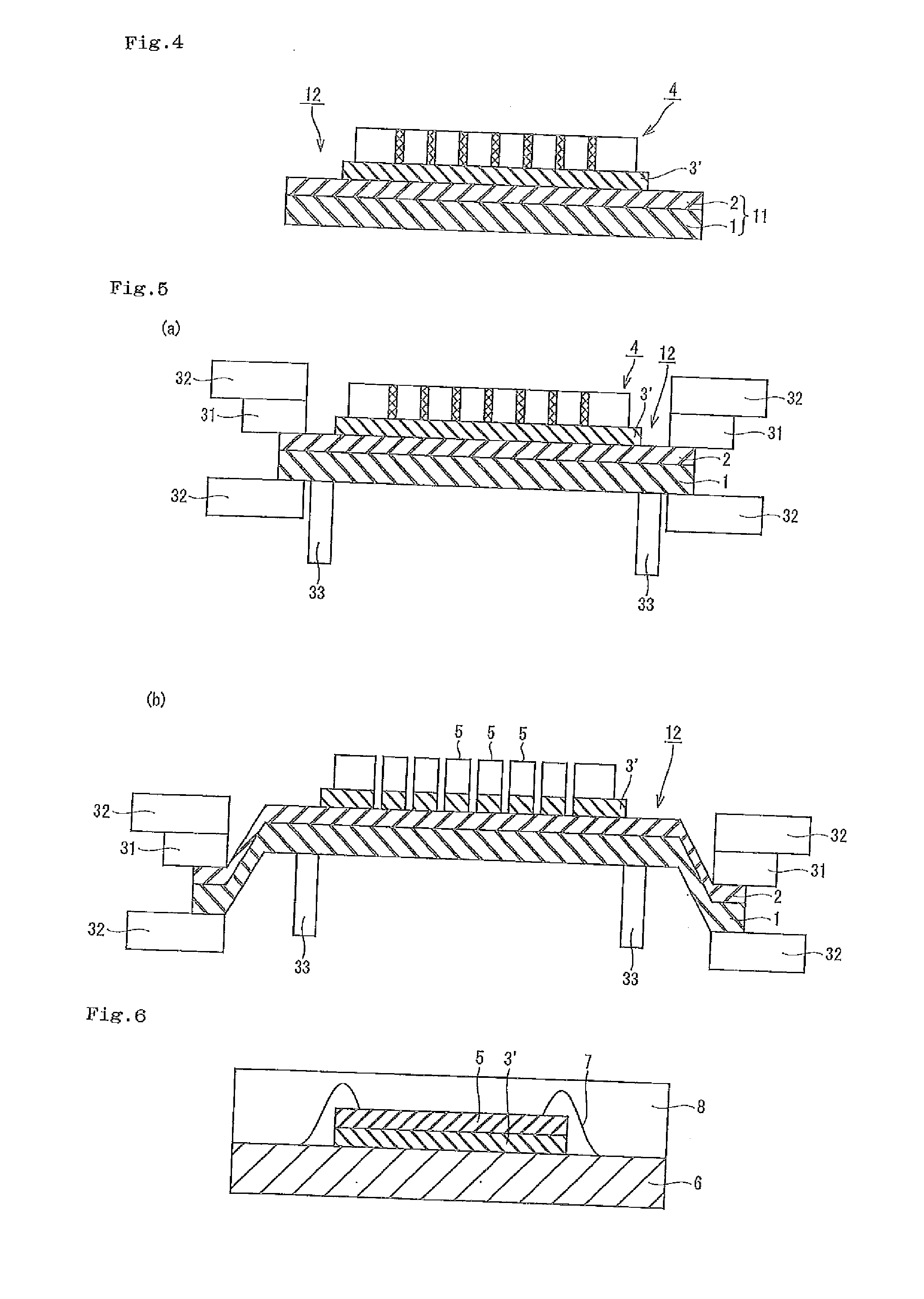

Capacitor for incorporation in wiring board, wiring board, method of manufacturing wiring board, and ceramic chip for embedment

InactiveUS20070030628A1High bonding strengthImprove reliabilitySemiconductor/solid-state device detailsSolid-state devicesDielectric layerCapacitor

A capacitor comprising: a capacitor body including a plurality of laminated dielectric layers, a plurality of inner electrode layers which are respectively disposed between mutually adjacent ones of the dielectric layers, a first main surface located in a laminated direction of the dielectric layers, and a second main surface opposite to the first main surface; a first outer electrode formed on the first main surface of the capacitor body and electrically connected to the inner electrode layers; a second outer electrode formed on the second main surface of the capacitor body and electrically connected to the inner electrode layers; a first dummy electrode formed on the first main surface of the capacitor body; and a second dummy electrode formed on the second main surface of the capacitor body.

Owner:NGK SPARK PLUG CO LTD

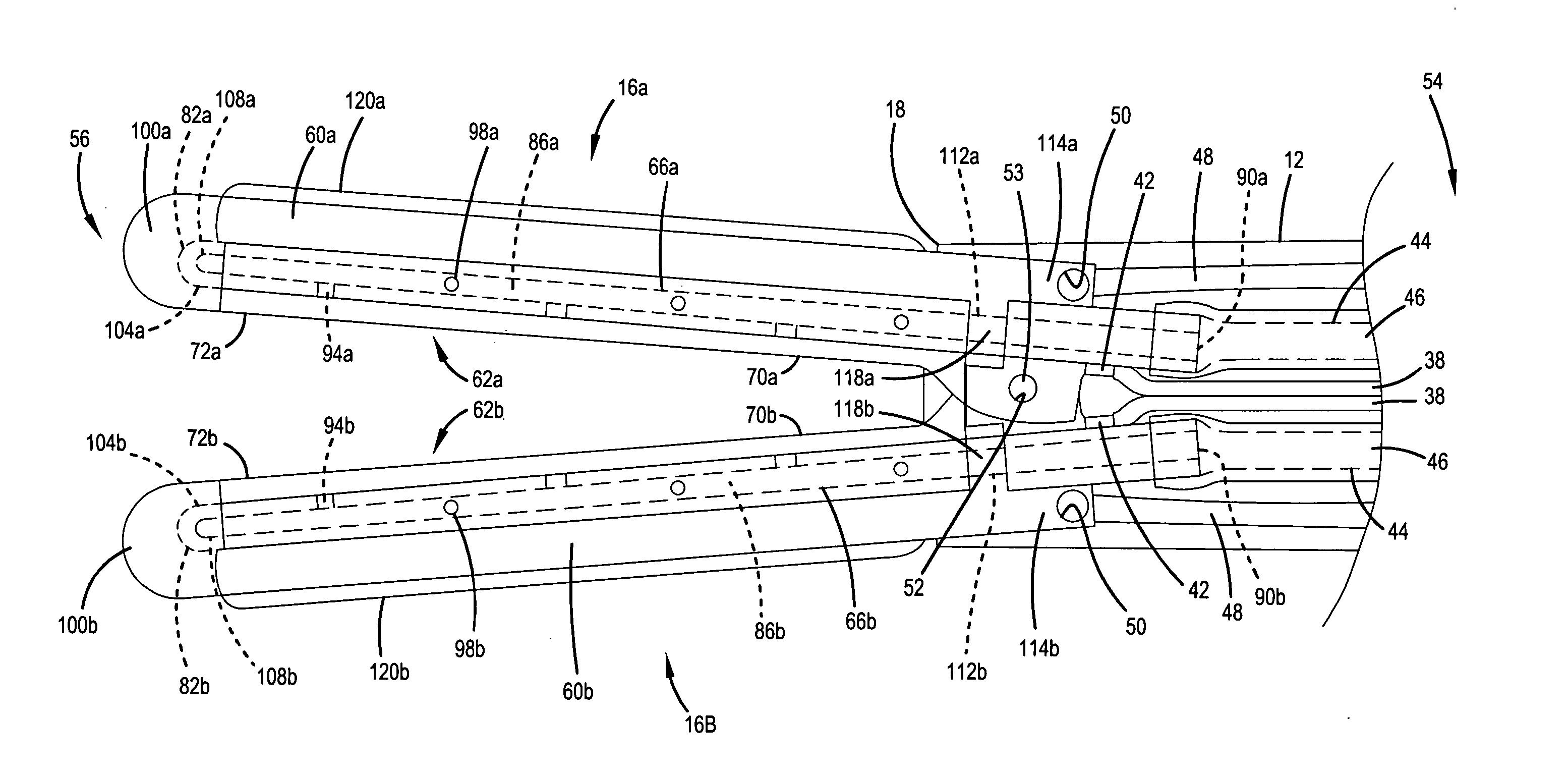

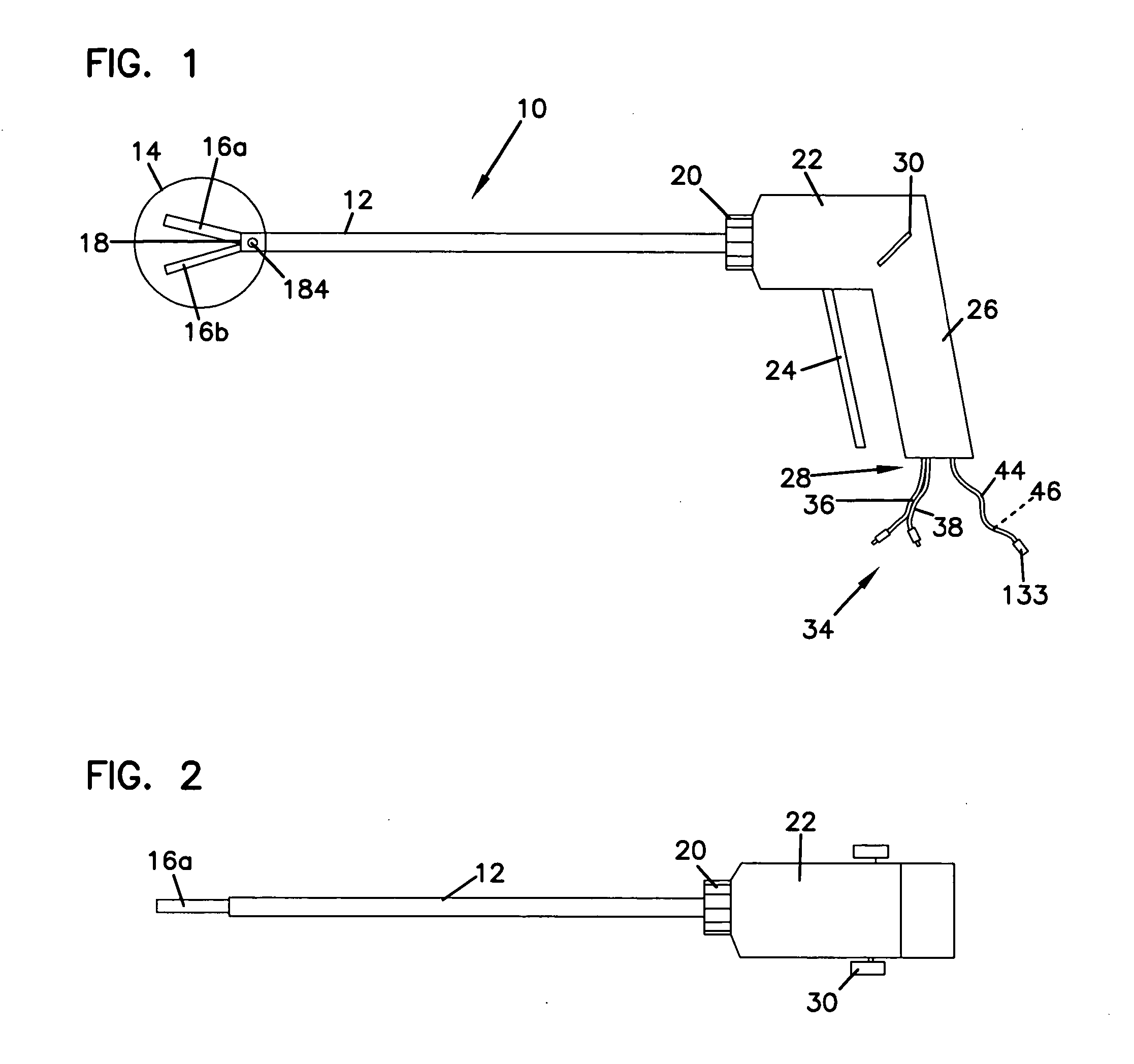

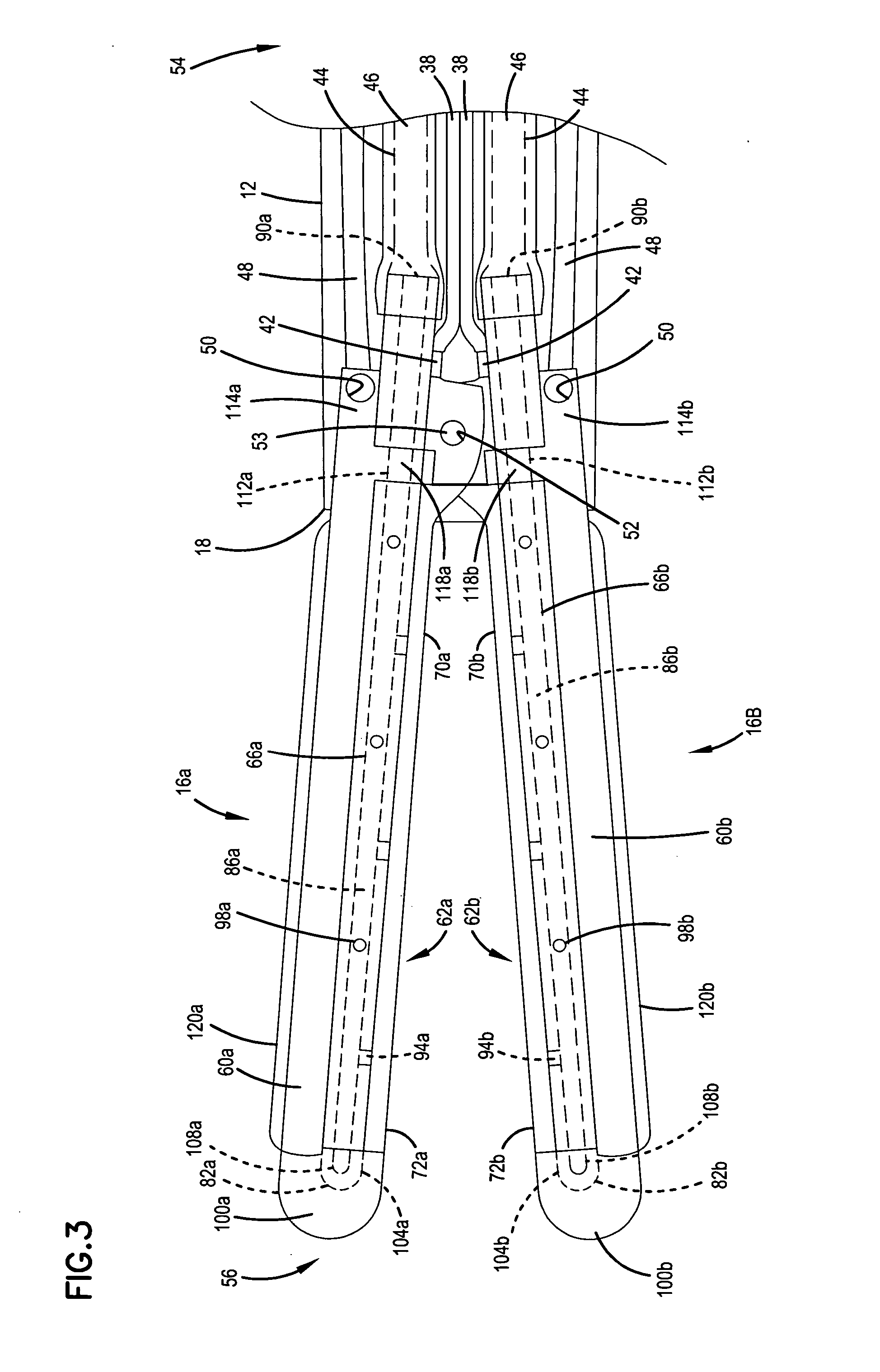

Fluid-assisted medical devices, systems and methods

Surgical devices, systems and methods for treating tissue. An exemplary surgical device comprises a tip portion including first and second jaws each having a tissue grasping surface, at least one of the jaws being movable toward the other jaw. The tissue grasping surface of each jaw has includes an electrically insulative surface. The device also includes first and second electrodes connectable to different terminals of an RF generator to generate electrical current flow therebetween, with each of the electrodes having an electrode surface. One of the electrode surfaces is located on one of the jaws separated from one edge of the tissue grasping surface, and the other of the electrode surfaces is located on one or the other of the jaws separated from the other edge of the tissue grasping surface. The device also includes at least one fluid passage being connectable to a fluid source.

Owner:MEDTRONIC ADVANCED ENERGY

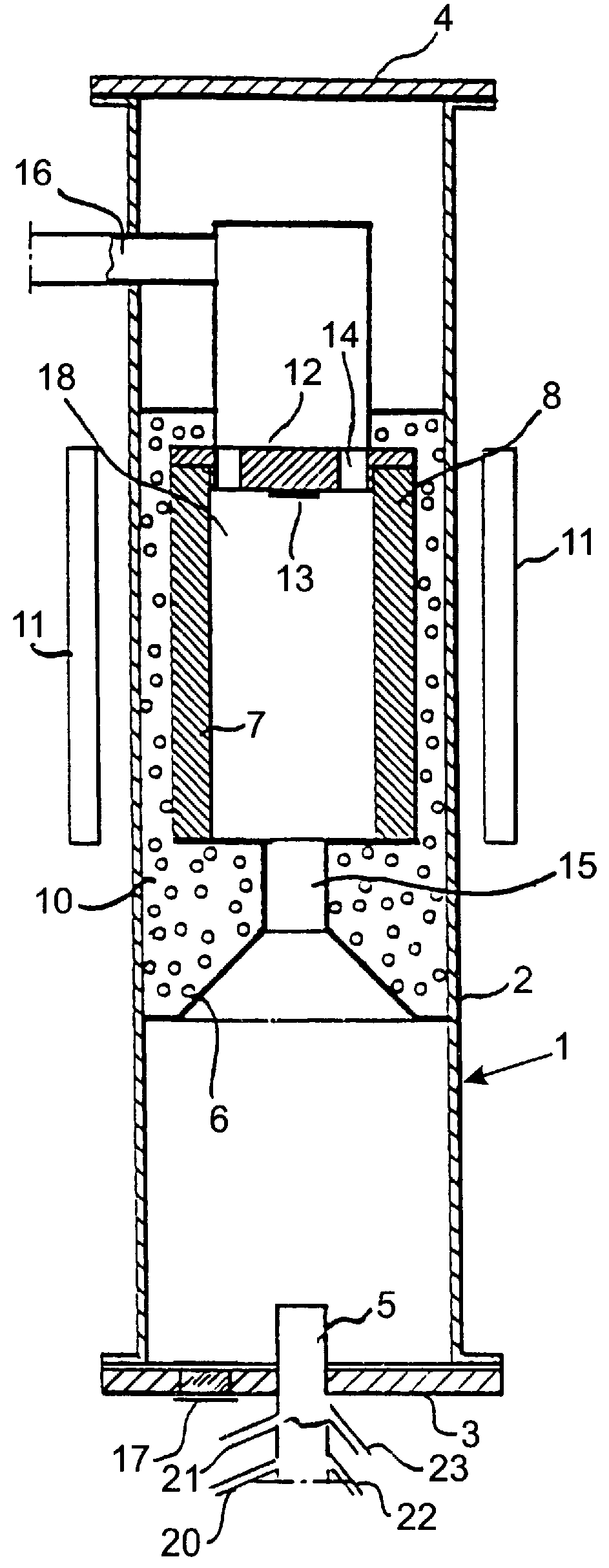

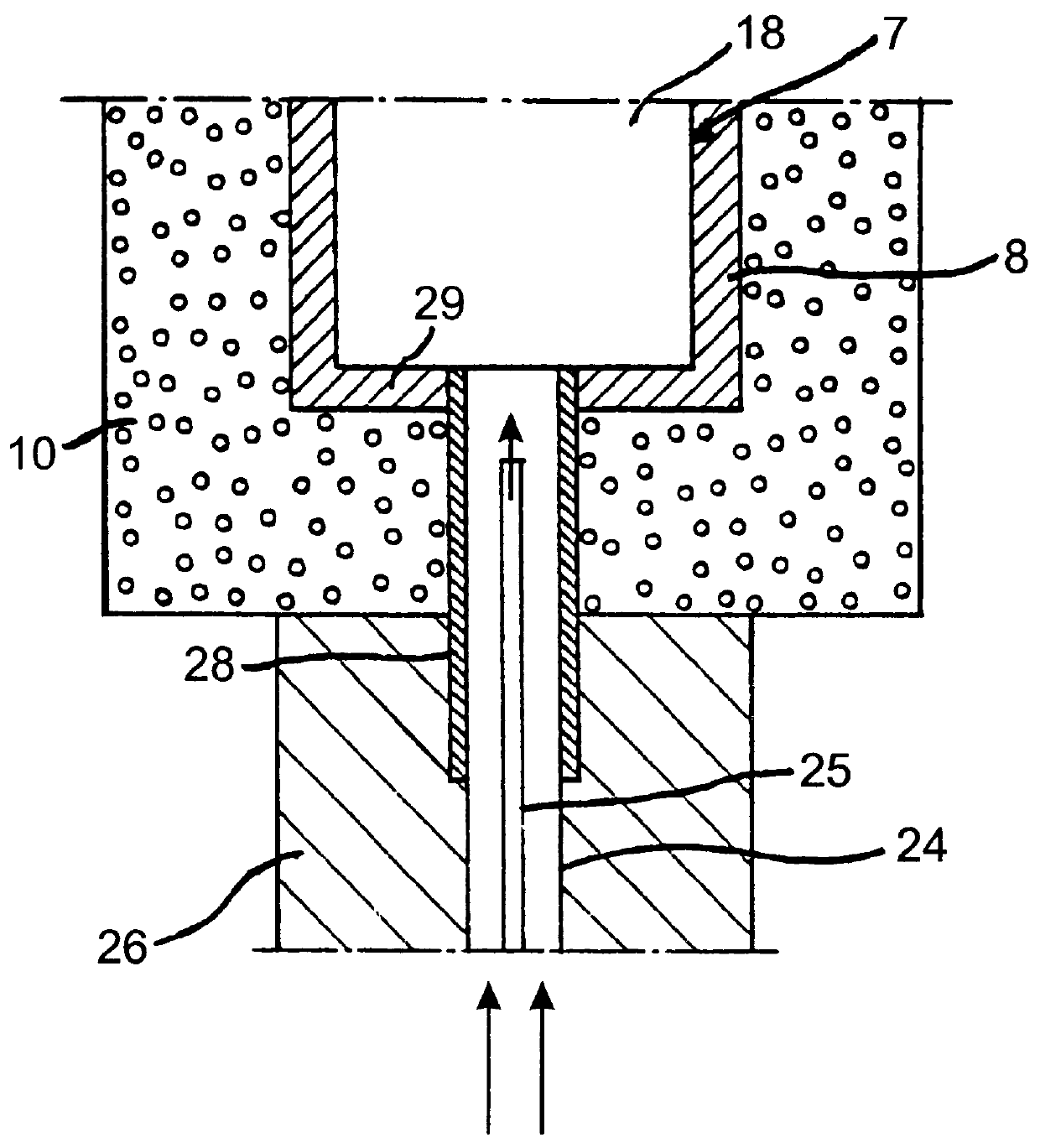

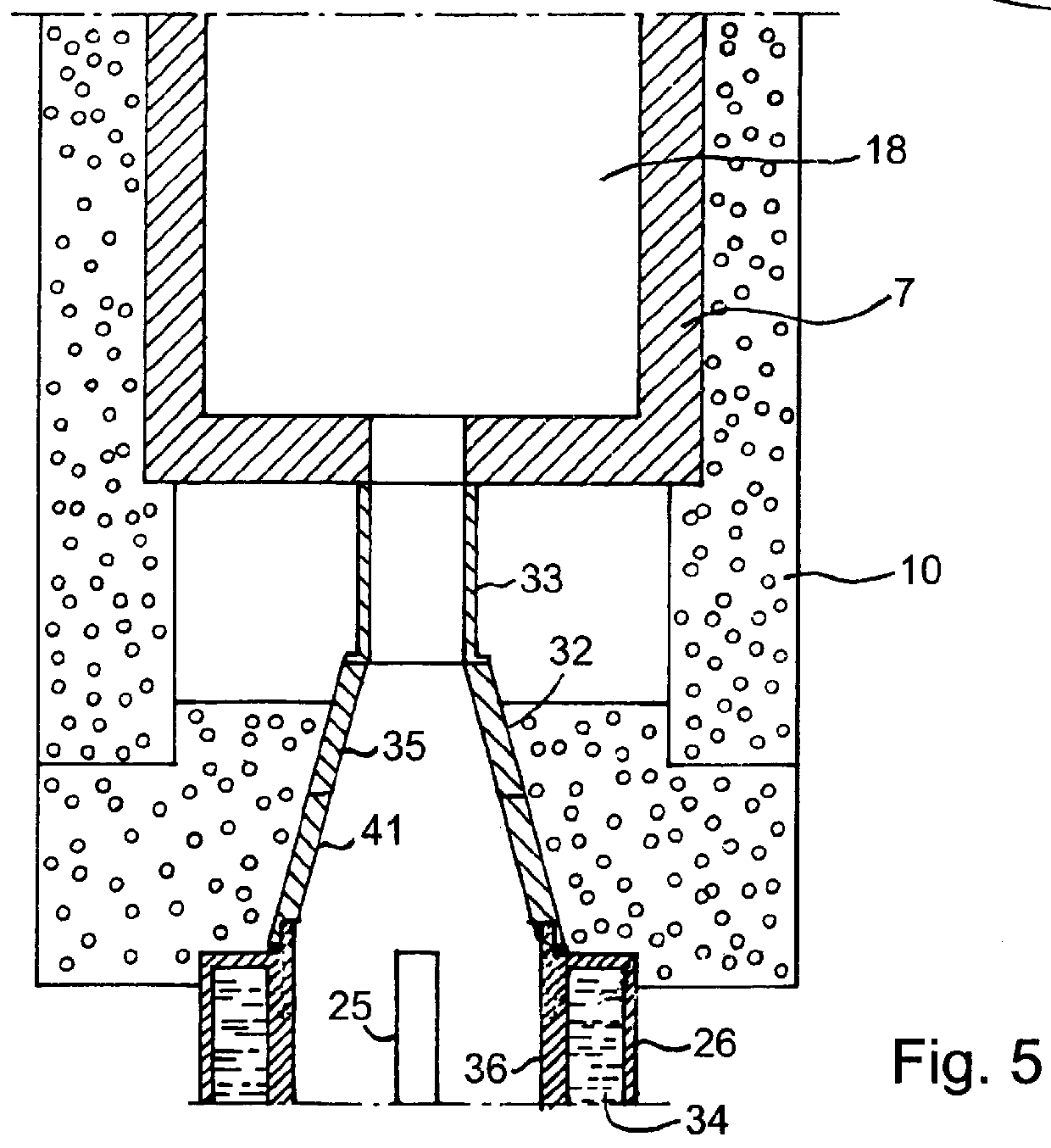

Device for epitaxially growing objects and method for such a growth

InactiveUS6039812AVelocity increasesImprove economyPolycrystalline material growthFrom chemically reactive gasesGas phaseReactive gas

A device for epitaxially growing objects of for instance SiC by Chemical Vapor Deposition on a substrate has a first conduit (24) arranged to conduct substantially only a carrier gas to a room (18) receiving the substrate and a second conduit (25) received in the first conduit, having a smaller cross-section than the first conduit and extending in the longitudinal direction of the first conduit with a circumferential space separating it from inner walls of the first conduit. The second conduit is adapted to conduct substantially the entire flow of reactive gases and it ends as seen in the direction of the flows, and emerges into the first conduit at a distance from said room.

Owner:NORSTEL

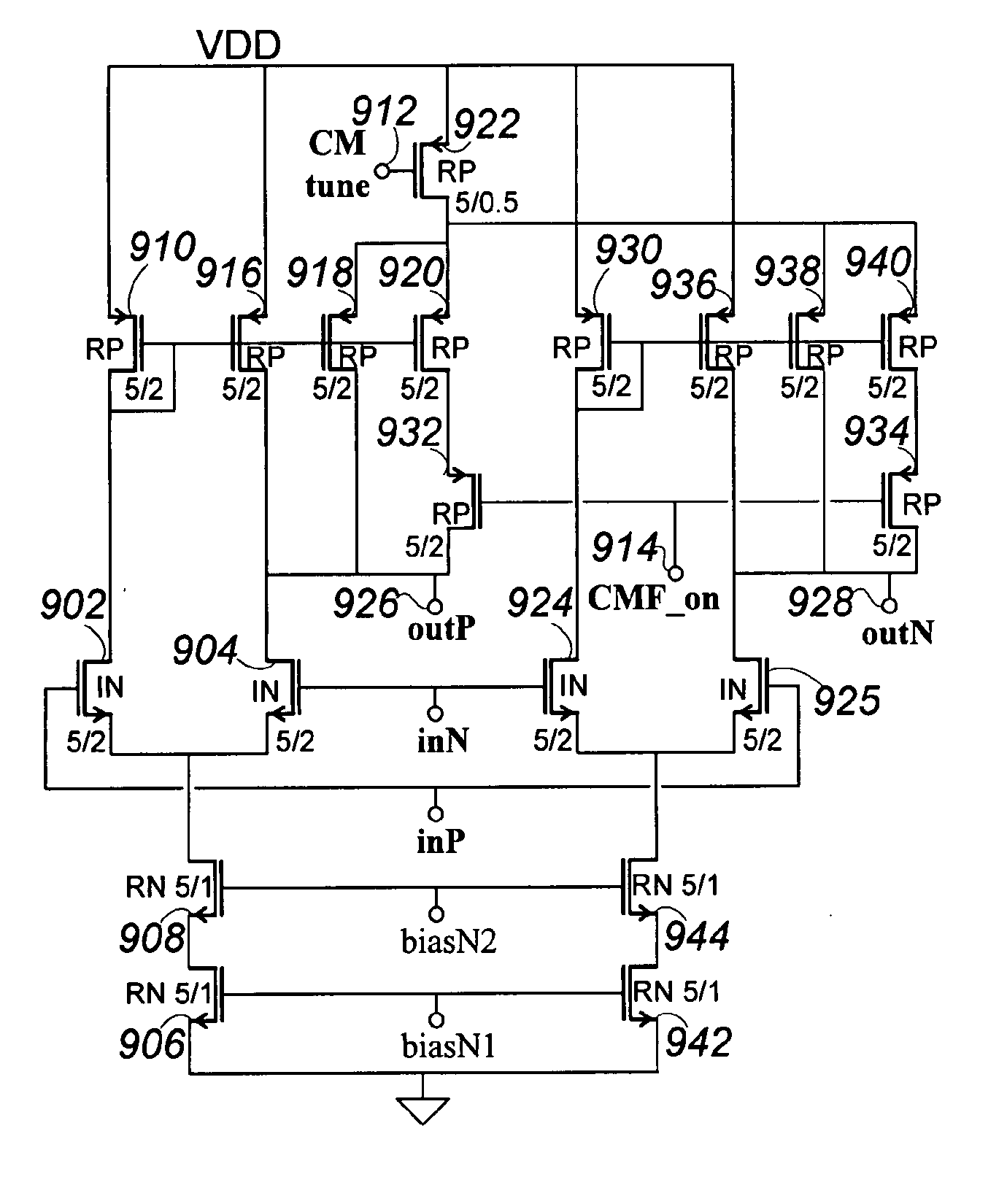

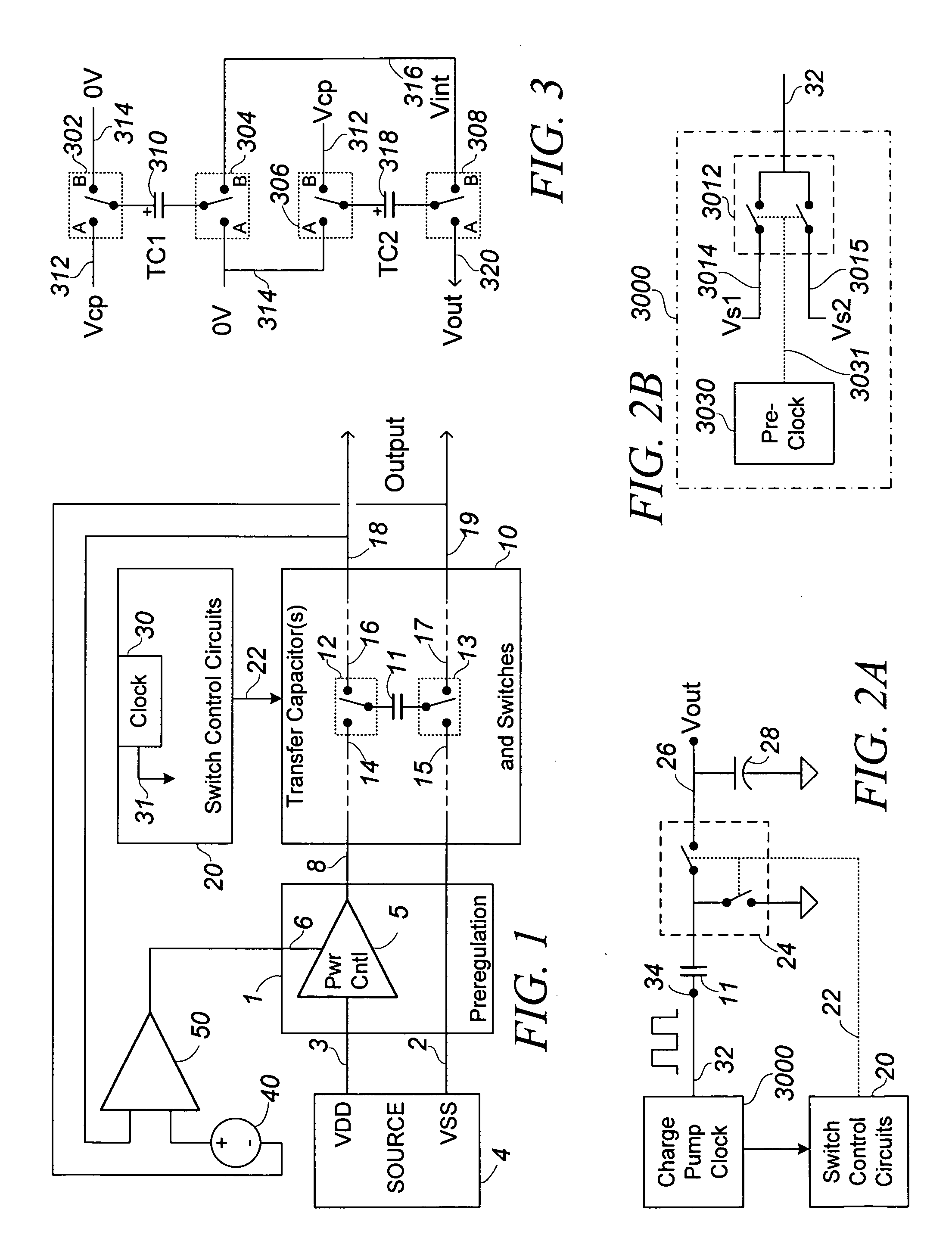

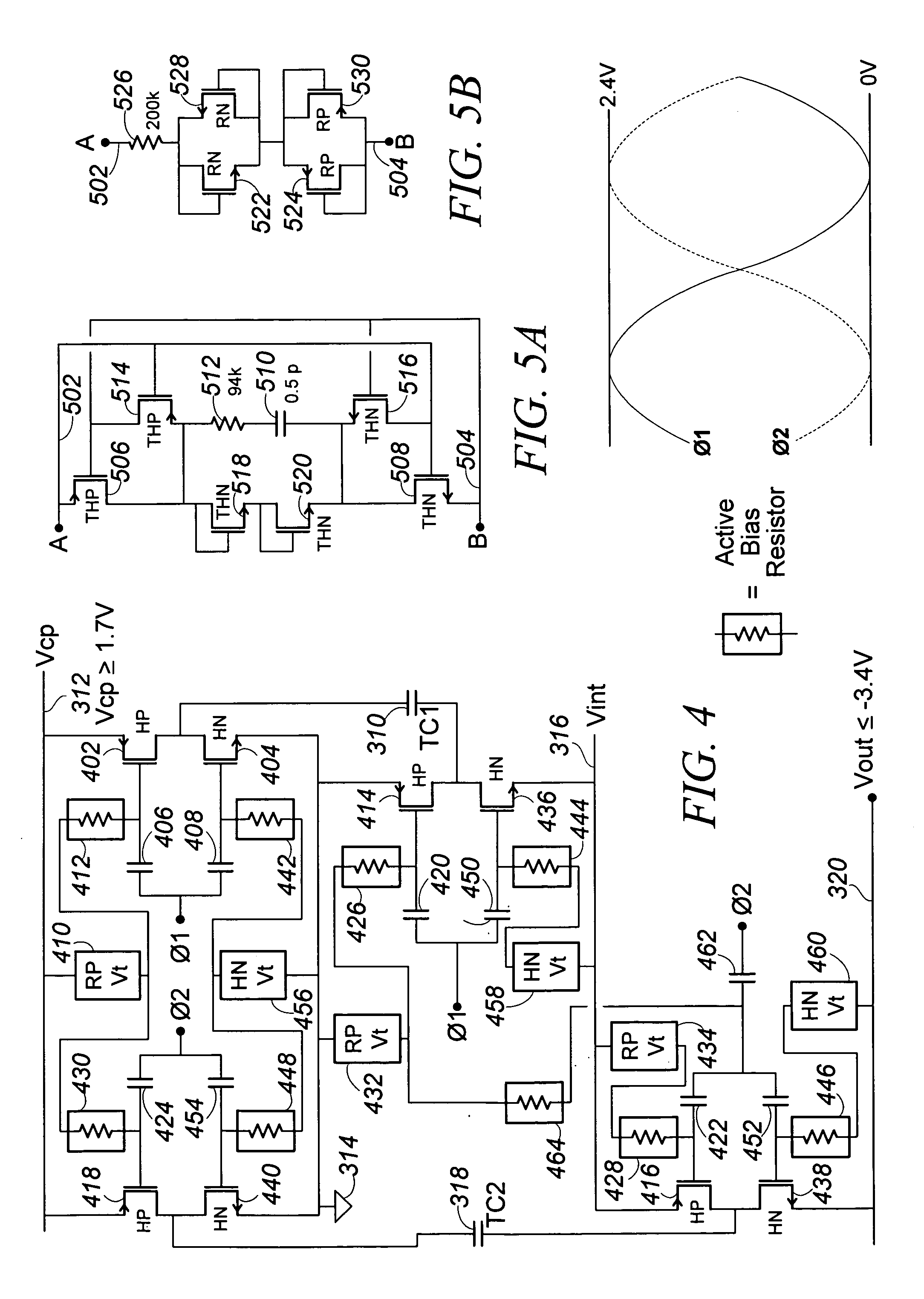

Low-Noise High Efficiency Bias Generation Circuits and Method

ActiveUS20110156819A1Reduce voltageAvoid problemsAmplifier modifications to reduce noise influenceActive element networkLow noiseCapacitance

A bias generation method or apparatus defined by any one or any practical combination of numerous features that contribute to low noise and / or high efficiency biasing, including: having a charge pump control clock output with a waveform having limited harmonic content or distortion compared to a sine wave; having a ring oscillator to generating a charge pump clock that includes inverters current limited by cascode devices and achieves substantially rail-to-rail output amplitude; having a differential ring oscillator with optional startup and / or phase locking features to produce two phase outputs suitably matched and in adequate phase opposition; having a ring oscillator of less than five stages generating a charge pump clock; capacitively coupling the clock output(s) to some or all of the charge transfer capacitor switches; biasing an FET, which is capacitively coupled to a drive signal, to a bias voltage via an “active bias resistor” circuit that conducts between output terminals only during portions of a waveform appearing between the terminals, and / or wherein the bias voltage is generated by switching a small capacitance at cycles of said waveform. A charge pump for the bias generation may include a regulating feed back loop including an OTA that is also suitable for other uses, the OTA having a ratio-control input that controls a current mirror ratio in a differential amplifier over a continuous range, and optionally has differential outputs including an inverting output produced by a second differential amplifier that optionally includes a variable ratio current mirror controlled by the same ratio-control input. The ratio-control input may therefore control a common mode voltage of the differential outputs of the OTA. A control loop around the OTA may be configured to control the ratio of one or more variable ratio current mirrors, which may particularly control the output common mode voltage, and may control it such that the inverting output level tracks the non-inverting output level to cause the amplifier to function as a high-gain integrator.

Owner:PSEMI CORP

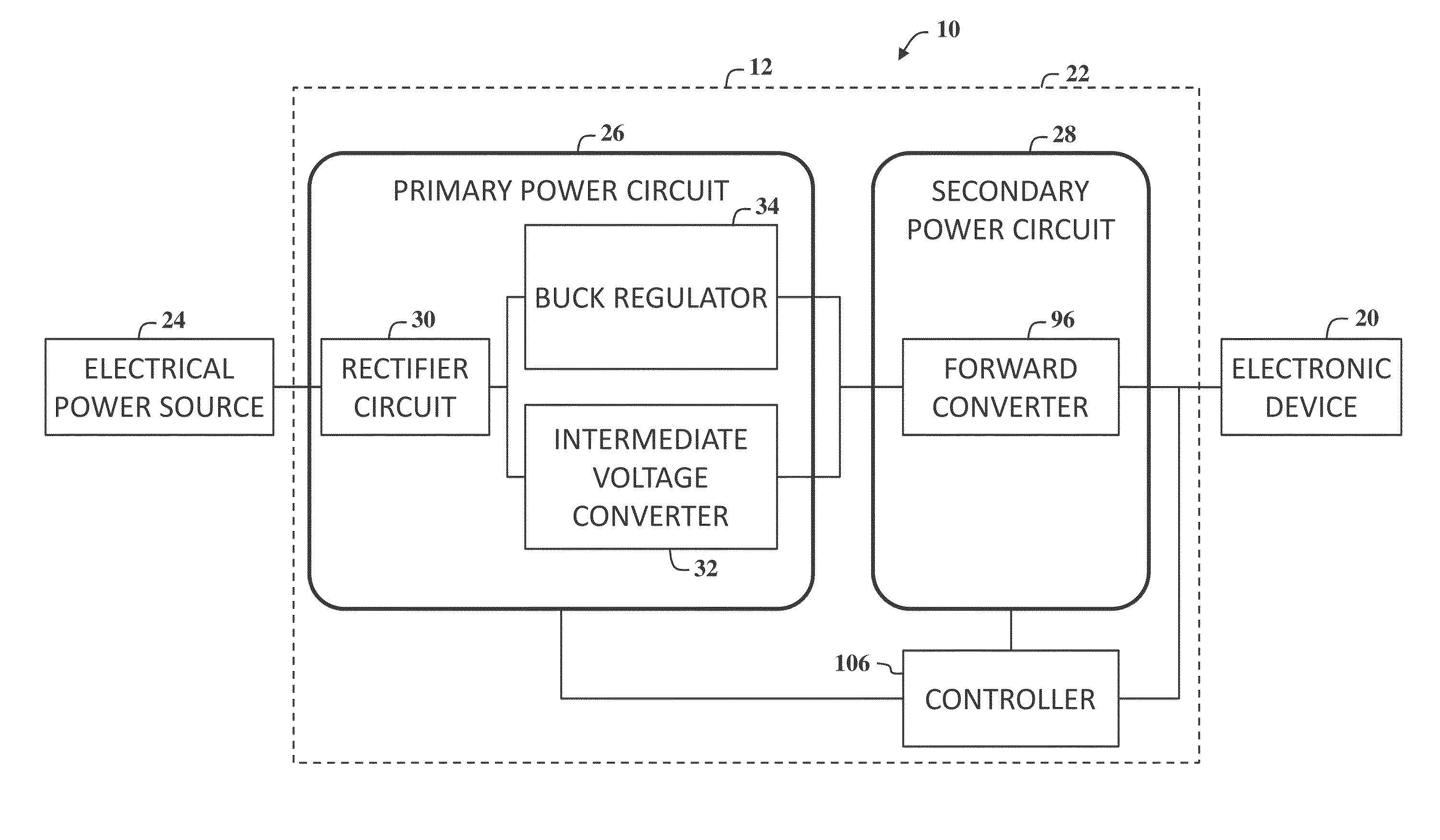

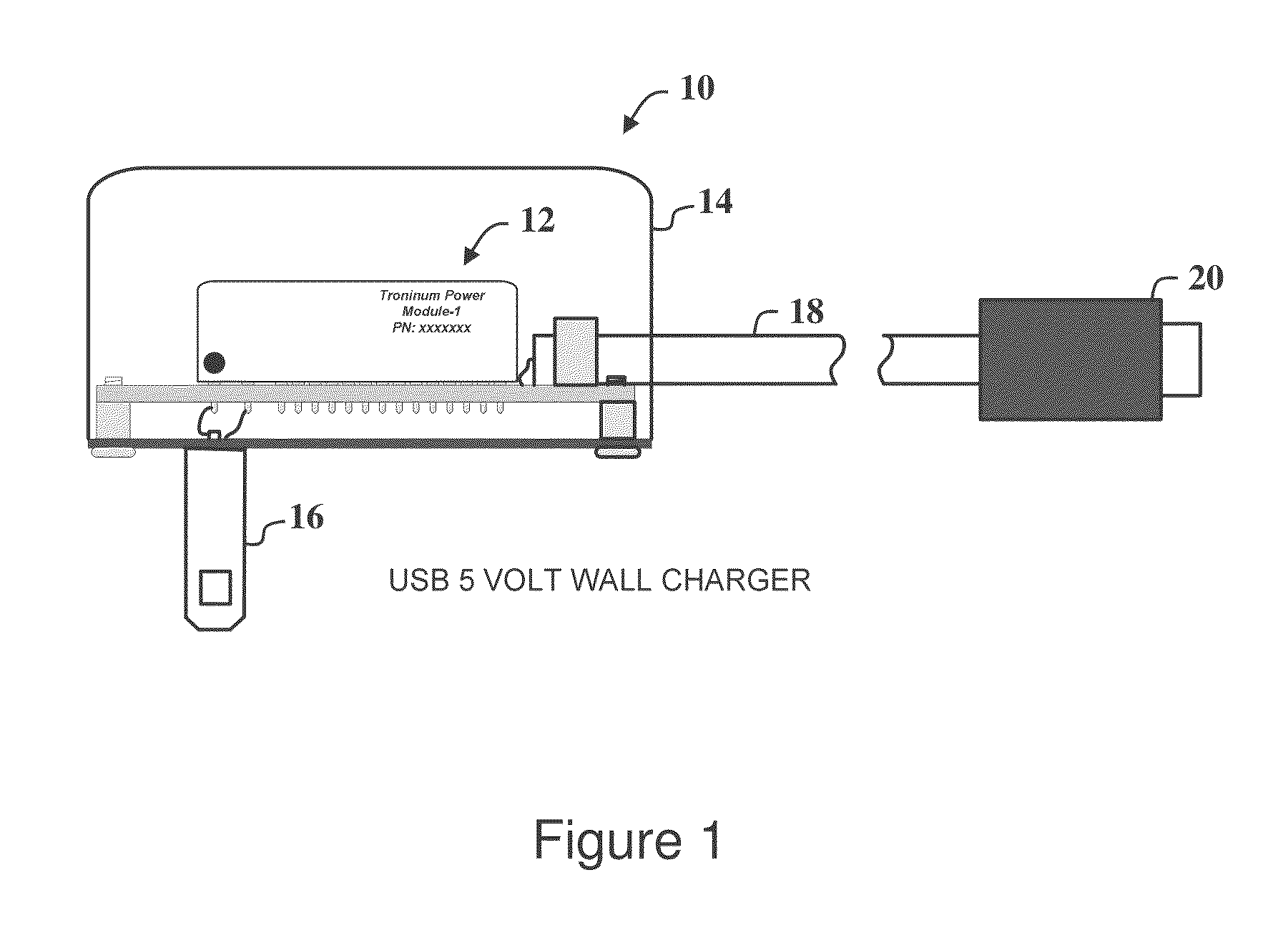

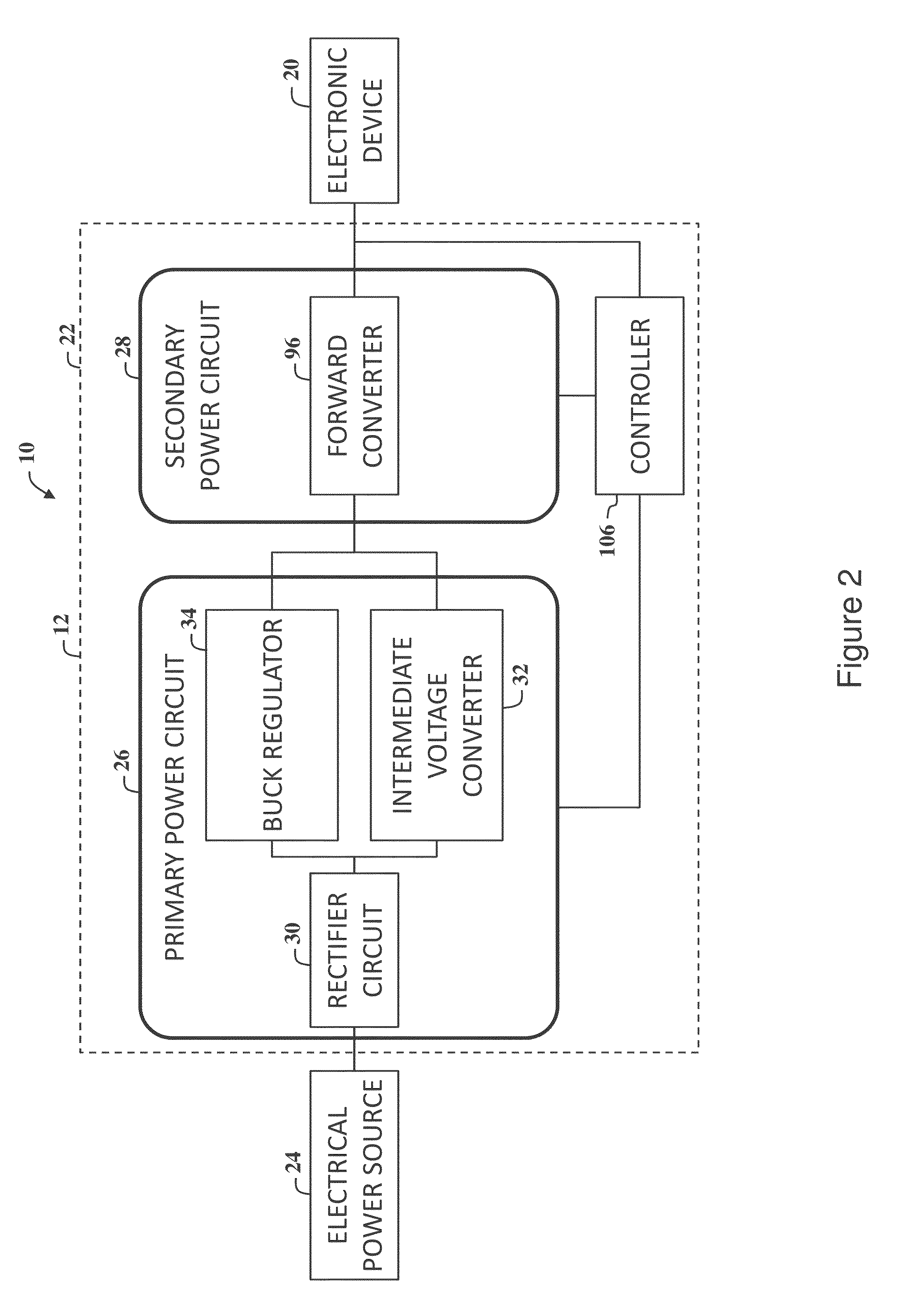

Electrical circuit for delivering power to consumer electronic devices

ActiveUS20160116925A1Lower resistanceReduce conductionAc-dc conversion without reversalBoards/switchyards circuit arrangementsData centerEngineering

An electrical circuit for providing electrical power for use in powering electronic devices, such as monitors, televisions, white goods, data centers, and telecom circuit boards, is described herein. The electrical circuit includes a voltage reduction circuit cell that includes a first capacitor, a second capacitor, a switching circuit, and a hold capacitor. The switching circuit includes a plurality of switching devices that are coupled to the first and the second capacitors for delivering power from an input terminal to an output terminal. The plurality of switching devices includes at least two switching devices that are coupled to ground. The voltage reduction circuit cell also includes a controller for operating the switching circuit in a plurality of operational modes to deliver an output power signal at a desired voltage level.

Owner:SMART PRONG TECH INC

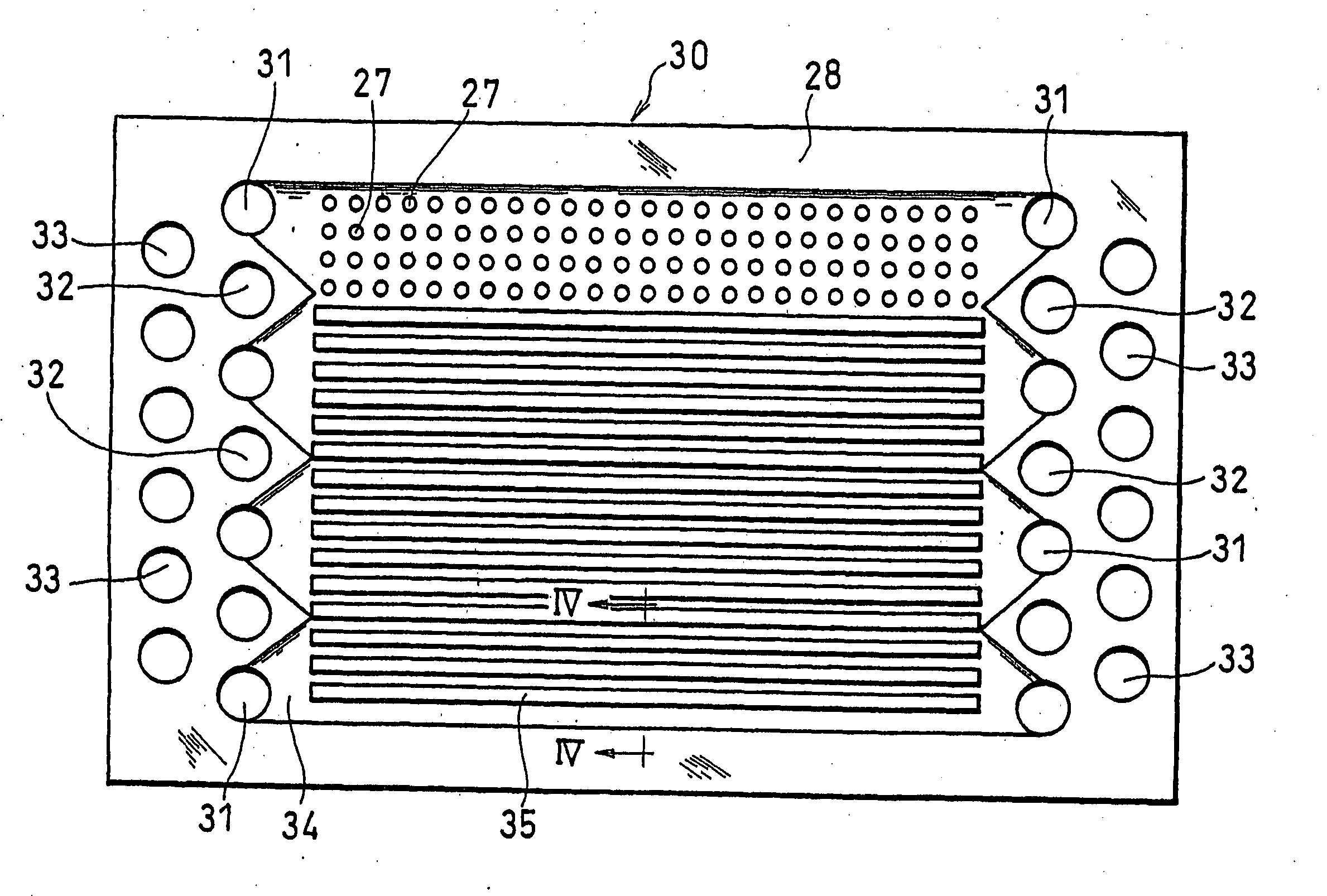

Polymer electrolyte fuel cell and method of manufacturing the same

InactiveUS20040197633A1Improves product water-removal efficiencyEvenly distributedFuel cell heat exchangeFinal product manufacturePolymer electrolytesFuel cells

The present invention relates to a polymer electrolyte fuel cell comprising: an electrolyte membrane-electrode assembly including an anode, a cathode and a polymer electrolyte membrane interposed therebetween; an anode-side conductive separator plate having a gas flow channel for supplying a fuel gas to the anode; and a cathode-side conductive separator plate having a gas flow channel for supplying an oxidant gas to the cathode. A conductive separator plate made of carbon has poor wettability with water. This has posed the disadvantage that variations in performance are induced by nonuniform gas distribution among cells due to the accumulation of product water or humidifying water in the gas flow channel on the surface of the separator plate. The present invention employs a conductive separator plate comprising a conductive carbon having a hydrophilic functional group, at least in a portion of the gas flow channels, thereby preventing water from accumulating in the gas flow channels.

Owner:PANASONIC CORP

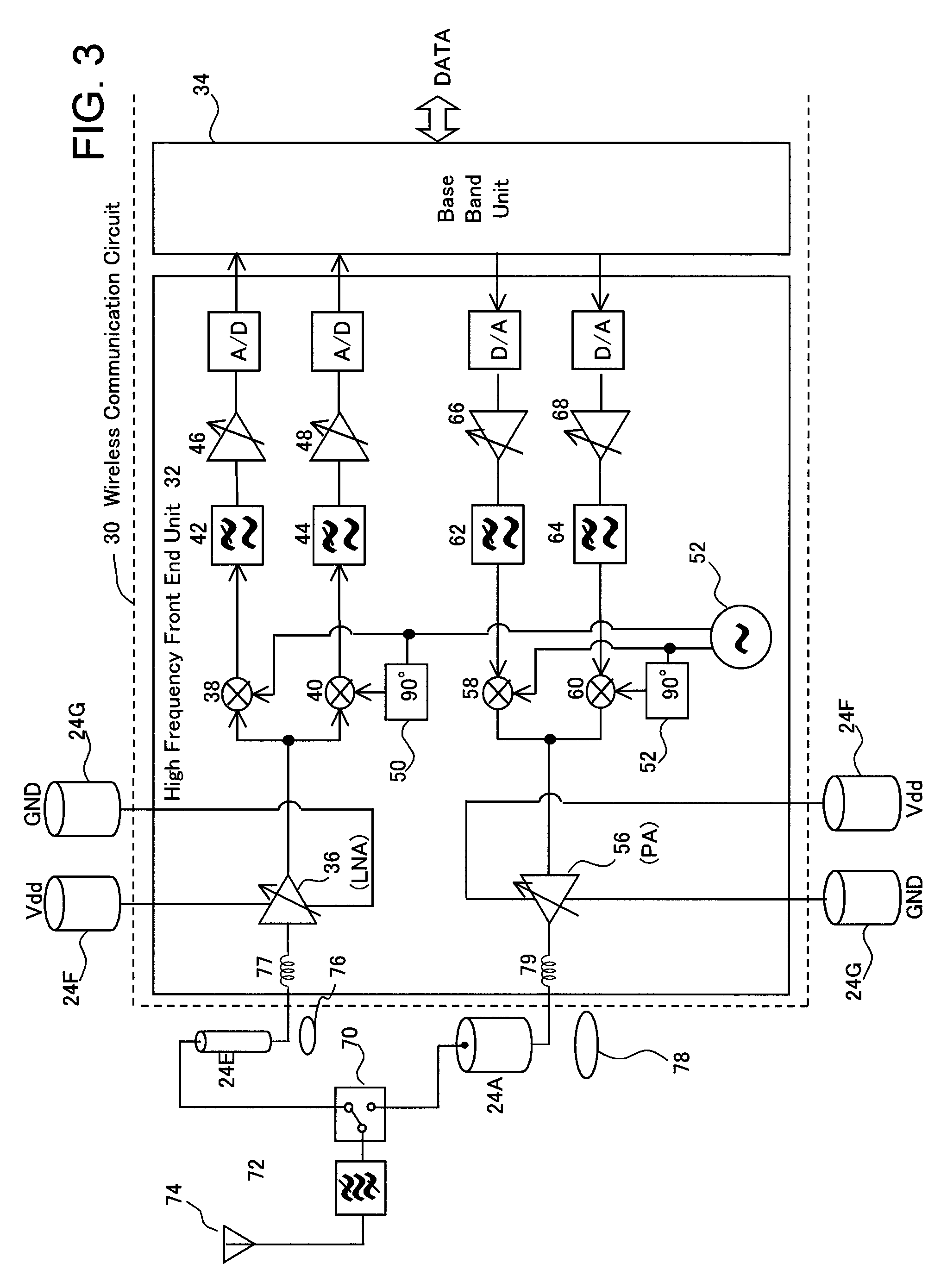

High-frequency device

ActiveUS6998710B2Small sizeImprove featuresSemiconductor/solid-state device detailsSolid-state devicesAudio power amplifierSemiconductor

Owner:FUJITSU LTD

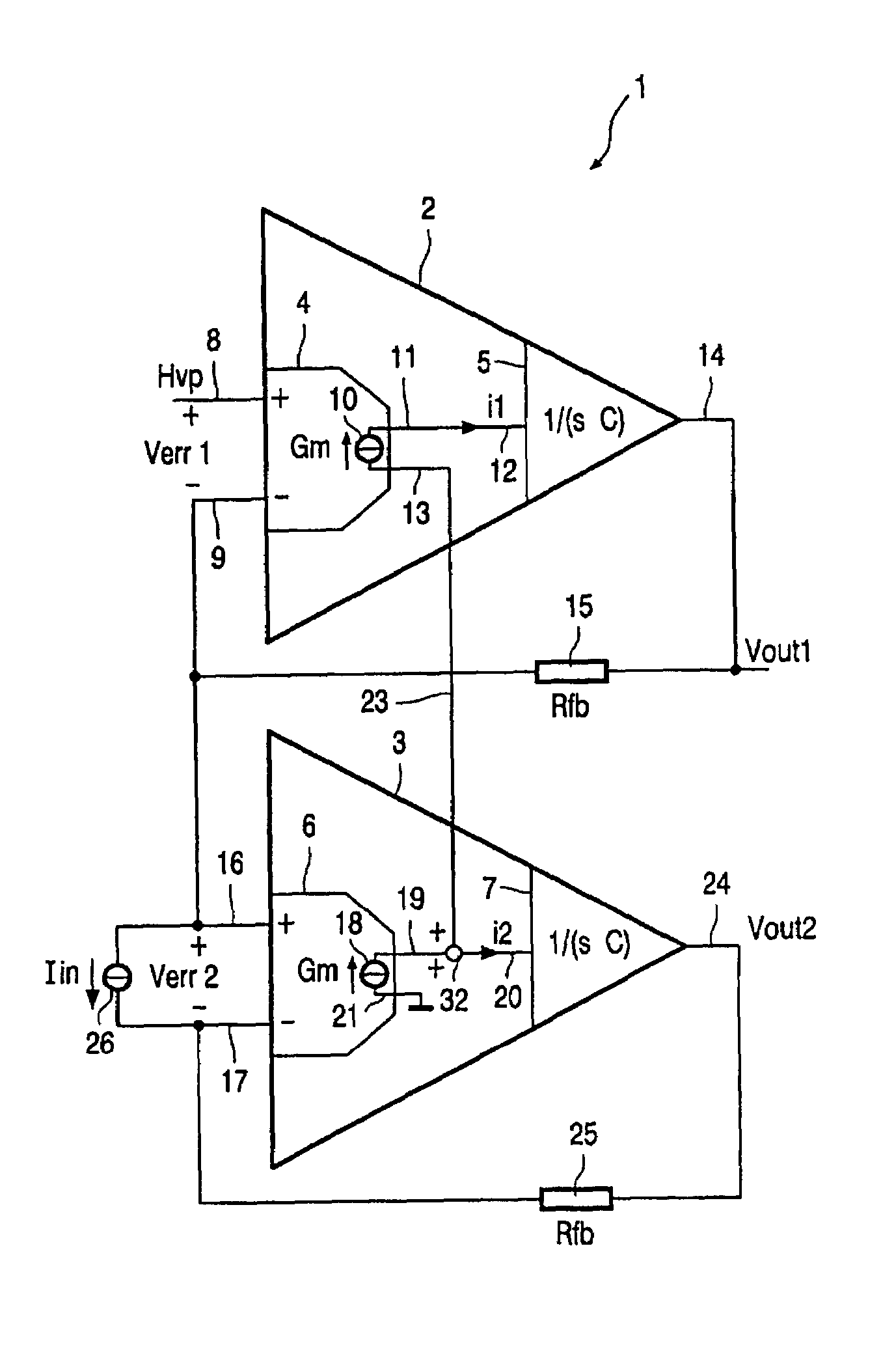

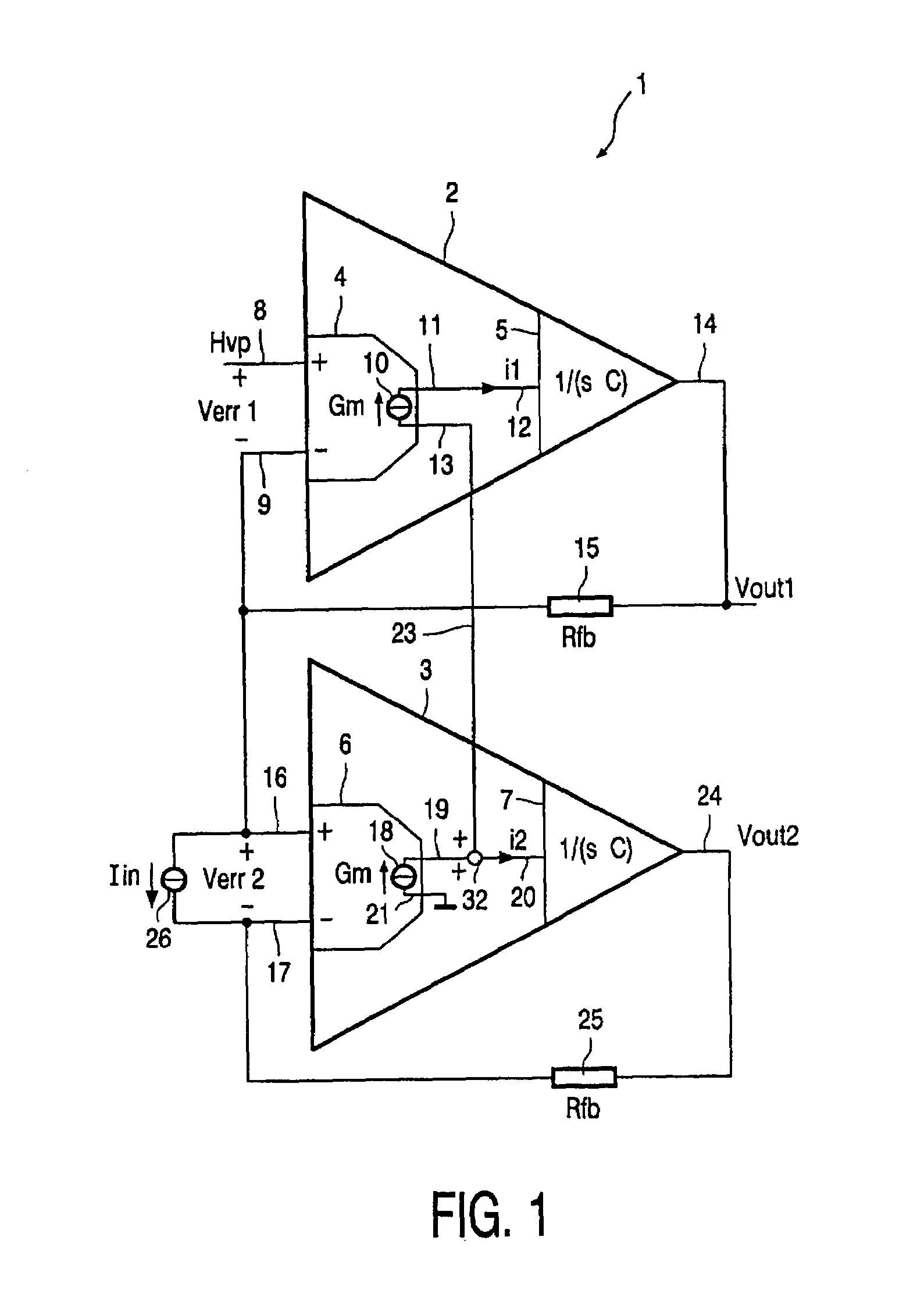

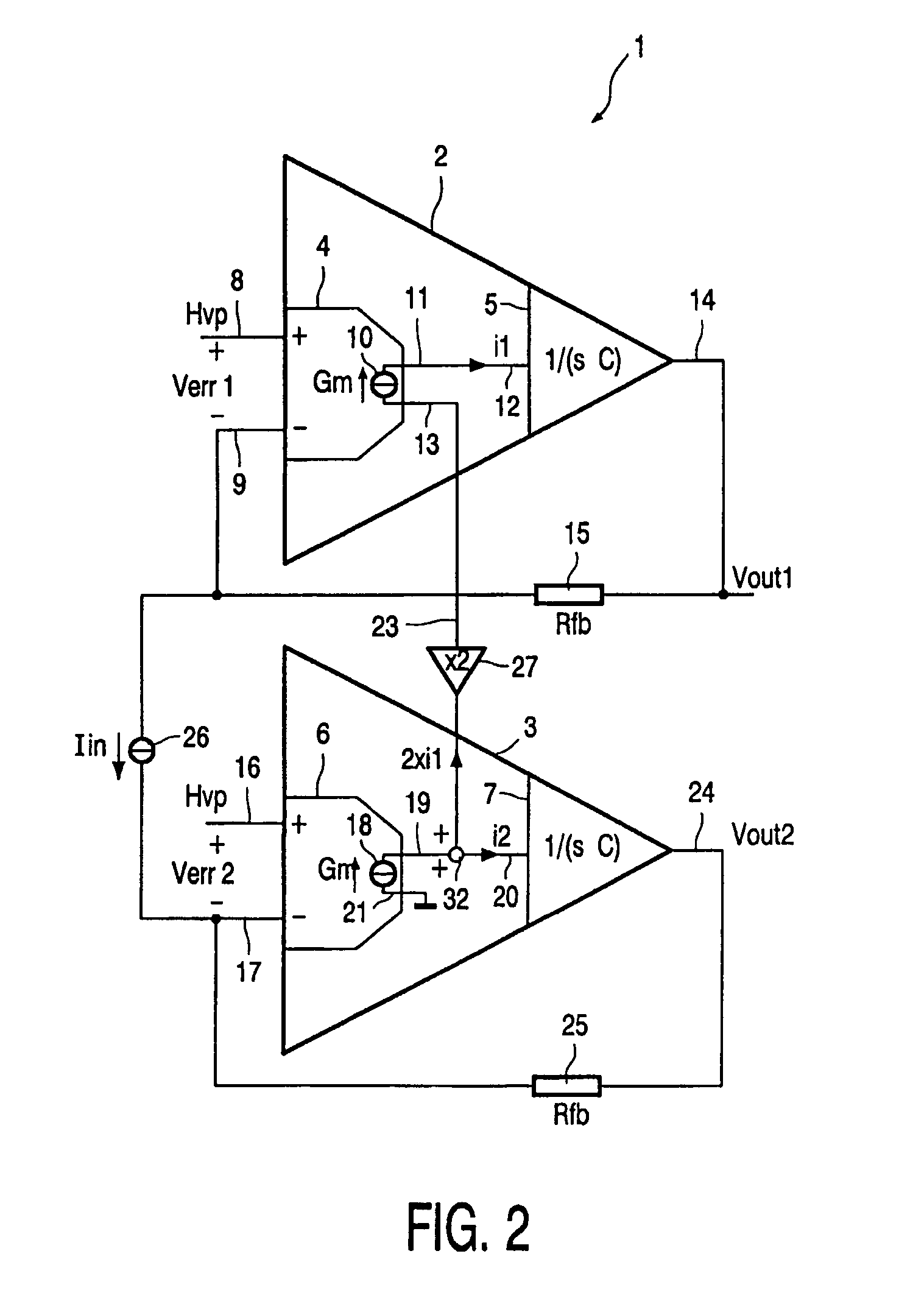

Power amplifier module with distortion compensation

InactiveUS7068099B2Reduce conductionImprove transconductanceNegative-feedback-circuit arrangementsAmplifier combinationsAudio power amplifierEngineering

The invention relates to a power amplifier module comprising a first amplifier 2 having a first front-end 4 and a first backend amplifier stage 5 and a second amplifier 3 having a second front-end 6 and a second backend amplifier stage 7, the first amplifier and the second amplifier being arranged in a Bridge Tied Load (BTL) configuration with feedback over the load,characterized in thatthe first and the second backend amplifier stages having point symmetrical transfer functions with respect to the origin,the input current i1 of the first backend amplifier stage being substantially equal to the input current i2 of the second backend amplifier stage.

Owner:NXP BV

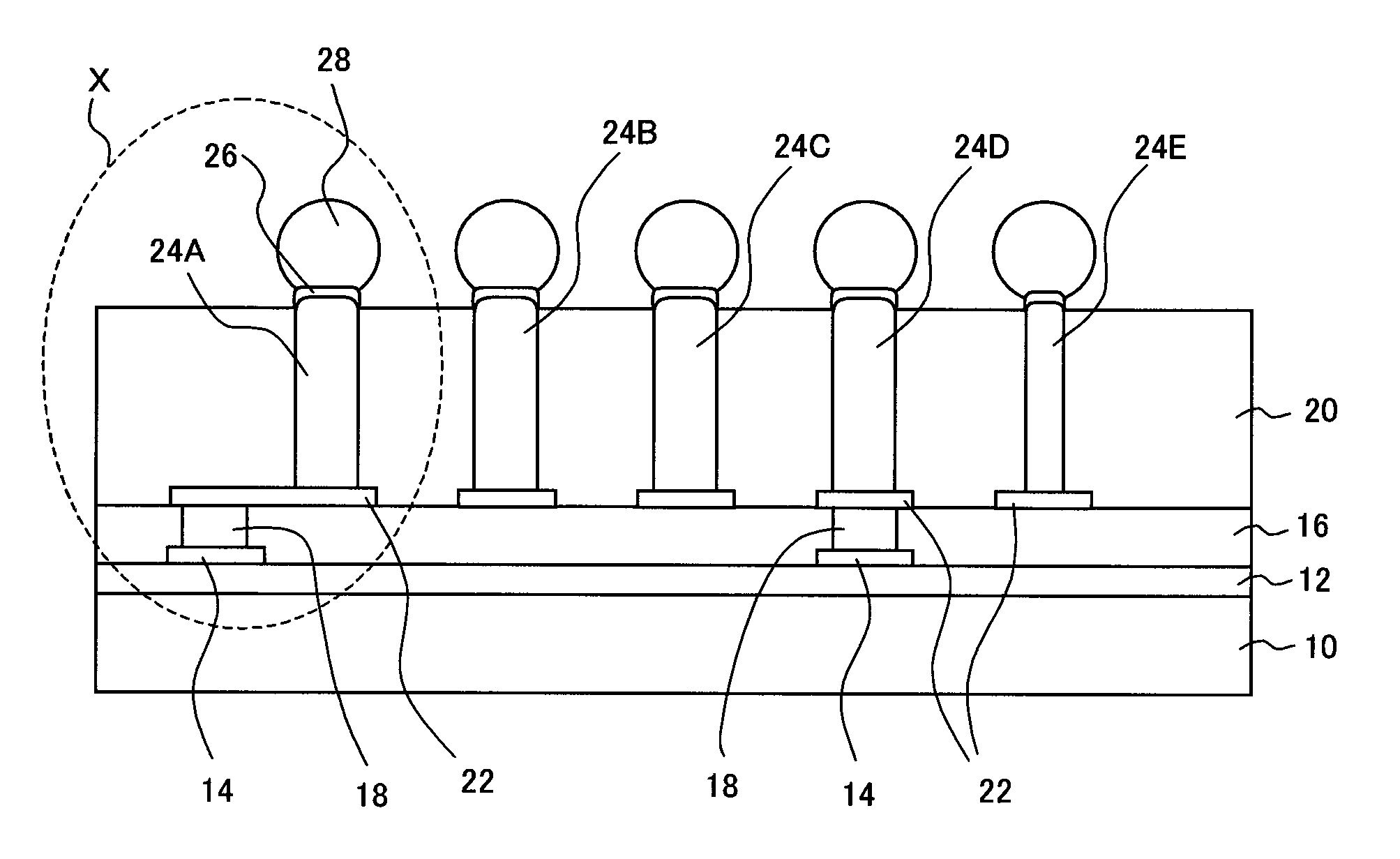

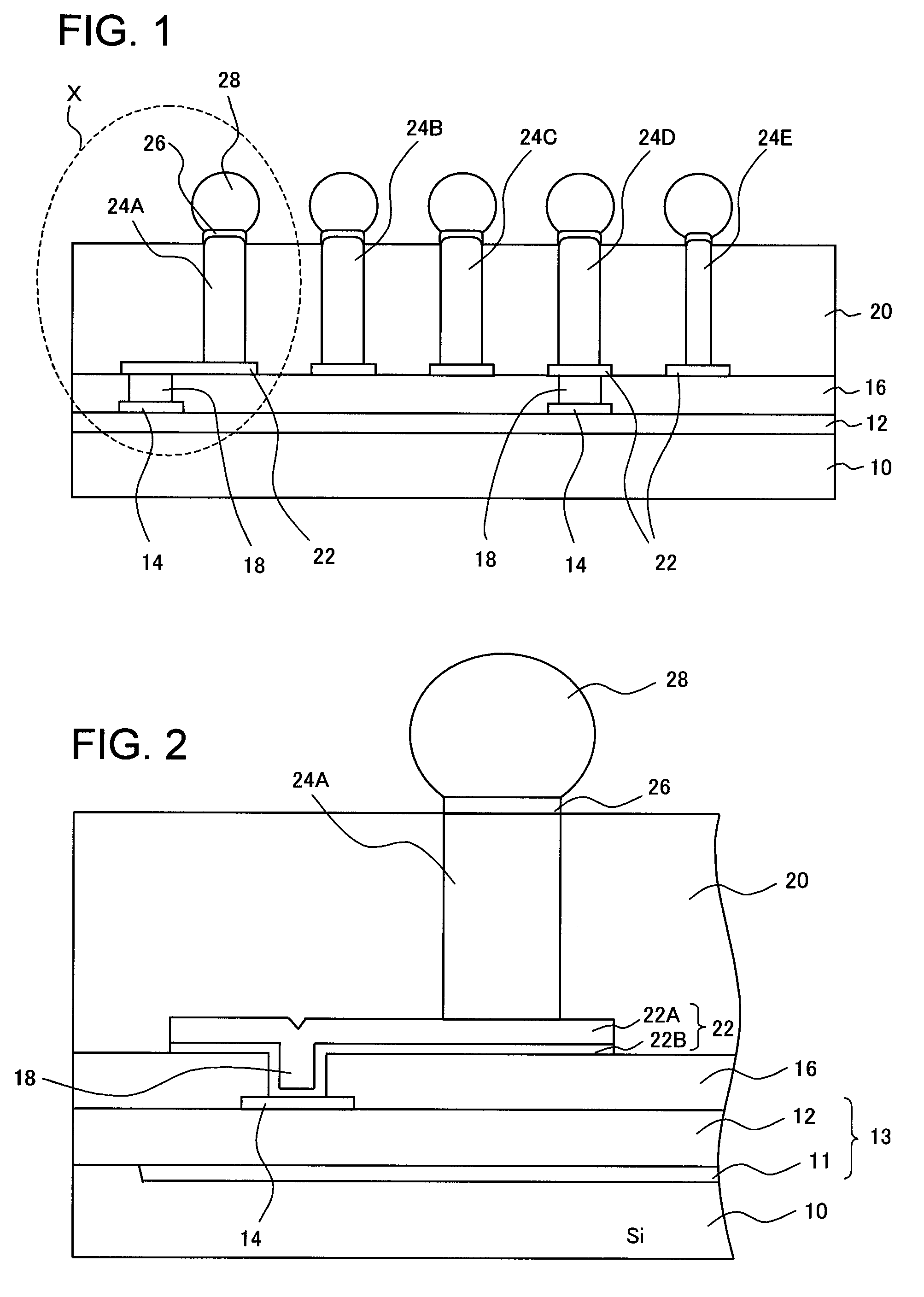

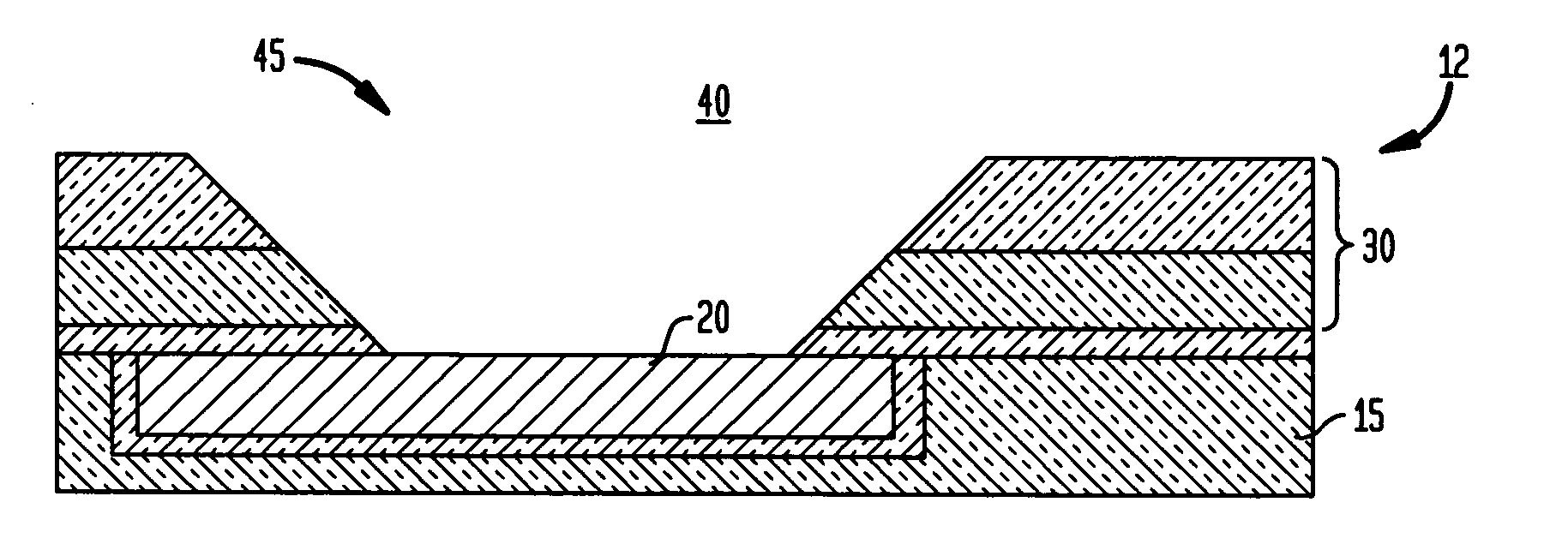

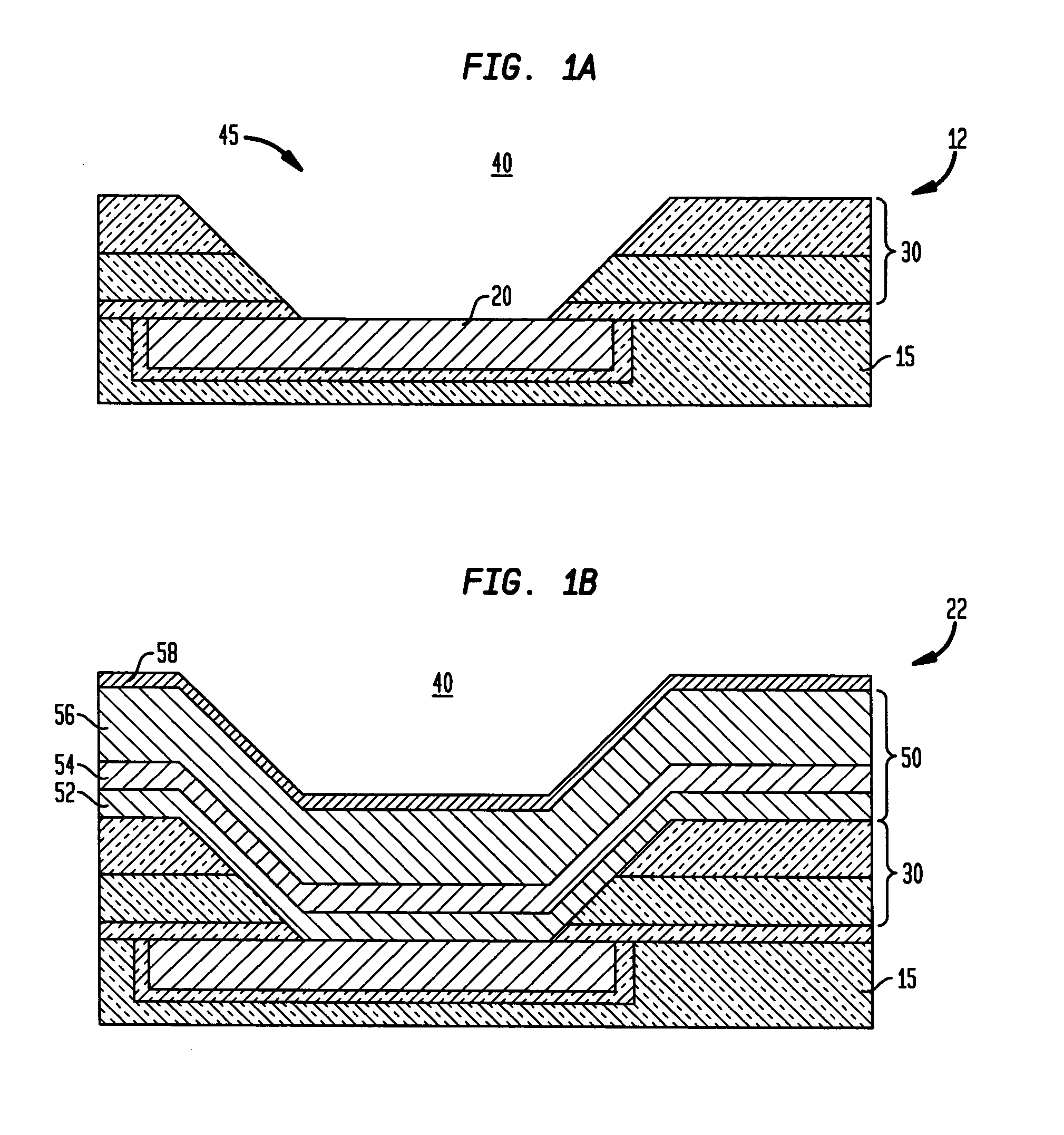

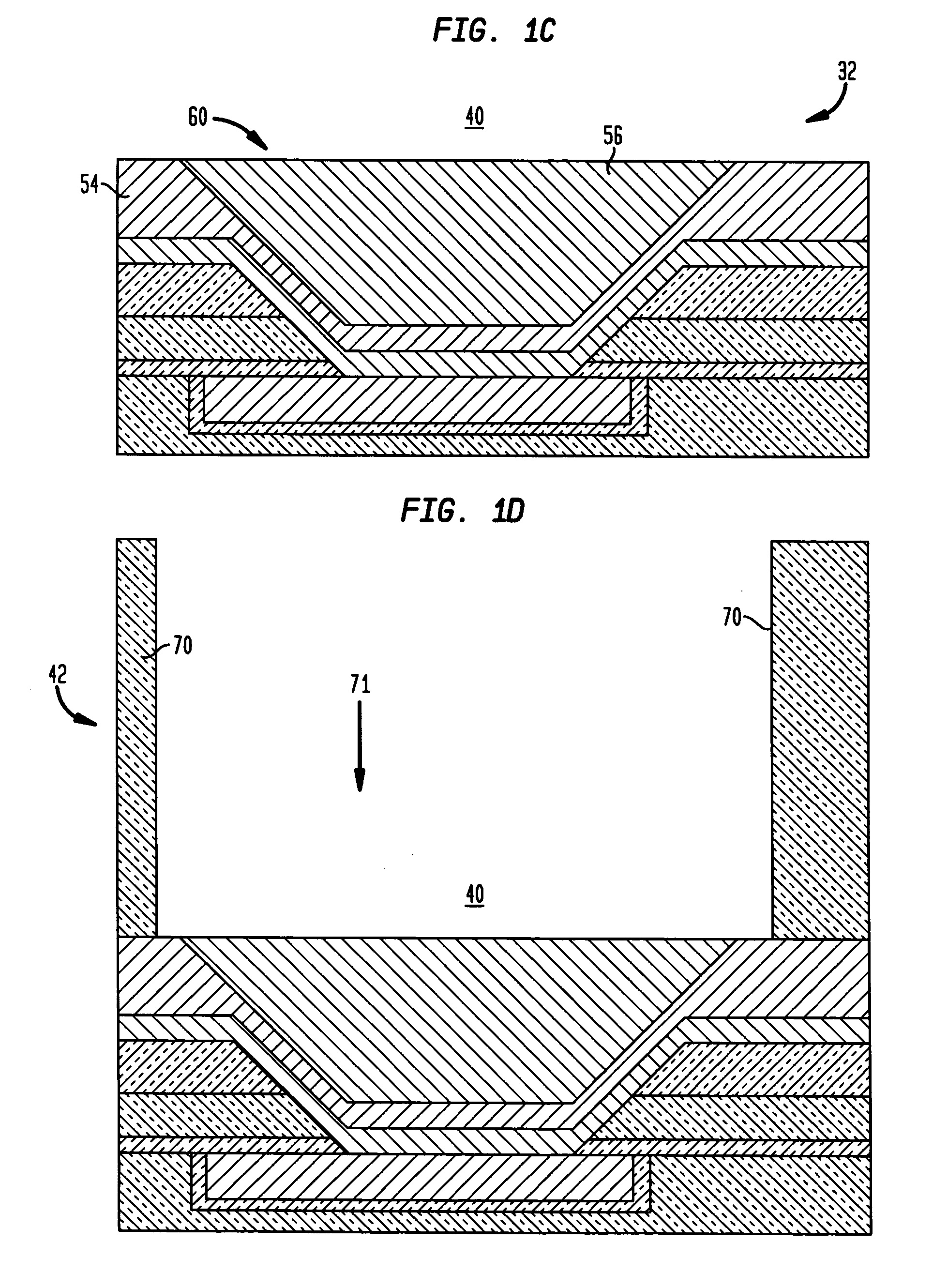

Damascene patterning of barrier layer metal for C4 solder bumps

InactiveUS20060016861A1Reduce the amount presentReduce spacingPrinted circuit assemblingSemiconductor/solid-state device detailsEtchingCopper

A system and method for forming a novel C4 solder bump for BLM (Ball Limiting Metallurgy) includes a novel damascene technique is implemented to eliminate the Cu undercut problem and improve the C4 pitch. In the process, a barrier layer metal stack is deposited above a metal pad layer. A top layer of the barrier layer metals (e.g., Cu) is patterned by CMP. Only bottom layers of the barrier metal stack are patterned by a wet etching. The wet etch time for the Cu-based metals is greatly reduced resulting in a reduced undercut. This allows the pitch of the C4 solder bumps to be reduced. An alternate method includes use of multiple vias at the solder bump terminal.

Owner:GLOBALFOUNDRIES INC

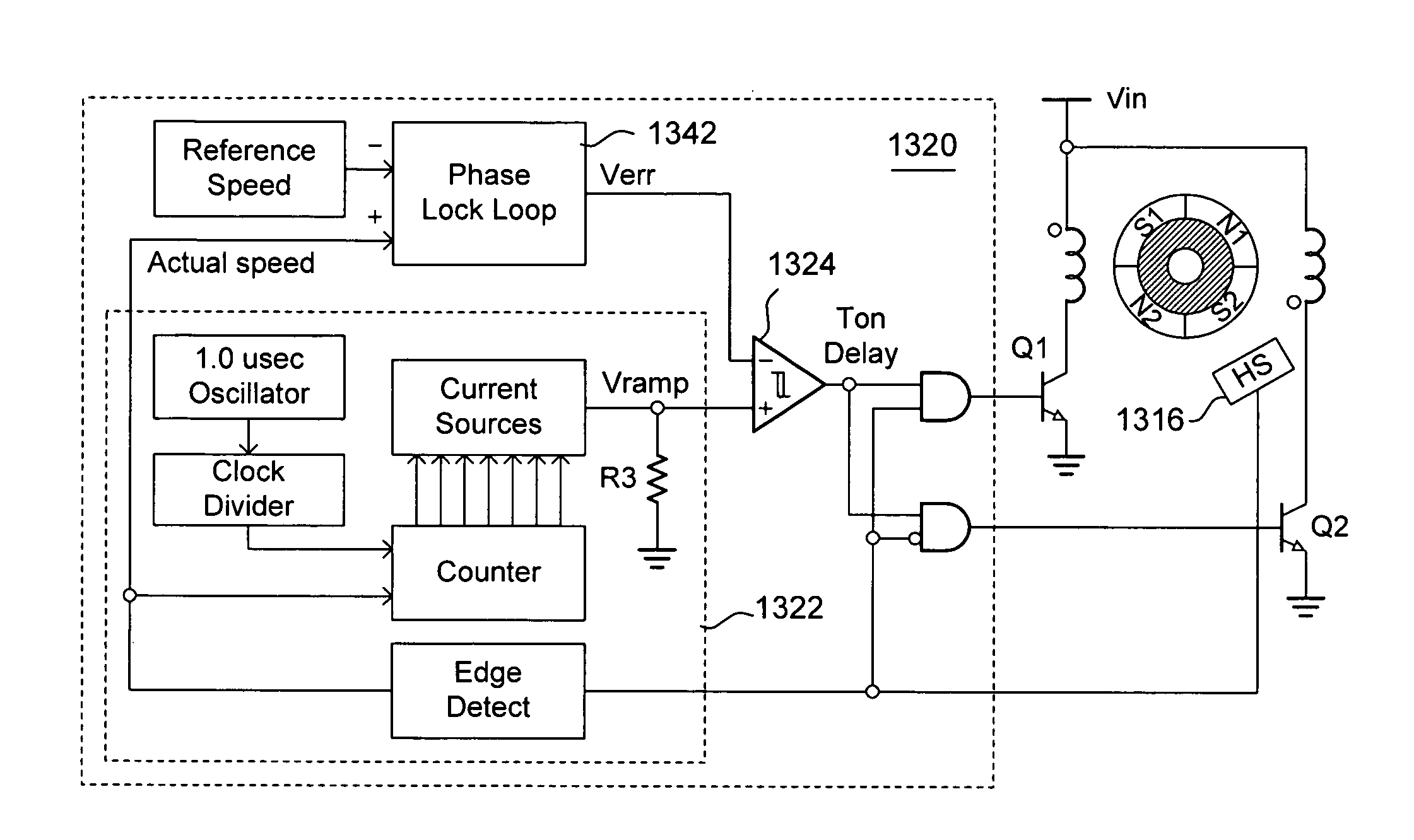

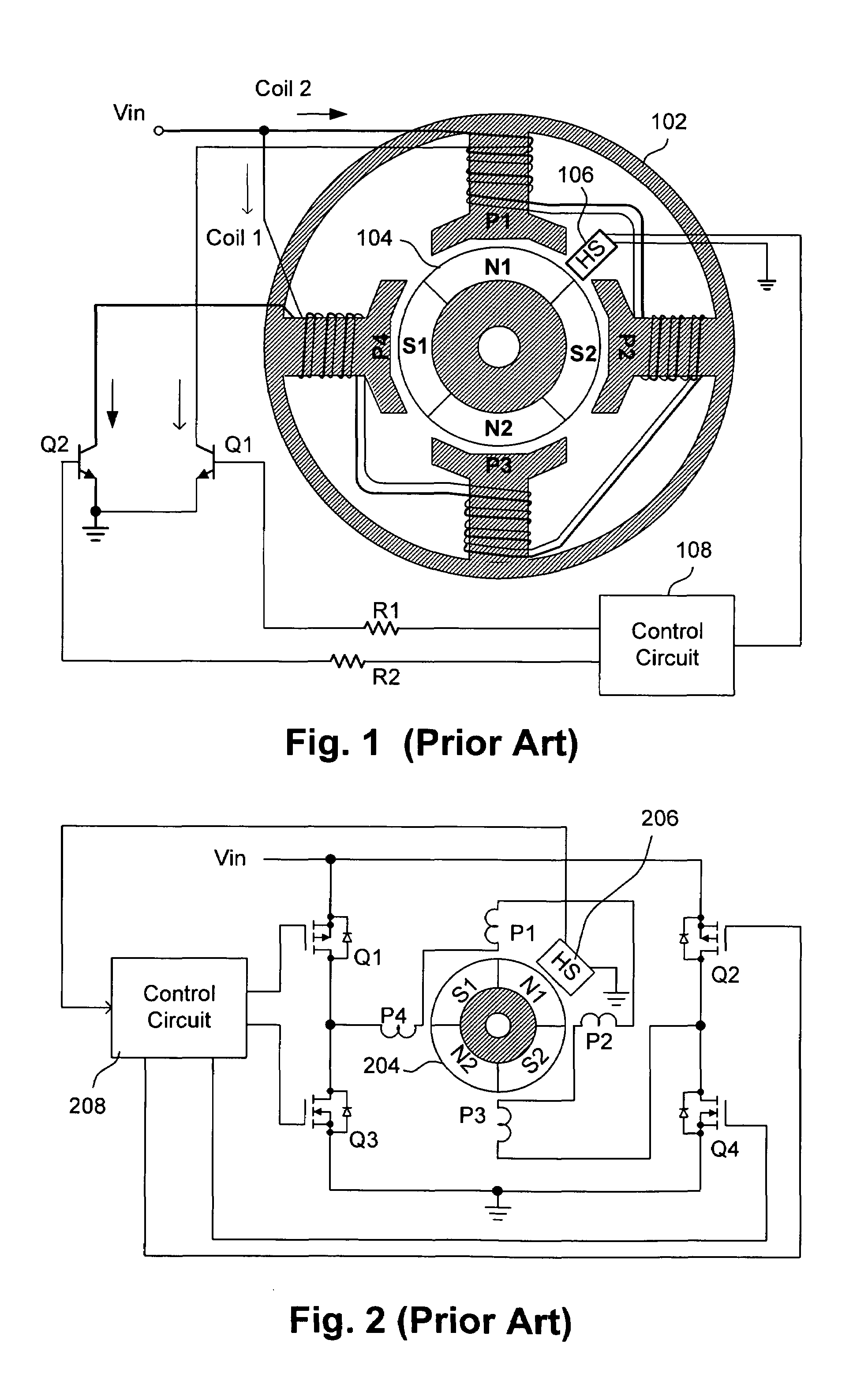

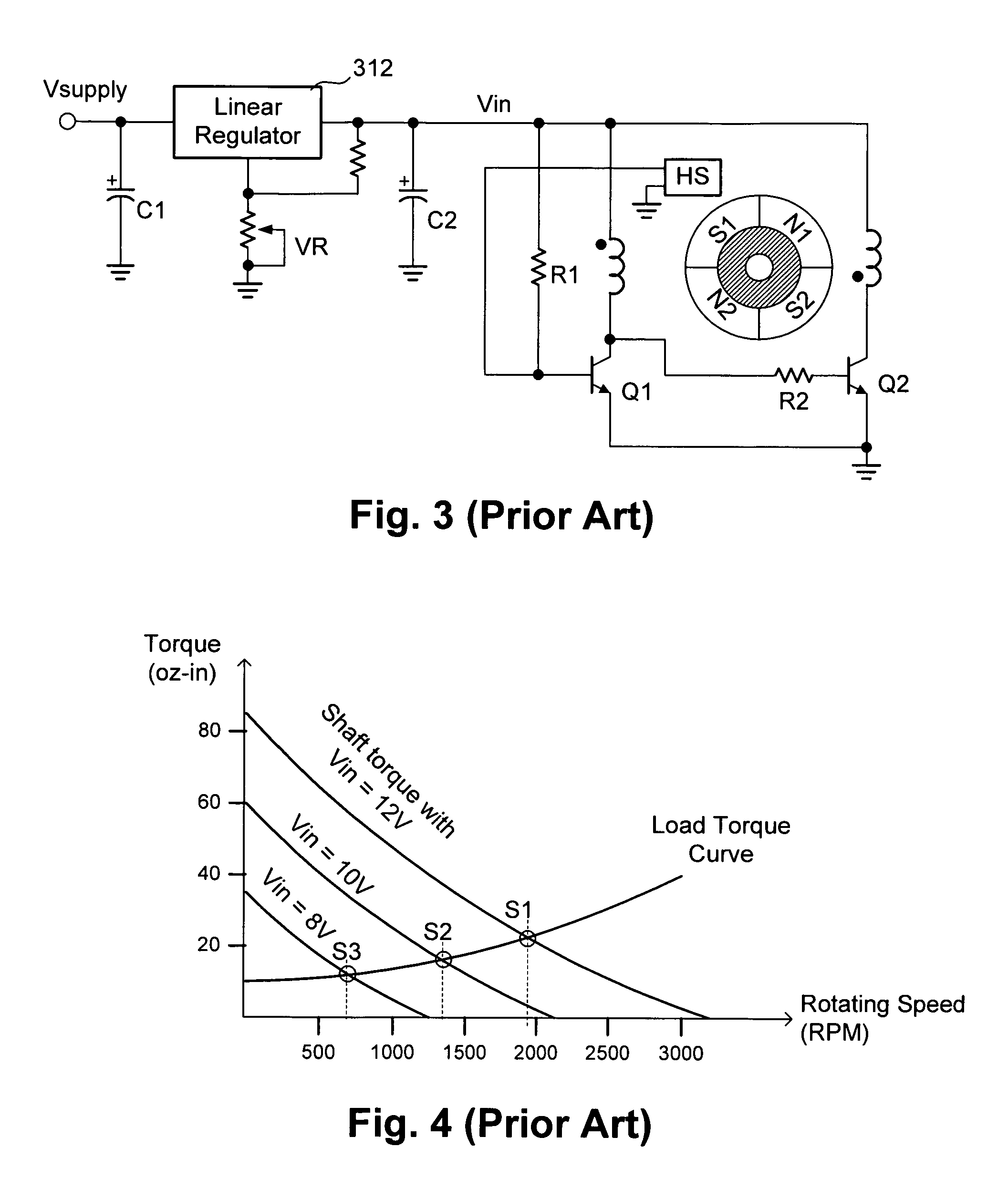

Speed control of brushless DC motors

InactiveUS7259531B1Convenient speed adjustmentEliminate degradationAC motor controlSynchronous motors startersEngineeringControl circuit

The speed control apparatus comprises a plurality of Hall sensors, a plurality of switches, a turn-on control circuit, and a gate drive logic. The Hall sensors are configured to detect magnetic rotor sections of a poly-phase brushless DC motor at different positions. The switches apply voltages on a plurality of windings to respectively produce magnetic north or south on stator poles of the poly-phase BLDC motor. The turn-on control circuit generates a conduction time reduction after each output transition of the Hall sensors. The gate drive logic separately turns on or turns off the switches according to different output transitions of the Hall sensors to respectively apply voltages on the windings with the conduction time reduction.

Owner:GREEN MARK TECH

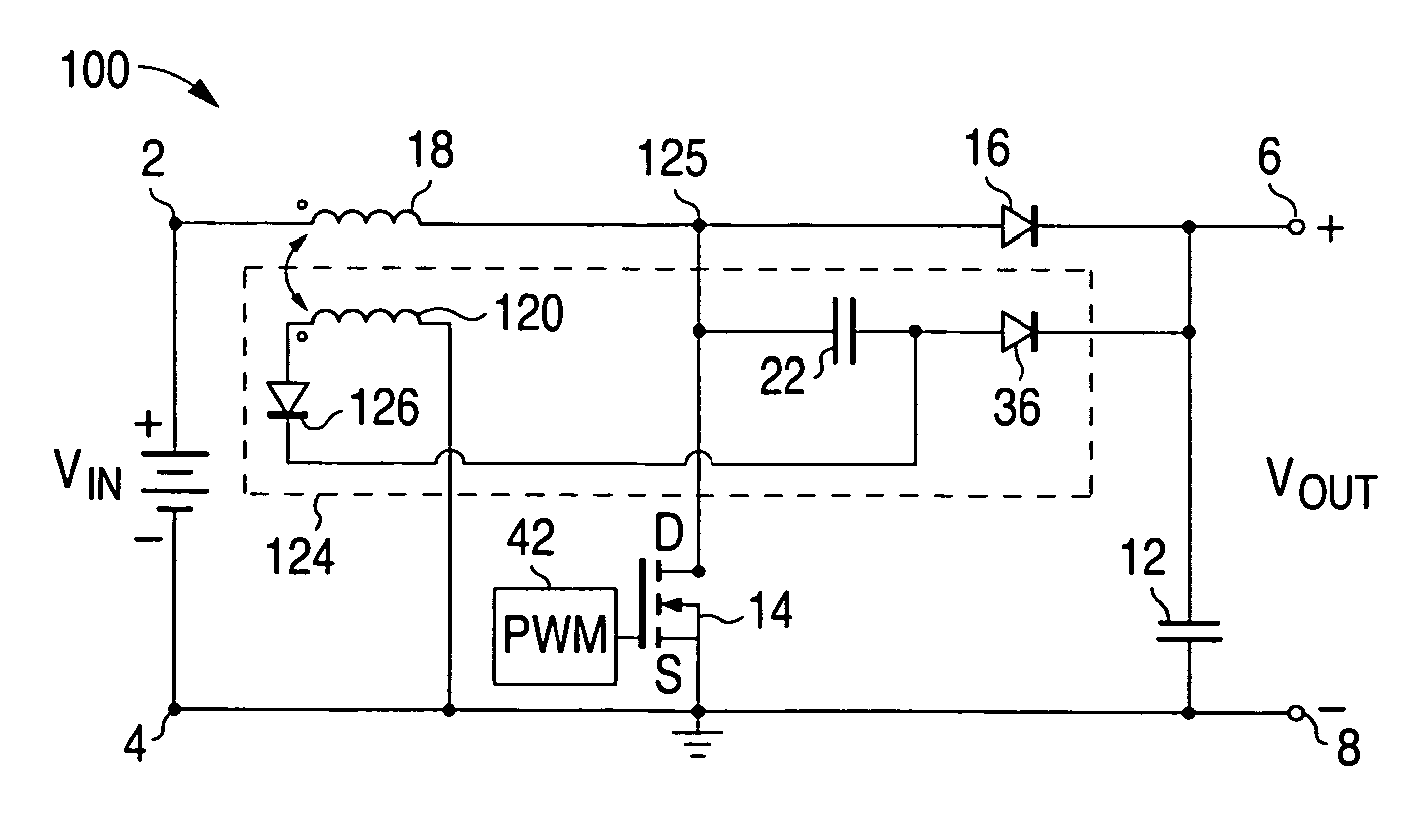

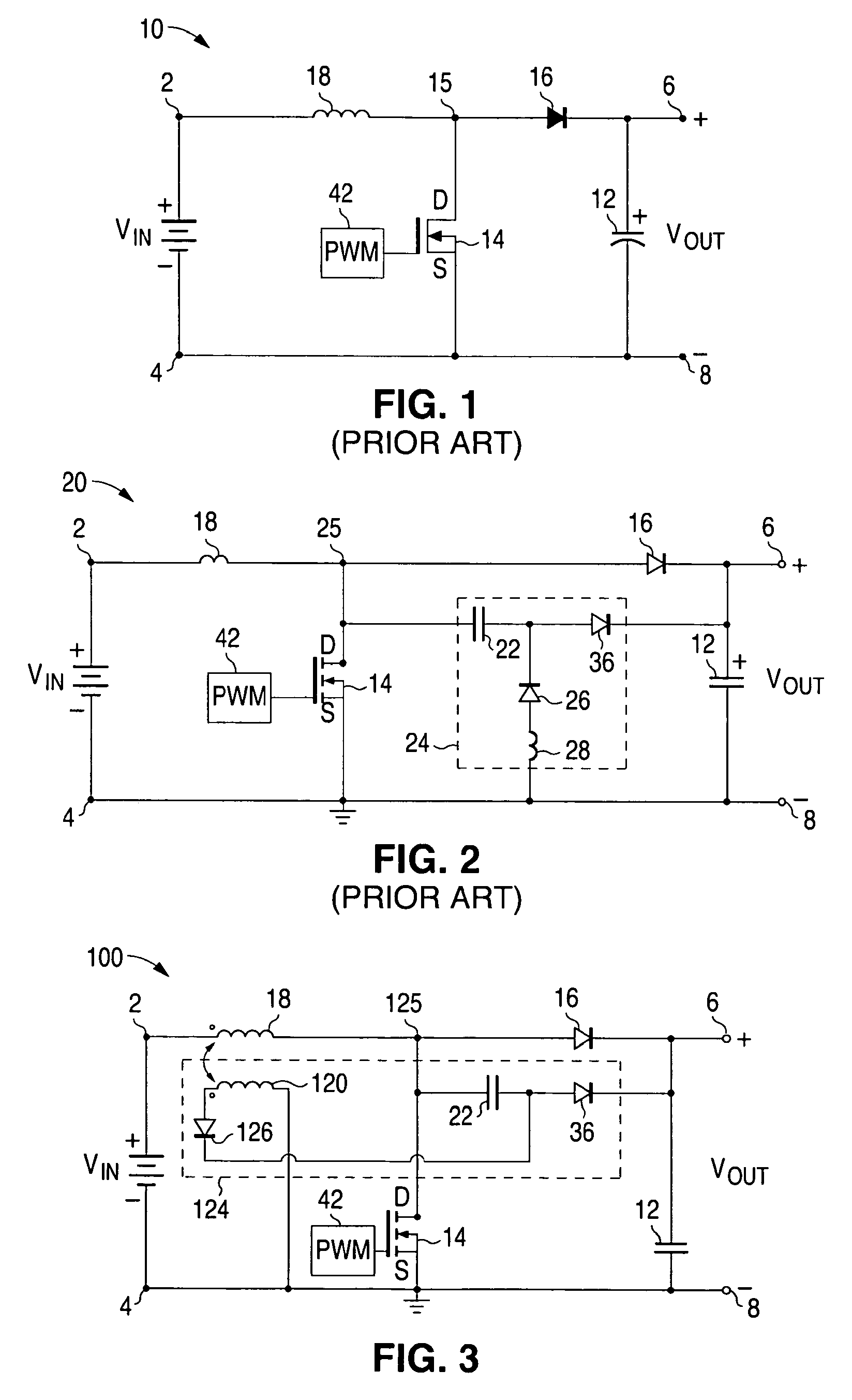

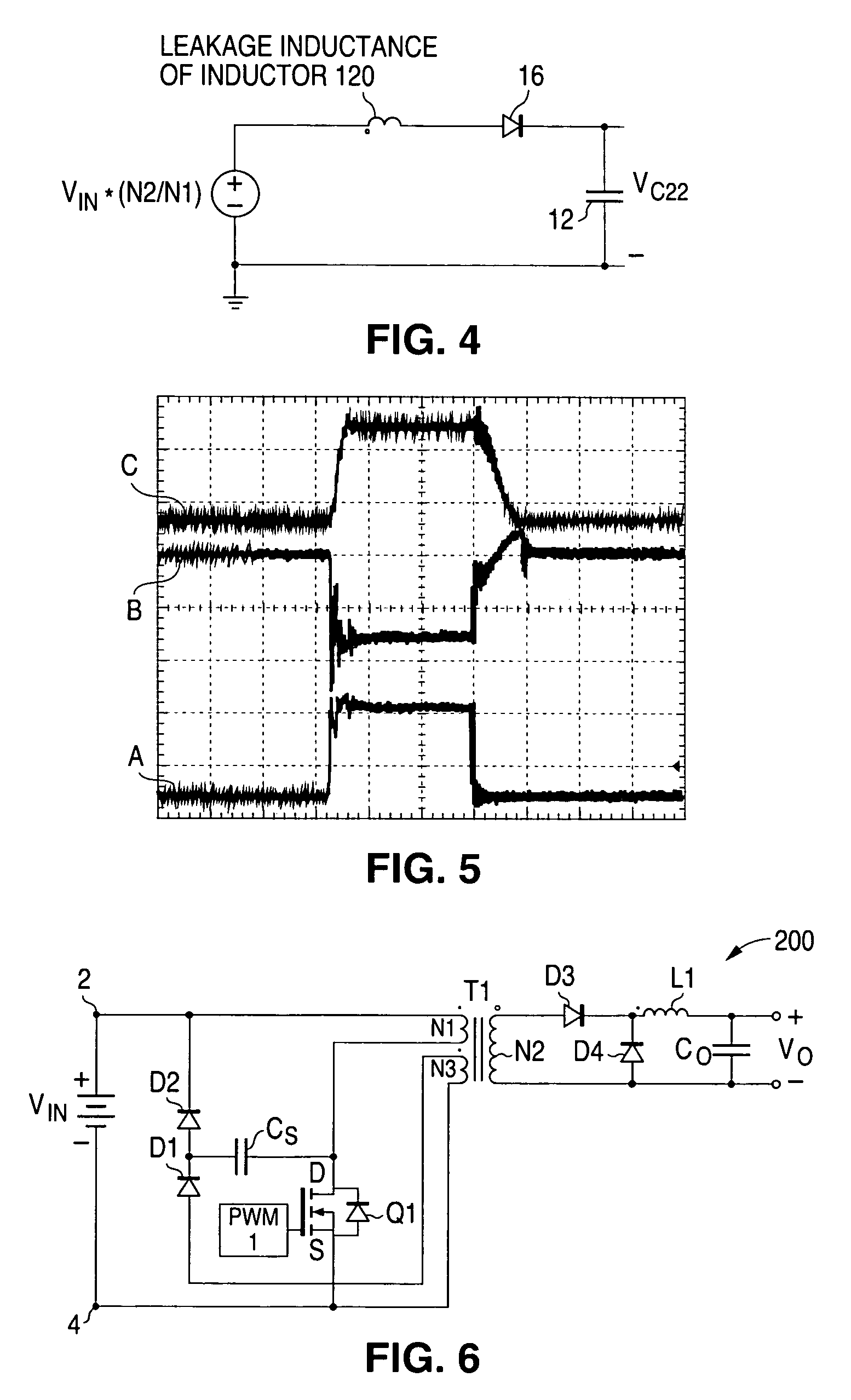

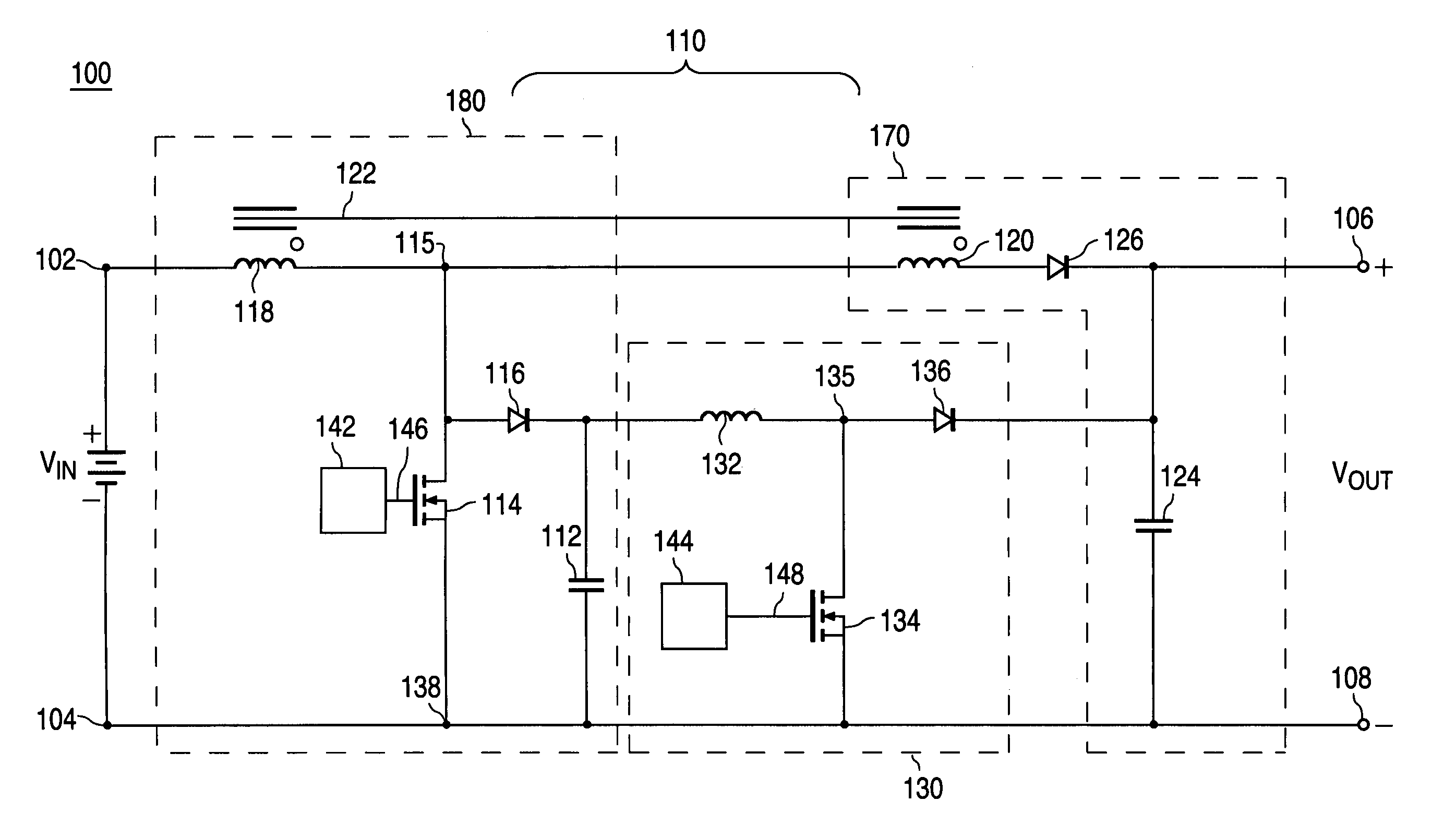

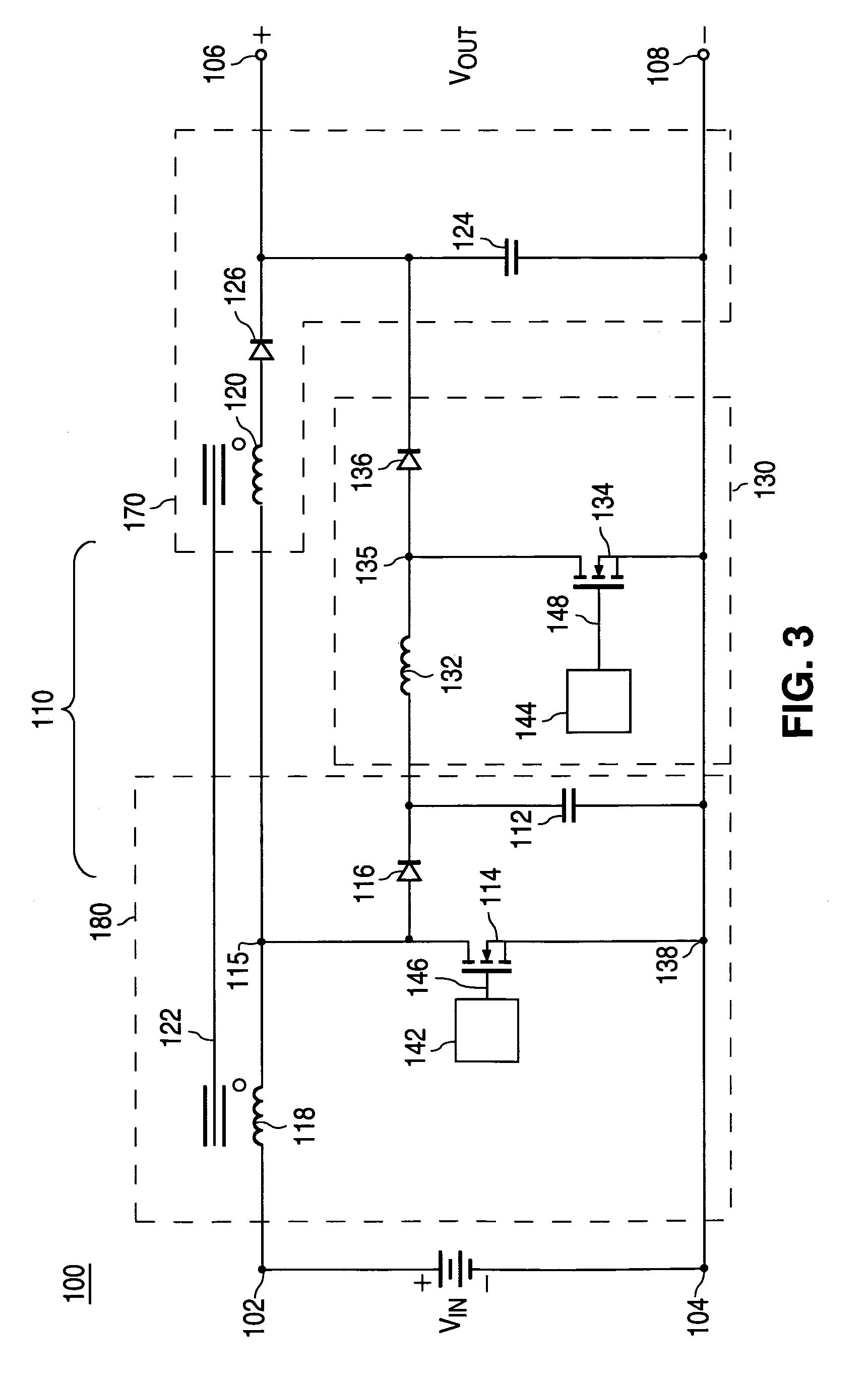

Two stage boost converter topology

ActiveUS7023186B2Reduce voltageSmall and less-costlyDc-dc conversionElectric variable regulationMOSFETVoltage spike

A power converter having a two stage boost circuit and a small boost converter. The main power flow for the power converter is via the two stage booster circuit having a single switch. The voltage spike of the switch is clamped by a diode and a capacitor. The energy at the capacitor is transferred to the power converter's output terminals by the small boost converter. The two stage boost converter topology enables the use of much lower voltage and Rdson MOSFET switches so as to reduce cost, switch conduction loss and turn on loss.

Owner:ASTEC INT LTD

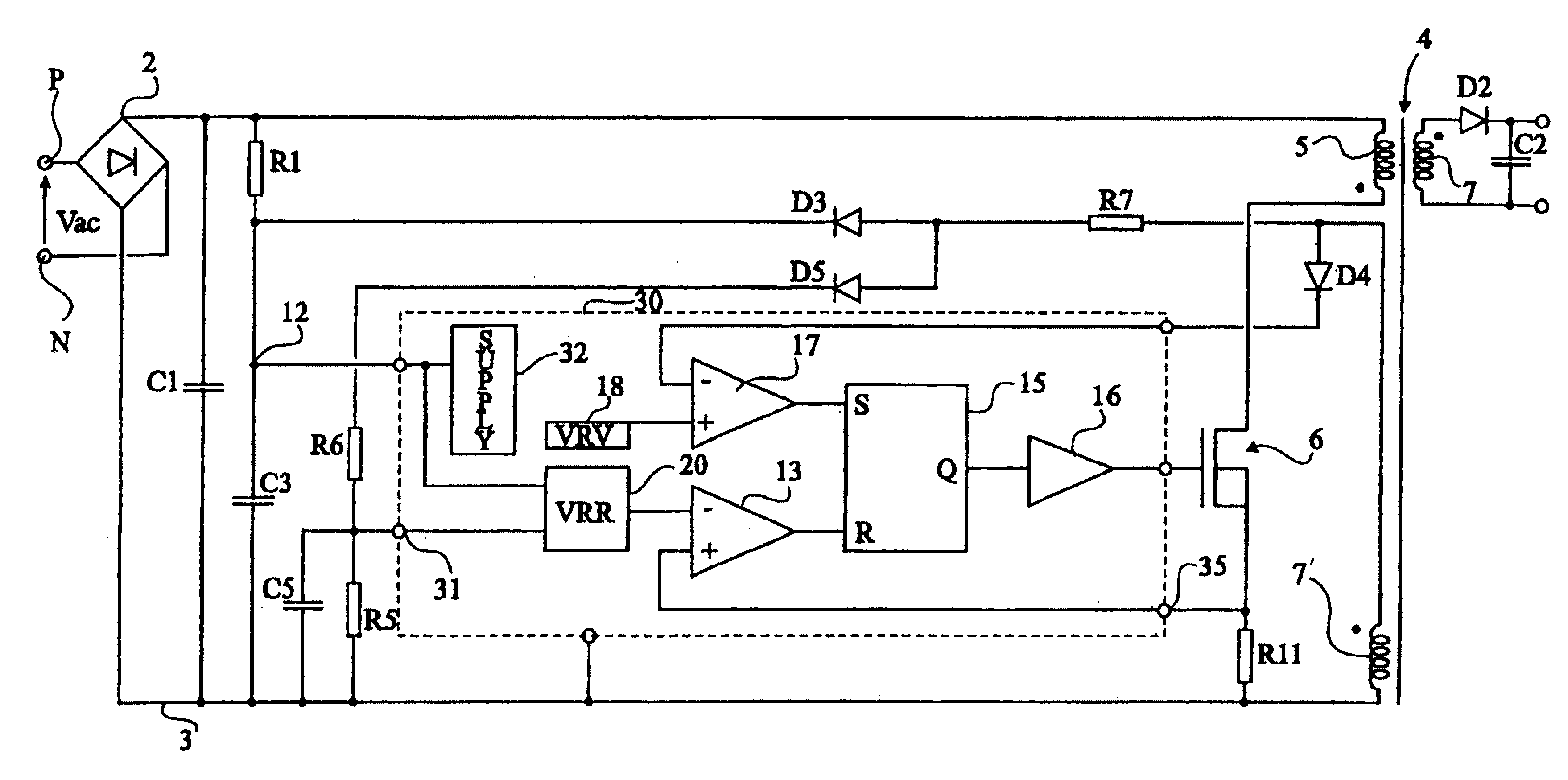

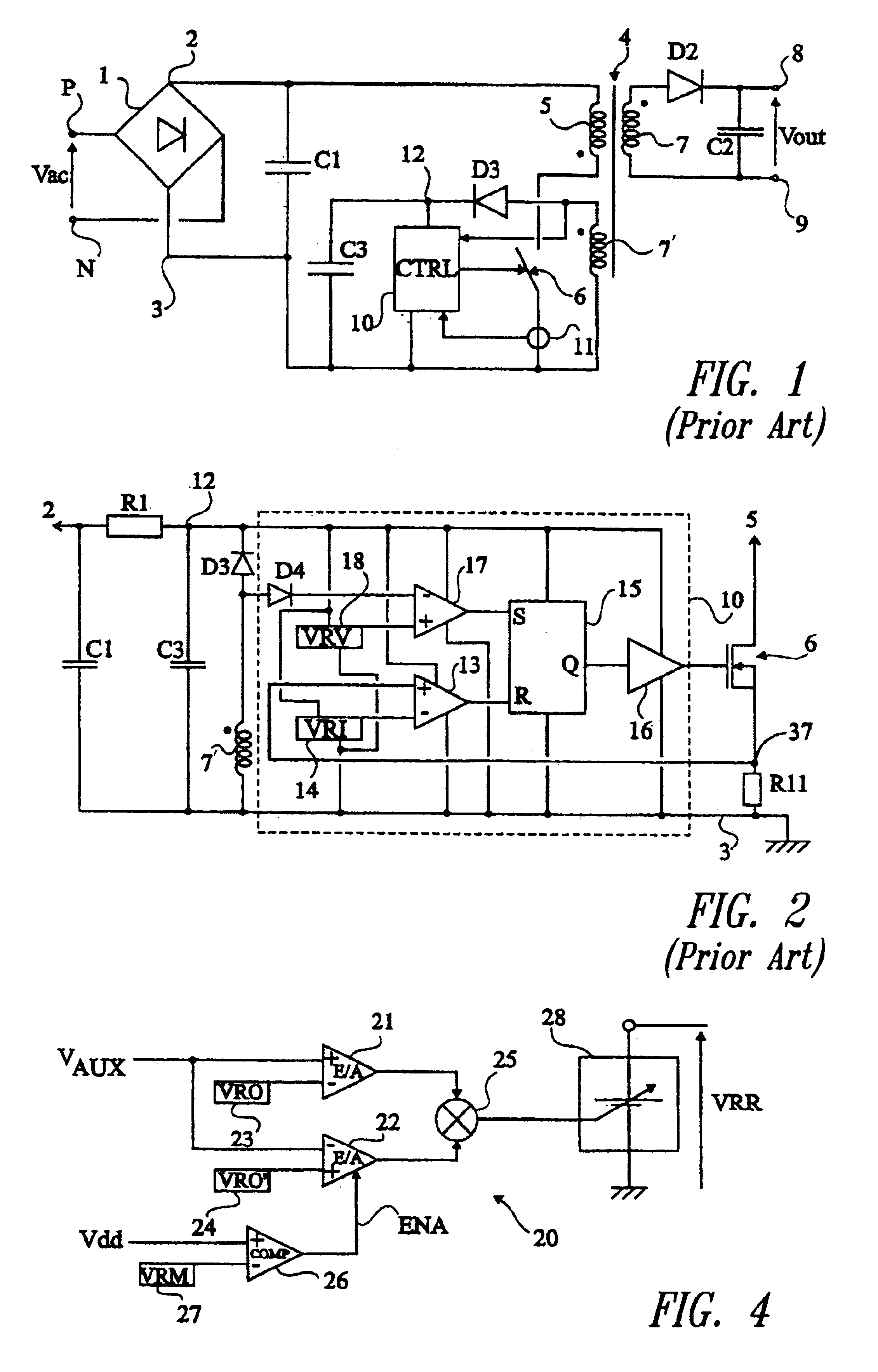

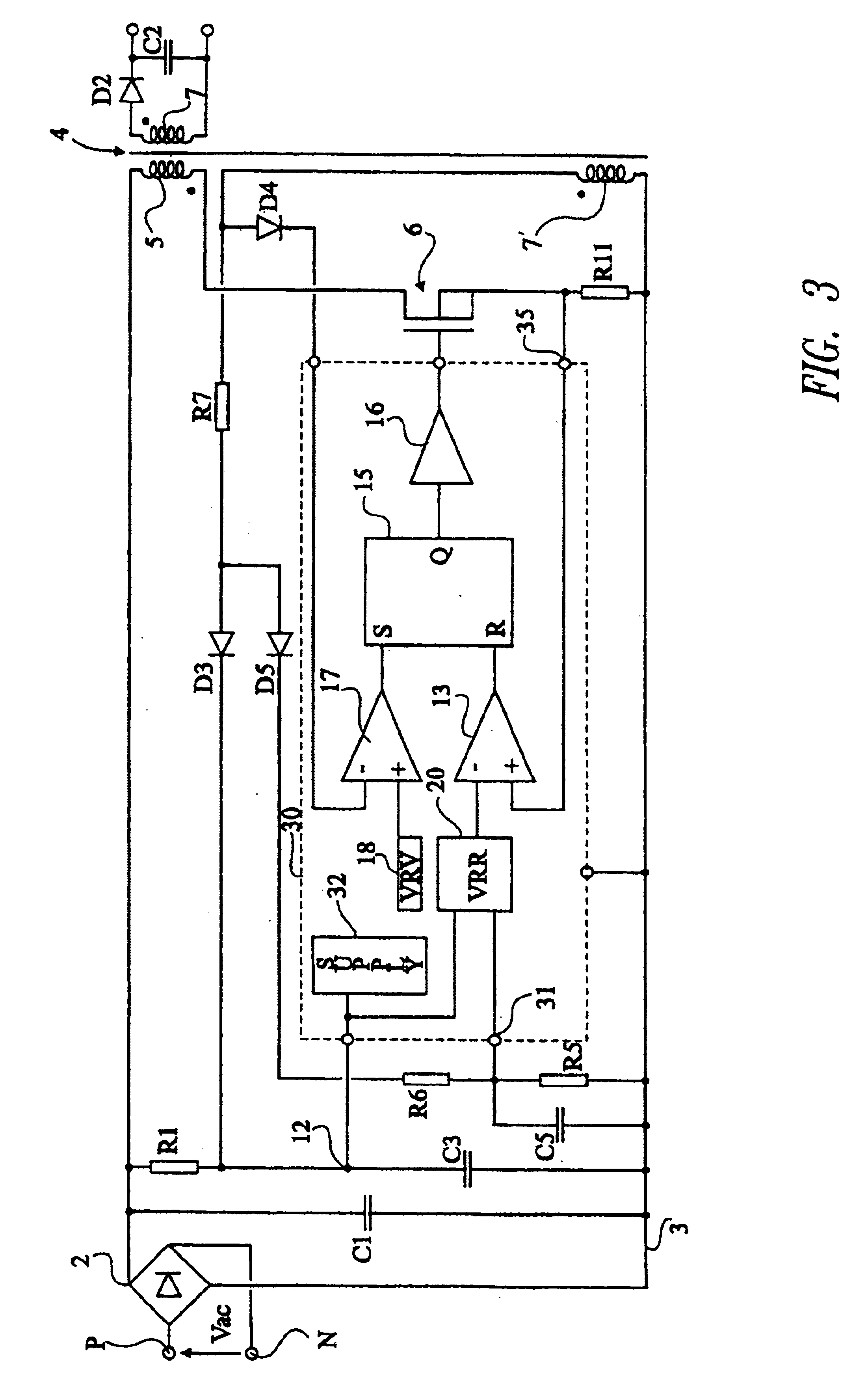

Voltage converter with a self-oscillating control circuit

InactiveUS6963496B2Reduce conductionConversion with intermediate conversion to dcDc-dc conversionVoltage converterTransformer

A voltage converter including a transformer having a primary winding connected in series with a switch for cutting-up a supply voltage and having a secondary winding associated with a capacitor providing a D.C. low voltage, and a self-oscillating control circuit of the switch for detecting the end of the demagnetization of an auxiliary winding of the transformer, to turn the switch on, and for detecting the current in the on-state switch to turn it off when this current reaches a reference point. The reference point is made variable according to the voltage across the auxiliary winding.

Owner:STMICROELECTRONICS SRL

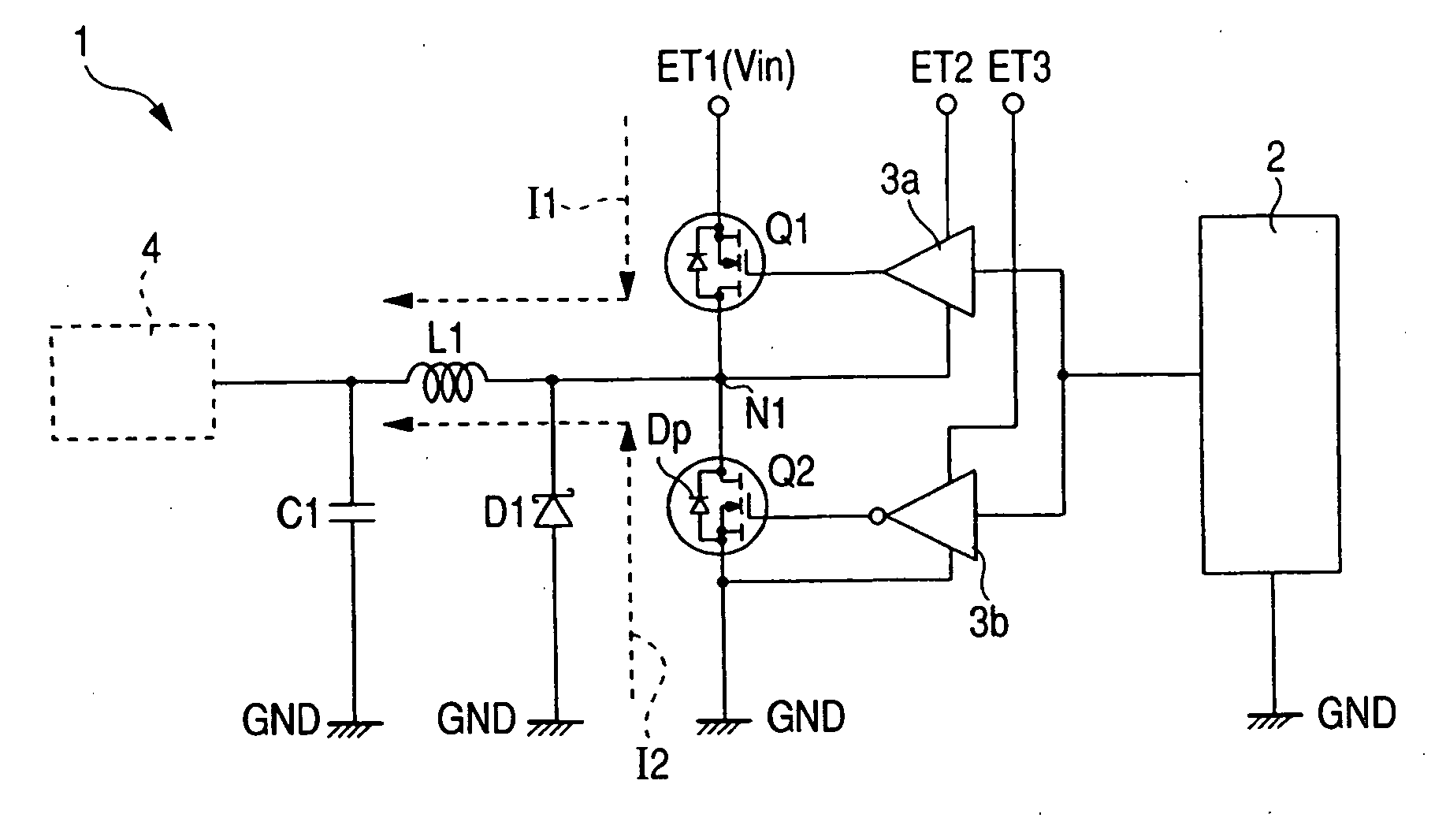

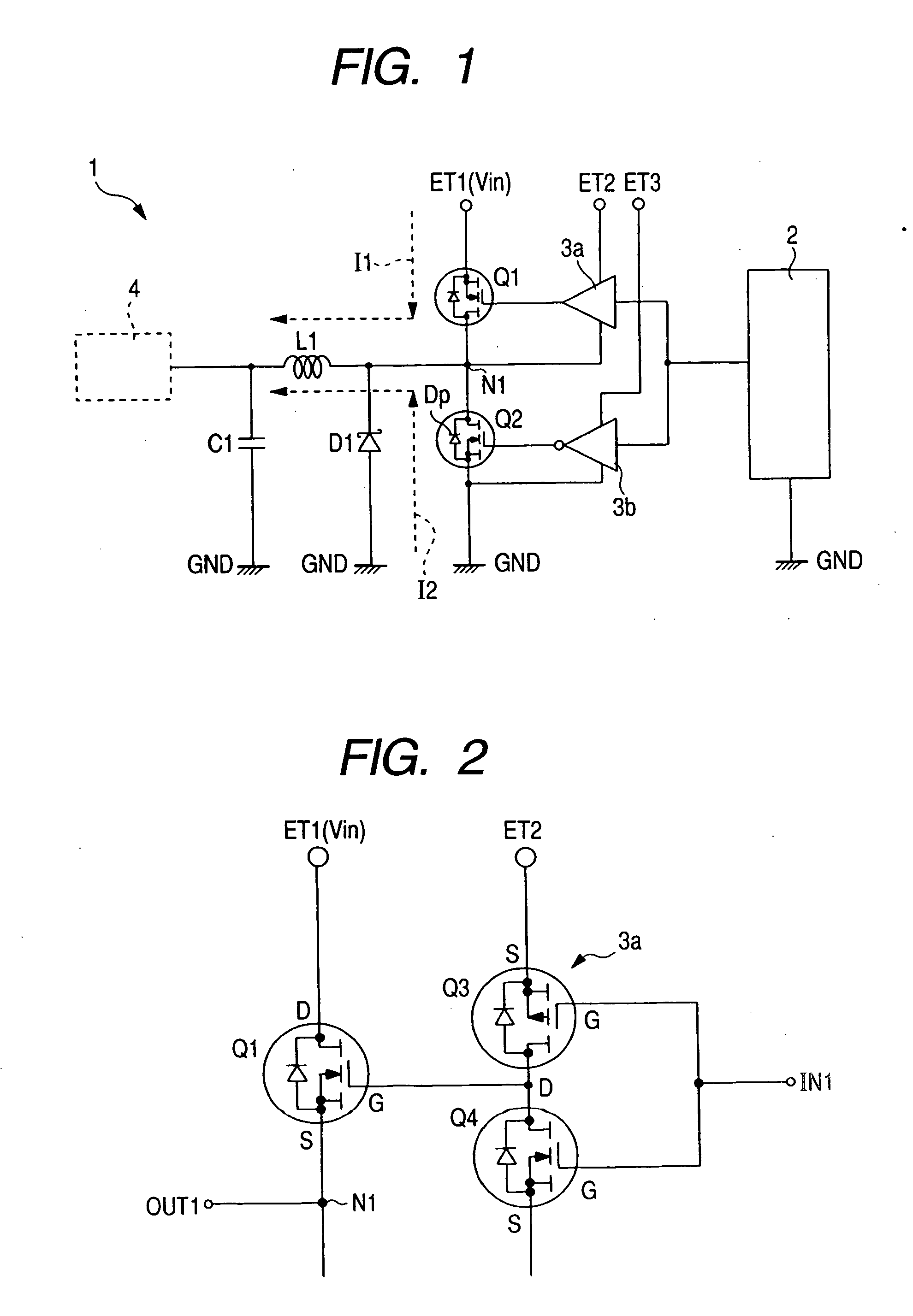

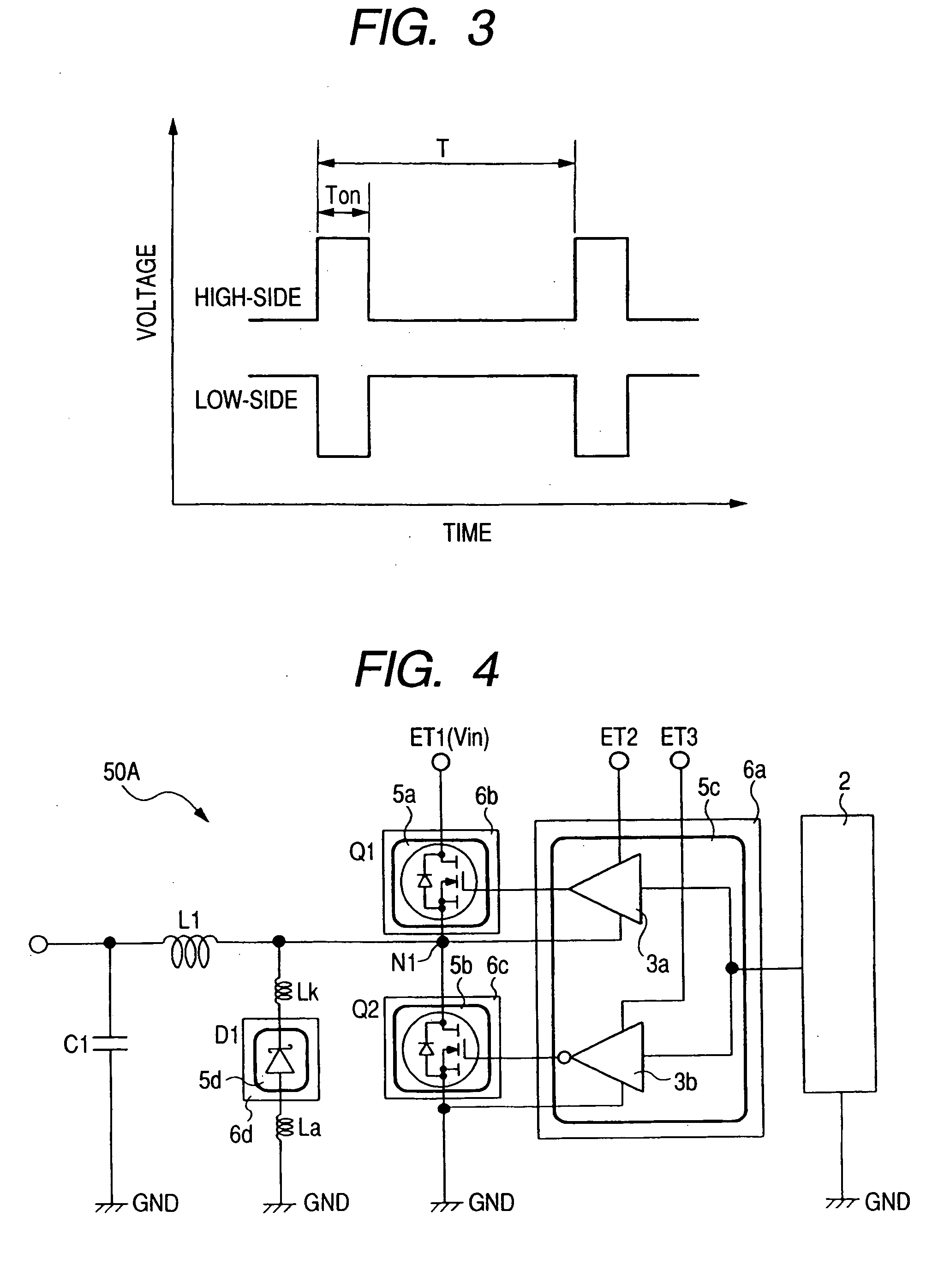

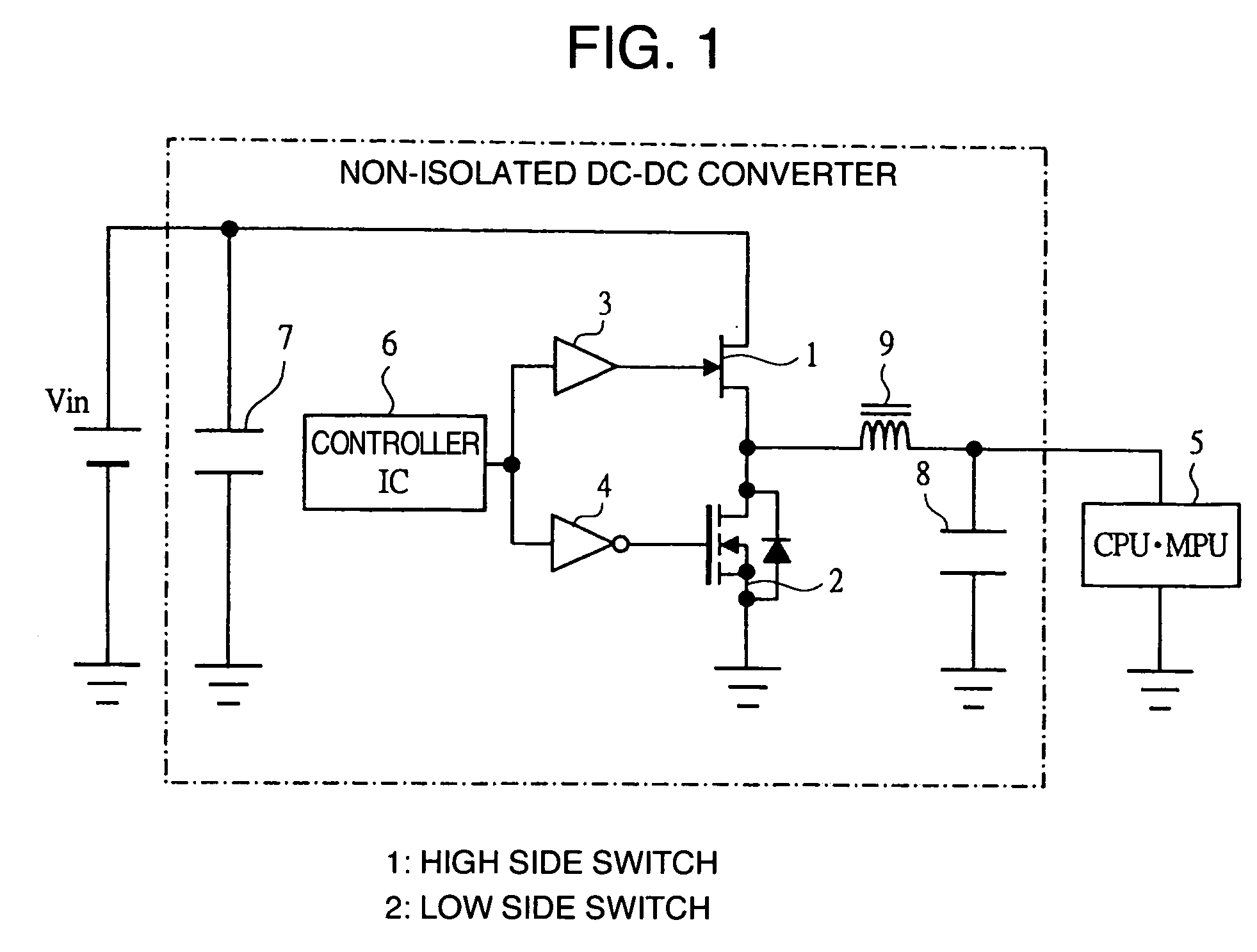

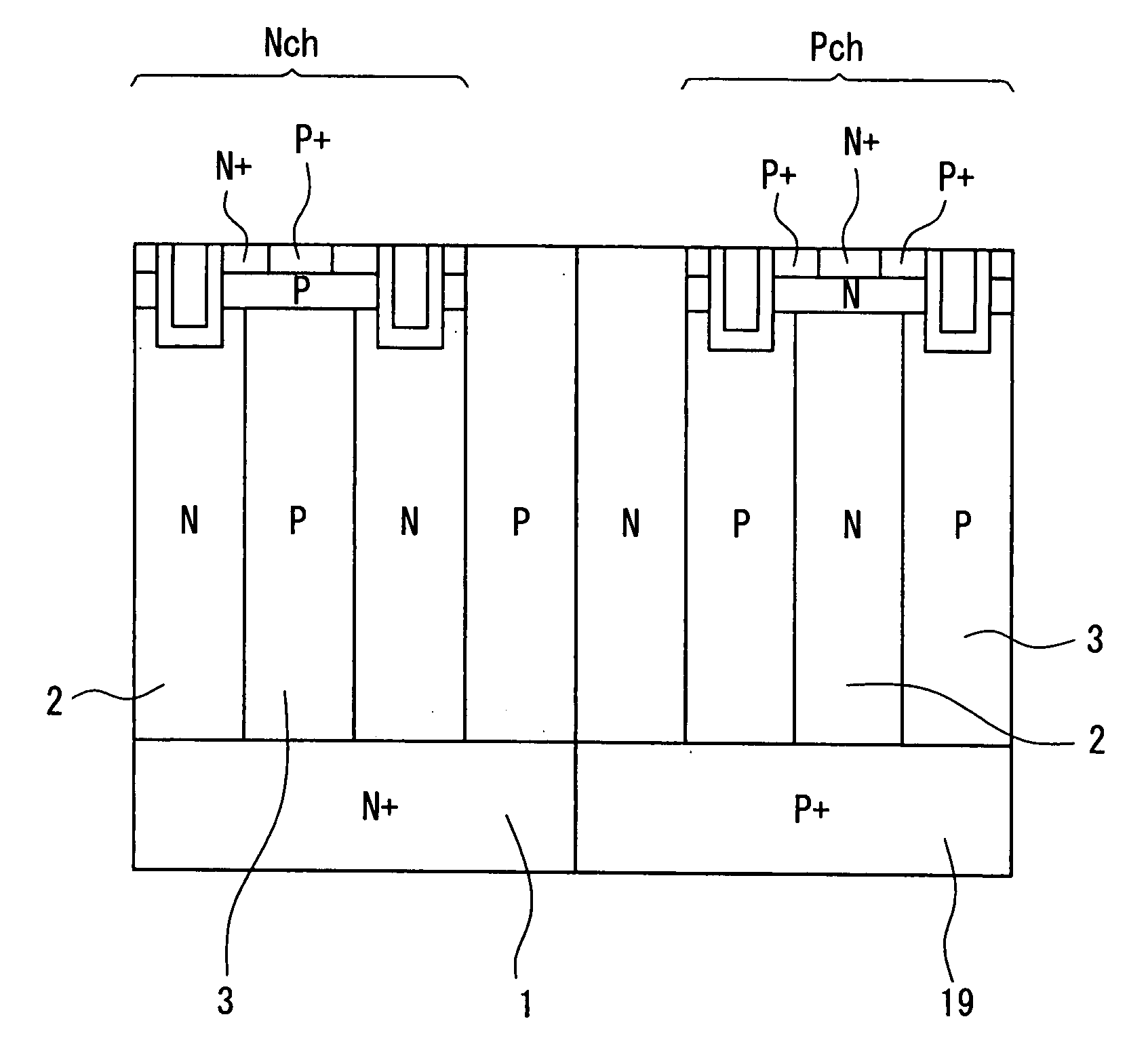

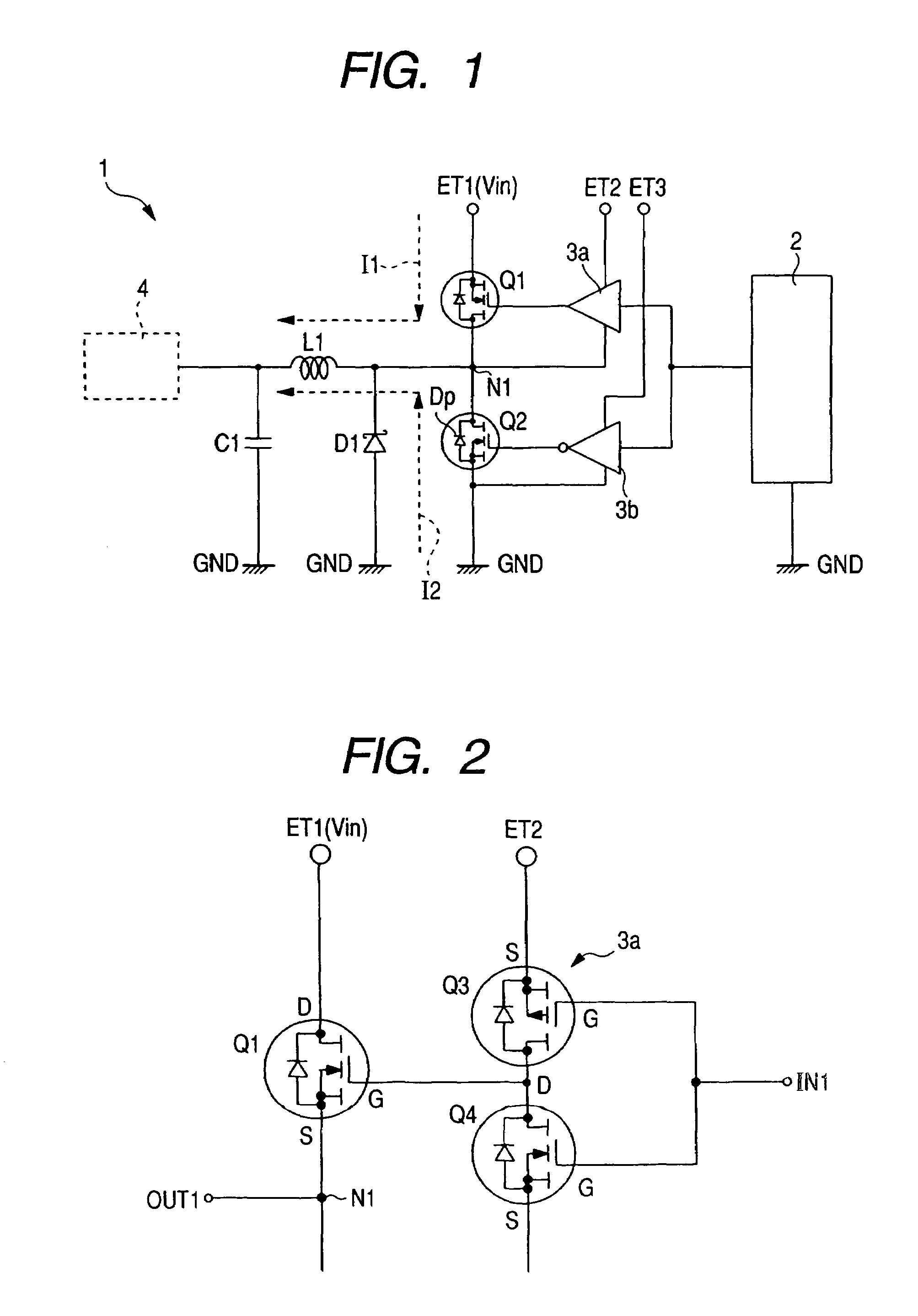

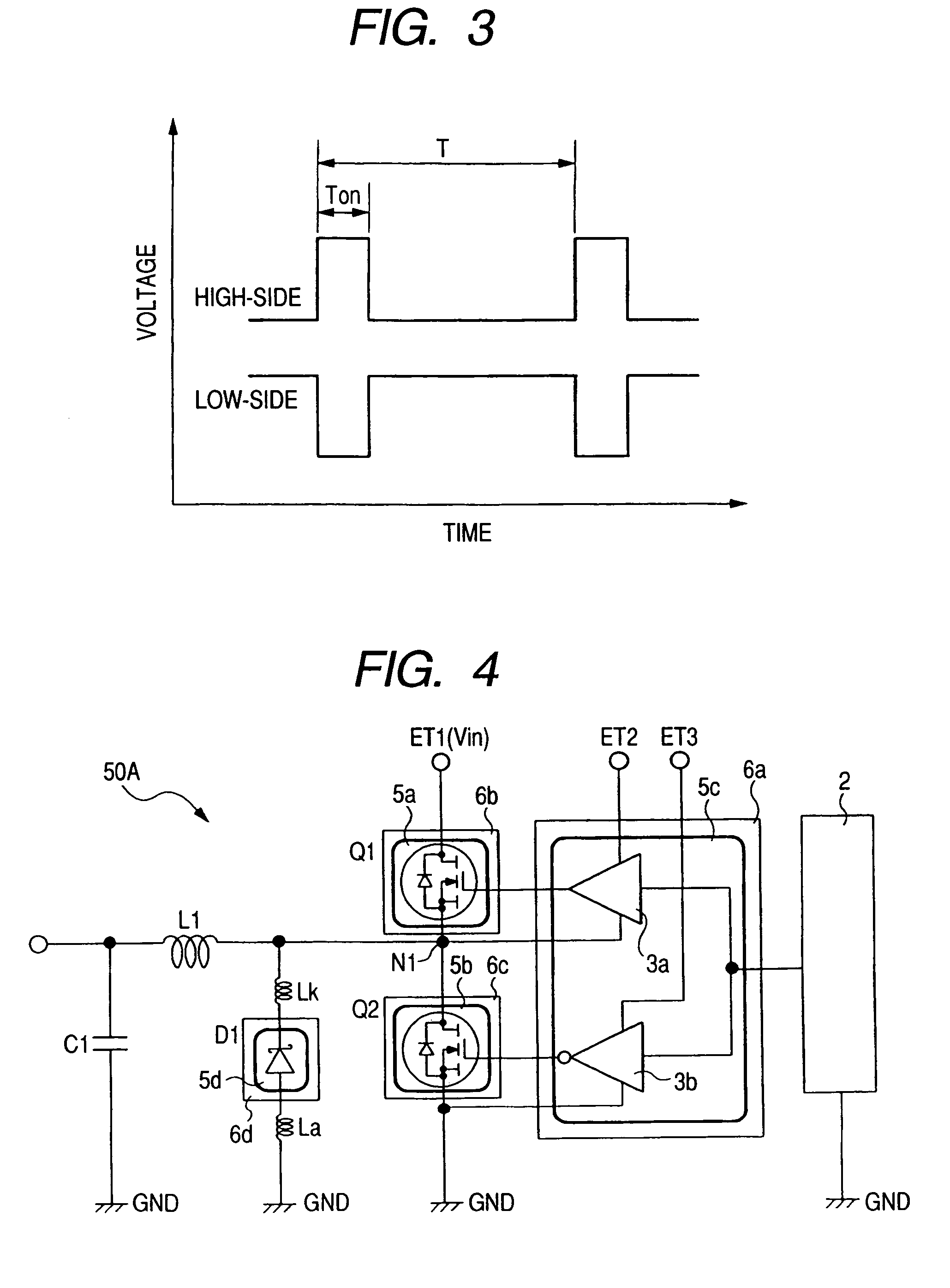

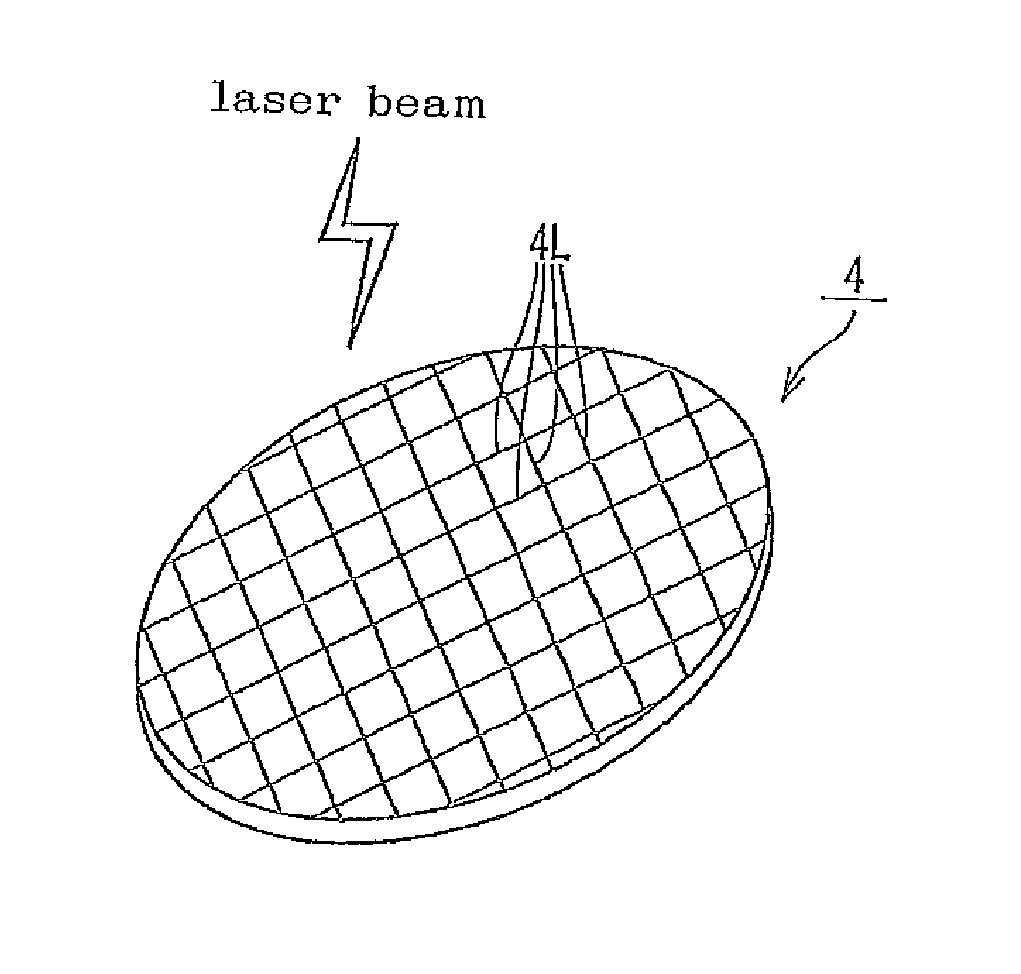

Semiconductor device

InactiveUS20050231990A1Shorten the lengthLow sectionTransistorAc-dc conversionPower semiconductor deviceDriver circuit

A non-insulated DC-DC converter a power MOS·FRT for a highside switch and a power MOS·FET for a lowside switch. In the non-insulated DC-DC converter, the power MOS·FET for the highside switch and the power MOS·FET for the lowside switch, driver circuits that control operations of these elements, respectively, and a Schottky barrier diode connected in parallel with the power MOS·FET for the lowside switch are respectively formed in four different semiconductor chips. These four semiconductor chips are housed in one package. The semiconductor chips are mounted over the same die pad. The semiconductor chips are disposed so as to approach each other.

Owner:RENESAS ELECTRONICS CORP

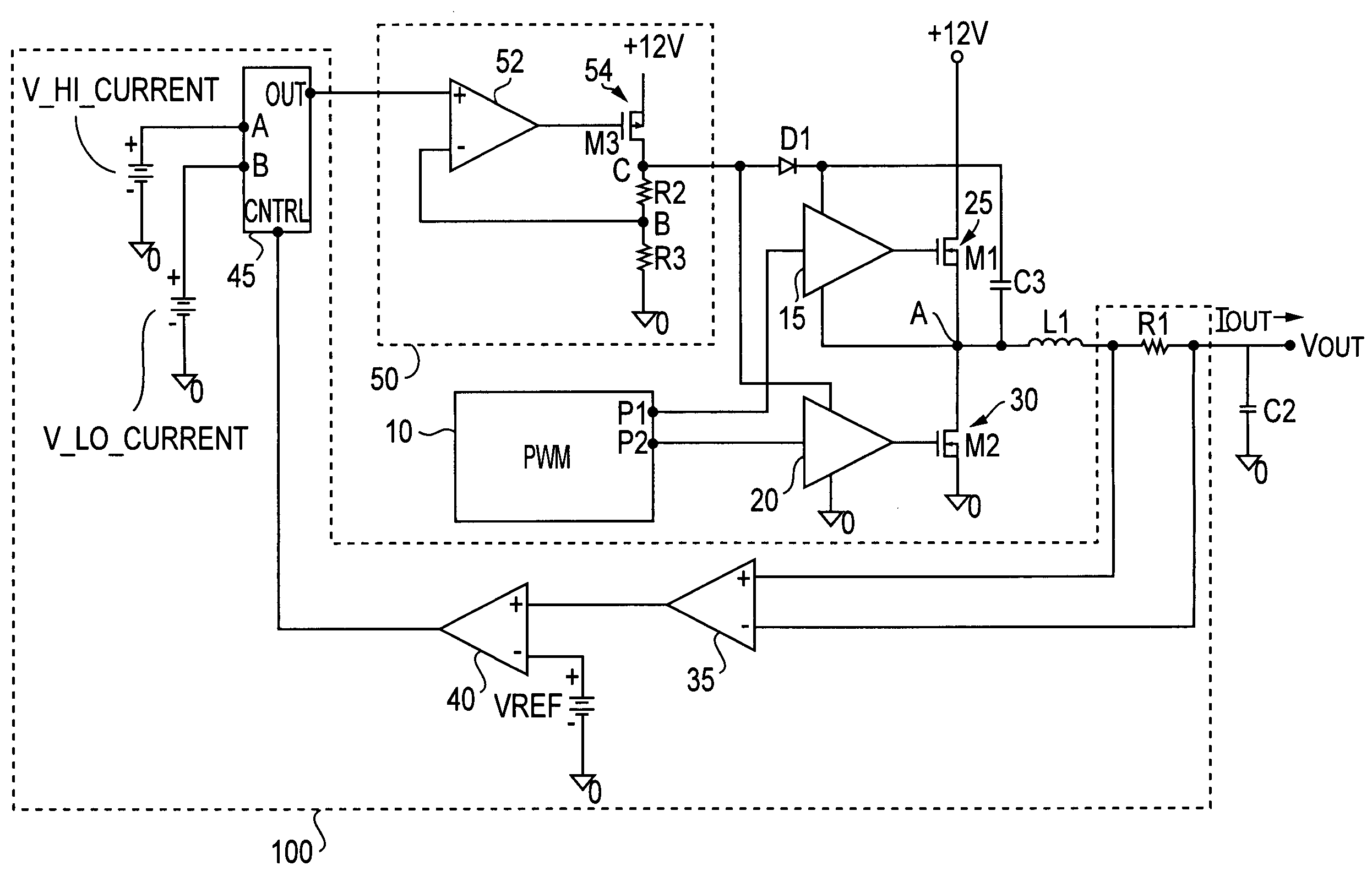

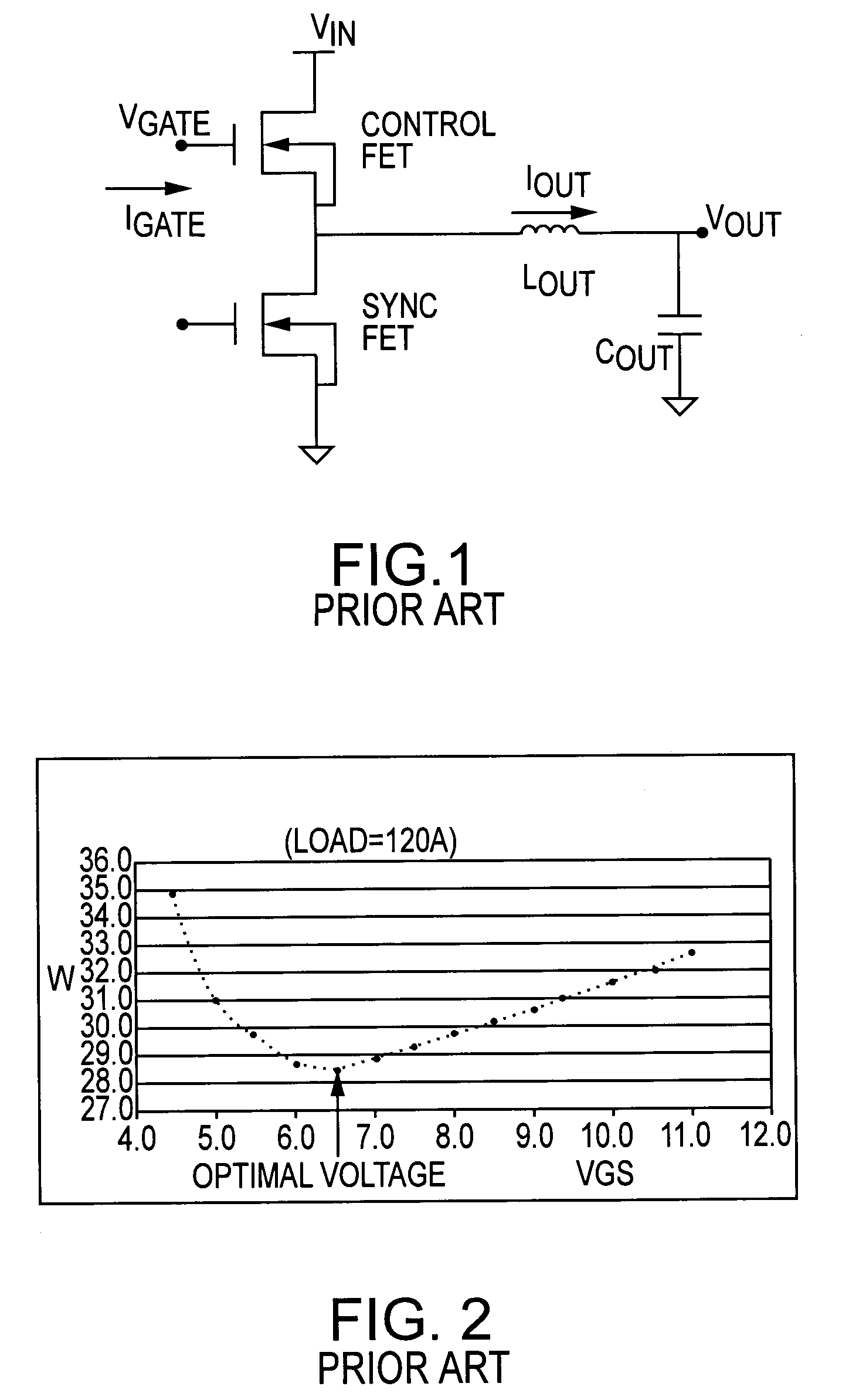

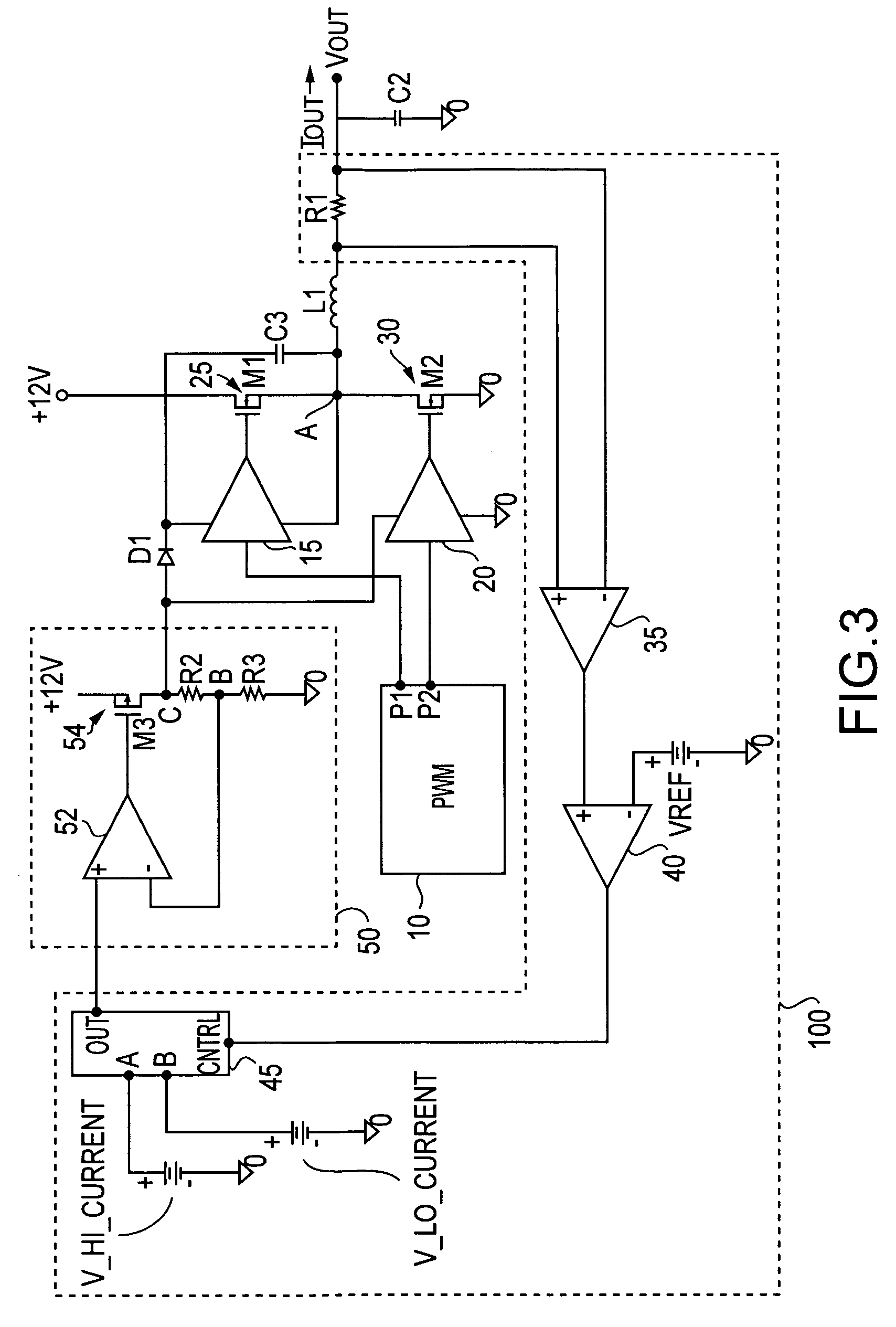

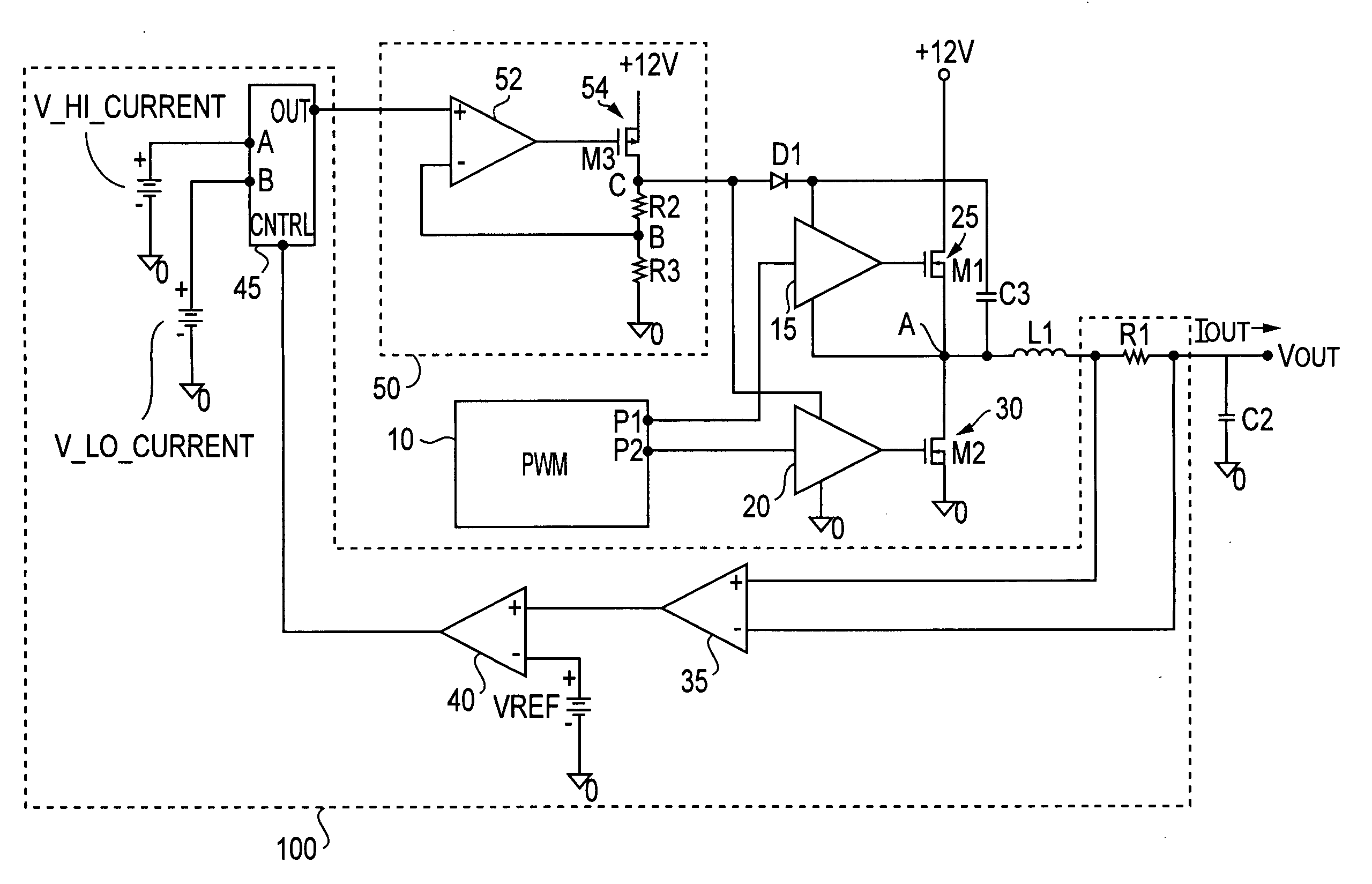

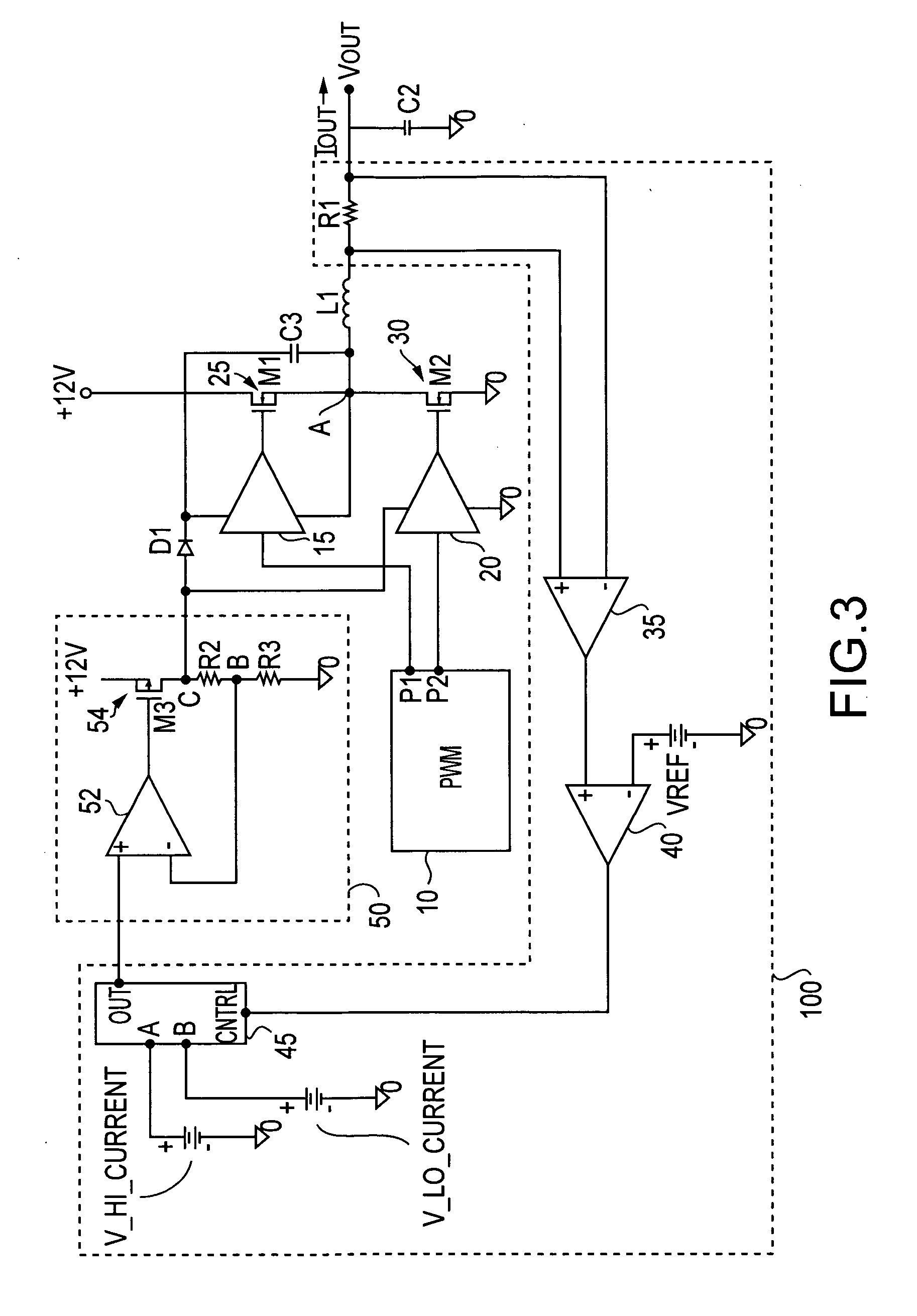

Adaptive gate drive voltage circuit

ActiveUS7265601B2Reduce lossesLower gate voltageTransistorAmplifier with semiconductor-devices/discharge-tubesEngineeringSelf adaptive

A circuit and method for reducing losses in a DC / DC converter by optimizing gate drive voltage. The circuit and method detect a change in the output load, or more specifically the output current, and adjust the gate voltage accordingly; in other words, providing adaptive gate drive voltage. In response to a reduction of output current, the invention reduces the gate voltage so as to reduce both conduction and switching losses in the semiconductor switching devices in the output stage.

Owner:INFINEON TECH AMERICAS CORP

Adaptive gate drive voltage circuit

ActiveUS20060038547A1Preventing unwanted noiseReduce power lossTransistorAmplifier with semiconductor-devices/discharge-tubesEngineeringVoltage response

A circuit and method for reducing losses in a DC / DC converter by optimizing gate drive voltage. The circuit and method detect a change in the output load, or more specifically the output current, and adjust the gate voltage accordingly; in other words, providing adaptive gate drive voltage. In response to a reduction of output current, the invention reduces the gate voltage so as to reduce both conduction and switching losses in the semiconductor switching devices in the output stage.

Owner:INFINEON TECH AMERICAS CORP

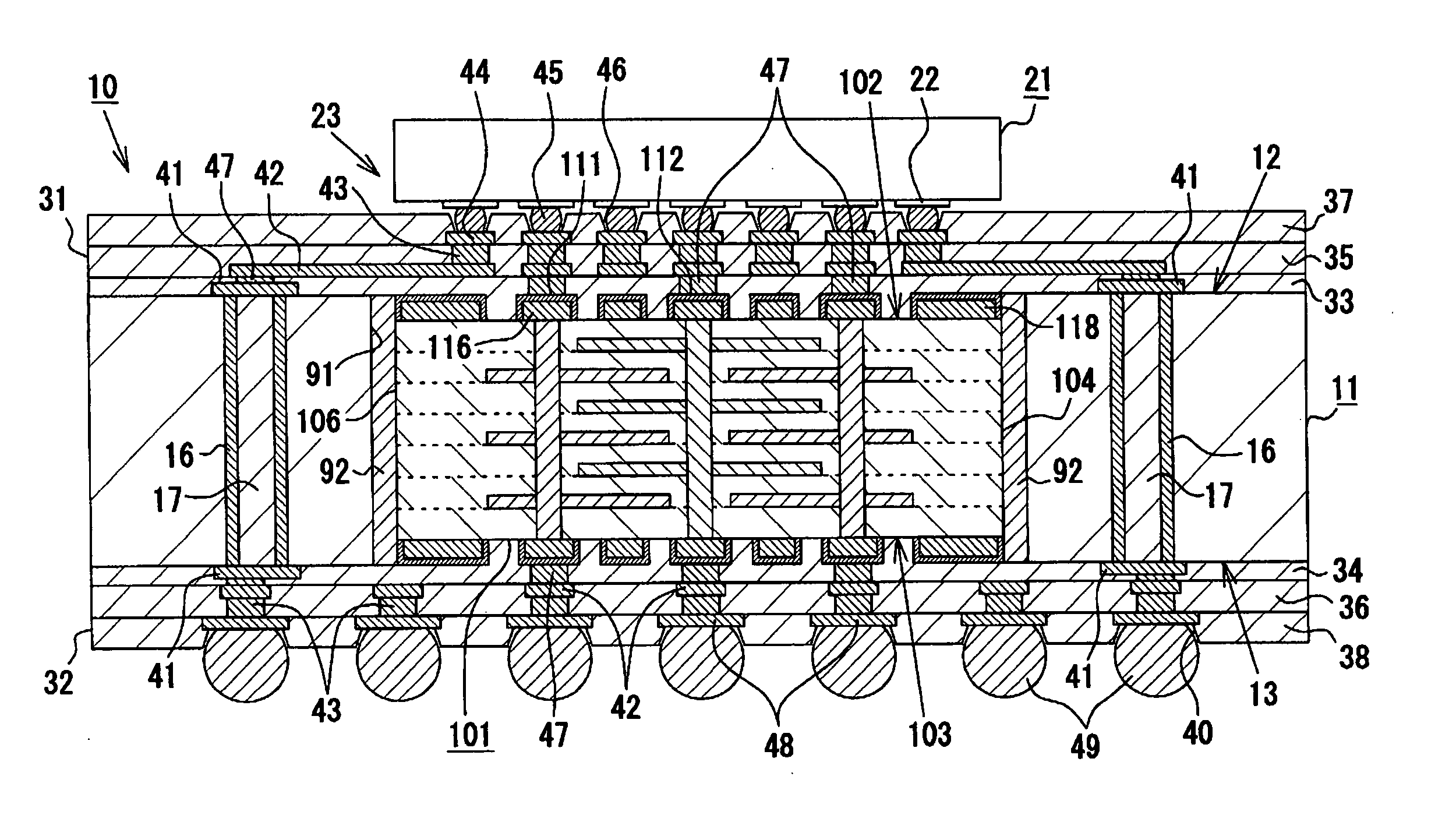

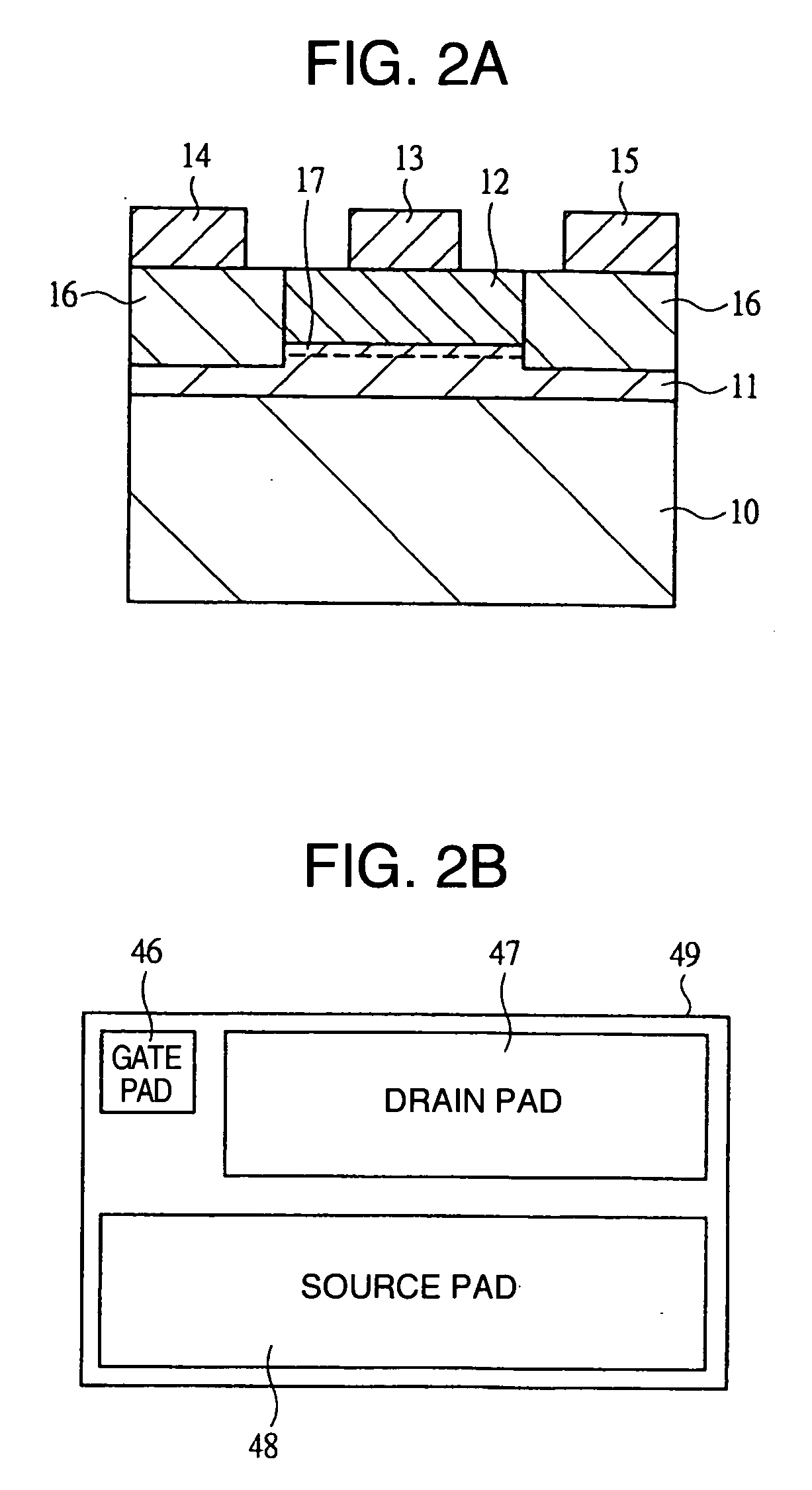

Power supply, multi chip module, system in package and non-isolated DC-DC converter

InactiveUS20060175627A1Reduce capacityLower on-resistanceEfficient power electronics conversionSemiconductor/solid-state device detailsDc dc converterComputer module

A power supply includes a non-isolated DC-DC converter for use in a power source system having a high side switch and a low side switch, in which HEMT or HFET or gallium nitride device with low capacity and low on-resistance is used for the high side switch and a vertical power MOSFET of silicon device with low on-resistance is used for the low side switch.

Owner:RENESAS TECH CORP

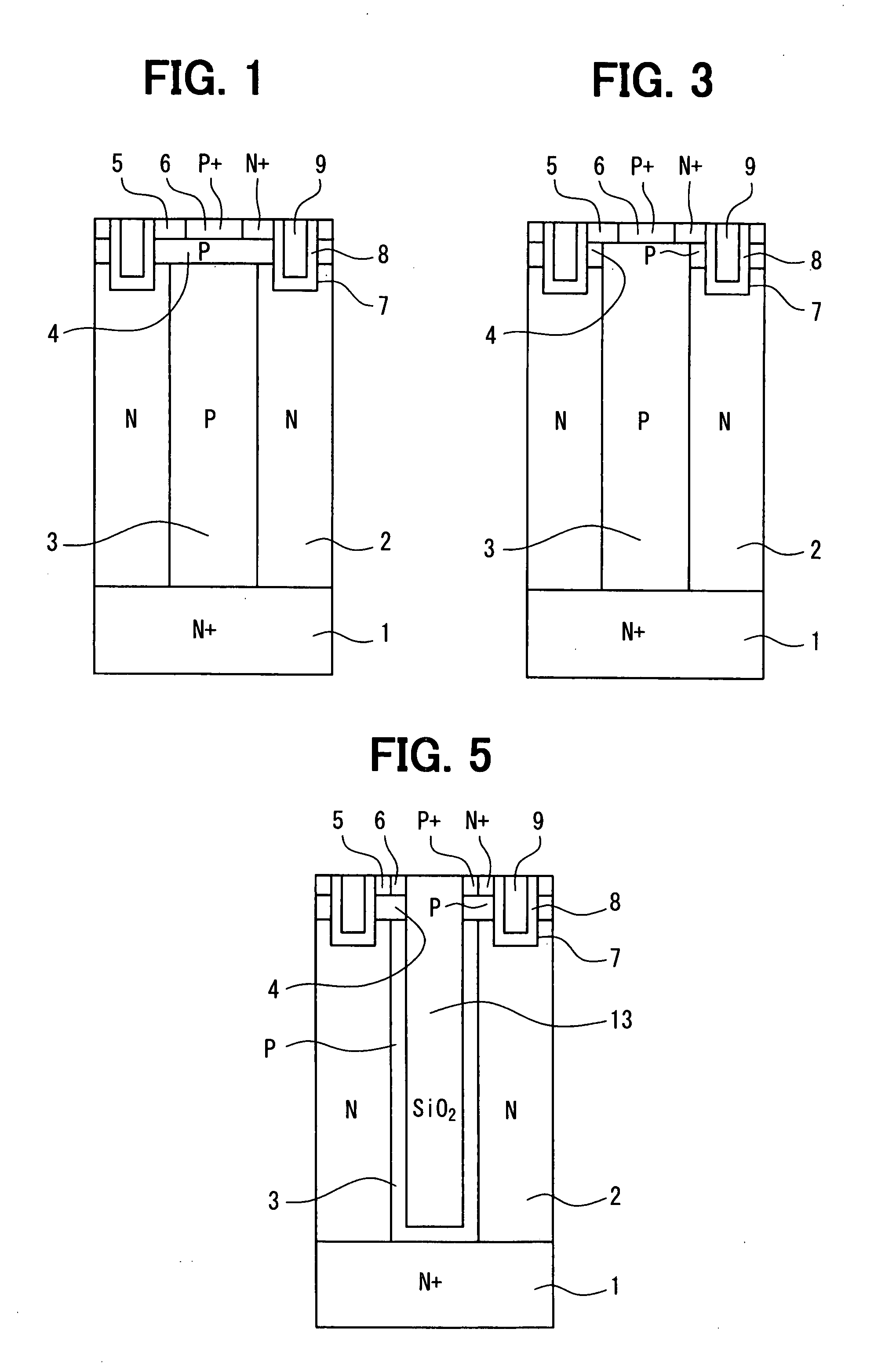

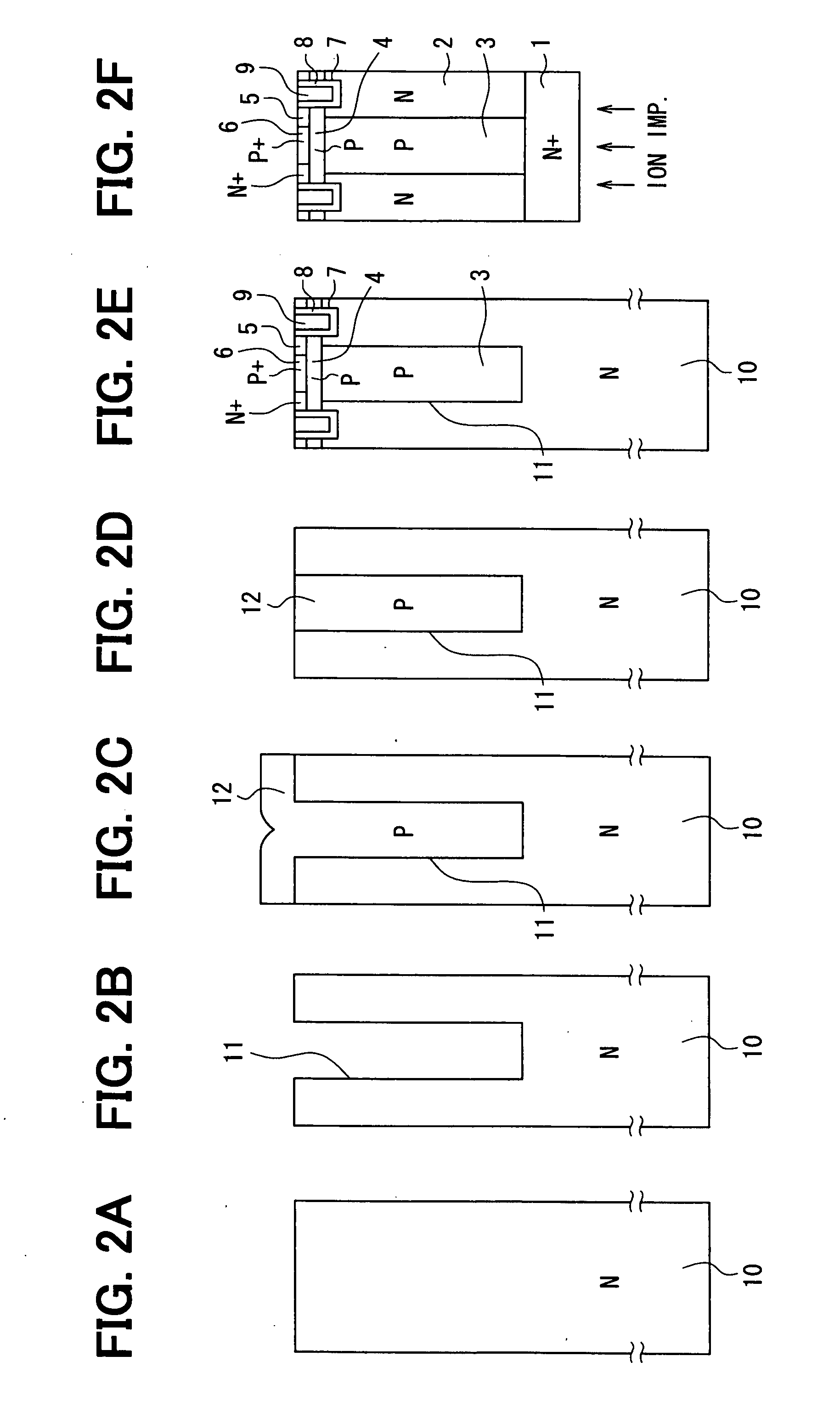

Method for manufacturing semiconductor device

ActiveUS20080038850A1Reduce manufacturing costReduce time costSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingEngineeringSemiconductor

A manufacturing method of a semiconductor device includes: forming multiple trenches on a semiconductor substrate; forming a second conductive type semiconductor film in each trench to provide a first column with the substrate between two trenches and a second column with the second conductive type semiconductor film in the trench, the first and second columns alternately repeated along with a predetermined direction; thinning a second side of the substrate; and increasing an impurity concentration in a thinned second side so that a first conductive type layer is provided. The impurity concentration of the first conductive type layer is higher than the first column. The first column provides a drift layer so that a vertical type first-conductive-type channel transistor is formed.

Owner:DENSO CORP

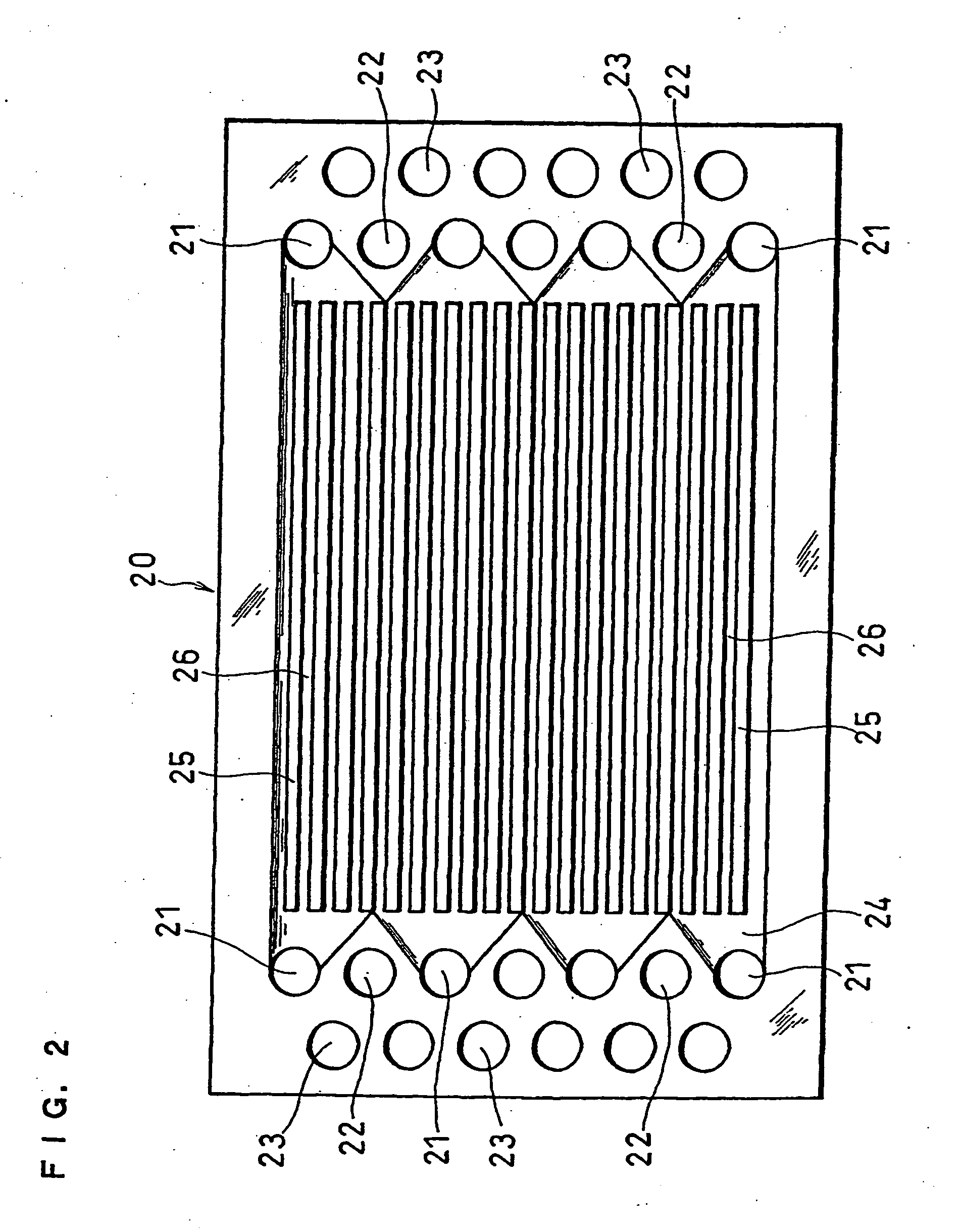

Semiconductor device

InactiveUS7436070B2Shorten the lengthImprove voltage conversion efficiencyTransistorSemiconductor/solid-state device detailsPower semiconductor deviceDriver circuit

A non-insulated DC-DC converter hs a power MOS•FRT for a highside switch and a power MOS•FET for a lowside switch. In the non-insulated DC-DC converter, the power MOS•FET for the highside switch and the power MOS•FET for the lowside switch, driver circuits that control operations of these elements, respectively, and a Schottky barrier diode connected in parallel with the power MOS•FET for the lowside switch are respectively formed in four different semiconductor chips. These four semiconductor chips are housed in one package. The semiconductor chips are mounted over the same die pad. The semiconductor chips are disposed so as to approach each other.

Owner:RENESAS ELECTRONICS CORP

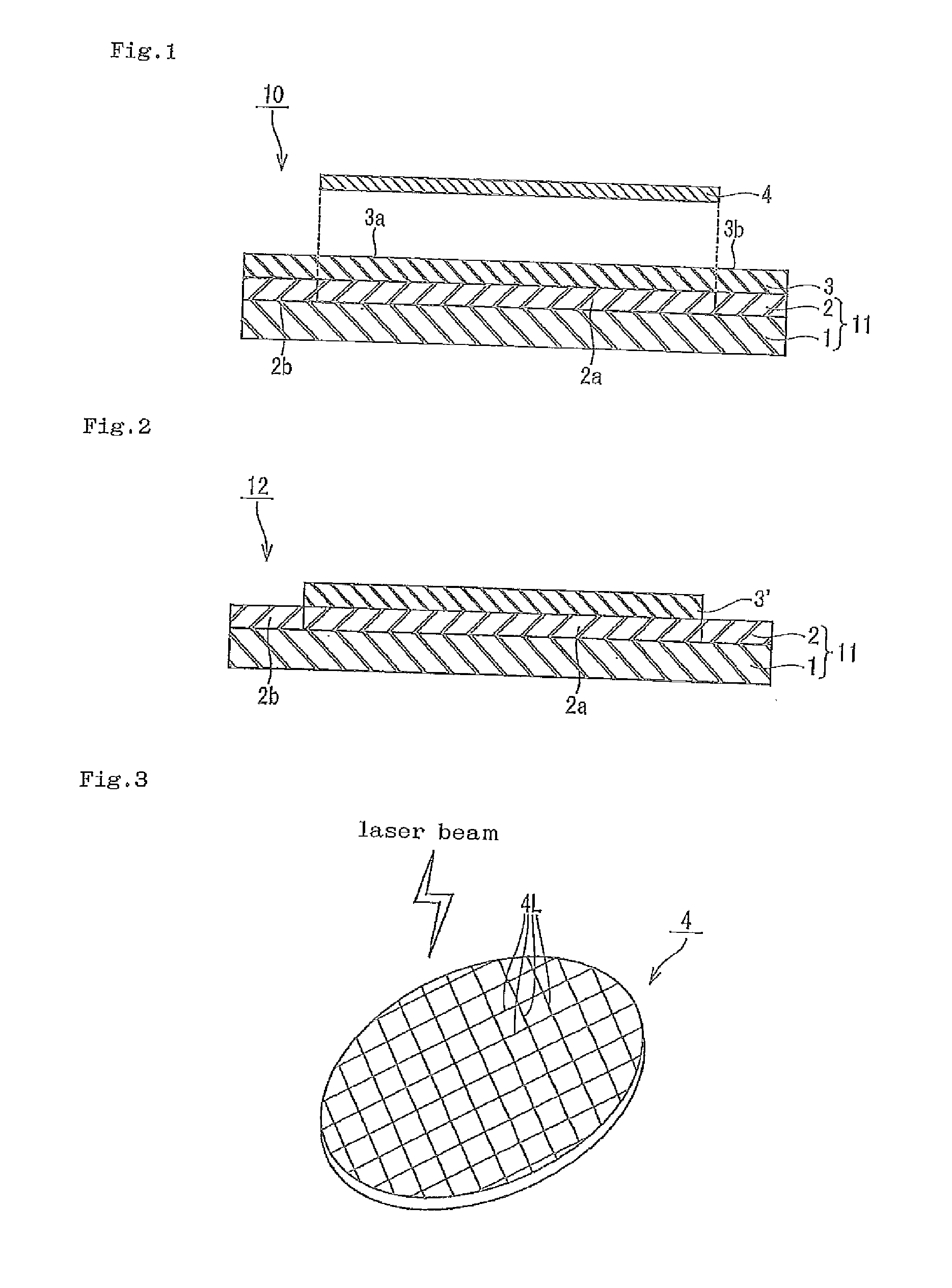

Dicing die bond film

InactiveUS20120061805A1Good tackinessImprove workabilitySemiconductor/solid-state device detailsSolid-state devicesDie bondingPolymer chemistry

The present invention provides a dicing die bond film in which peeling electrification hardly occurs and which has good tackiness and workability. The dicing die bond film of the present invention is a dicing die bond film including a dicing film and a thermosetting type die bond film provided thereon, wherein the thermosetting type die bond film contains conductive particles, the volume resistivity of the thermosetting type die bond film is 1×10−6 Ω·cm or more and 1×10−3 Ω·cm or less, and the tensile storage modulus of the thermosetting type die bond film at −20° C. before thermal curing is 0.1 to 10 GPa.

Owner:NITTO DENKO CORP

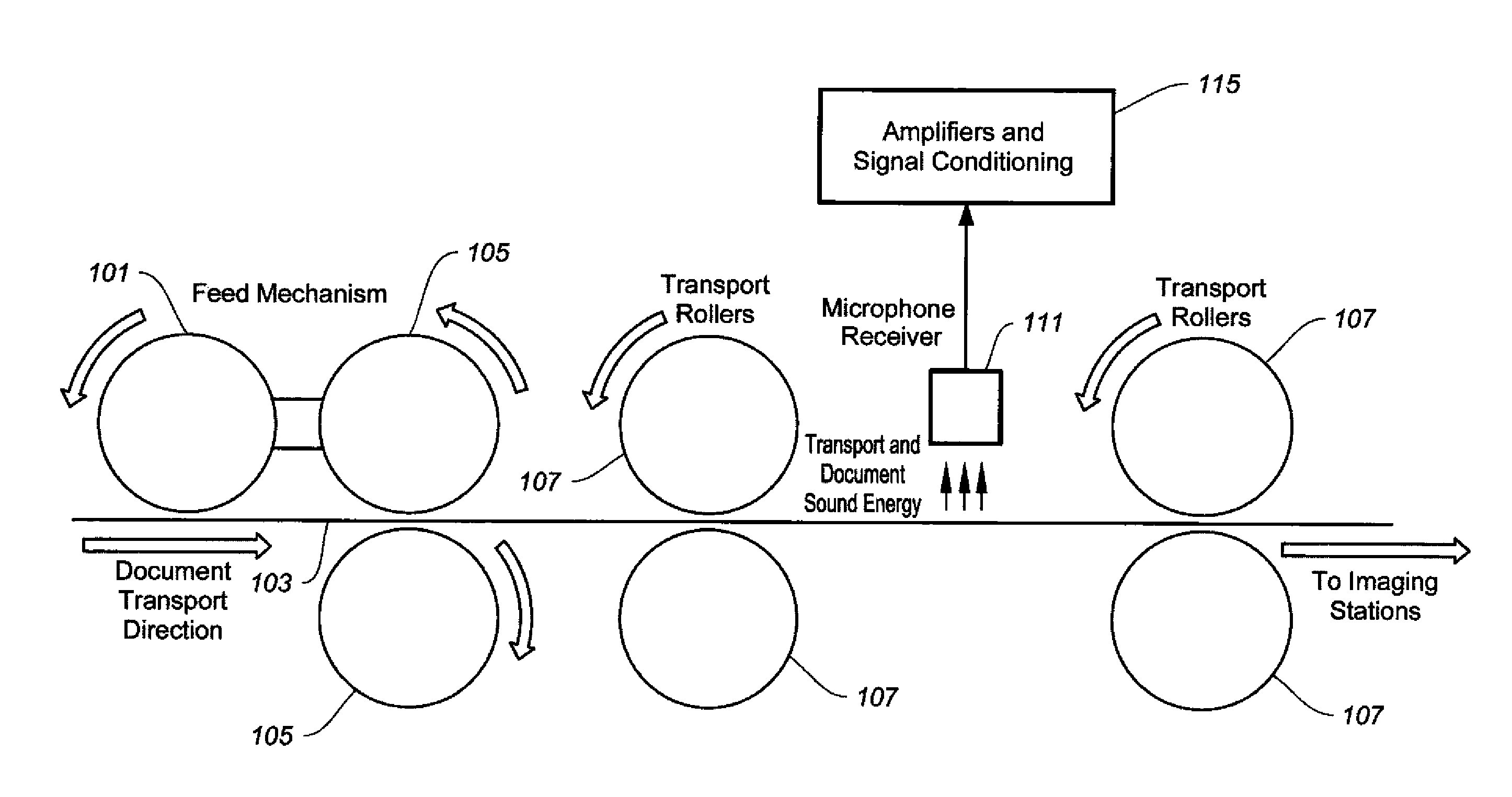

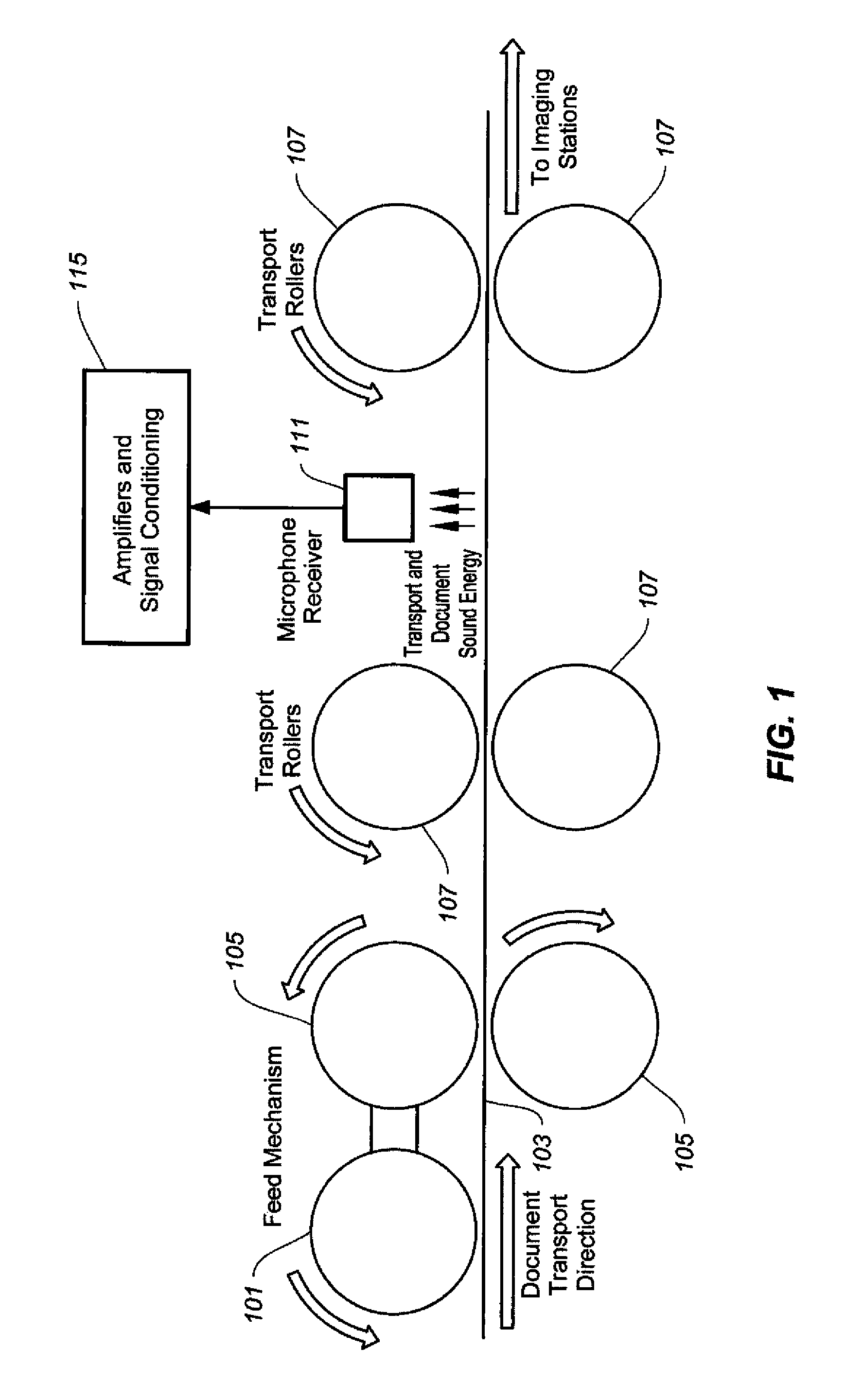

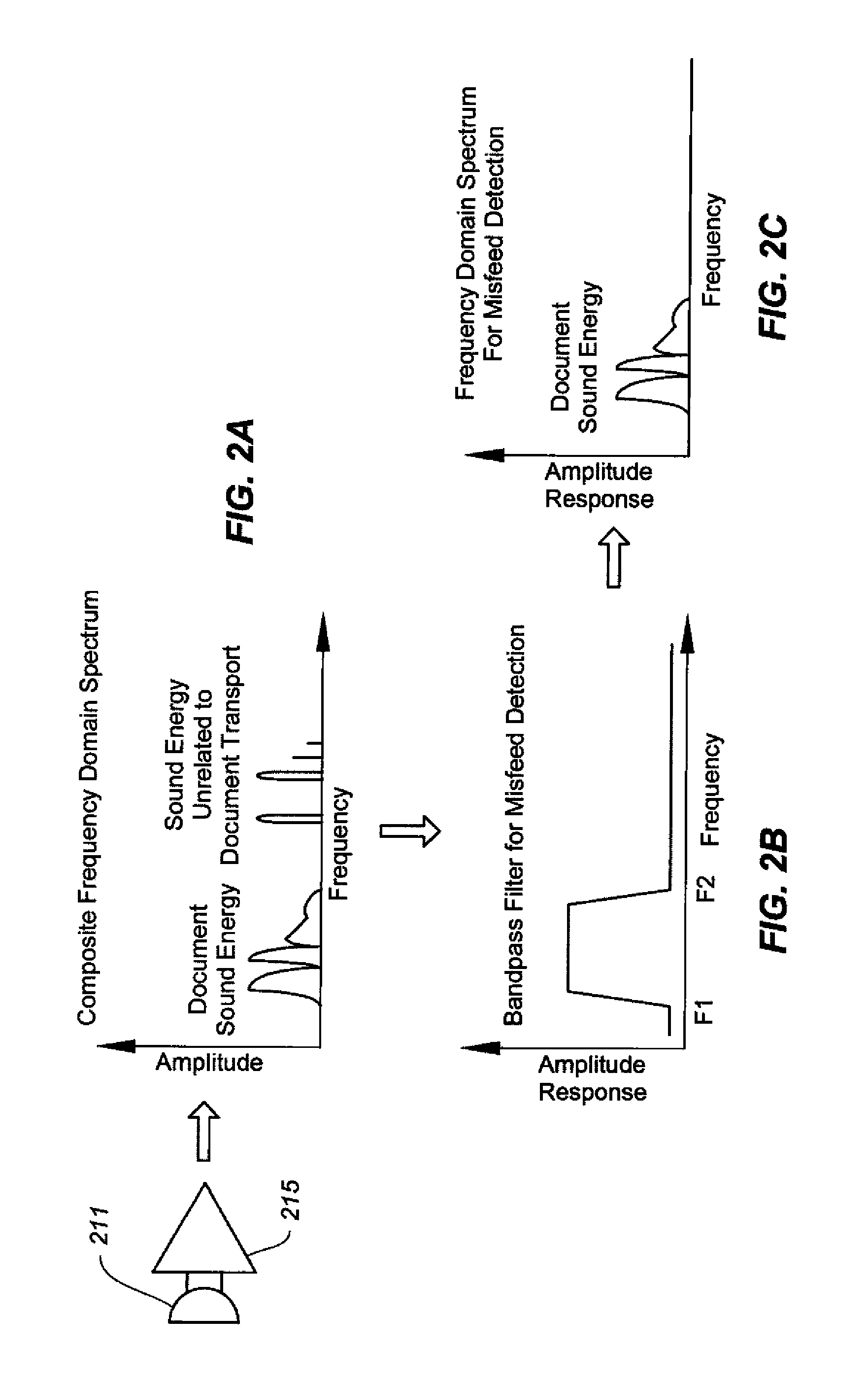

Sound-based damage detection

InactiveUS20130140757A1Conserve costSpace is at premiumFunction indicatorsElectrographic process apparatusDocument handlingPaper document

A document handling apparatus having a document transport path for moving a document therethrough. A single detector proximate the transport detects a misfeed indication in the transport path. A processing system processes the indication and issues a termination signal if a misfeed is determined.

Owner:EASTMAN KODAK CO

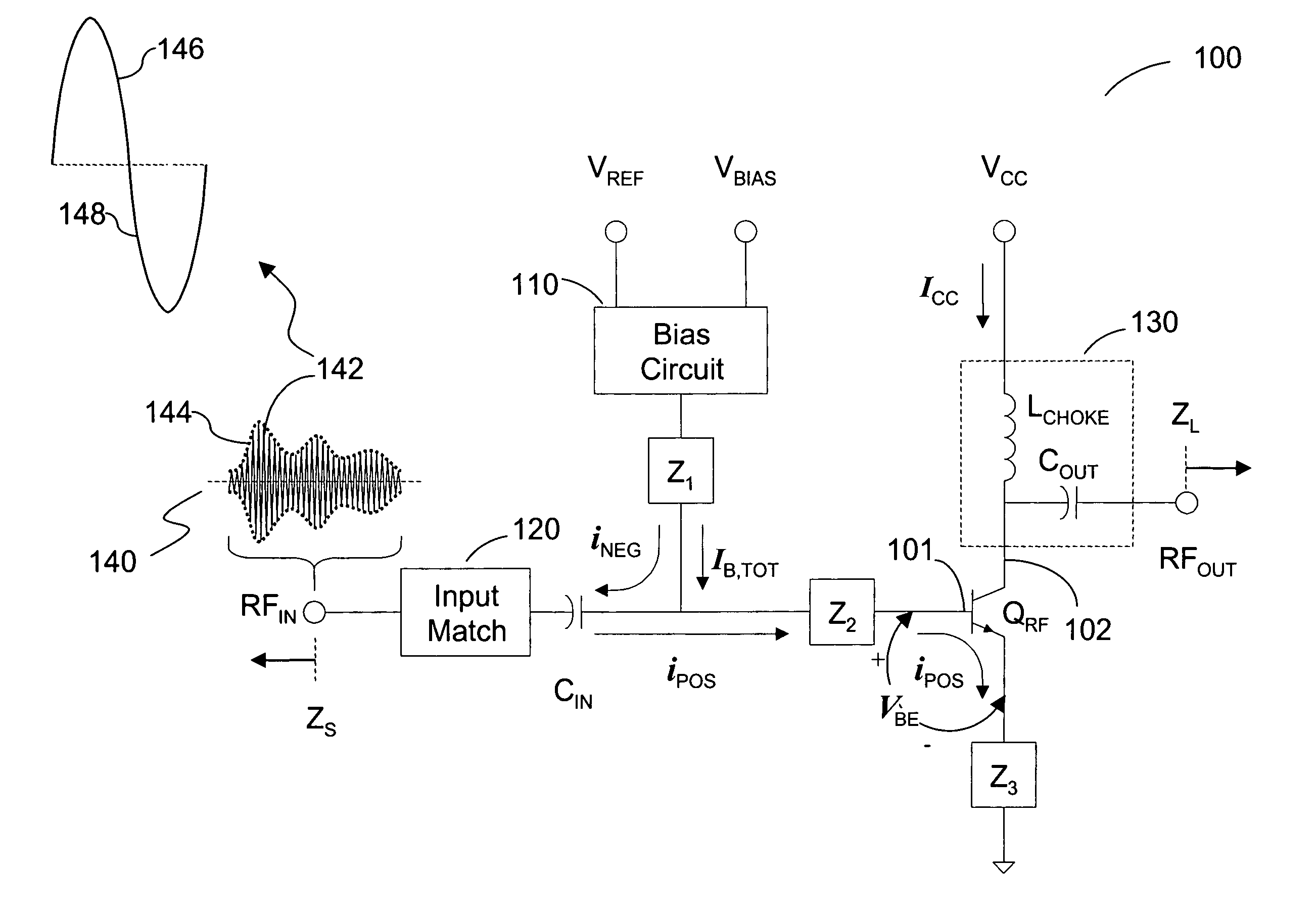

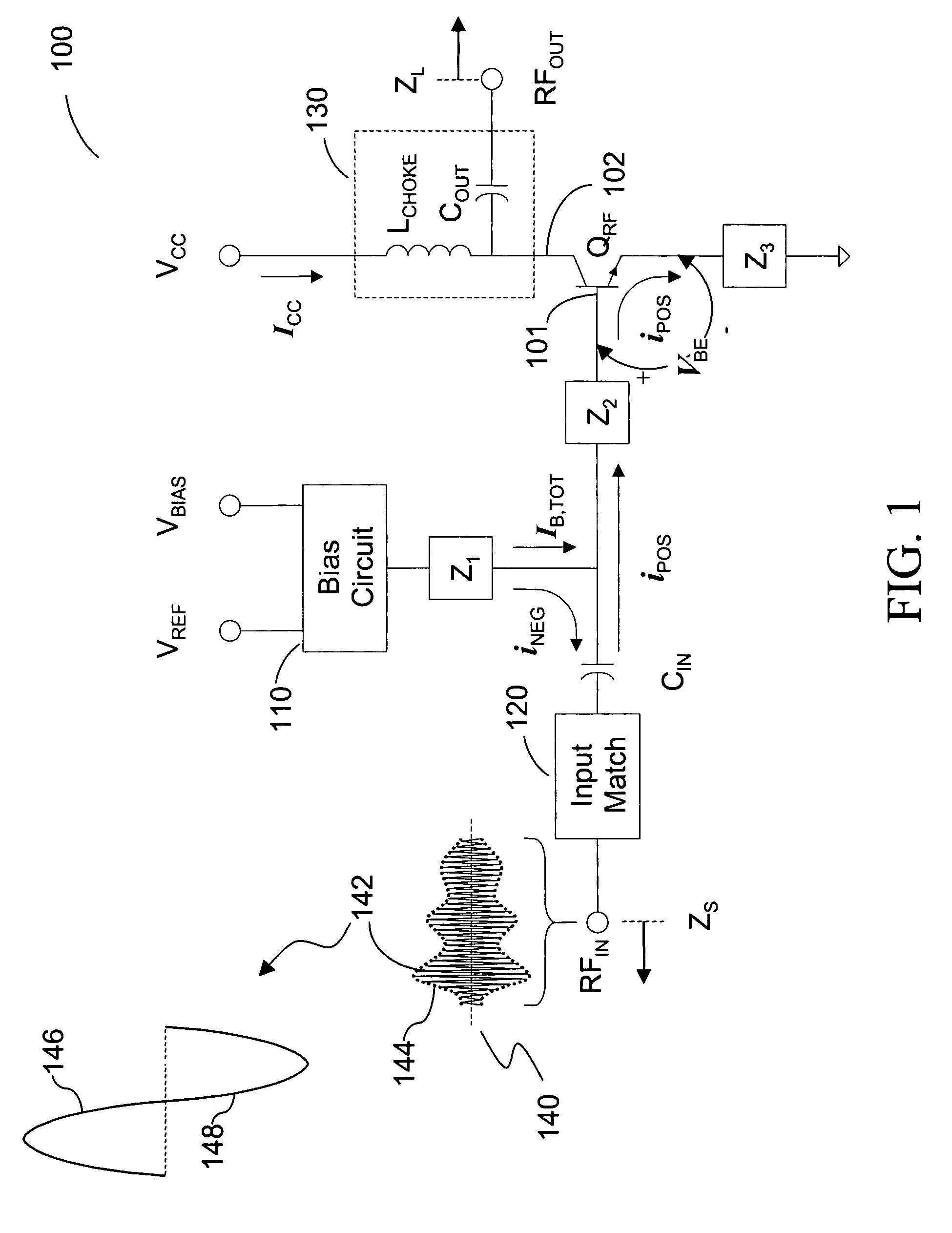

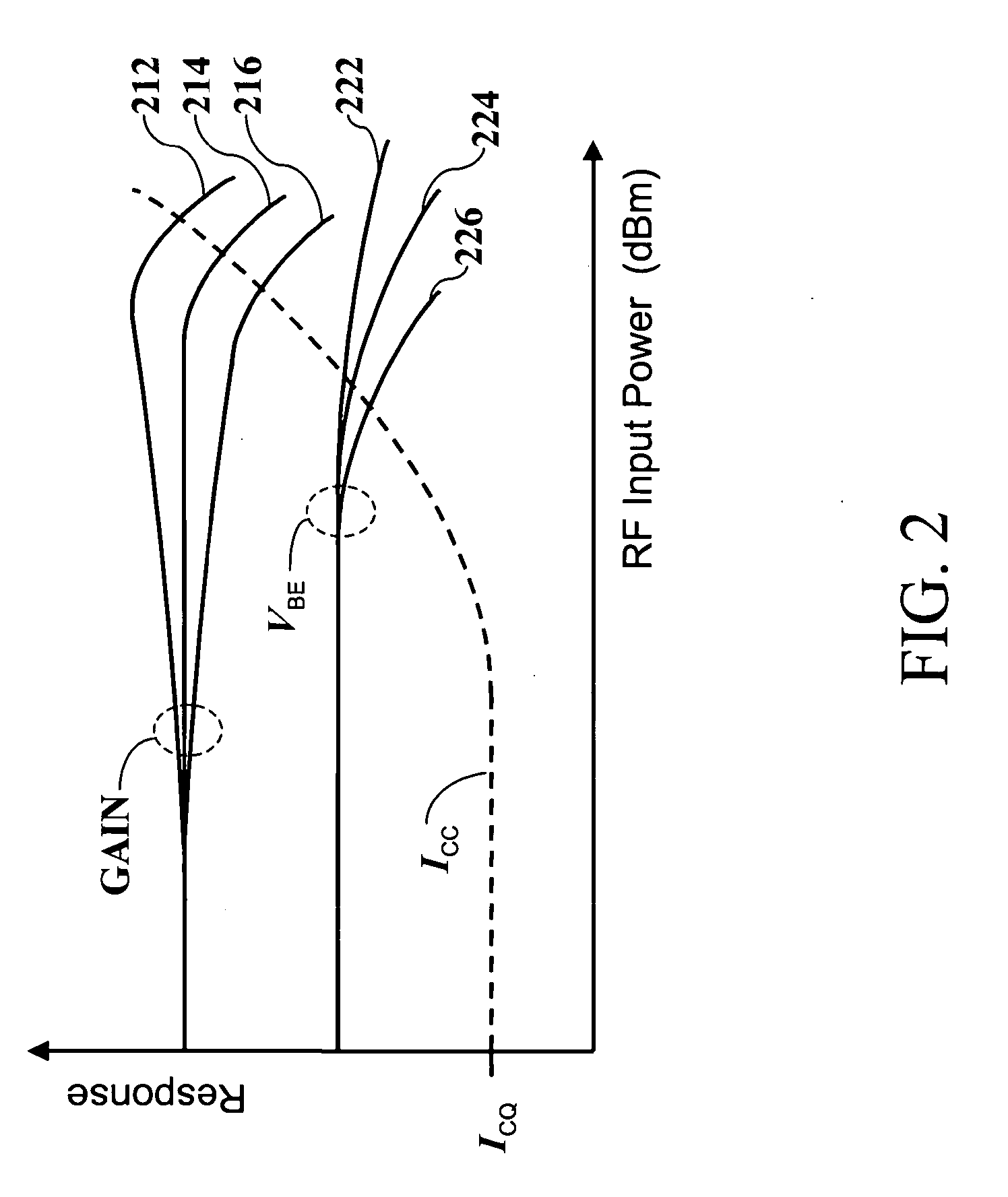

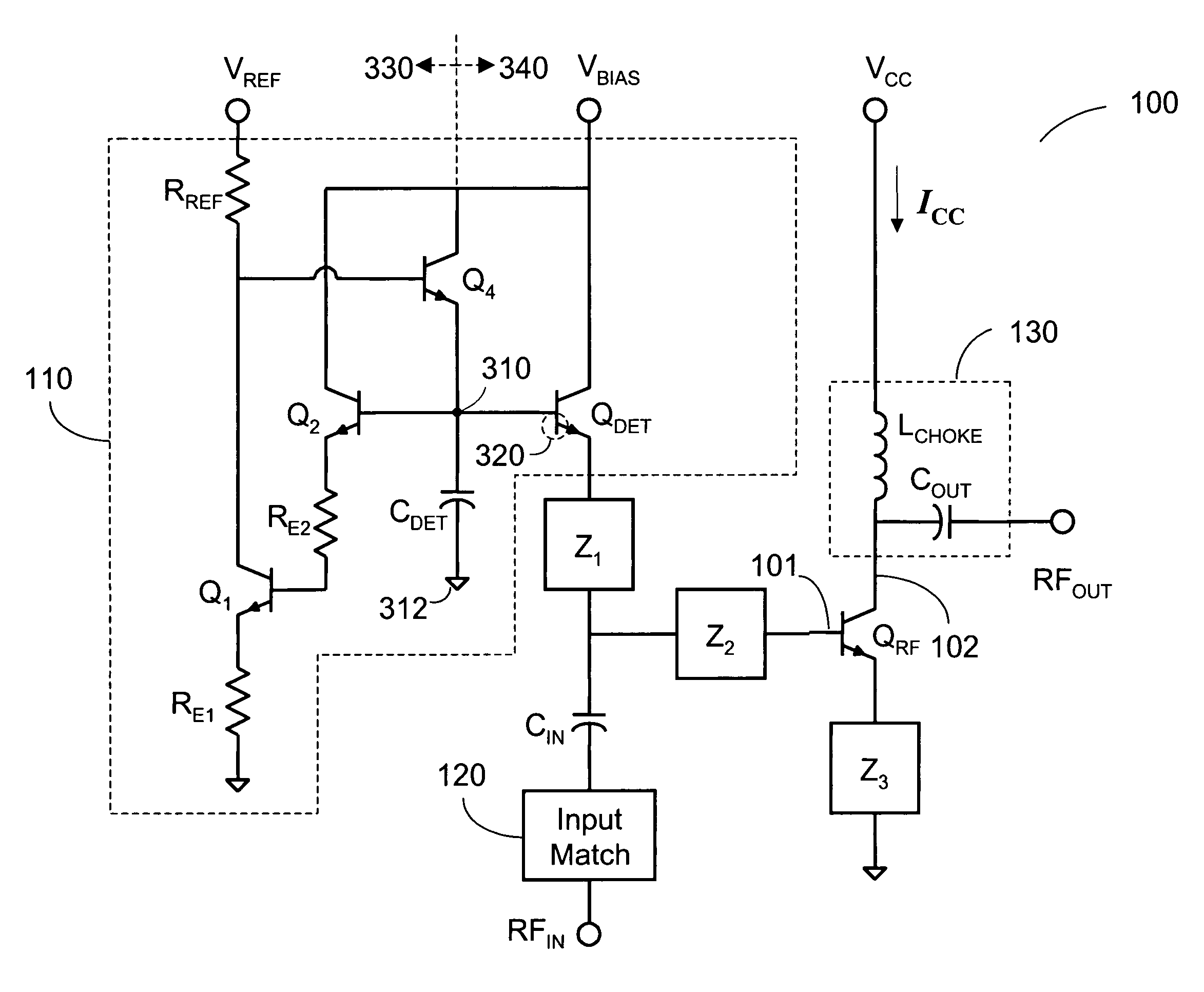

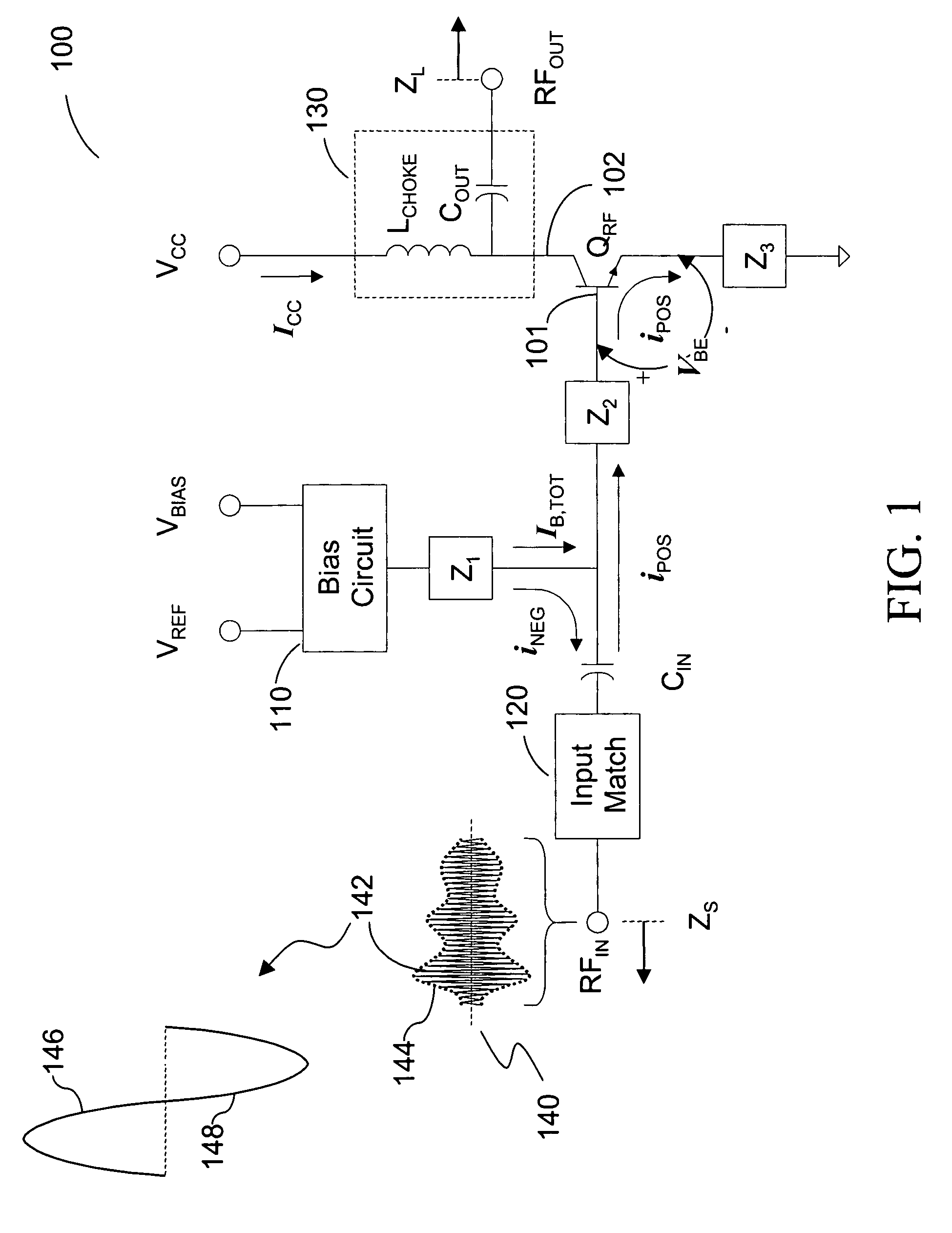

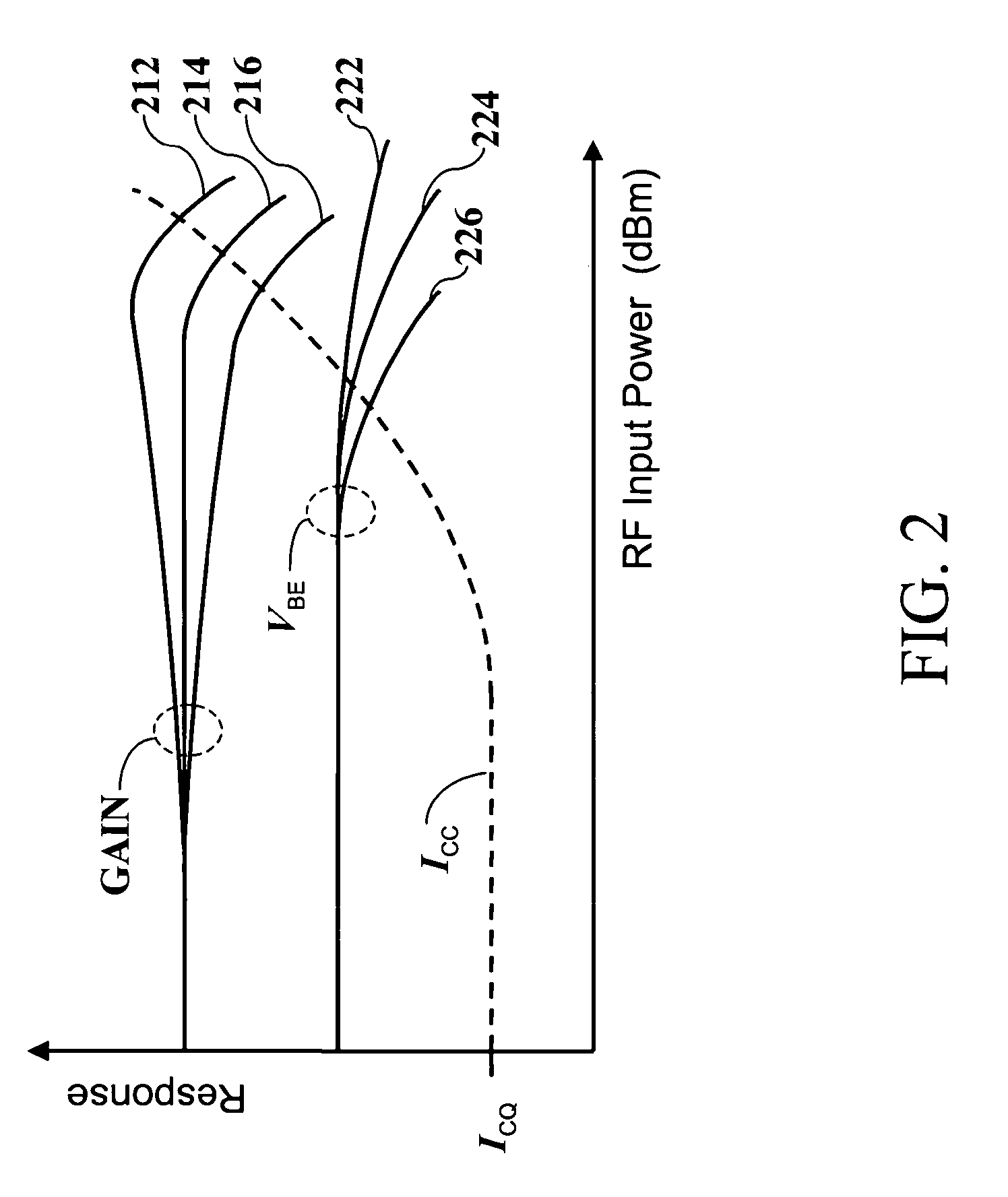

Bias circuit for BJT amplifier

ActiveUS20070096823A1Reduction in odd-order intermodulation distortionImprove efficiencyAmplifier modifications to reduce non-linear distortionGain controlTime rangeEngineering

The embodiments of the present invention include a bias circuit for a power-amplifying device, which receives and amplifies an input RF signal having a series of RF cycles within a modulation envelop. The bias circuit compensates odd-order distortion processes by detecting the power in the input signal and providing a dynamic adjustment to a bias stimulus for the power-amplifying device within a time scale of the modulation envelope.

Owner:WJ COMM

Bias circuit for BJT amplifier

ActiveUS7345547B2Low intermodulationReduce conductionAmplifier modifications to reduce non-linear distortionGain controlAudio power amplifierEngineering

The embodiments of the present invention include a bias circuit for a power-amplifying device, which receives and amplifies an input RF signal having a series of RF cycles within a modulation envelop. The bias circuit compensates odd-order distortion processes by detecting the power in the input signal and providing a dynamic adjustment to a bias stimulus for the power-amplifying device within a time scale of the modulation envelope.

Owner:WJ COMM

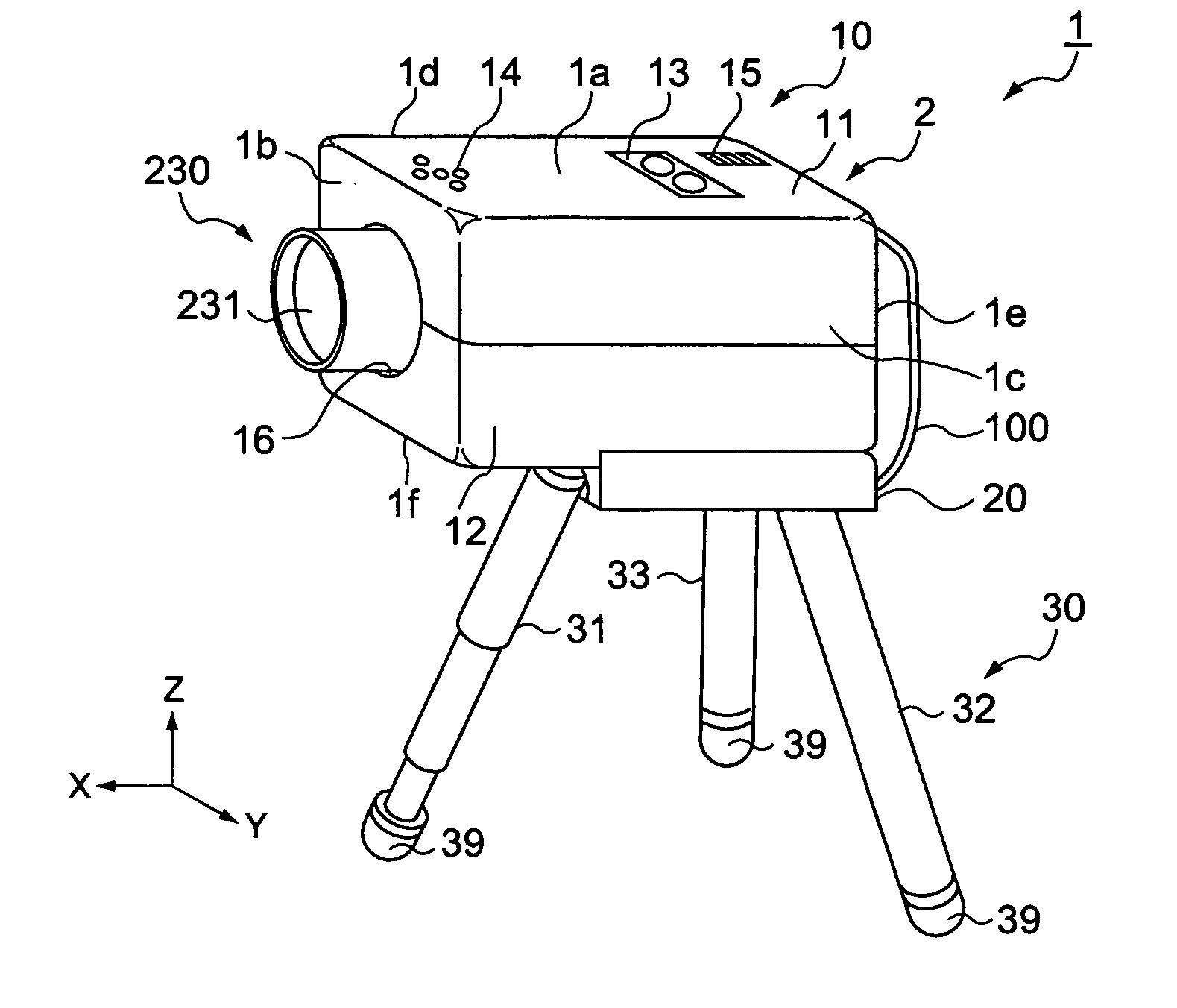

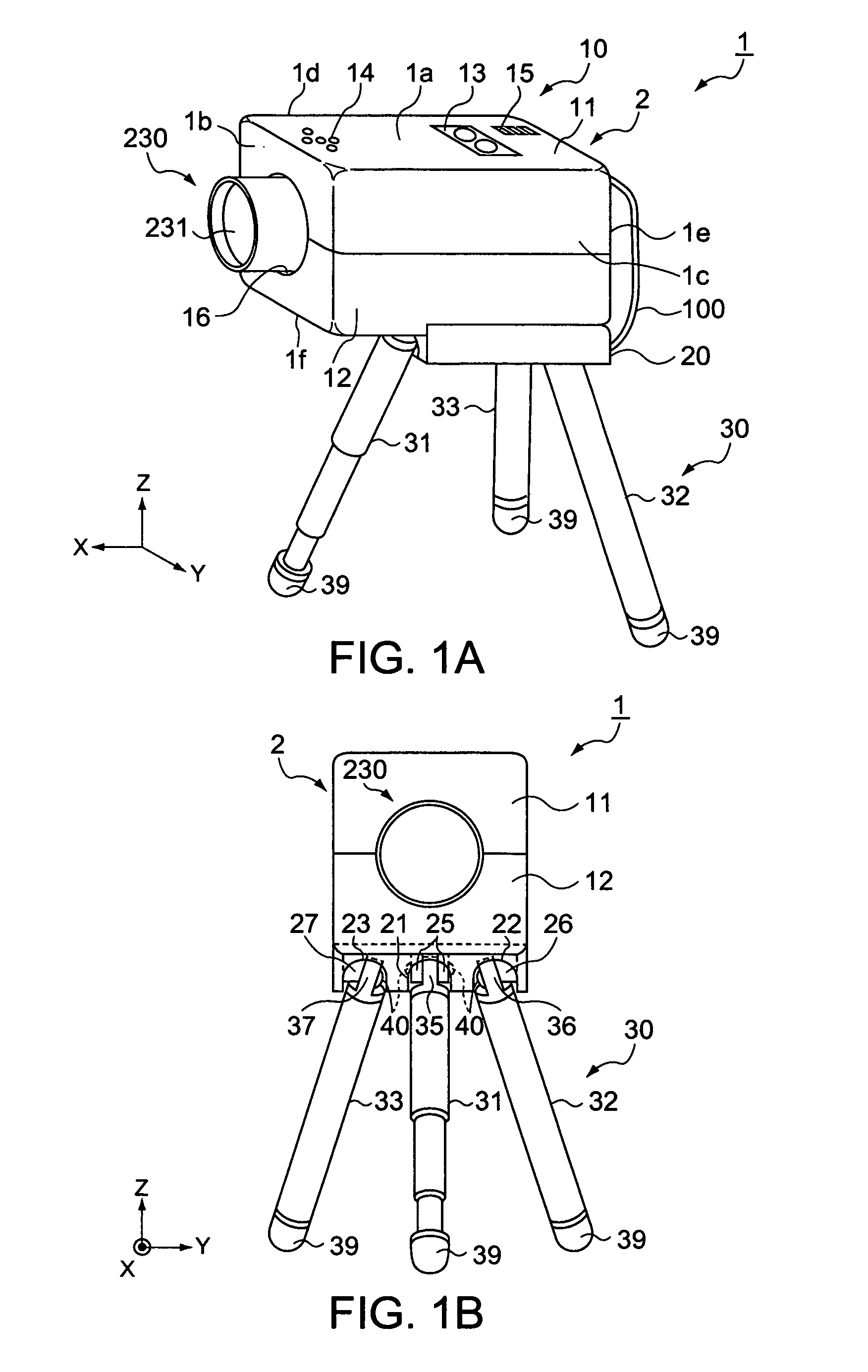

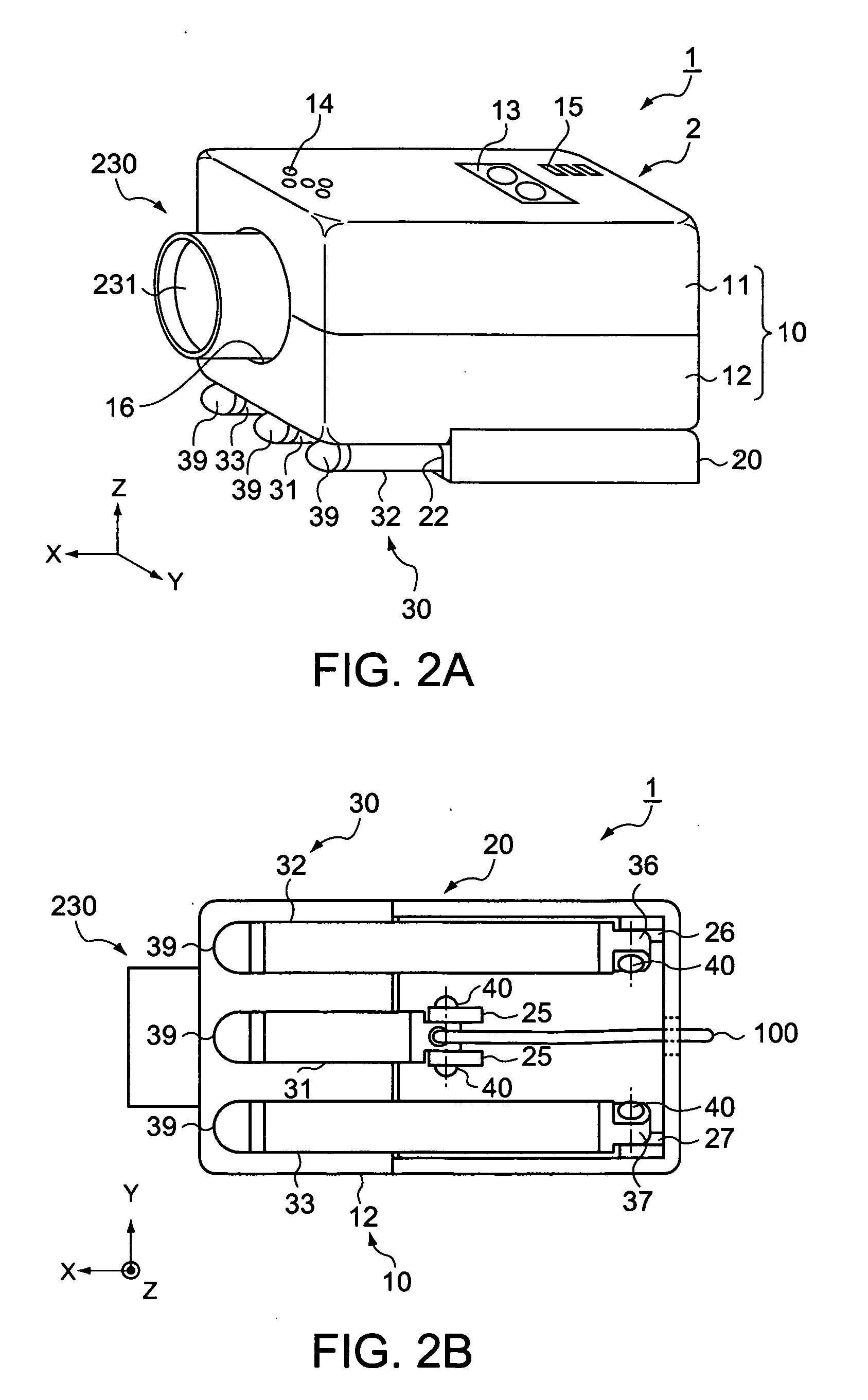

Projector

InactiveUS20060170885A1Efficient and effectiveImprove cooling efficiencyTelevision system detailsProjectorsEngineeringProjector

A projector for image projection, includes: an optical element included by an optical system to project an image; a tripod that supports the projector; and a tripod-fixing part that is connected with the optical element and fixes the tripod, wherein the tripod and tripod-fixing part are each constituted by a heat-conductive member.

Owner:SEIKO EPSON CORP

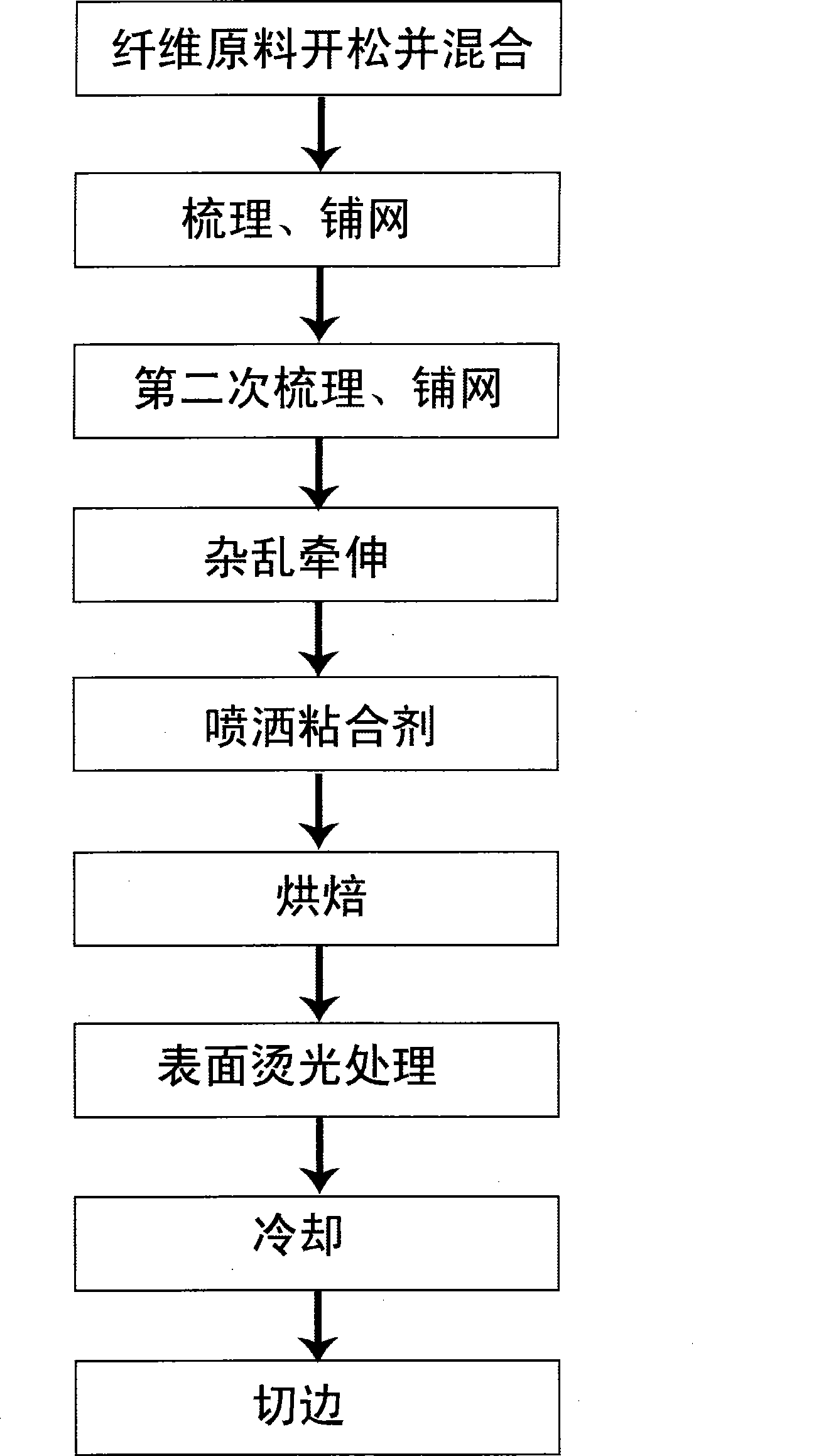

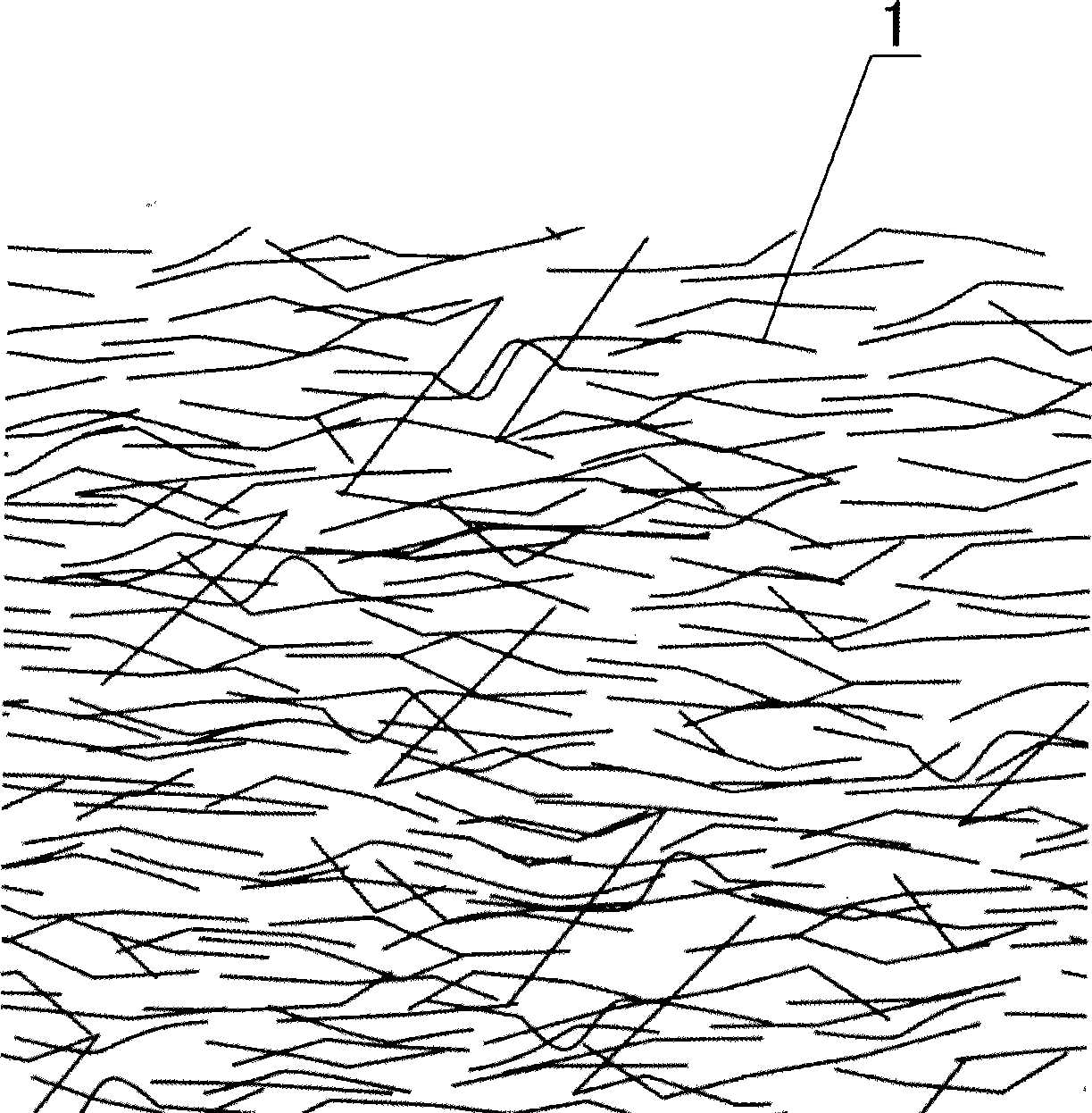

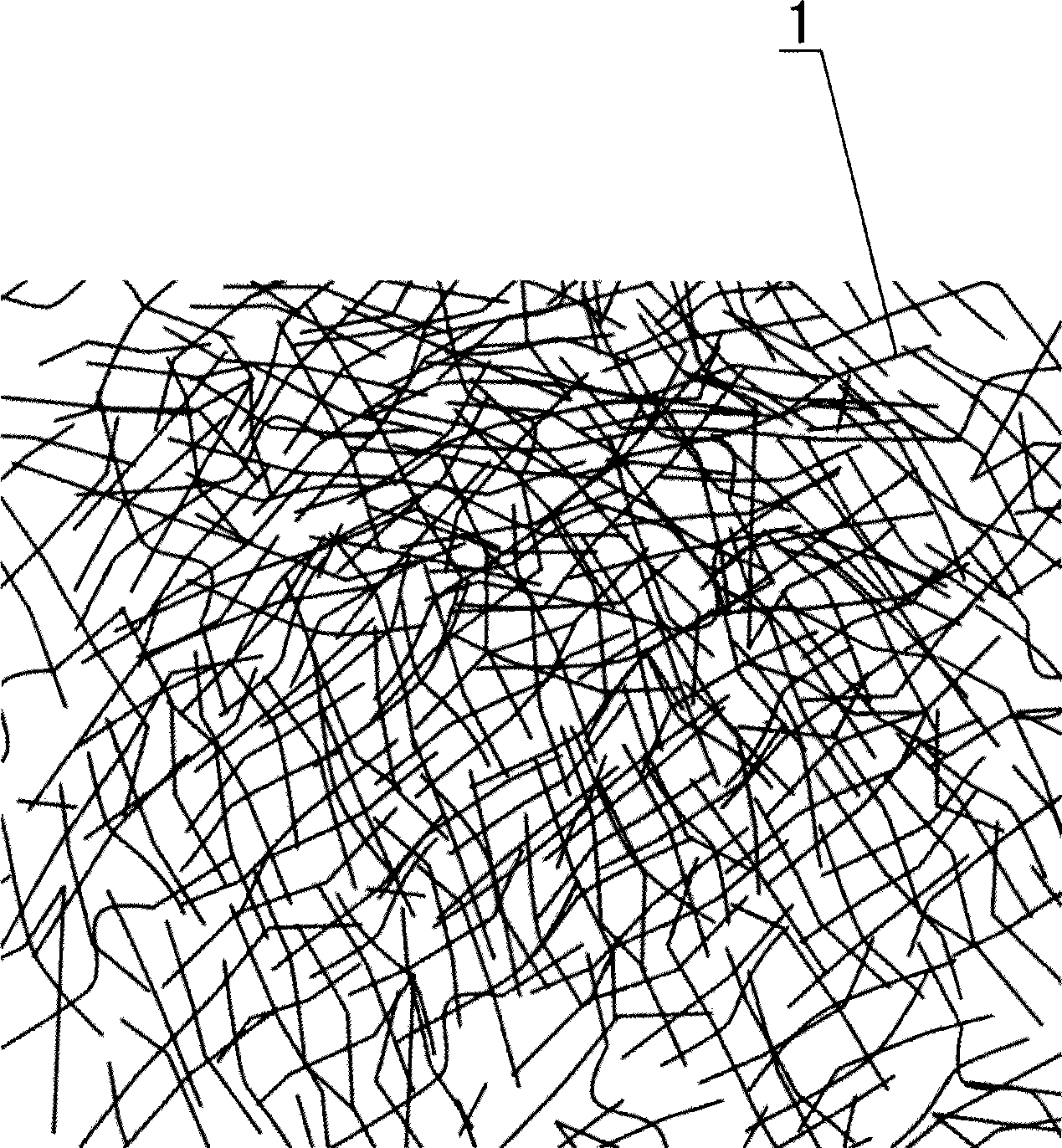

Thermal protection flocculus and manufacturing method thereof

InactiveCN101476212AReduce conductionConduction block or decreaseNon-woven fabricsAdhesivesFiberNet shape

The invention provides a keeping warm flocculus which is prepared from raw material by weight including 56%-85% fine denier fibre and / or super fine denier fibre, 0-30% hollow fibre, 5-30% felt fibre. The preparing method includes steps as follows: loosing and mixing various fibre raw material; then combing, lapping for forming fibre net; then processing disorder drafting to the felt net for forming solid net shape crossing struture; then heating and baking the felt net, at least melting surface of the felt fibre for felting surrounding fibre. The fine denier fibre can increase content of still air in the keeping warm flocculus, reduce heat quantity conduction, and can divide space in the keeping warm flocculus into smaller space for avoiding or reducing air convection, accordingly increase warm keeping property of the keeping warm flocculus; the hollow fibre can increase filling power and compress rebound property of the warm keeping flocculus; filling power and compress rebound property of the warm keeping flocculus are increased after being disorder draft.

Owner:汕头市奥山服饰有限公司

Semiconductor device, method for manufacturing the same, liquid crystal television and EL television

InactiveUS20050214983A1Improve usabilityReduce violationsTransistorSolid-state devicesDevice materialEngineering

A method for manufacturing a semiconductor device by a small number of processes and by a means with high usability of materials to have high-definition and a gate insulating with a high step coverage property is disclosed. According to the present invention, a method for manufacturing a semiconductor device comprises the steps of forming a plurality of first conductive layers over a substrate; forming a first insulating layer to fill the gaps of the plurality of the first conductive layers; forming a second insulating layer over the first insulating layer and the plurality of the first conductive layers; and forming a semiconductor region and a second conductive layer over the second insulating layer.

Owner:SEMICON ENERGY LAB CO LTD

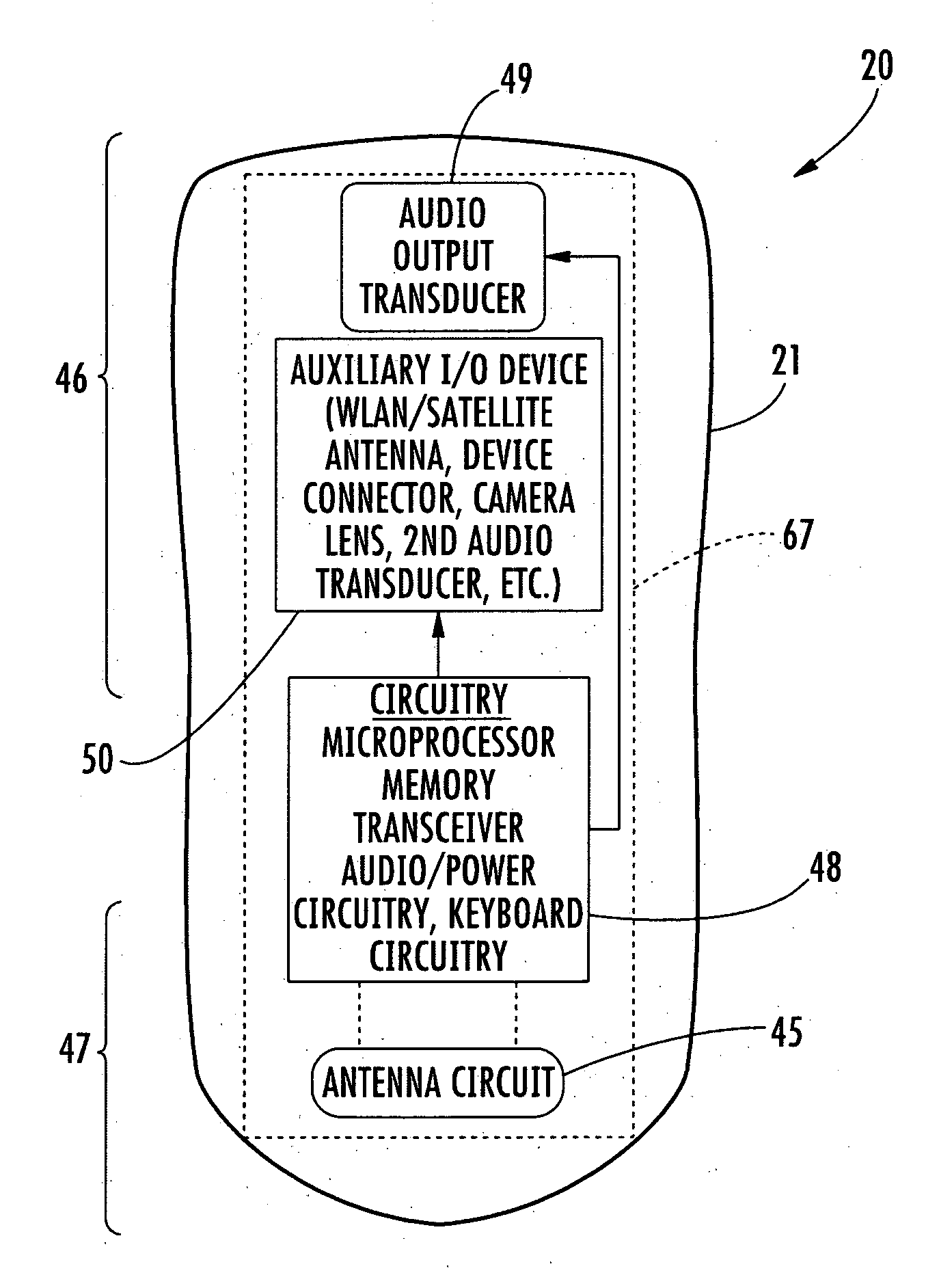

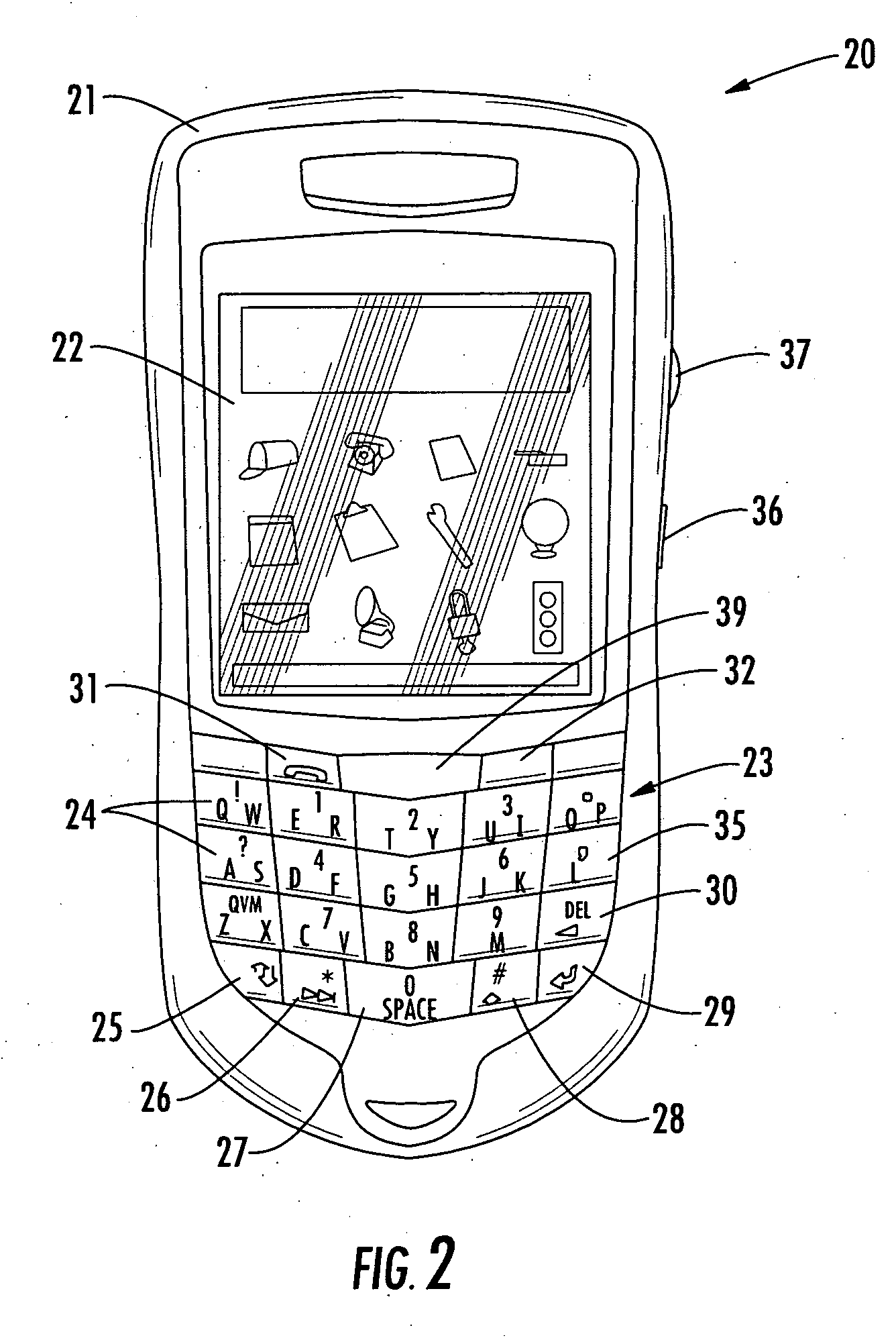

Mobile wireless communications device with reduced interfering energy into audio circuit and related methods

ActiveUS20060068856A1Reduce interference energyReduce conductionEnergy efficient ICTSubstation equipmentLoudspeakerAudio frequency

A mobile wireless communications device includes a housing and circuit board carried by the housing. RF circuitry and a processor are operative with each other and carried by the circuit board. A receiver speaker and microphone are carried by the housing. Audio circuitry is carried by the circuit board and operative with the RF circuitry and processor. A microphone audio switch and receiver speaker audio switch are carried by the circuit board and are connected with audio connection lines that interconnect the processor. A filter is operative with the audio connection lines and operatively connected to at least one of the microphone audio switch or receiver speaker audio switch to reduce conducted and radiated interfering RF energy from coupling into the audio circuitry.

Owner:MALIKIE INNOVATIONS LTD