PCIE exchange chip port configuration system and method supporting virtual exchange

A technology of virtual switching and switching chips, applied in the field of PCIE switching chips, which can solve problems such as conflicts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

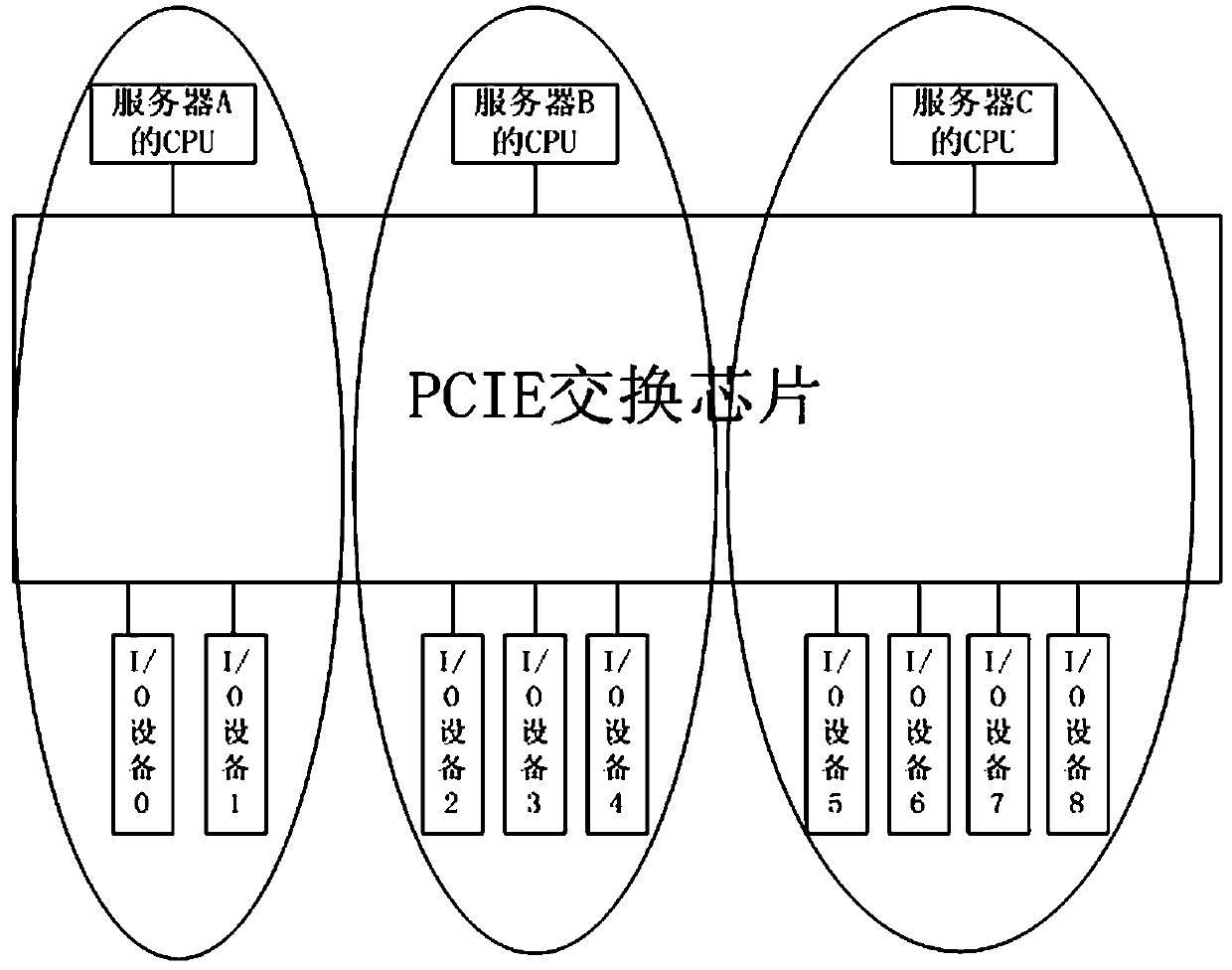

Problems solved by technology

Method used

Image

Examples

Embodiment 1

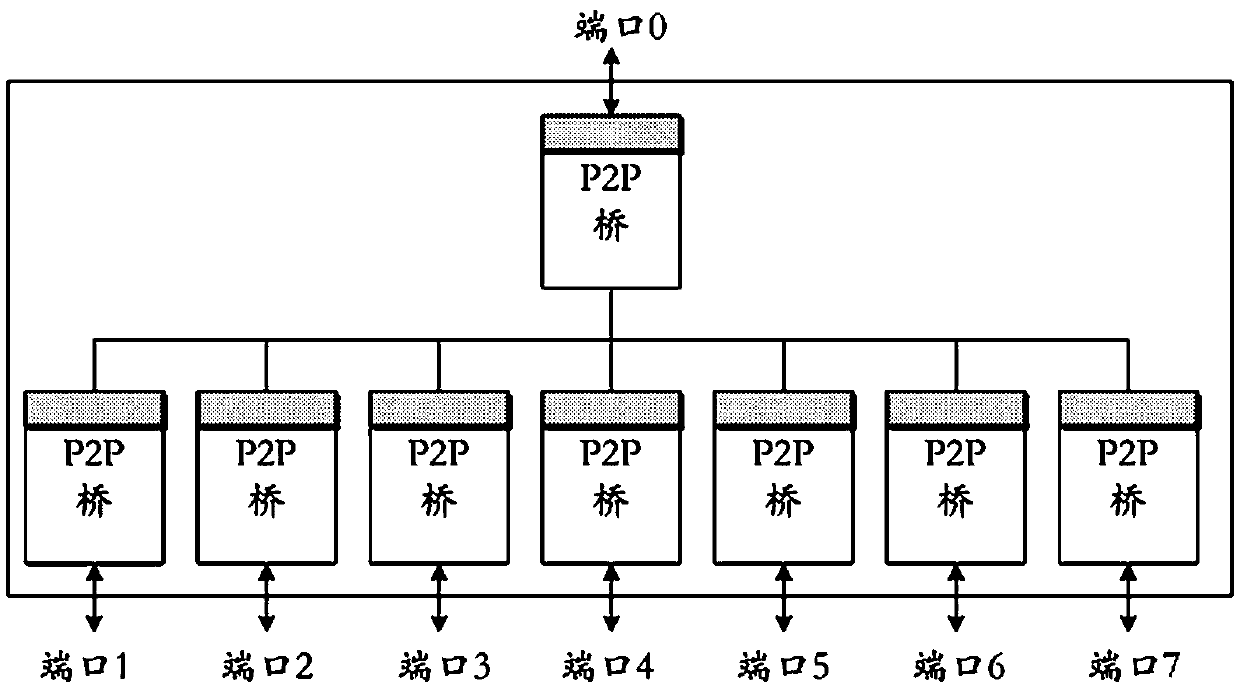

[0082] In the embodiment of the present invention, the PCIE switch chip is externally connected with an Electrically Erasable Programmable Read-Only Memory (Electronically Erasable Programmable Read-Only Memory, EEPROM for short), and the internal registers of the switch chip are initialized and loaded through the externally connected EEPROM. The PCIE switch chip port configuration system supporting virtual switching has n ports, where n is a natural number not less than three. The data packets received by the PCIE switch chip are divided into four types according to different routing methods: data packets based on identification number (Identification, abbreviated as ID), data packets based on memory address routing, and input / output based on input / output (abbreviated as ID). IO address routed packets and implicit routing (Implicit Routing) packets. In addition, the configuration package of the PCIE switch chip cannot come from the downstream port.

[0083] Each port of the ...

Embodiment 2

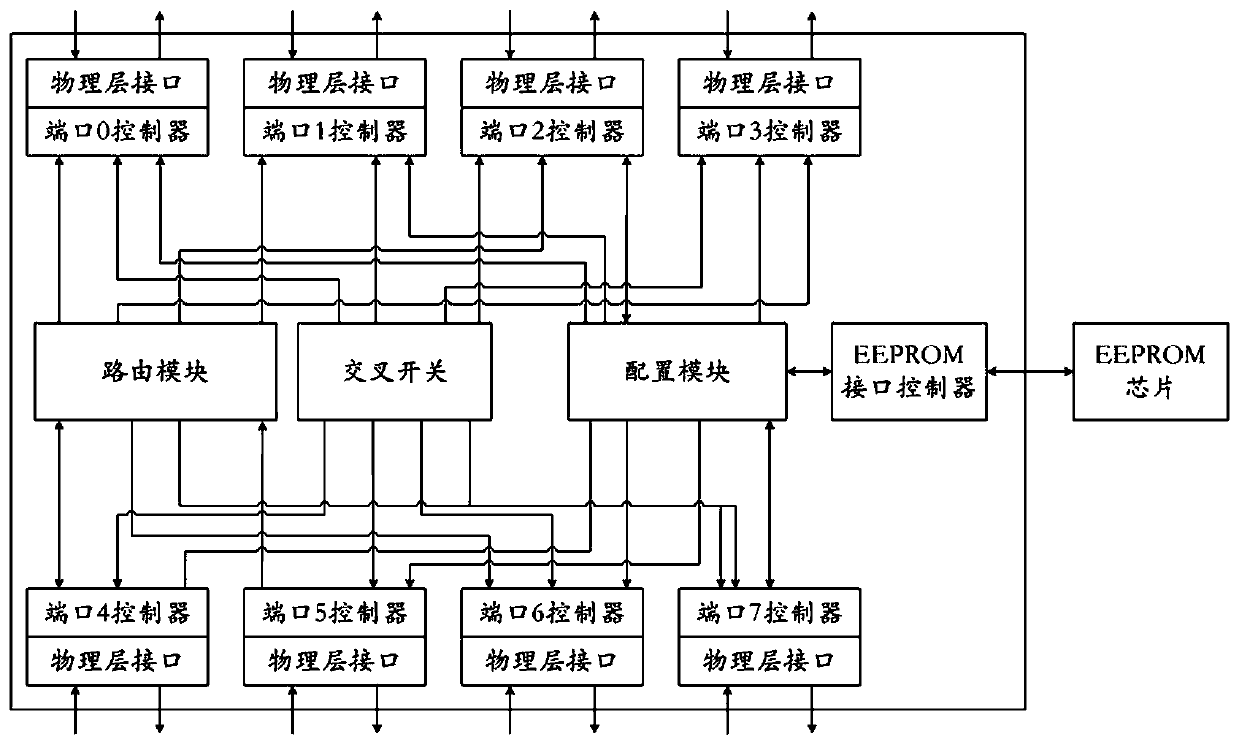

[0103] image 3 For the PCIE switch chip port configuration system structure schematic diagram supporting virtual switch according to the present invention, the implementation mechanism of virtual switch is illustrated below as an example of an eight-port PCIE switch chip that can be divided into four virtual switches internally, as image 3 As shown, the PCIE switch chip is mainly composed of a physical layer interface, a port controller, a routing module, an EEPROM interface controller, a configuration module, and a crossbar switch. The PCIE switch chip is externally connected with an EEPROM chip used to initialize port registers.

[0104] The external EEPROM is used to save the configuration register address and configuration data used for the initialization of the port register of the PCIE switch chip.

[0105] The physical layer interface implements the functions of the physical medium adaptation layer and the physical coding sublayer of the PCIE physical layer.

[0106...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More