Patents

Literature

52results about How to "Increase bit width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

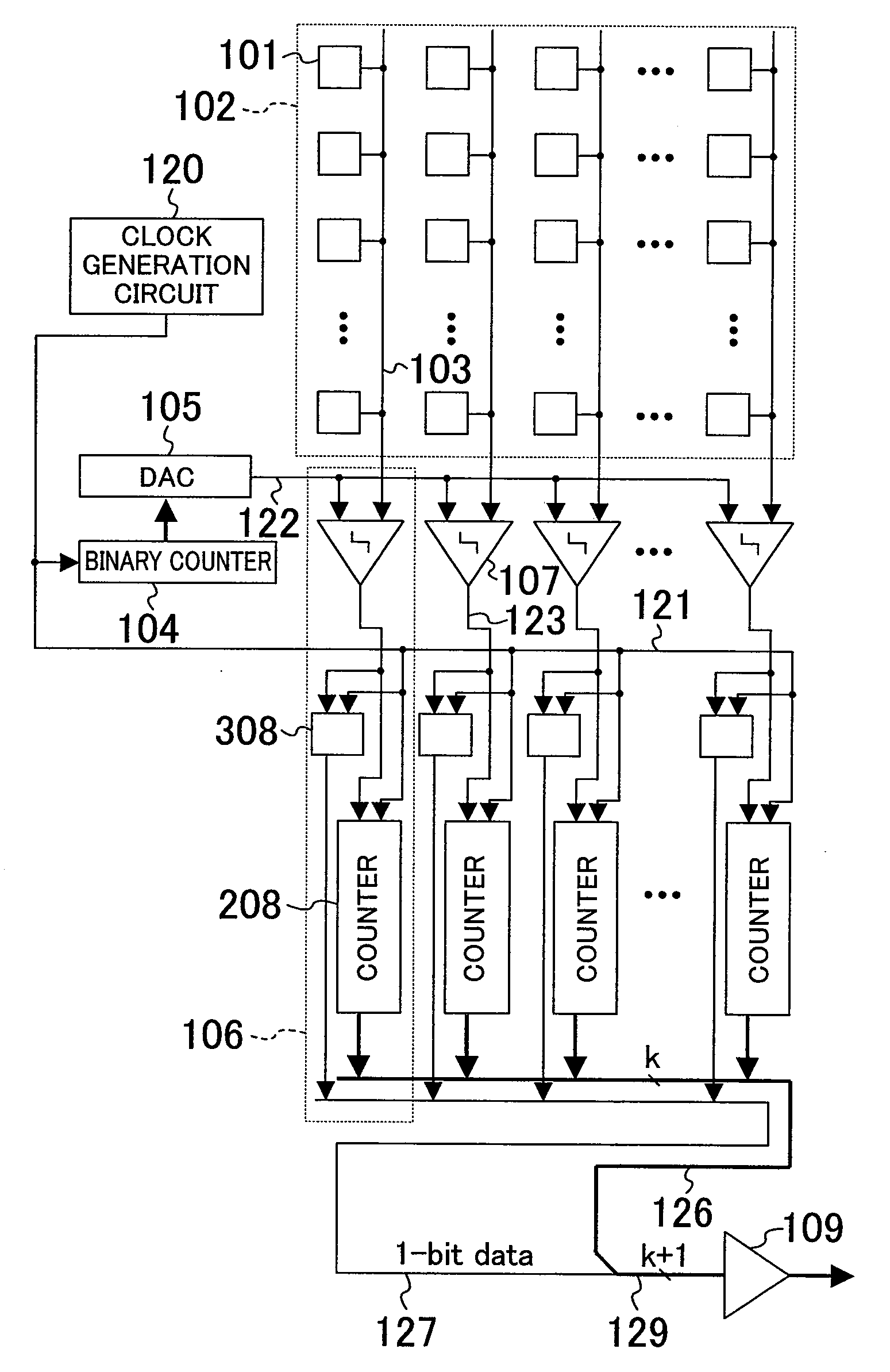

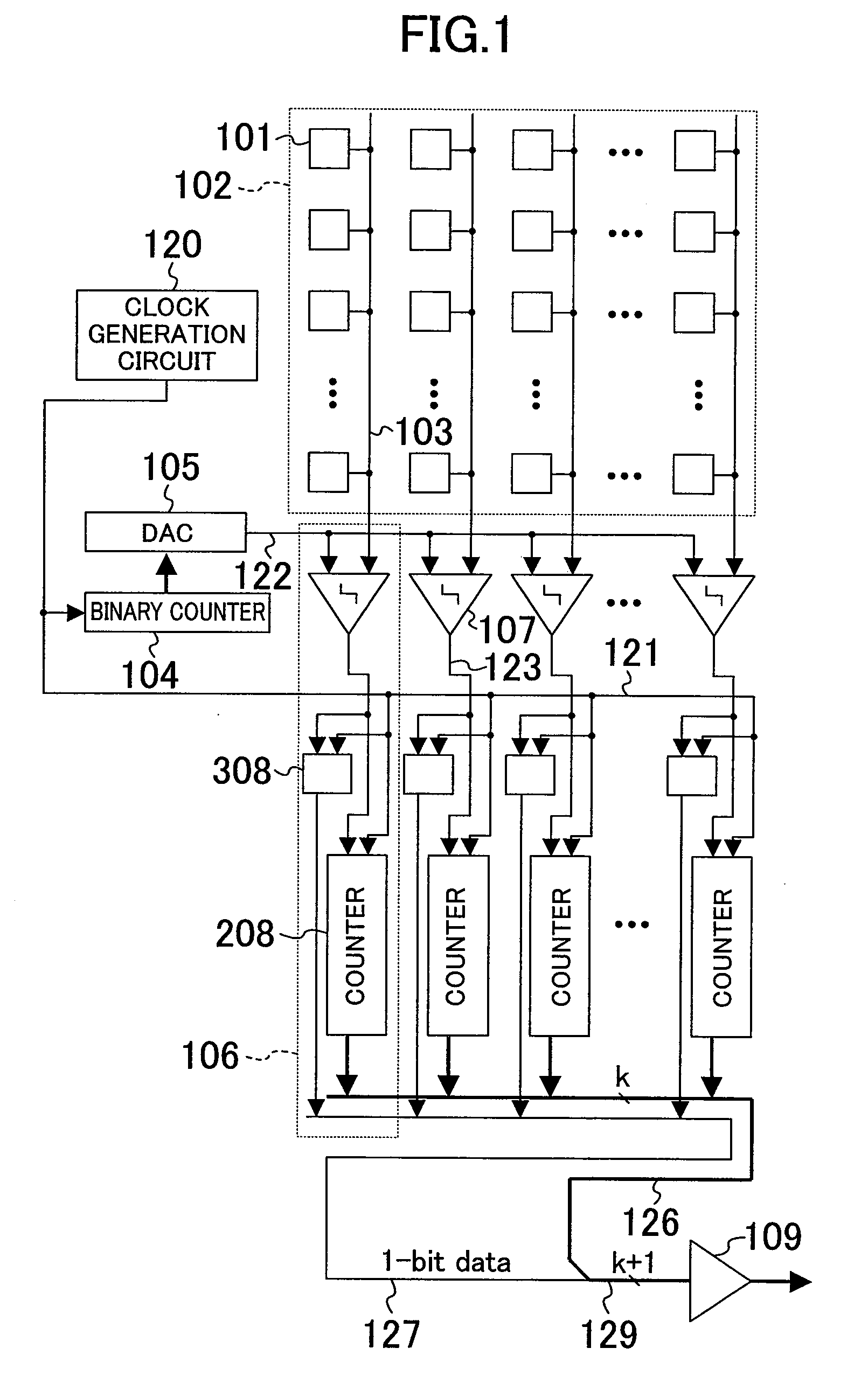

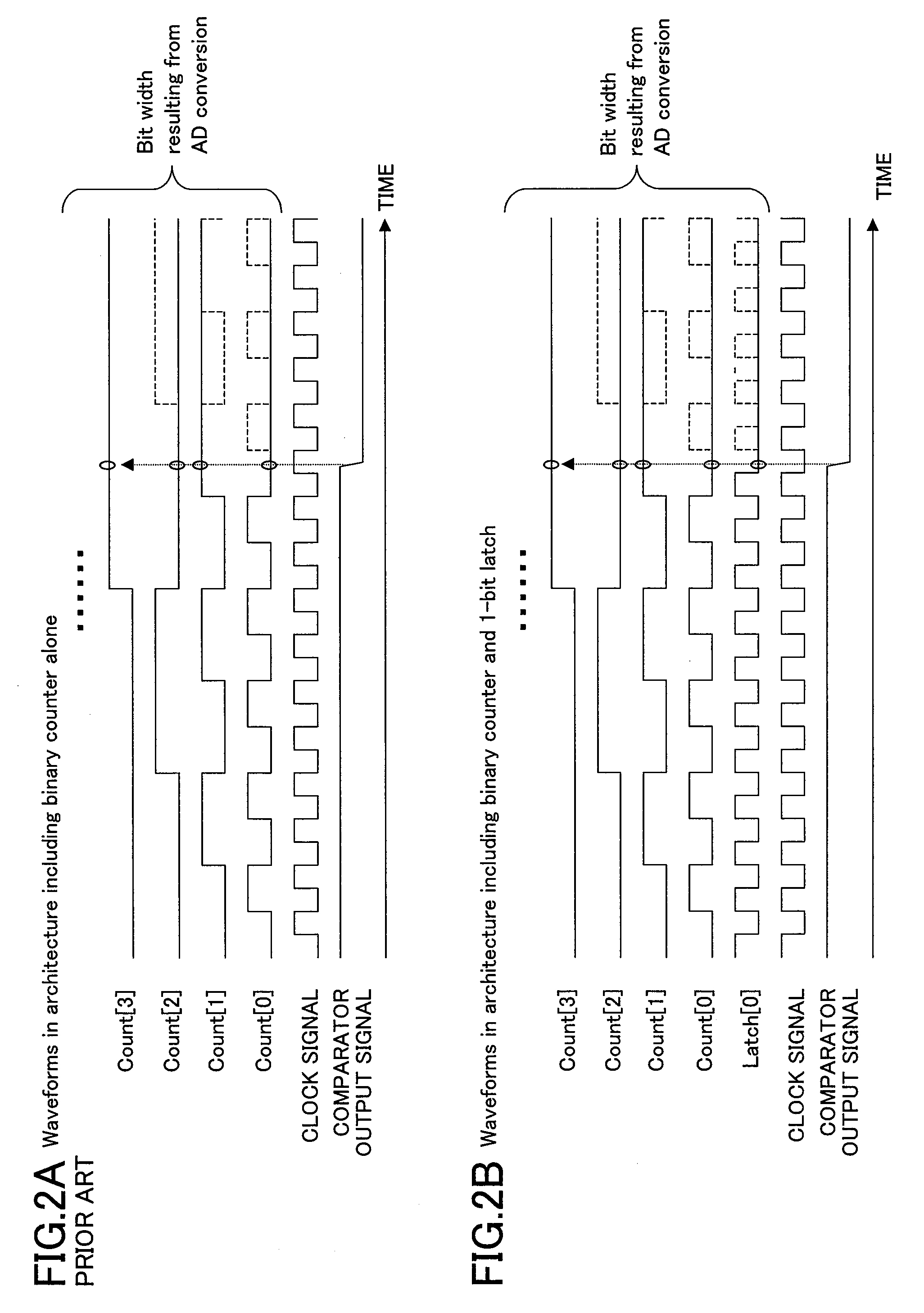

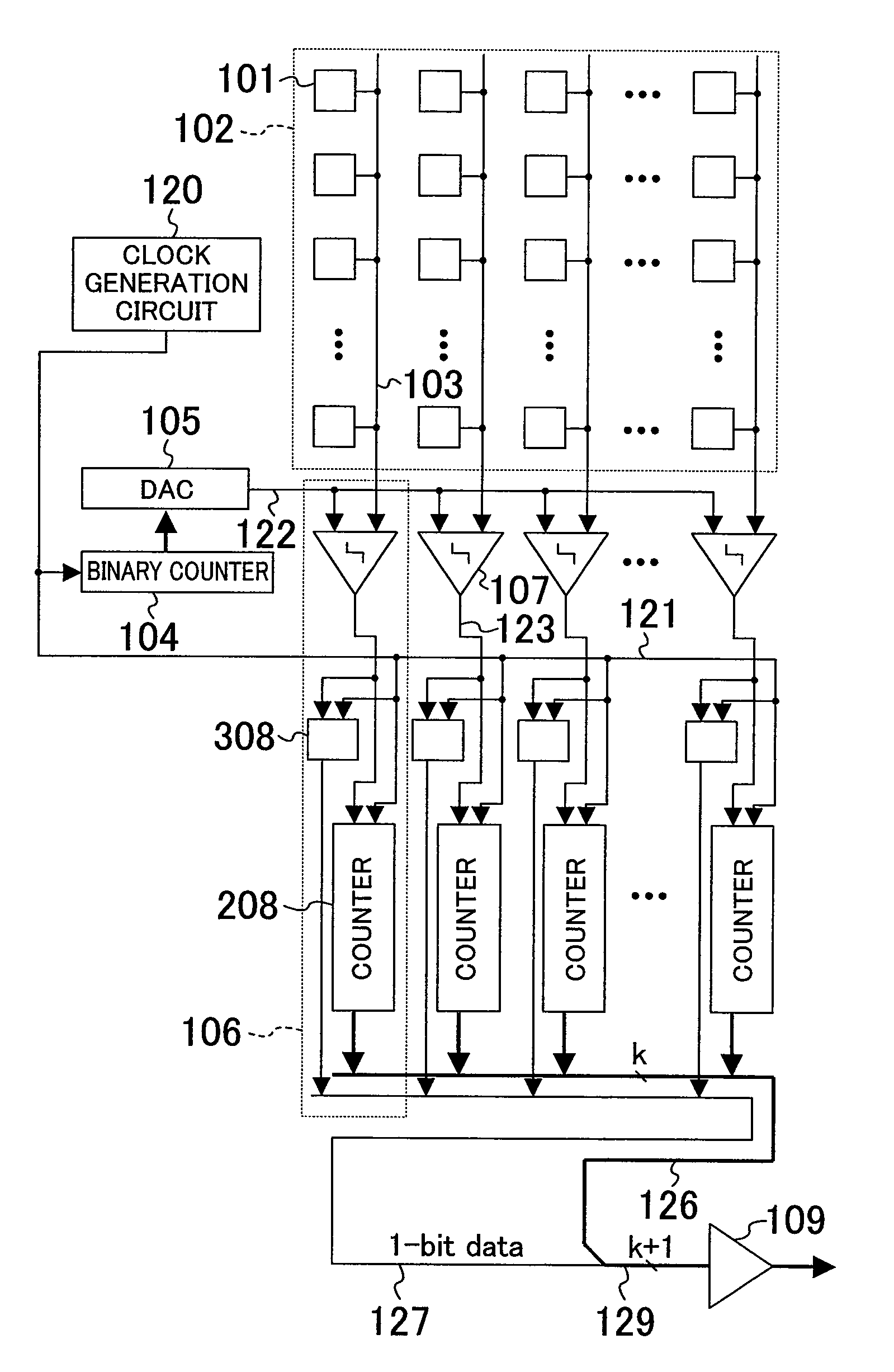

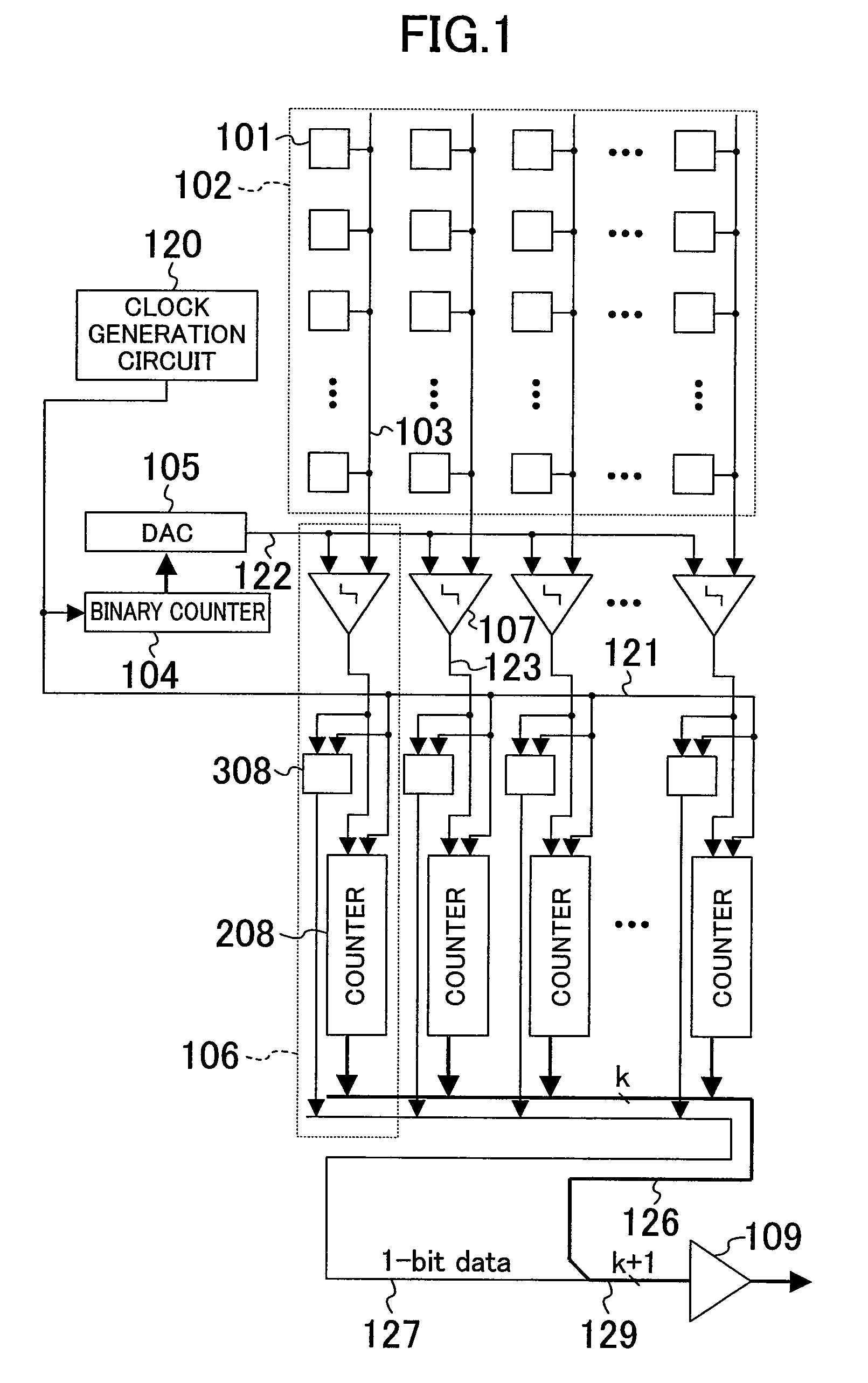

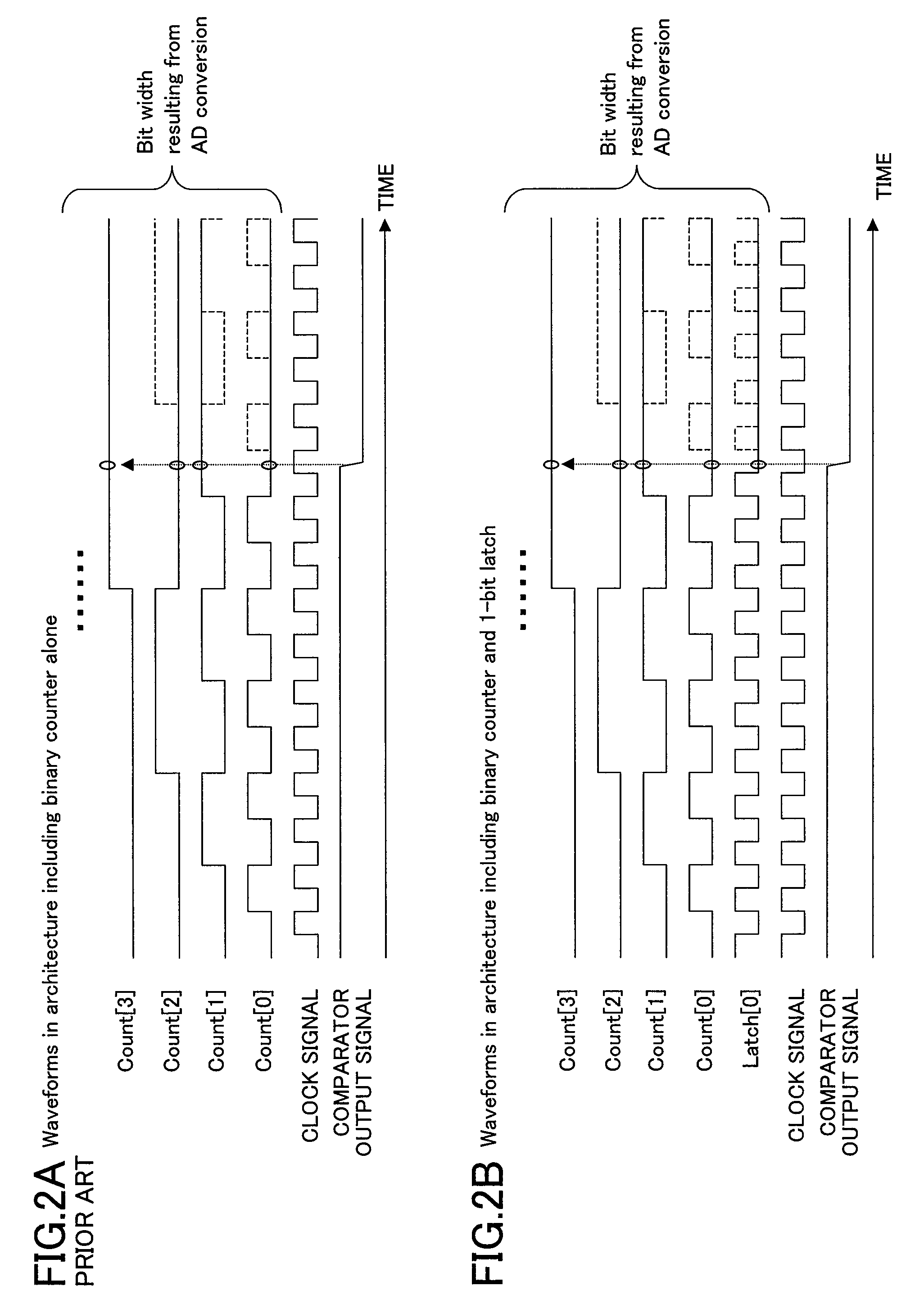

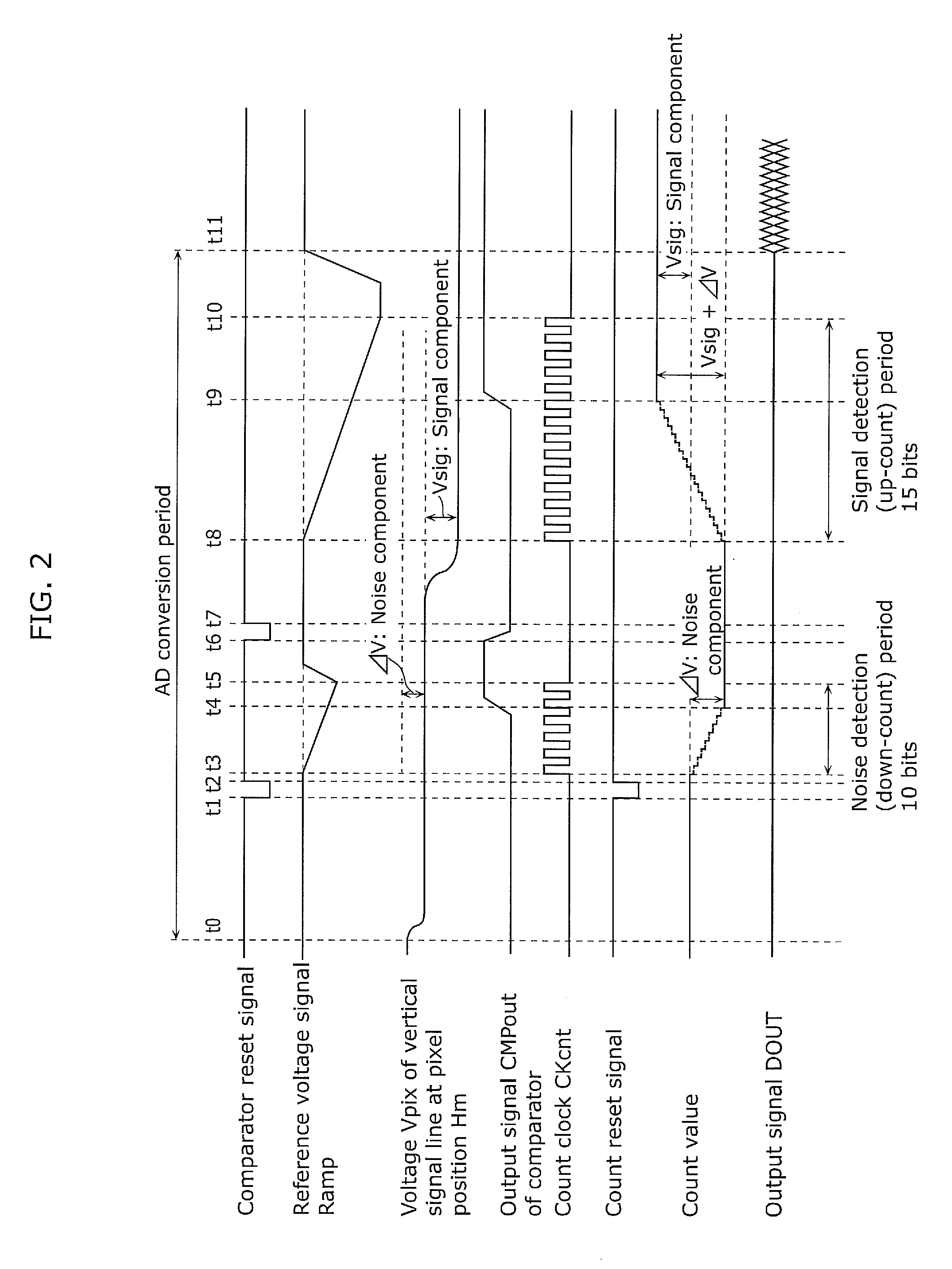

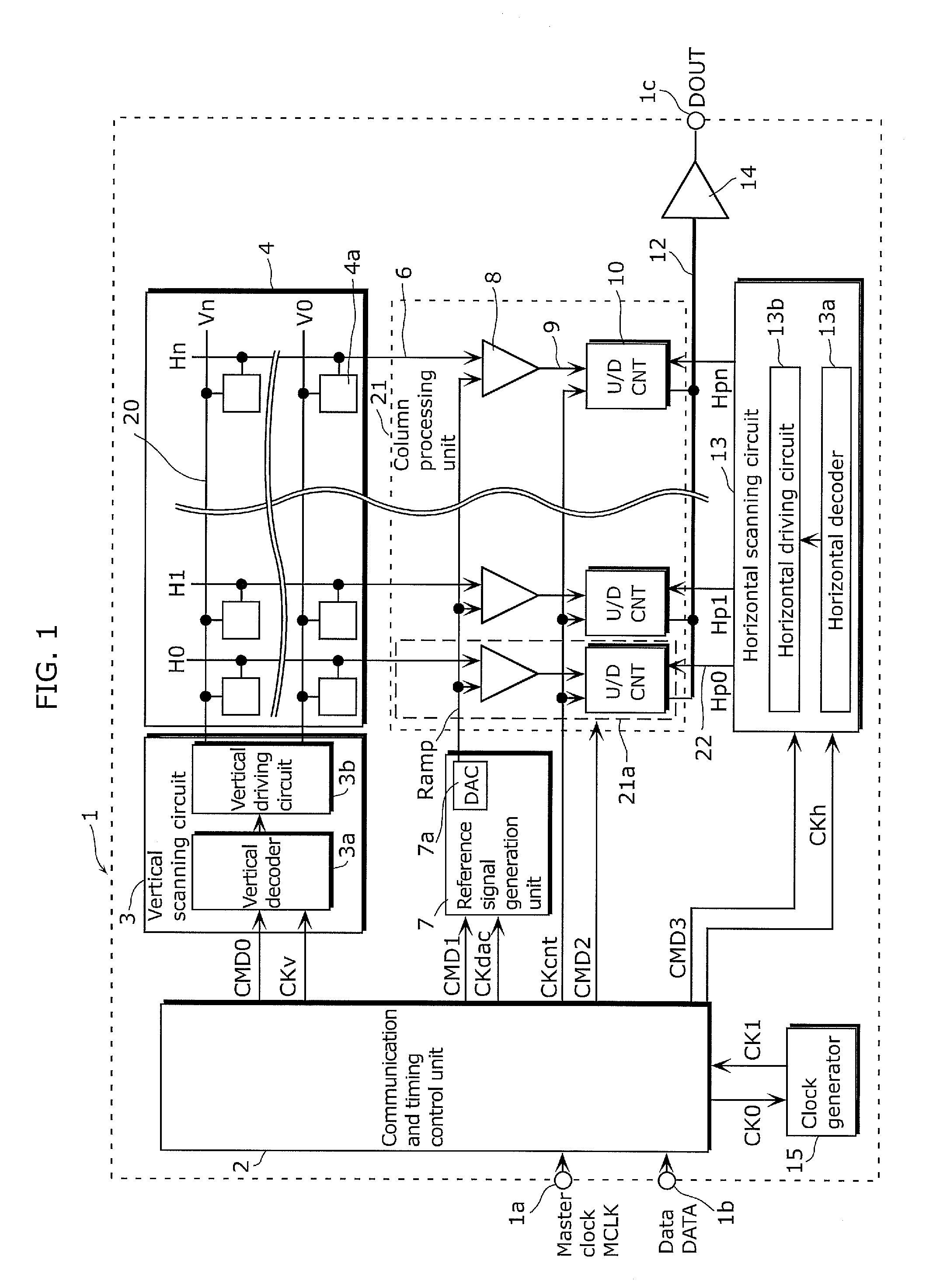

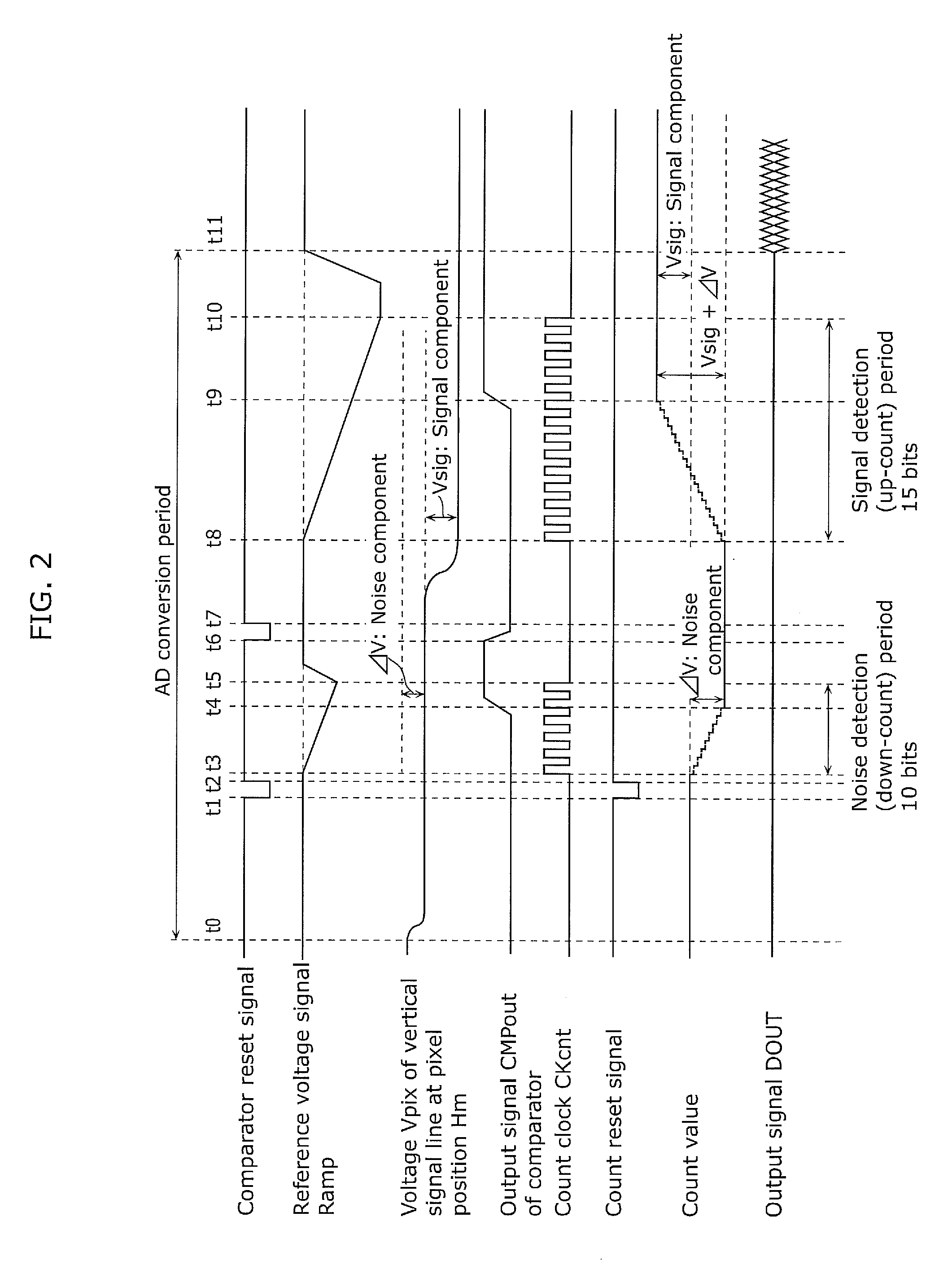

Physical quantity detecting apparatus and method for driving the same

ActiveUS20090026352A1Frequency of clock signal can be reducedBit accuracy can be improvedTelevision system detailsTelevision system scanning detailsPhysical quantityDigital camera

In a solid state imaging device to be included in an imaging device such as a digital camera, a ramp run-up AD conversion circuit for AD converting a pixel signal is provided corresponding to one or a plurality of pixel columns. A column counter provided in each ramp run-up AD conversion circuit holds an upper bit, and a clock signal is supplied to one or plural latches for holding a lower bit. Thus, fast and accurate AD conversion can be realized while suppressing increase of clock frequency.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Physical quantity detecting apparatus and method for driving the same

ActiveUS7671317B2Improve picture qualityConversion bit widthTelevision system detailsTelevision system scanning detailsEngineeringPhysical quantity

In a solid state imaging device to be included in an imaging device such as a digital camera, a ramp run-up AD conversion circuit for AD converting a pixel signal is provided corresponding to one or a plurality of pixel columns. A column counter provided in each ramp run-up AD conversion circuit holds an upper bit, and a clock signal is supplied to one or plural latches for holding a lower bit. Thus, fast and accurate AD conversion can be realized while suppressing increase of clock frequency.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

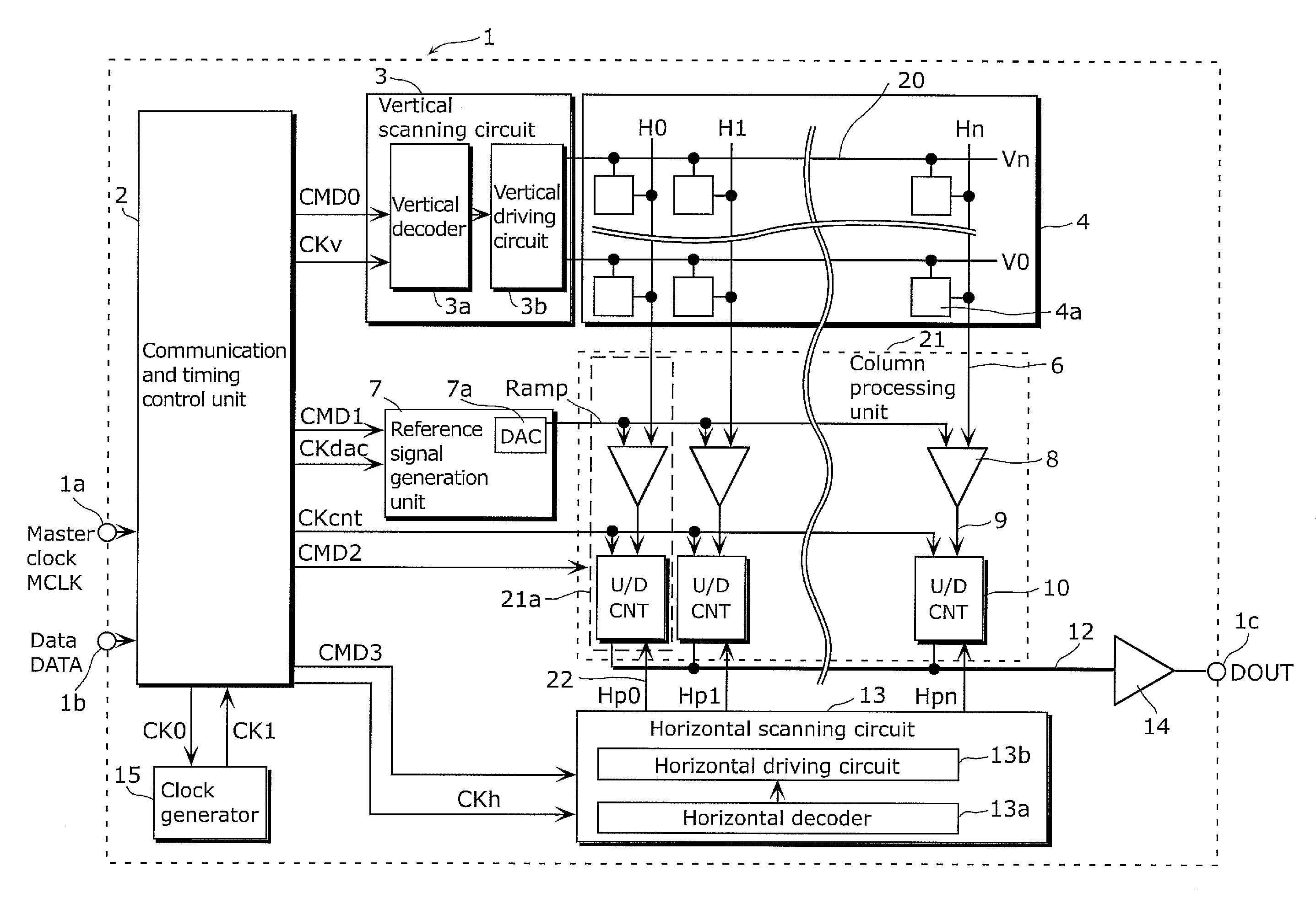

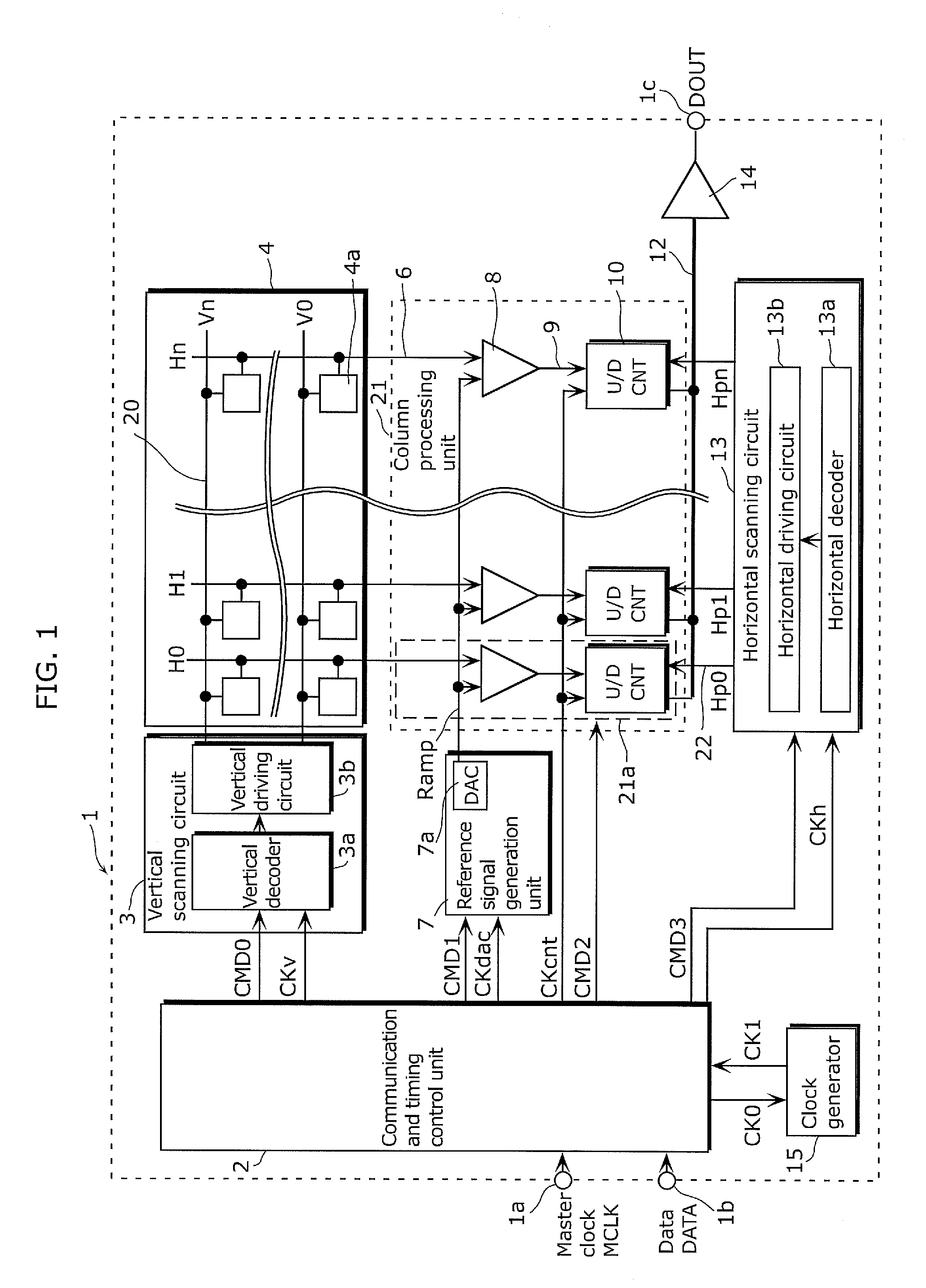

Solid-state imaging device, and imaging device

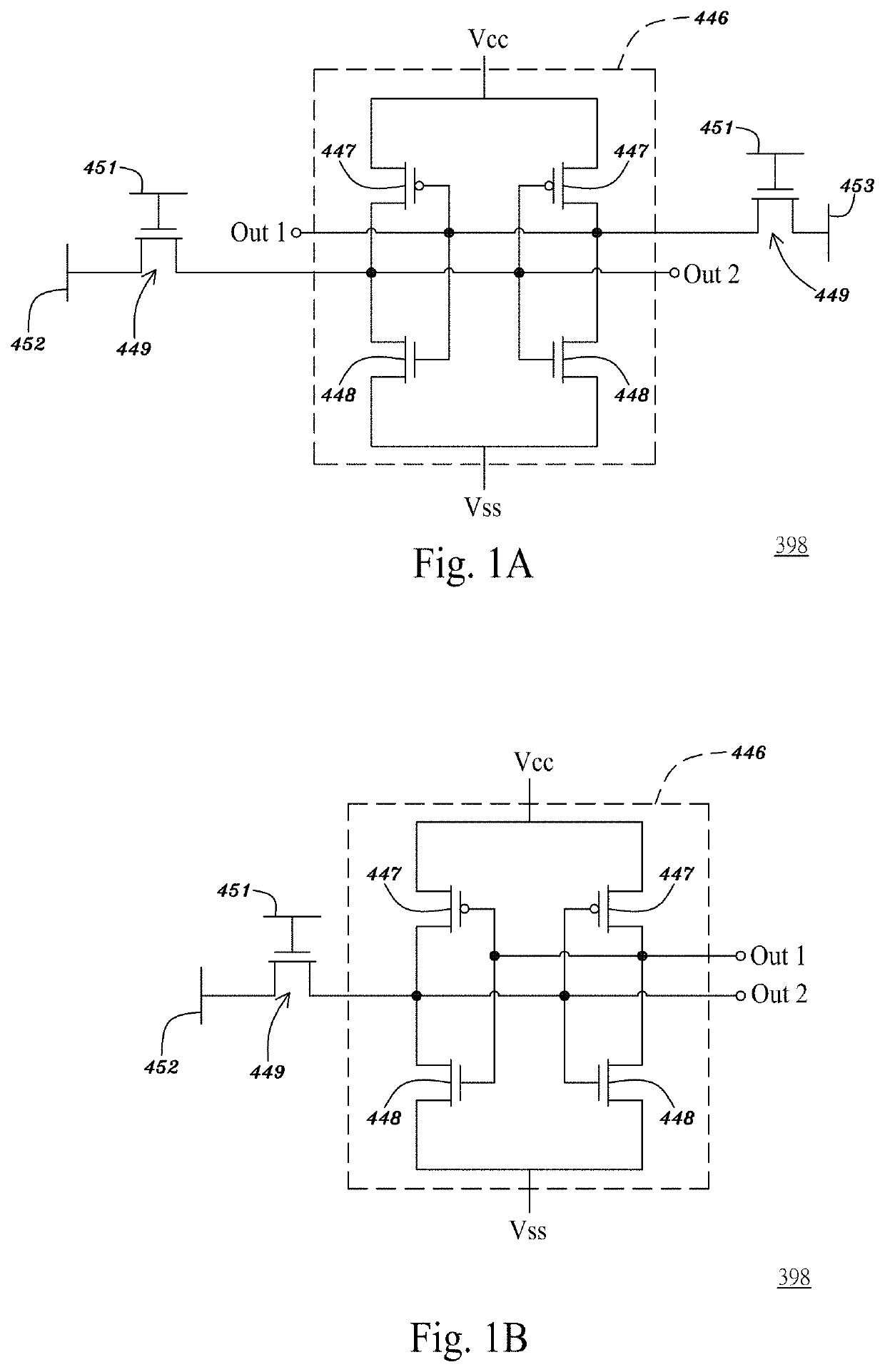

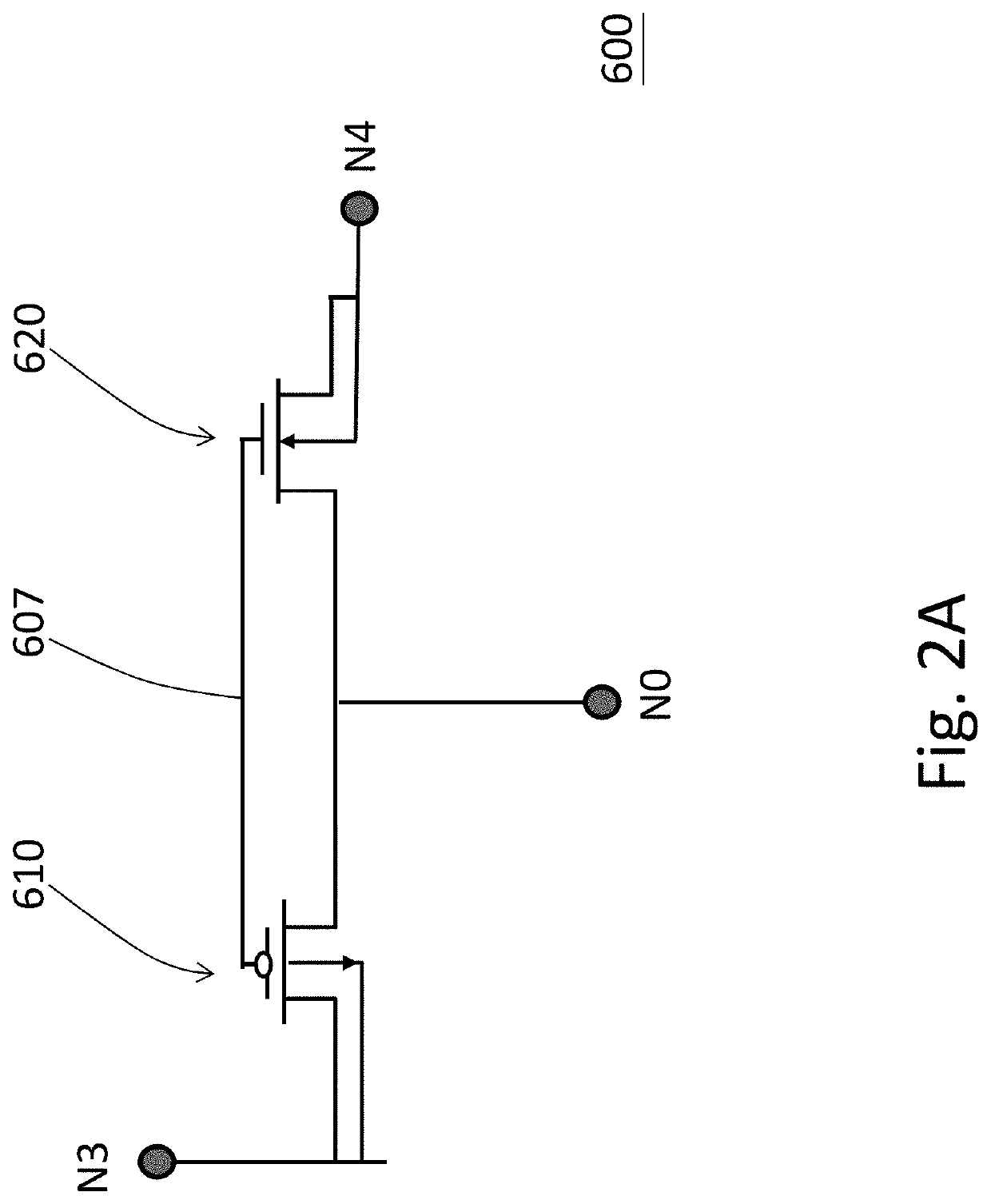

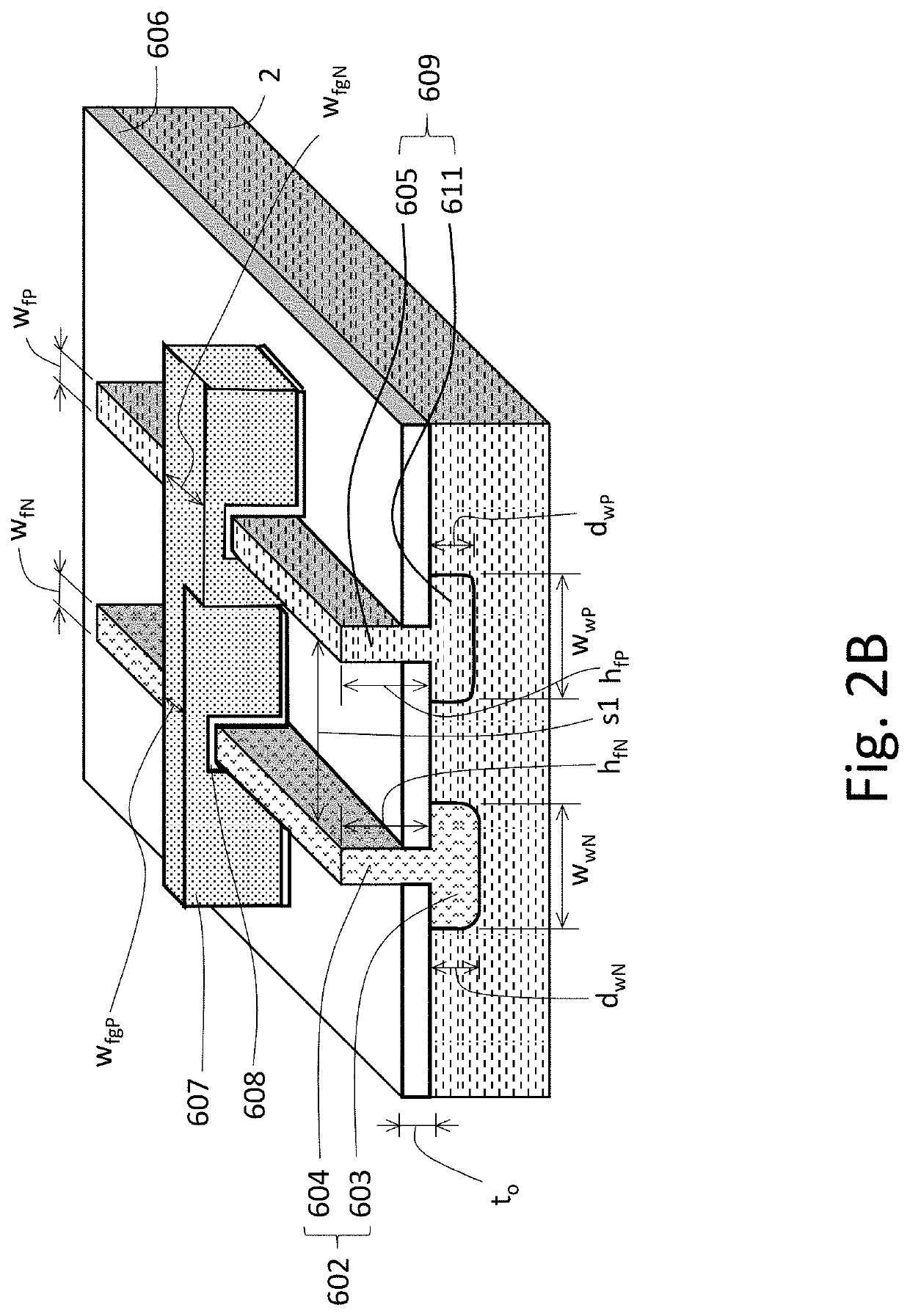

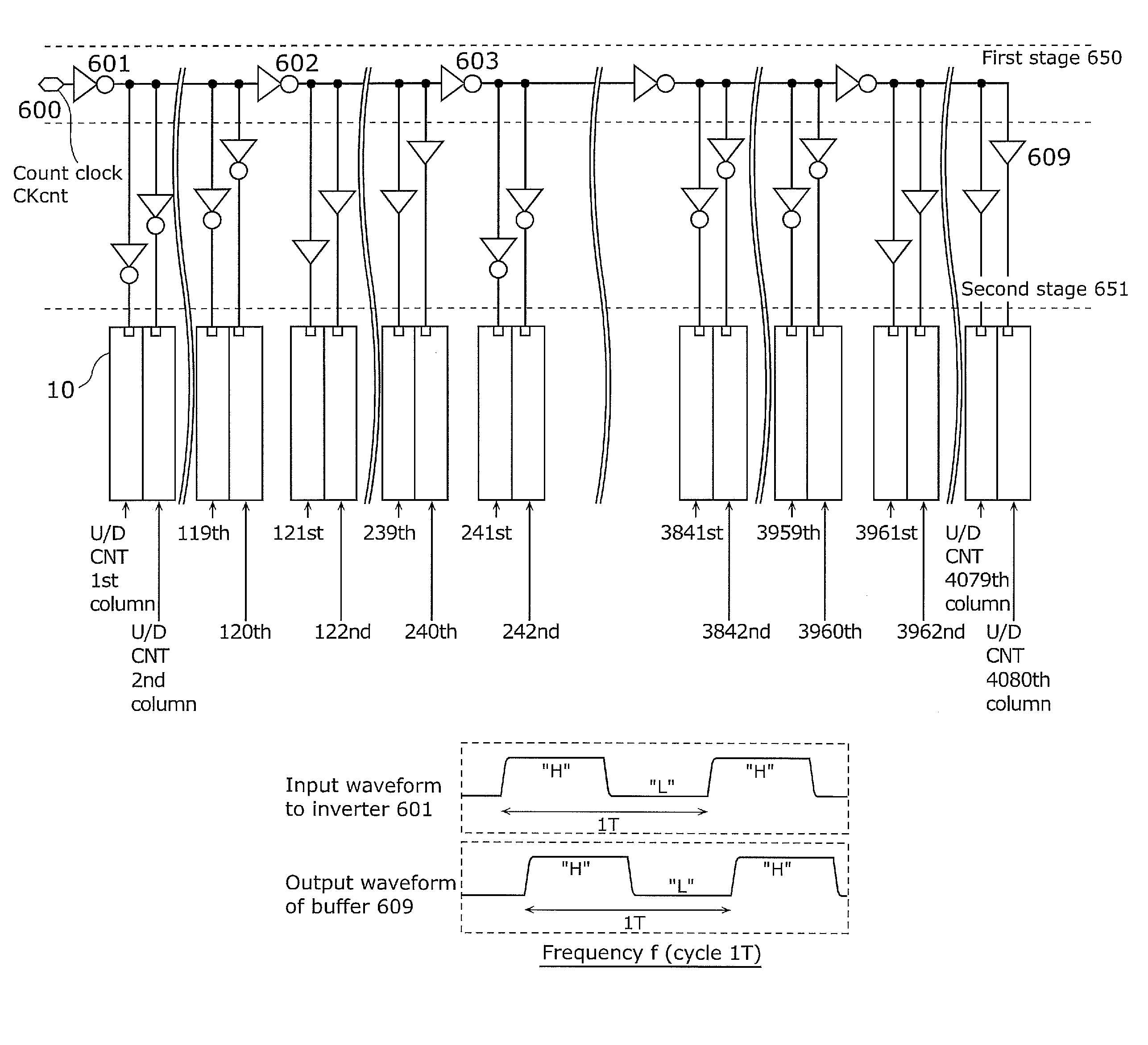

ActiveUS20120305752A1Reduce dutyEasy to realize extension of AD conversion bit widthTelevision system detailsSolid-state devicesSolid-stateEngineering

A solid-state imaging device includes: a column comparison circuit which compares a pixel signal with ramp waves and detects a timing at which the pixel signal and the ramp waves match; a counter circuit which is disposed for each of the pixel columns and measures the timing in the column comparison circuit by being supplied with a clock signal; and M first inverters which are equidistantly connected in series, wherein the counter circuit belongs to one of M groups corresponding to each of the M first inverters disposed in the upper clock stage, the odd-numbered group has second inverters disposed between the output terminal of the first inverter corresponding to the group and the counter circuit of the group, and the even-numbered group has buffers disposed between the output terminal of the first inverter corresponding to the group and the counter circuit of the group.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

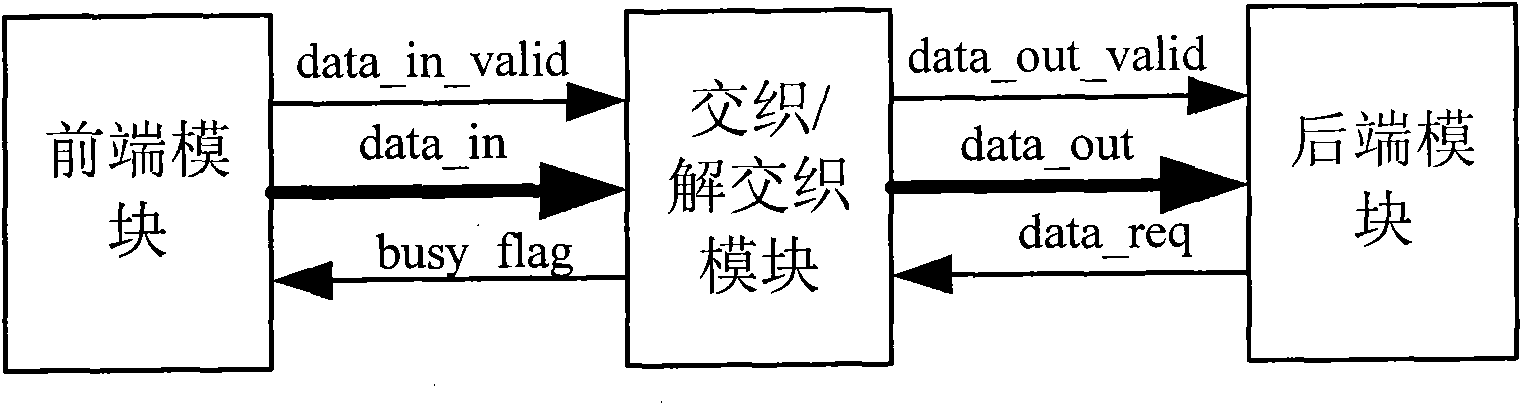

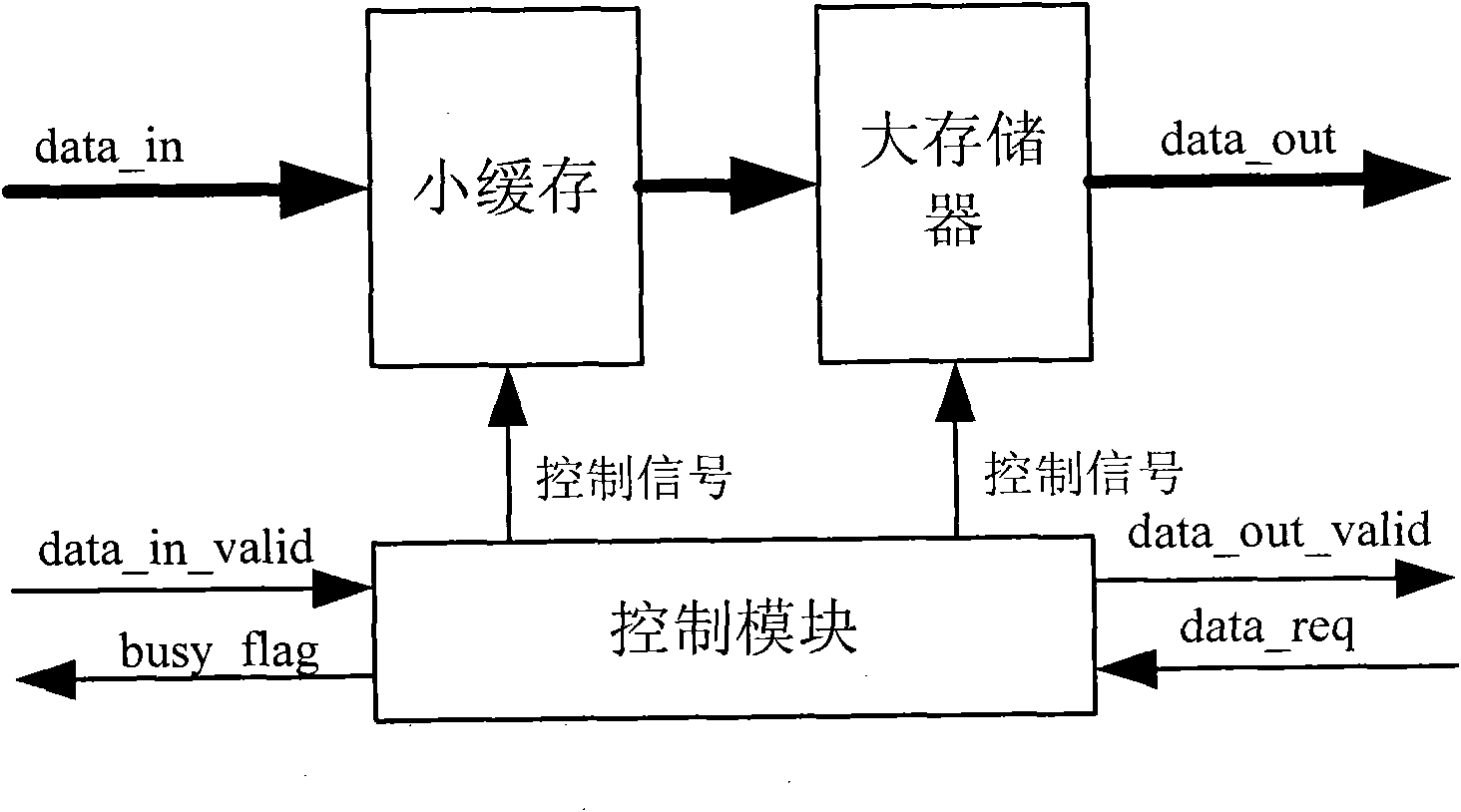

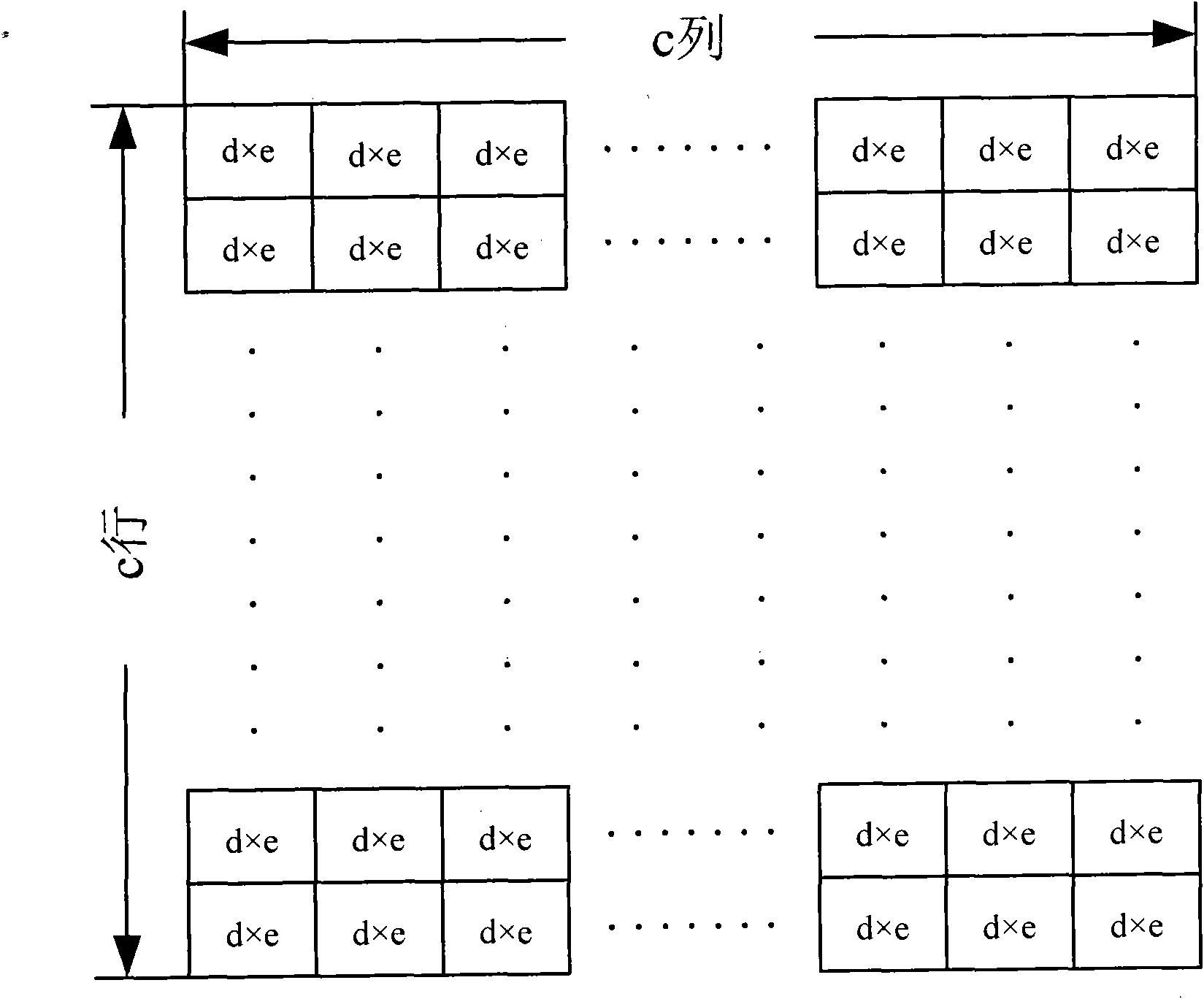

Interleaver or deinterleaver method and device thereof based on block interleaver

ActiveCN101800619AReduce sizeIncrease bit widthError preventionError correction/detection using multiple parity bitsComputer architectureExtended memory

The invention relates to an interleaver or deinterleaver method and a device thereof based on a block interleaver, an interleaver or deinterleaver block is extended to a square, when a first time interleaver or deinterleaver is carried out by the method of writing by row and reading by column, then a second time interleaver or deinterleaver is carried out by the method of writing by column and reading by row, therefore, the second time writing and the first time reading are basically carried out at the same time in a same memory and the data which is not processed by the first time interleaver or deinterleaver is not washed off. The method is carried out all the time alternately, only an extended memory is needed to finish the interleaver / deinterleaver, thereby greatly reducing the size of the needed memory, meanwhile, a little buffer memory is added before the memory to increase the bit wide of the memory, thereby being convenient to process.

Owner:FUZHOU ROCKCHIP SEMICON

Logic drive based on multichip package comprising standard commodity FPGA IC chip with cryptography circuits

ActiveUS20210005592A1Lower the barrierReduce expensesSemiconductor/solid-state device detailsSolid-state devicesData setSemiconductor chip

A multichip package comprising: a first chip package comprising a first semiconductor IC chip, a first polymer layer in a space beyond and extending from a sidewall of the first semiconductor IC chip, a first through package via in the first polymer layer, and a first interconnection scheme under the first semiconductor IC chip, first polymer layer and first through package via, wherein the first semiconductor IC chip comprises a plurality of volatile memory cells configured to store first data associated with a plurality of resulting values for a look-up table (LUT) and a selection circuit configured to select, in accordance with a first input data set thereof, a data from a second input data set thereof as an output data for the logic operation; a first metal bump under the first chip package; and a non-volatile memory IC chip over the first chip package, wherein the non-volatile memory IC chip comprises a plurality of first non-volatile memory cells configured to store second data associated with the plurality of resulting values for the look-up table (LUT), wherein the first data are associated with the second data.

Owner:ICOMETRUE CO LTD

Solid-state imaging device comprising an analog to digital converter with column comparison circuits, column counter circuits, first and second inverters, and buffers

ActiveUS8735796B2Improve accuracyDecrease in the duty of the clock is restrictedAnalogue/digital conversionTelevision system detailsAnalog-to-digital converterClock signal

A solid-state imaging device includes: a column comparison circuit which compares a pixel signal with ramp waves and detects a timing at which the pixel signal and the ramp waves match; a counter circuit which is disposed for each of the pixel columns and measures the timing in the column comparison circuit by being supplied with a clock signal; and M first inverters which are equidistantly connected in series, wherein the counter circuit belongs to one of M groups corresponding to each of the M first inverters disposed in the upper clock stage, the odd-numbered group has second inverters disposed between the output terminal of the first inverter corresponding to the group and the counter circuit of the group, and the even-numbered group has buffers disposed between the output terminal of the first inverter corresponding to the group and the counter circuit of the group.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

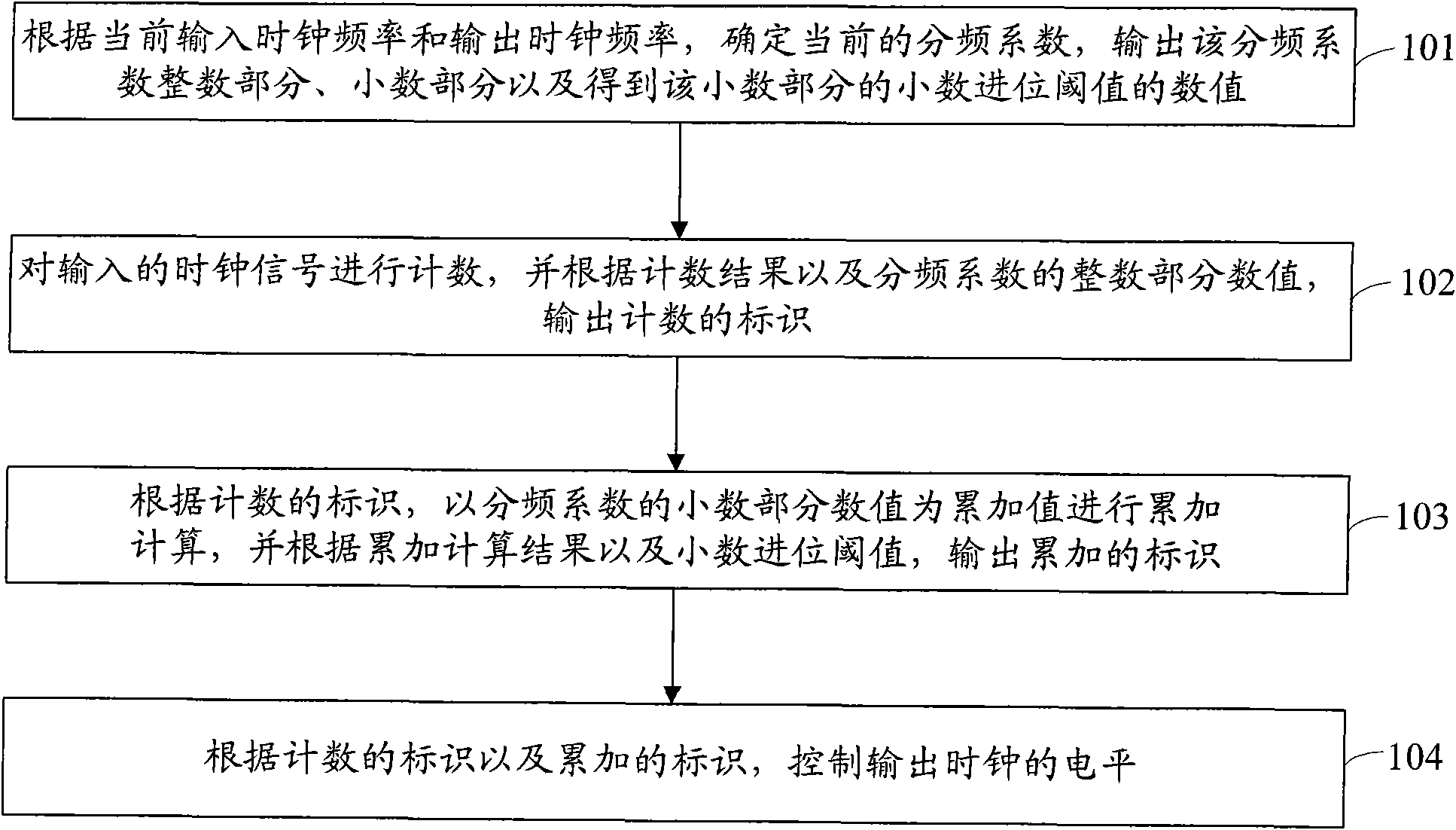

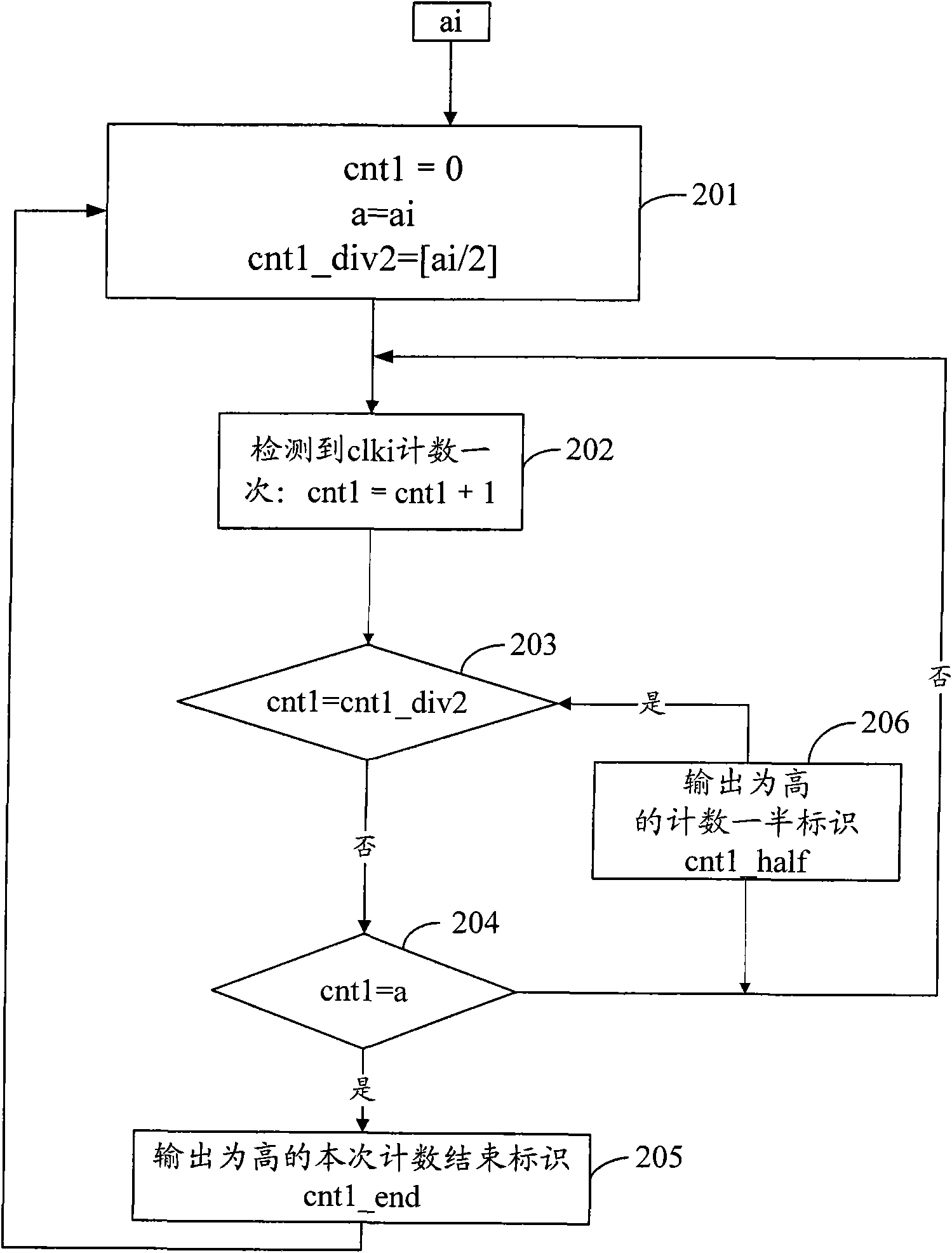

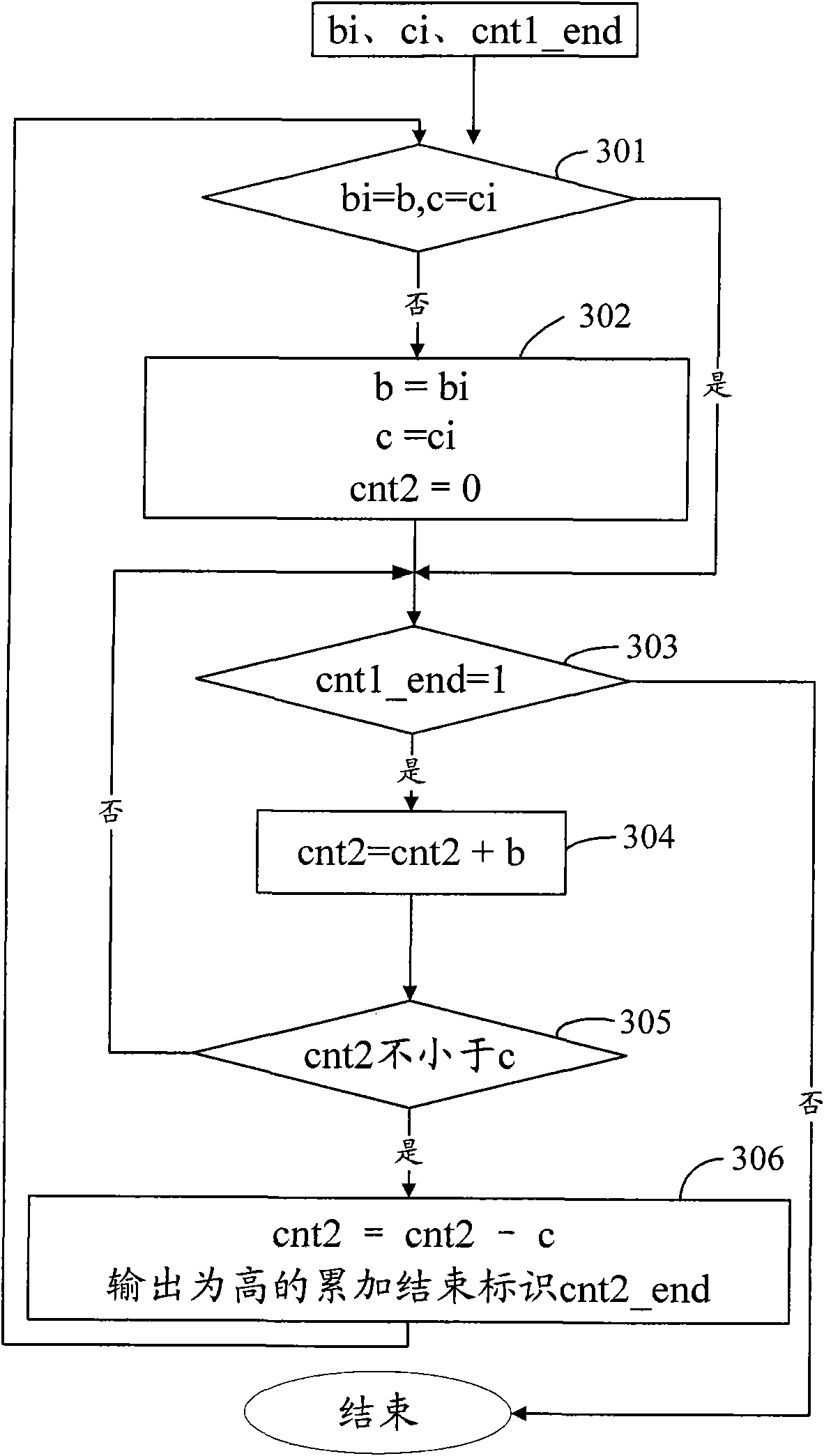

Method and device for clock division

InactiveCN101783676AAccuracy adjustableIncrease bit widthCounting chain pulse countersComputer scienceBand counts

The invention discloses a method for clock division, which comprises the following steps: fixing the current division coefficient at real time through the input clock signals and the output clock information, counting the input clock signals through the integer part and the decimal part of the division coefficient and the decimal carry threshold value of the decimal part, according to the counting result, beginning accumulative counting which takes the decimal part as the accumulated value, and finally controlling the output clock according to the counting result and the accumulative counting result. The invention further discloses a clock division device. Through the method and the device, the output signals can be dynamically adjusted according to the input signals, and the precision of the division coefficient can be adjusted by increasing the bit widths of the integer part and the decimal part of the division coefficient and the decimal carry threshold value of the decimal part according to needs.

Owner:ZTE CORP

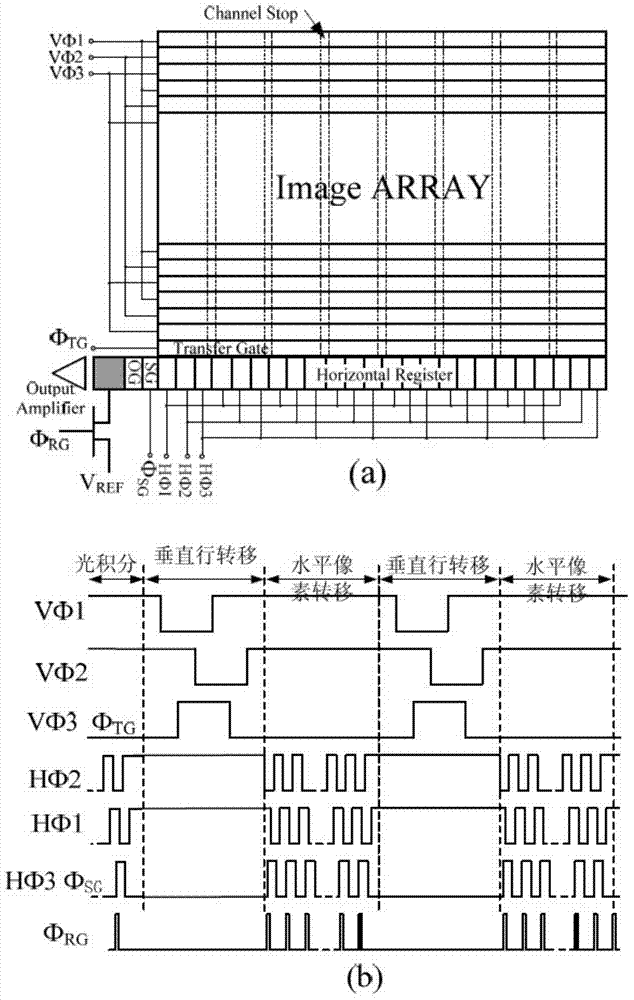

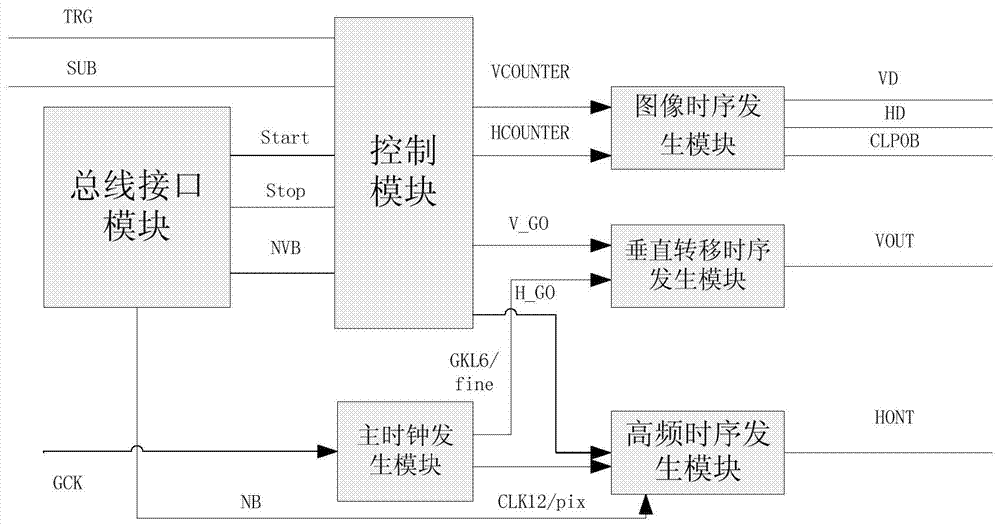

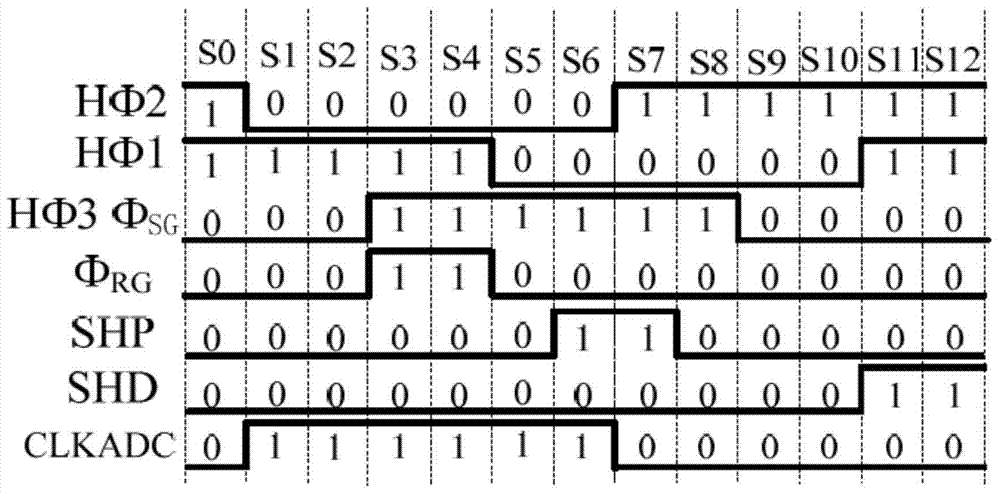

Universal area array CCD timing sequence driven generator

InactiveCN103795944AIncrease bit widthIncrease the number ofTelevision system detailsColor television detailsWave shapeImage resolution

The invention relates to a universal area array CCD timing sequence driven generator. The universal area array CCD timing sequence driven generator comprises a bus interface module, a control module, an image timing sequence generation module, a perpendicular transfer timing sequence generation module, a master clock generation module and a high frequency timing sequence generation module. The bus interface module is connected with the control module and connected with the high frequency timing sequence generation module. The control module is connected with the image timing sequence generation module, the perpendicular transfer timing sequence generation module and the high frequency timing sequence generation module. The master clock generation module is connected with the high frequency timing sequence generation module and connected with the perpendicular transfer timing sequence generation module. The timing sequence generator designed through the method has high universality and flexibility, and in other words, the waveforms and the mutual relations of the timing sequences can be changed by modifying output values of all states; the number of output signals can be increased by increasing the bit widths of the output values; the time resolution can be improved by increasing the number of the states of waveform division.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

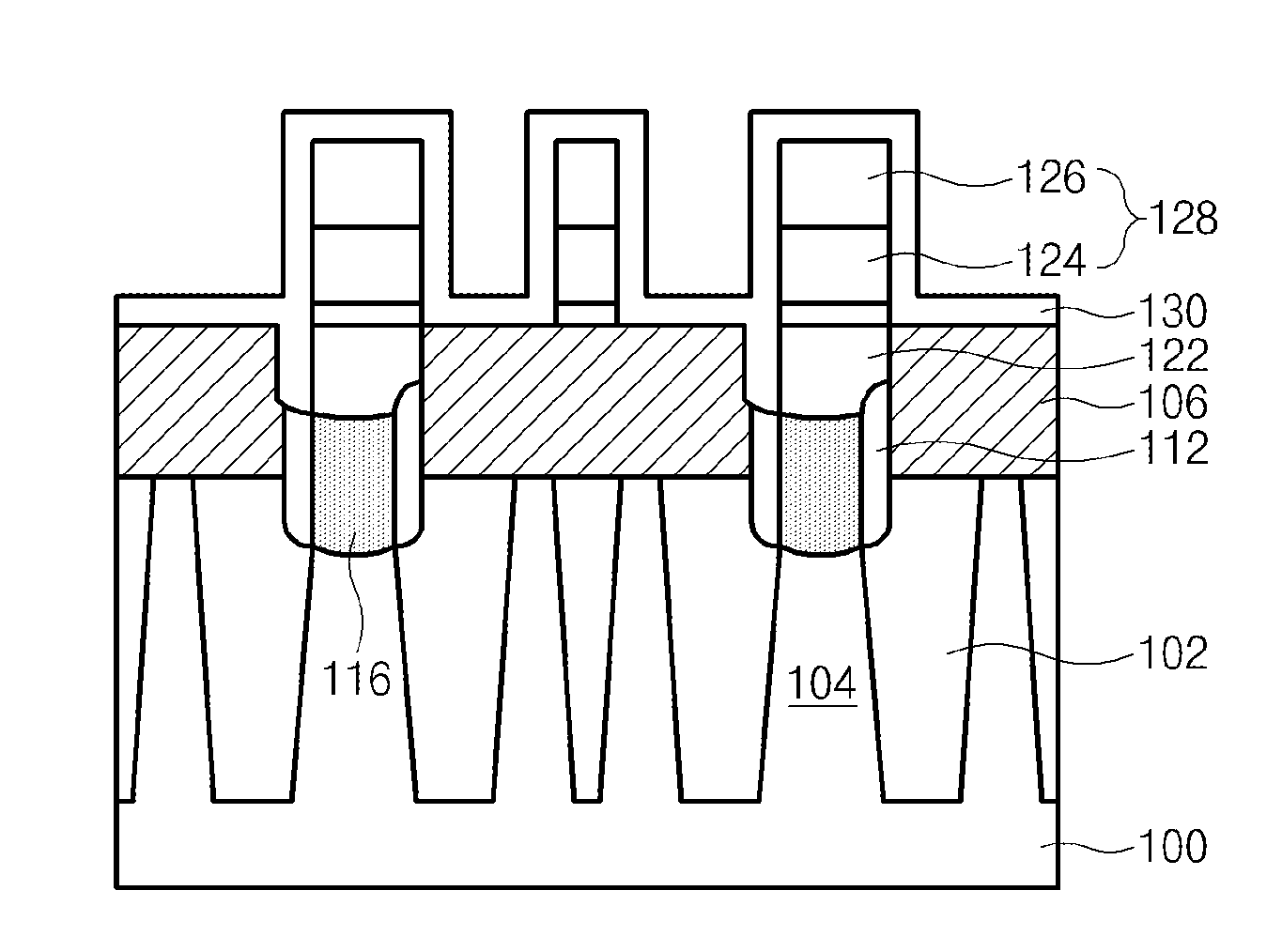

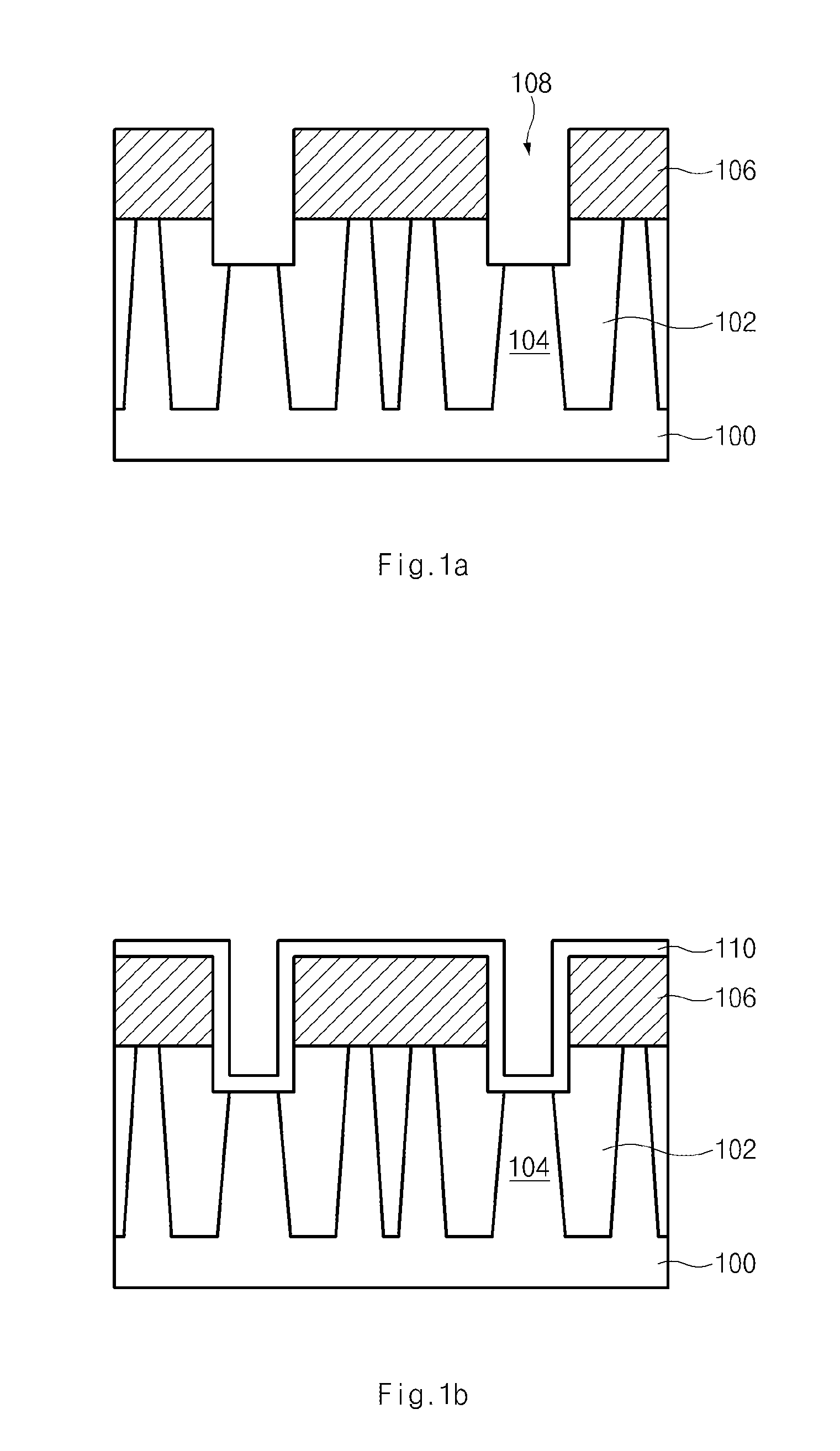

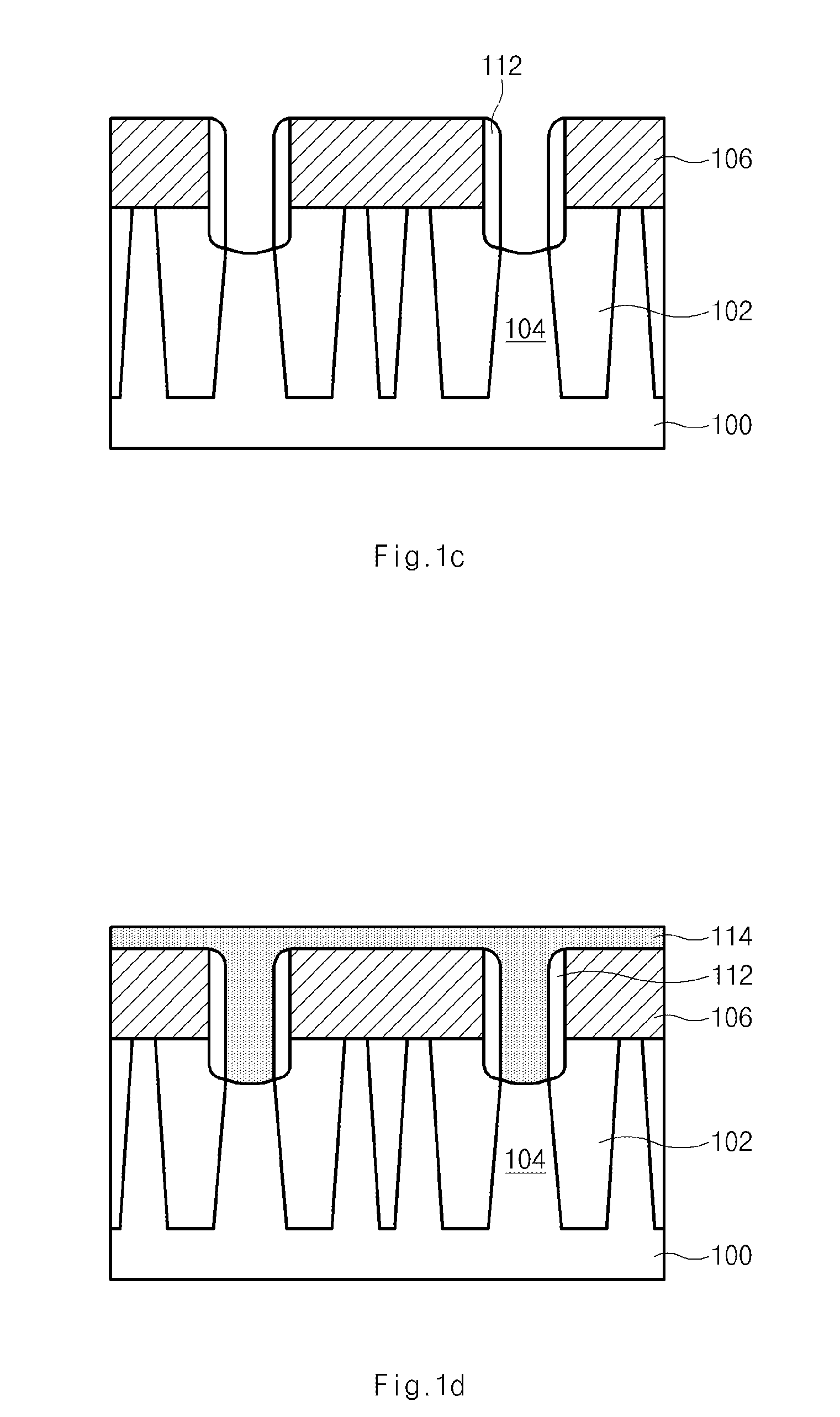

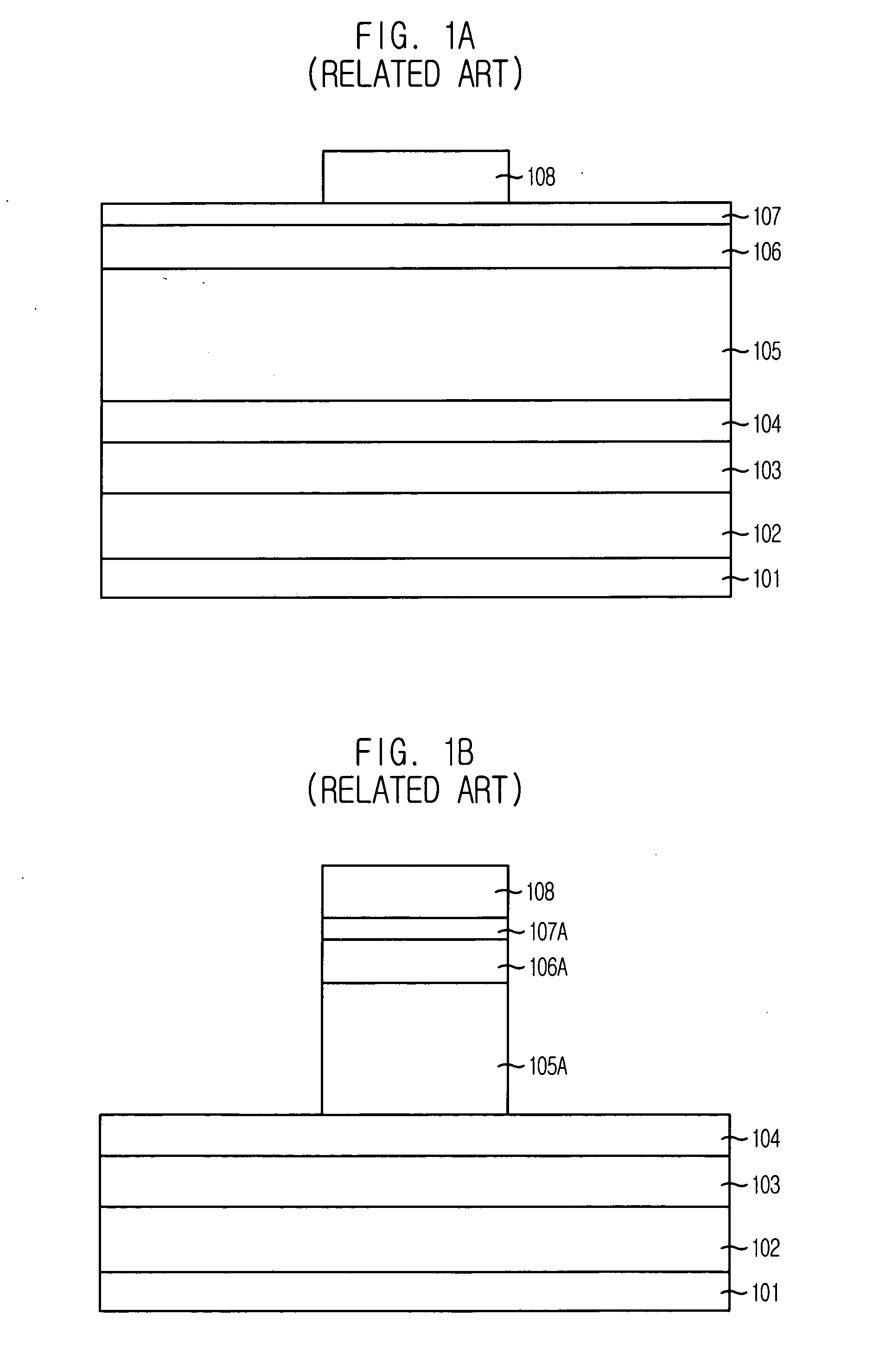

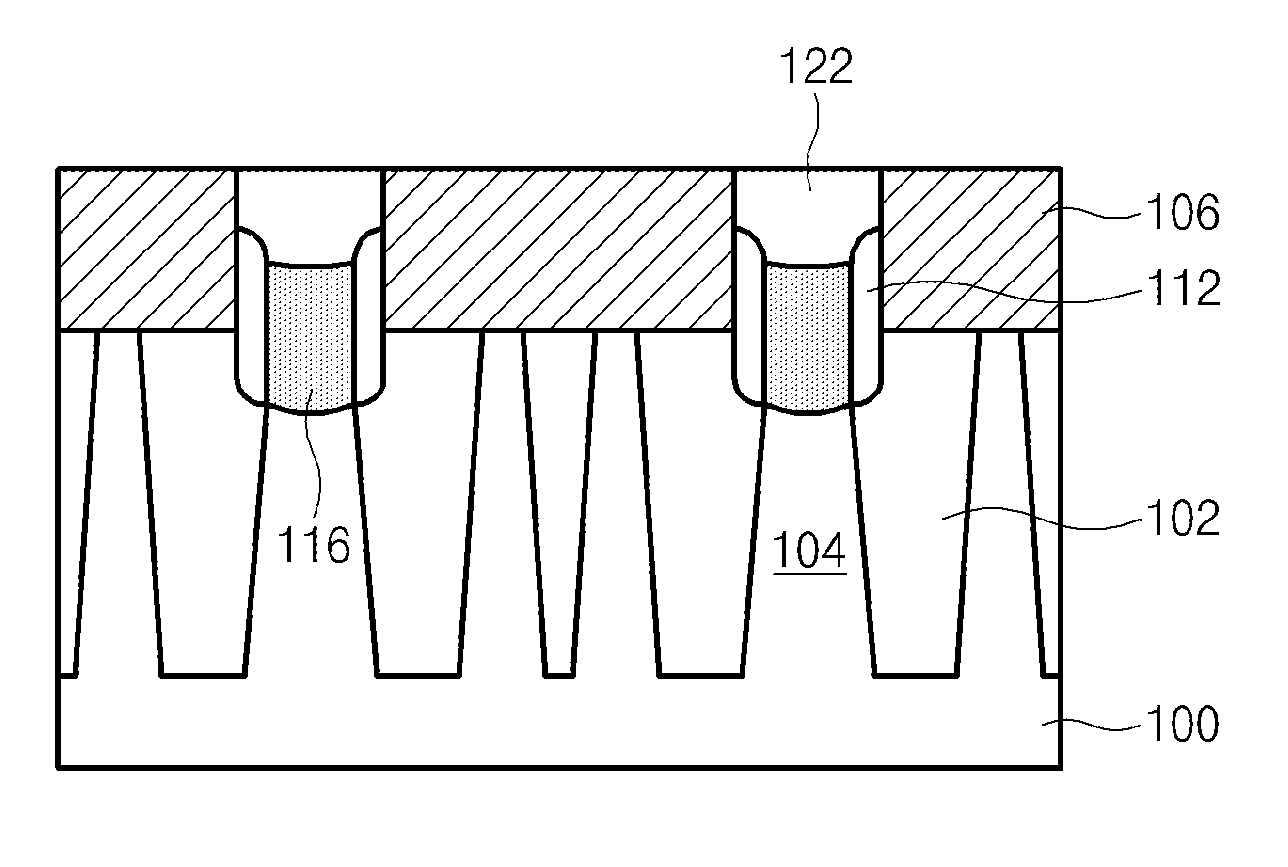

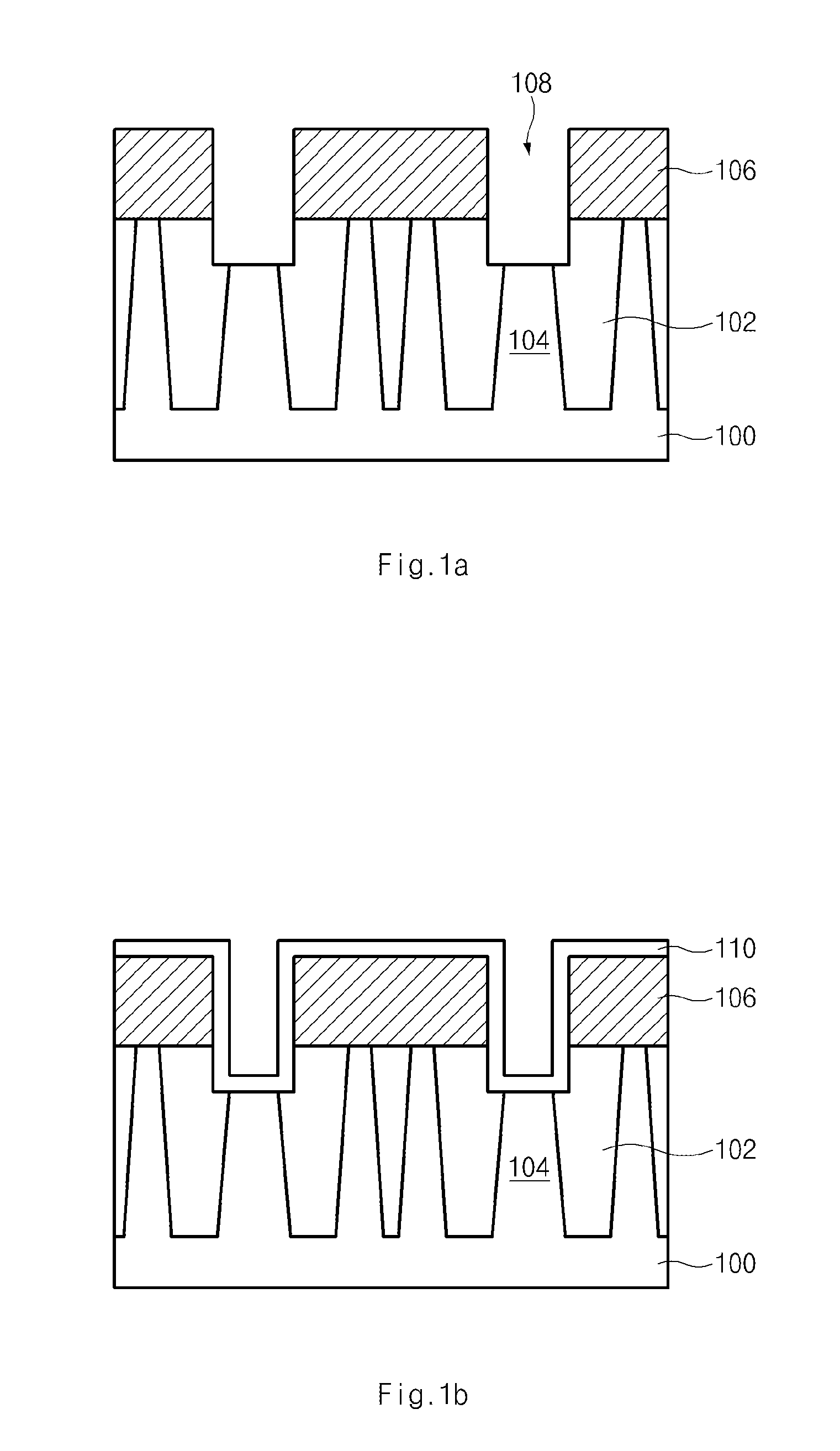

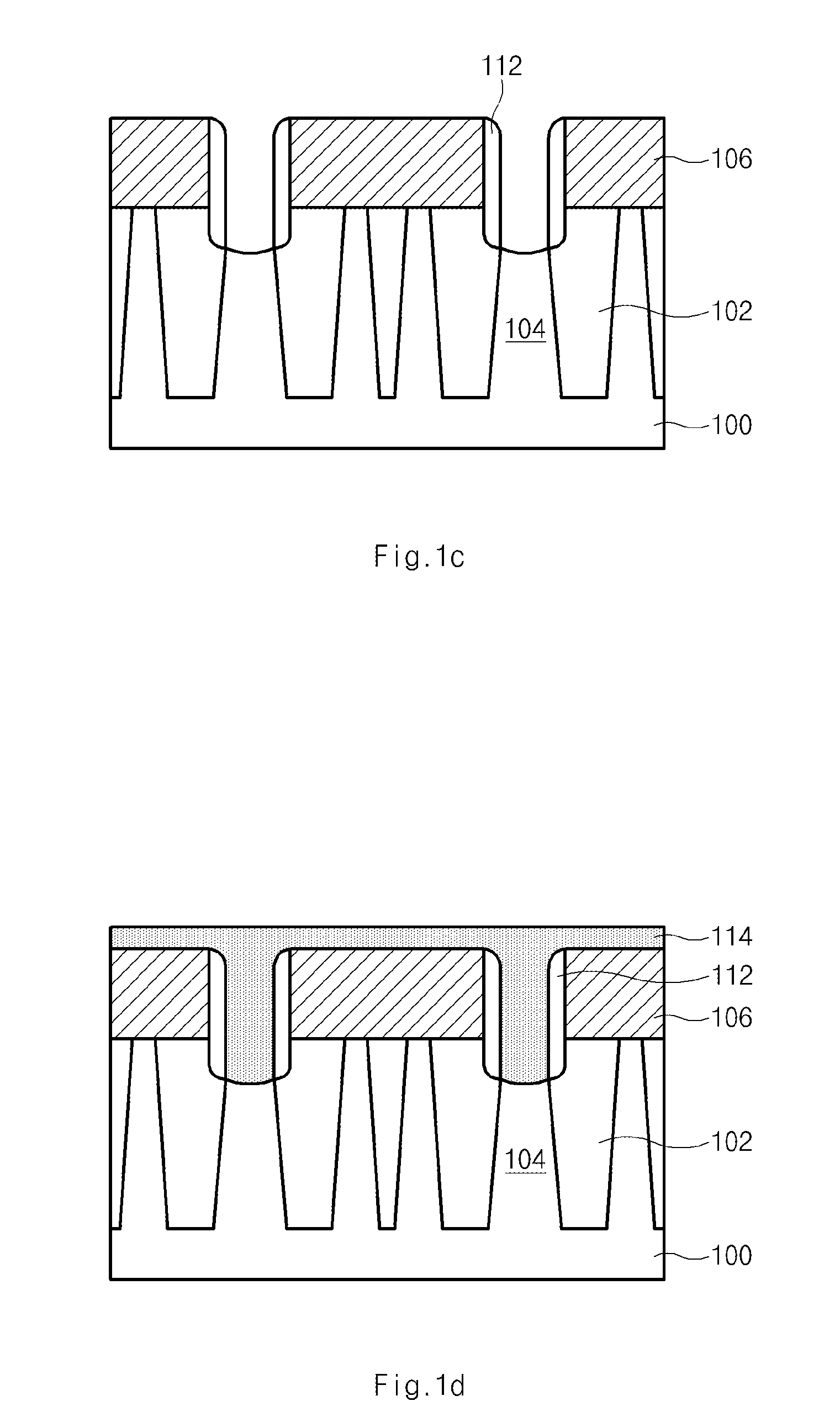

Method for fabricating semiconductor device

ActiveUS20110169174A1Increase resistanceIncrease bit widthSemiconductor/solid-state device detailsSolid-state devicesPhysicsSemiconductor

A method for forming a semiconductor device is disclosed. A method for forming a semiconductor device includes forming a first bit line contact over a semiconductor substrate, forming a second bit line contact that is coupled to the first bit line contact and has a larger width than the first bit line contact, and forming a bit line over the second bit line contact. When using the semiconductor device having a buried gate, although the bit line is formed to have a small width and the bit line pattern is misaligned, the method prevents incorrect coupling between a bit line and a bit line contact, so that it basically deteriorates unique characteristics of the semiconductor device.

Owner:SK HYNIX INC

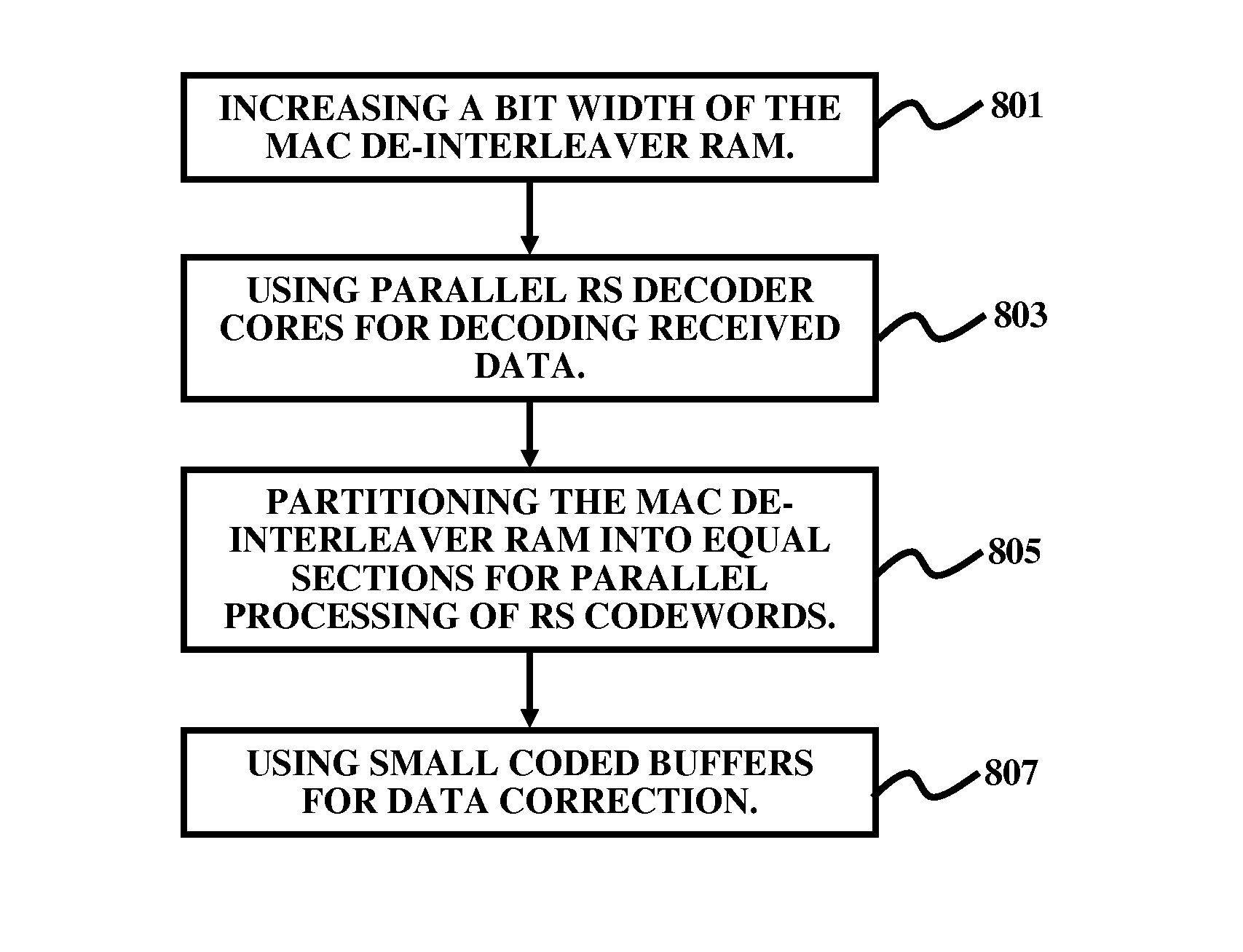

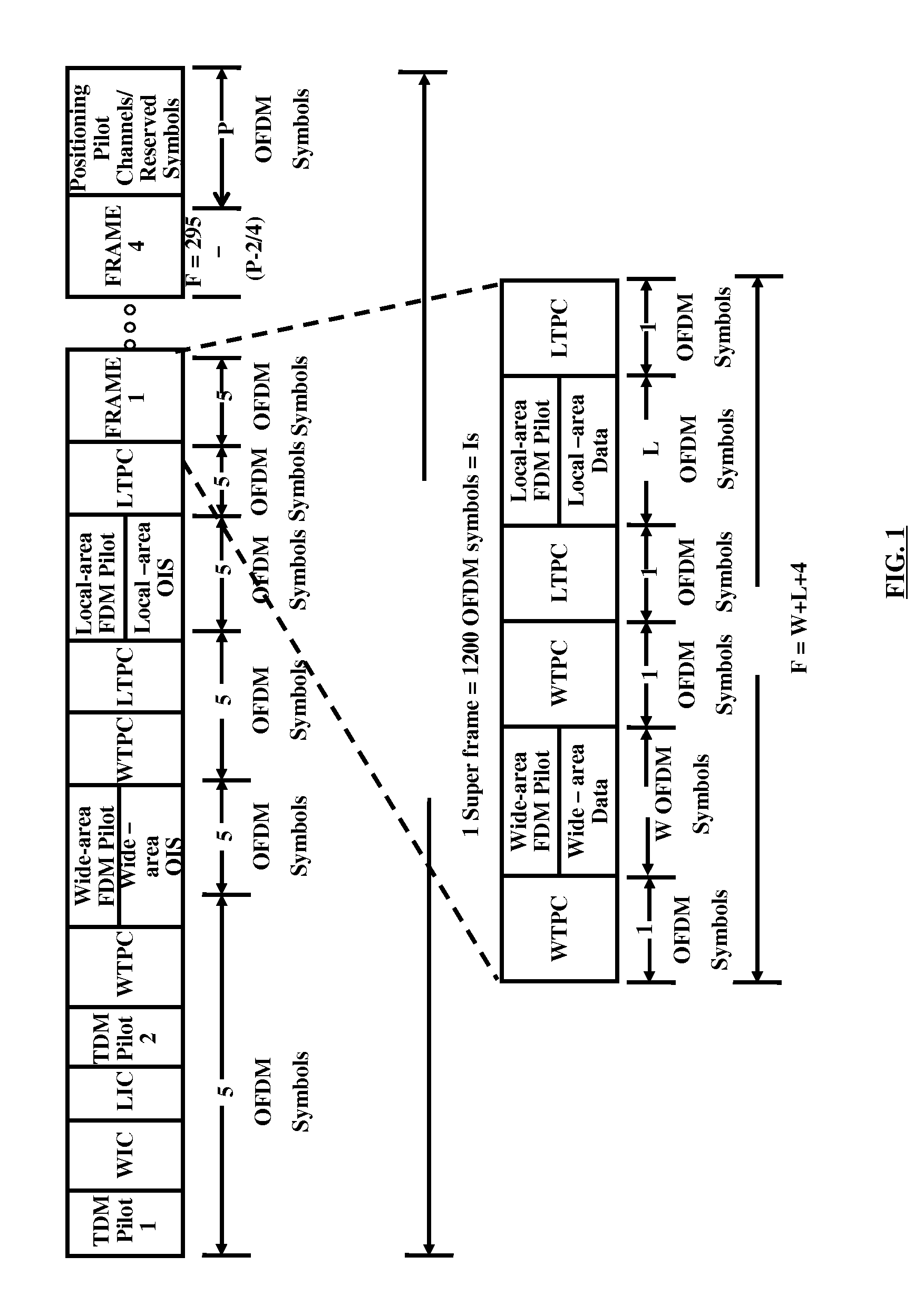

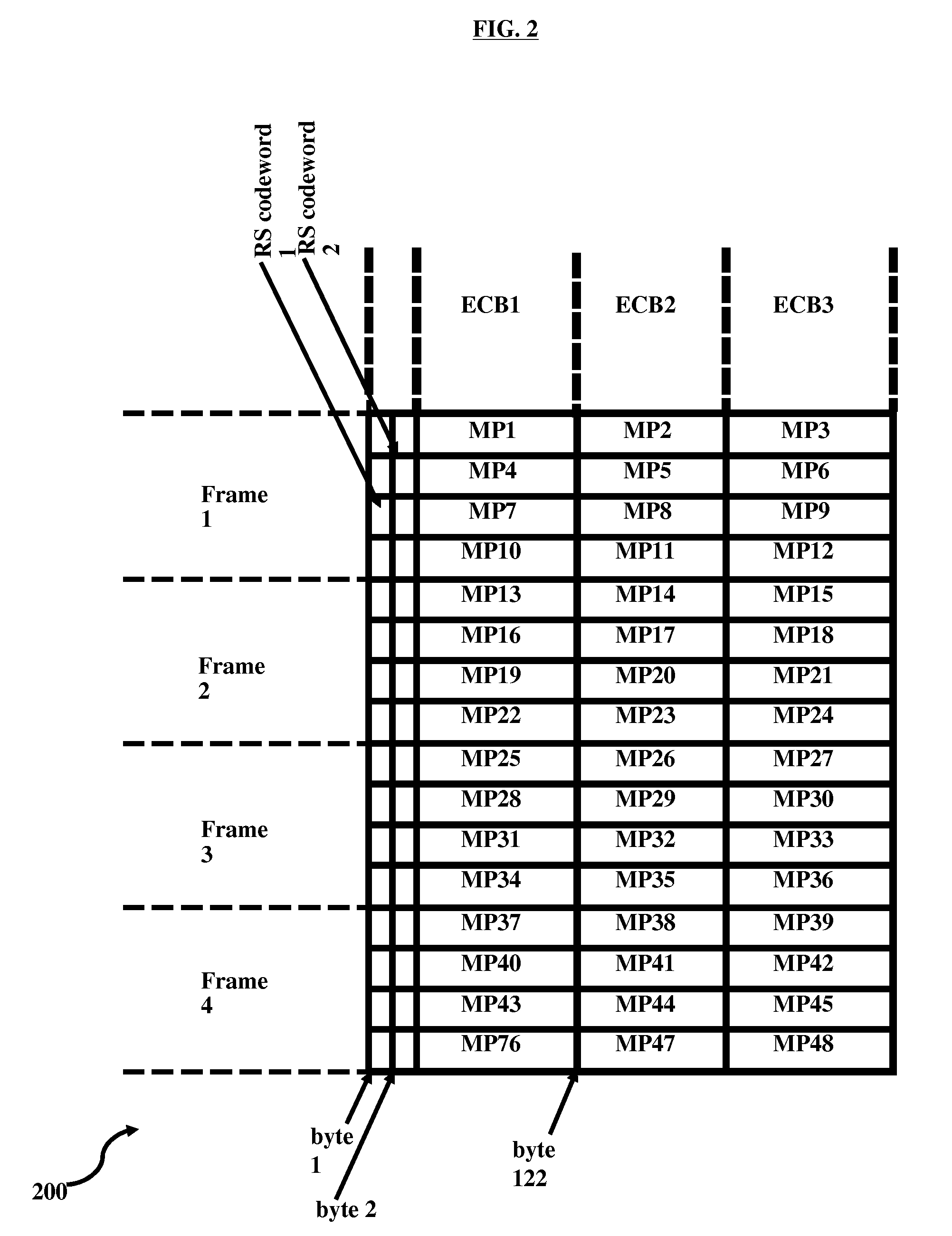

Memory architecture for high throughput RS decoding for MediaFLO receivers

InactiveUS8103944B2Improve throughputIncrease bit widthCode conversionCoding detailsMemory bankClock rate

A system and method for increasing the throughput of a RS decoder in MediaFLO™ receivers. A MAC de-interleaver RAM architecture allowing operation of parallel RS decoders comprises of four equal portioned memory banks, a codeword buffer for data correction, and a higher bit width RAM. The method of increasing throughput of RS decoder by minimizing RAM access and clock frequency includes increasing the bit width of the de-interleaver RAM, using parallel RS decoder cores for decoding received data, partitioning a 4-bank RAM and ECB allocation scheme, and correcting the data using intermediate buffers. The architecture enables on-chip implementation of the MAC de-interleaver RAM and RS decoders with reduced power consumption and provide higher RS decoder throughput.

Owner:ATMEL CORP

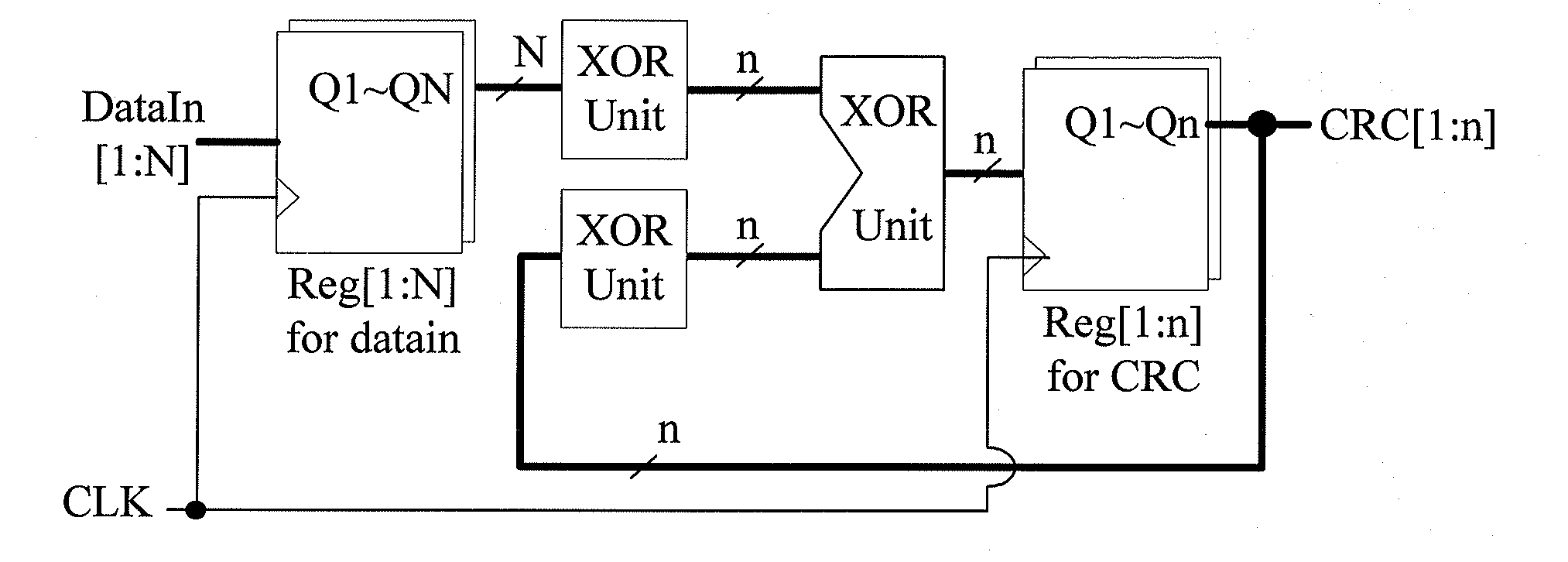

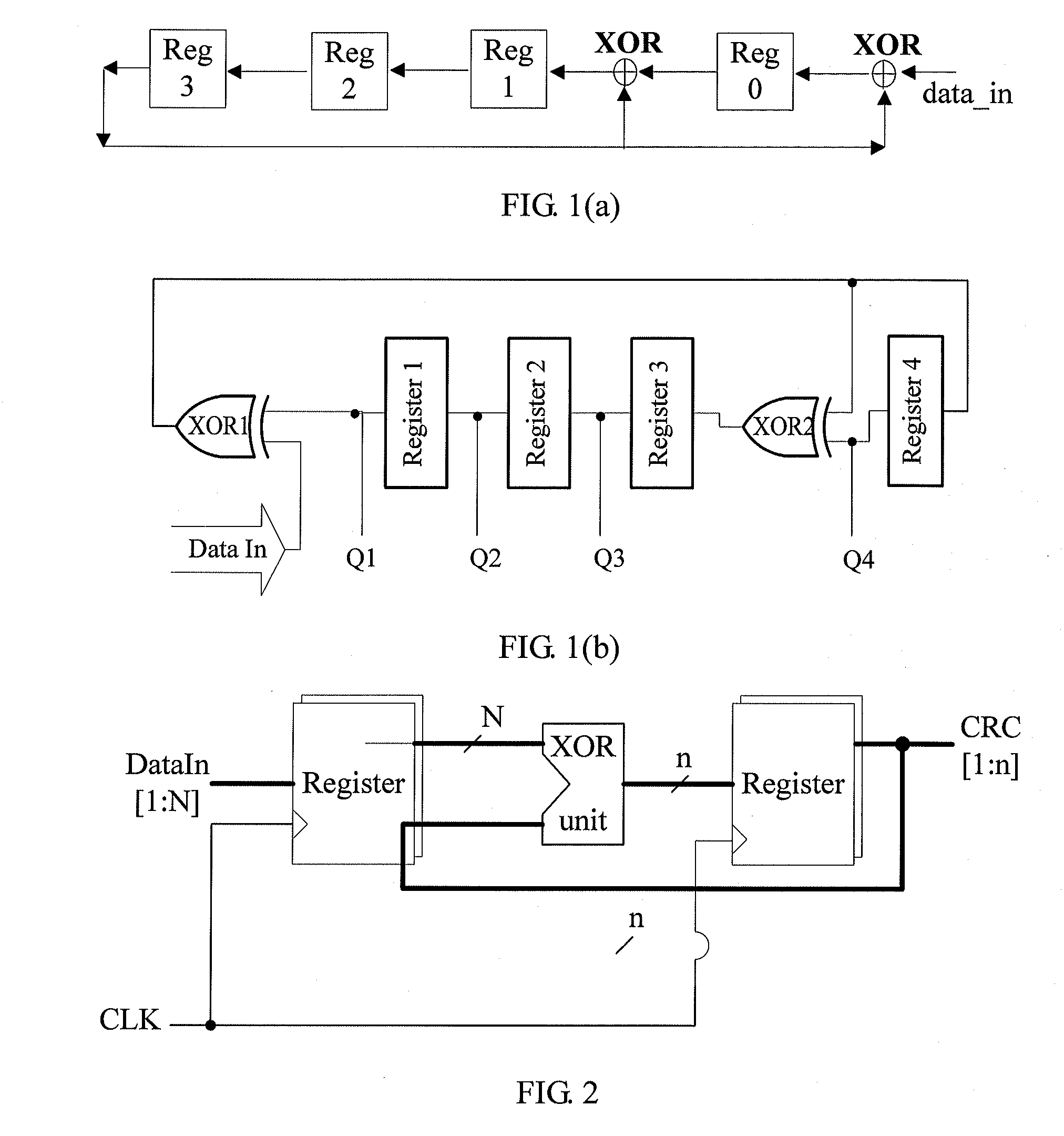

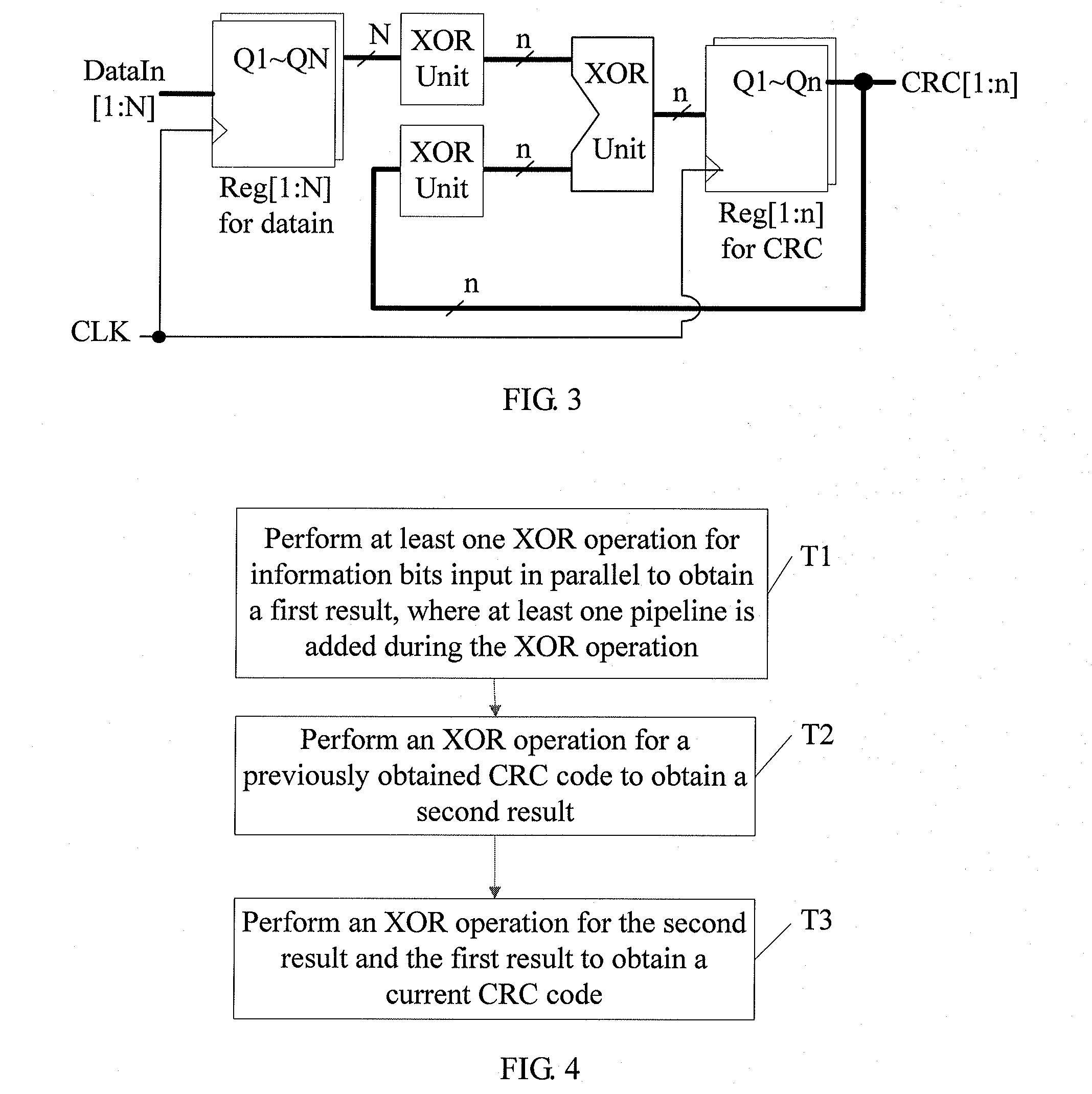

Method and device for implementing cyclic redundancy check codes

ActiveUS20120030548A1Improve business performanceIncrease clock frequencyCode conversionError detection onlyCommunications systemHigh rate

The present invention relates to an error control technology in the communication system and discloses a method and an apparatus for implementing Cyclic Redundancy Check (CRC) codes to improve the operation performance of the system significantly and satisfy operation requirements when processing high-rate CRC data. The method includes: performing at least one XOR operation for information bits input in parallel to obtain a first result, where at least one pipeline is added during the XOR operation; performing an XOR operation for a previously obtained CRC code to obtain a second result; and performing an XOR operation for the second result and the first result to obtain a current CRC code. The present invention is applicable to any field that needs to implement CRC codes by means of hardware.

Owner:HUAWEI TECH CO LTD

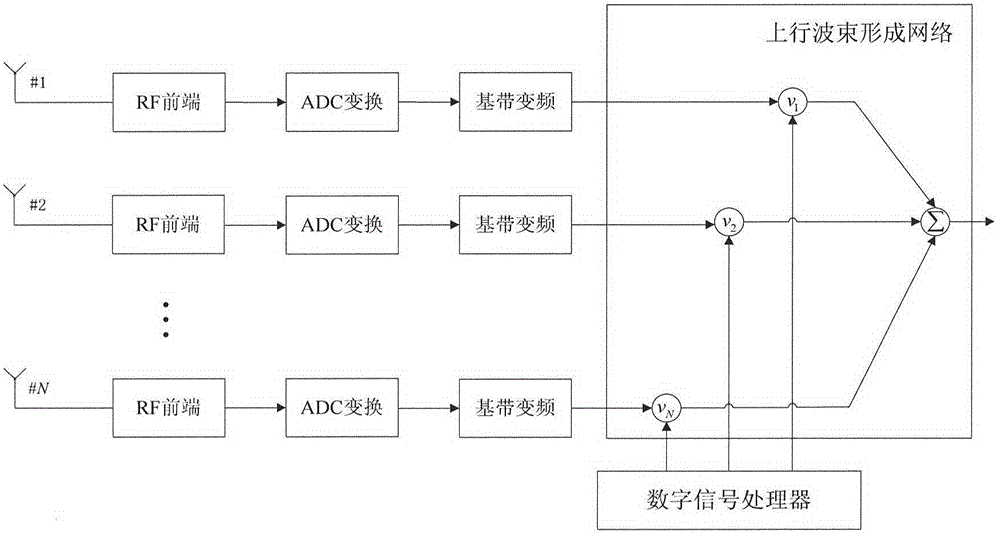

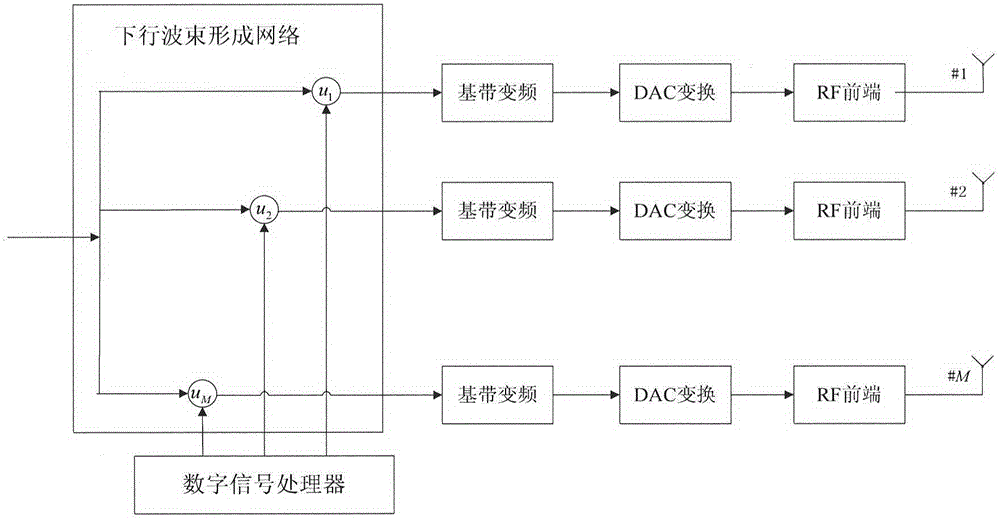

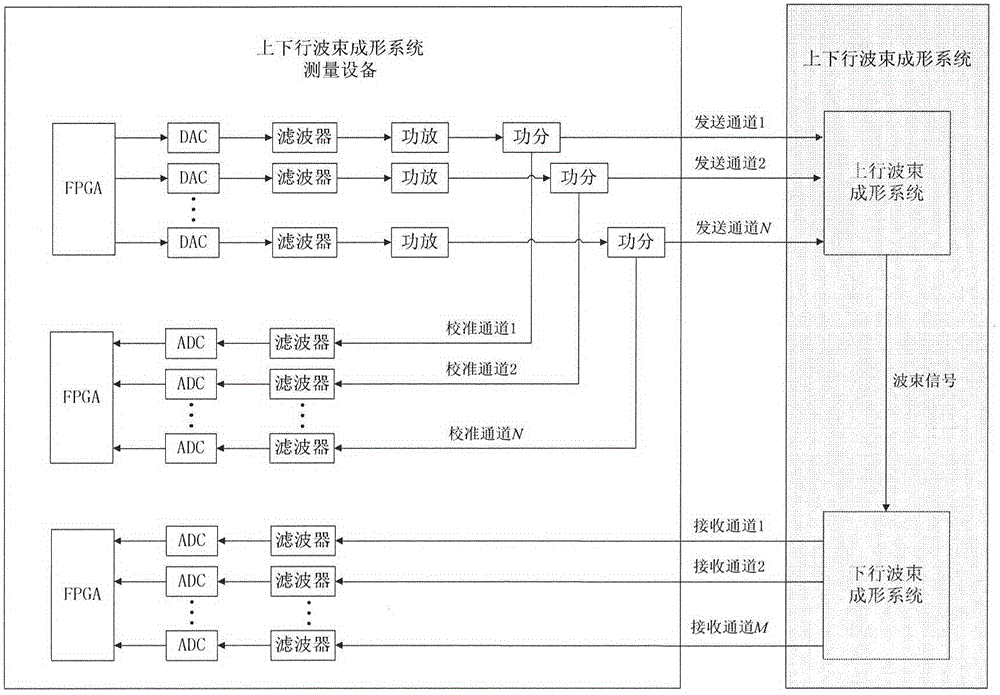

Uplink and downlink wave beam shaping measure system and method

InactiveCN105897351AIncrease bit widthImprove memory depthTransmitters monitoringSpatial transmit diversityTest efficiencyTransmission matrix

The present invention provides an uplink and downlink wave beam shaping measure system and method. The uplink and downlink wave beam shaping measure system and method are able to measure and obtain the transmission matrix of a whole wave beam shaping system based on a software radio technology. The system comprises: a sending terminal of an uplink wave beam shaping system, wherein a sending channel is connected with a calibration channel of a sending channel amplitude consistency calibration network and the receiving channel of the feed source matrix of the uplink wave beam shaping network; the sending channel amplitude consistency calibration network employing an online calibration mode; and a downlink wave beam shaping system receiving terminal, wherein the receive channel is connected with the sending channel of the feed source matrix of the downlink wave beam shaping network. The uplink and downlink wave beam shaping measure system and method are able to ensure the accurate degree of the sending terminal to send multi-path sinusoidal signal amplitude phase information and perform the calibration of sending feed source signals and the test of the receiving feed source signals at the same time so as to improve the test efficiency of the test system and effectively reduce the test workload and the test system complexity.

Owner:CHINA ACADEMY OF SPACE TECHNOLOGY

Configurable dynamical time slice round-robin scheduling algorithm

ActiveCN105824769AReasonable timeReduce overheadElectric digital data processingExtensibilityLow resource

The invention discloses a configurable dynamical time slice round-robin scheduling algorithm, which is applicable to the condition that a plurality of on-line tracking units in an on-line tracking system need to carry out data output through a single transmission interface. According to the algorithm, through configuring a corresponding threshold value, time slice length and priority, judgments in active states of the on-line tracking units are combined, and the data output request of each on-line tracking unit is arbitrated by adopting two inquiry ways. By using the configurable dynamical time slice round-robin scheduling algorithm, the synthesis on a plurality of ways of track data can be realized on premises of a low resource consumption, a low data overflow rate and a high expandability, so as to solve the scheduling problem of a plurality of data cache queues in the on-line tracking system.

Owner:HEFEI UNIV OF TECH

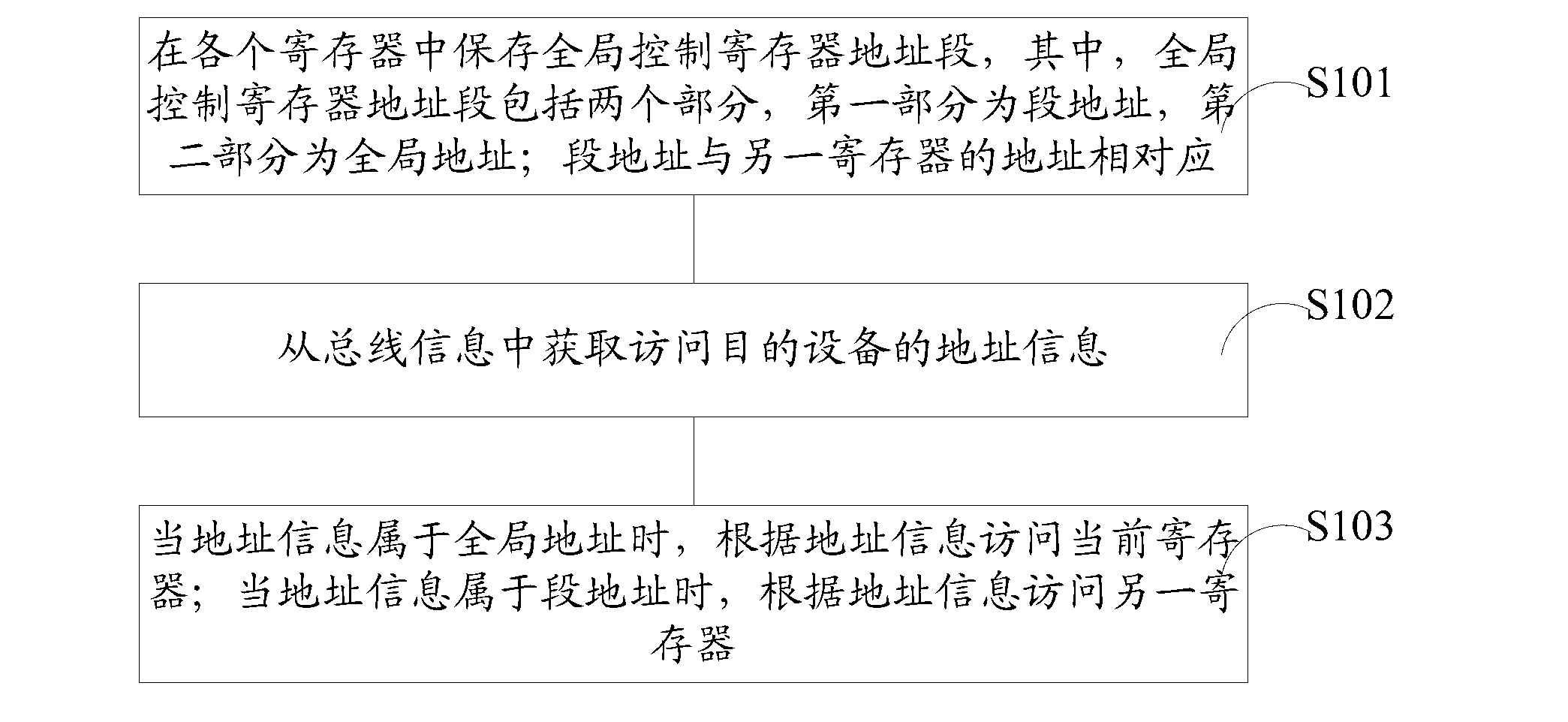

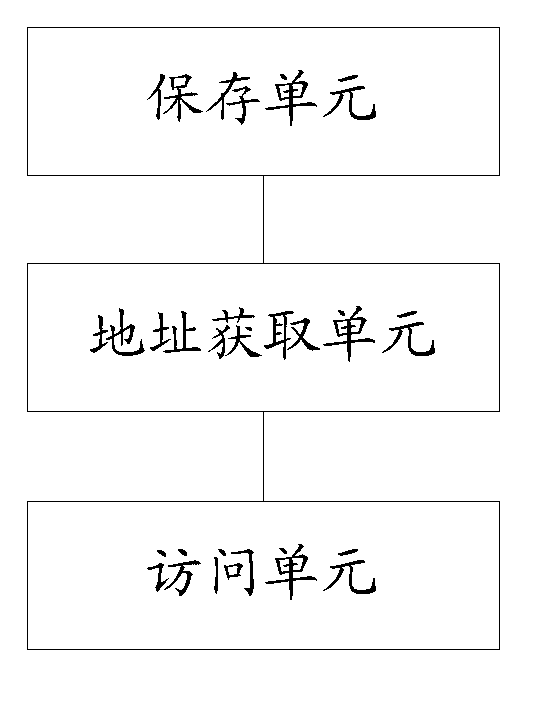

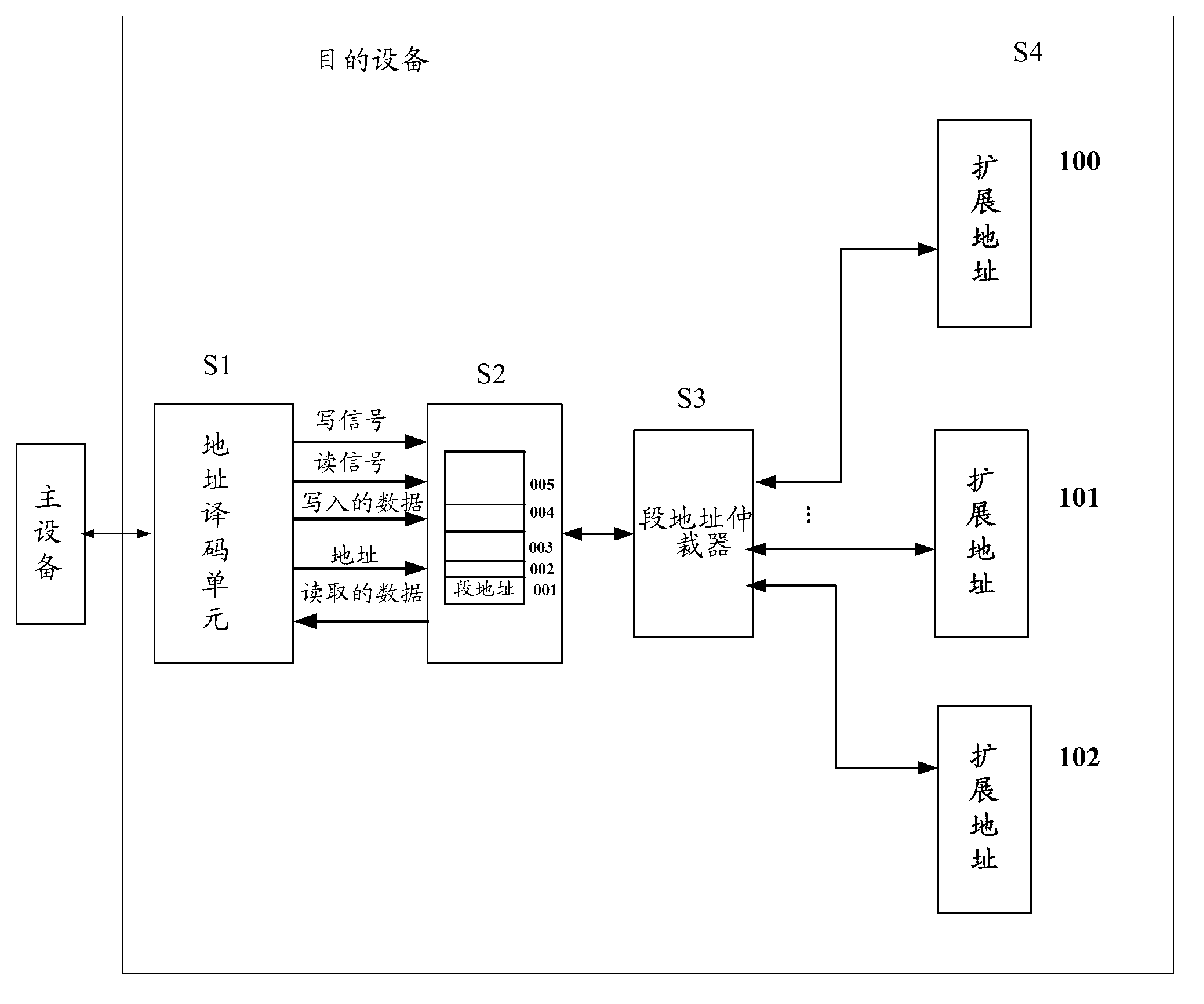

Method and device adopting bus for communication

InactiveCN103019972AIncrease bit widthIncrease the number of spacesElectric digital data processingProcessor registerControl register

The invention provides a method adopting a bus for communication. The method comprises the following steps: saving a global control register address field in each register, wherein the global control register address field comprises two parts, the first part is a segment address, the second part is a global address, and the segment address corresponds to the address of another register; acquiring the address information of visiting object equipment from bus information; visiting the current register according to the address information when the address information belongs to the global address; and visiting another register according to the address information when the address information belongs to the global address. The invention further provides a device adopting the bus for communication, so as to overcome the space limitation when the bus is used for visiting the inner address of the equipment, and improve the developing efficiency.

Owner:GUANGDONG VTRON TECH CO LTD

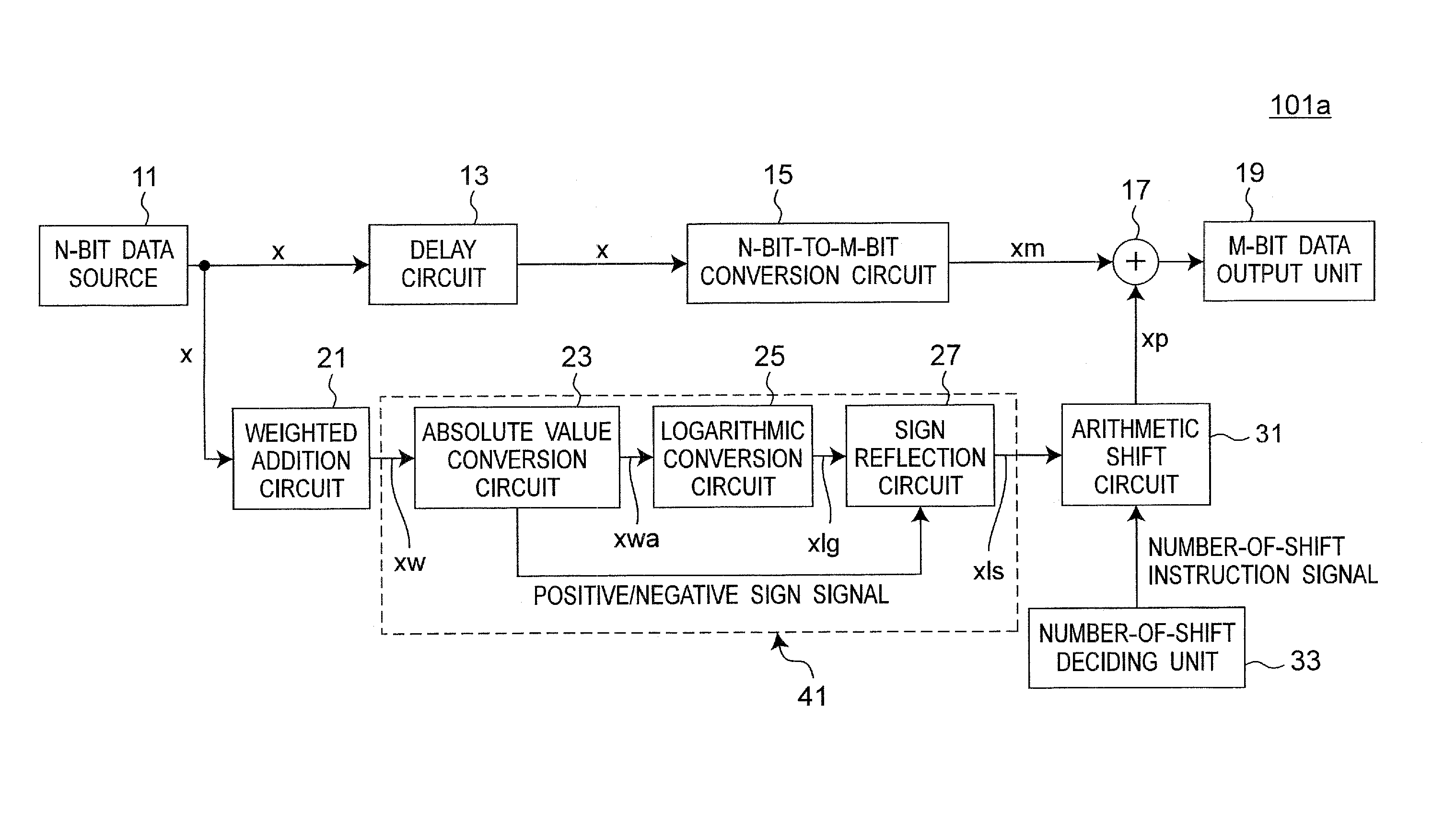

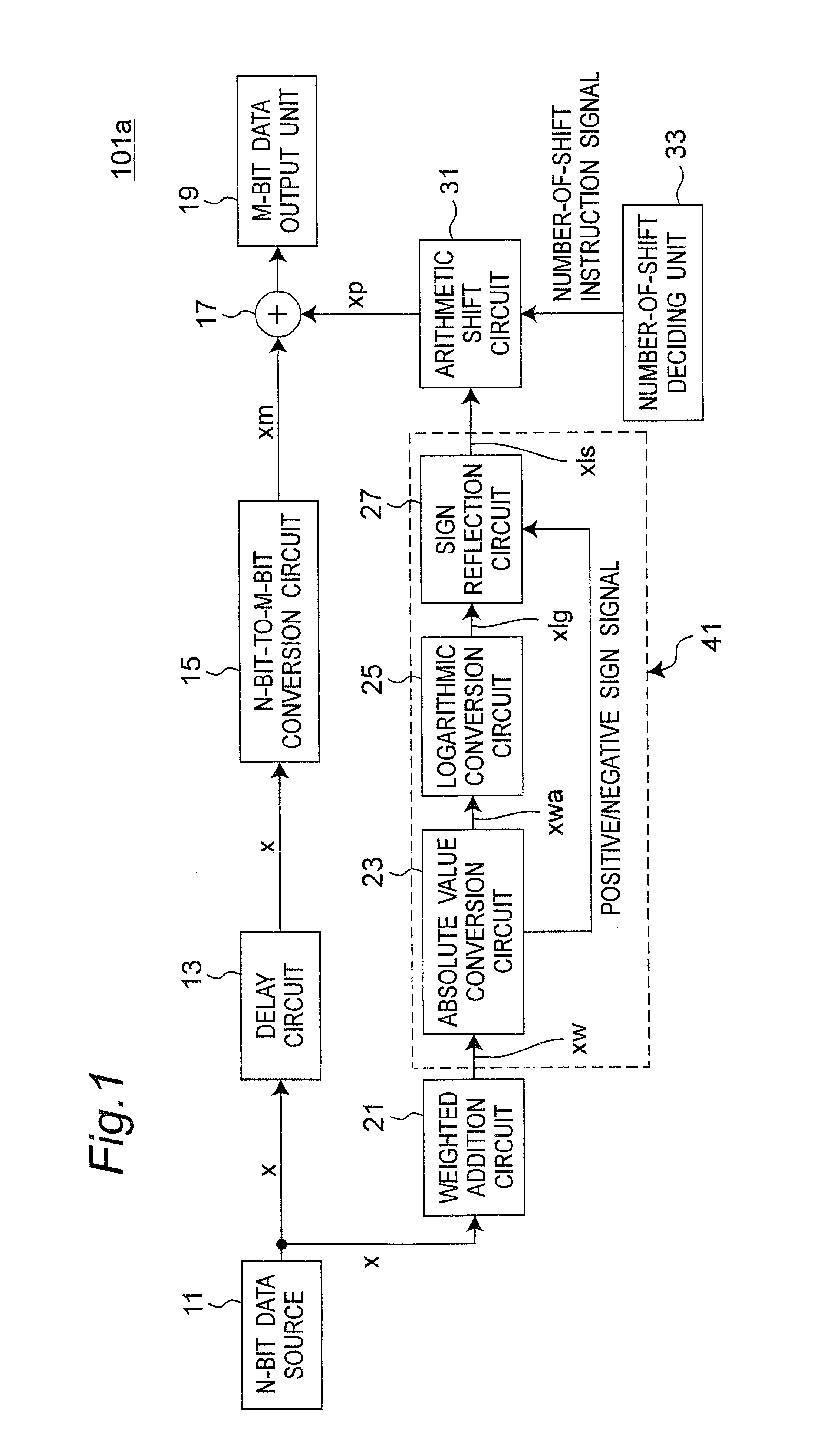

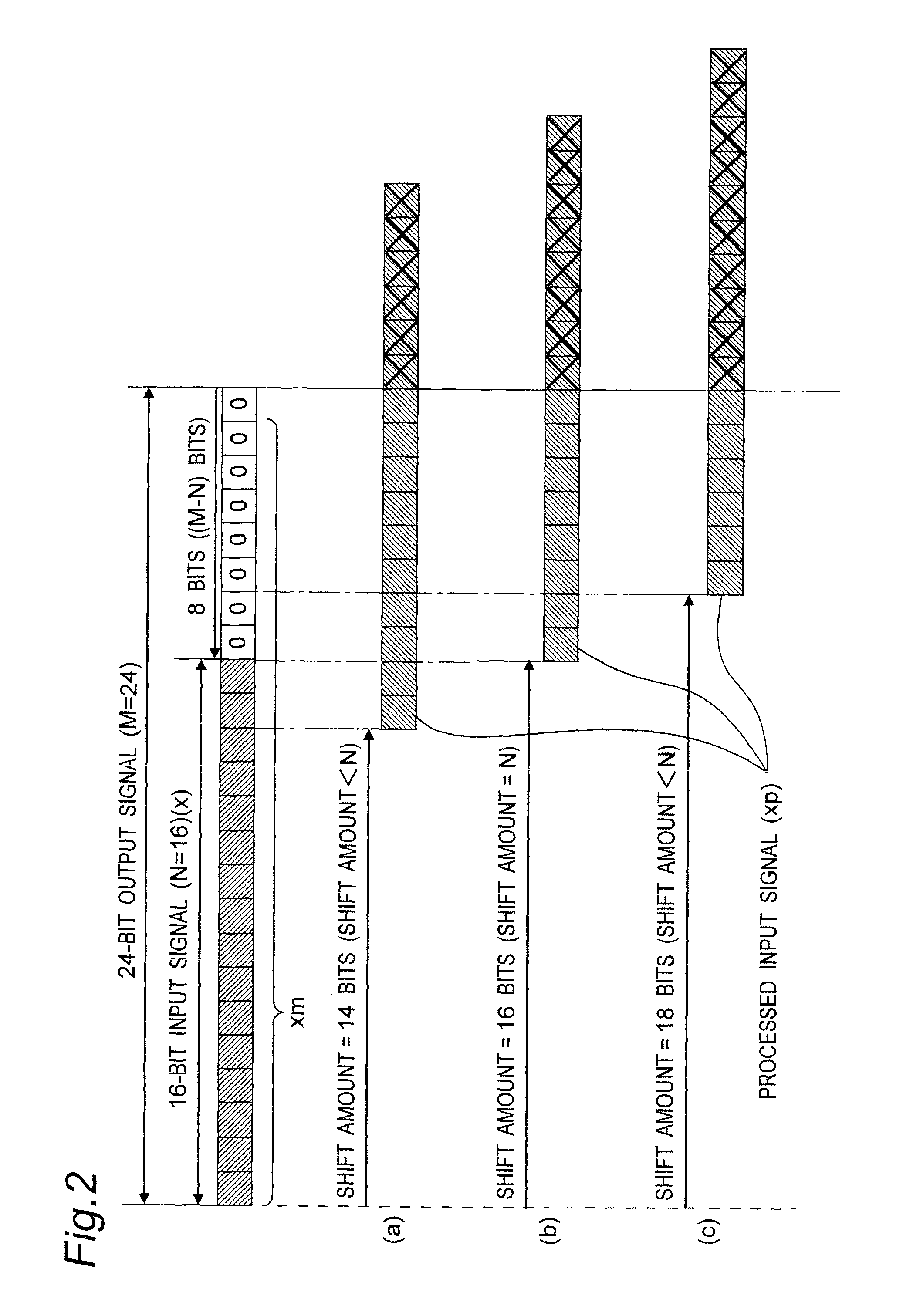

Digital data processor

ActiveUS8443017B2Calculations are simpleIncrease bit widthComputation using non-contact making devicesSpeech analysisDigital dataData source

A digital data processor which receives an N-bit input signal from a data source and converts the N-bit input signal into an M-bit output signal, the M-bit being larger than the N-bit. The digital data processor includes: an weighted addition circuit which is operable to perform weighted addition on at least the input signal and a signal being time-shifted with respect to the input signal and output as a weighted added input signal; an arithmetic shift circuit which is operable to perform an arithmetic rightward shift operation on the weighted added input signal for a predetermined number of shifts and output as a processed input signal; a bit extension circuit which is operable to attach a predetermined bits to an LSD side of the input signal to generate an intermediate signal of M bits; and an addition circuit which is operable to perform addition of the intermediate signal and the processed input signal so as to generate the M-bit output signal.

Owner:PANASONIC CORP

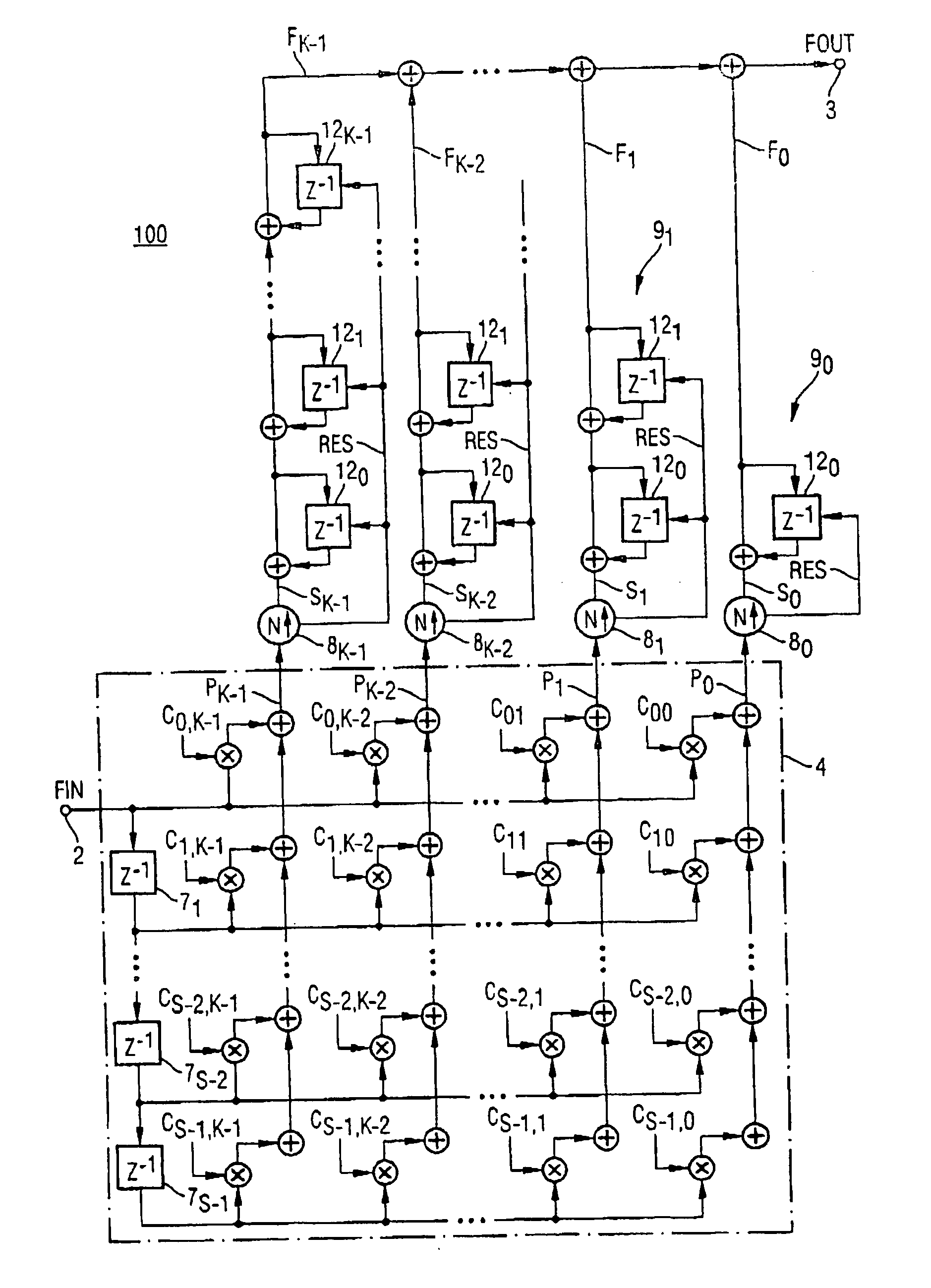

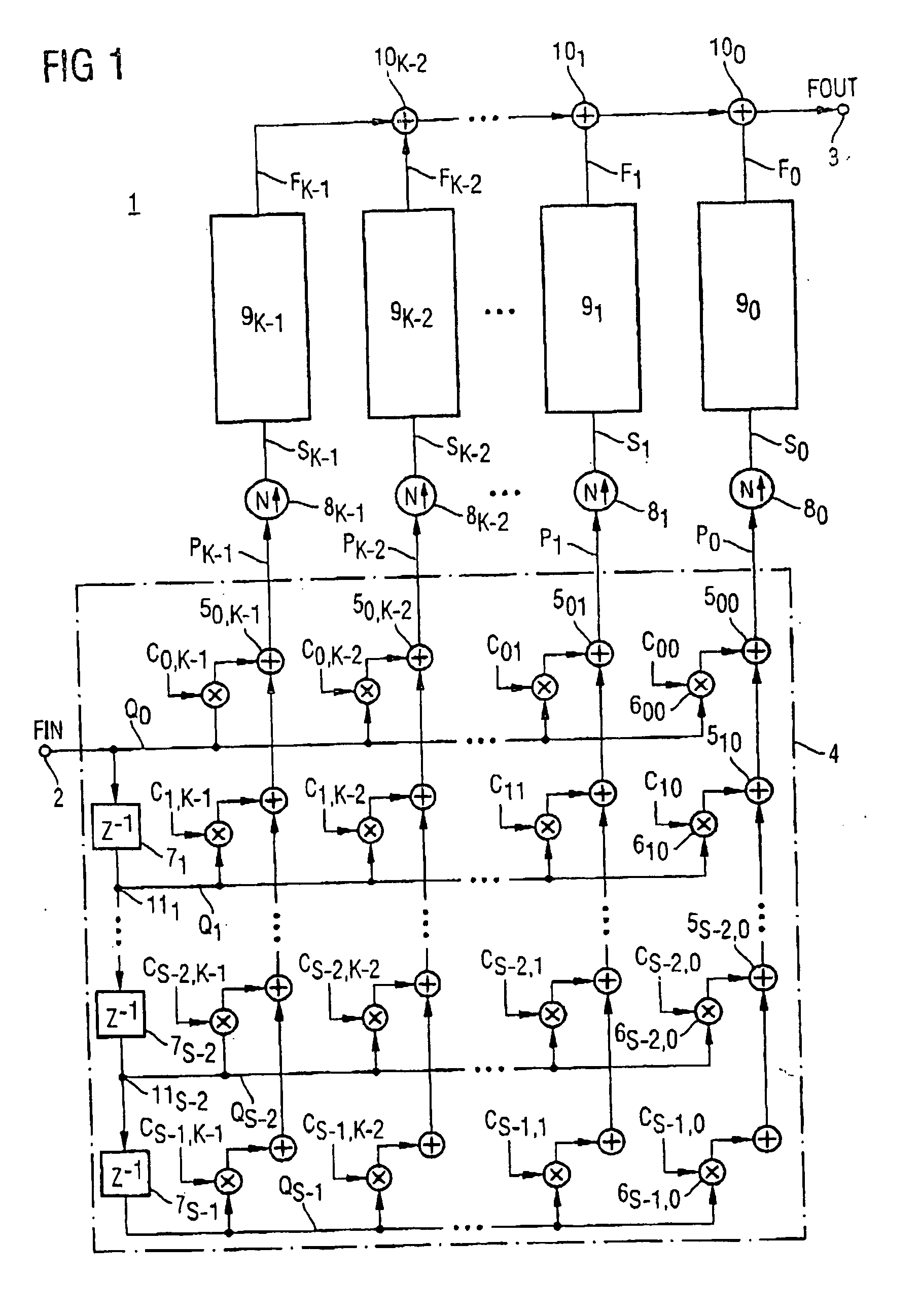

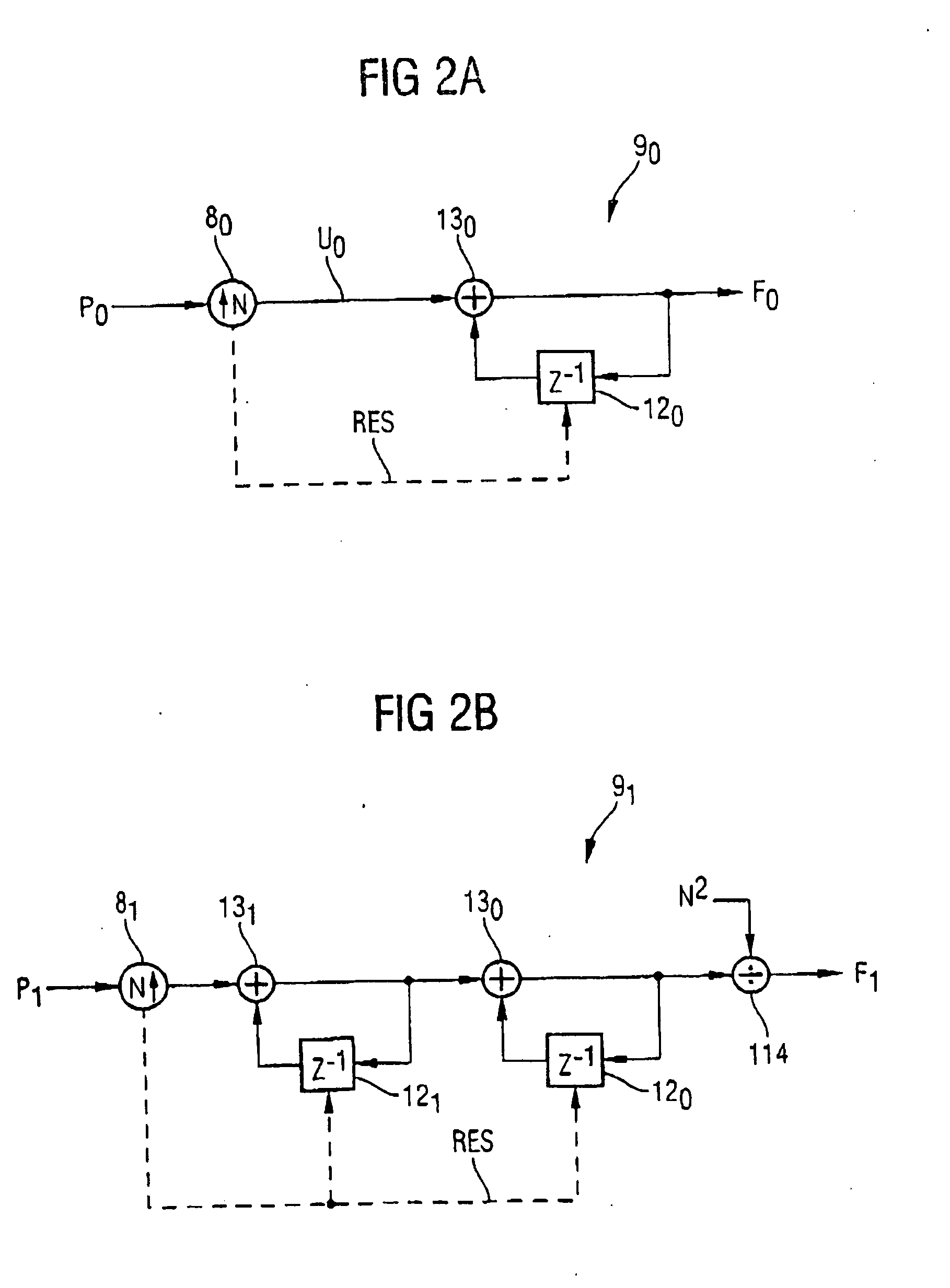

Digital filter and method for designing digital filters

InactiveUS20070220073A1Reduce clock frequencyImplementation expenditureDigital technique networkDigital data processing detailsConversion factorSample rate conversion

A digital filter comprises a plurality of filter units each realizing mutually independent filter functions with a predetermined recursive filter order on a signal path between the input and the output of the filter and operating at a first clock rate, a plurality of sampling devices operating at the first clock rate, and a weighting network coupled to the sampling devices and operating at a second clock rate. The filter units comprise at least one delay element which can be reset to a predeterminable value. To each of the filter units one of the sampling devices is allocated setting the respective delay element to a predetermined value dependent on a sampling rate conversion factor. An input signal is conducted, via the weighting network, to a respective sampling device, or digital internal sampling signals output by a respective sampling device are conducted to the output via the weighting network.

Owner:LANTIQ BET GMBH & CO KG

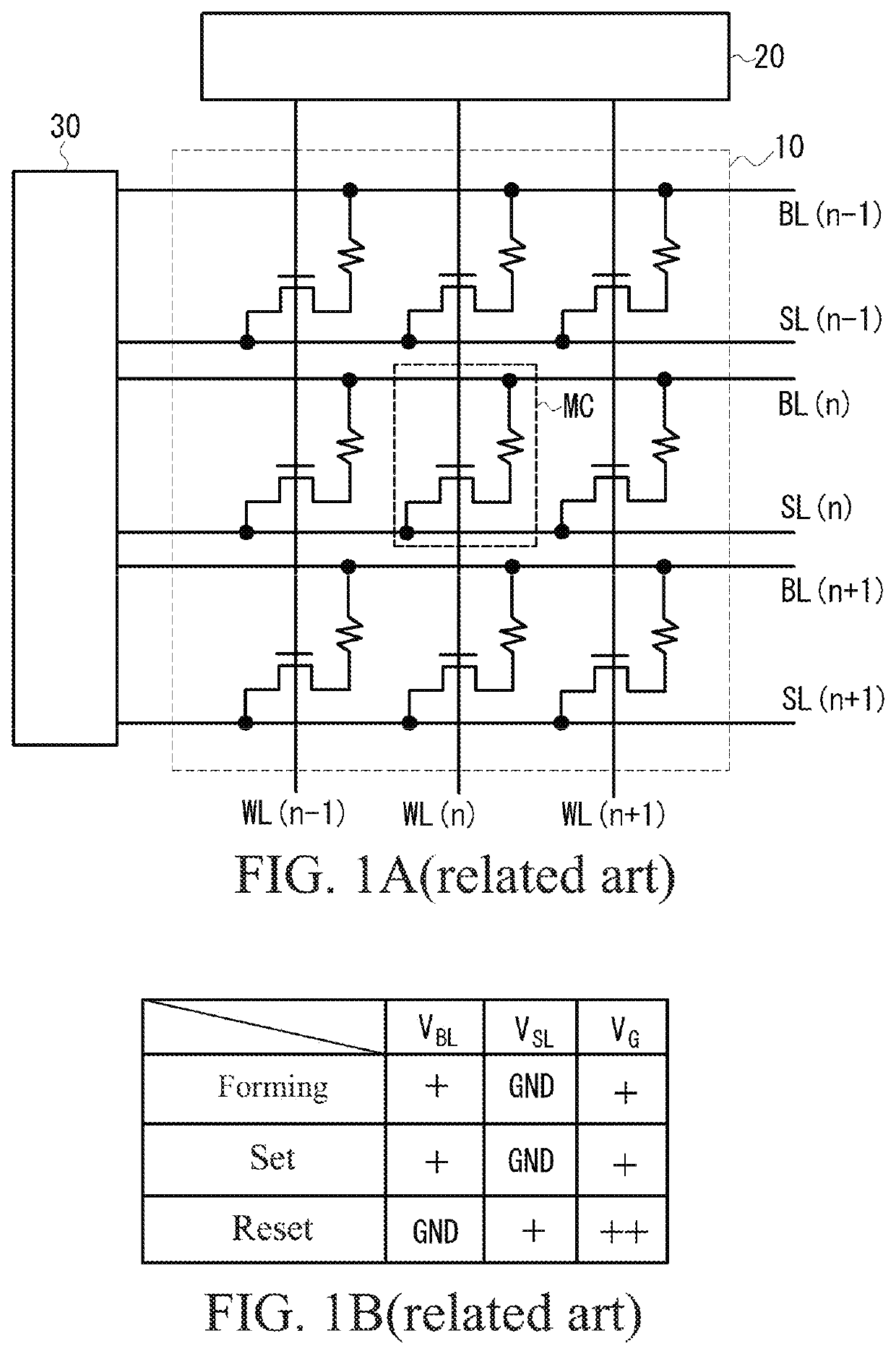

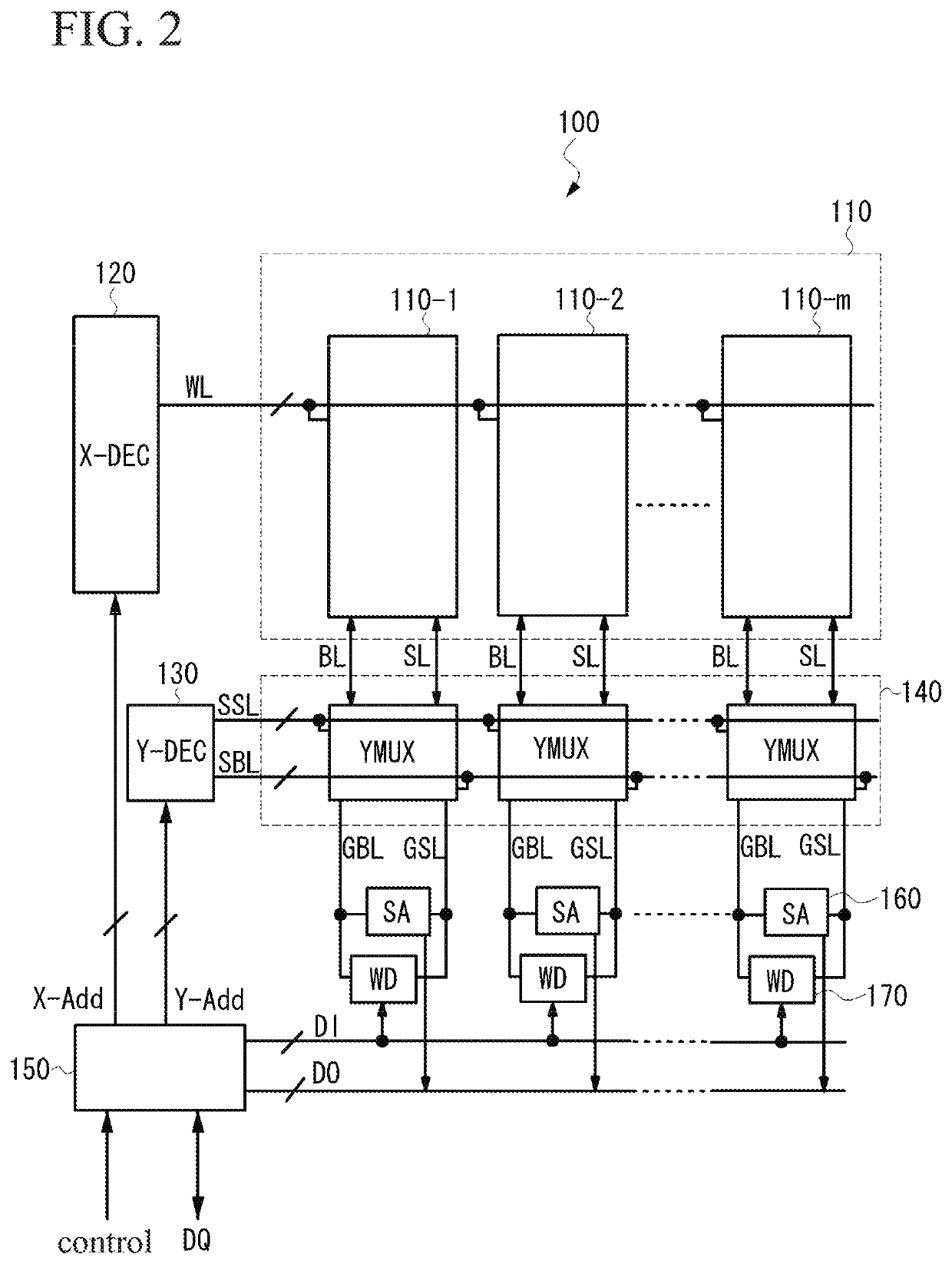

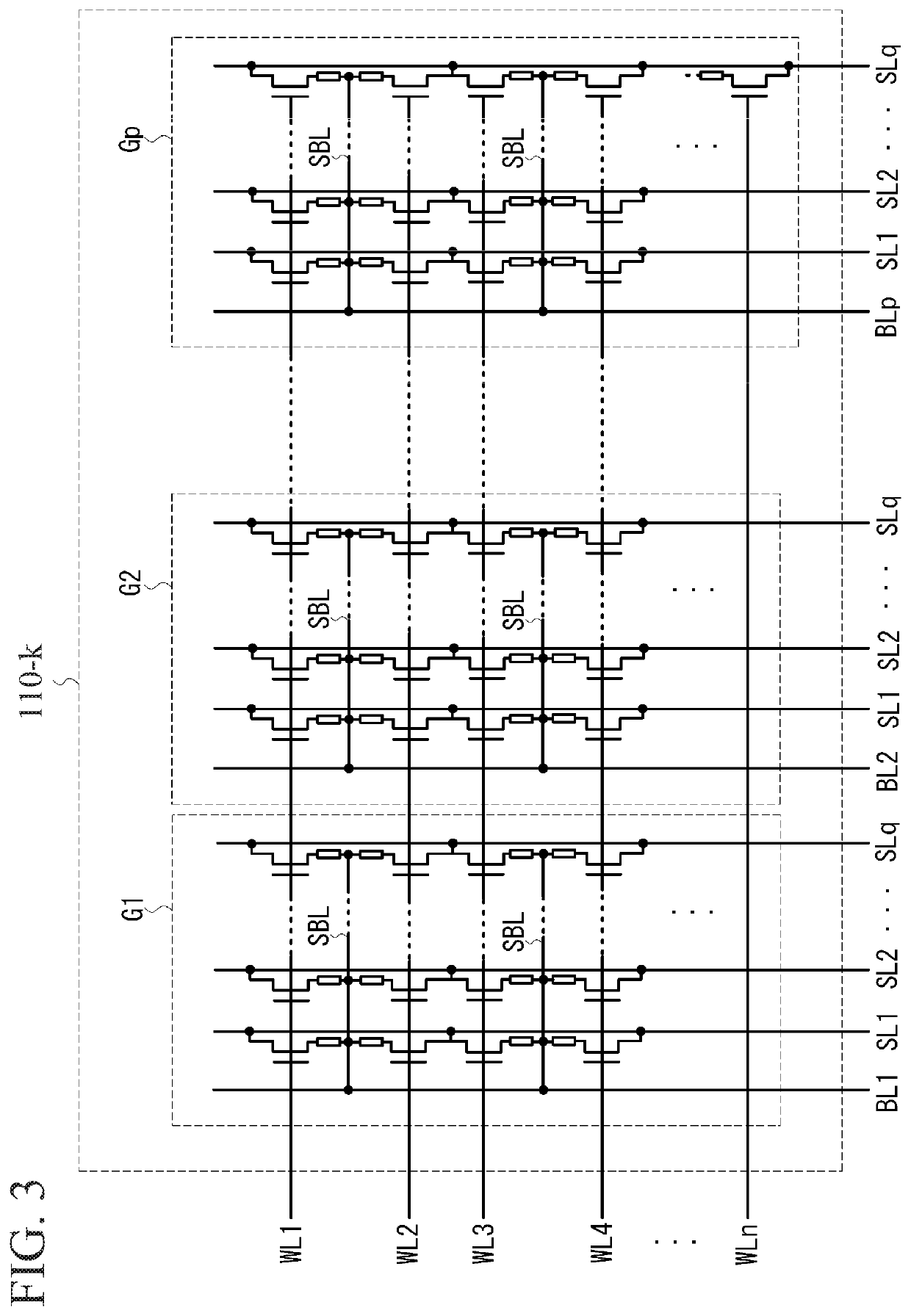

Resistive memory

ActiveUS20200111836A1Improve reliabilityAchieve symmetrySemiconductor/solid-state device detailsSolid-state devicesComputer hardwareBit line

The invention provides a resistive memory with better area efficiency without degrading reliability, which includes an array area, word lines, a local bit line, source lines, and a shared bit line. In the array area, memory cells are arranged in a matrix, and each memory cells includes a variable resistance element and an accessing transistor. The word lines extend in a row direction of the array area and are connected to the memory cells in the row direction. The local bit line extends in a column direction of the array area. The source lines extend in the column direction and are connected to first electrodes of the memory cells in the column direction. The shared bit line is connected to the local bit line. The shared bit line extends in the row direction and is connected to second electrodes of the memory cells in the row direction.

Owner:WINBOND ELECTRONICS CORP

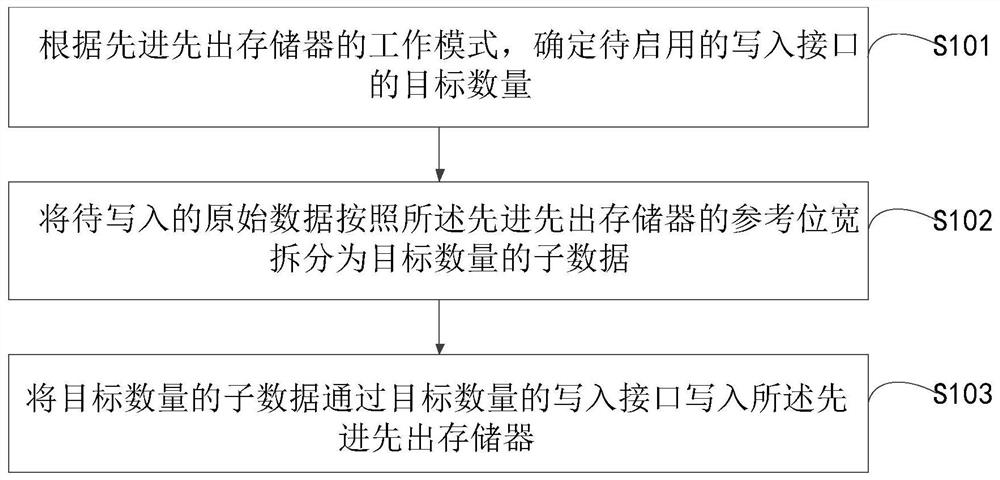

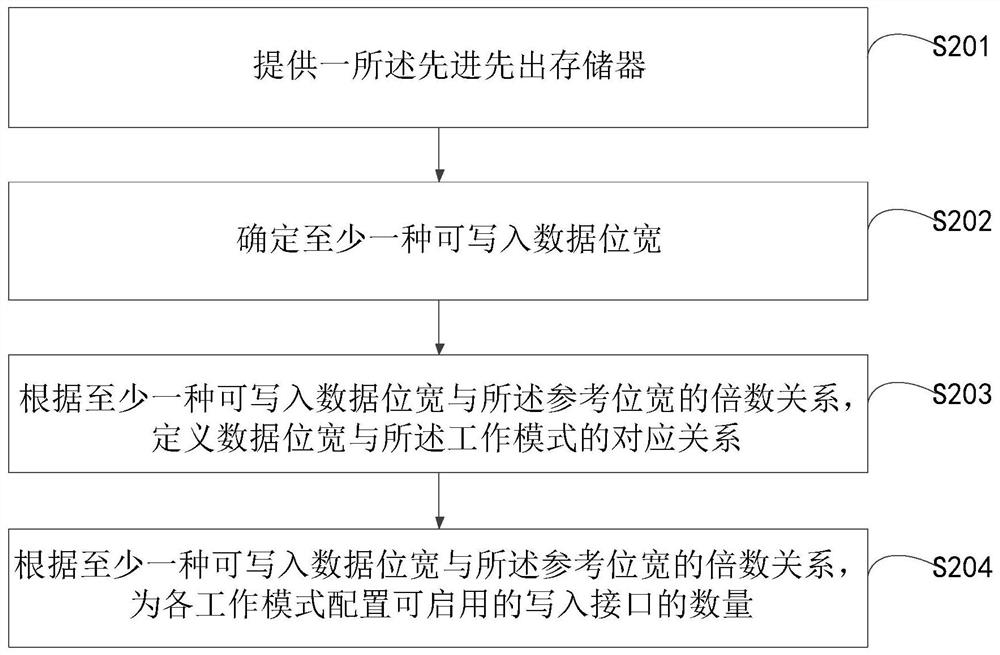

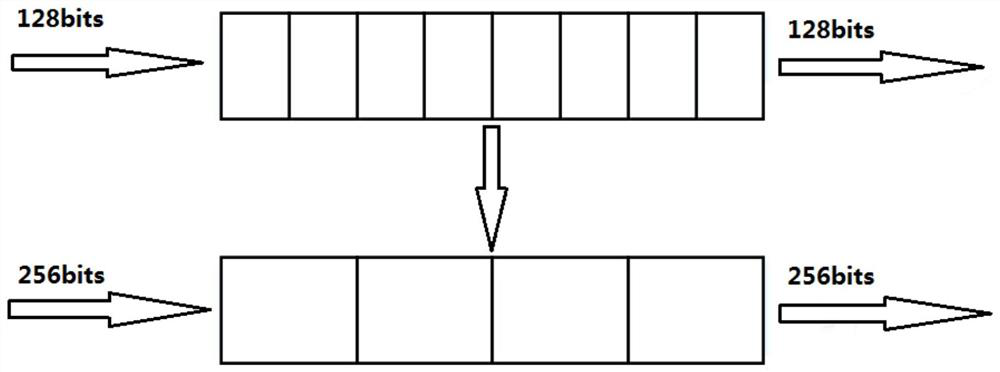

Data writing method, data reading method and first-in first-out memory

PendingCN113485647AReduce in quantitySave resourcesInput/output to record carriersData conversionComputer hardwareComputer engineering

The embodiment of the invention discloses a data writing method, a data reading method and a first-in first-out memory, and the data writing method comprises the steps: determining a target number of to-be-started writing interfaces according to a working mode of the first-in first-out memory; splitting to-be-written original data into a target number of sub-data according to the reference bit width; and writing the target number of sub-data into the first-in first-out memory through the target number of write-in interfaces. The data reading method comprises the steps of determining a target number of to-be-started reading interfaces according to a working mode of a first-in first-out memory; reading the target number of to-be-read sub-data from the first-in first-out memory through the target number of read-out interfaces; and splicing the target number of sub-data into original data. According to the invention, one first-in first-out memory is utilized to meet the requirements of different application scenes, the number of first-in first-out memories in a chip is reduced, resources are saved, the area of the chip is reduced, and meanwhile, expansion of various bit widths and depths can be carried out.

Owner:HUNAN GOKE MICROELECTRONICS

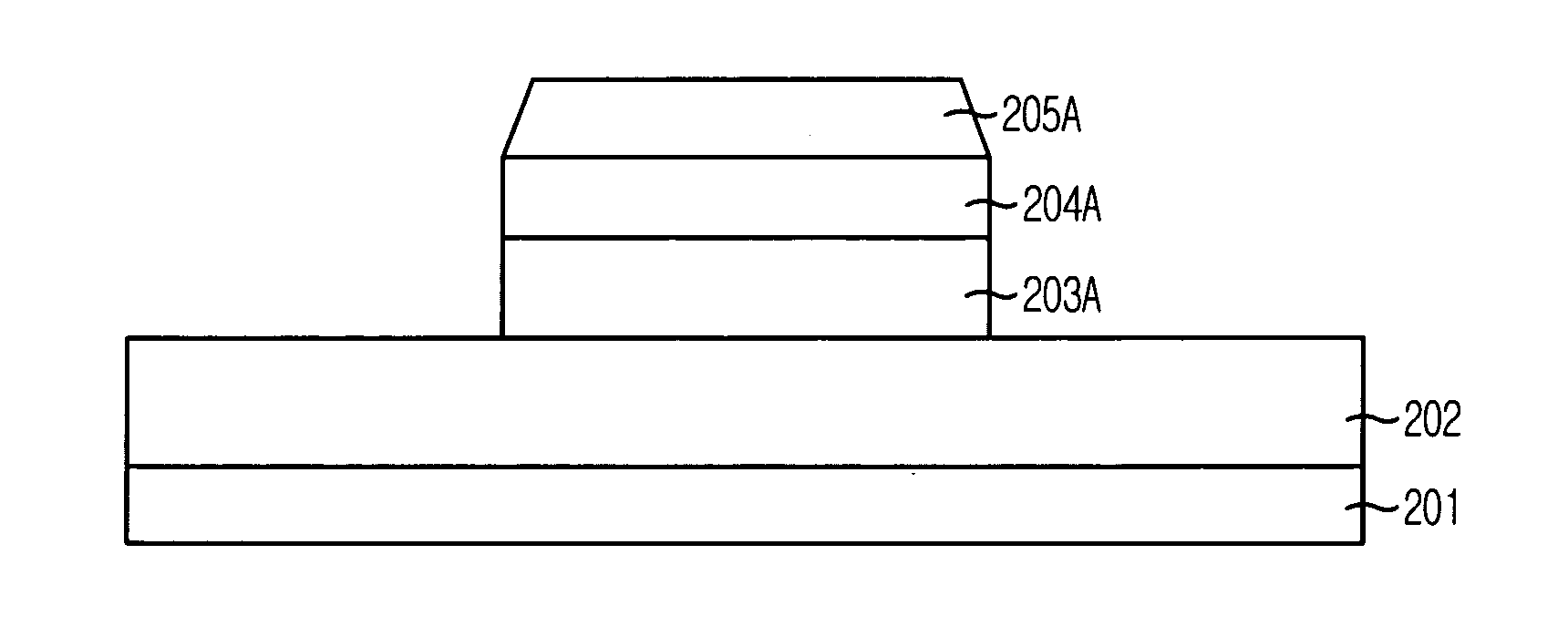

Method for fabricating semiconductor device

InactiveUS20060292886A1Increase line widthIncrease bit widthSolid-state devicesSemiconductor/solid-state device manufacturingLine widthAnti-reflective coating

A method for fabricating a semiconductor device is provided. The method includes sequentially forming etch target layers, a hard mask layer and an anti-reflective coating layer, selectively etching the anti-reflective coating layer and the hard mask layer using a gas generating polymers, thereby increasing a line width of a bottom portion of the hard mask layer due to the polymers, and etching the etch target layers using a patterned hard mask layer with the increased line width.

Owner:SK HYNIX INC

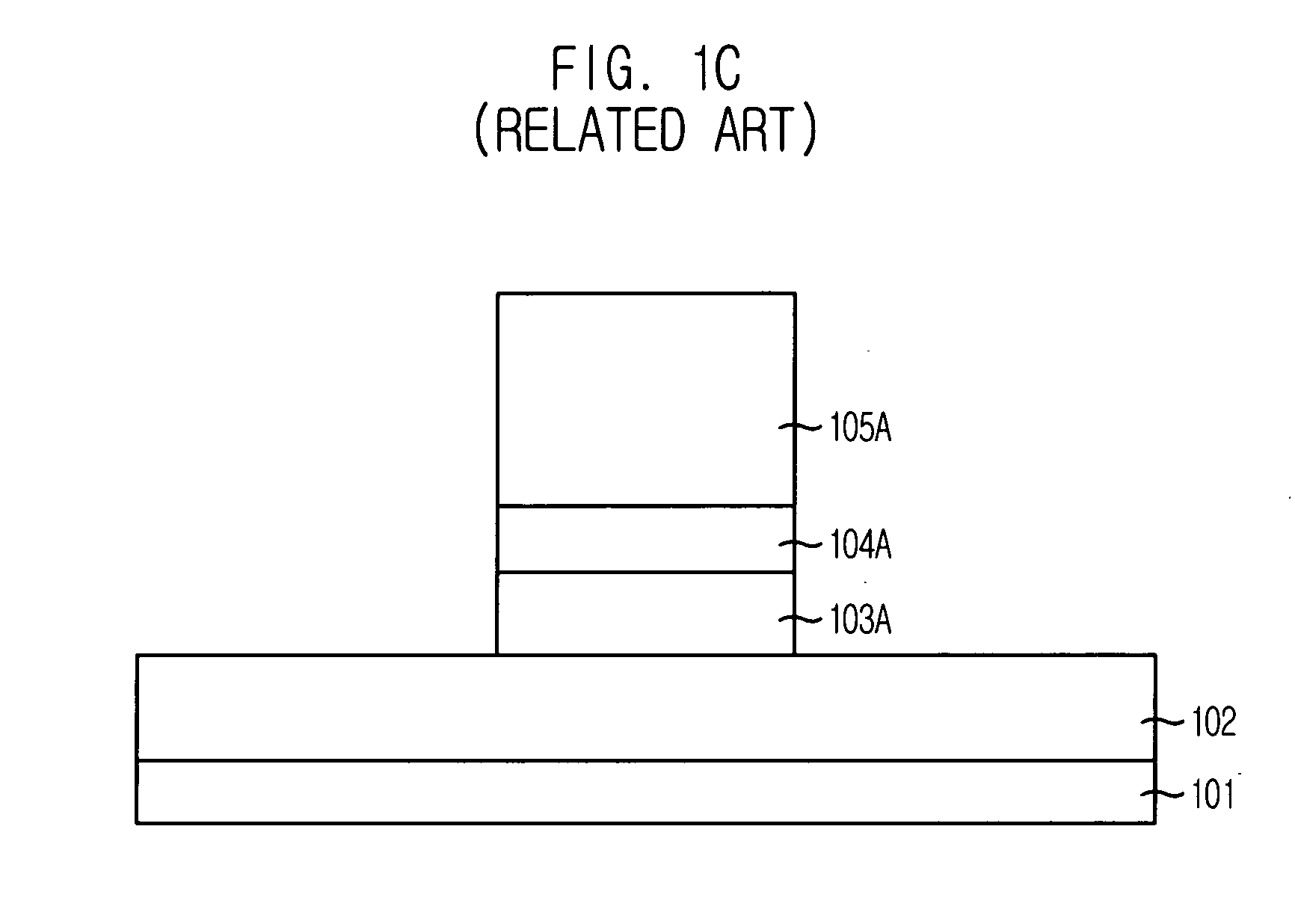

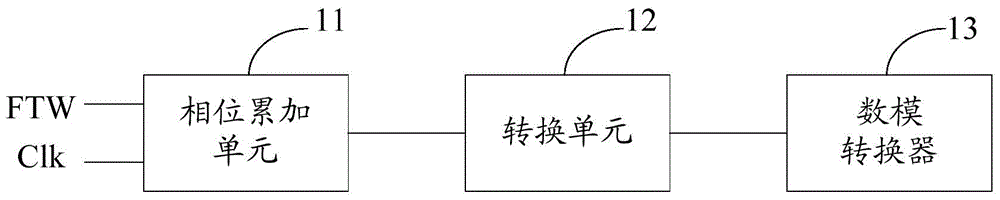

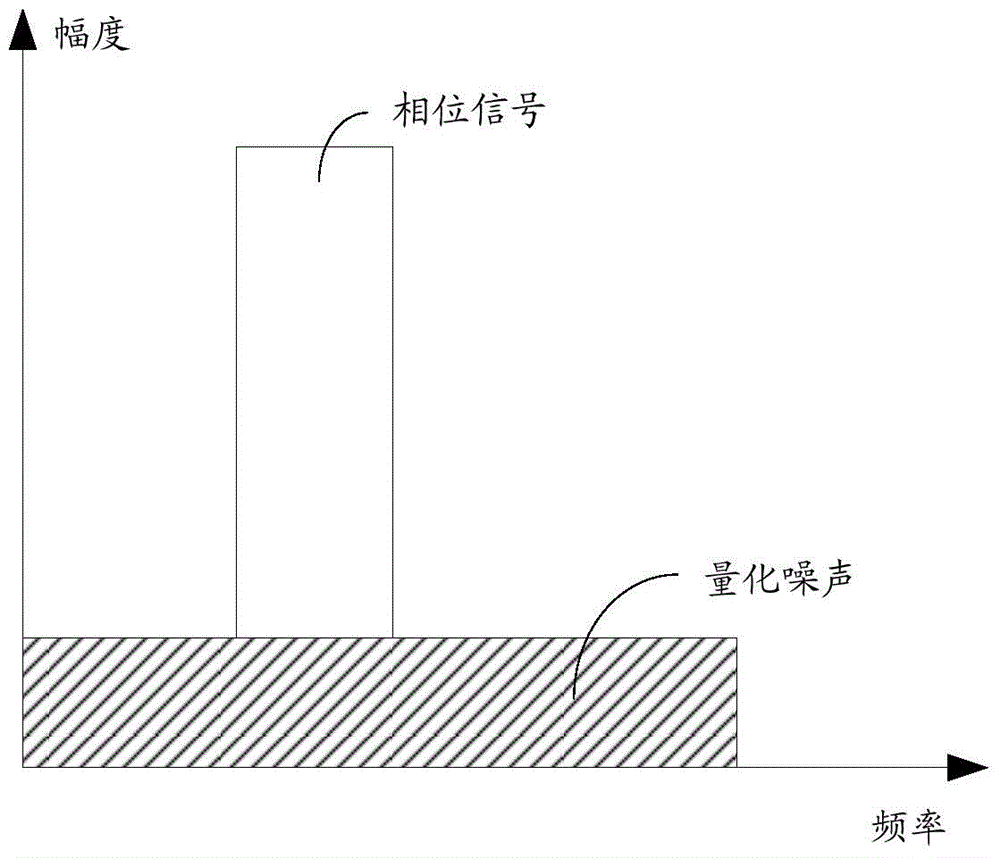

Digital control oscillator and magnetic resonance imaging system

ActiveCN104639160AImprove signal-to-noise ratioQuantization noise energy reductionPulse automatic controlDiagnostic recording/measuringUltrasound attenuationSignal-to-noise ratio (imaging)

Disclosed are a digital control oscillator and a magnetic resonance imaging system. The digital control oscillator comprises a phase accumulation unit, a quantitative shaping unit and a conversion unit. The phase accumulation unit is used for accumulating frequency control words to generate first phase signals; the quantitative shaping unit is used for quantizing the first phase signals to generate second phase signals, performing low-frequency attenuation and high-frequency amplification on quantizing noises generated from quantization and performing low-pass filtering on the quantizing noises subjected to low-frequency attenuation and high-frequency amplification; the conversion unit is used for outputting waveform data corresponding to the second phase signals. Since the quantizing noises are shaped by the digital control oscillator, the signal to noise ratio and the stray-free dynamic range of outputted periodic signals are increased.

Owner:SHANGHAI UNITED IMAGING HEALTHCARE

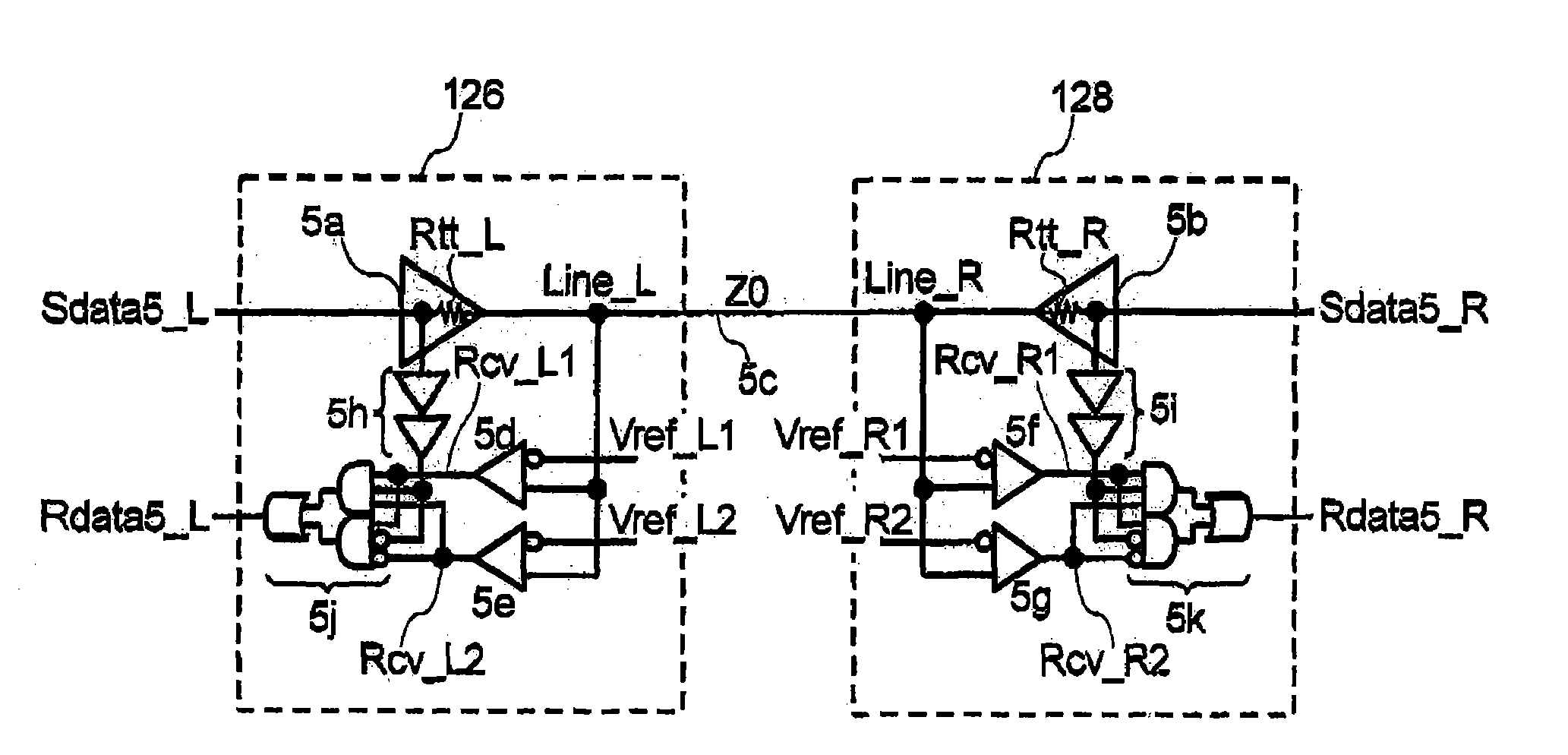

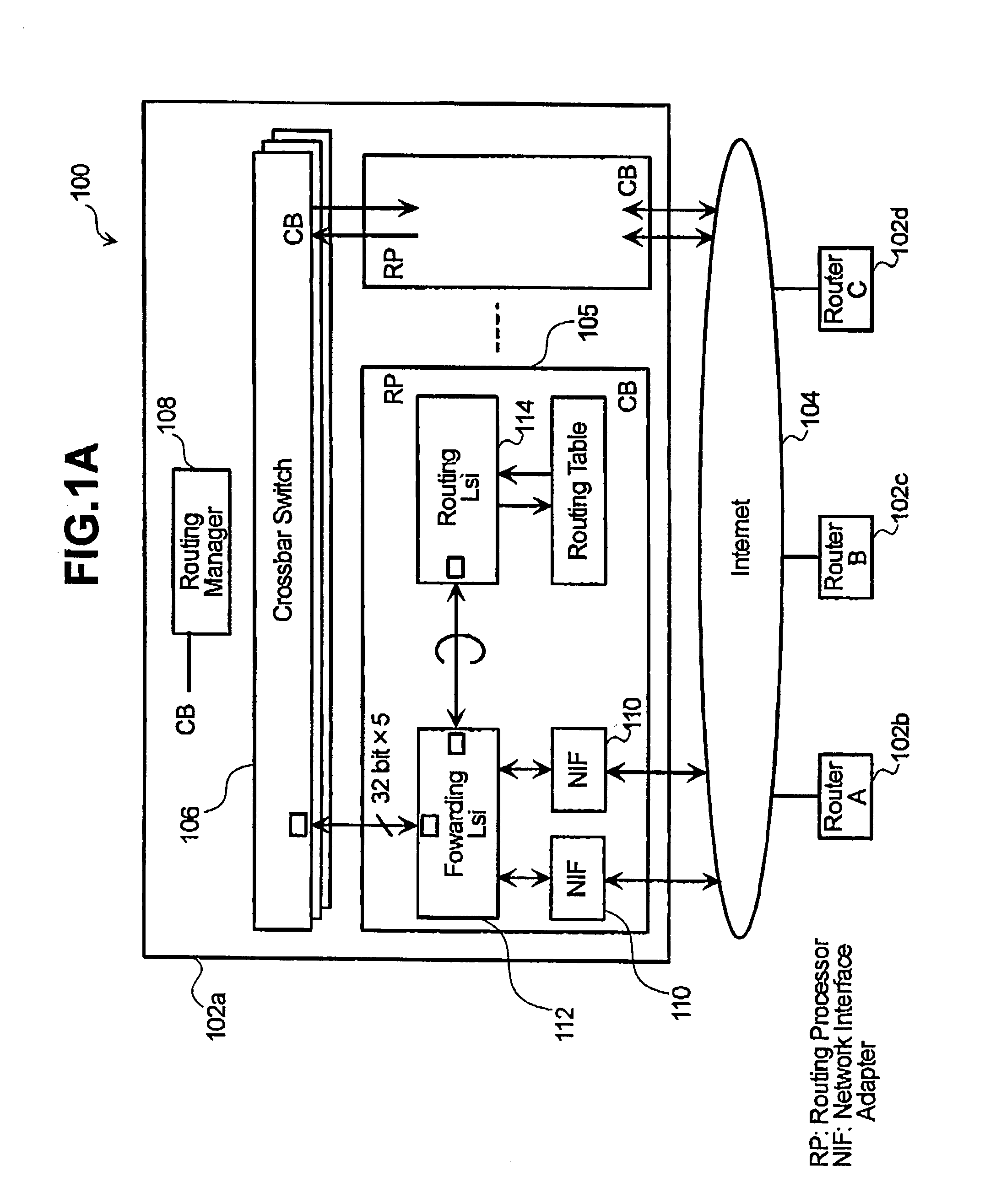

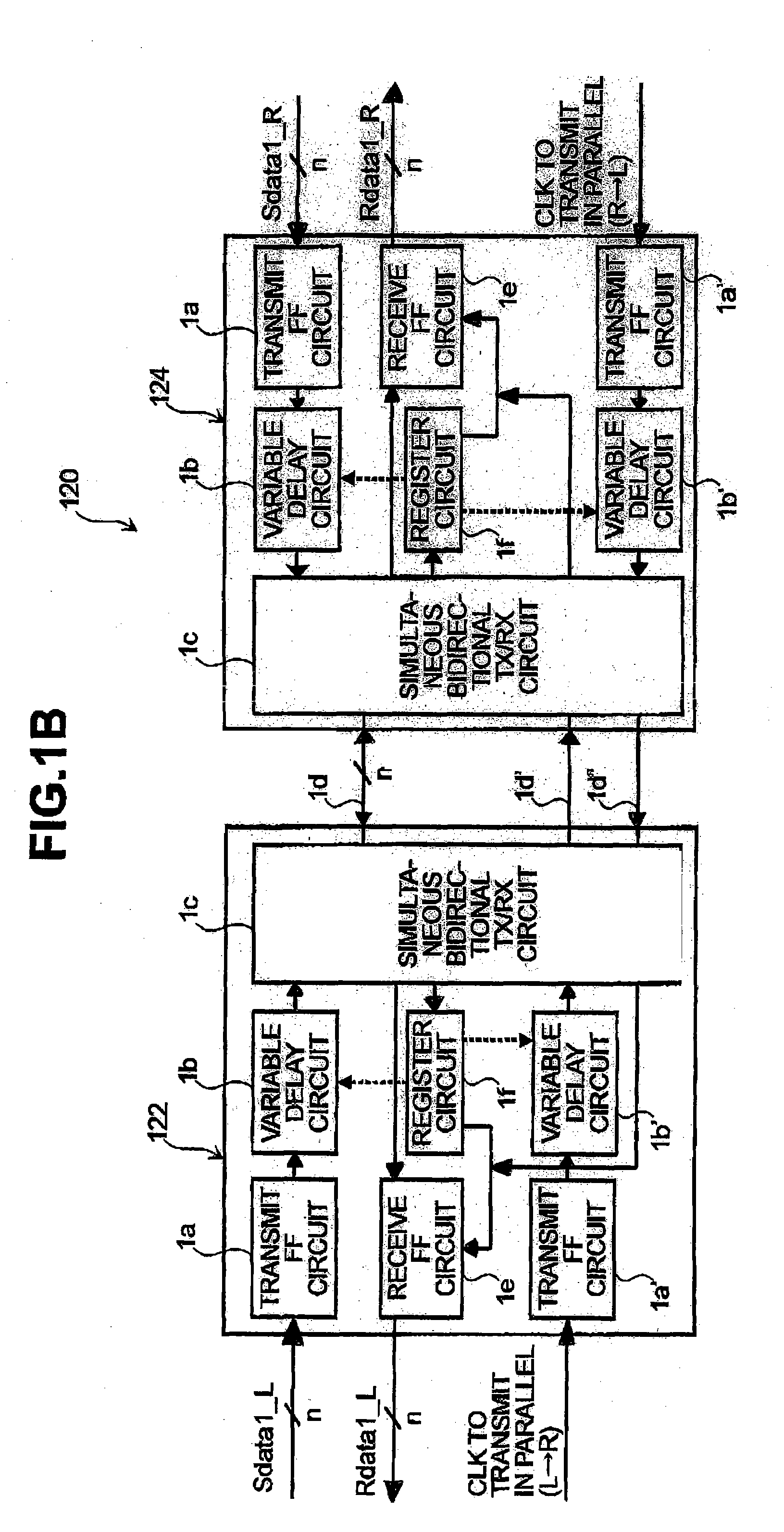

Method and system of bidirectional data transmission and reception

InactiveUS7440494B2Guaranteed high speed operationHigh popularityData switching by path configurationSynchronisation signal speed/phase controlEngineeringData transmission

A simultaneous bi-directional data transferring method includes obtaining a combined signal from a portion of a data line proximate a host device. The combined signal is a signal that combines input and output signals that are being transmitted over the data line. The output signal is a signal transmitted by the host device, and the input signal is a signal transmitted by a remote device. The combined signal is provided to first and second receivers of the host device. A first fixed reference voltage is inputted to the first receiver, and a second fixed reference voltage is inputted to the second receiver. The first and second fixed reference voltages are independent of values of the output signal. A first output receiver signal is outputted from the first receiver using the first fixed reference voltage and the combined signal, and a second output signal is outputted from the second receiver using the second fixed reference voltage and the combined signal. The input signal is reproduced using the first and second output receiver signals. A length of the data line is set to enable the input signal transmitted by the remote device to arrive at an input point of the host device at an integer multiple of a clock cycle.

Owner:HITACHI LTD

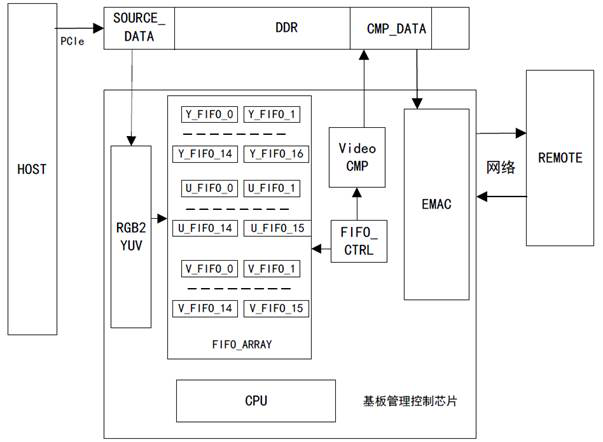

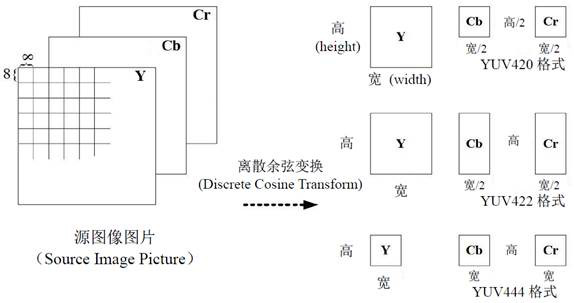

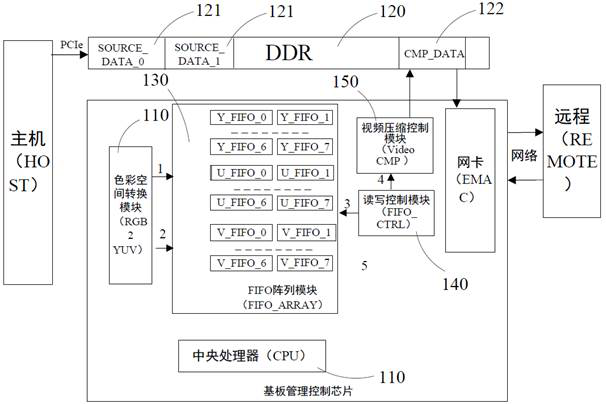

Video compression system and method, computer readable storage medium and server

ActiveCN114501024AImprove compression efficiencyIncrease bit widthDigital video signal modificationComputer hardwareEmbedded system

The invention discloses a video compression system and method, a computer readable storage medium and a server, the video compression system comprises a color space conversion module, a memory, an FIFO array module, a read-write control module and a video compression control module, the memory comprises a cache space and a compressed data storage space, the FIFO array module comprises a plurality of FIFOs, and the read-write control module comprises a read-write control module and a video compression control module. The FIFO is used for storing data of a Y component or a V component or a U component, and the FIFO array module is configured to correspondingly set the bit width of the FIFO based on the number of the FIFO so as to enable the FIFO to store the data of the Y component or the U component or the V component of two adjacent rows at the same time; and the read-write control module is configured to sequentially read Y component or U component or V component data at corresponding positions of two adjacent rows from the corresponding FIFO in each clock period and send the data to the video compression control module. Through the scheme of the invention, the reading speed of the video data and the video compression speed are improved.

Owner:SUZHOU LANGCHAO INTELLIGENT TECH CO LTD

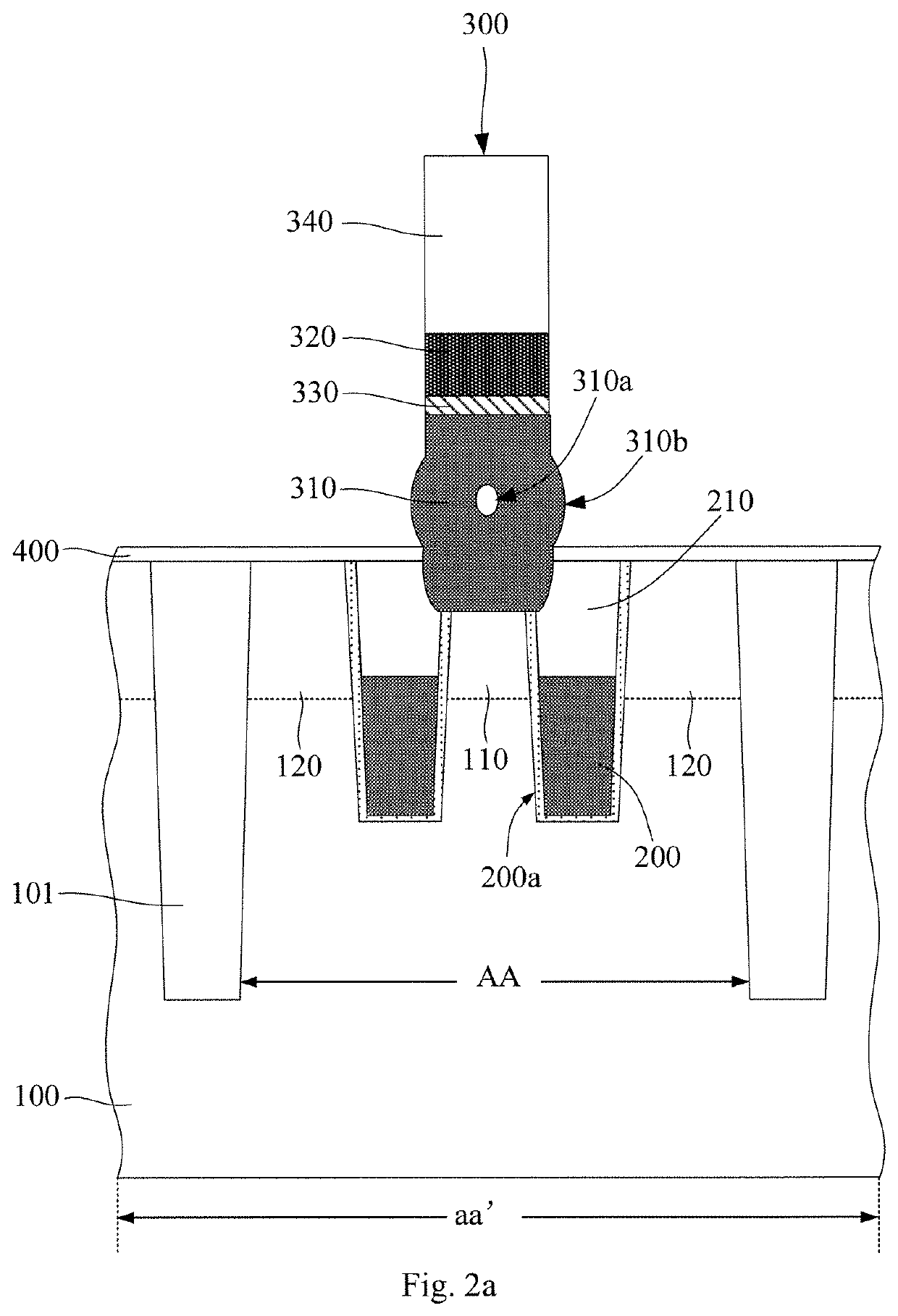

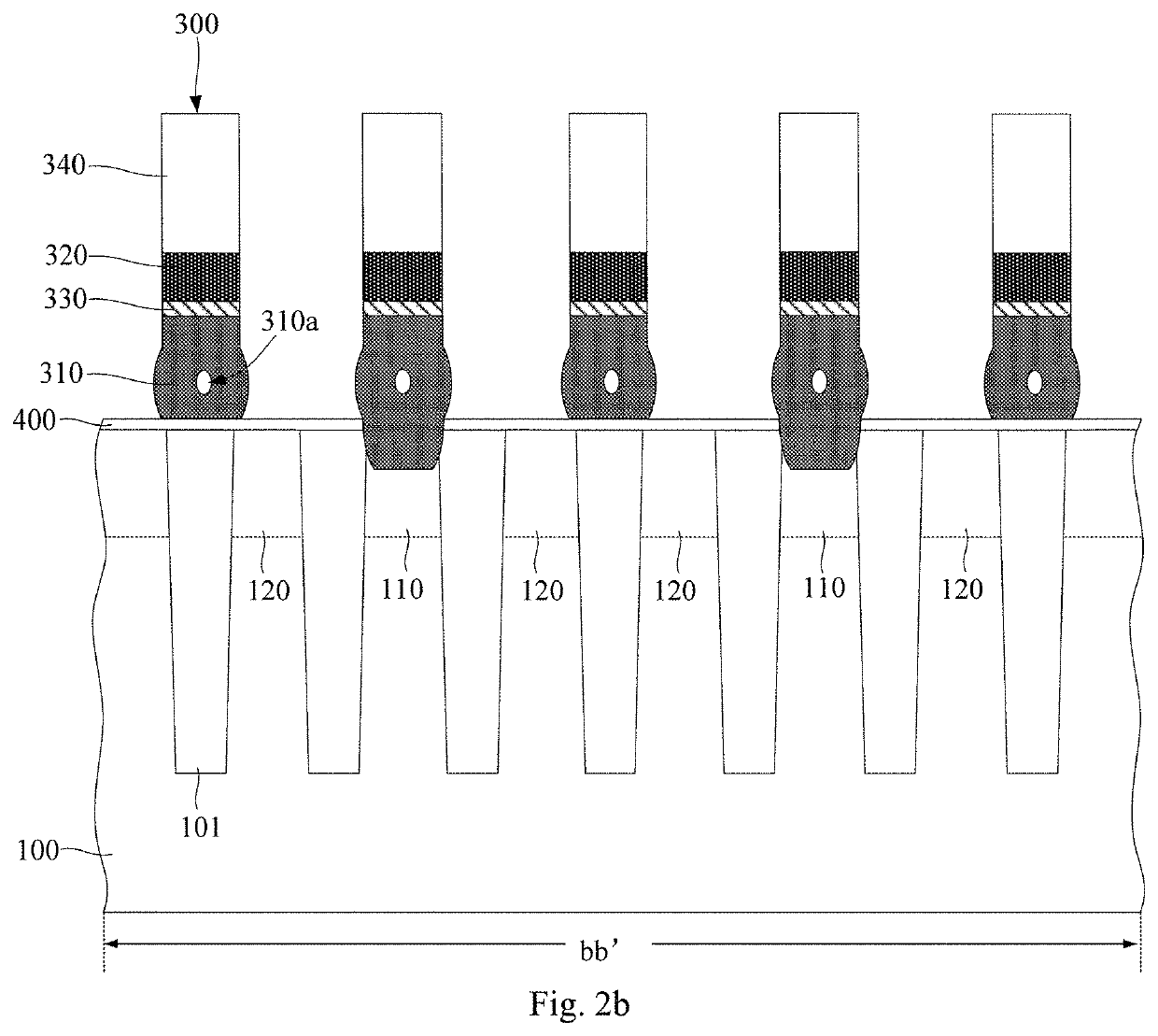

Semiconductor device, method of fabricating same and memory

ActiveUS20210082923A1Improve throughputHigh utilityTransistorSolid-state devicesBit lineDevice material

A semiconductor device, a method of fabricating the semiconductor device and a memory are disclosed. In the provided semiconductor device, bit line contact plugs partially reside on insulating material layers in gate trenches in active areas and thus can come into sufficient contact with the active areas. This ensures good electrical transmission between the bit line contact plugs and the active areas even when there are internal voids in the bit line contact plugs. Such bit line contact plugs allowed to contain internal voids can be fabricated in an easier and faster manner, thus allowing a significantly enhanced memory fabrication throughput.

Owner:FUJIAN JINHUA INTEGRATED CIRCUIT CO LTD

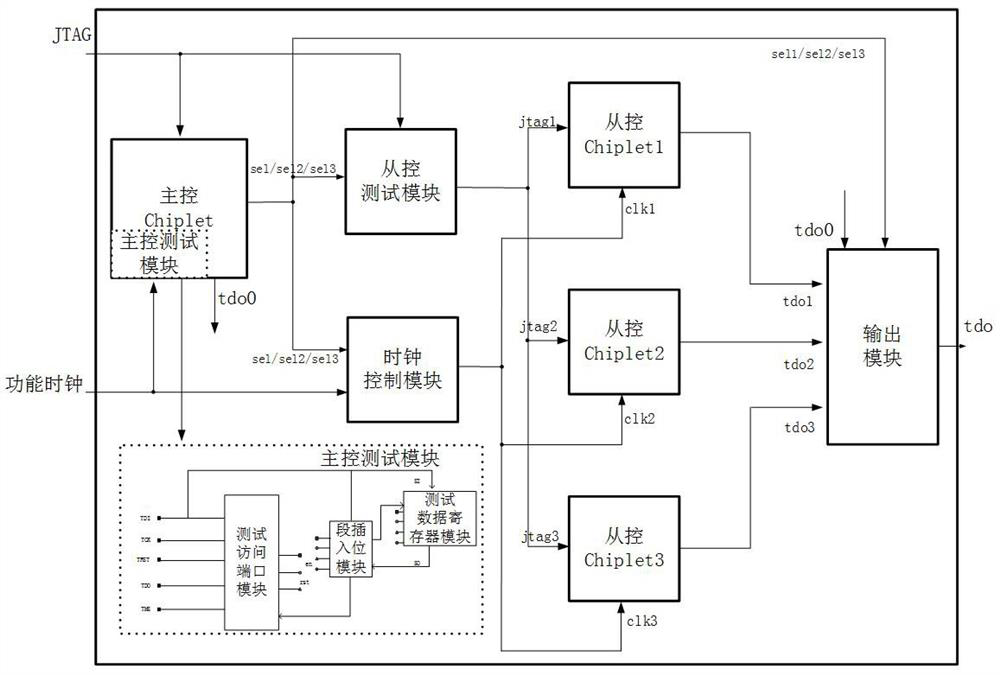

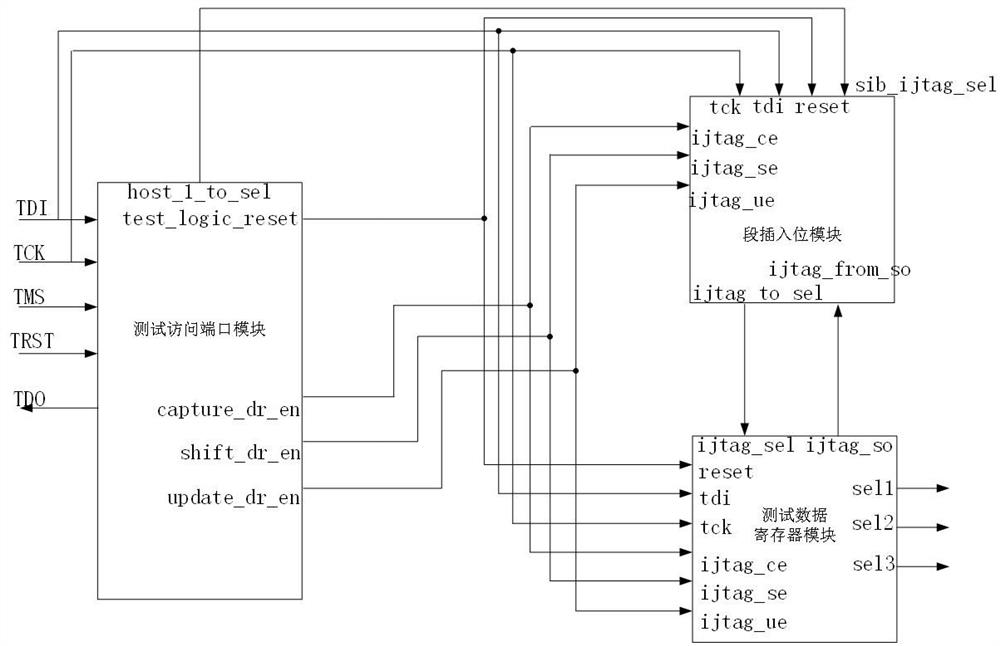

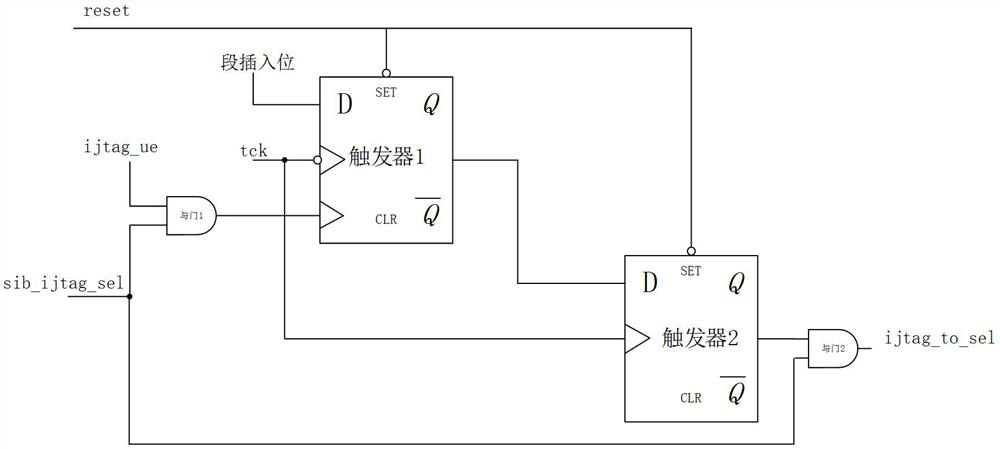

Controllable Chiplet serial test circuit

ActiveCN114578217AReduce the numberGuaranteed shift operationElectronic circuit testingTest inputControl signal

The invention discloses a controllable Chiplet serial test circuit, and belongs to the technical field of testing or measuring of semiconductor devices in the manufacturing or processing process. The test circuit comprises a master control test module, a slave control test module, a clock control module and an output module, the master control test module is composed of a test access port module, a segment insertion bit module and a test data register module, and a test control signal is generated through the master control test module; the slave control test modules respectively control test input signals of the slave control core particles after receiving the test control signals. Meanwhile, the test control signal is input to the clock control module to obtain a clock signal of the slave control core particle. The output signal of the test output module is determined by the test control signal. According to the test circuit, an external test port is used for directly controlling an internal test signal of the multi-core-particle integrated circuit, core particle test selection and final test output are realized, and effectiveness and independence of each core particle test are ensured.

Owner:NANJING UNIV OF POSTS & TELECOMM +1

ARM-based data acquisition network uploading device and method

InactiveCN105516120AIncreased data transfer rateIncrease the number of packets sentTransmissionUser Datagram ProtocolGigabit Ethernet

The invention relates to the communication technical field, in particular to an ARM-based data acquisition network uploading device with high efficiency and low cost. The device is characterized by comprising an FPGA (Field Programmable Gate Array) module used for carrying out data acquisition and processing, an ARM module used for receiving data output by the FPGA module and packaging and uploading according to a UDP (User Datagram Protocol), a PHY (Physical Layer) module used for receiving the data uploaded by the ARM module and an RJ45 interface module connected to the PHY module. The FPGA module adopts ALTERA Cyclone V series, the ARM module adopts ATMEL SAMA5 series, the PHY module adopts Micrel ksz9031 series, and the RJ45 interface can upload the data to an upper computer or a router. In comparison with the prior art, gigabit Ethernet is realized based on the ARM, and meanwhile, the device and the method have the advantages of low cost, safety, reliability and the like and are suitable for data acquisition and uploading application of mass data in multiple fields.

Owner:WEIHAI BEIYANG ELECTRIC GRP CO LTD BEIJING BRANCH +1

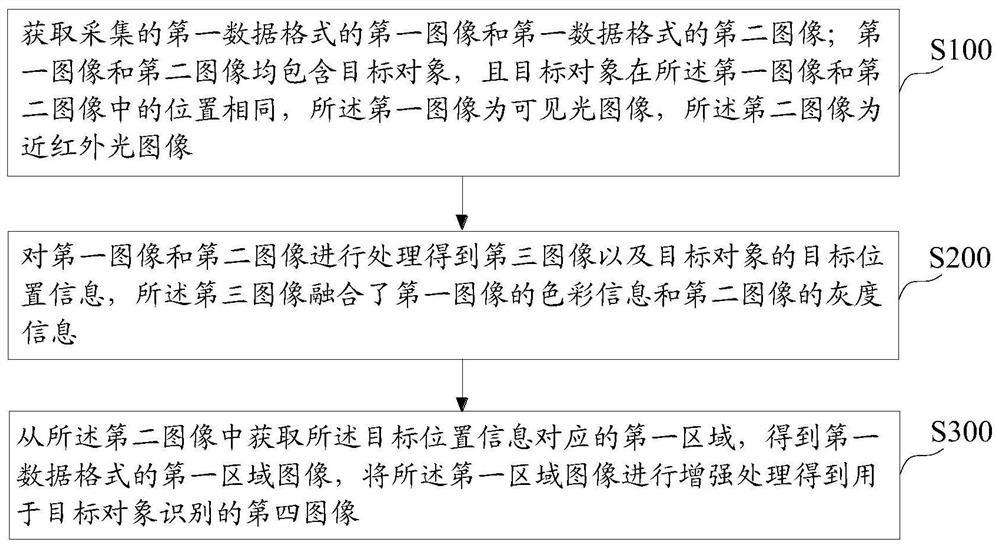

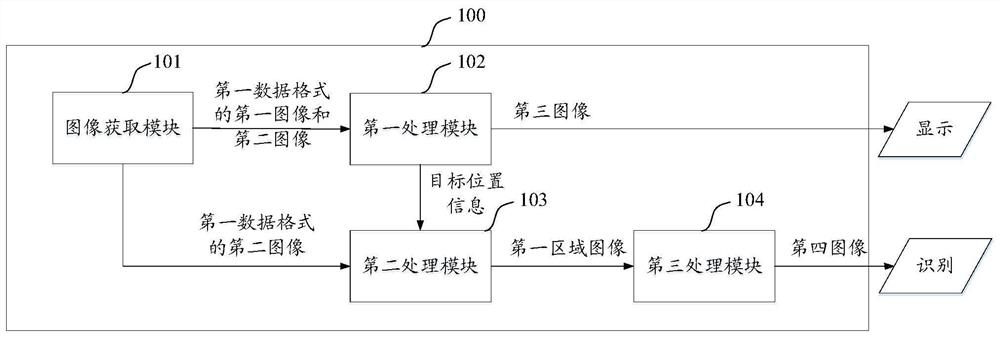

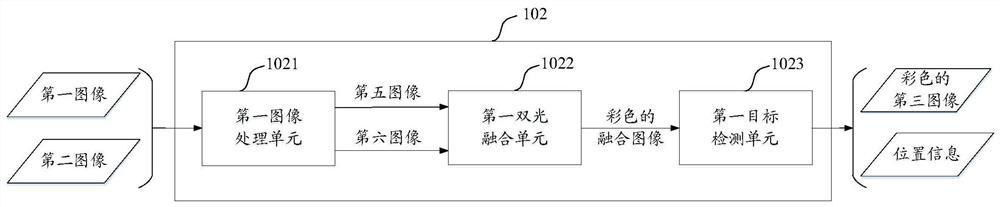

Image processing method and device, equipment and storage medium

ActiveCN112241935AQuality improvementIncrease bit widthImage enhancementImage analysisImaging processingRadiology

The invention provides an image processing method, apparatus and device, and a storage medium. The image processing method comprises the steps of obtaining an acquired first image in a first data format and an acquired second image in the first data format; wherein the first image and the second image both comprise target objects, the positions of the target objects in the first image and the second image are the same, the first image is a visible light image, and the second image is a near-infrared light image; processing the first image and the second image to obtain a third image and targetposition information of the target object, wherein the third image fuses color information of the first image and gray information of the second image; and intercepting an area corresponding to the target position information from the second image to obtain a first area image in a first data format, and performing enhancement processing on the first area image to obtain a fourth image for targetobject identification. Complete monitoring information can be provided, and the accuracy of target recognition is improved.

Owner:HANGZHOU HIKVISION DIGITAL TECH

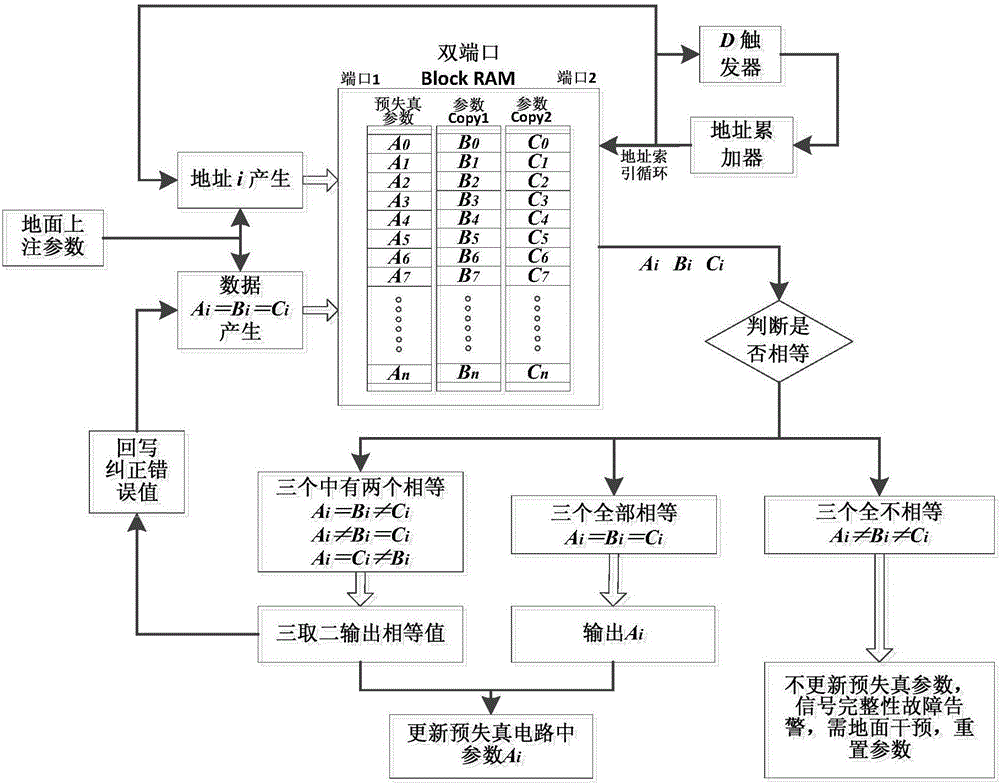

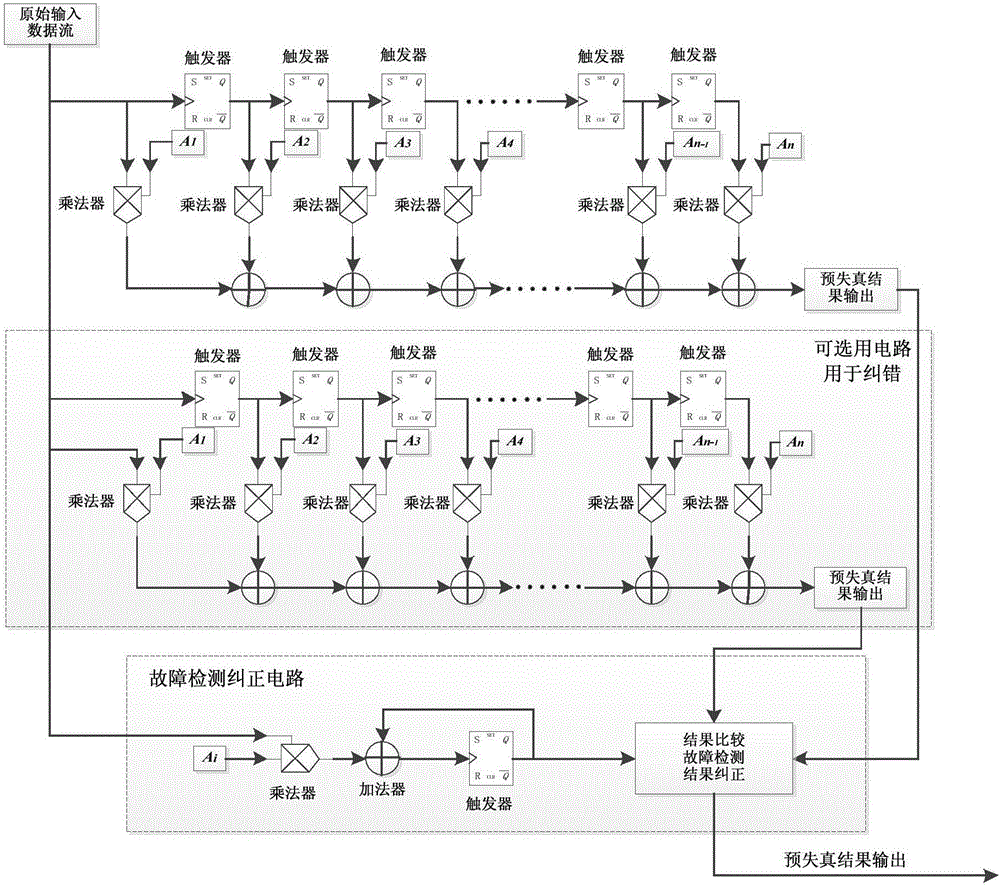

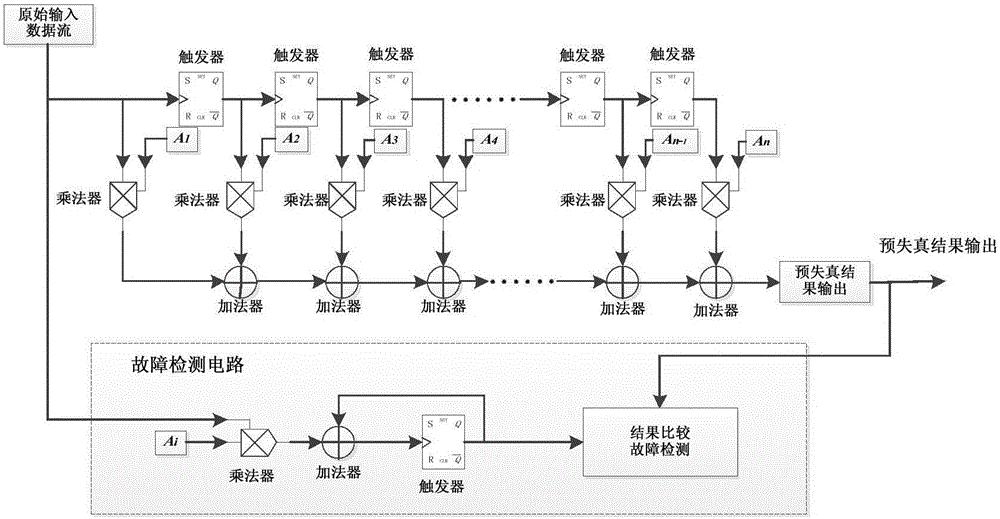

Radiation-resistant reinforcing method for on-satellite reconfigurable FIR filter

ActiveCN106849908ASolve flipIncrease bit widthTransversal filtersDigital technique networkRadiation resistantBinary multiplier

The invention discloses a radiation-resistant reinforcing method for an on-satellite reconfigurable FIR filter. The method comprises the steps of firstly acquiring the bit width of the filter, and performing reinforcement or not according to conditions, wherein when the bit width is expanded, occupied BRAM is increased and the idle BRAM cannot be provided, reinforcement is not performed, and when the bit width is expanded and the occupied BRAM is unchanged, or when the bit width is expanded and the residual idle BRAM is provided, radiation-resistant reinforcement is performed on the parameter of the reconfigurable filter on the ground; and then acquiring the number of on-satellite idle multiplying units, the number of on-satellite idle Slice resources, and the number of the multiplying units and the number of Slice resources used by the filter, if the number of the on-satellite idle multiplying units is not less than the sum of 1 and the number of the used multiplying units, and the number of the idle Slice resource is more than or equal to the product of the number of the used Slice resources and (1+1 / n), using the filter to achieve radiation-resistant fault detection and correction of a circuit, and if no idle multiplying unit is provided or the number of the idle Slice resources is less than the quotient of the number of Slice resources and n, using the filter with low resource consumption to achieve radiation-resistant fault detection of the circuit, and otherwise using the filter with the single multiplying unit to achieve radiation-resistant fault detection of the circuit.

Owner:XIAN INSTITUE OF SPACE RADIO TECH

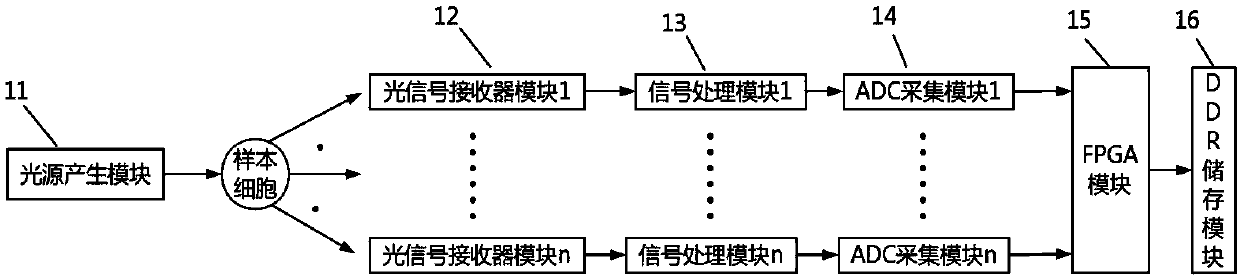

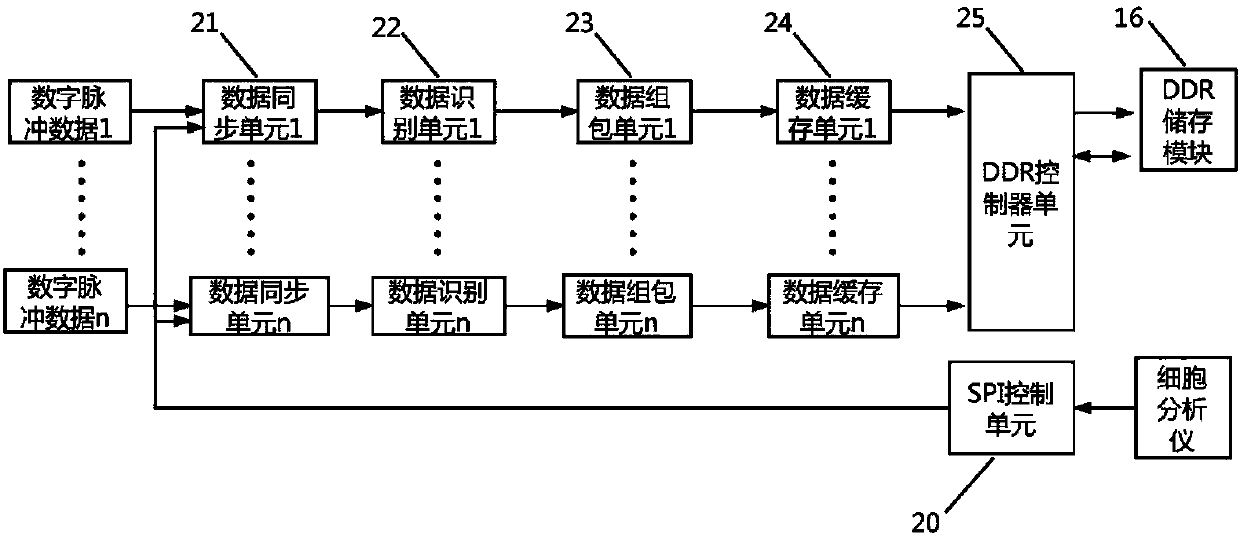

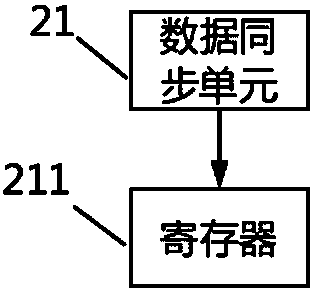

Cell analyzer capable of synchronously storing paths of pulse data and control method of cell analyzer

PendingCN109946216AImplementing Synchronous Storage RequirementsLow costIndividual particle analysisElectricityMicrocontroller

The invention relates to a cell analyzer capable of synchronously storing paths of pulse data and a control method of the cell analyzer. The cell analyzer comprises a light source generation module, light signal receiver modules, signal processing modules, ADC collection modules, an FPGA module and a DDR storage module. The number of the light signal receiver modules, the number of the signal processing modules and the number of the ADC collection modules are the same; and the light signal receiver modules, signal processing modules, ADC collection modules, FPGA module and DDR storage module are electrically connected in order. According to the provided cell analyzer, the FPGA module replaces a microcontroller, a parallel processing manner of the FPGA and abundant logic resources of the same are used, data synchronization units correspond to the paths of digital pulse data, the speed is improved by increasing the area, and thus, the paths of digital pulse data are synchronously stored.

Owner:SHENZHEN DYMIND BIOTECH

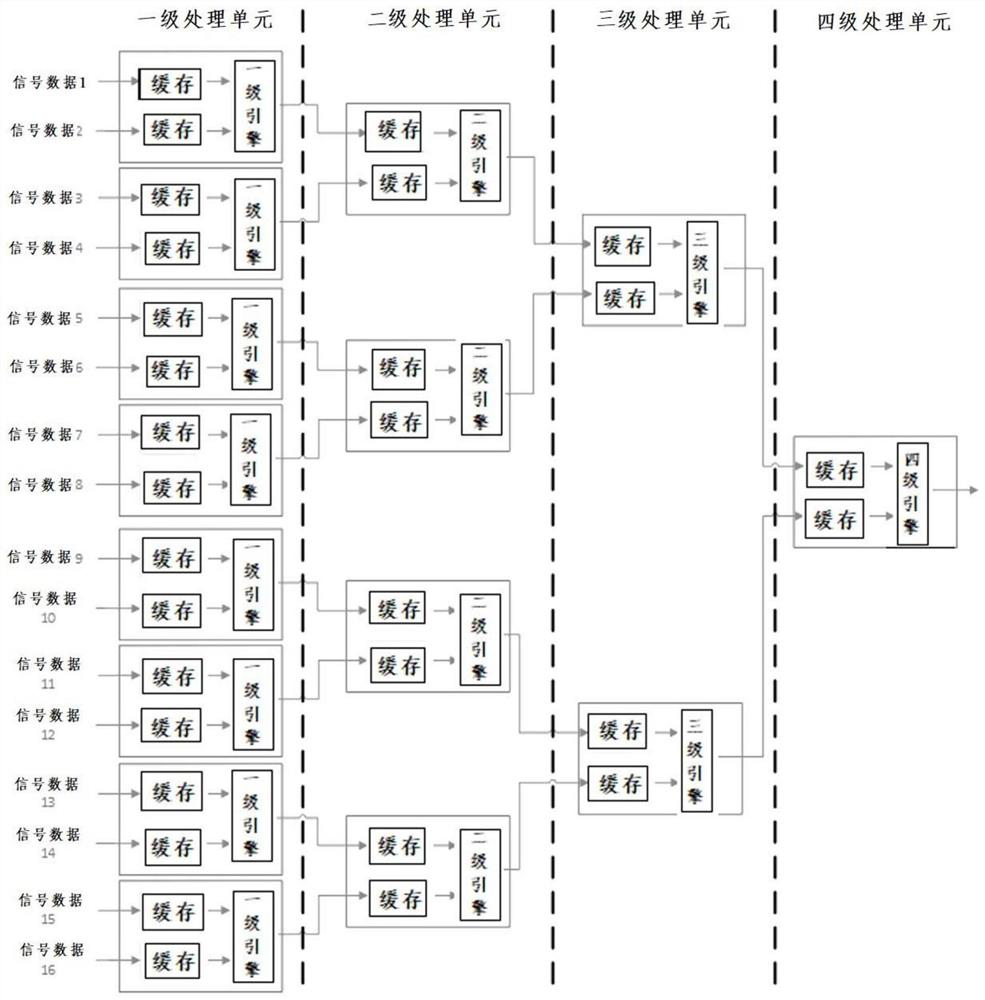

Multi-path parallel data sampling system and method

PendingCN111767687ASimple structureReduce design costComputer aided designSpecial data processing applicationsProcessing elementArbiter

The invention discloses a multi-path parallel data sampling system, which comprises a multi-path data parallel input and processing unit, the processing unit comprises a first-stage processing unit, asecond-stage processing unit,..., and a Y-stage processing unit which are cascaded, Y is greater than or equal to 2, and Y is a positive integer; each stage of processing unit comprises a unit consisting of a plurality of caches and a data engine; the data engine comprises an MUX and an arbiter, the arbiter monitors the data states of the caches, when one cache meets a data reading condition, thearbiter controls the MUX to gate the cache, read data and aggregate multiple outputs of the caches into one path of data output, and the bandwidth of the data engine is greater than or equal to the sum of the bandwidths of multiple paths of input data. The invention further discloses a multi-path parallel sampling method, the collection of multi-path data is realized on one chip, and dozens of paths or even hundreds of paths of parallel data sampling is realized. No matter in FPGA or ASIC design, a circuit structure with a good time sequence can be generated.

Owner:成都博宇利华科技有限公司

Method for fabricating semiconductor device

ActiveUS8580669B2Avoid resistanceIncrease bit widthSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceEngineering

A method for forming a semiconductor device is disclosed. A method for forming a semiconductor device includes forming a first bit line contact over a semiconductor substrate, forming a second bit line contact that is coupled to the first bit line contact and has a larger width than the first bit line contact, and forming a bit line over the second bit line contact. When using the semiconductor device having a buried gate, although the bit line is formed to have a small width and the bit line pattern is misaligned, the method prevents incorrect coupling between a bit line and a bit line contact, so that it basically deteriorates unique characteristics of the semiconductor device.

Owner:SK HYNIX INC