Patents

Literature

165 results about "Pixel shaders" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A pixel shader is a computer graphics tool that allows for the creation of image effects such as light, texture, shape and color. Pixel shaders make images more realistic by taking away the computerized look to them.

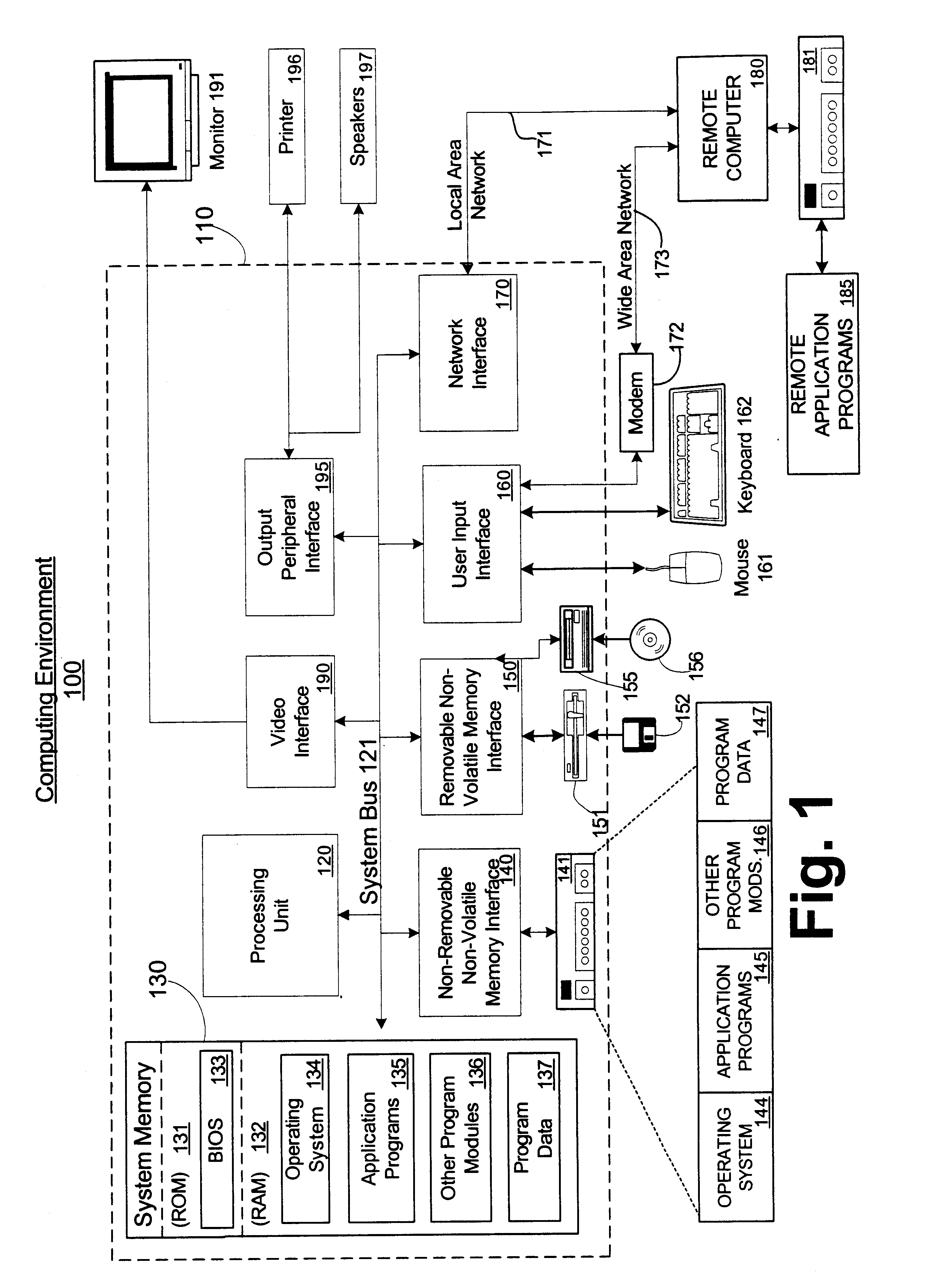

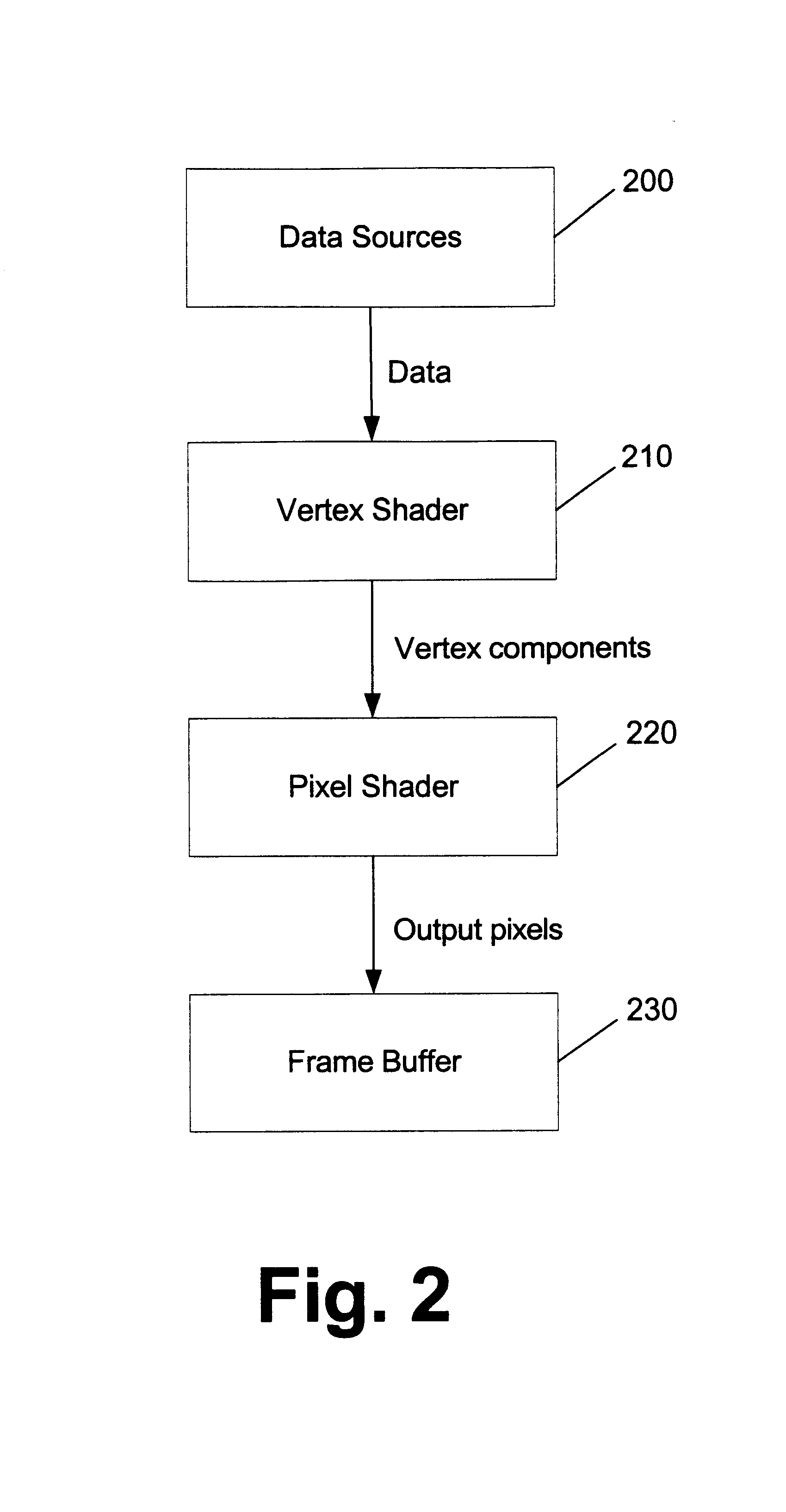

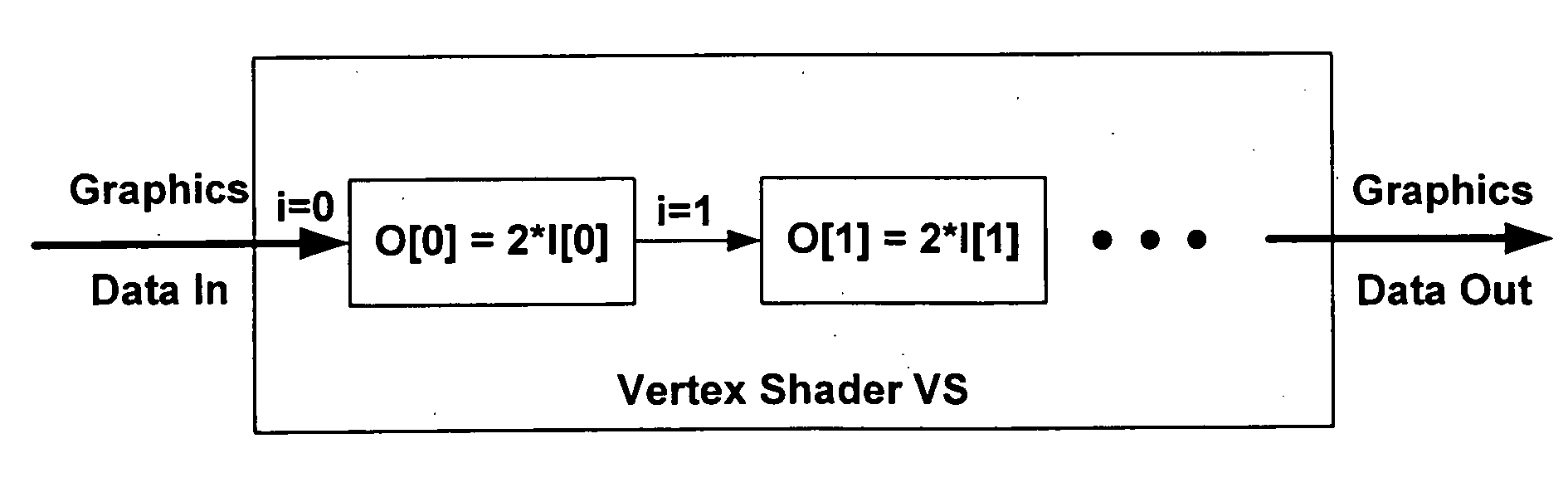

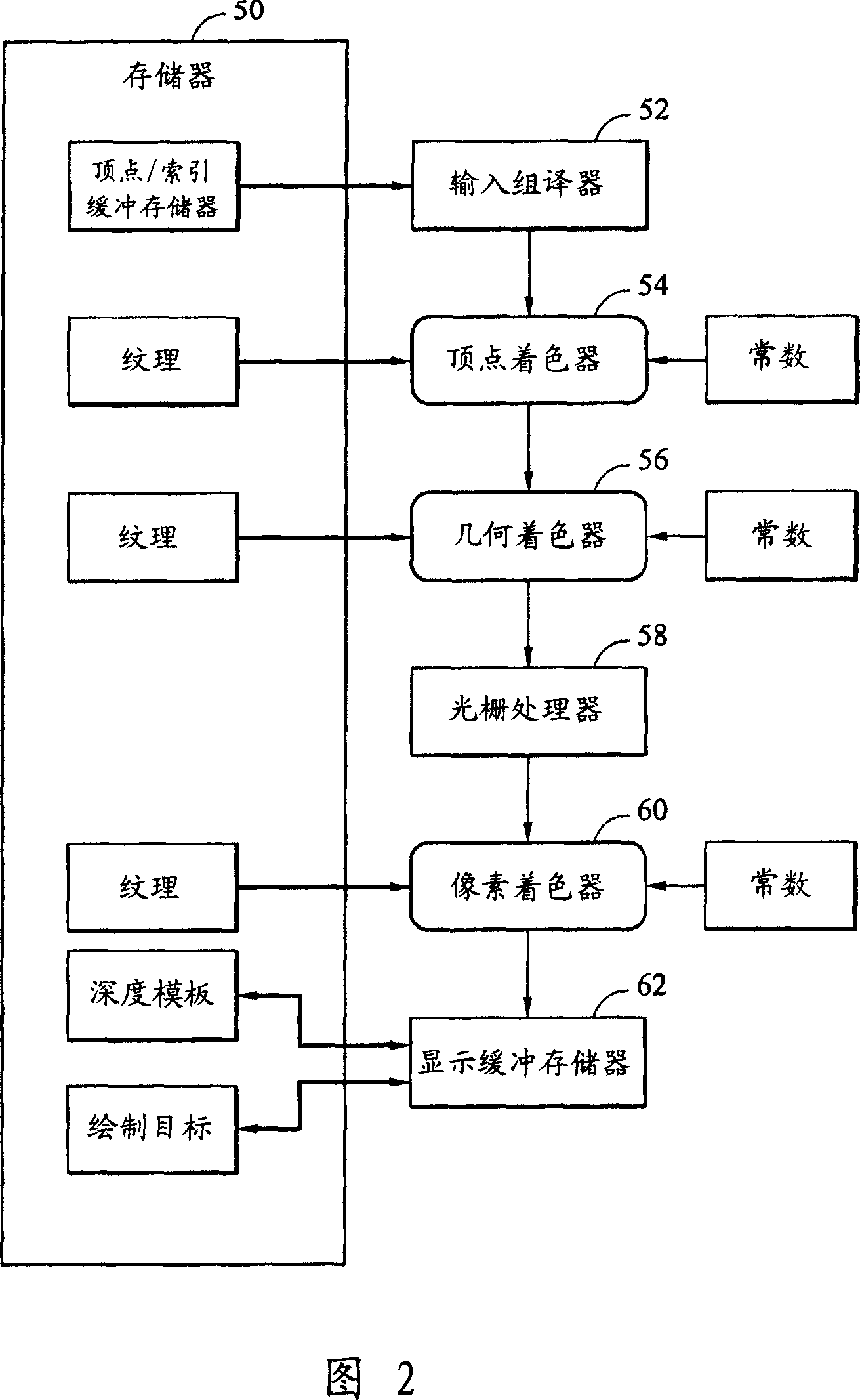

Method and system for scalable, dataflow-based, programmable processing of graphics data

ActiveUS6980209B1Improve system performanceLess system performanceCathode-ray tube indicatorsProcessor architectures/configurationArray data structureNetwork packet

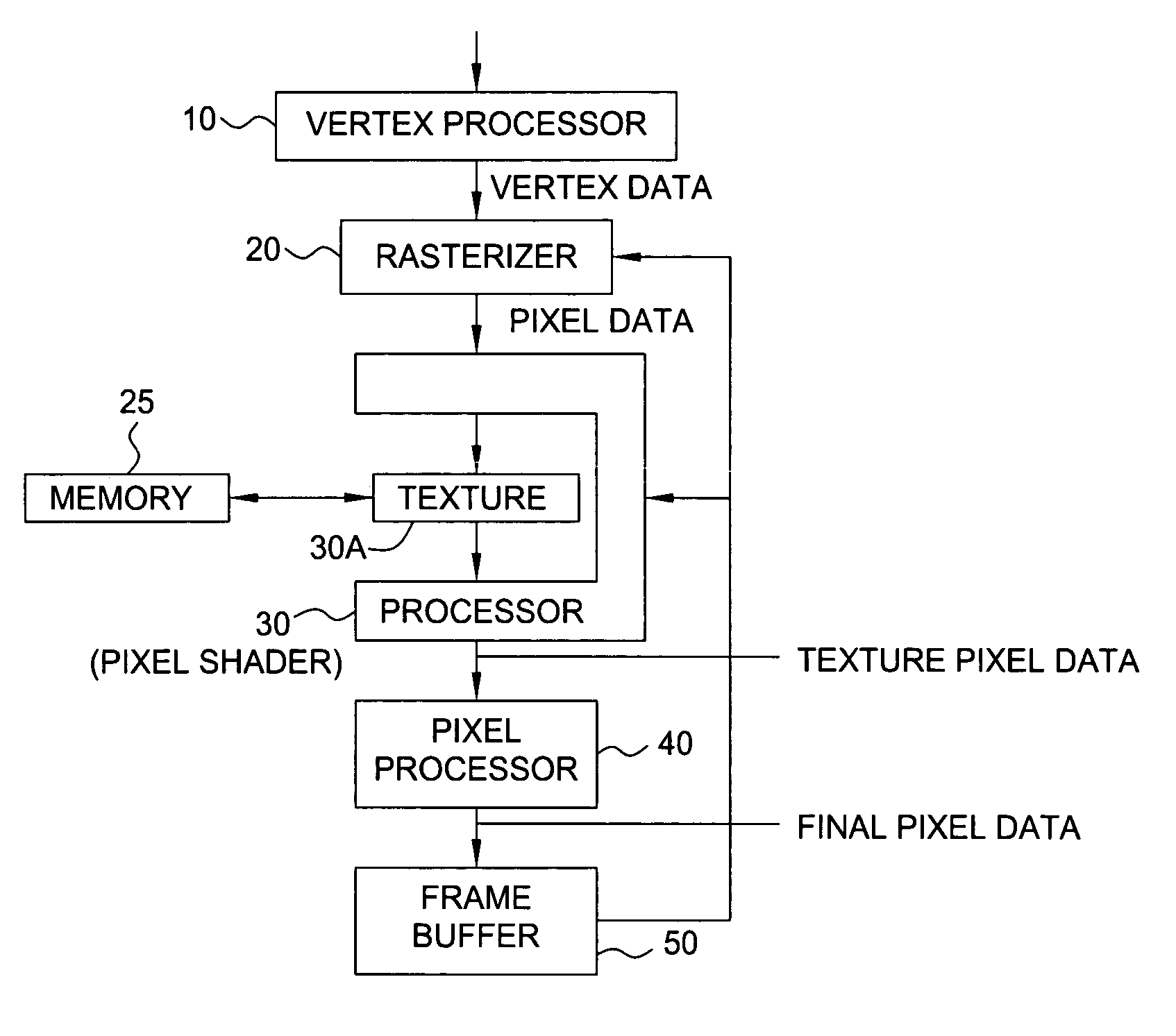

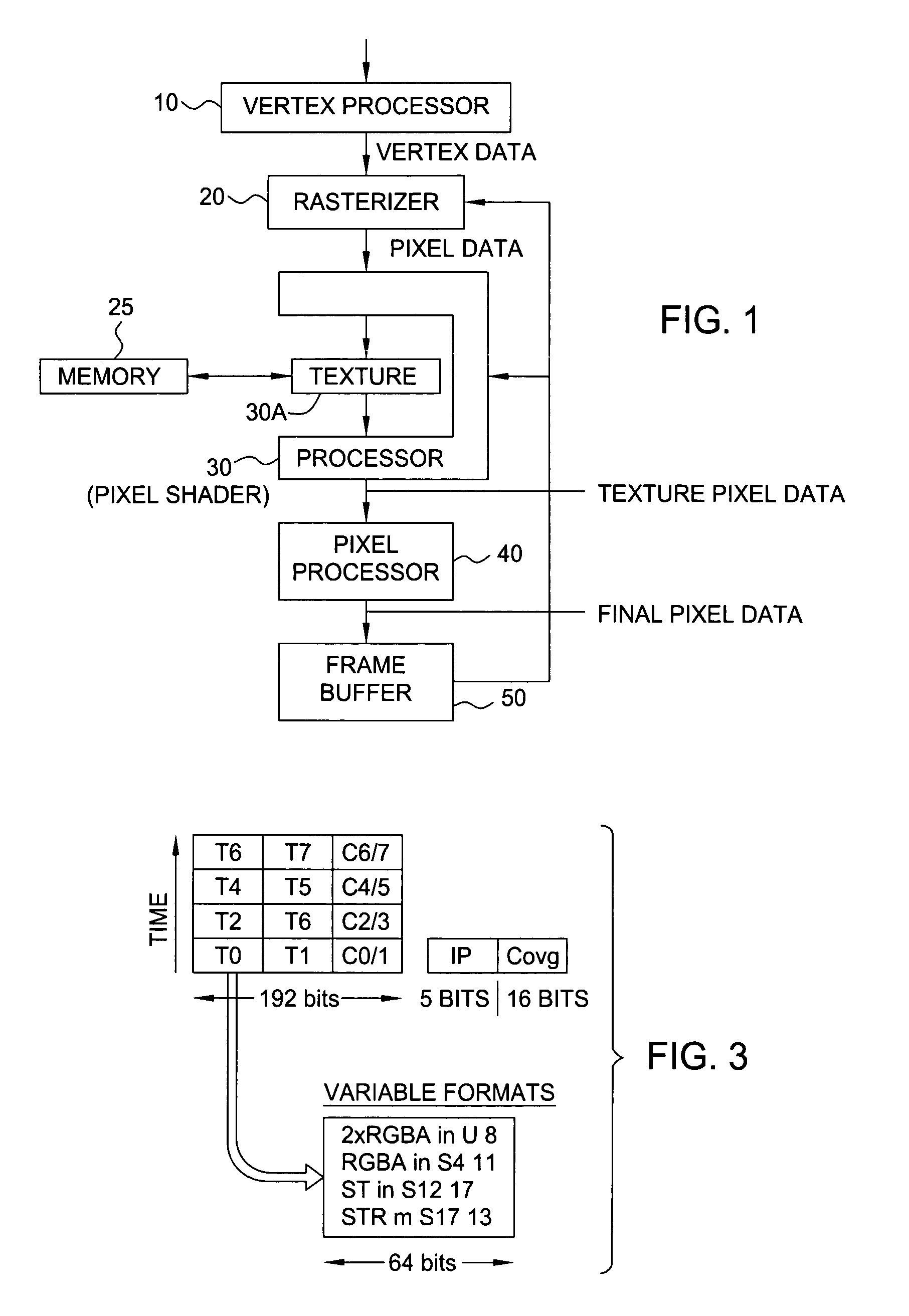

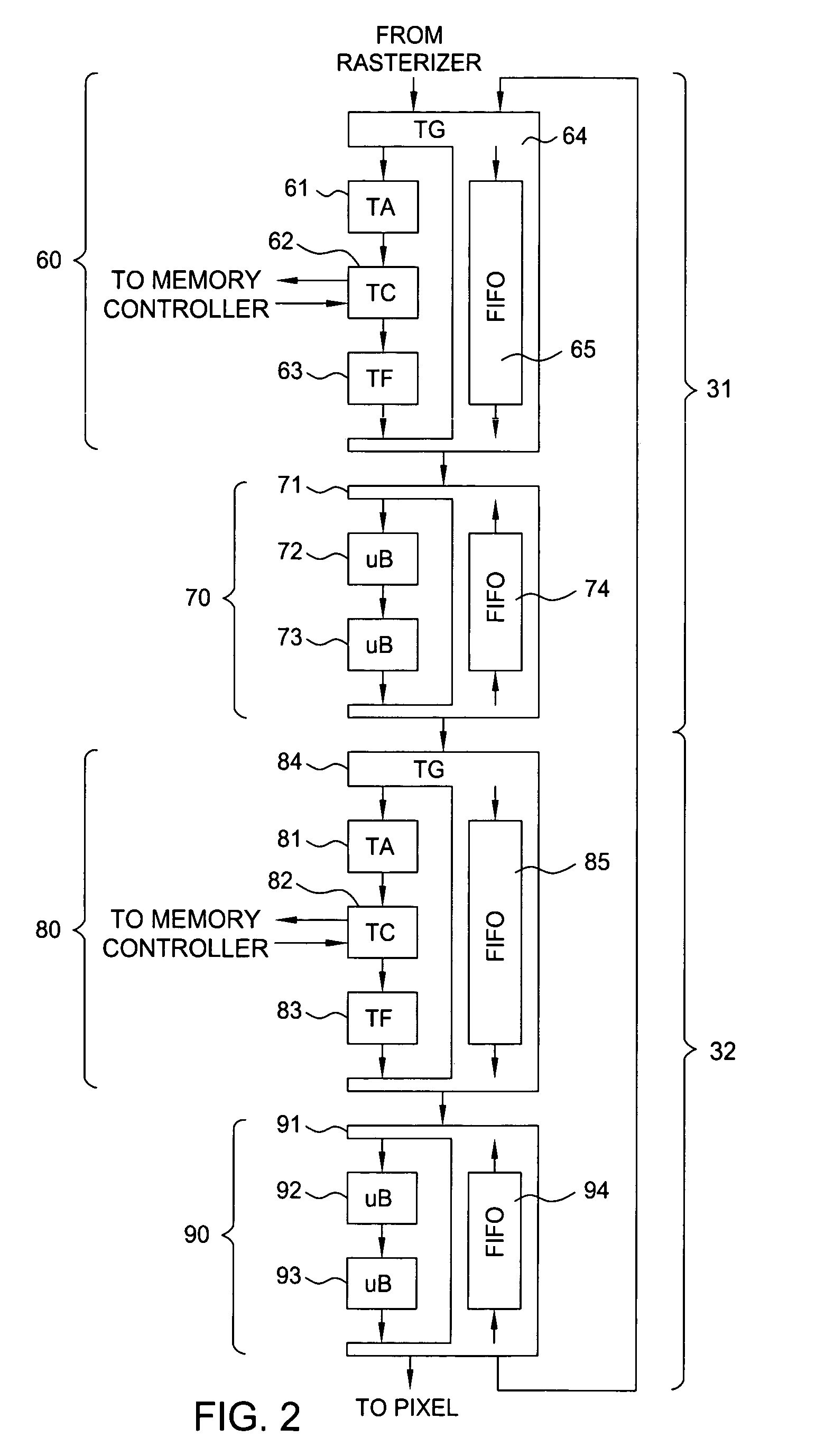

A scalable pipelined pixel shader that processes packets of data and preserves the format of each packet at each processing stage. Each packet is an ordered array of data values, at least one of which is an instruction pointer. Each member of the ordered array can be indicative of any type of data. As a packet progresses through the pixel shader during processing, each member of the ordered array can be replaced by a sequence of data values indicative of different types of data (e.g., an address of a texel, a texel, or a partially or fully processed color value). Information required for the pixel shader to process each packet is contained in the packet, and thus the pixel shader is scalable in the sense that it can be implemented in modular fashion to include any number of identical pipelined processing stages and can execute the same program regardless of the number of stages. Preferably, each processing stage is itself scalable, can be implemented to include an arbitrary number of identical pipelined instruction execution stages known as microblenders, and can execute the same program regardless of the number of microblenders. The current value of the instruction pointer (IP) in a packet determines the next instruction to be executed on the data contained in the packet. Any processing unit can change the instruction that will be executed by a subsequent processing unit by modifying the IP (and / or condition codes) of a packet that it asserts to the subsequent processing unit. Other aspects of the invention include graphics processors (each including a pixel shader configured in accordance with the invention), methods and systems for generating packets of data for processing in accordance with the invention, and methods for pipelined processing of packets of data.

Owner:PVC CONTAINER CORP +1

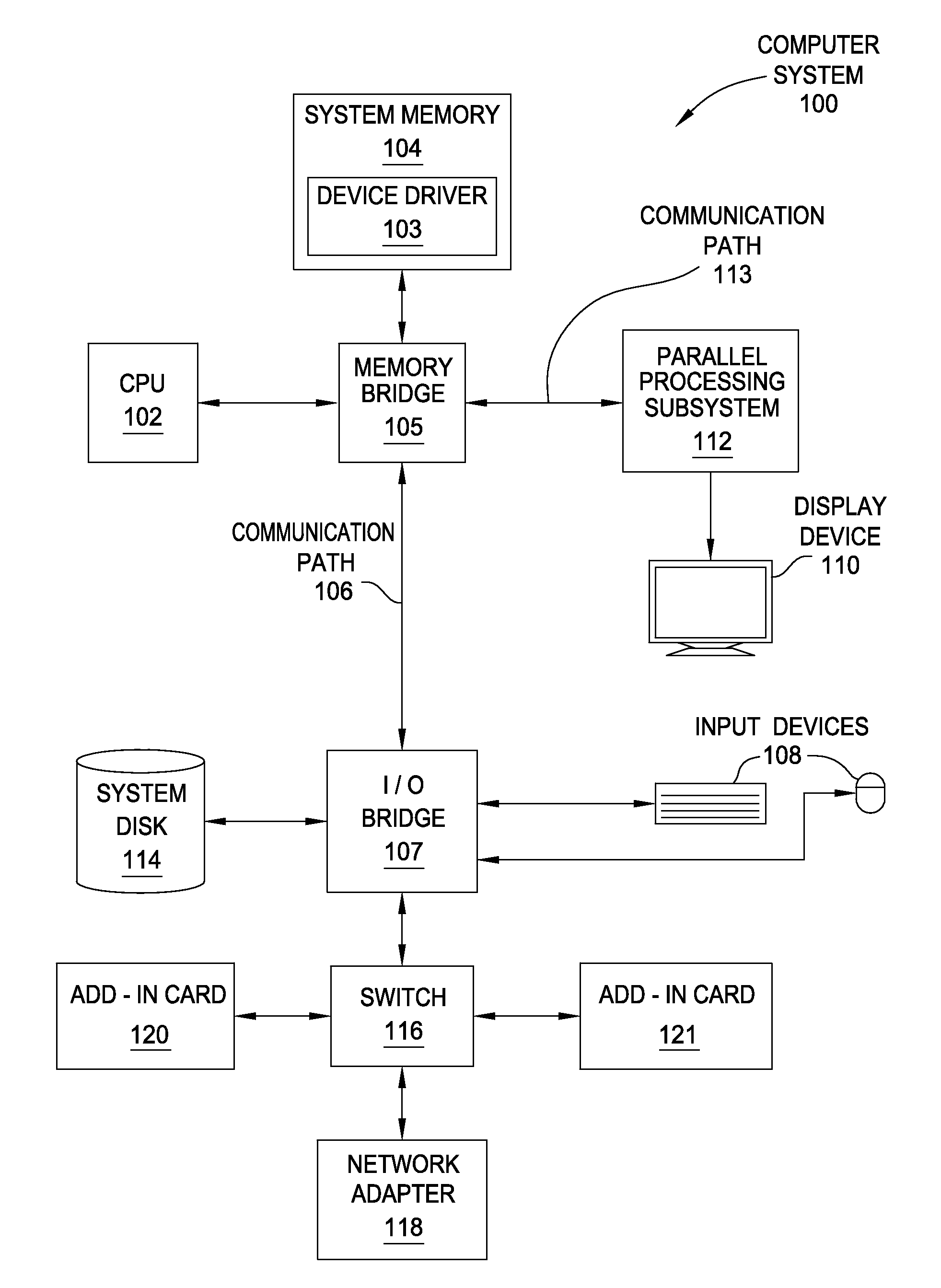

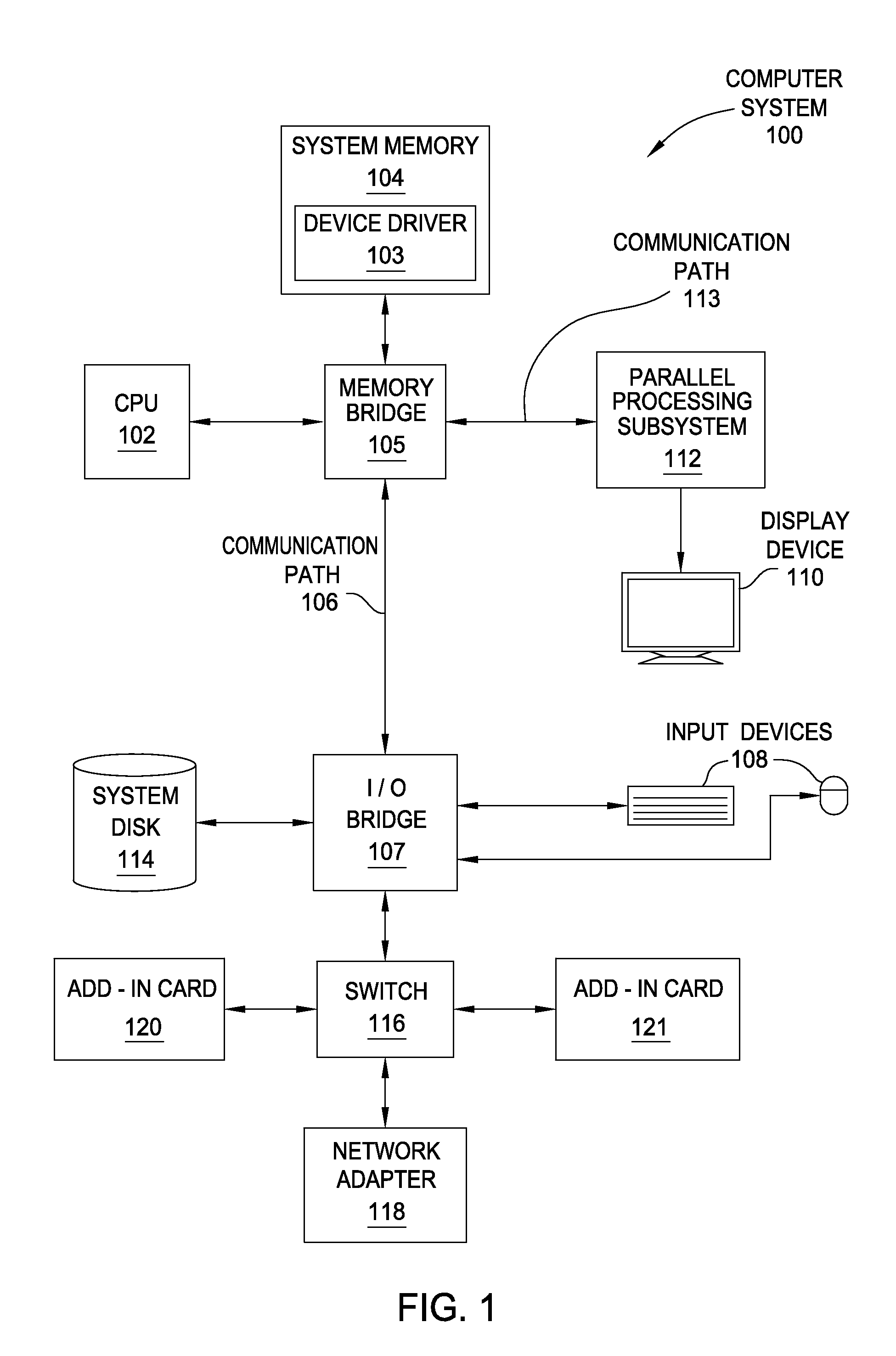

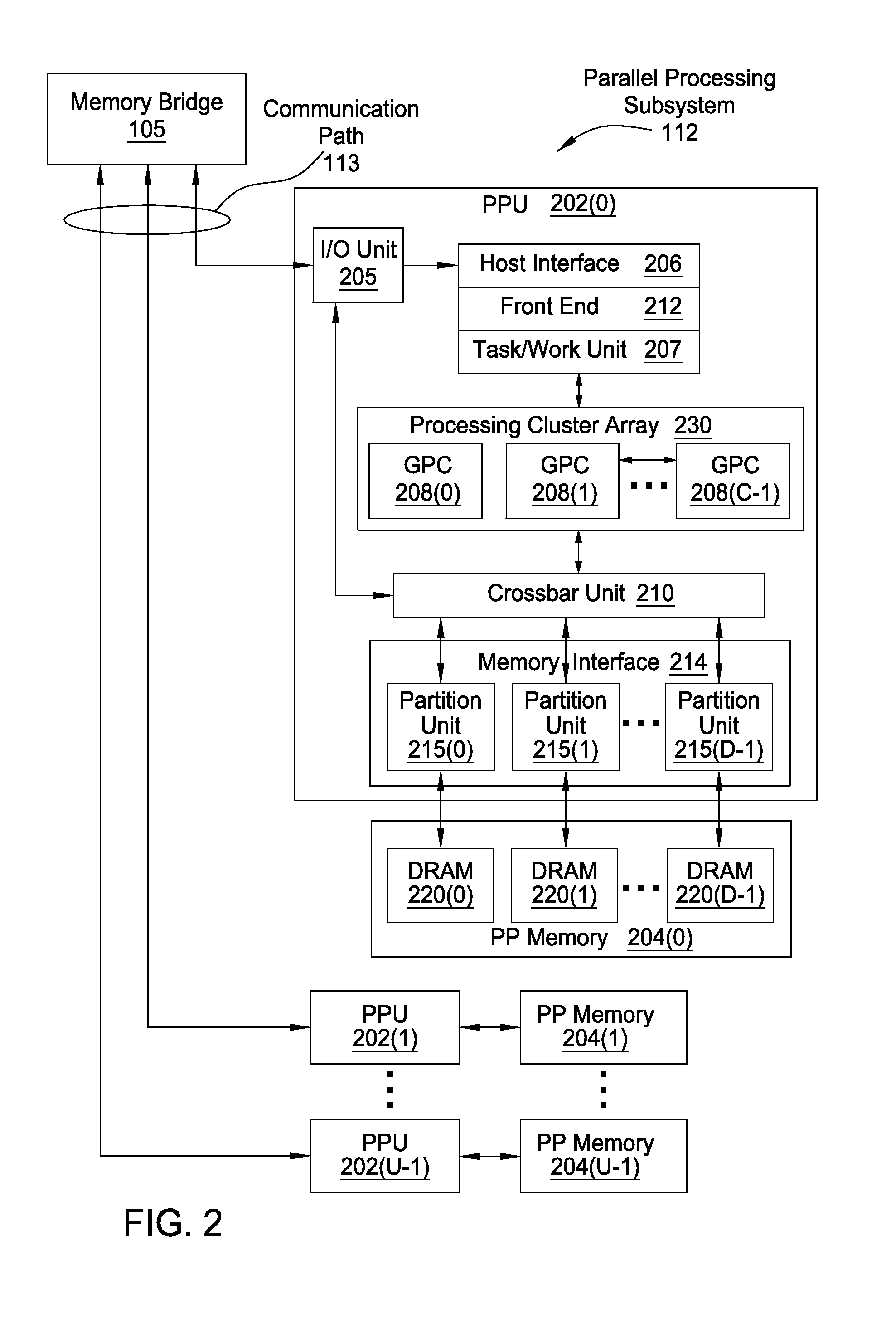

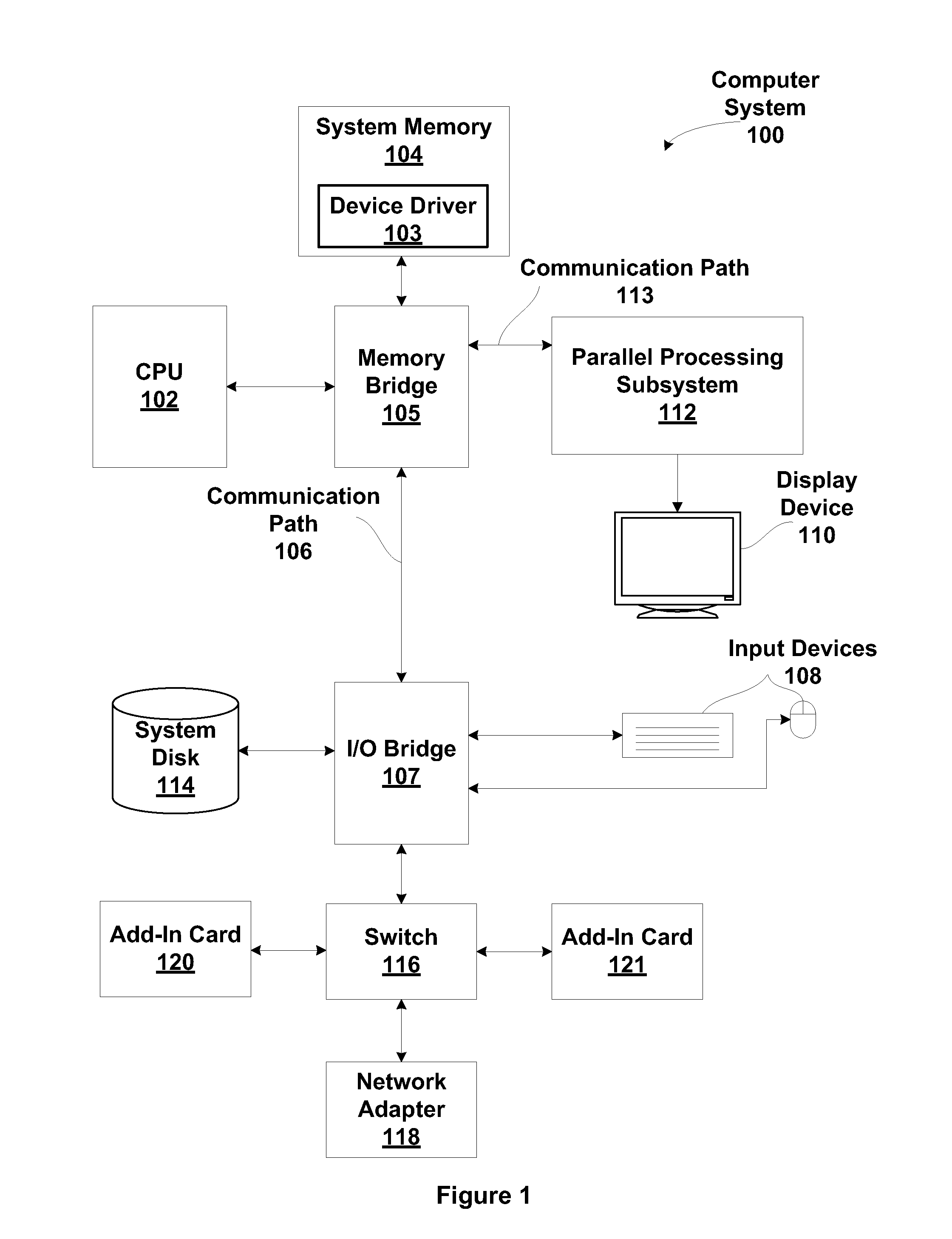

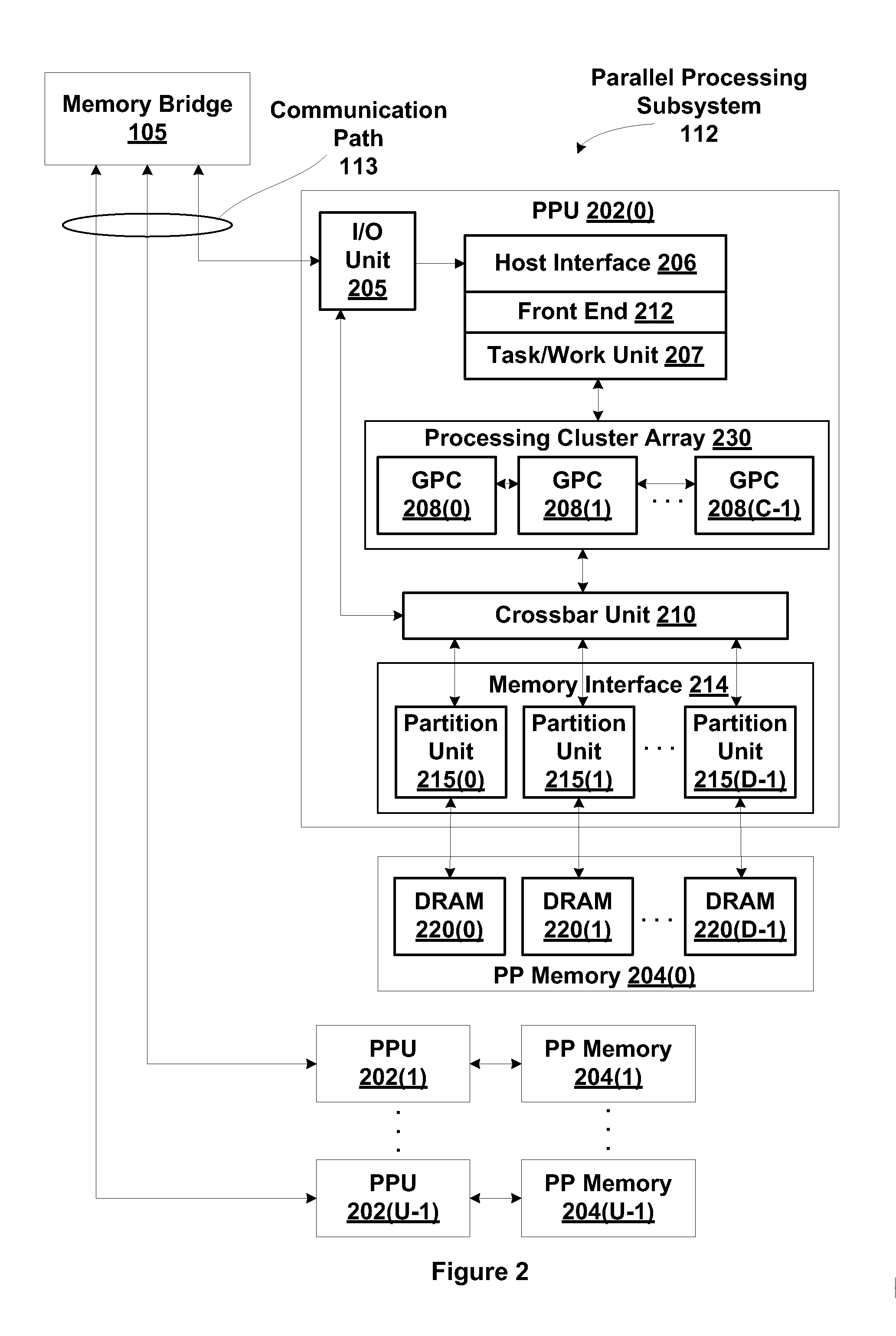

Parallel Array Architecture for a Graphics Processor

InactiveUS20070159488A1Improving memory localityImprove localitySingle instruction multiple data multiprocessorsCathode-ray tube indicatorsProcessing coreParallel computing

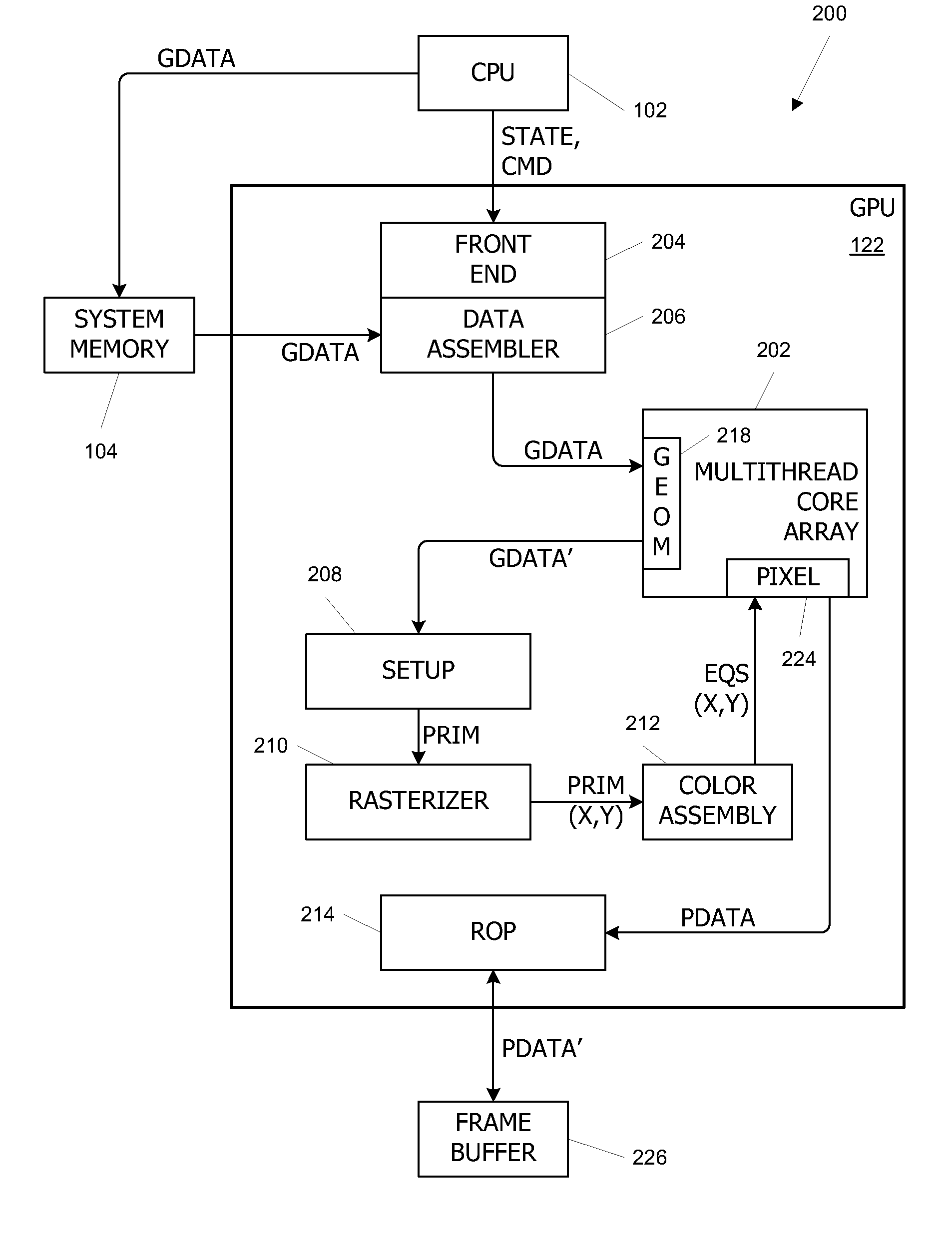

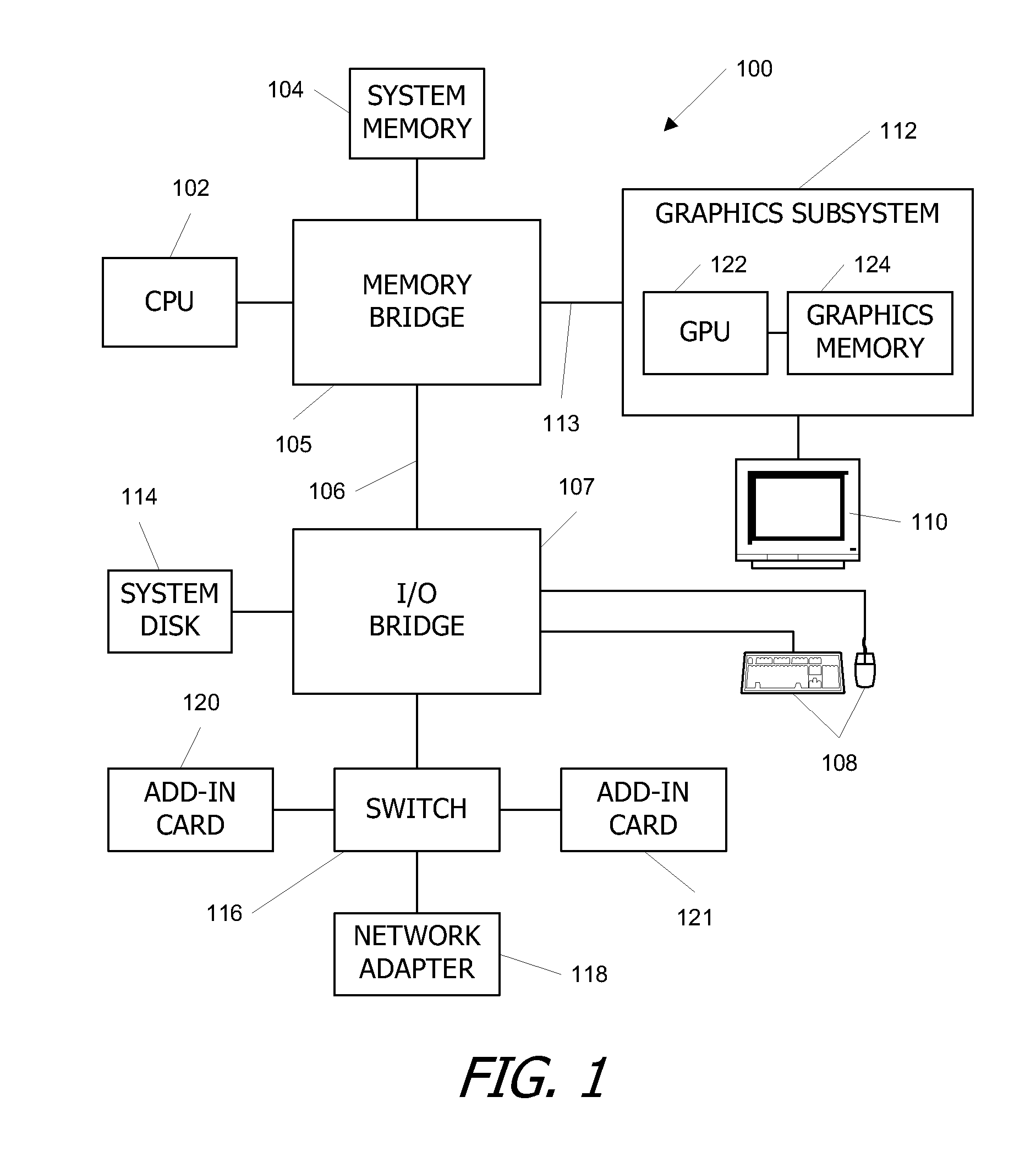

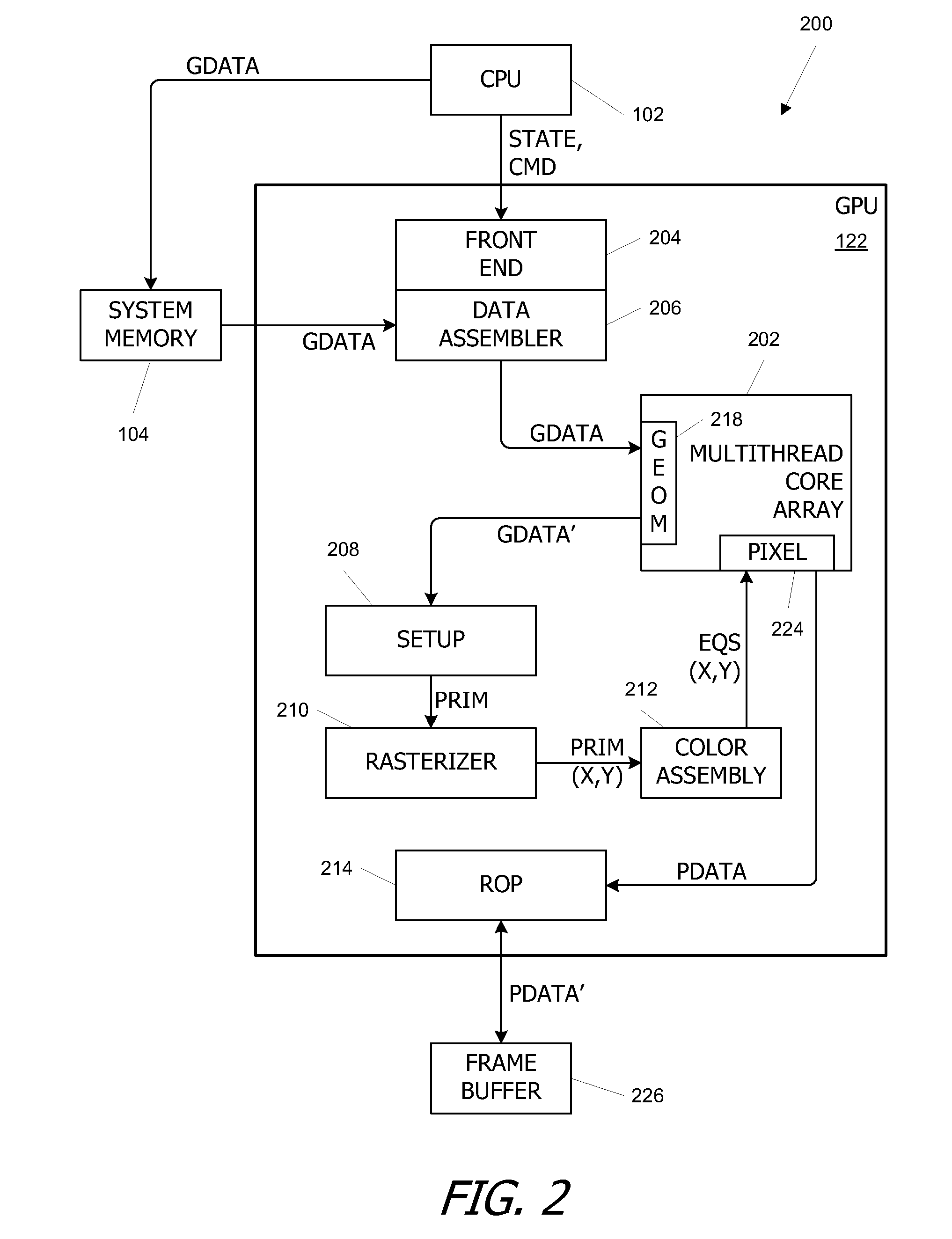

A parallel array architecture for a graphics processor includes a multithreaded core array including a plurality of processing clusters, each processing cluster including at least one processing core operable to execute a pixel shader program that generates pixel data from coverage data; a rasterizer configured to generate coverage data for each of a plurality of pixels; and pixel distribution logic configured to deliver the coverage data from the rasterizer to one of the processing clusters in the multithreaded core array. The pixel distribution logic selects one of the processing clusters to which the coverage data for a first pixel is delivered based at least in part on a location of the first pixel within an image area. The processing clusters can be mapped directly to the frame buffers partitions without a crossbar so that pixel data is delivered directly from the processing cluster to the appropriate frame buffer partitions. Alternatively, a crossbar coupled to each of the processing clusters is configured to deliver pixel data from the processing clusters to a frame buffer having a plurality of partitions. The crossbar is configured such that pixel data generated by any one of the processing clusters is deliverable to any one of the frame buffer partitions.

Owner:NVIDIA CORP

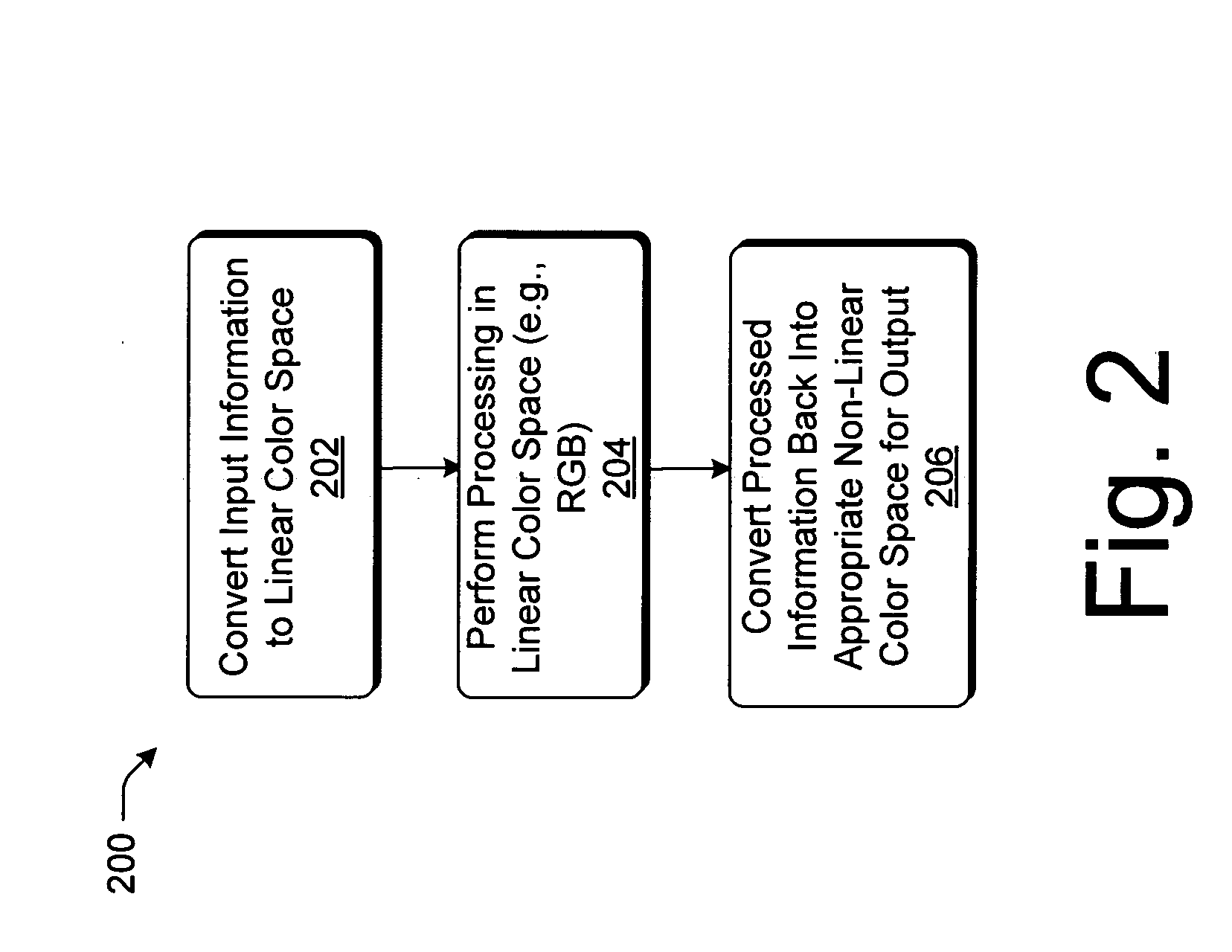

Image processing using linear light values and other image processing improvements

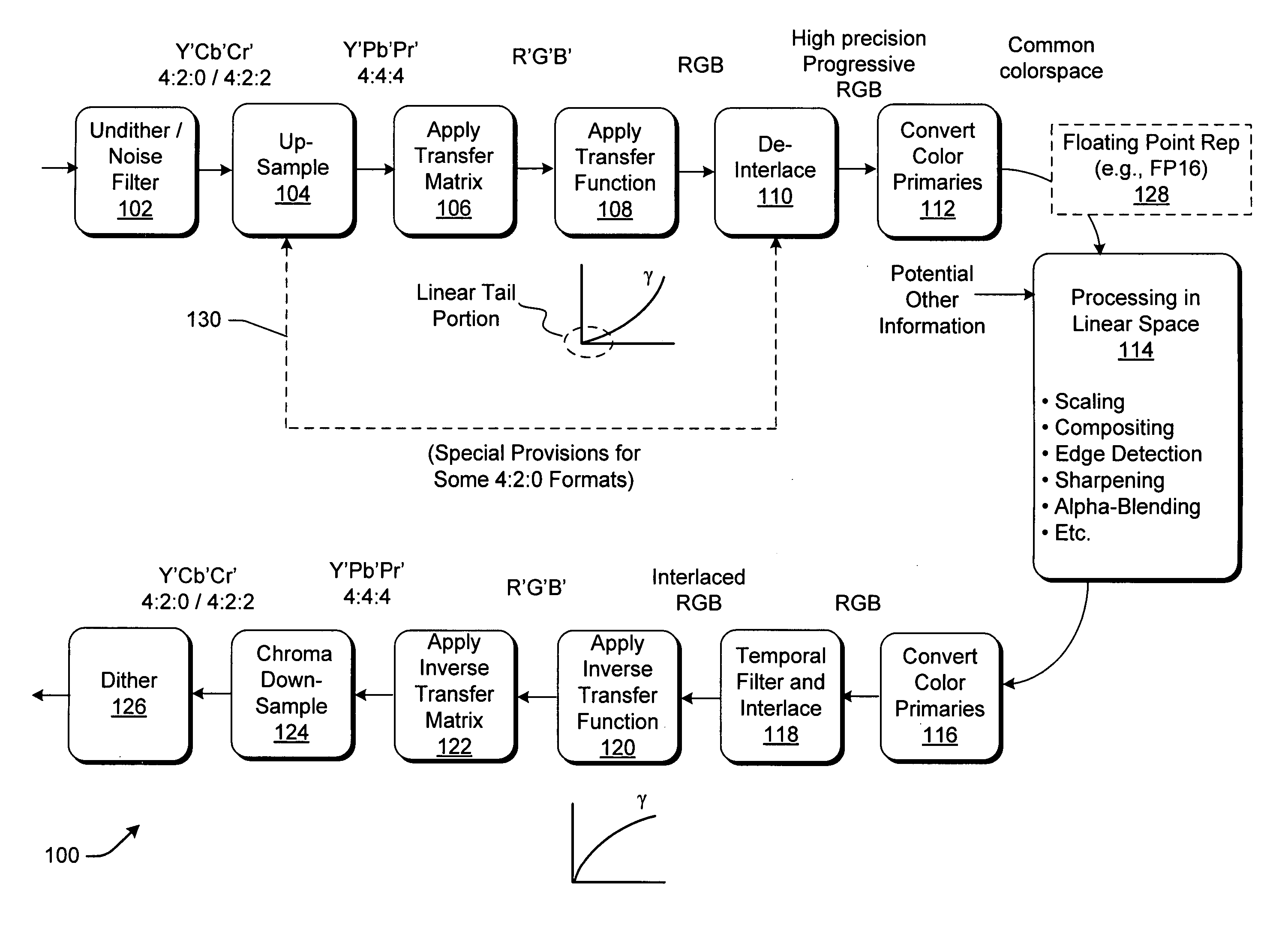

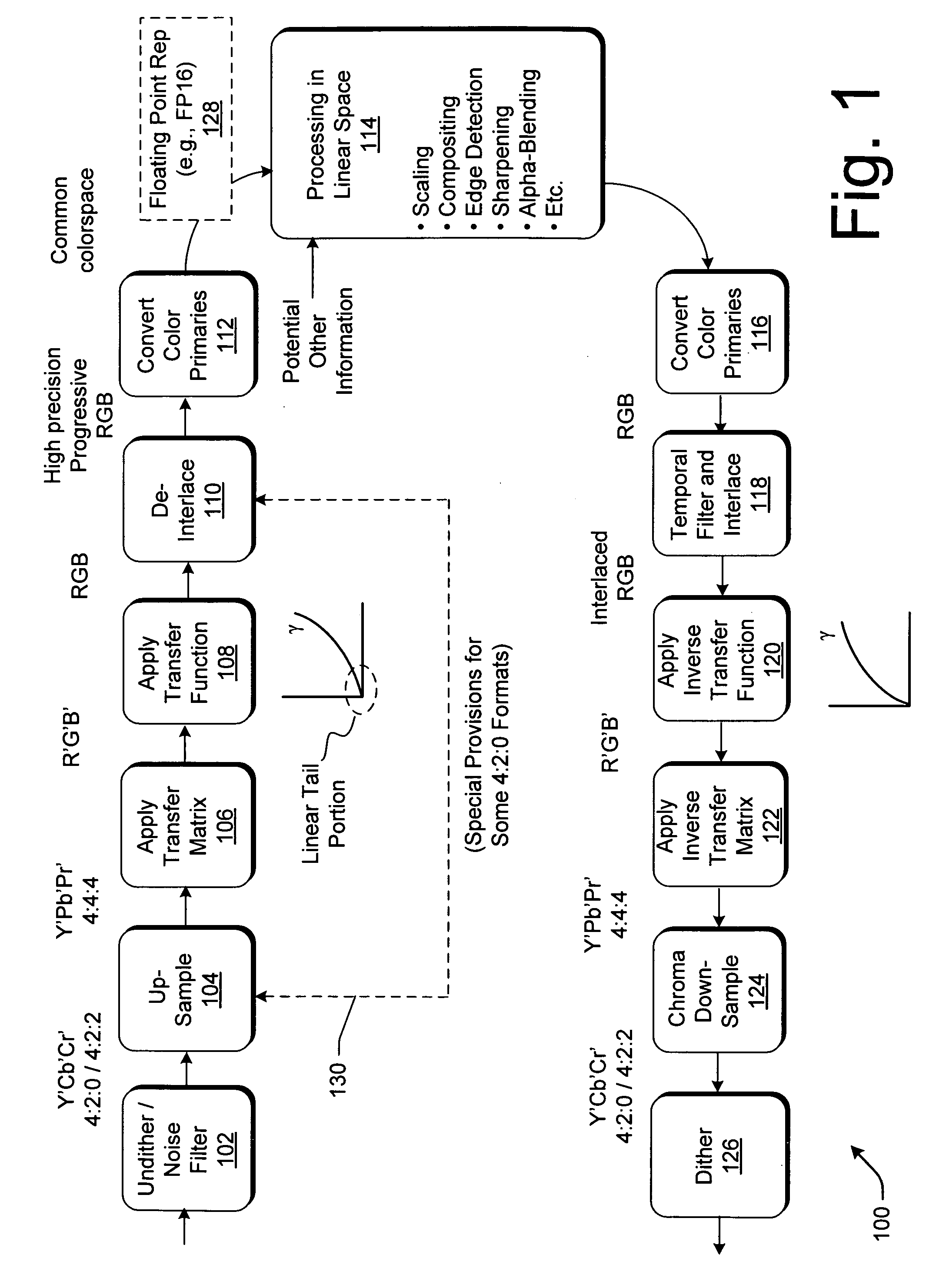

ActiveUS20050063586A1Reduce the amount requiredImprove accuracyCharacter and pattern recognitionPictoral communicationImaging processingFloating point

Strategies are described for processing image information in a linear form to reduce the amount of artifacts (compared to processing the data in nonlinear form). Exemplary types of processing operations can include, scaling, compositing, alpha-blending, edge detection, and so forth. In a more specific implementation, strategies are described for processing image information that is: a) linear; b) in the RGB color space; c) high precision (e.g., provided by floating point representation); d) progressive; and e) full channel. Other improvements provide strategies for: a) processing image information in a pseudo-linear space to improve processing speed; b) implementing an improved error dispersion technique; c) dynamically calculating and applying filter kernels; d) producing pipeline code in an optimal manner; and e) implementing various processing tasks using novel pixel shader techniques.

Owner:MICROSOFT TECH LICENSING LLC

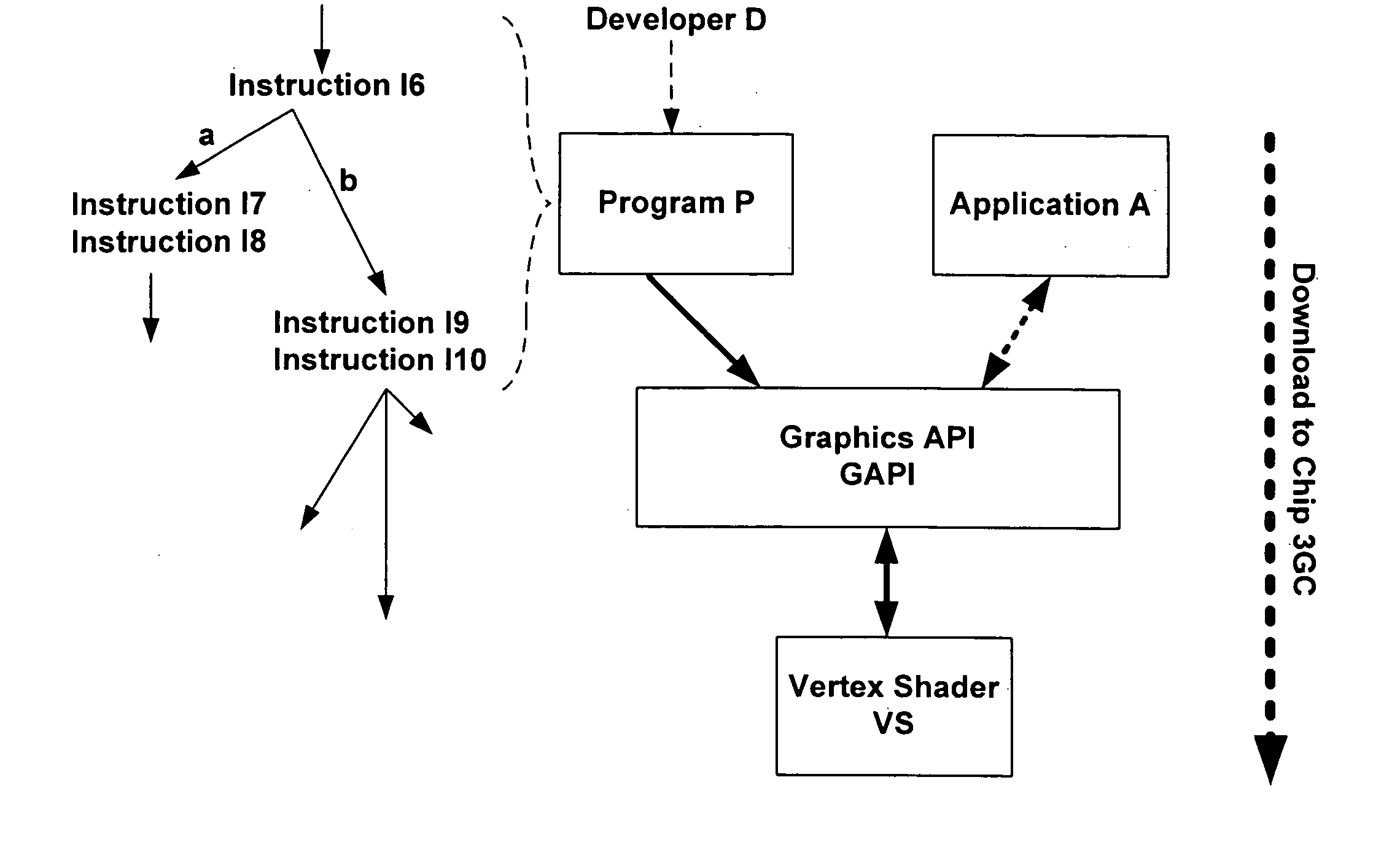

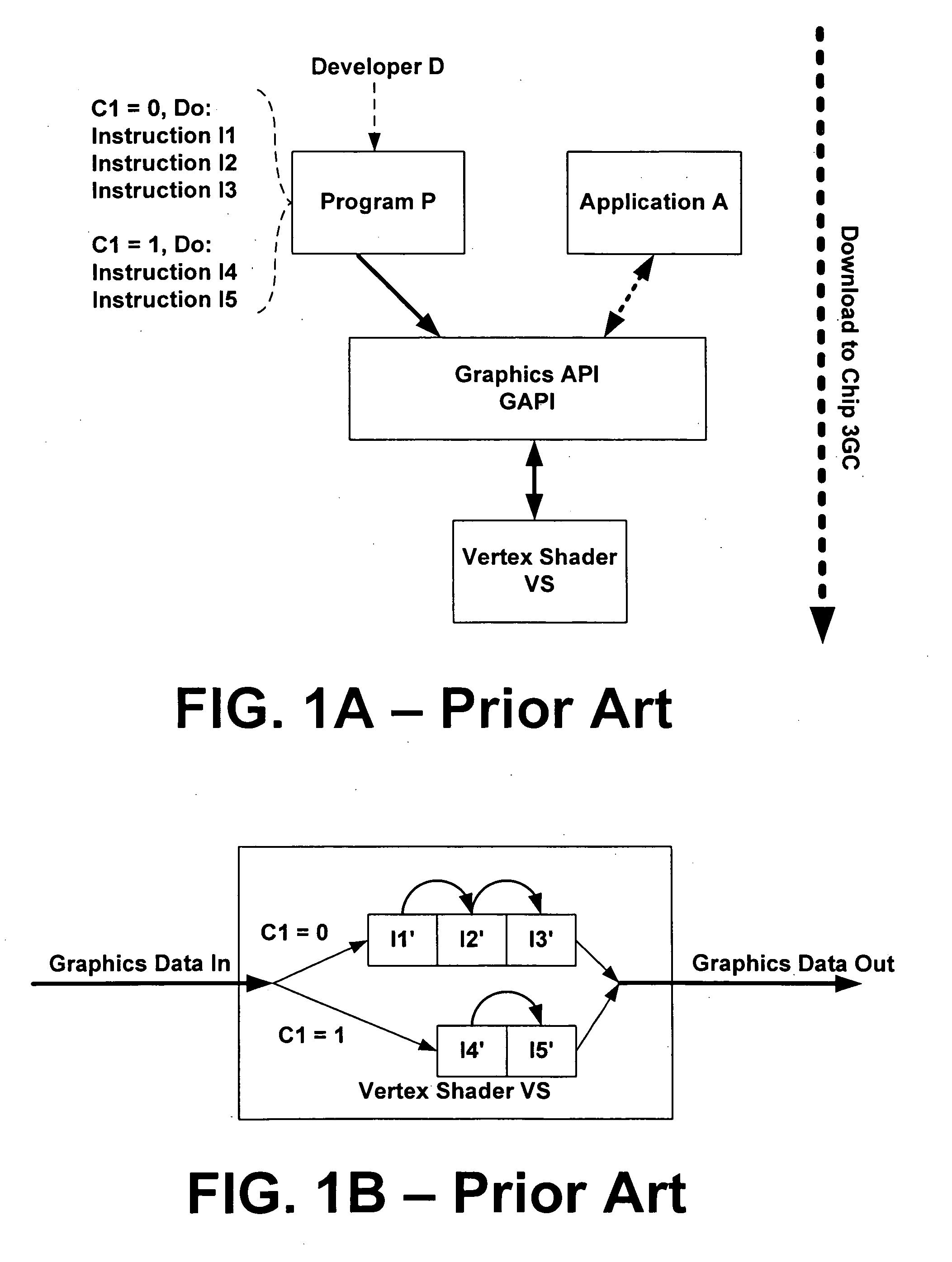

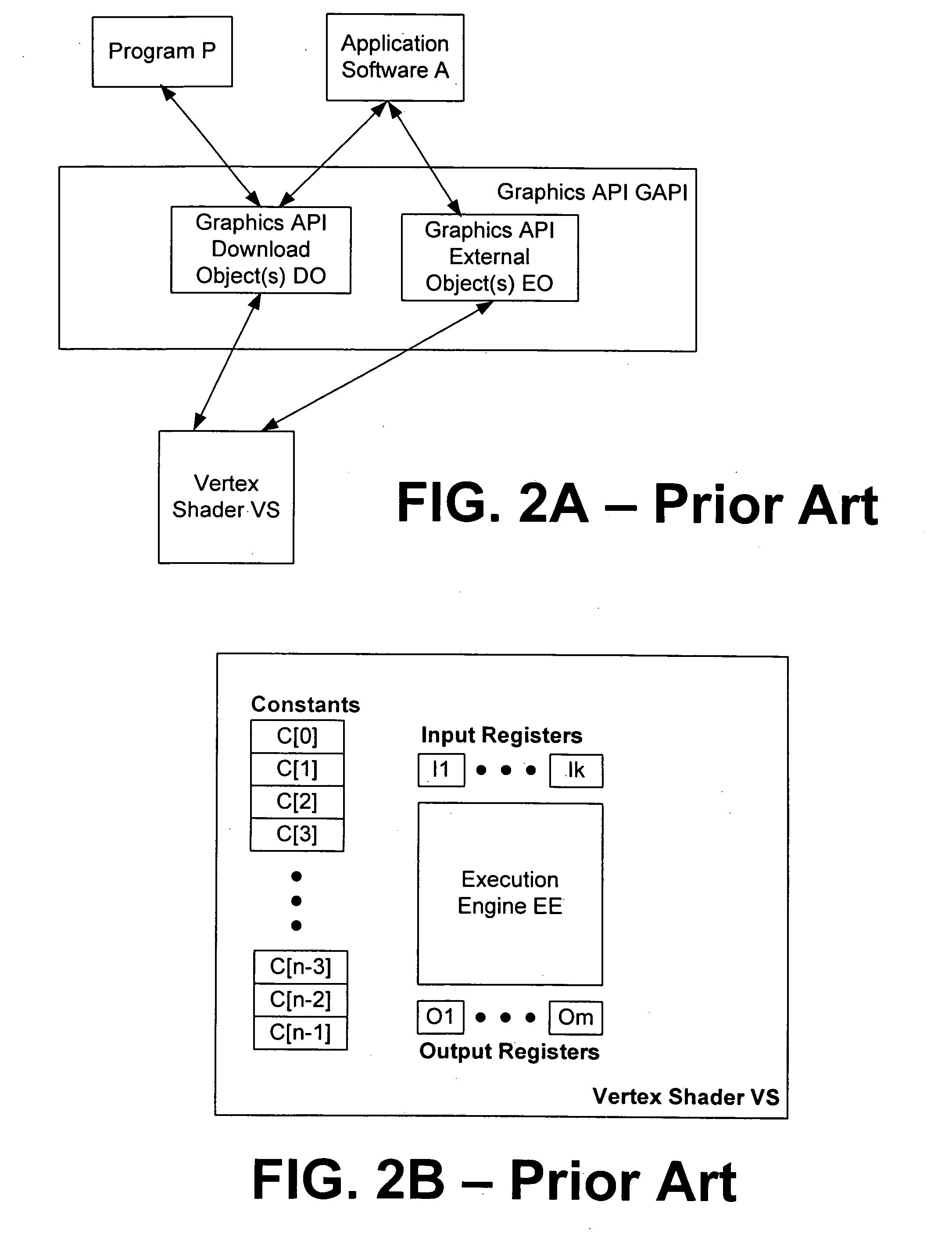

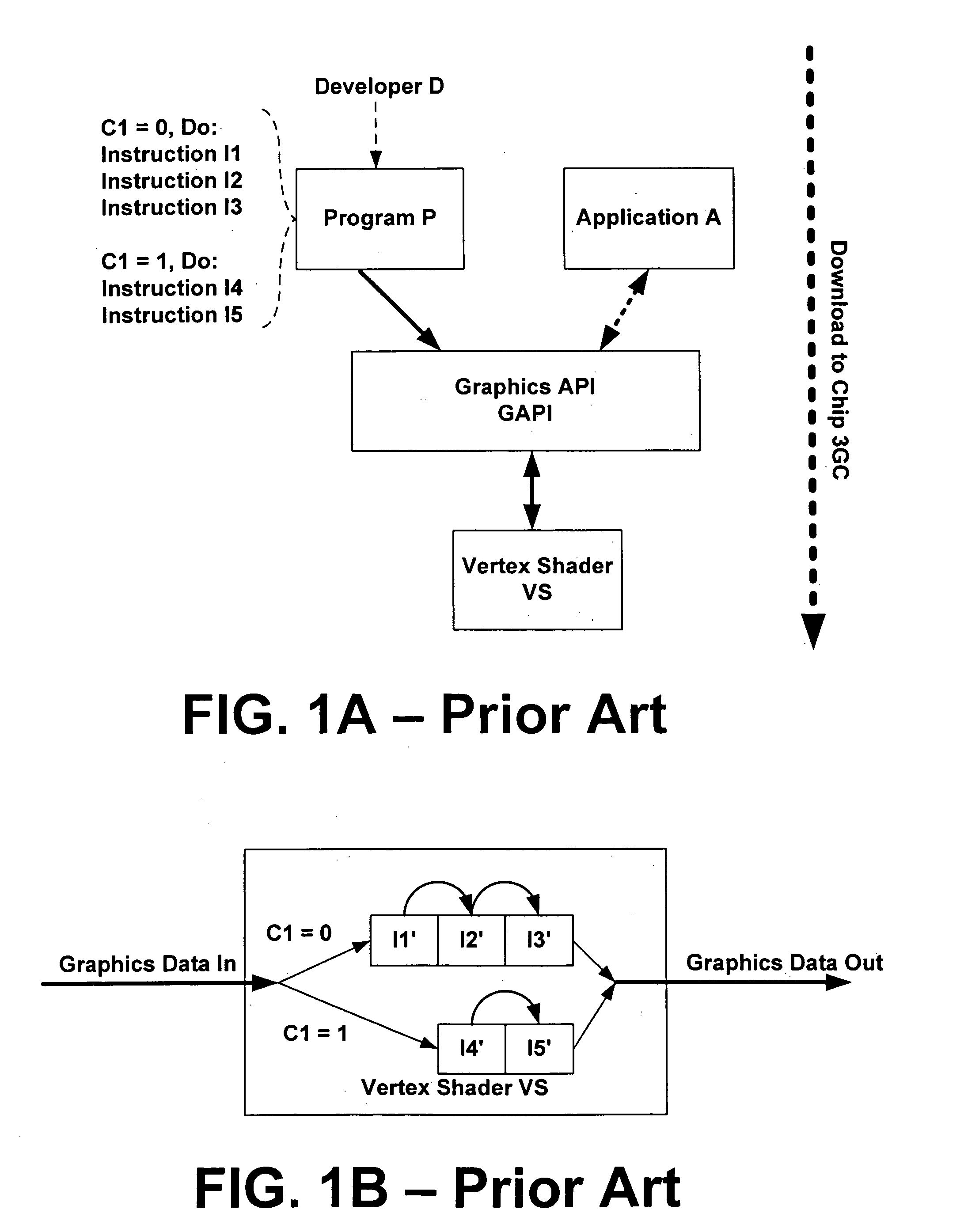

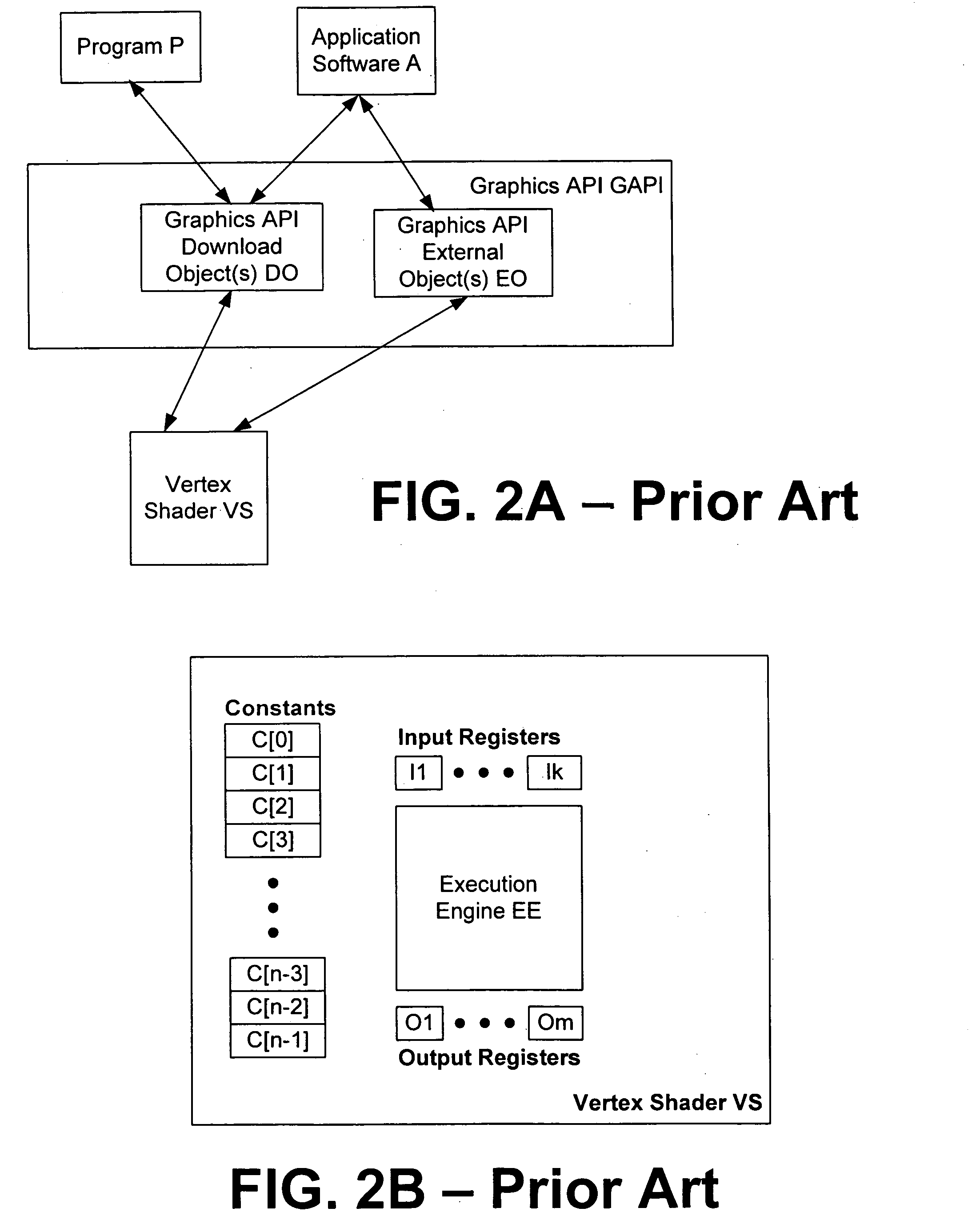

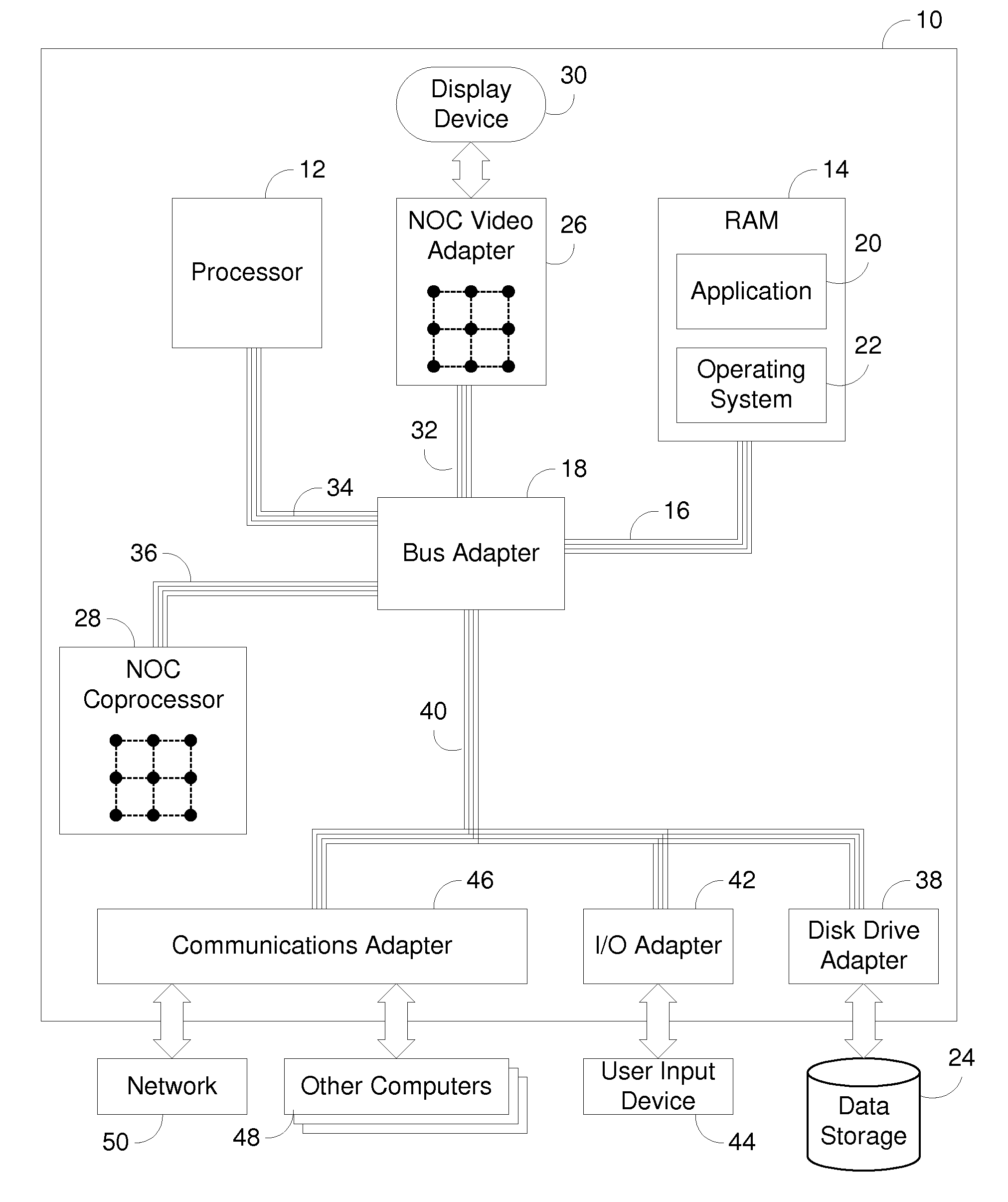

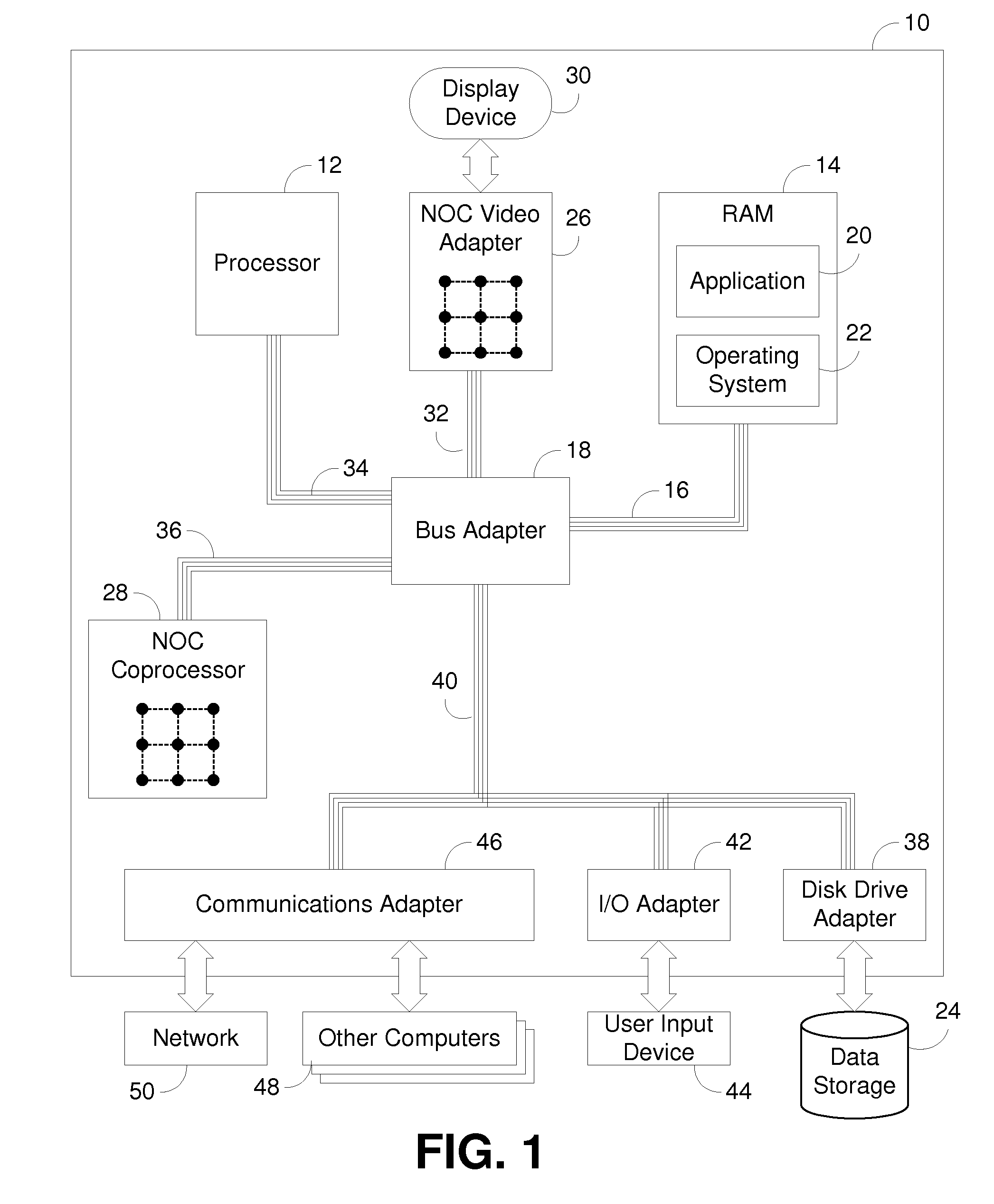

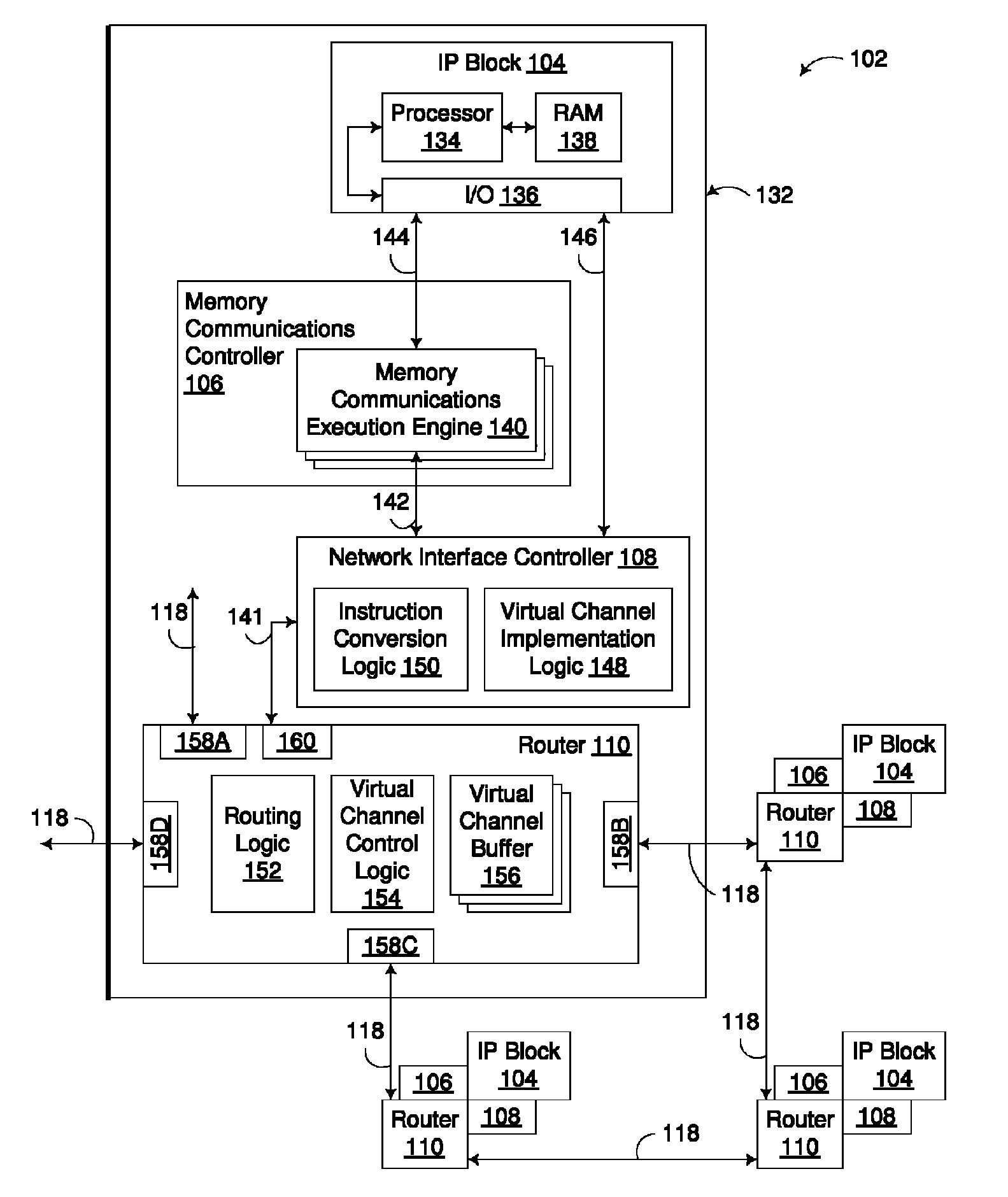

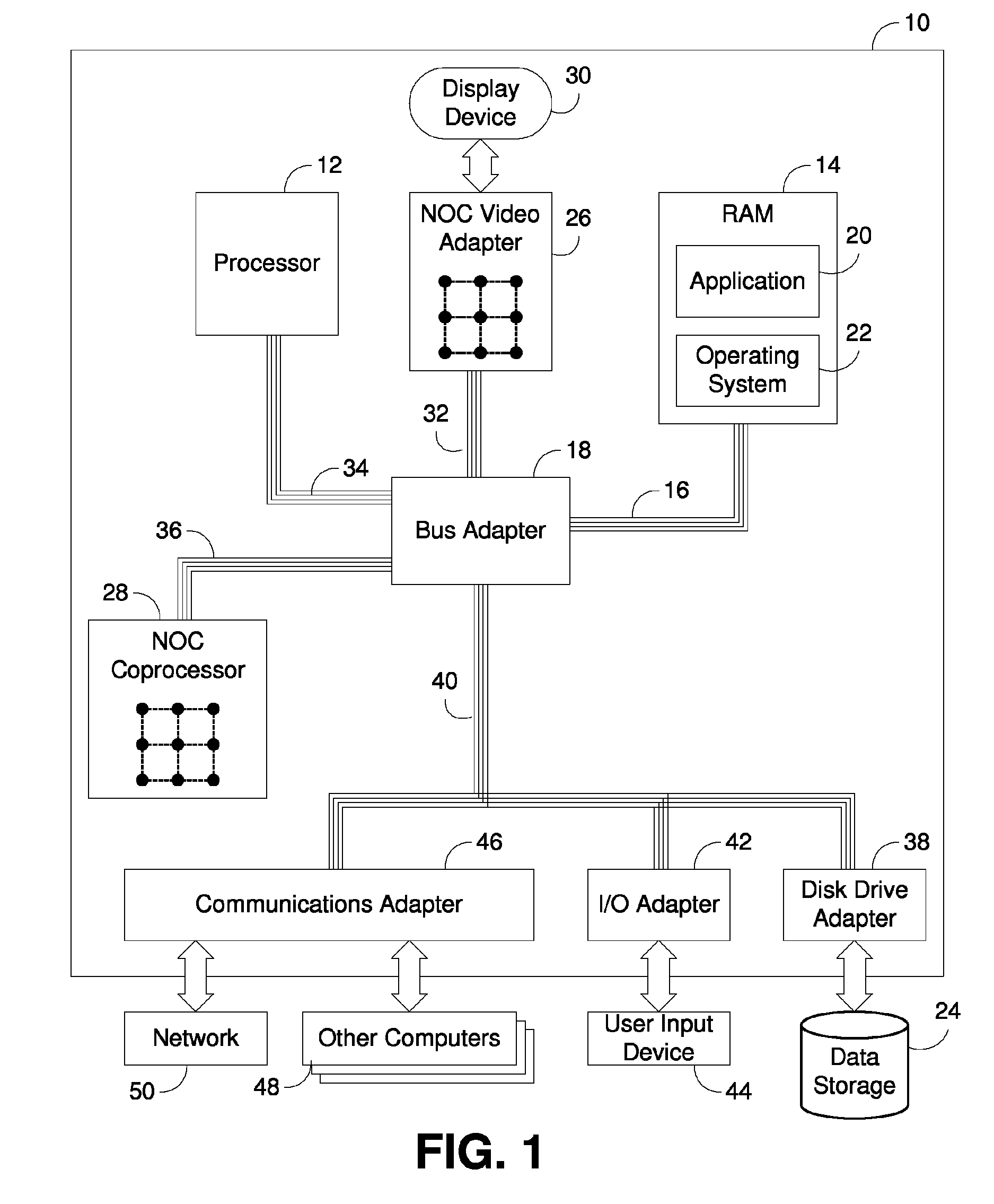

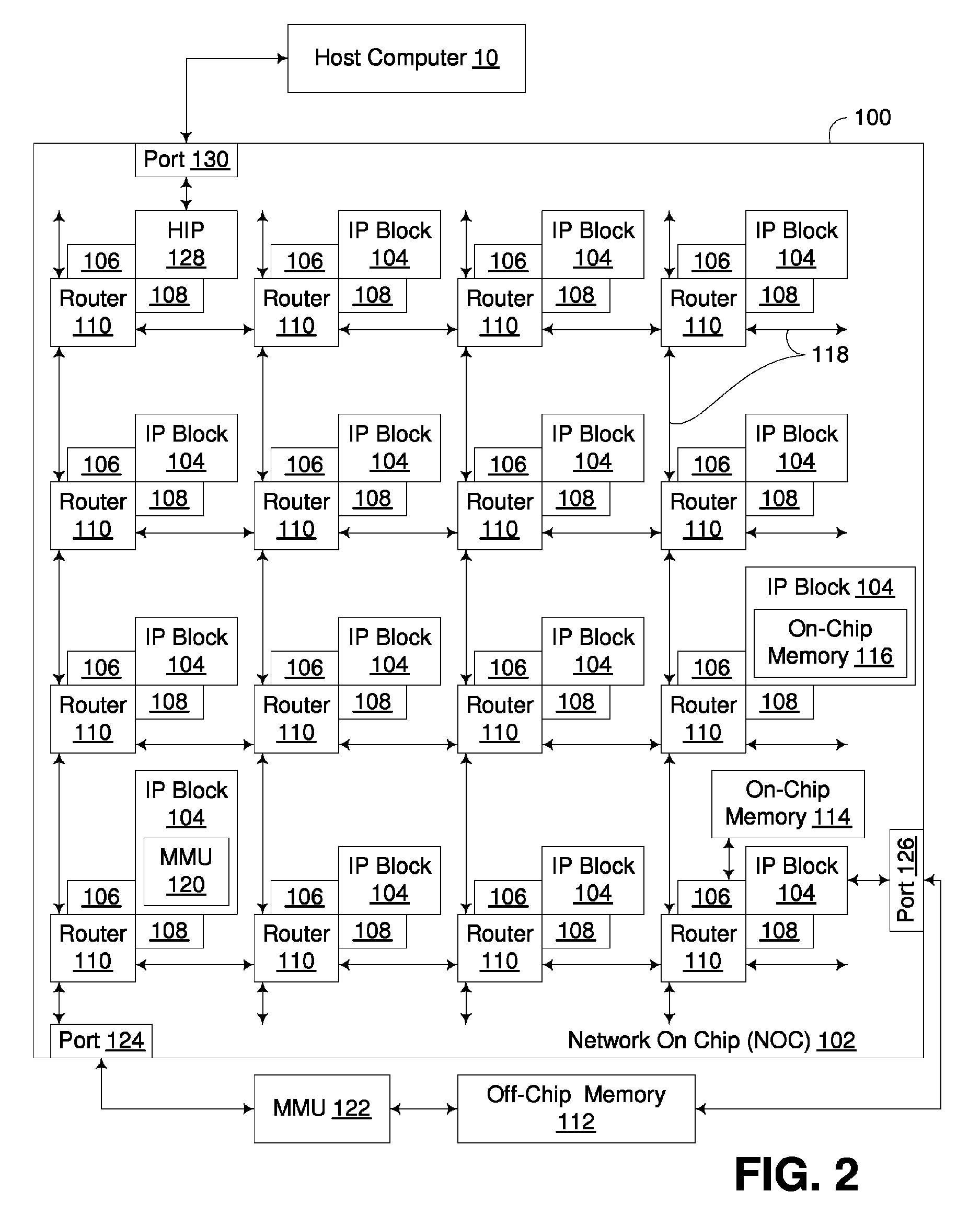

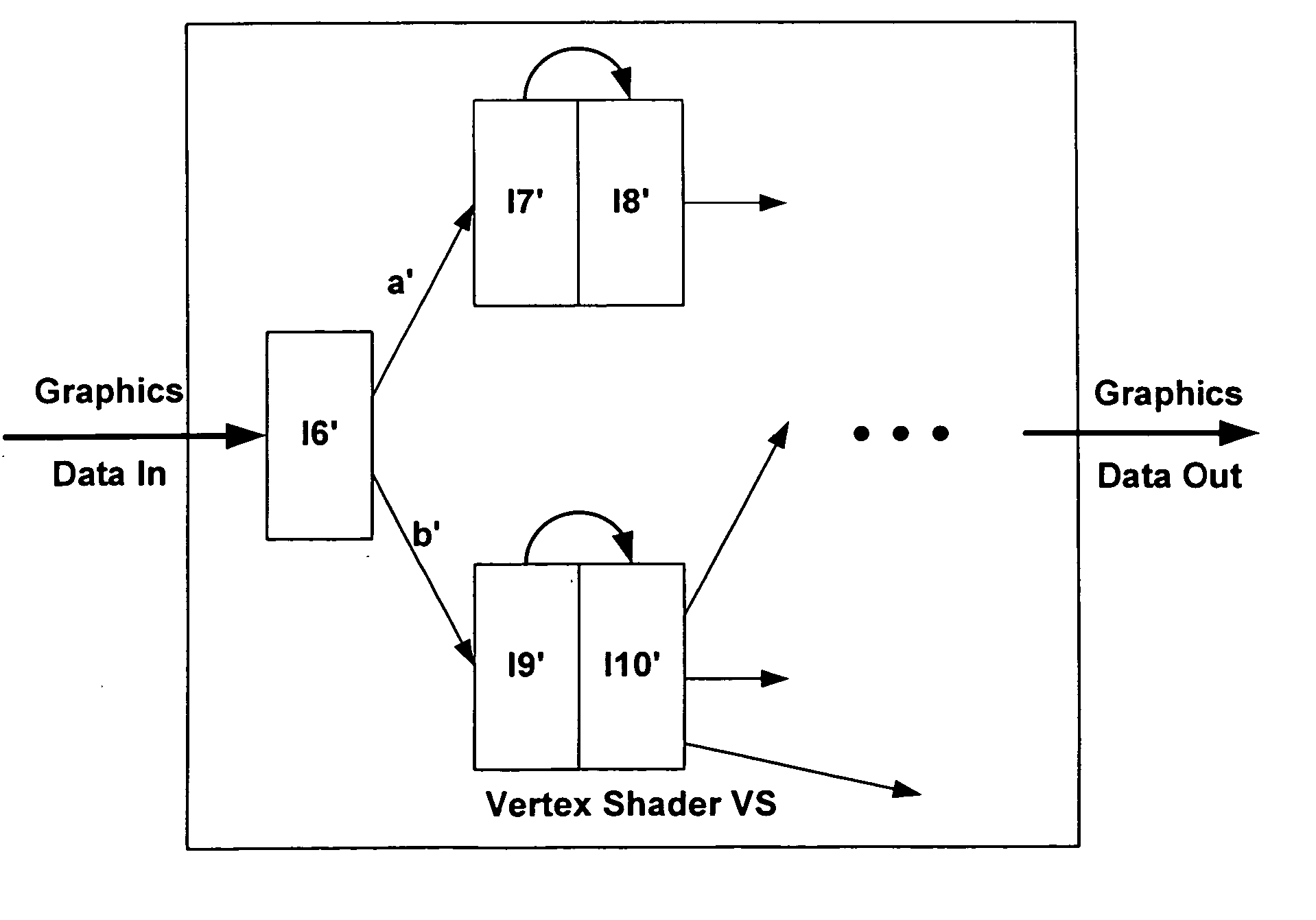

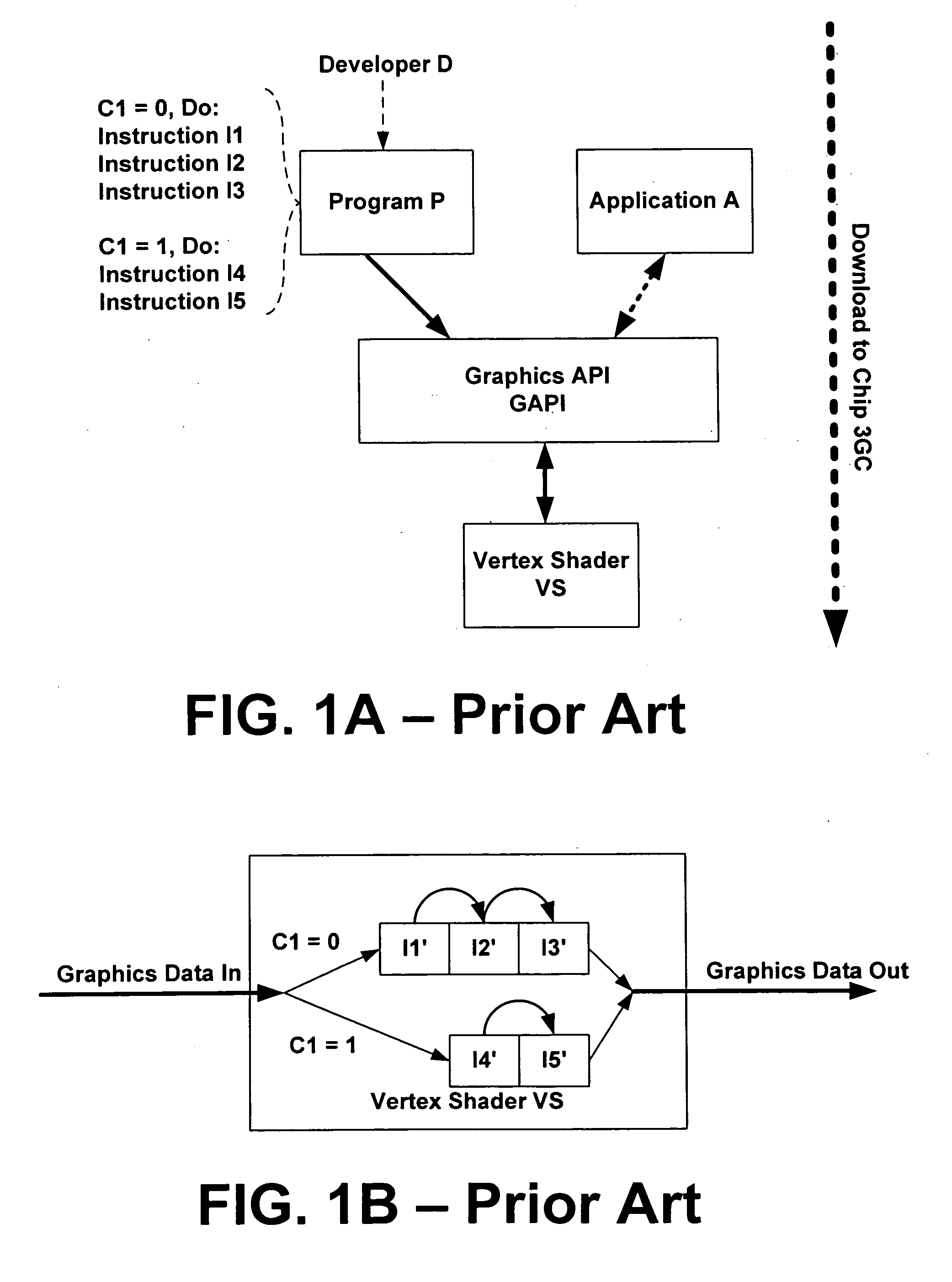

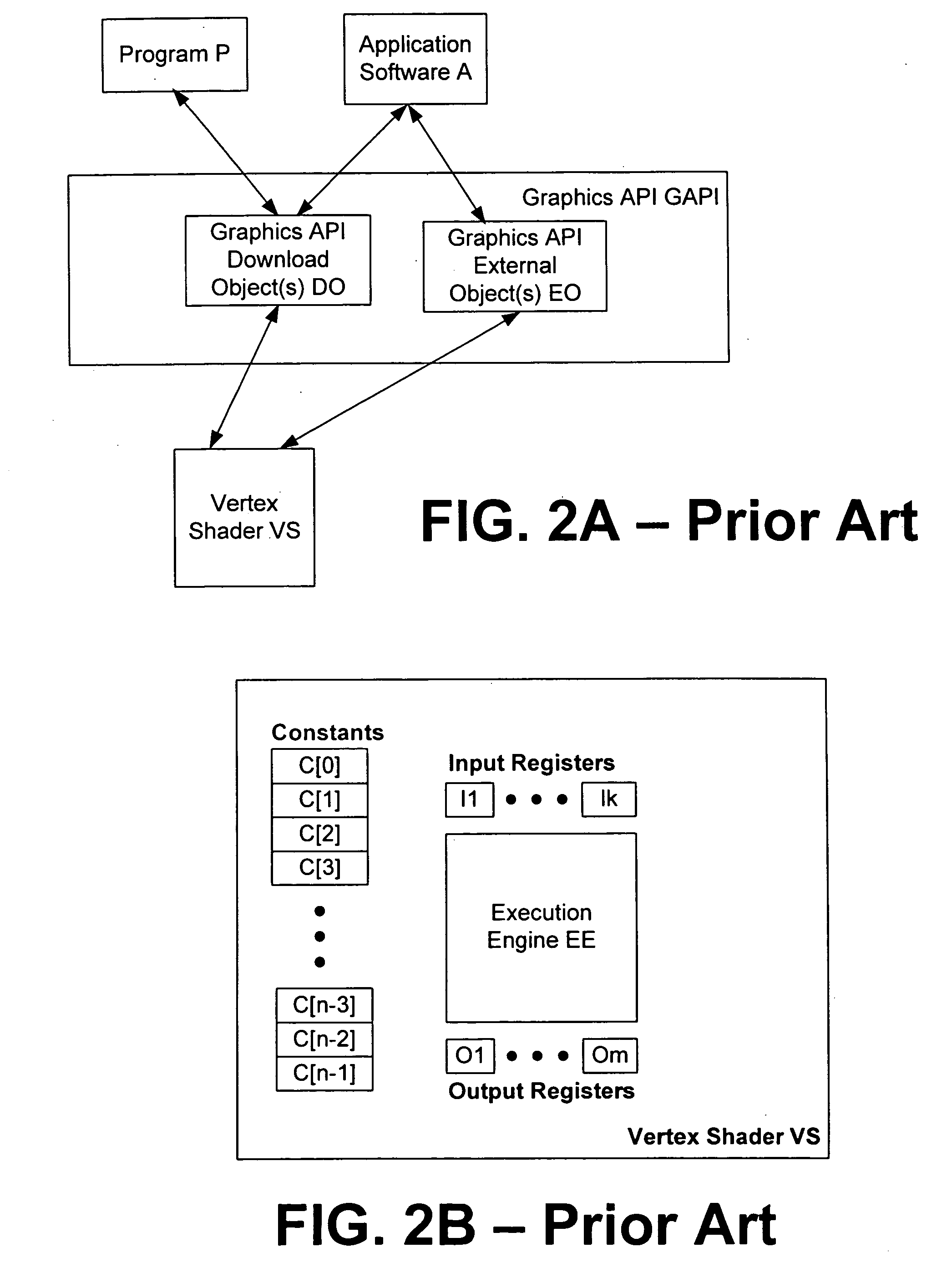

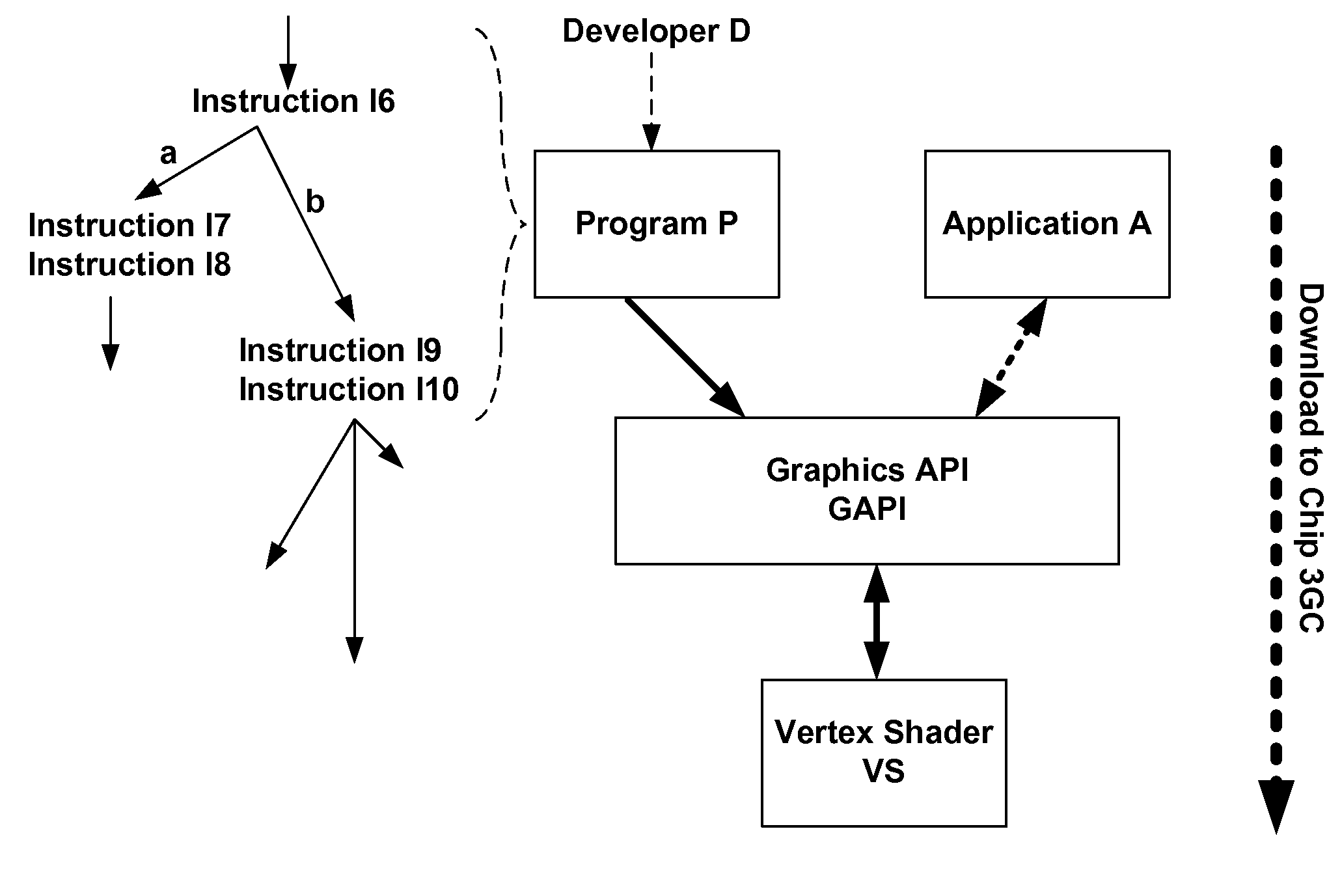

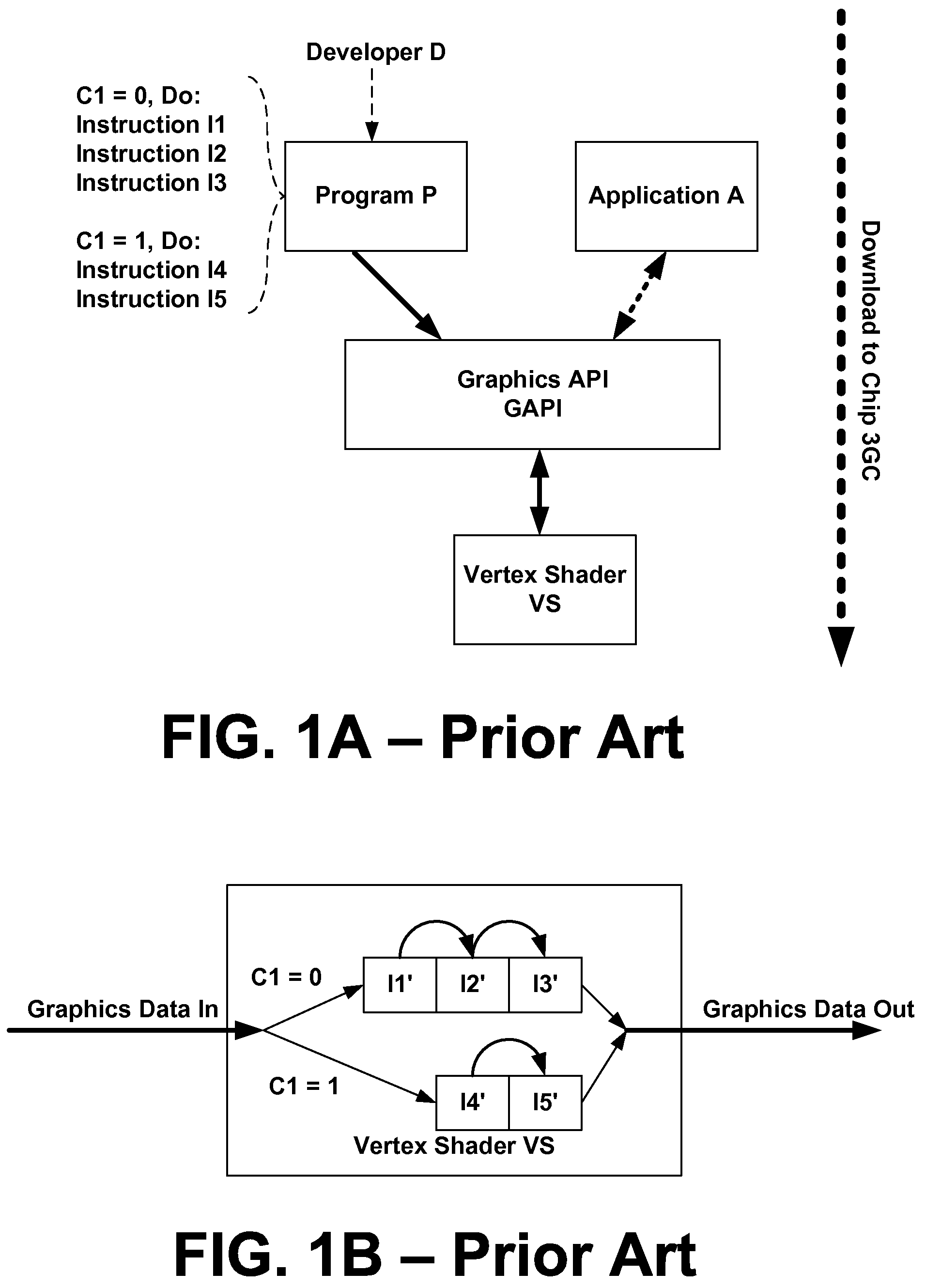

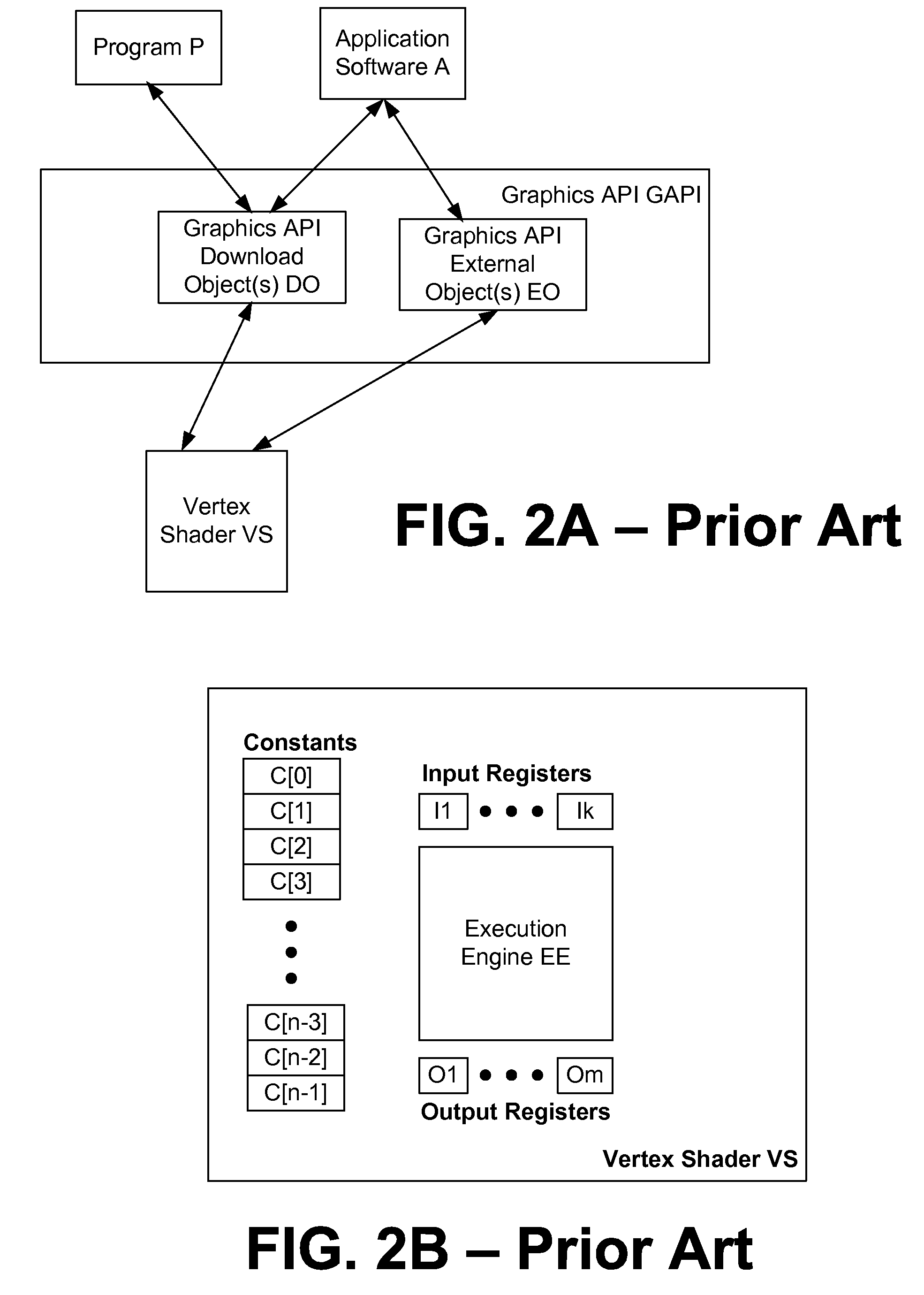

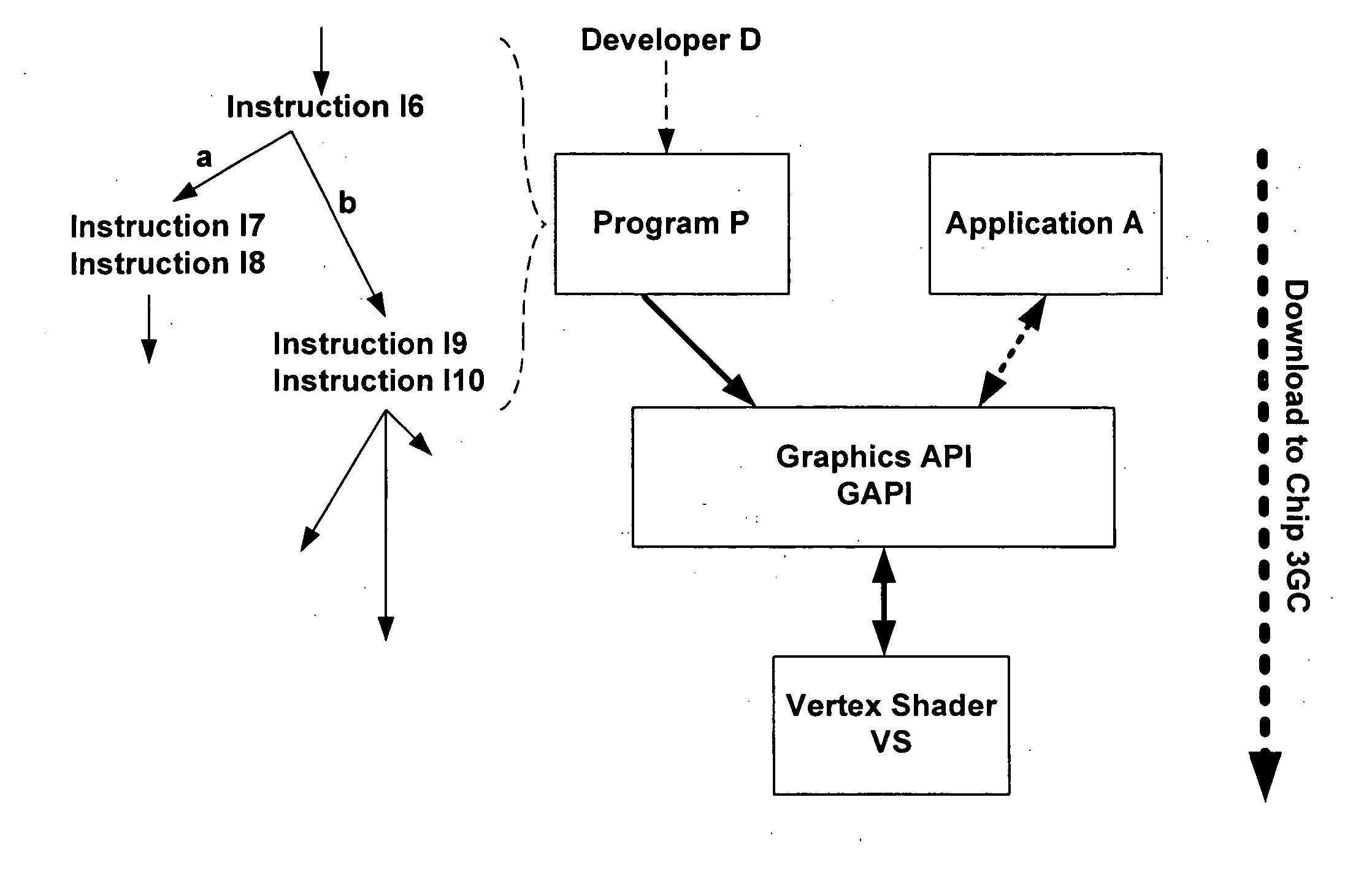

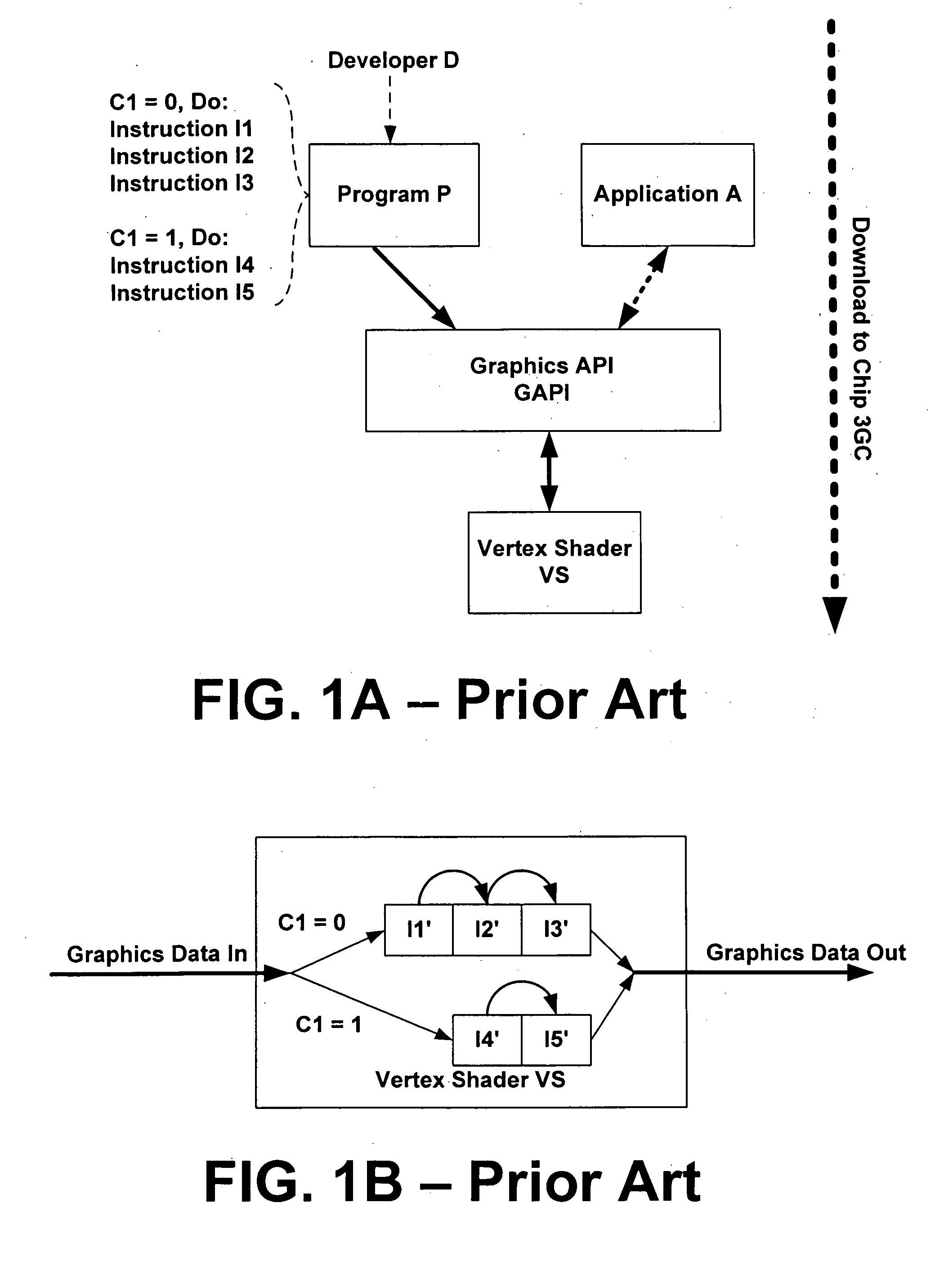

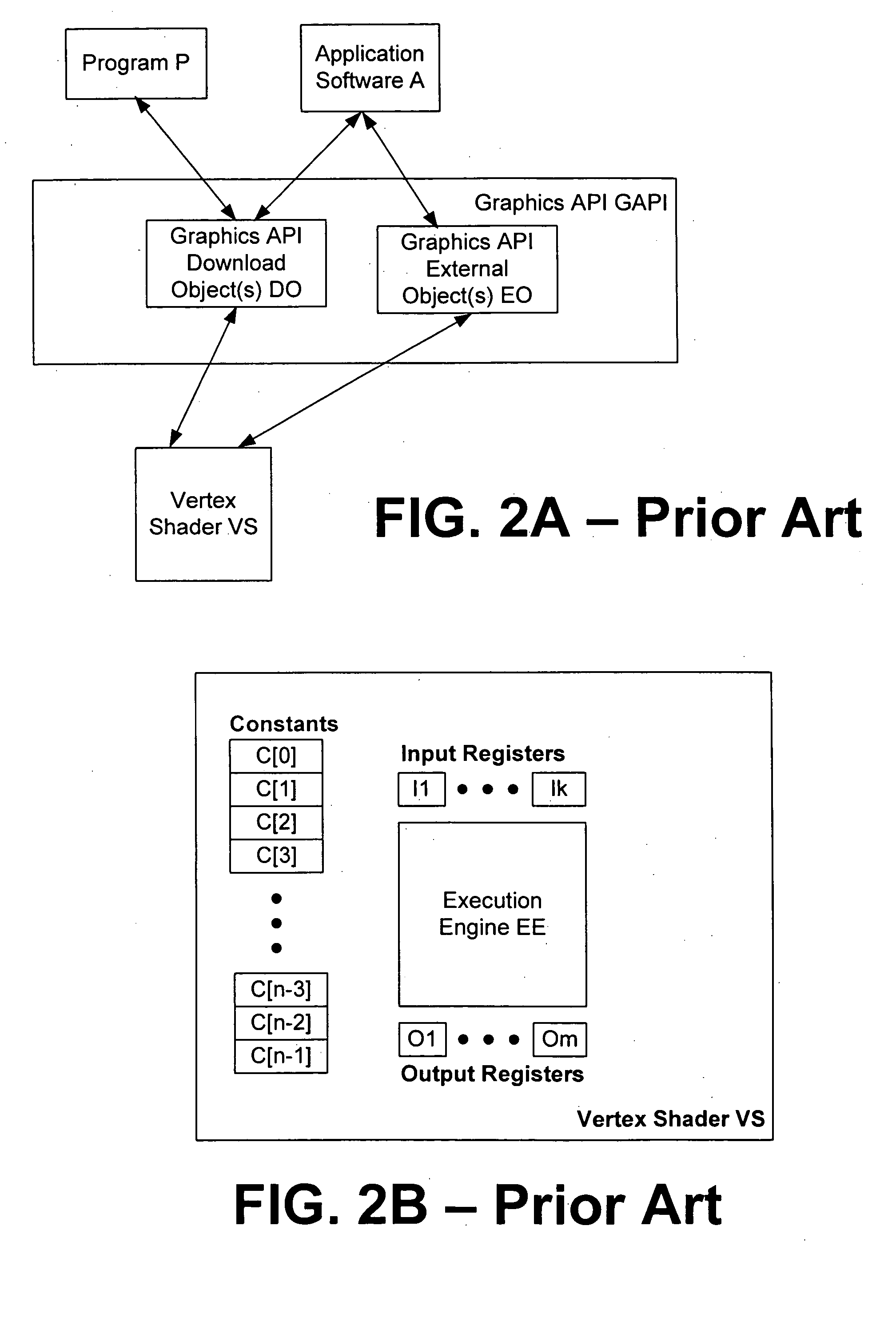

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding techniques

ActiveUS20050122330A1Improve abilitiesSophisticated effectDigital computer detailsNext instruction address formationComputational scienceCoprocessor

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding processing and communication techniques are provided. For an improved graphics pipeline, the invention provides a class of co-processing device, such as a graphics processor unit (GPU), providing improved capabilities for an abstract or virtual machine for performing graphics calculations and rendering. The invention allows for runtime-predicated flow control of programs downloaded to coprocessors, enables coprocessors to include indexable arrays of on-chip storage elements that are readable and writable during execution of programs, provides native support for textures and texture maps and corresponding operations in a vertex shader, provides frequency division of vertex streams input to a vertex shader with optional support for a stream modulo value, provides a register storage element on a pixel shader and associated interfaces for storage associated with representing the “face” of a pixel, provides vertex shaders and pixel shaders with more on-chip register storage and the ability to receive larger programs than any existing vertex or pixel shaders and provides 32 bit float number support in both vertex and pixel shaders.

Owner:MICROSOFT TECH LICENSING LLC

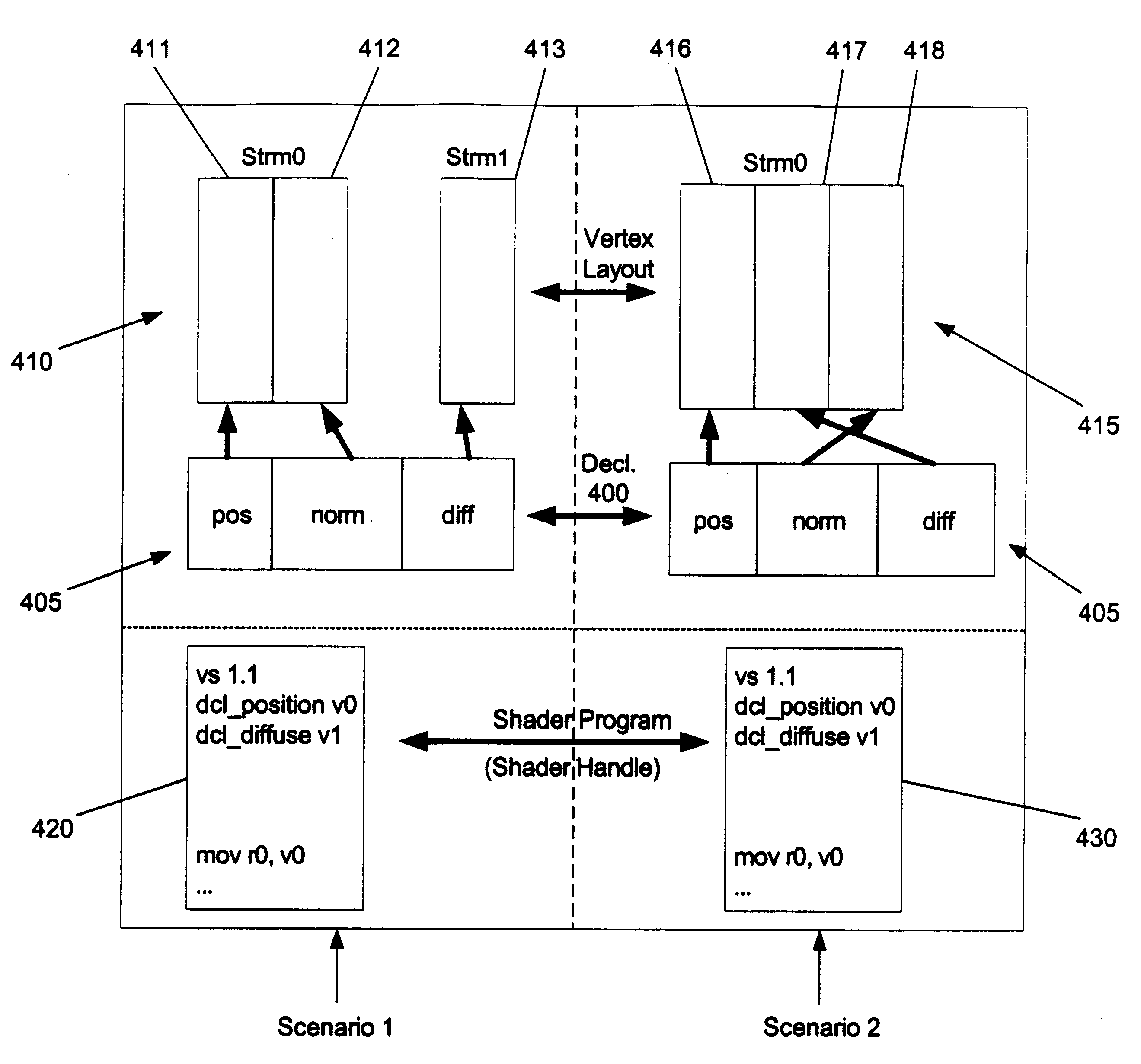

Usage semantics

InactiveUS6839062B2Improve the level ofFlexible workflowData processing applicationsImage data processing detailsData streamData set

Usage semantics allow for shaders to be authored independently of the actual vertex data and accordingly enables their reuse. Usage semantics define a feature that binds data between distinct components to allow them to work together. In various embodiments, the components include high level language variables that are bound by an application or by vertex data streams, high level language fragments to enable several fragments to be developed separately and compiled at a later time together to form a single shader, assembly language variables that get bound to vertex data streams, and parameters between vertex and pixel shaders. This allows developers to be able to program the shaders in the assembly and high level language with variables that refer to names rather than registers. By allowing this decoupling of registers from the language, developers can work on the language separately from the vertex data and modify and enhance high level language shaders without having to manually manipulate the registers. This also allows the same shaders to work on different sets of mesh data, allowing the shaders to be reused. Generally, semantics can be used as a data binding protocol between distinct areas of the programmable pipeline to allow for a more flexible workflow.

Owner:MICROSOFT TECH LICENSING LLC

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding techniques

ActiveUS20050122334A1Improve abilitiesSophisticated effectDigital computer detailsNext instruction address formationComputational scienceCoprocessor

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding processing and communication techniques are provided. For an improved graphics pipeline, the invention provides a class of co-processing device, such as a graphics processor unit (GPU), providing improved capabilities for an abstract or virtual machine for performing graphics calculations and rendering. The invention allows for runtime-predicated flow control of programs downloaded to coprocessors, enables coprocessors to include indexable arrays of on-chip storage elements that are readable and writable during execution of programs, provides native support for textures and texture maps and corresponding operations in a vertex shader, provides frequency division of vertex streams input to a vertex shader with optional support for a stream modulo value, provides a register storage element on a pixel shader and associated interfaces for storage associated with representing the “face” of a pixel, provides vertex shaders and pixel shaders with more on-chip register storage and the ability to receive larger programs than any existing vertex or pixel shaders and provides 32 bit float number support in both vertex and pixel shaders.

Owner:MICROSOFT TECH LICENSING LLC

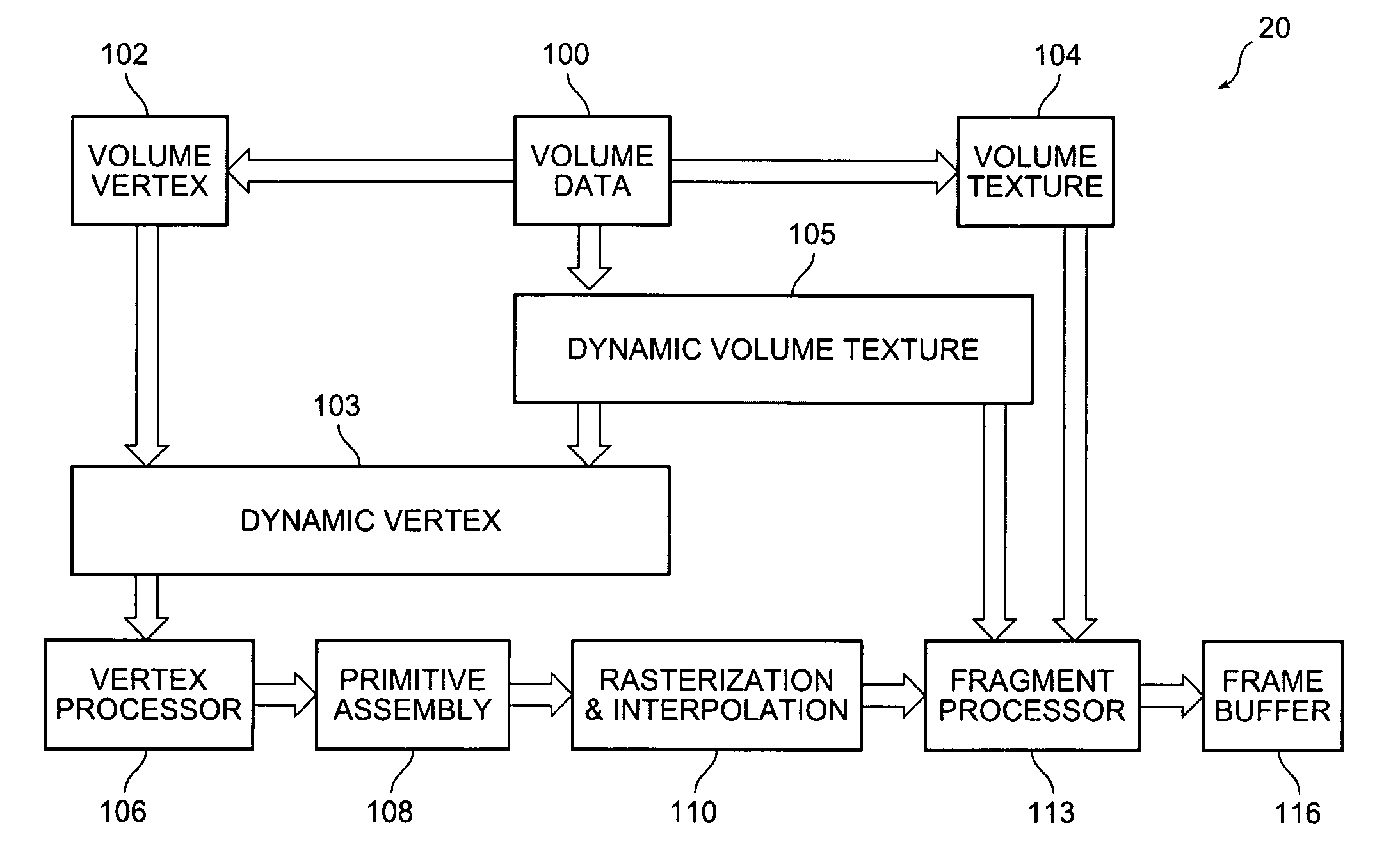

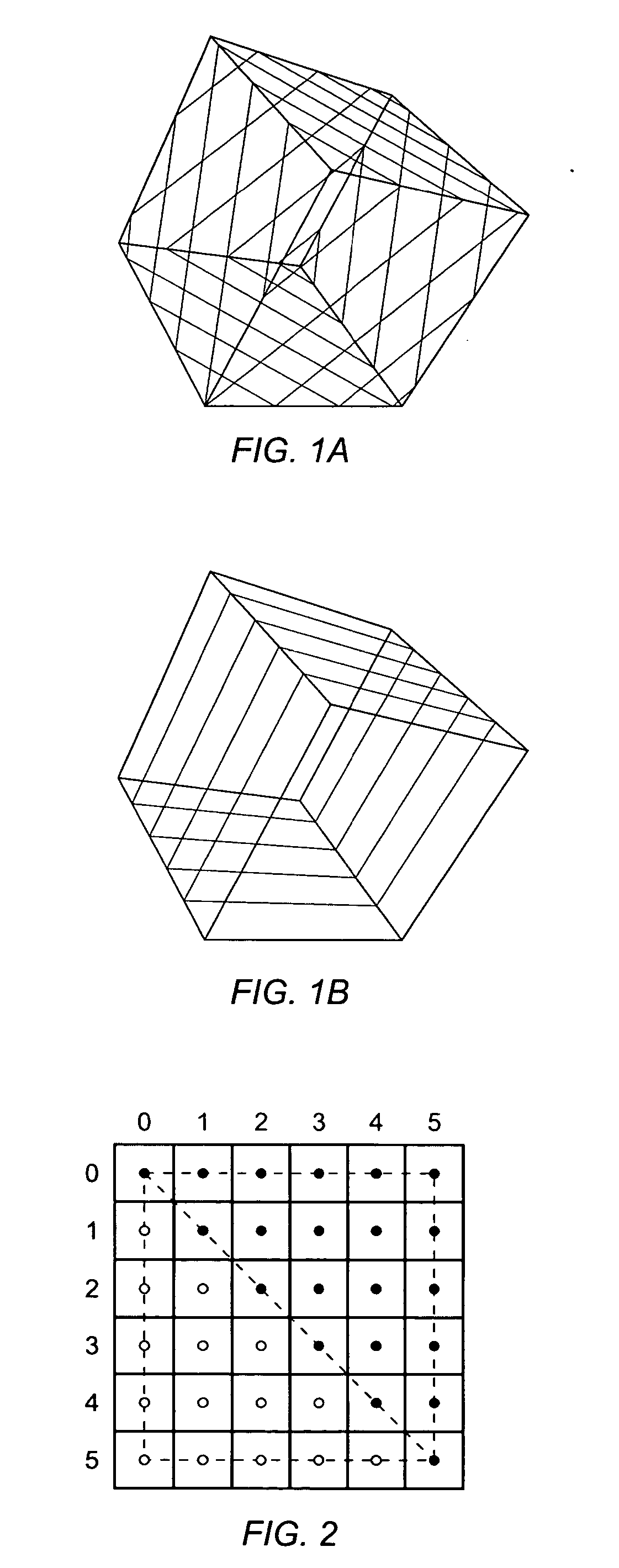

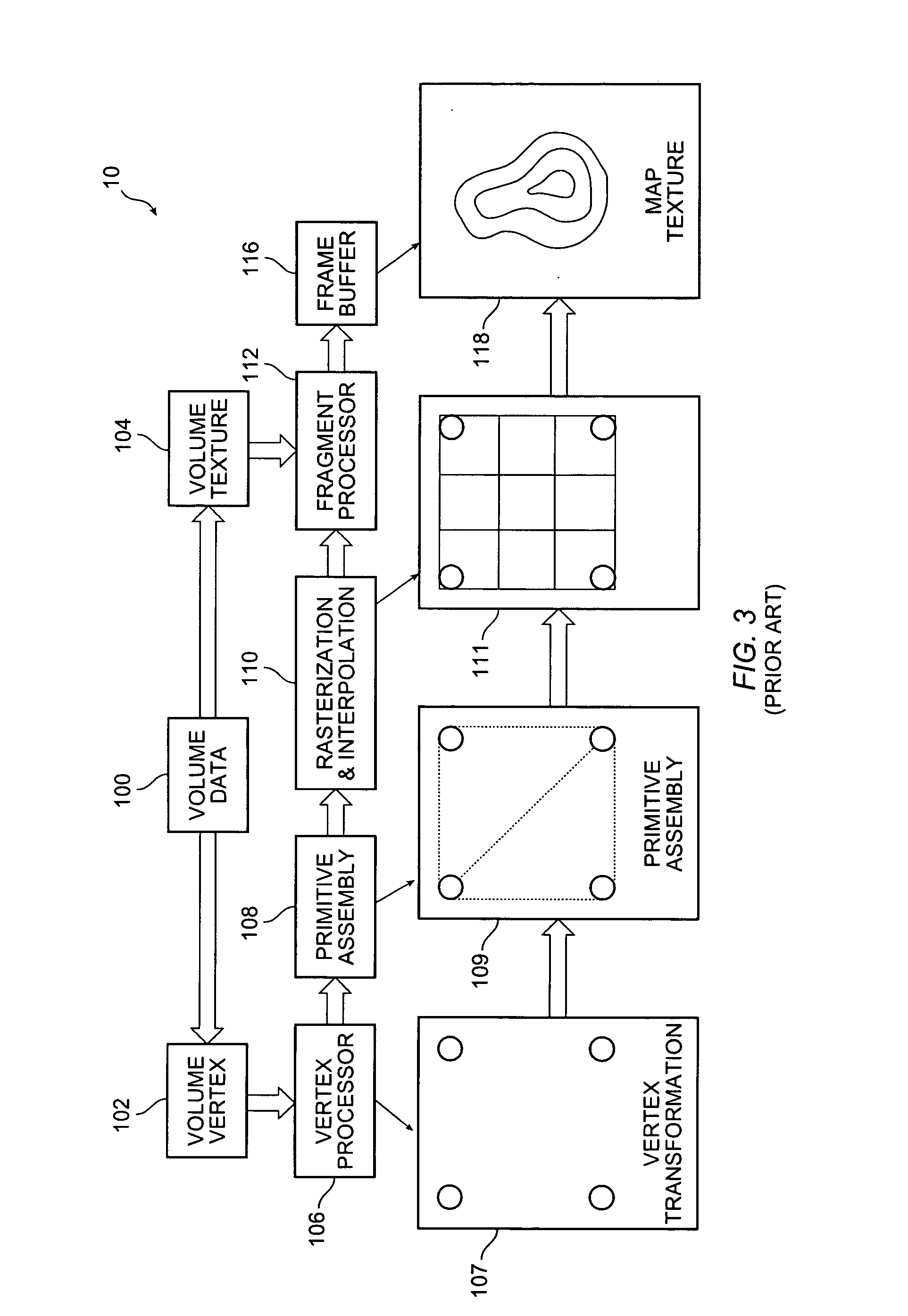

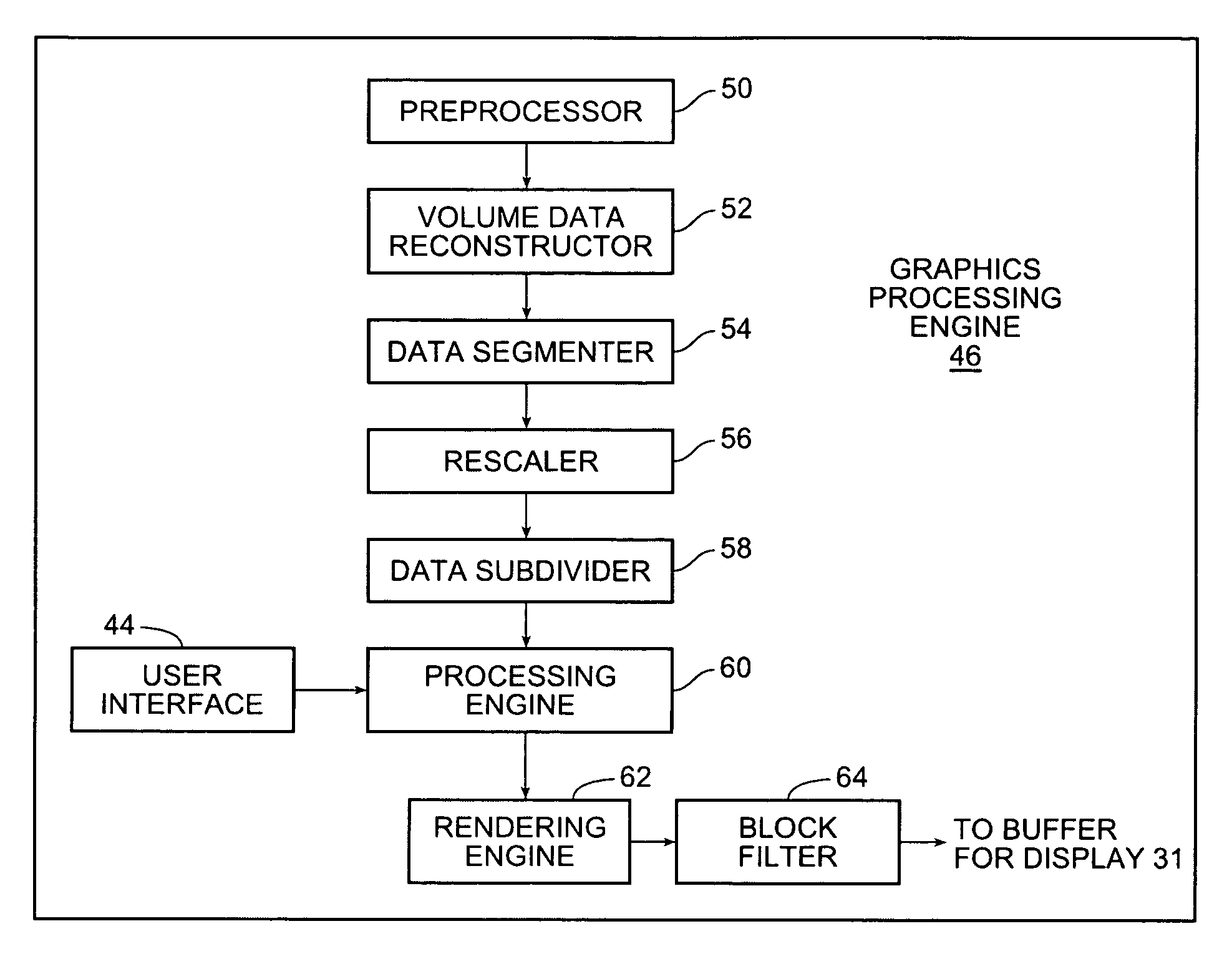

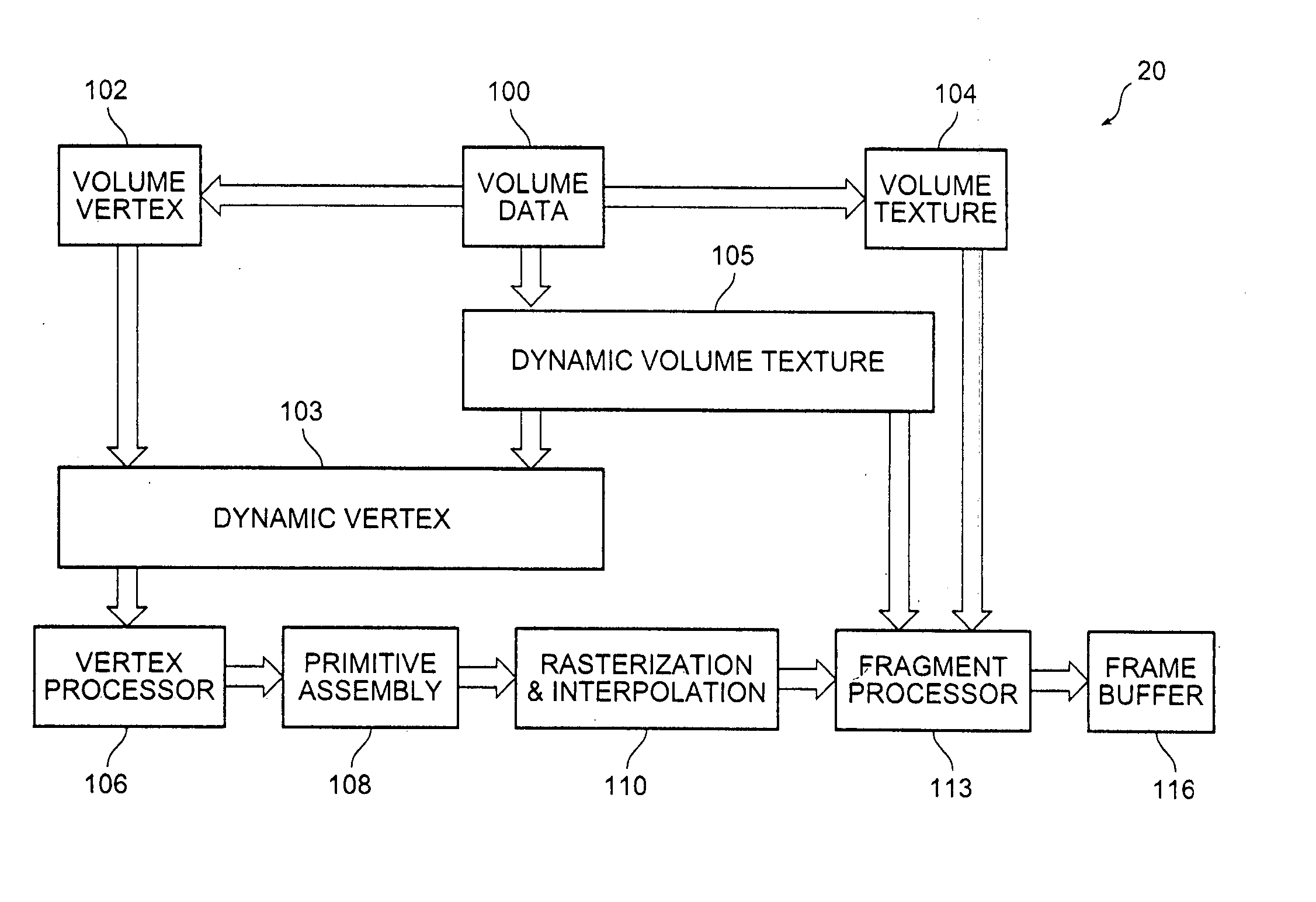

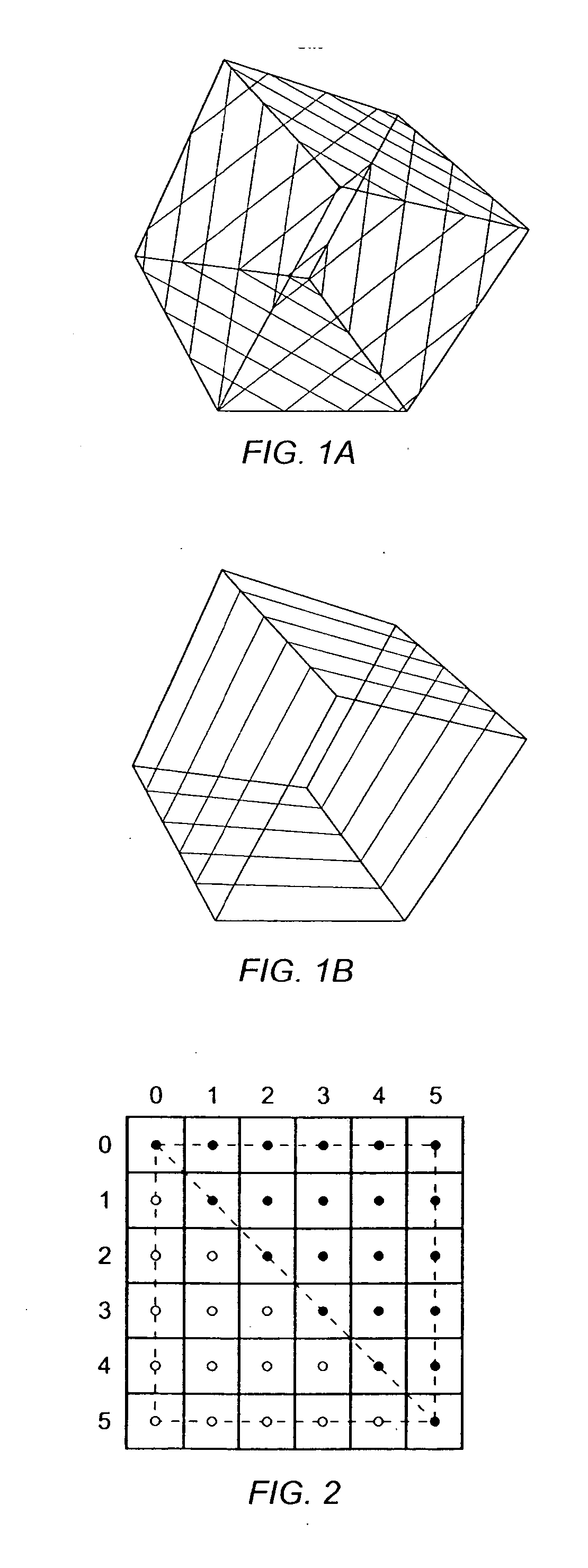

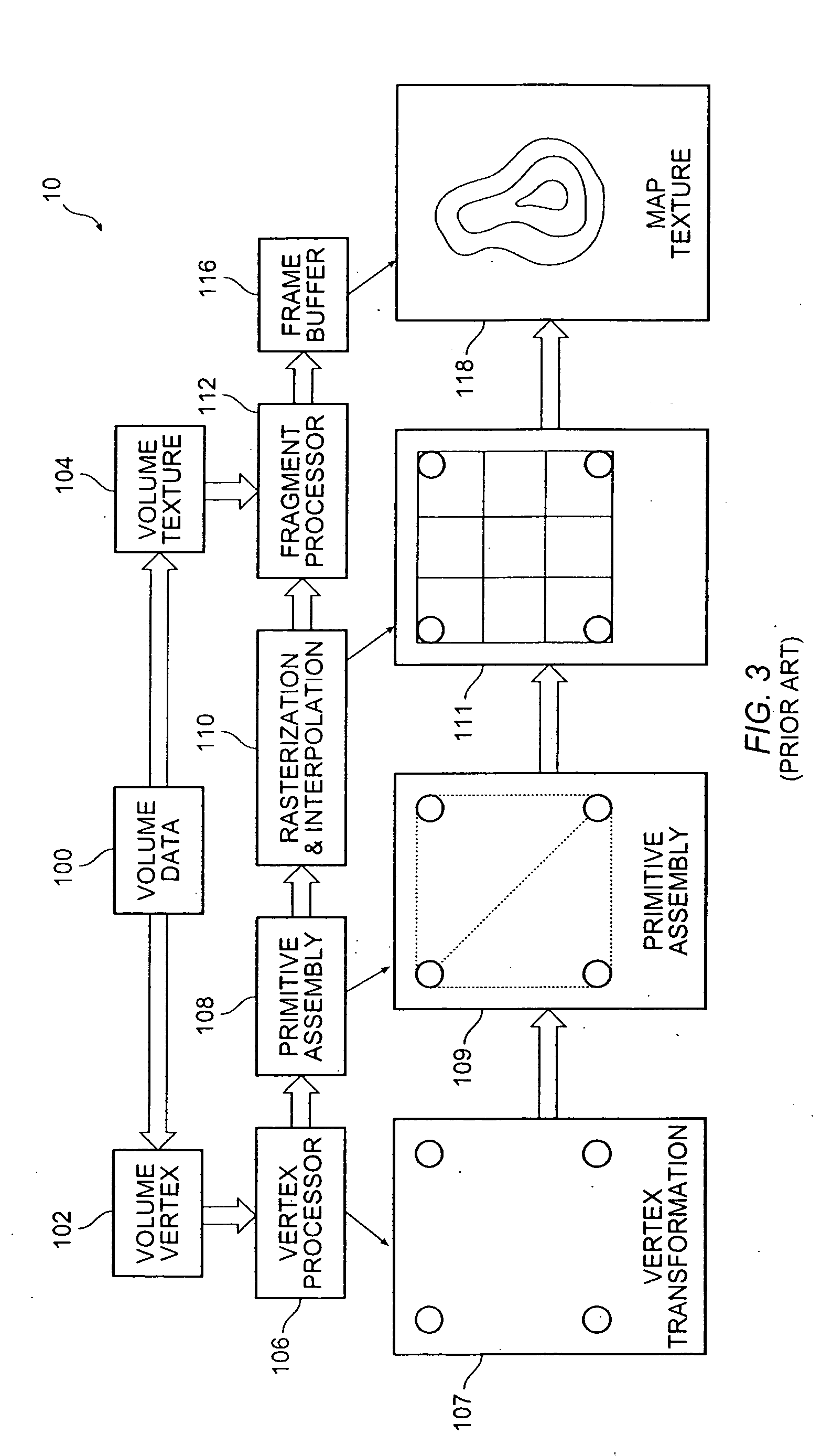

Block-based fragment filtration with feasible multi-GPU acceleration for real-time volume rendering on conventional personal computer

ActiveUS20050231503A1Reduce the burden onDetails involving 3D image dataCathode-ray tube indicatorsVoxelFiltration

A computer-based method and system for interactive volume rendering of a large volume data on a conventional personal computer using hardware-accelerated block filtration optimizing uses 3D-textured axis-aligned slices and block filtration. Fragment processing in a rendering pipeline is lessened by passing fragments to various processors selectively in blocks of voxels based on a filtering process operative on slices. The process involves generating a corresponding image texture and performing two-pass rendering, namely a virtual rendering pass and a main rendering pass. Block filtration is divided into static block filtration and dynamic block filtration. The static block filtration locates any view-independent unused signal being passed to a rasterization pipeline. The dynamic block filtration determines any view-dependent unused block generated due to occlusion. Block filtration processes utilize the vertex shader and pixel shader of a GPU in conventional personal computer graphics hardware. The method is for multi-thread, multi-GPU operation.

Owner:THE CHINESE UNIVERSITY OF HONG KONG

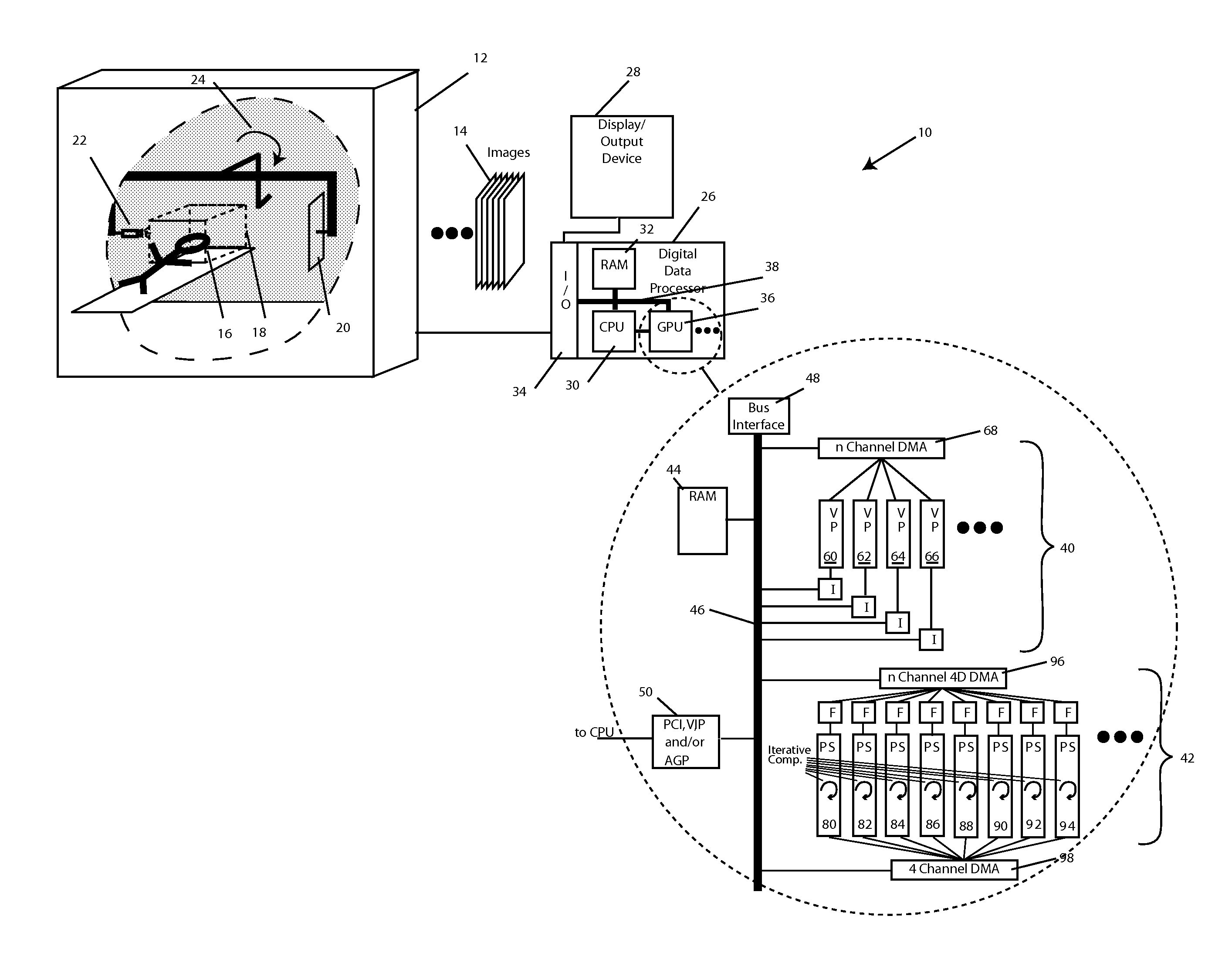

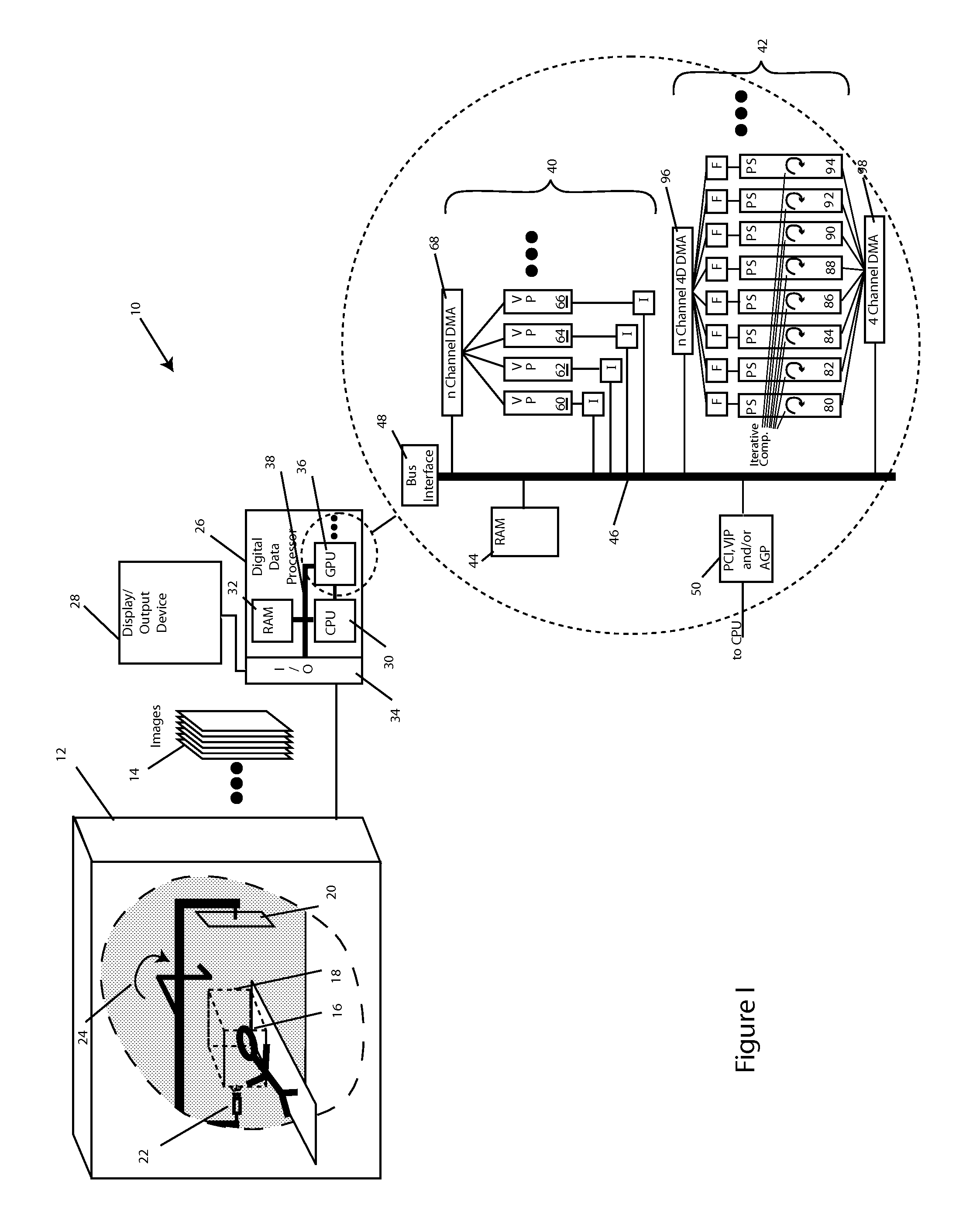

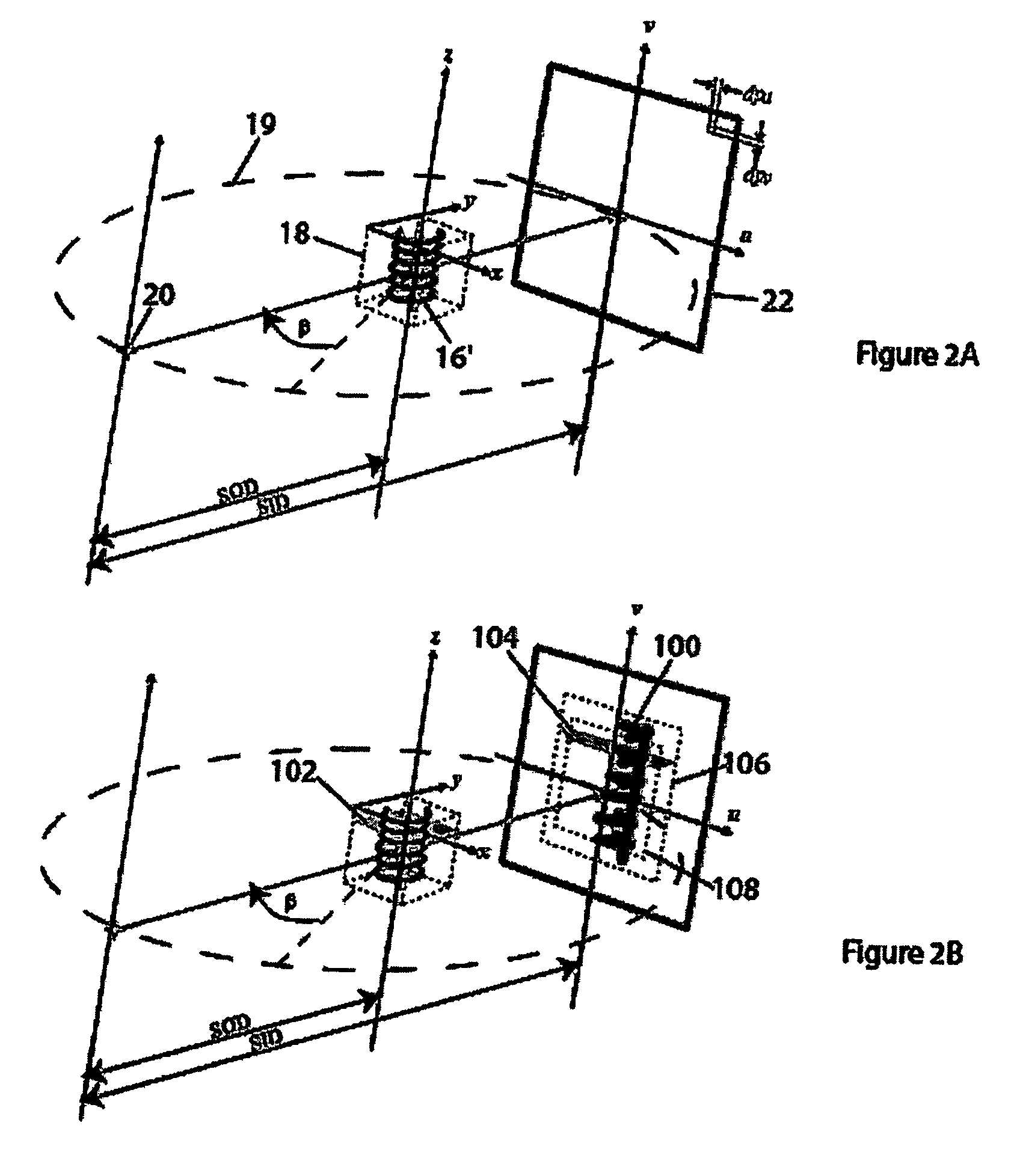

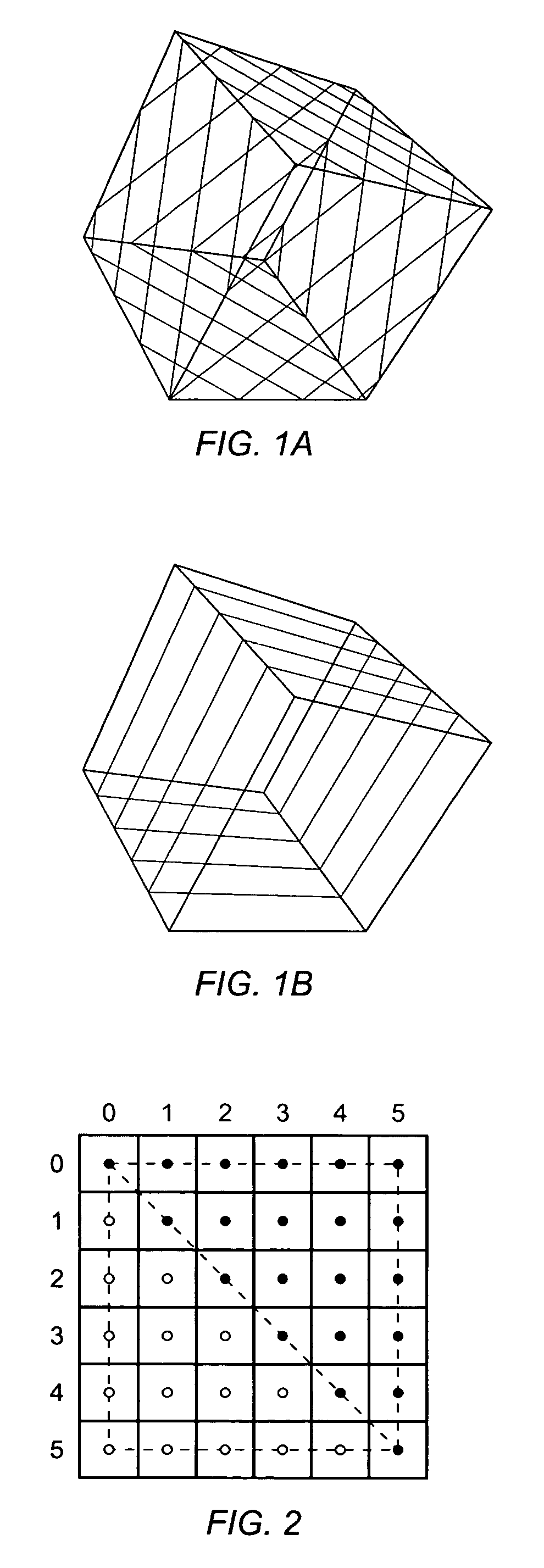

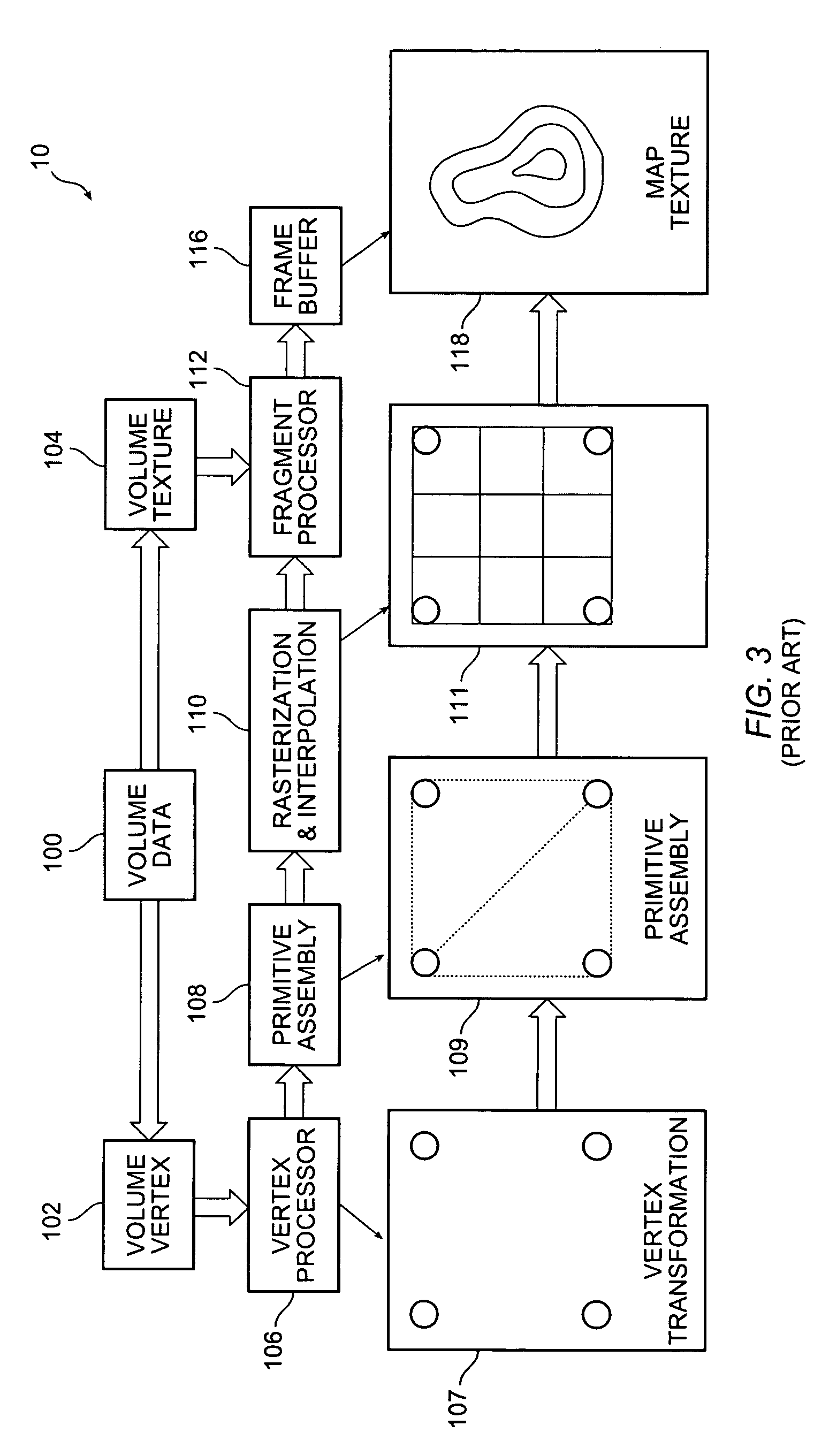

Method and apparatus for visualizing three-dimensional and higher-dimensional image data sets

ActiveUS8189002B1Improve performanceQuality improvementProcessor architectures/configurationImage generationDigital dataData set

In one aspect, the invention provides improvements in a digital data processor of the type that renders a three-dimensional (3D) volume image data into a two-dimensional (2D) image suitable for display. The improvements include a graphics processing unit (GPU) that comprises a plurality of programmable vertex shaders that are coupled to a plurality of programmable pixel shaders, where one or more of the vertex and pixel shaders are adapted to determine intensities of a plurality of pixels in the 2D image as an iterative function of intensities of sample points in the 3D image through which a plurality viewing rays associated with those pixels are passed. The pixel shaders compute, for each ray, multiple iteration steps of the iterative function prior to computing respective steps for a subsequent ray.

Owner:PME IP

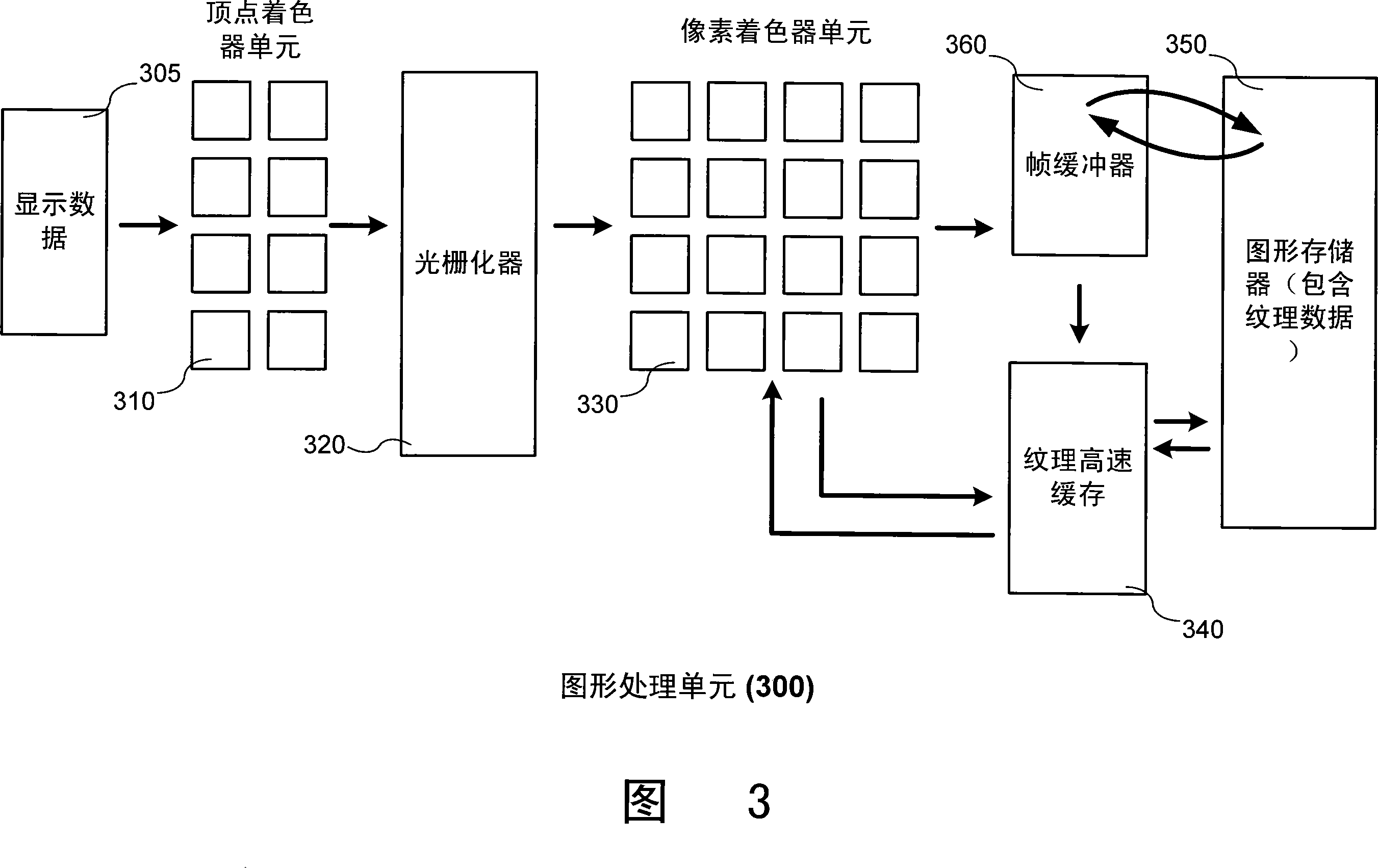

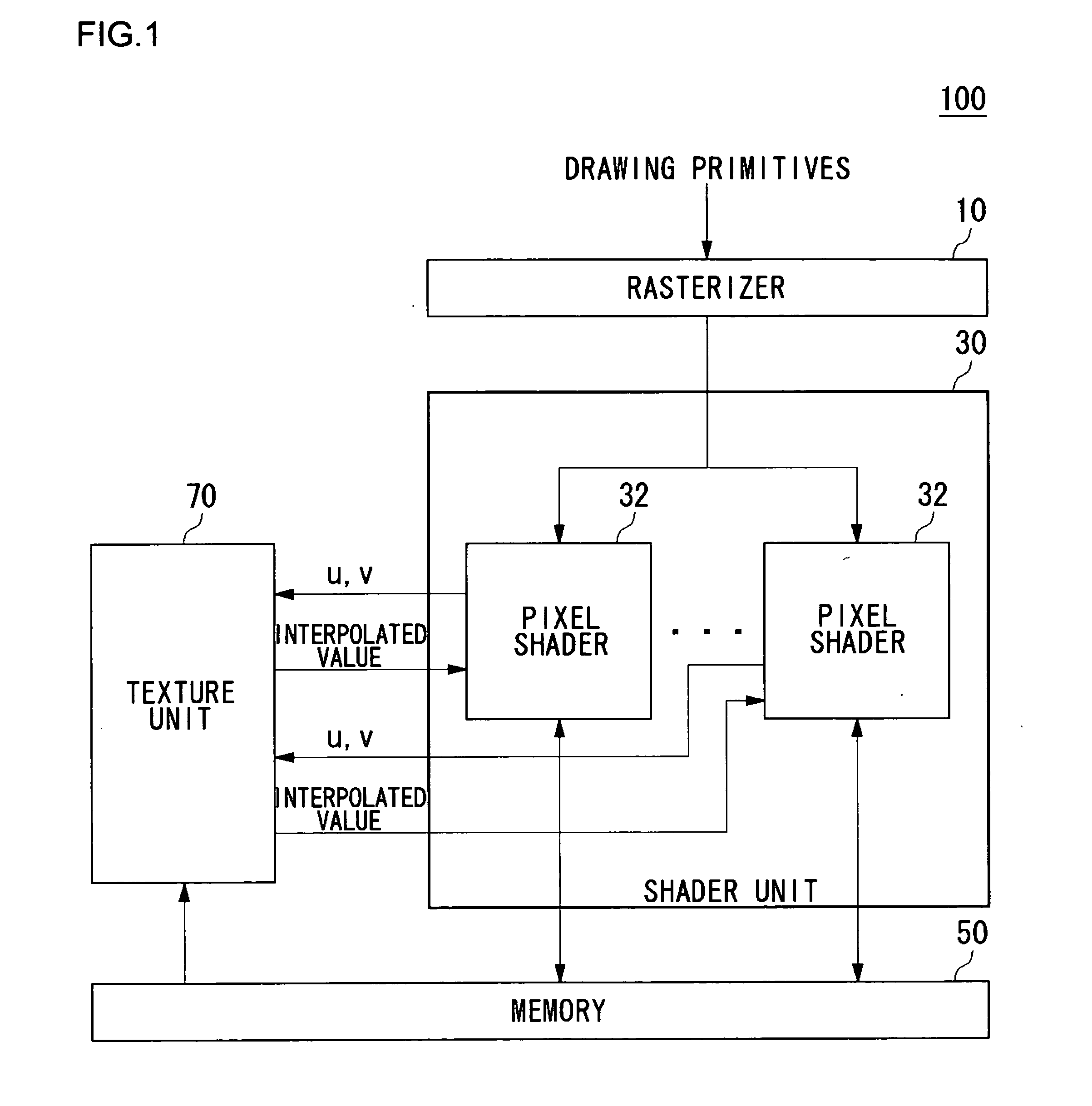

Image Processing with Highly Threaded Texture Fragment Generation

ActiveUS20090231348A1Minimizing any bottleneckImprove hardware utilizationCharacter and pattern recognitionCathode-ray tube indicatorsImaging processingComputer graphics (images)

A circuit arrangement and method support a multithreaded rendering architecture capable of dynamically routing pixel fragments from a pixel fragment generator to any pixel shader from among a pool of pixel shaders. The pixel fragment generator is therefore not tied to a specific pixel shader, but is instead able to utilize multiple pixel shaders in a pool of pixel shaders to minimize bottlenecks and improve overall hardware utilization and performance during image processing.

Owner:RAKUTEN GRP INC

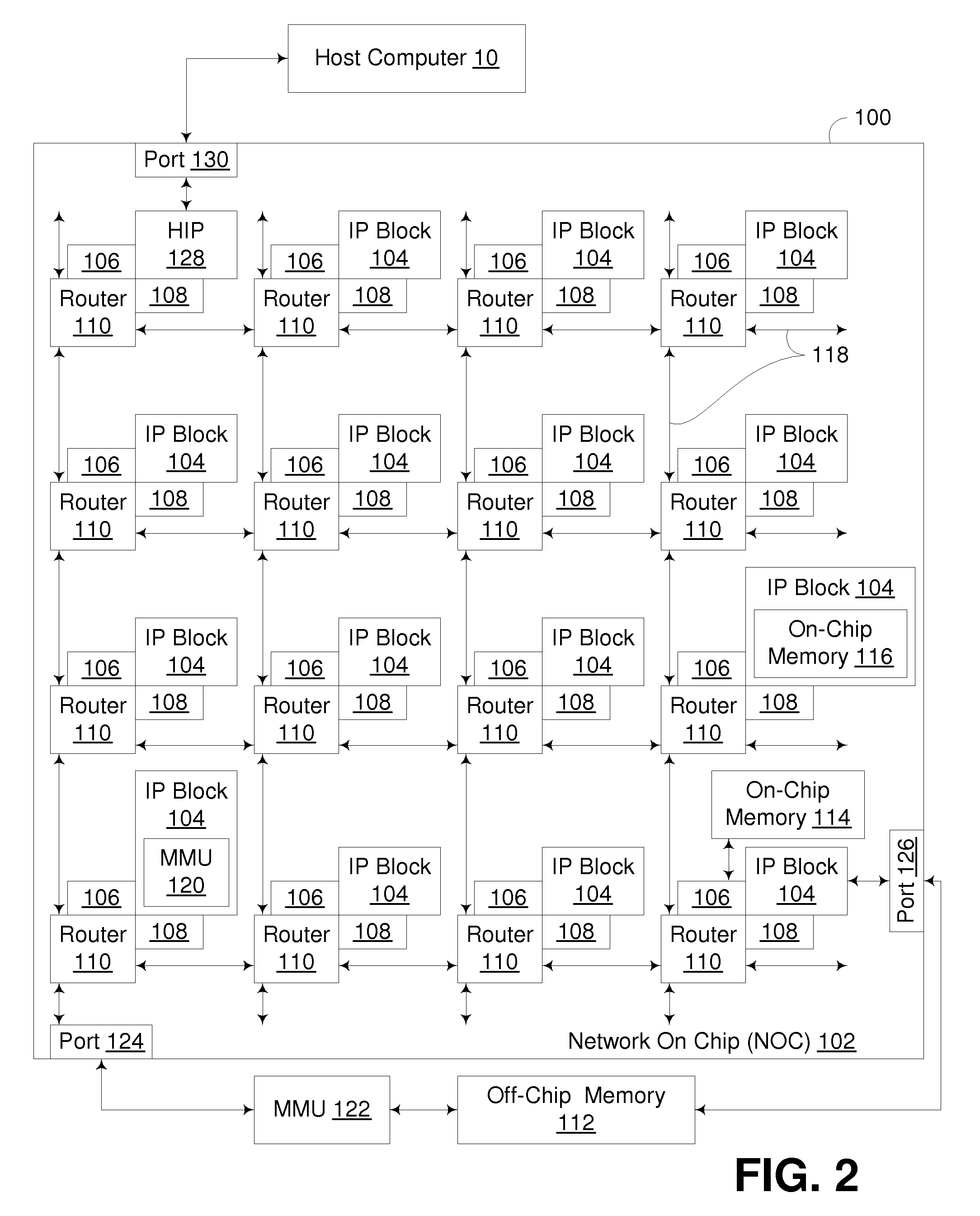

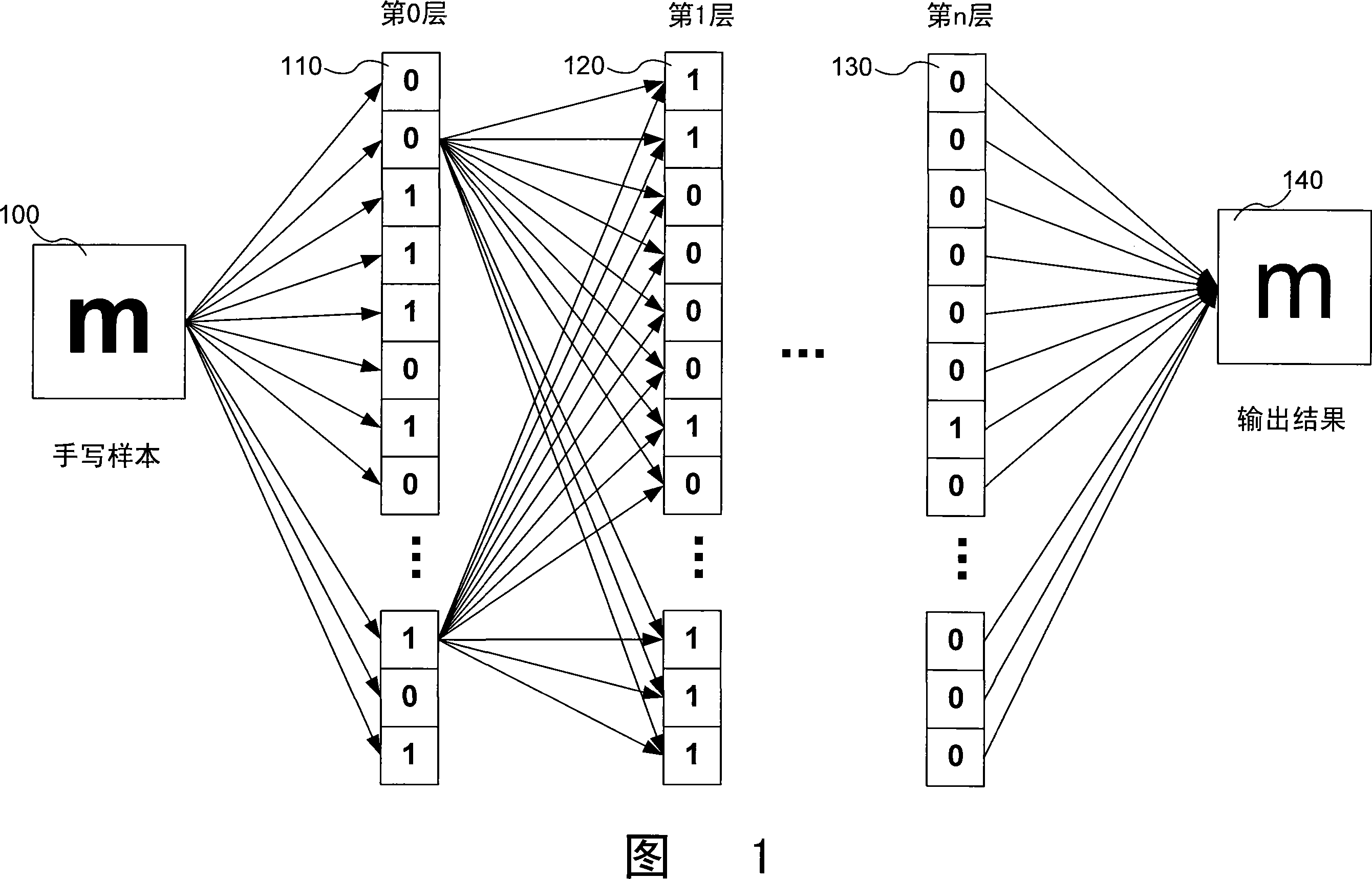

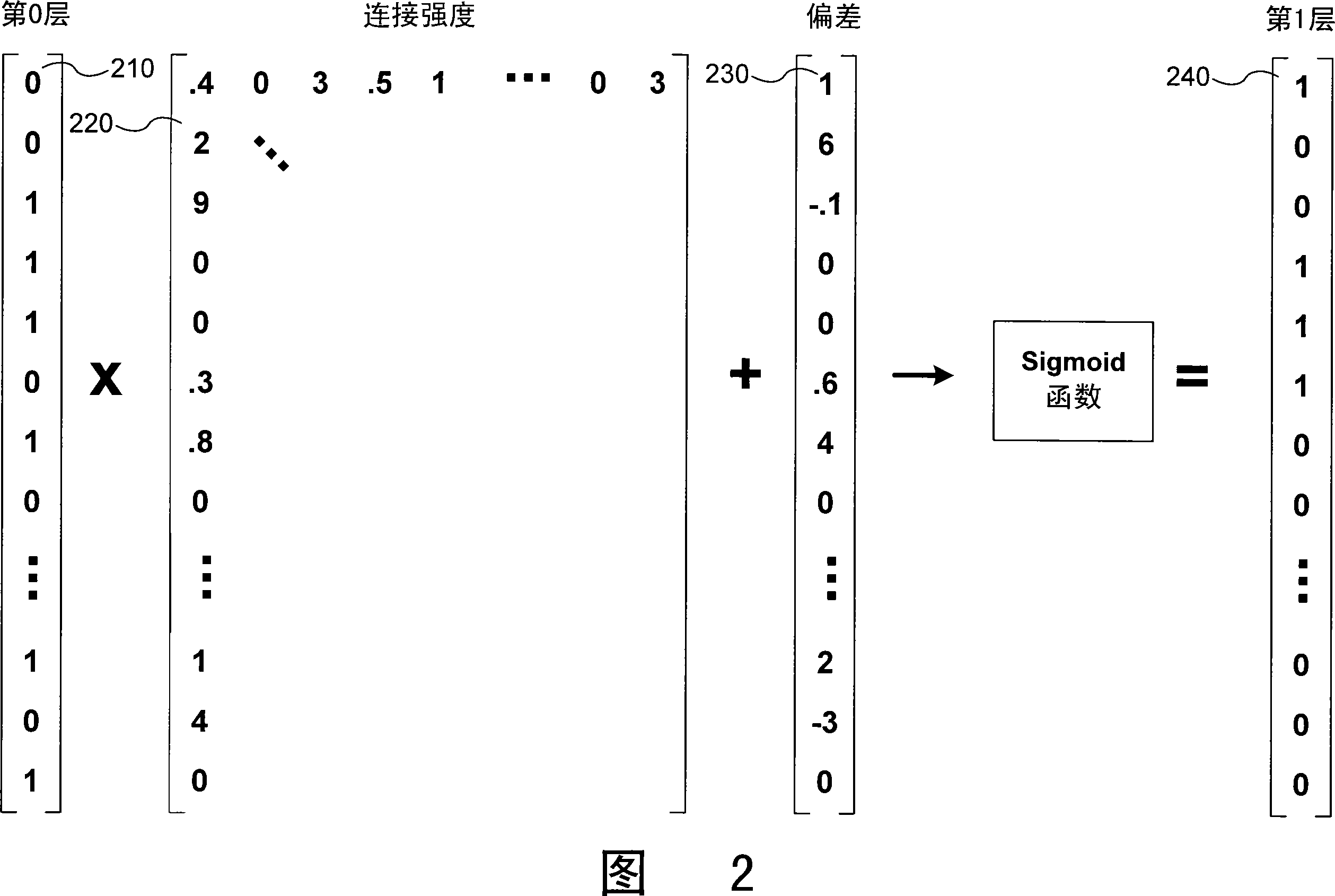

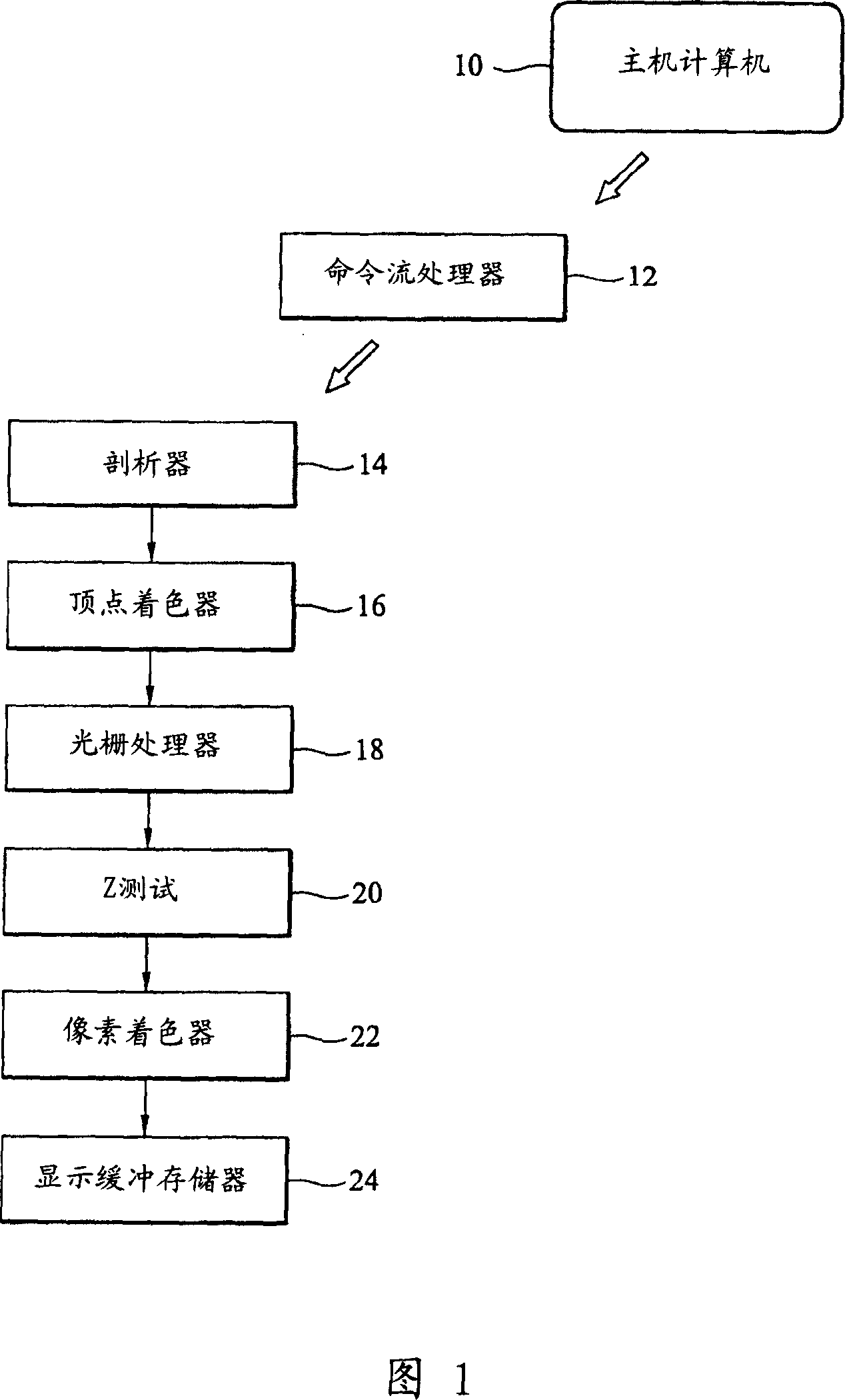

Training convolutional neural networks on graphics processing units

InactiveCN101253493ADigital computer detailsImage data processing detailsComputational scienceError function

A convolutional neural network is implemented on a graphics processing unit. The network is then trained through a series of forward and backward passes, with convolutional kernels and bias matrices modified on each backward pass according to a gradient of an error function. The implementation takes advantage of parallel processing capabilities of pixel shader units on a GPU, and utilizes a set of start-to-finish formulas to program the computations on the pixel shaders. Input and output to the program is done through textures, and a multi-pass summation process is used when sums are needed across pixel shader unit registers.

Owner:MICROSOFT TECH LICENSING LLC

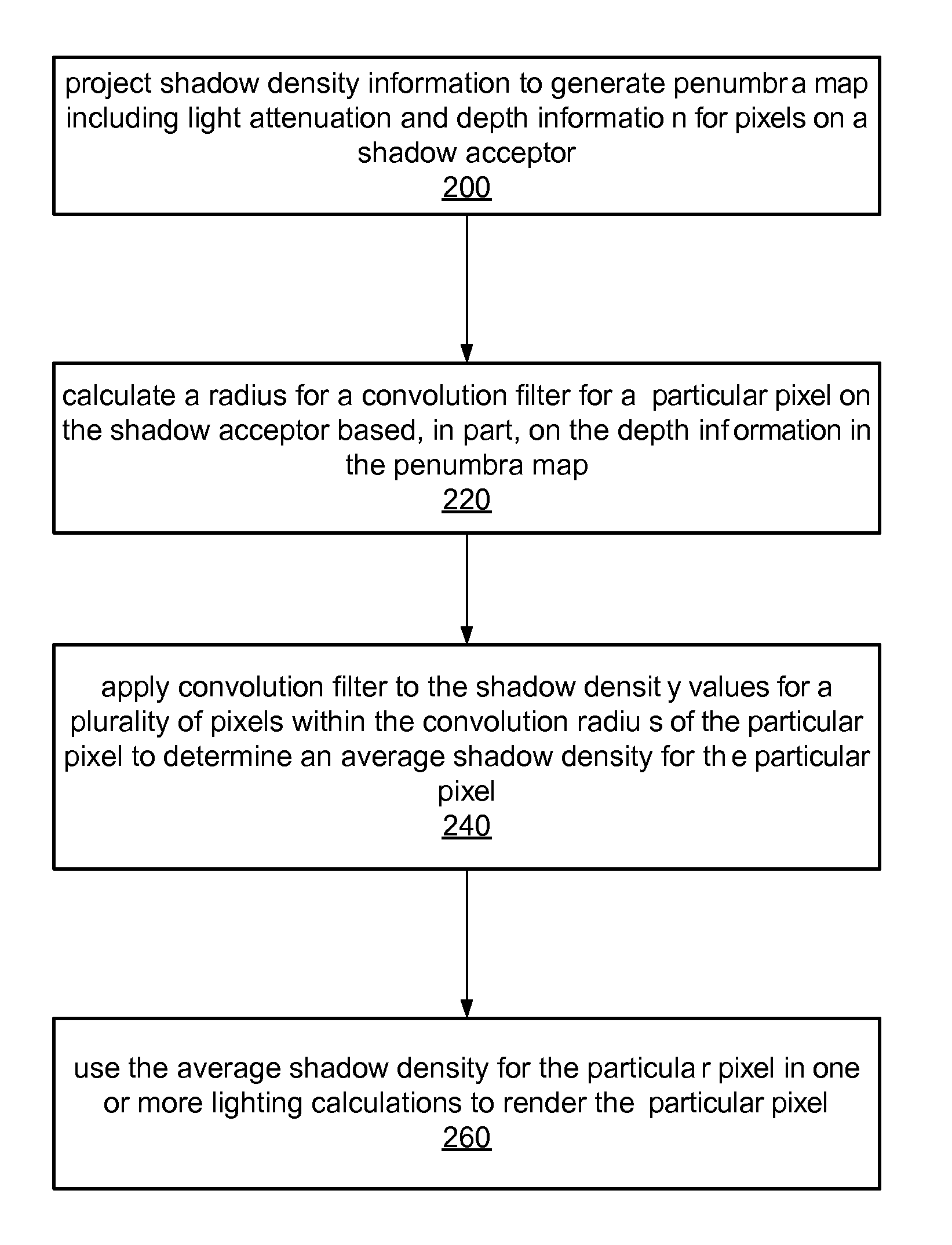

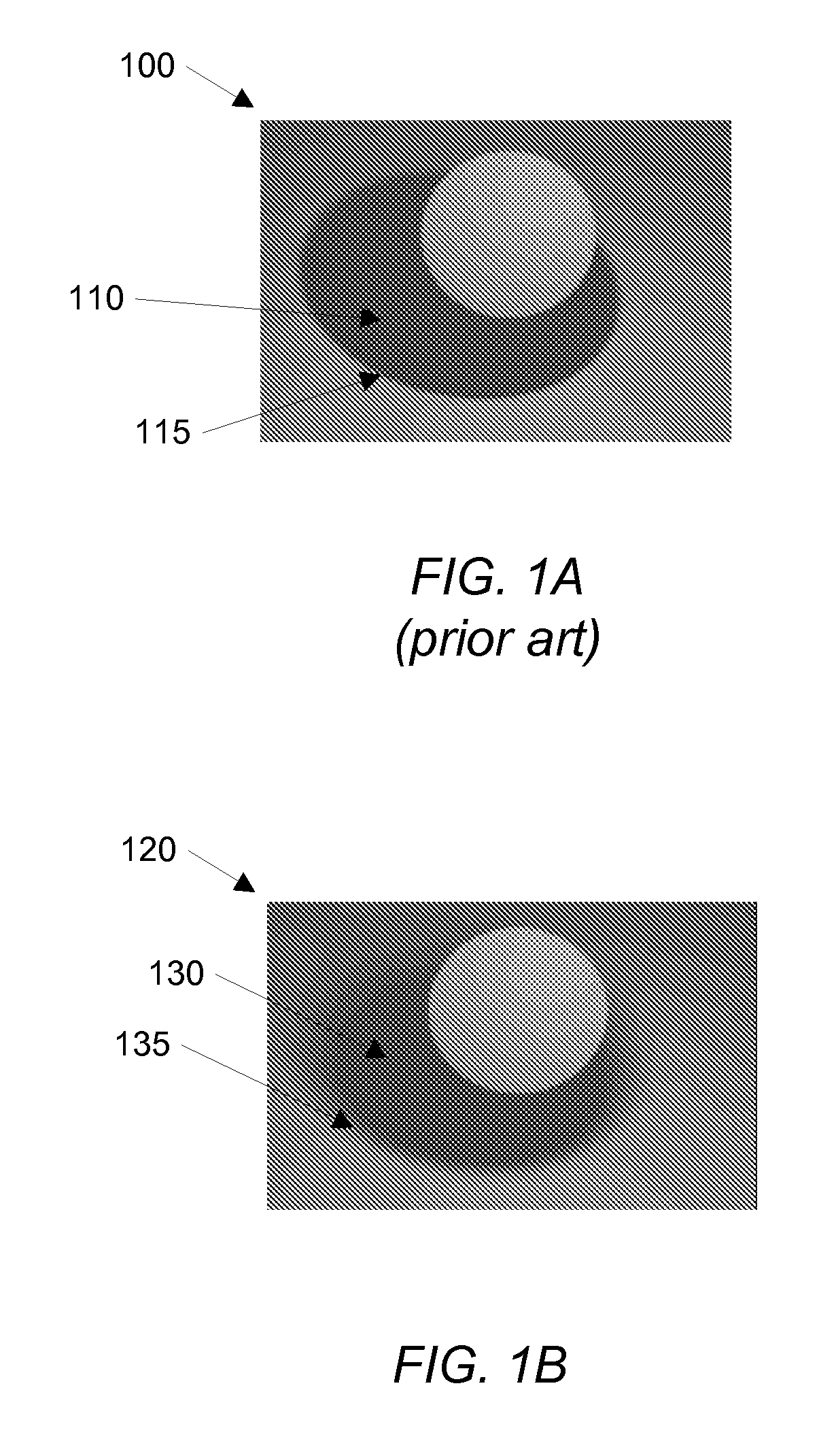

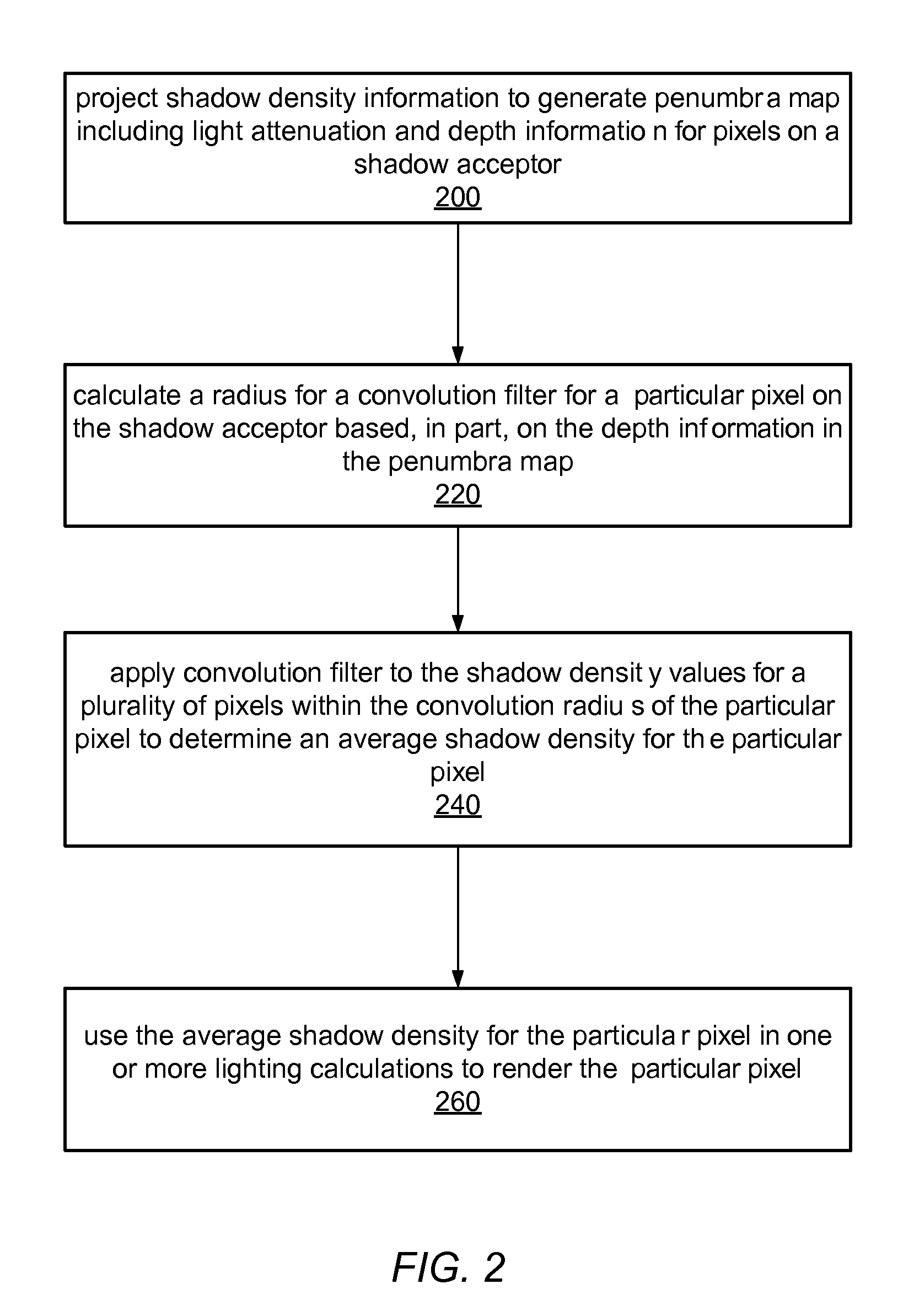

Calculating shadow from area light sources using a spatially varying blur radius

ActiveUS7817823B1Reduce the amount requiredCharacter and pattern recognition3D-image renderingComputer graphics (images)Caster

Shadows from physical lights have a penumbra region, in which the light is only partially hidden from the shadow acceptor. The intensity of light in this region may be calculated using an approximation of the amount of light visible. For example a fragment or pixel shader program execution on a GPU may generate a shadow from a light source using the light intensities for each pixel being rendered. Per-pixel shadow density information may be projected from the shadow caster onto the shadow acceptor. A penumbra map may contain both depth information and light attenuation information for the shadow acceptor. This information may be blurred using a fragment or pixel shader on a GPU to determine an average shadow density for a pixel being rendered.

Owner:ADOBE INC

Block-based fragment filtration with feasible multi-GPU acceleration for real-time volume rendering on conventional personal computer

ActiveUS7154500B2Reduce the burden onDetails involving 3D image dataCathode-ray tube indicatorsVoxelFiltration

A computer-based method and system for interactive volume rendering of a large volume data on a conventional personal computer using hardware-accelerated block filtration optimizing uses 3D-textured axis-aligned slices and block filtration. Fragment processing in a rendering pipeline is lessened by passing fragments to various processors selectively in blocks of voxels based on a filtering process operative on slices. The process involves generating a corresponding image texture and performing two-pass rendering, namely a virtual rendering pass and a main rendering pass. Block filtration is divided into static block filtration and dynamic block filtration. The static block filtration locates any view-independent unused signal being passed to a rasterization pipeline. The dynamic block filtration determines any view-dependent unused block generated due to occlusion. Block filtration processes utilize the vertex shader and pixel shader of a GPU in conventional personal computer graphics hardware. The method is for multi-thread, multi-GPU operation.

Owner:THE CHINESE UNIVERSITY OF HONG KONG

Image processing with highly threaded texture fragment generation

ActiveUS7973804B2Minimizing any bottleneckImprove performanceCharacter and pattern recognitionCathode-ray tube indicatorsImaging processingComputer graphics (images)

A circuit arrangement and method support a multithreaded rendering architecture capable of dynamically routing pixel fragments from a pixel fragment generator to any pixel shader from among a pool of pixel shaders. The pixel fragment generator is therefore not tied to a specific pixel shader, but is instead able to utilize multiple pixel shaders in a pool of pixel shaders to minimize bottlenecks and improve overall hardware utilization and performance during image processing.

Owner:RAKUTEN GRP INC

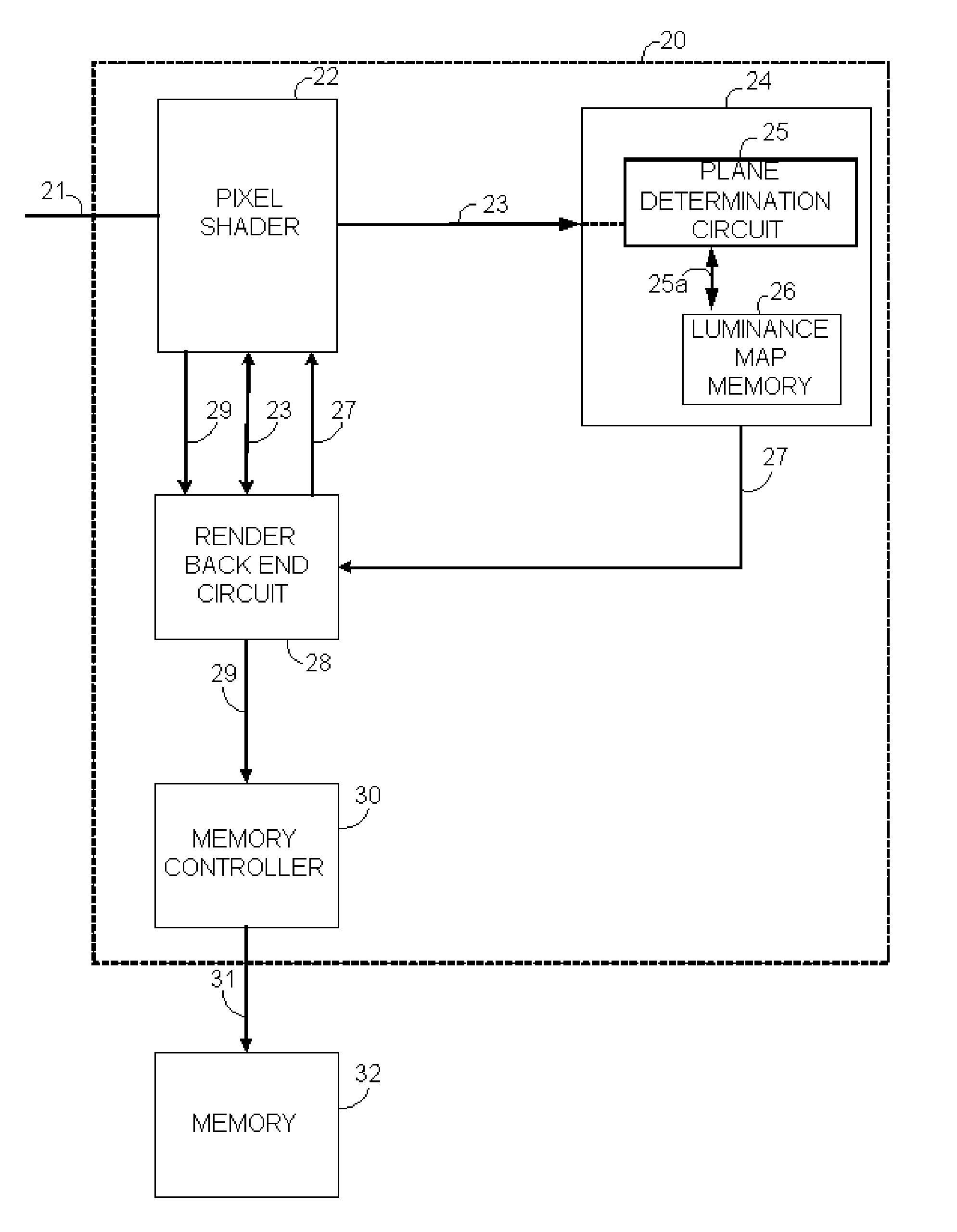

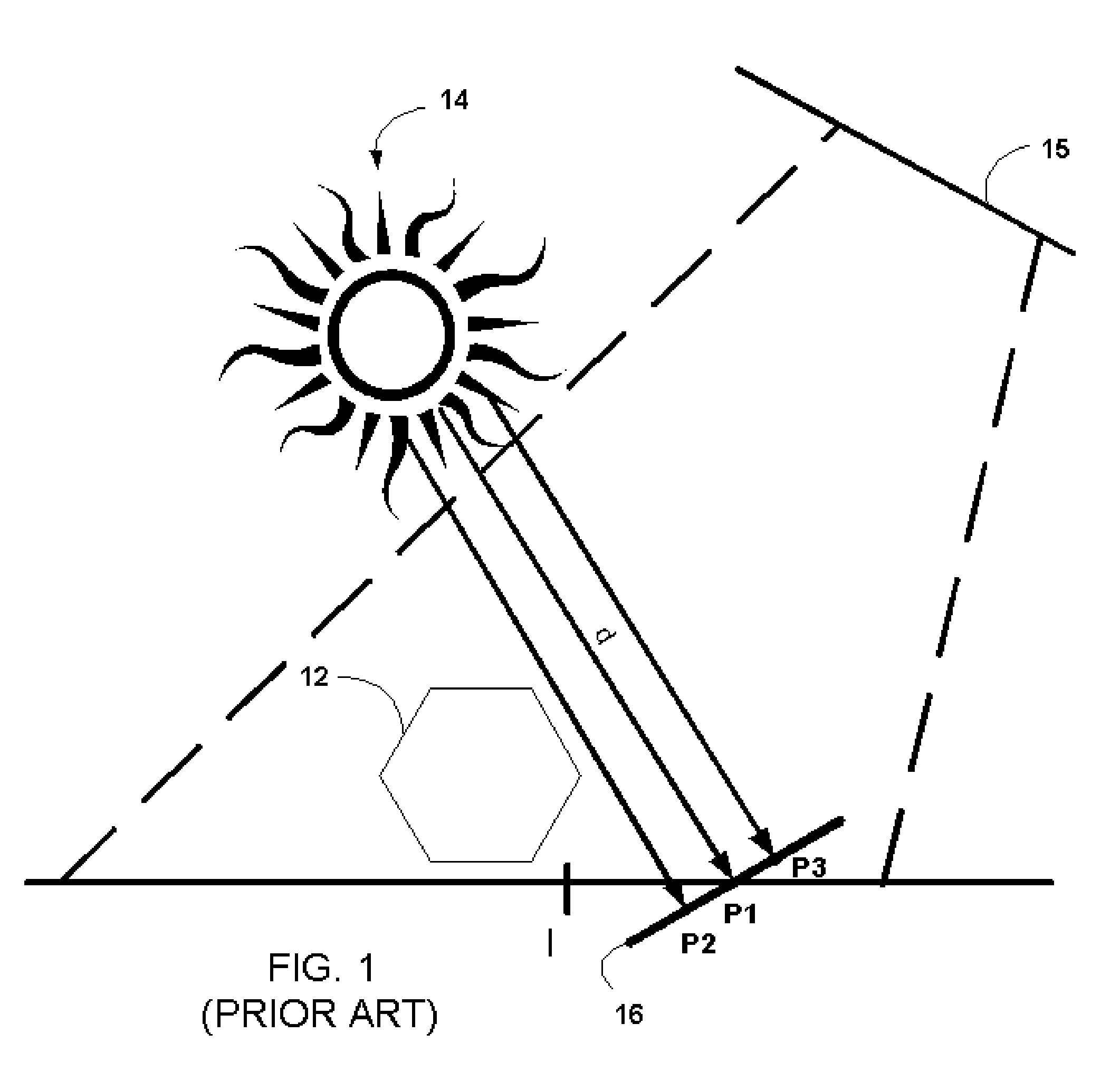

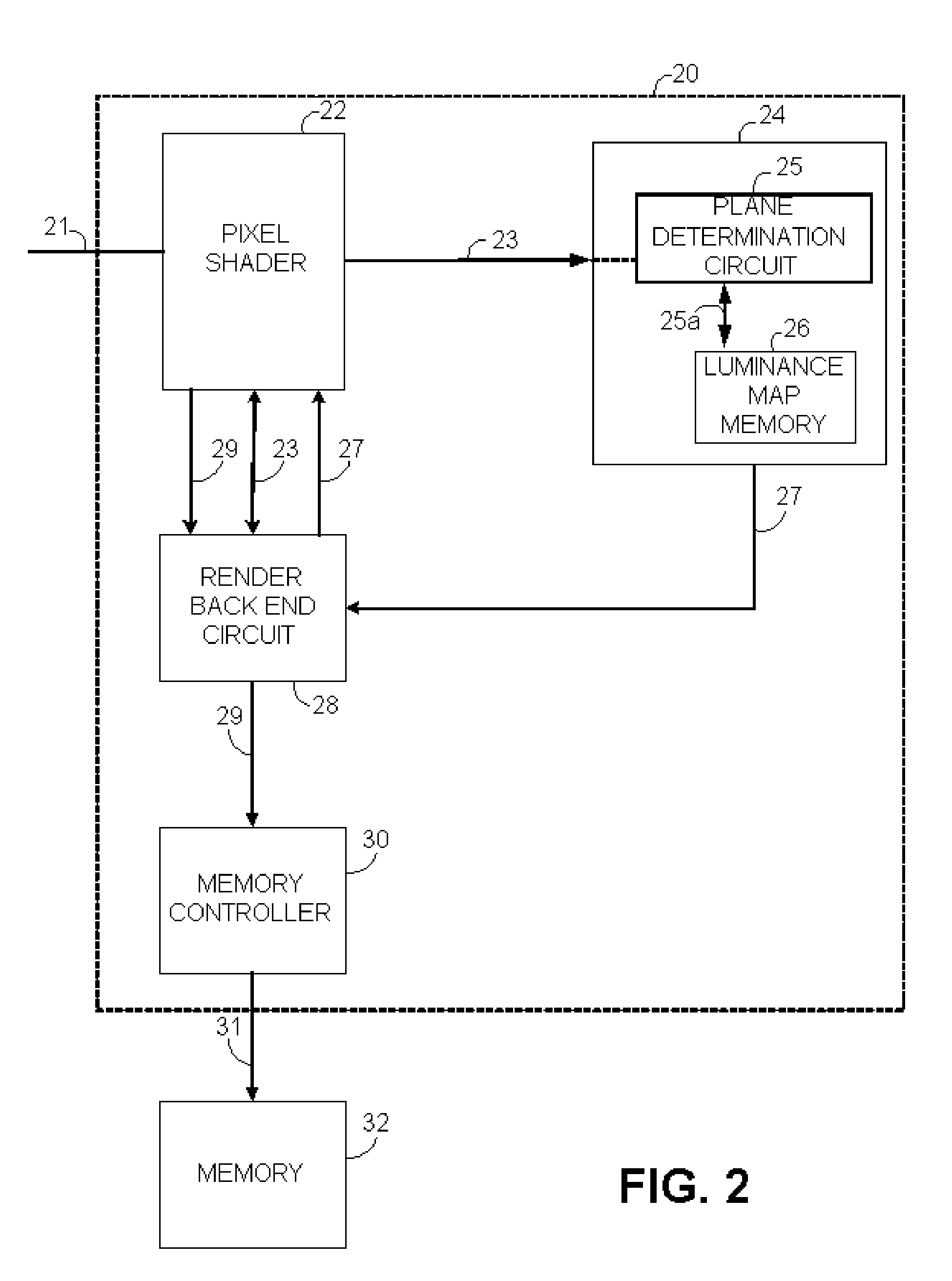

System and method for determining illumination of a pixel by shadow planes

A graphics processing circuit includes a pixel shader operative to provide pixel color information in response to image data representing a scene to be rendered; a texture circuit, coupled to the pixel shader, operative to determine a luminance value to be applied to a pixel of interest based on the luminance values of the pixels that define a plane including the pixel of interest; and a render back end circuit, coupled to the texture circuit, operative to compute the luminance values from a shadow map that specifies the distance from the light source of the nearest object at a plurality of locations. A pixel illumination method includes receiving color information for a pixel to be rendered, defining a plane containing at least one pixel of interest, the plane including a plurality of planar values; comparing the plurality of planar values to a corresponding set of distance values; determining a luminance value for the at least one pixel of interest; and applying the luminance value to the at least one pixel of interest.

Owner:ATI TECH INC

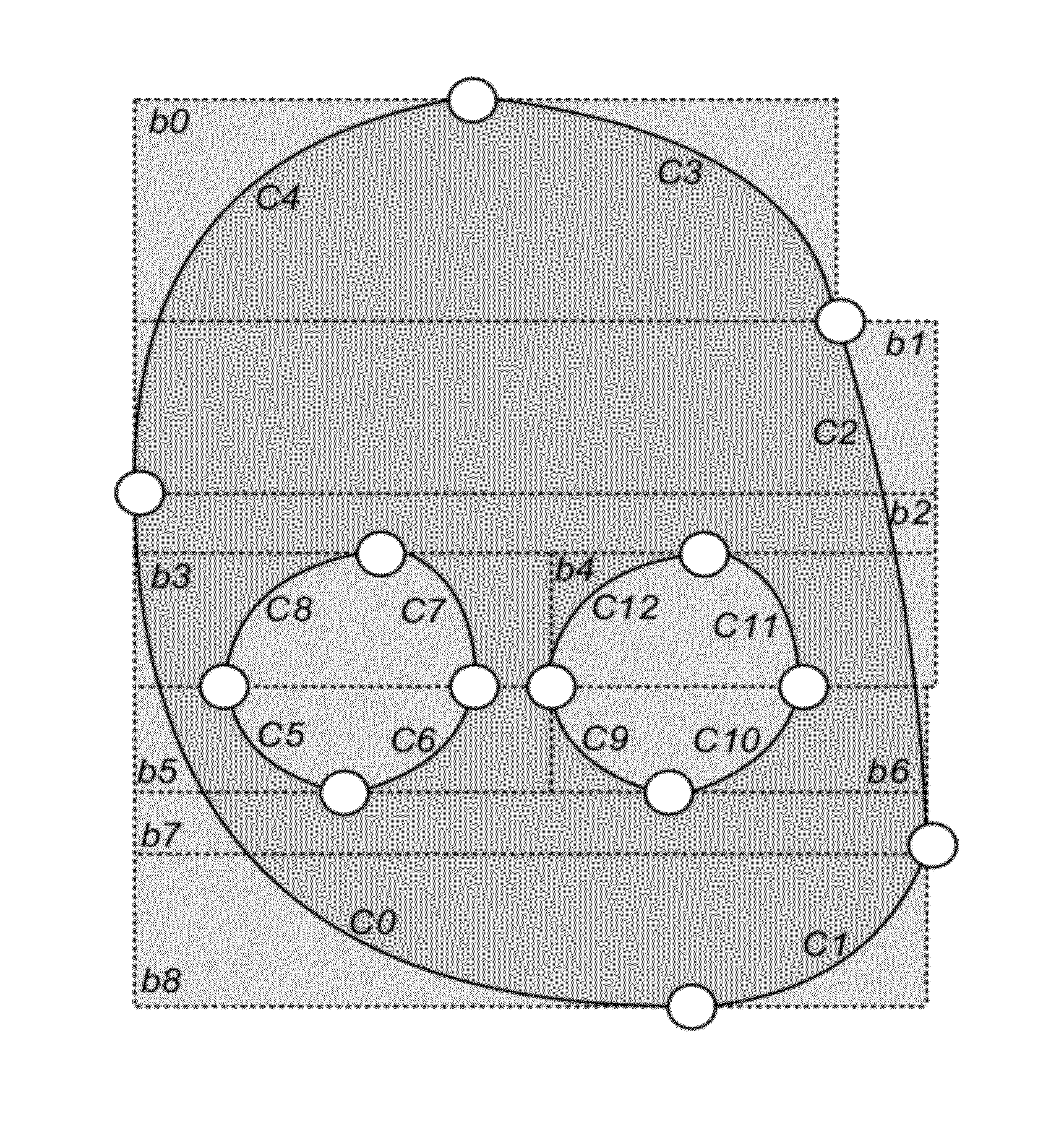

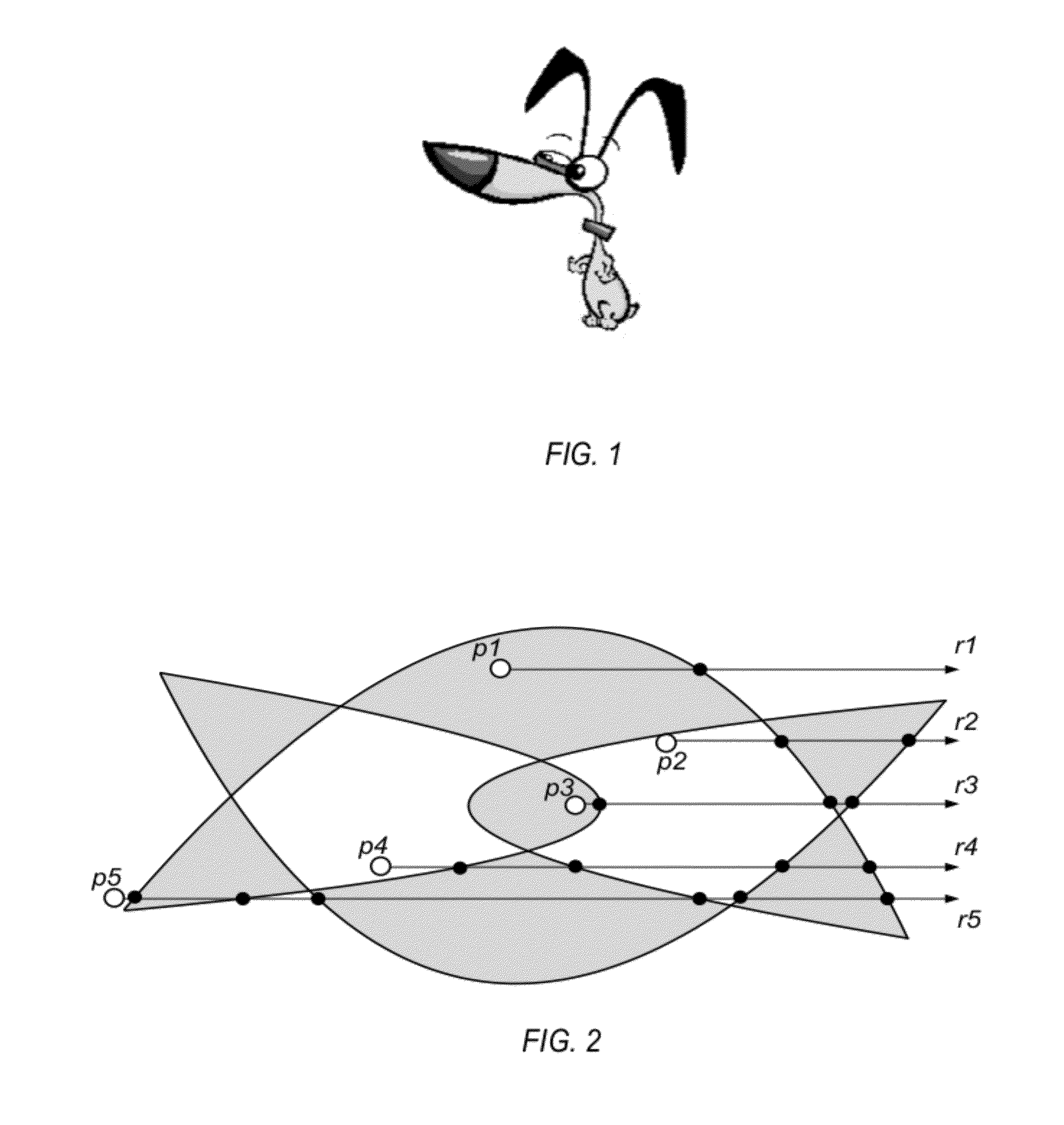

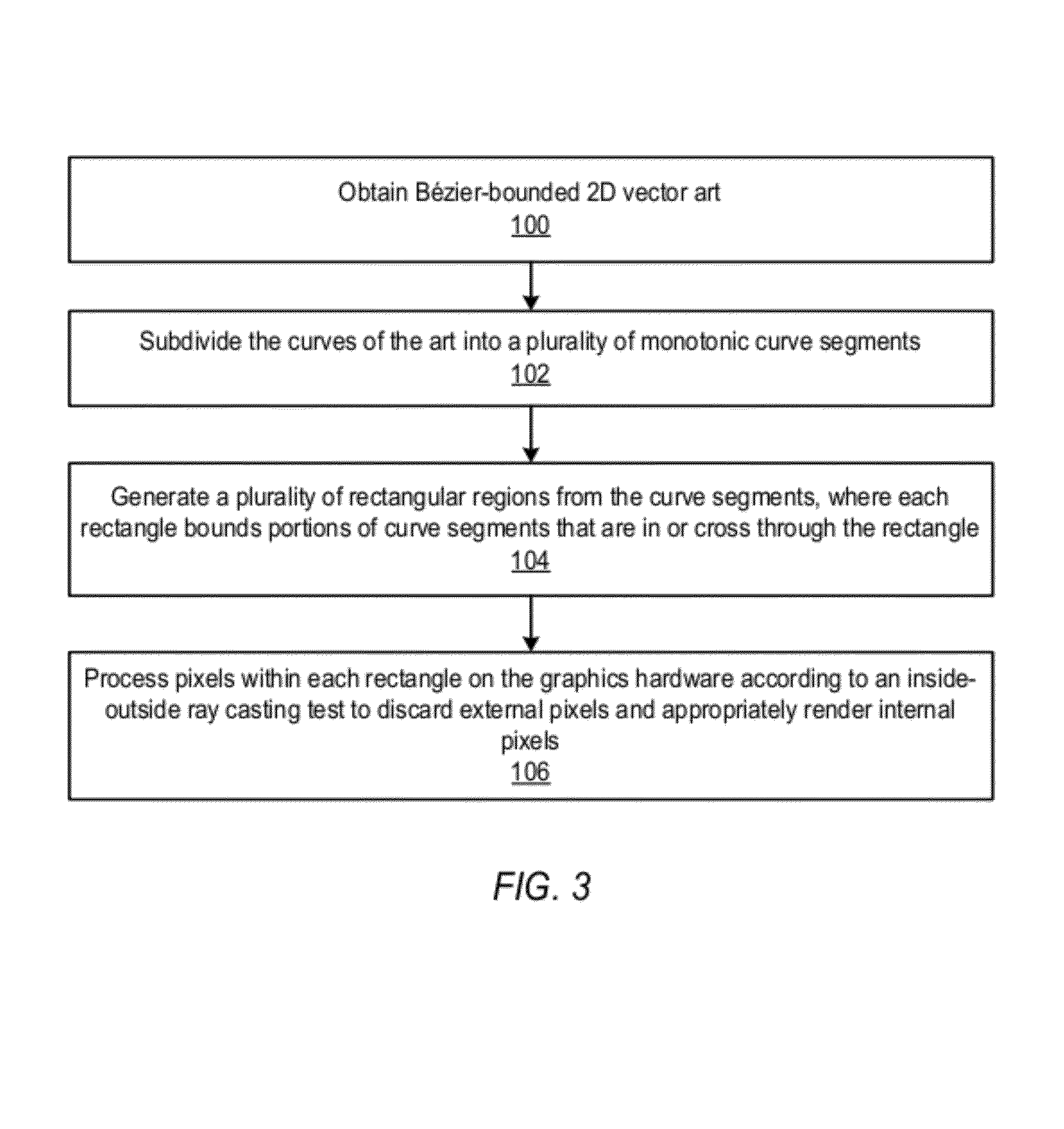

Methods and apparatus for rendering vector art on graphics hardware

ActiveUS8379025B1Reduce CPU overheadEfficiently render quadratic2D-image generation3D-image renderingComputational scienceAnimation

Methods and apparatus for ray-casting 2D animated vector art on graphics hardware. Embodiments maintain curves in their analytic form when transmitted to the GPU. On the CPU, the curves in the vector art may be subdivided into a plurality of monotonic curve segments. A plurality of intervals may be generated from the curve segments. Further subdivision may be applied on the CPU to any interval that includes more than n curves, where n is the maximum number of curves that can be processed in parallel in the pixel shader. On the GPU, the pixels are evaluated to determine whether each pixel is inside or outside of the curve network. The technique used in the GPU may be based on a point-in-polygon algorithm that casts rays from points under test and counts the number of curve crossings before the rays exit the shape using a modified implicit formula.

Owner:ADOBE SYST INC

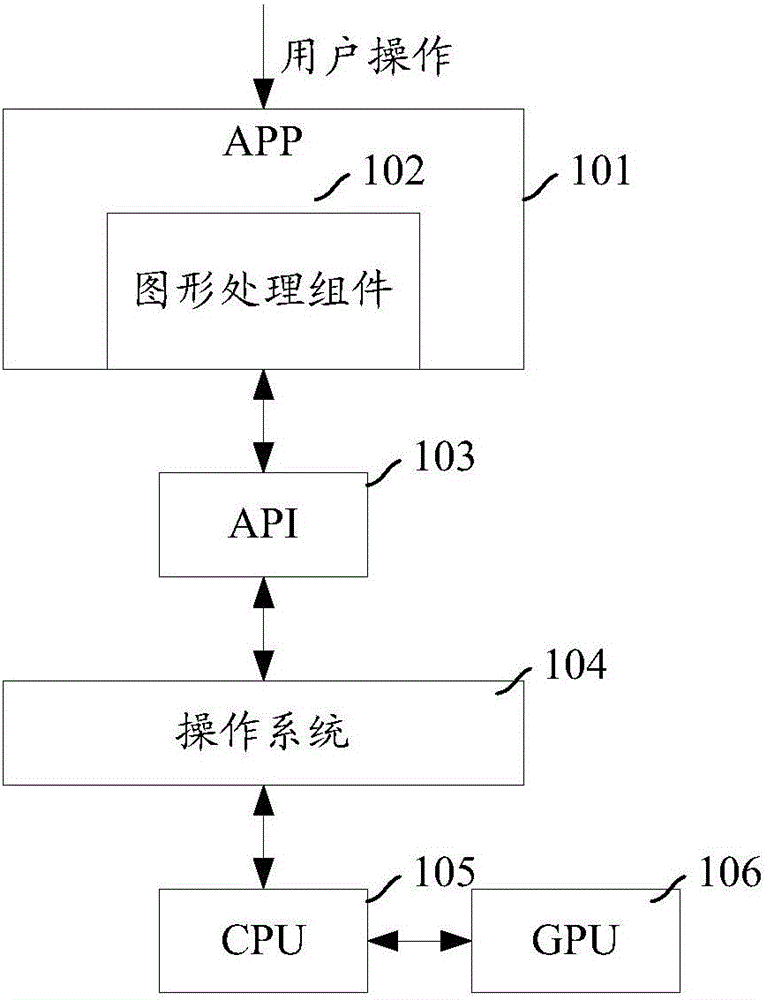

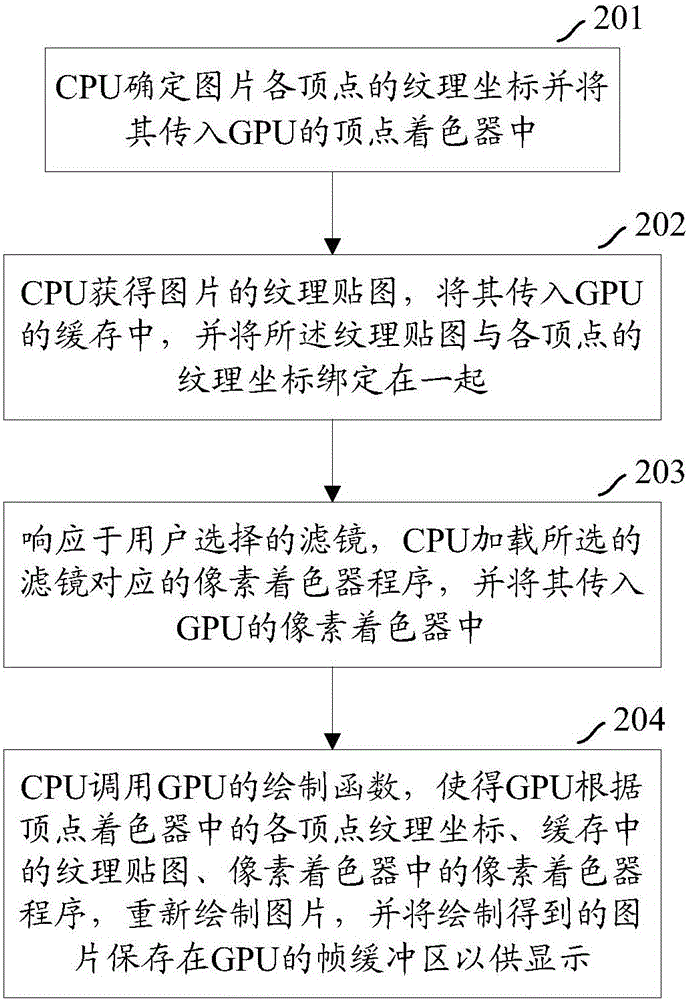

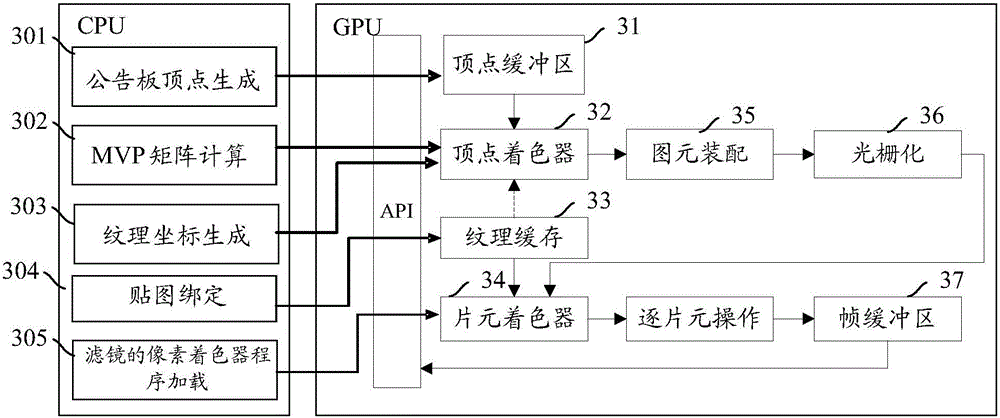

Graph processing method and device

ActiveCN105741228AImprove filter processing efficiencyImprove concurrencyProcessor architectures/configurationPixel shaders

The invention discloses a graph processing method for the graph processing assembly. The invention provides a shader program set comprising a plurality of pixel tinter programs, wherein each pixel tinter program correspond to one filter. The graph processing method comprises steps of determining a texture coordinate of each vertex of the image through the CPU and transmitting the texture coordinator to the vertex tinter of the GPU, obtaining the texture chartlet of the image through the CPU, transmitting the texture chartlet into the buffer memory of the GPU, binding the texture charplet with the texture coordinate of the vertex, responding to the filter chosen by the user, loading the corresponding pixel tinter program through the CPU, transmitting the pixel tinter program to the pixel tinter of the GPU, invoking the drawing function of the GPU through the CPU, enabling the GPU to draw the image according to the texture coordinate, the texture charplet and the pixel tinter program of each vertex and storing the image in the frame buffering zone. The invention also discloses a corresponding device. The graph processing method and device can improve the filter processing efficiency.

Owner:TENCENT TECH (SHENZHEN) CO LTD

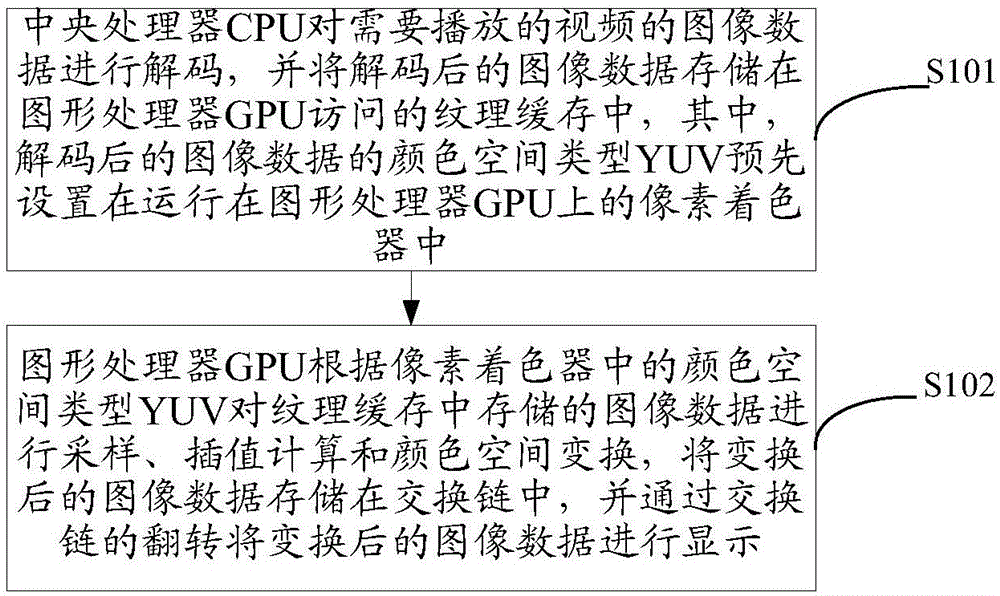

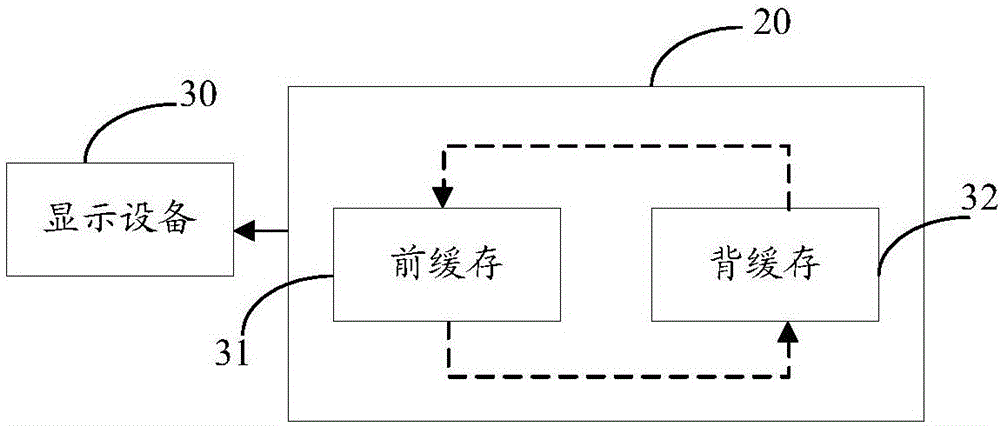

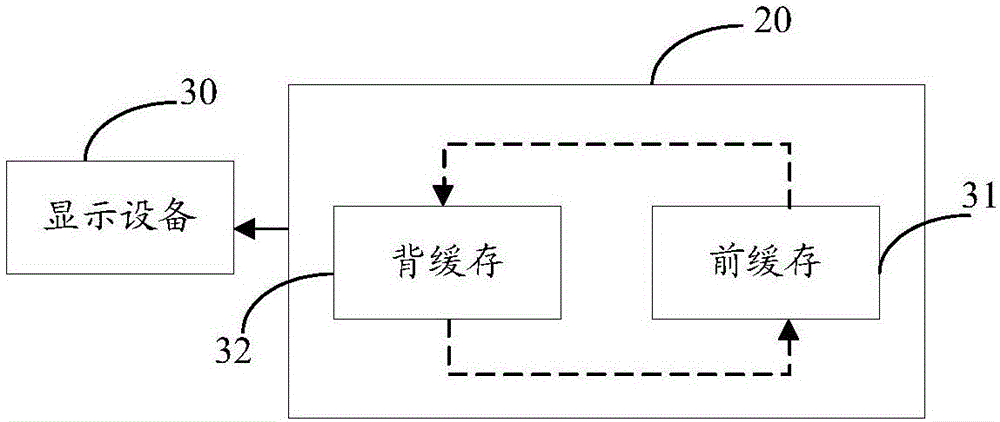

Video rendering method and device

InactiveCN106210883AReduce lossColor signal processing circuitsSelective content distributionCache accessGraphics processing unit

The present invention discloses a video rendering method and device, which aim to lower central processing unit (CPU) performance loss in video rendering. The video rendering method comprises the steps that the CPU decodes image data of a to-be-played video, and stores the decoded image data in a pattern cache accessed by a graphics processing unit (GPU), wherein a color space type YUV of the decoded image data is preset in a pixel shader running on the GPU; and the GPU performs sampling, interpolation calculation and color space conversion on the image data stored in the pattern cache according to the color space type YUV in the pixel shader, and stores the converted image data in an exchange chain, and the converted image data is displayed through overturn of the exchange chain.

Owner:ZHEJIANG DAHUA TECH CO LTD

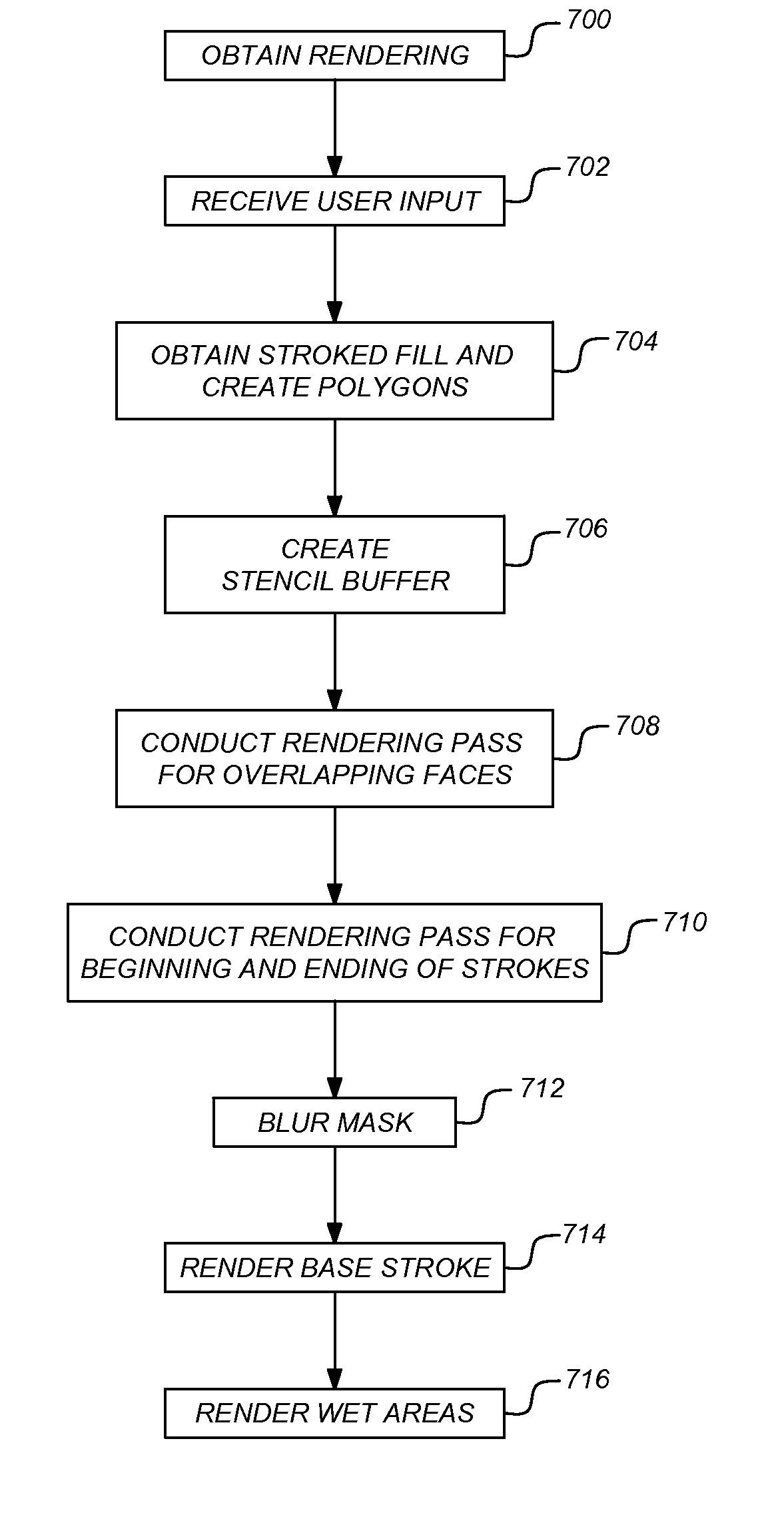

Vector marker strokes

ActiveUS20080018650A1Quickly and efficientlyDrawing from basic elementsFilling planer surface with attributesUser inputComputer graphics (images)

An apparatus, method, and article of manufacture are configured to display a vector marker stroke. A stroked fill of vector splines and polygons having faces along the spline are created based on a user input marker stroke. A stencil buffer is created indicating the number of vector faces incident at each pixel. When the number indicates that a pixel has overlapping faces, a pixel shader (that determines an opacity value for the pixel in a mask) is executed as many times as the number. When the number indicates that a pixel has at least one face and is at a beginning or an ending of the stroke, the shader is executed to add to the opacity value. A blur shading operation is executed on each of the pixels. The stroked fill is rendered and a wet color is rendered, using the mask, on top of the stroked fill.

Owner:AUTODESK INC

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding techniques

ActiveUS20050122332A1Increased programming flexibilityImprove abilitiesDigital computer detailsNext instruction address formationComputational scienceCoprocessor

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding processing and communication techniques are provided. For an improved graphics pipeline, the invention provides a class of co-processing device, such as a graphics processor unit (GPU), providing improved capabilities for an abstract or virtual machine for performing graphics calculations and rendering. The invention allows for runtime-predicated flow control of programs downloaded to coprocessors, enables coprocessors to include indexable arrays of on-chip storage elements that are readable and writable during execution of programs, provides native support for textures and texture maps and corresponding operations in a vertex shader, provides frequency division of vertex streams input to a vertex shader with optional support for a stream modulo value, provides a register storage element on a pixel shader and associated interfaces for storage associated with representing the “face” of a pixel, provides vertex shaders and pixel shaders with more on-chip register storage and the ability to receive larger programs than any existing vertex or pixel shaders and provides 32 bit float number support in both vertex and pixel shaders.

Owner:MICROSOFT TECH LICENSING LLC

Block-based fragment filtration with feasible multi-GPU acceleration for real-time volume rendering on conventional personal computer

A computer-based method and system for interactive volume rendering of a large volume data on a conventional personal computer using hardware-accelerated block filtration optimizing uses 3D-textured axis-aligned slices and block filtration. Fragment processing in a rendering pipeline is lessened by passing fragments to various processors selectively in blocks of voxels based on a filtering process operative on slices. The process involves generating a corresponding image texture and performing two-pass rendering, namely a virtual rendering pass and a main rendering pass. Block filtration is divided into static block filtration and dynamic block filtration. The static block filtration locates any view-independent unused signal being passed to a rasterization pipeline. The dynamic block filtration determines any view-dependent unused block generated due to occlusion. Block filtration processes utilize the vertex shader and pixel shader of a GPU in conventional personal computer graphics hardware. The method is for multi-thread, multi-GPU operation.

Owner:THE CHINESE UNIVERSITY OF HONG KONG

Pixel shader bypass for low power graphics rendering

ActiveUS20140267318A1Processor architectures/configurationFilling planer surface with attributesComputational sciencePixel shaders

A computer-implemented method for drawing graphical objects within a graphics processing pipeline is disclosed. The method includes determining that a bypass mode for a first primitive is a no-bypass mode. The method further includes rasterizing the first primitive to generate a first set of rasterization results. The method further includes generating a first set of colors for the first set of rasterization results via a pixel shader unit. The method further includes rasterizing a second primitive to generate a second set of rasterization results. The method further includes generating a second set of colors for the second set of rasterization results without the pixel shader unit performing any processing operations on the second set of rasterization results. The method further includes transmitting the first set of pixel colors and the second set of pixel colors to a raster operations (ROP) unit for further processing.

Owner:NVIDIA CORP

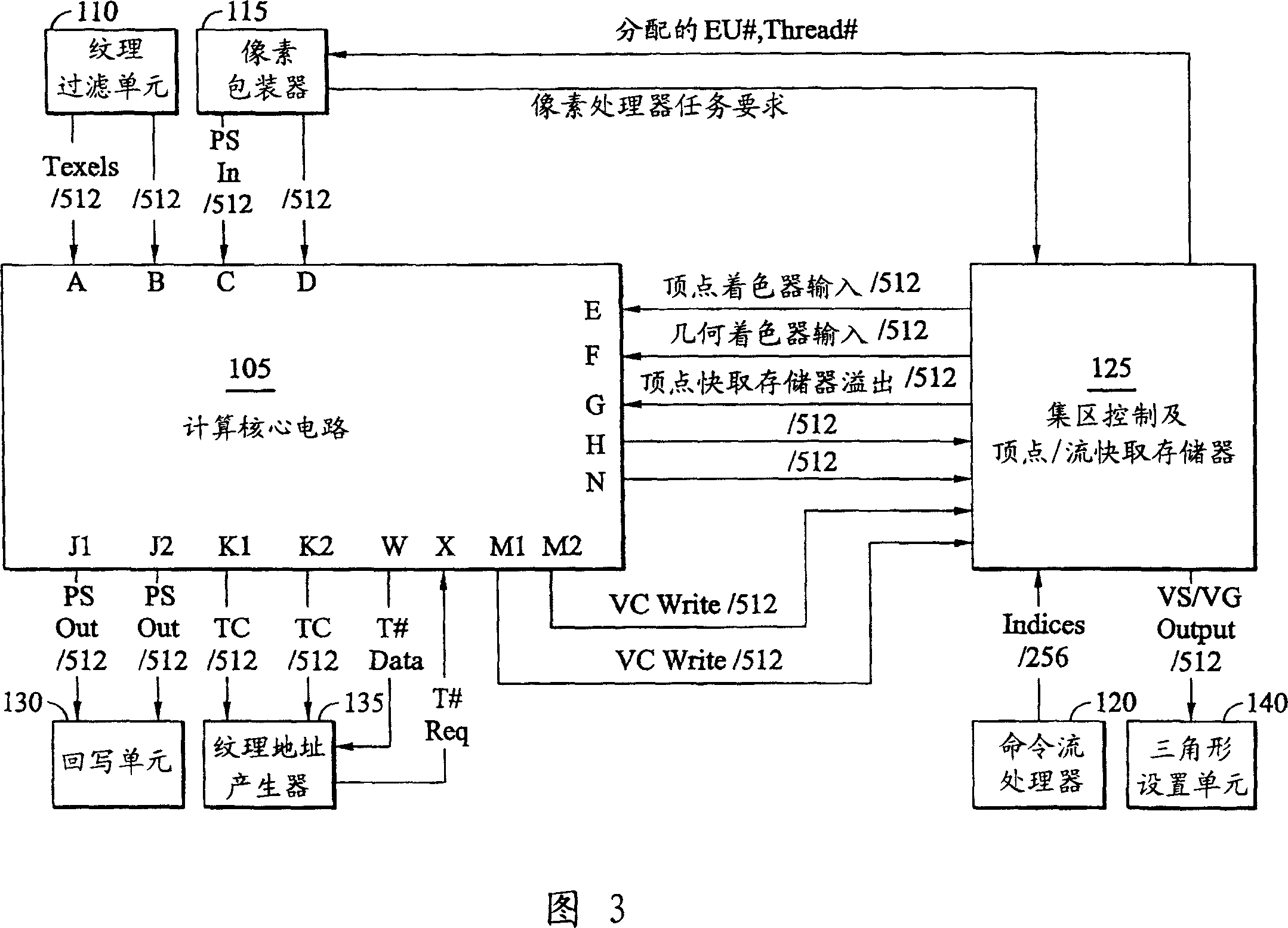

Graphics processing apparatus and method for performing shading operations therein

ActiveCN1928918AProcessor architectures/configuration3D-image renderingComputational scienceExecution unit

The present disclosure is directed to novel methods and apparatus for managing or performing the dynamic allocation or reallocation of processing resources among a vertex shader, a geometry shader, and pixel shader of a graphics processing unit. In one embodiment a method for graphics processing comprises assigning at least one execution unit to each of a plurality of shader units, the plurality of shader units comprising a vertex shader, a geometry shader, and a pixel shader, wherein an execution unit assigned to a given shader unit performs processing tasks for only that shader unit, determining that one of the plurality of shader units is bottlenecked, and reassigning at least one execution unit from a non-bottlenecked shader unit to the shader unit determined to be bottlenecked.

Owner:VIA TECH INC

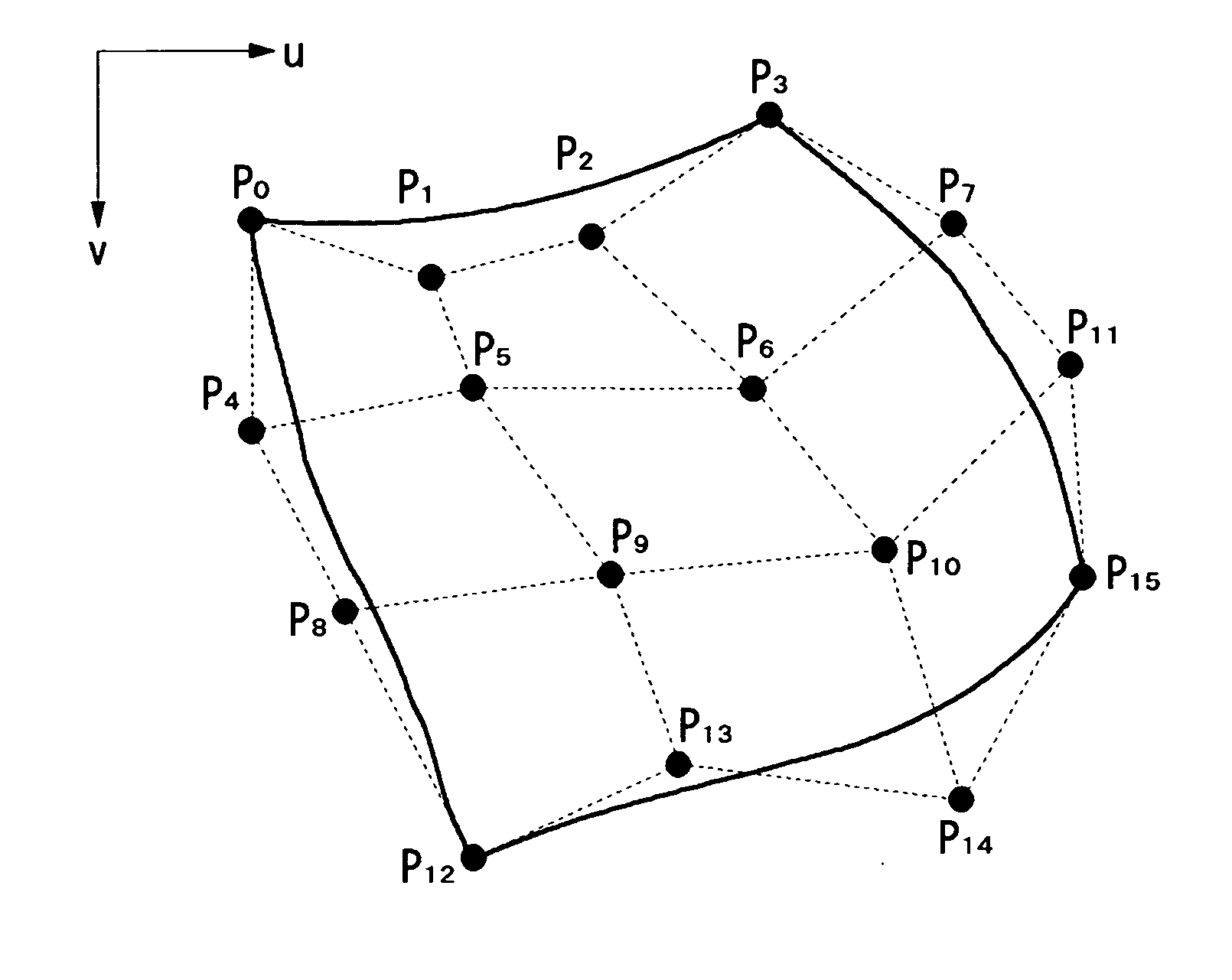

Drawing processing apparatus, texture processing apparatus, and tessellation method

InactiveUS20060197760A1Large memory capacityPerforming processing efficientlyAnalogue computers for chemical processesCathode-ray tube indicatorsLoad instructionComputer graphics (images)

Owner:SONY COMPUTER ENTERTAINMENT INC

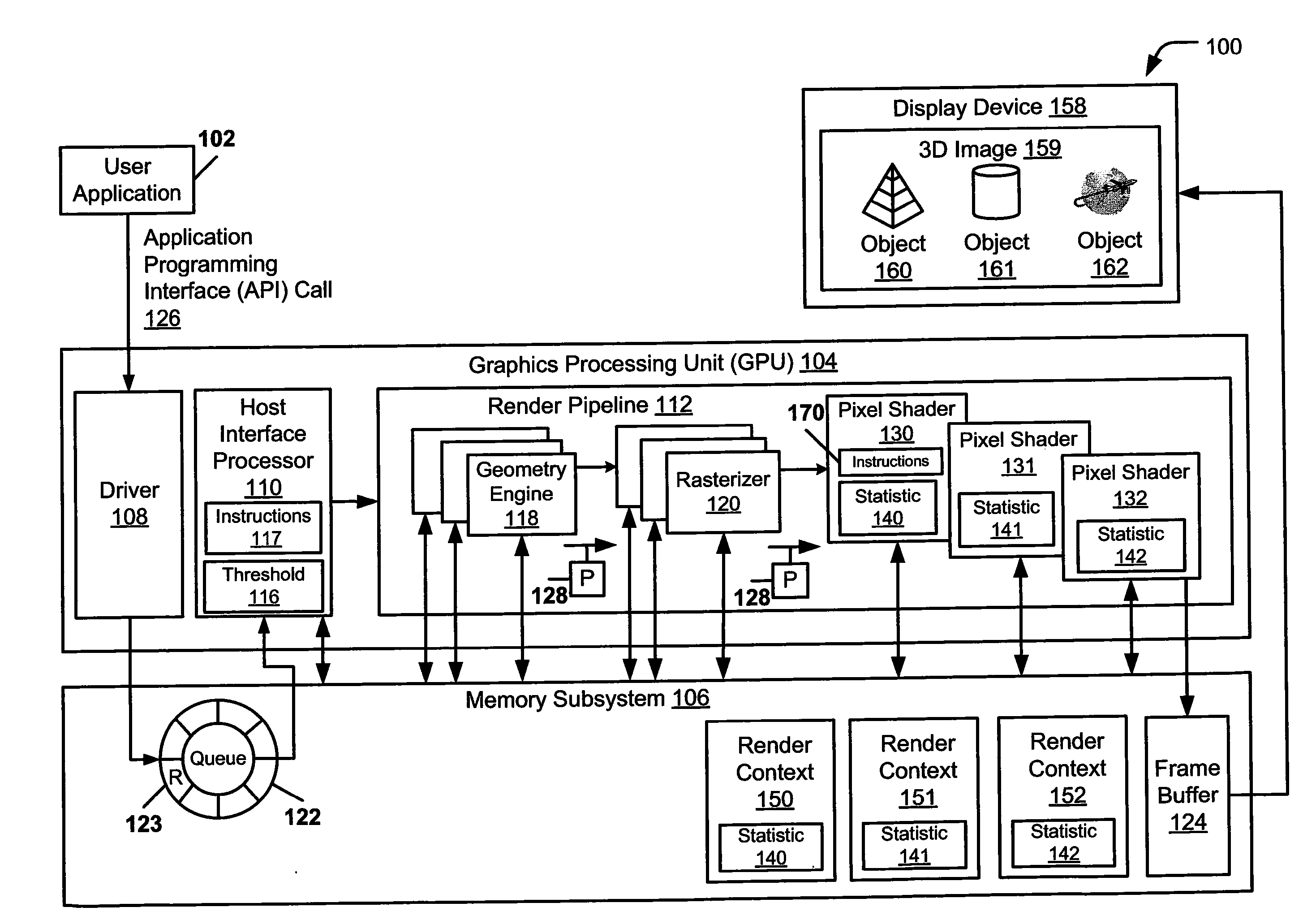

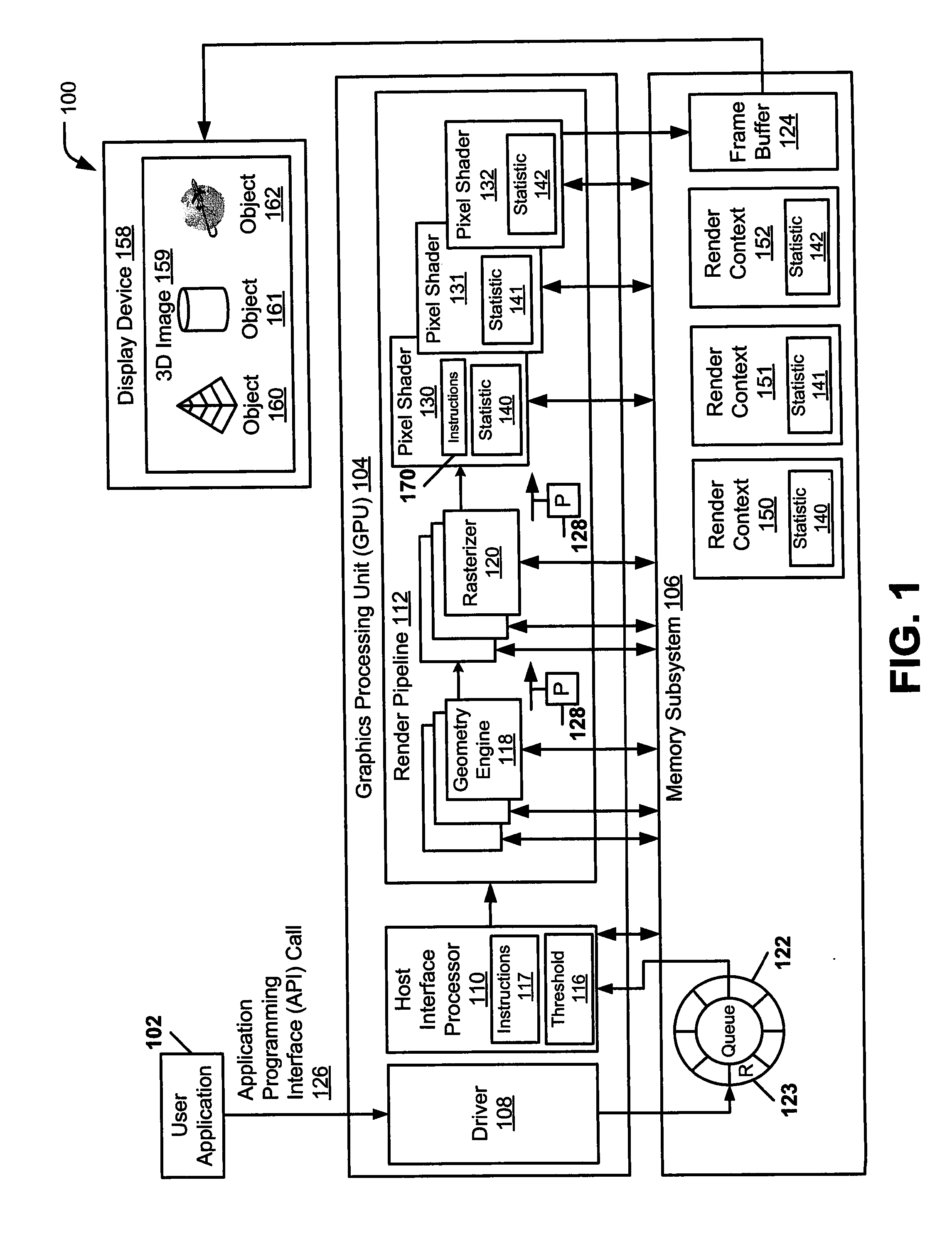

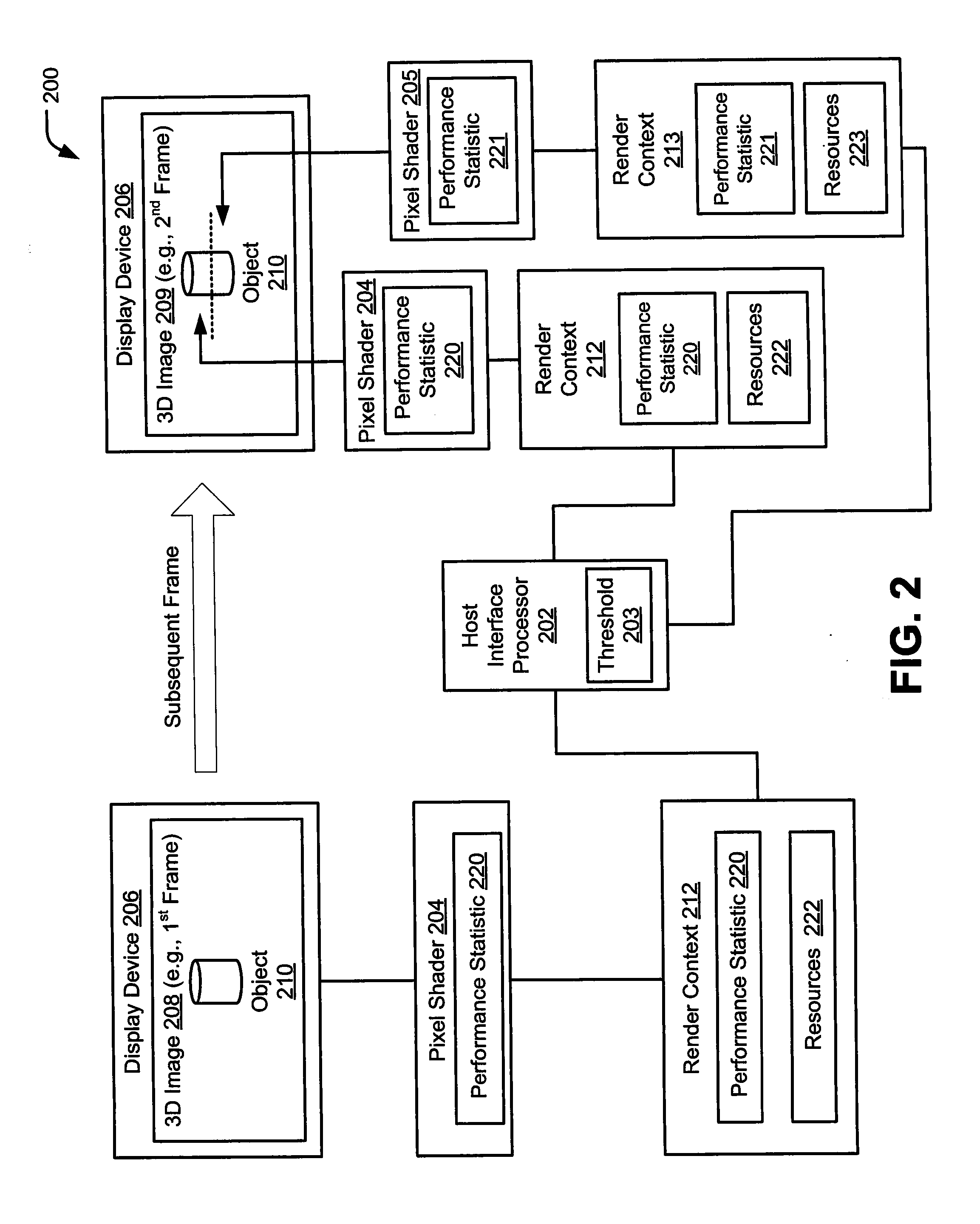

Allocating Resources Based On A Performance Statistic

InactiveUS20110285709A1Multiple digital computer combinationsElectric digital data processingComputer graphics (images)Context data

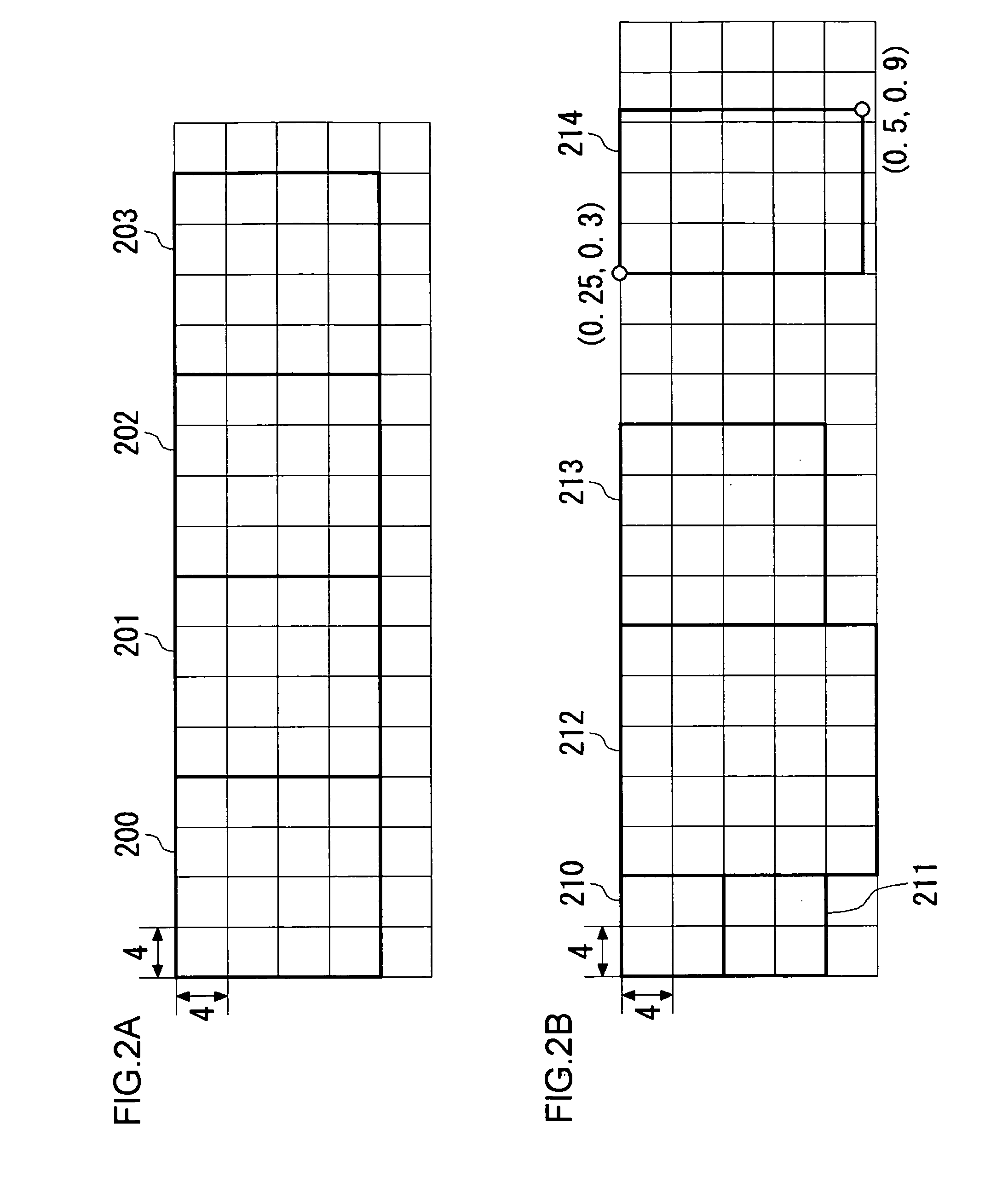

A method includes rendering an object of a three dimensional image via a pixel shader based on a render context data structure associated with the object. The method includes measuring a performance statistic associated with rendering the object. The method also includes storing the performance statistic in the render context data structure associated with the object. The performance statistic is accessible to a host interface processor to determine whether to allocate a second pixel shader to render the object in a subsequent three-dimensional image.

Owner:IBM CORP

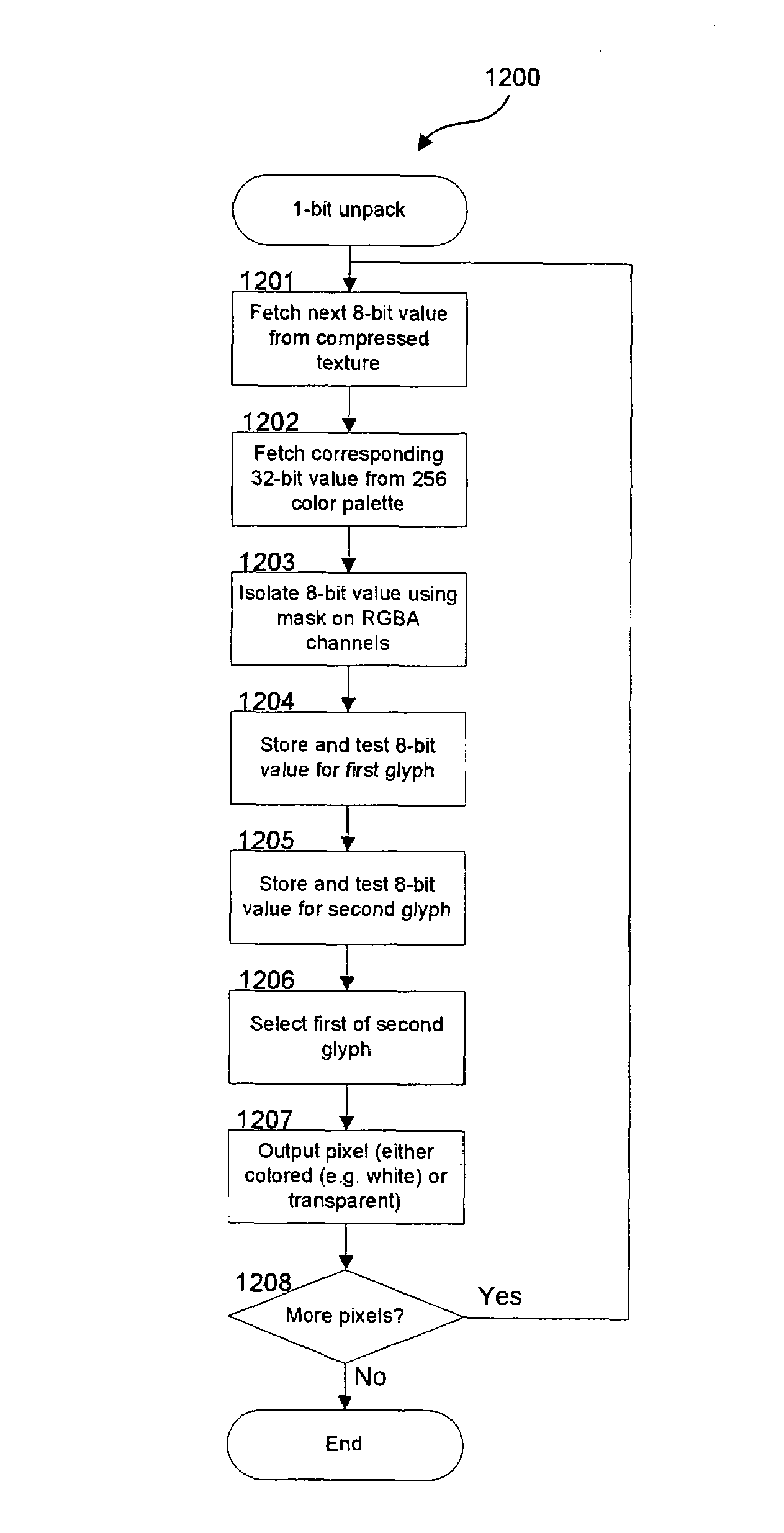

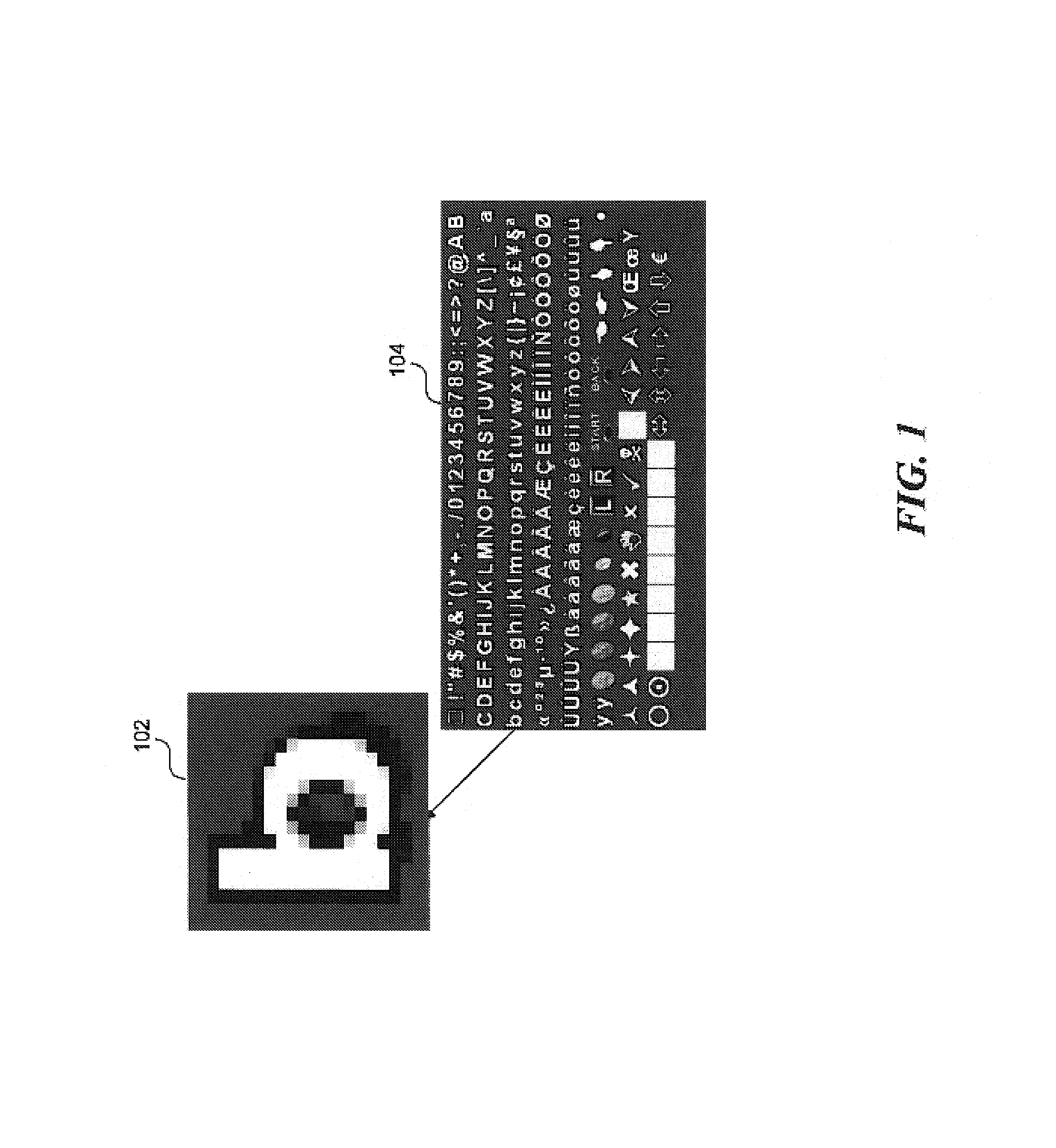

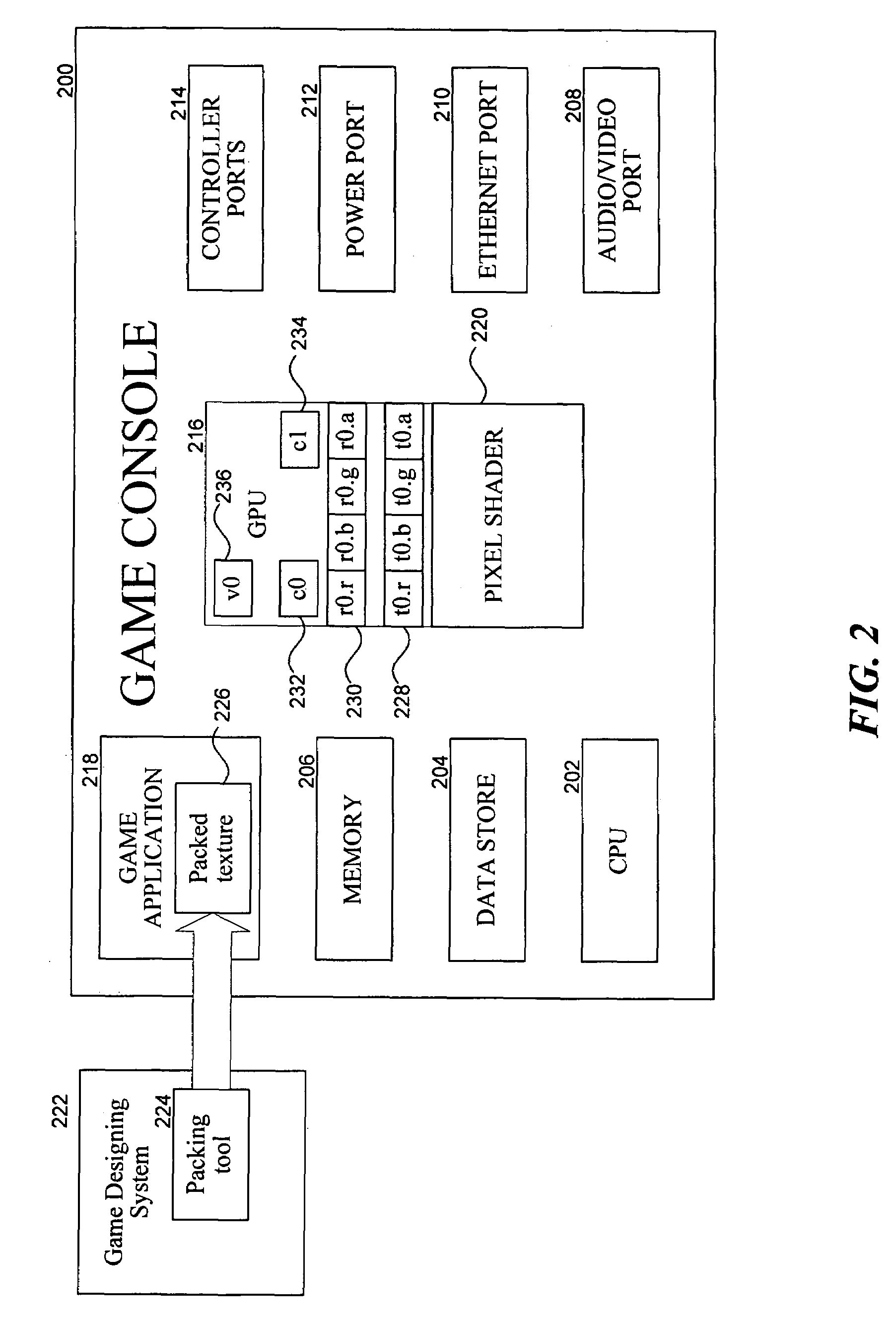

Texture-based packing, such as for packing 8-bit pixels into two bits

InactiveUS7643032B2Easy to processCharacter and pattern recognitionCathode-ray tube indicatorsPattern recognition8-bit color

A method and system for rendering three-dimensional graphics, including text, provide a compressed texture bitmap. The texture bitmap may represent multiple symbols, each comprised of multiple pixels. Each pixel in the texture bitmap may store information for more than one symbol, including compressed pixels corresponding to multiple distinct symbols. For example, the compressed texture bitmap may have n-bit pixels (e.g., 8-bit pixels) that each store m (e.g., four) n / m-bit (e.g., 2-bit) compressed values. The compressed texture bitmap may be configured for unpacking by a conventional pixel shader, such as a pixel shader that does not typically perform bitwise operations. The unpacking may include matching a fetched pixel to a value in a lookup table, such as a 32-bit value from a 256-color palette. The looked-up value can be separated into separate sub-values to facilitate processing by the pixel shader. For example, the looked-up value can be split into RGBA values conventionally used in processing colored pixels.

Owner:MICROSOFT TECH LICENSING LLC

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding techniques

ActiveUS20080198169A1Improve abilitiesSophisticated effectDigital computer detailsNext instruction address formationComputational scienceCoprocessor

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding processing and communication techniques are provided. For an improved graphics pipeline, the invention provides a class of co-processing device, such as a graphics processor unit (GPU), providing improved capabilities for an abstract or virtual machine for performing graphics calculations and rendering. The invention allows for runtime-predicated flow control of programs downloaded to coprocessors, enables coprocessors to include indexable arrays of on-chip storage elements that are readable and writable during execution of programs, provides native support for textures and texture maps and corresponding operations in a vertex shader, provides frequency division of vertex streams input to a vertex shader with optional support for a stream modulo value, provides a register storage element on a pixel shader and associated interfaces for storage associated with representing the “face” of a pixel, provides vertex shaders and pixel shaders with more on-chip register storage and the ability to receive larger programs than any existing vertex or pixel shaders and provides 32 bit float number support in both vertex and pixel shaders.

Owner:MICROSOFT TECH LICENSING LLC

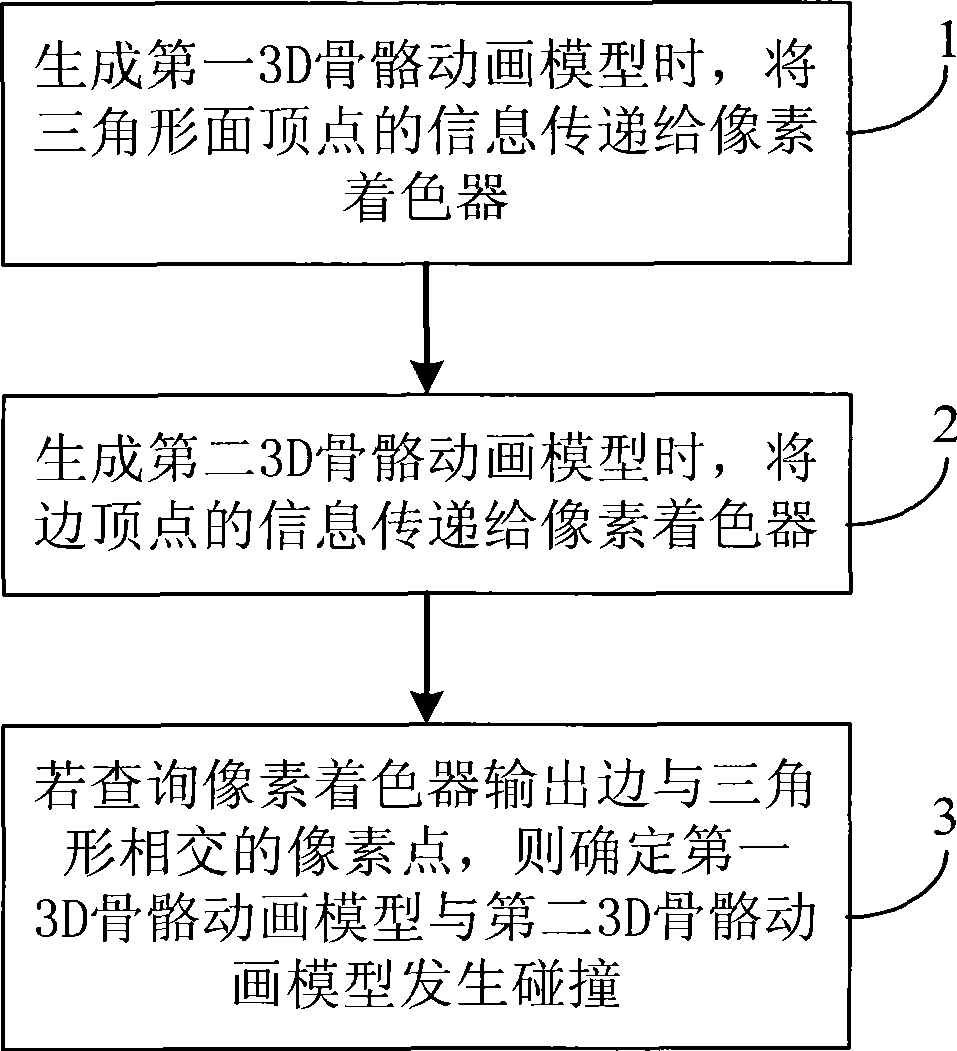

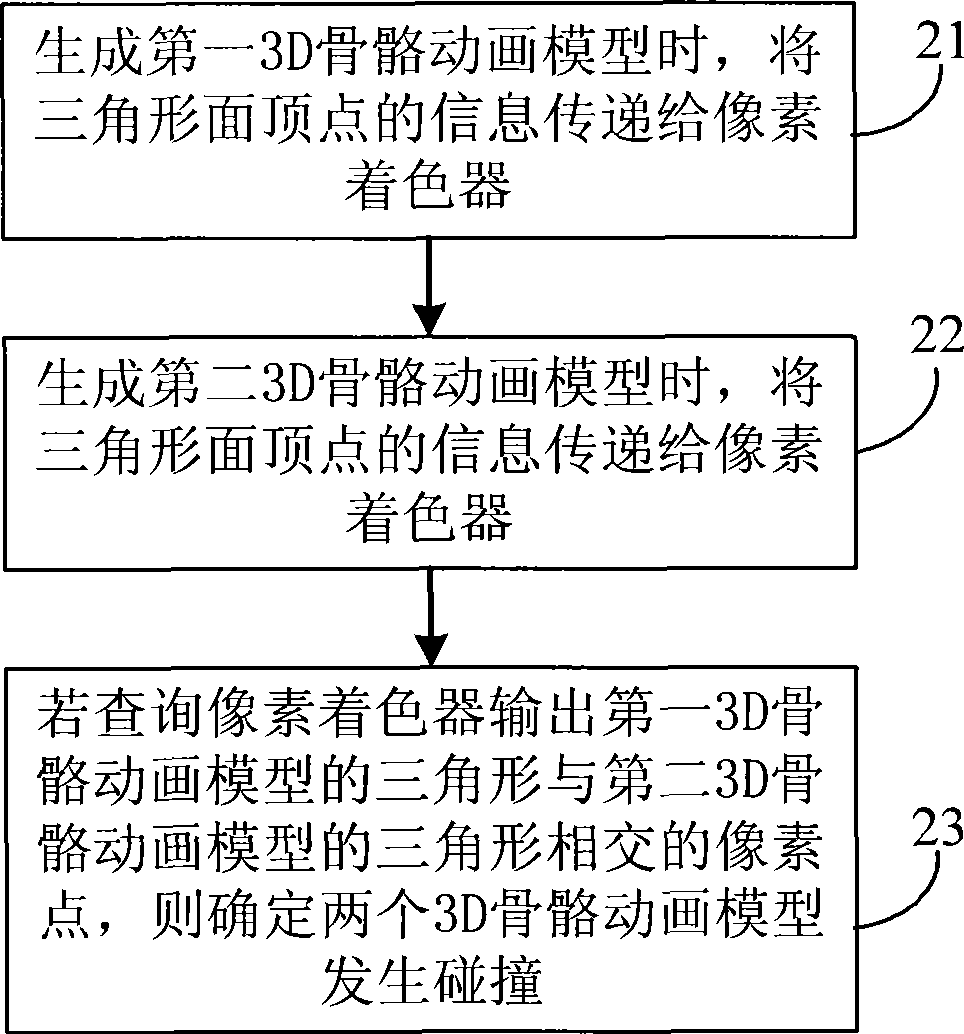

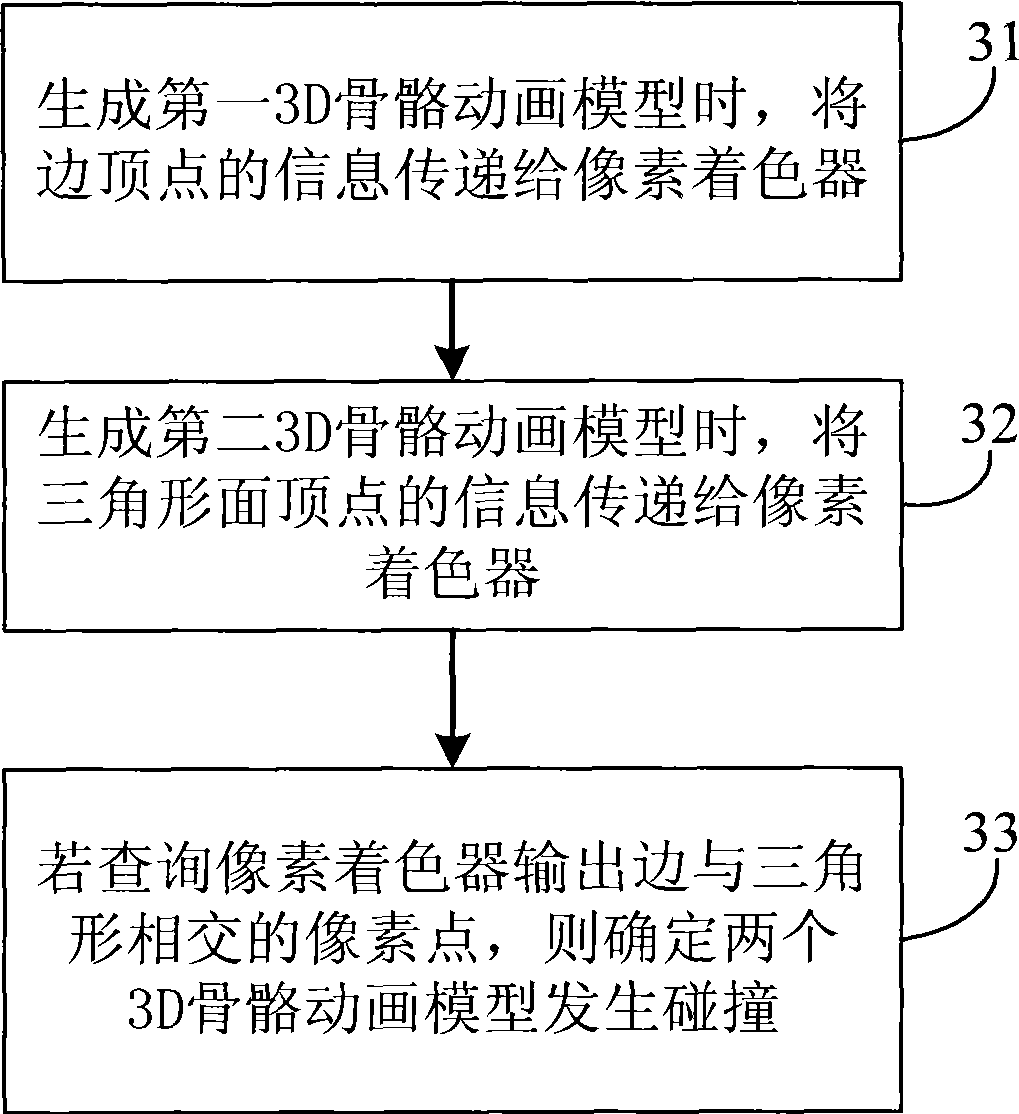

Collision detection method implementing 3D animation model in display card, display card and system therefor

ActiveCN101458825AFully utilize processing powerImage data processing detailsAnimationGraphic cardInformation transmission

The invention provides a collision detection method for realizing 3D skeleton animation in display card, a display card and a system therefore, belonging to computer graphic technical field. The method comprises: in the generation of triangle surface top point texture or edge top point texture of a first 3D skeleton animation model, transmitting the determined information of the triangle surface top point or the edge top points to a pixel coloring device of the display card; in the generation of edge top point texture or triangle surface top point texture of a second 3D skeleton animation model, transmitting the determined information of the edge top point or the triangle surface top point to the pixel coloring device of the display card; using the pixel coloring device of the display card to output the crossed pixel points of the triangle surface or edge of the first 3D skeleton animation model and the edge or triangle surface of the second 3D skeleton animation model; inquiring if there is pixel point output of the pixel coloring device of the display card, thinking there is collision between the first 3D skeleton animation model and the second 3D skeleton animation model. The method utilizes display card to complete collision detection of generated 3D skeleton animation models, to save CPU resource and reduce CPU utility.

Owner:TENCENT TECH CHENGDU

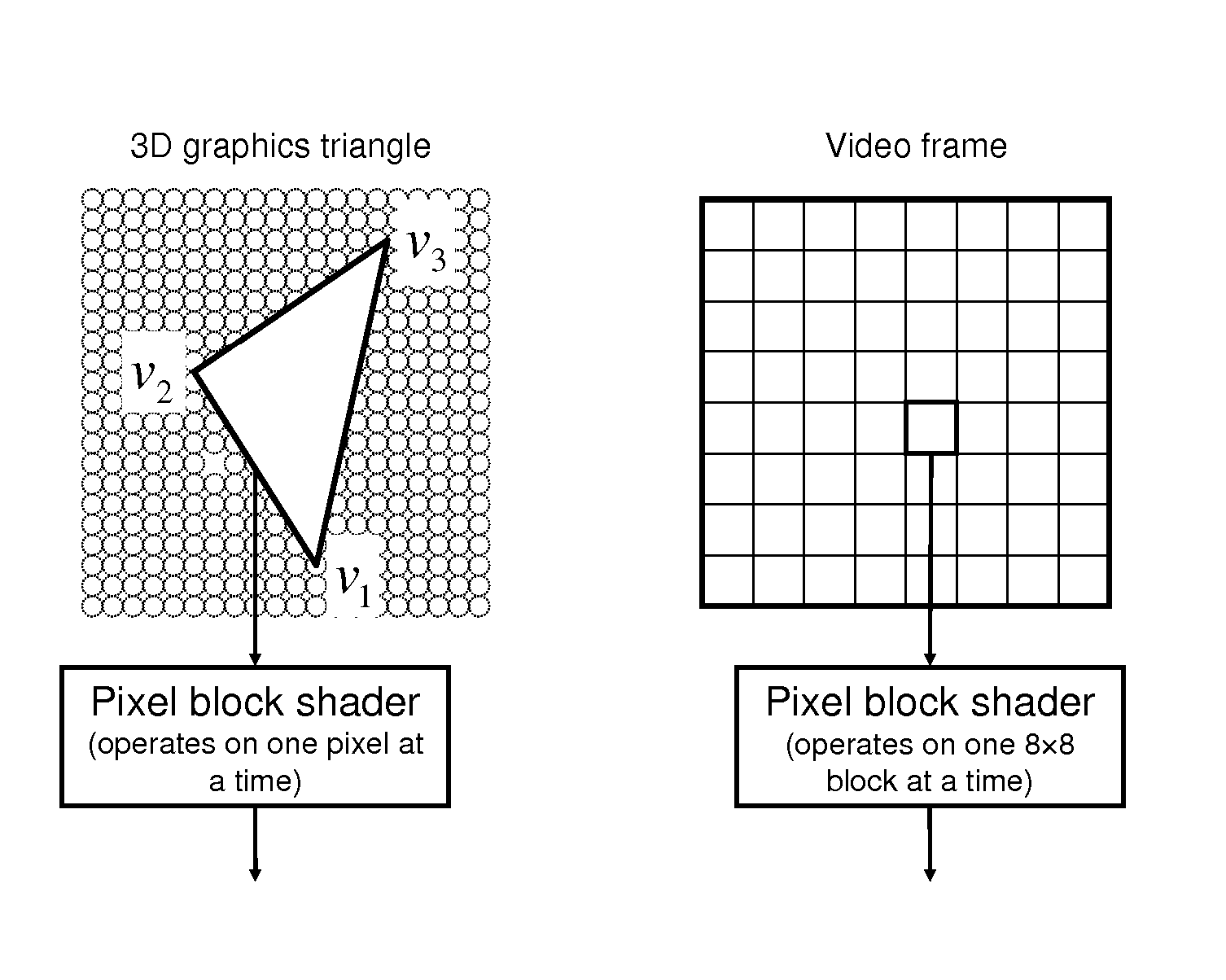

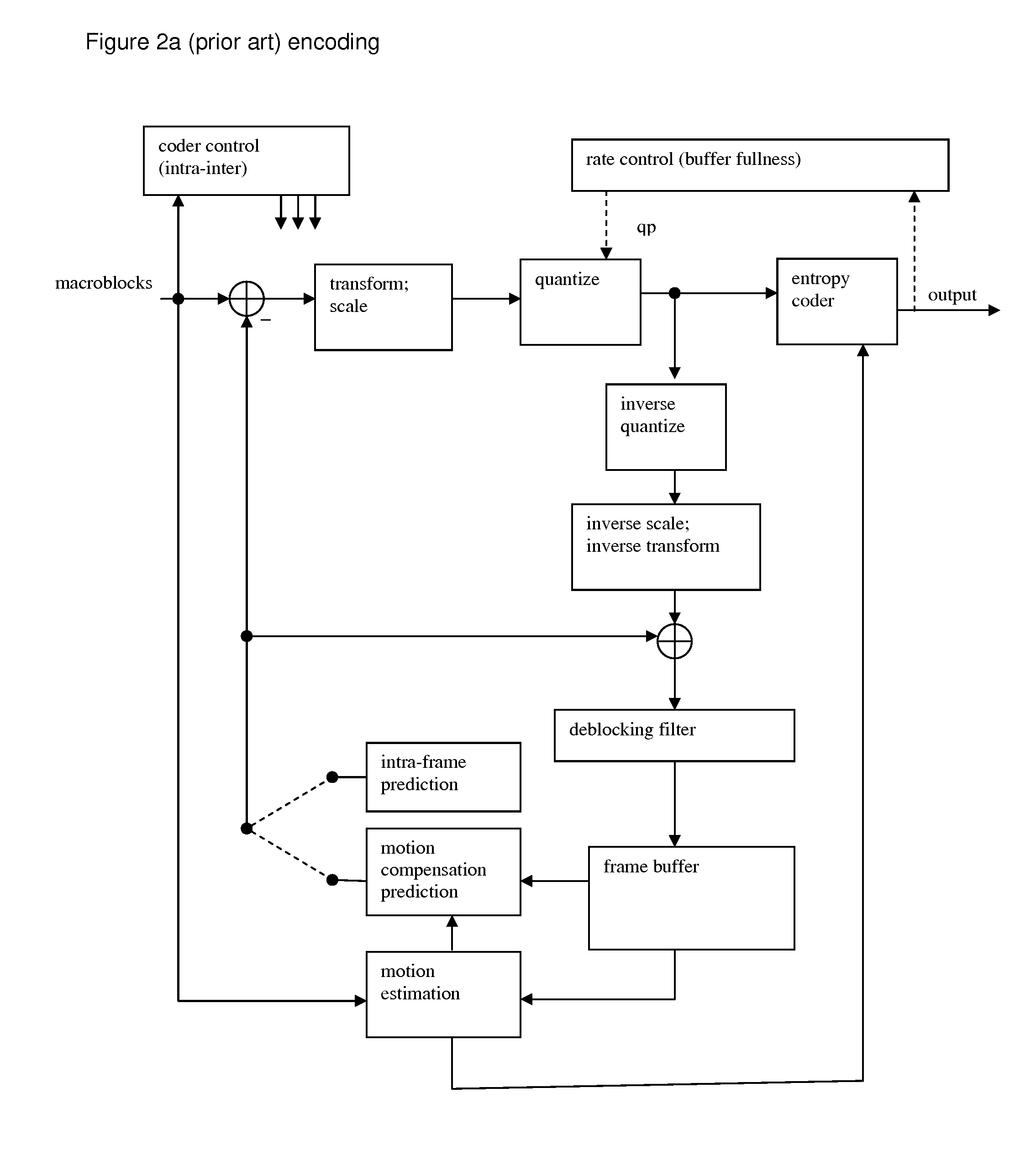

Video decoding with 3D graphics shaders

Video coding using 3D graphics rendering hardware by enhancing pixel shaders to pixel block shaders to provide efficient motion compensation computations. Reference frame prediction corresponds to texture lookup, and matrix multiplication is cast in linear combinations of rows format to correspond to pixel shader vector operations.

Owner:TEXAS INSTR INC

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding techniques

ActiveUS20050122331A1Improve abilitiesSophisticated effectDigital computer detailsNext instruction address formationComputational scienceCoprocessor

Systems and methods for downloading algorithmic elements to a coprocessor and corresponding processing and communication techniques are provided. For an improved graphics pipeline, the invention provides a class of co-processing device, such as a graphics processor unit (GPU), providing improved capabilities for an abstract or virtual machine for performing graphics calculations and rendering. The invention allows for runtime-predicated flow control of programs downloaded to coprocessors, enables coprocessors to include indexable arrays of on-chip storage elements that are readable and writable during execution of programs, provides native support for textures and texture maps and corresponding operations in a vertex shader, provides frequency division of vertex streams input to a vertex shader with optional support for a stream modulo value, provides a register storage element on a pixel shader and associated interfaces for storage associated with representing the “face” of a pixel, provides vertex shaders and pixel shaders with more on-chip register storage and the ability to receive larger programs than any existing vertex or pixel shaders and provides 32 bit float number support in both vertex and pixel shaders.

Owner:MICROSOFT TECH LICENSING LLC

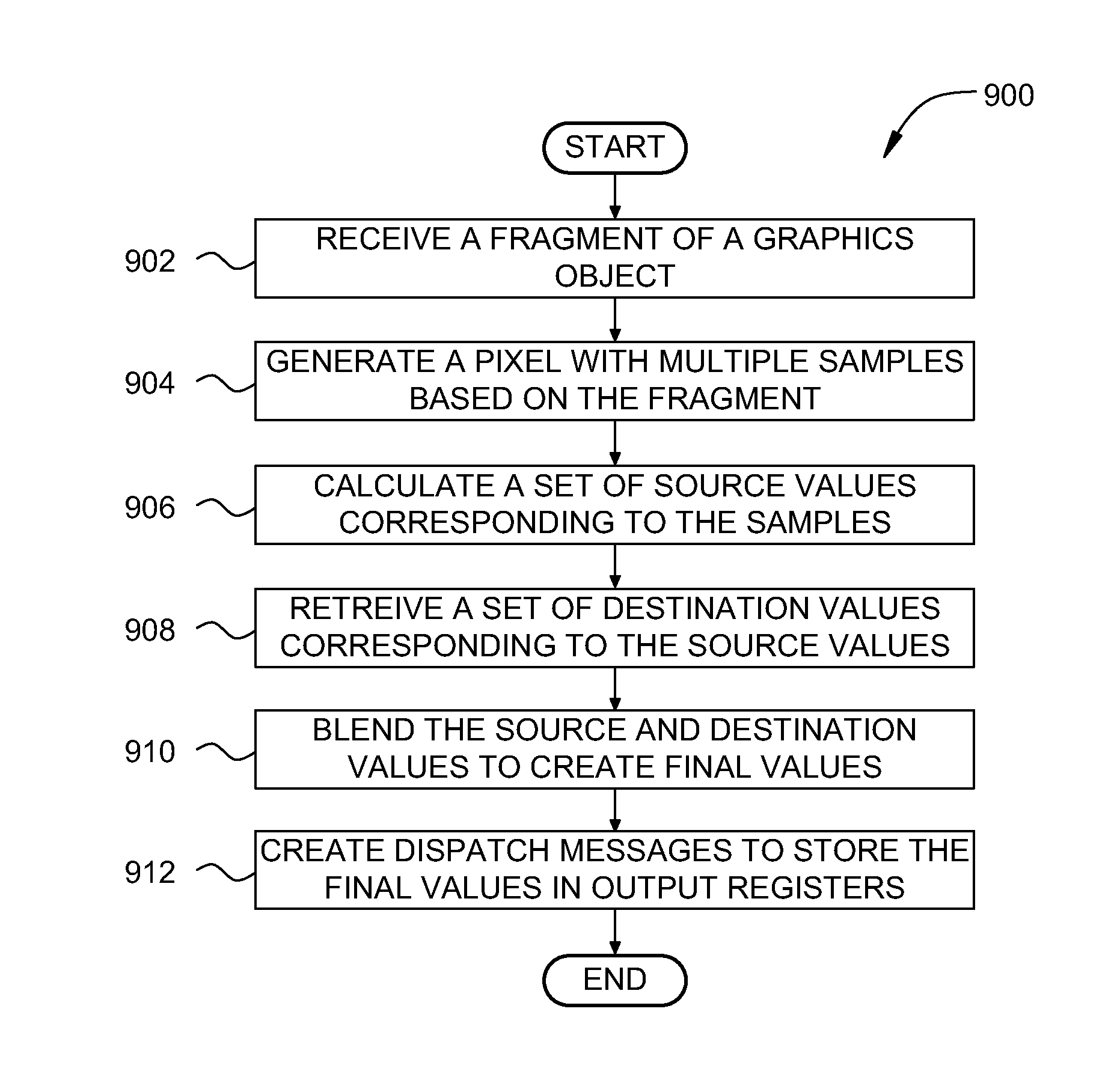

Efficient super-sampling with per-pixel shader threads

ActiveUS20140176579A1Improve efficiencyImprove image qualityProcessor architectures/configurationImage generationFragment processingComputational science

Techniques are disclosed for dispatching pixel information in a graphics processing pipeline. A fragment processing unit generates a pixel that includes multiple samples based on a first portion of a graphics primitive received by a first thread. The fragment processing unit calculates a first value for the first pixel, where the first value is calculated only once for the pixel. The fragment processing unit calculates a first set of values for the samples, where each value in the first set of values corresponds to a different sample and is calculated only once for the corresponding sample. The fragment processing unit combines the first value with each value in the first set of values to create a second set of values. The fragment processing unit creates one or more dispatch messages to store the second set of values in a set of output registers. One advantage of the disclosed techniques is that pixel shader programs perform per-sample operations with increased efficiency.

Owner:NVIDIA CORP