Patents

Literature

38 results about "Nibble" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In computing, a nibble (occasionally nybble or nyble to match the spelling of byte) is a four-bit aggregation, or half an octet. It is also known as half-byte or tetrade. In a networking or telecommunication context, the nibble is often called a semi-octet, quadbit, or quartet. A nibble has sixteen (2⁴) possible values. A nibble can be represented by a single hexadecimal digit and called a hex digit.

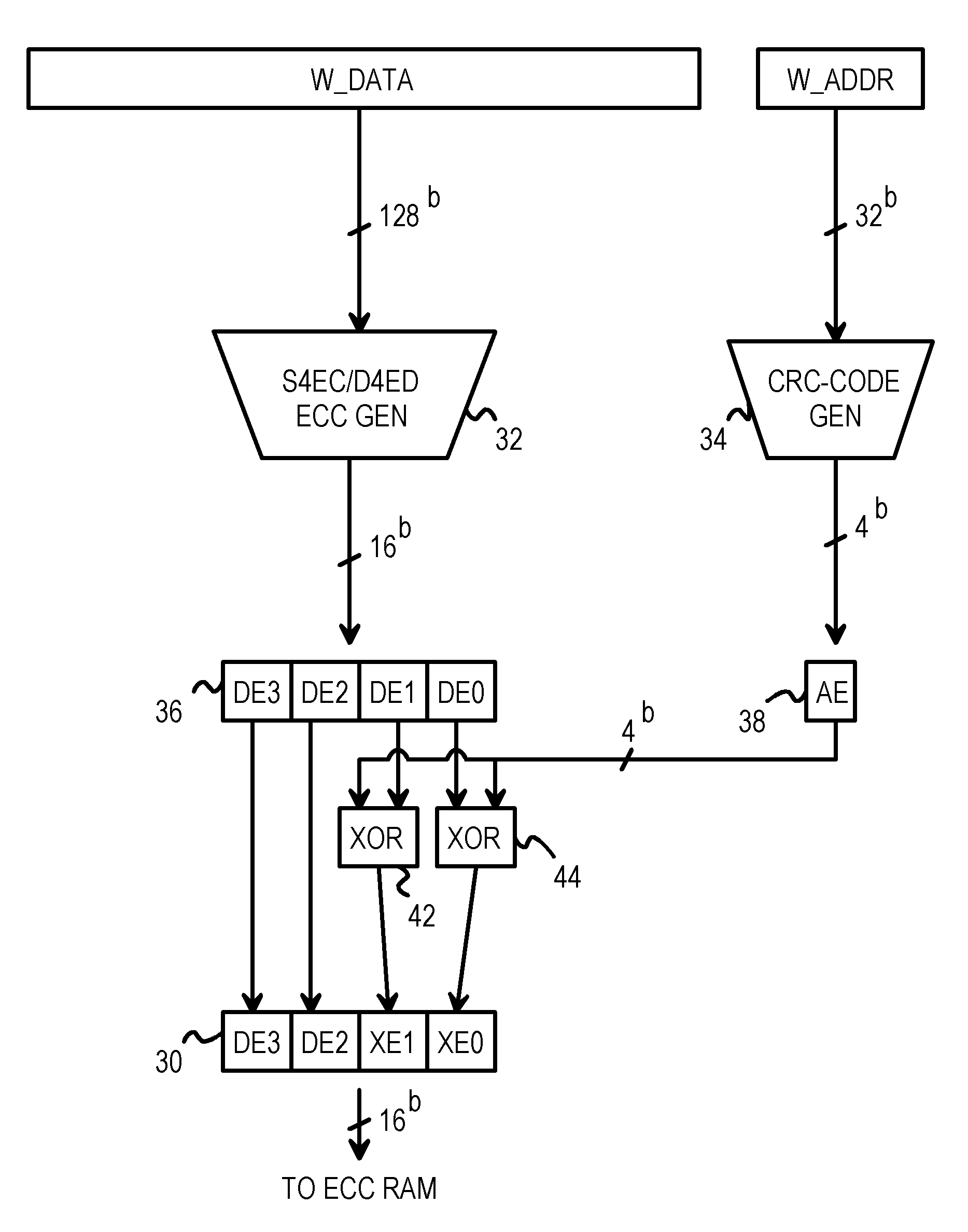

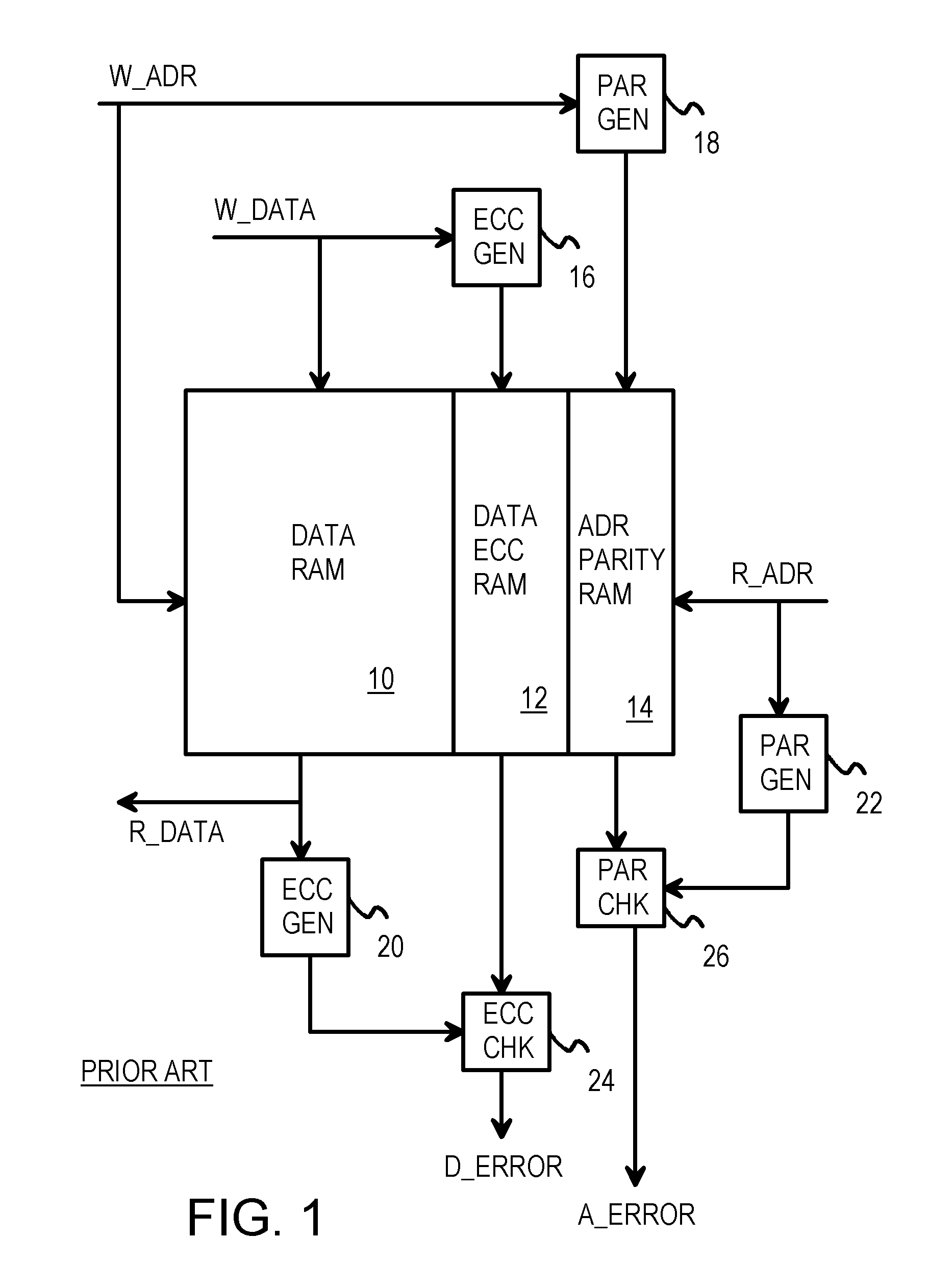

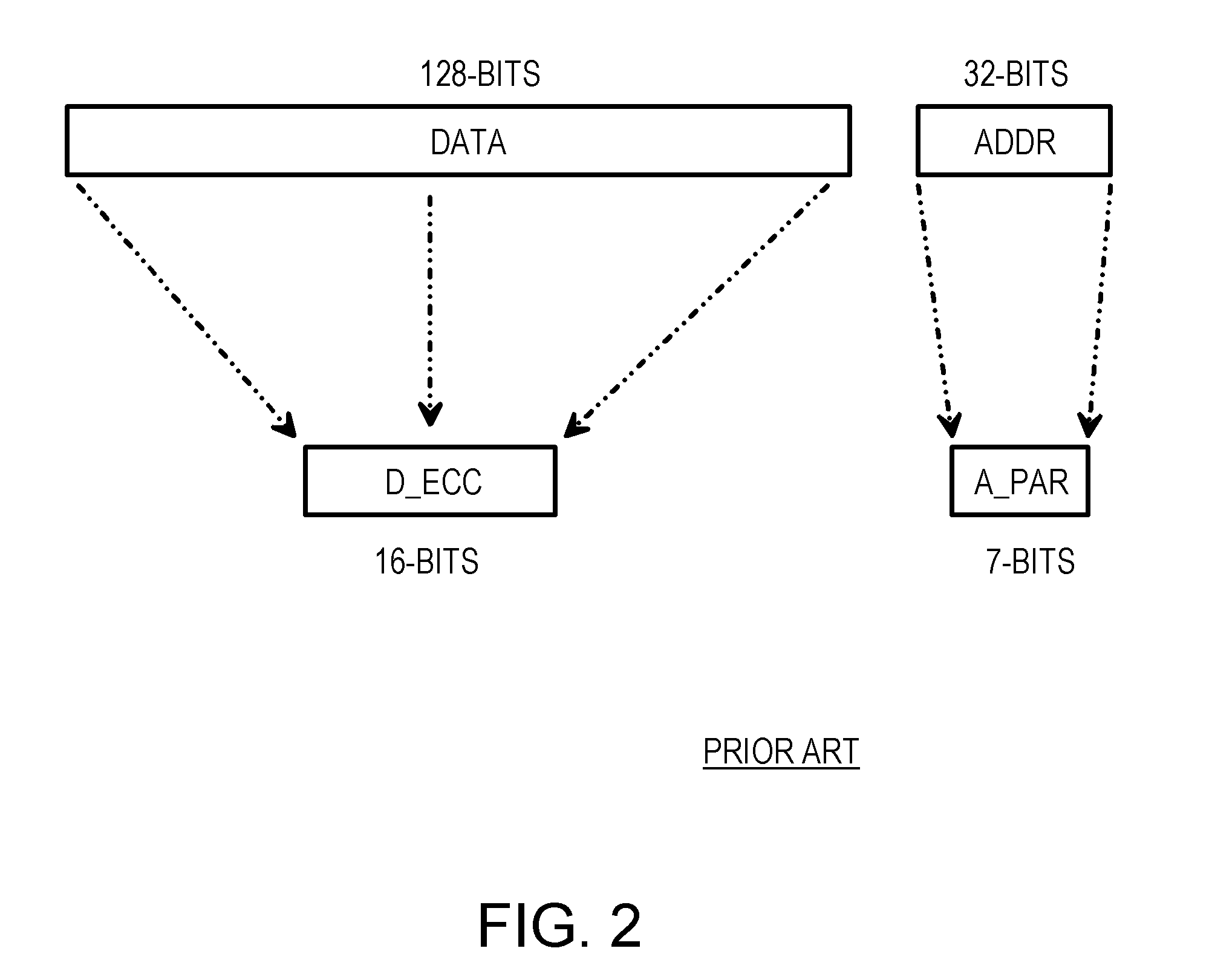

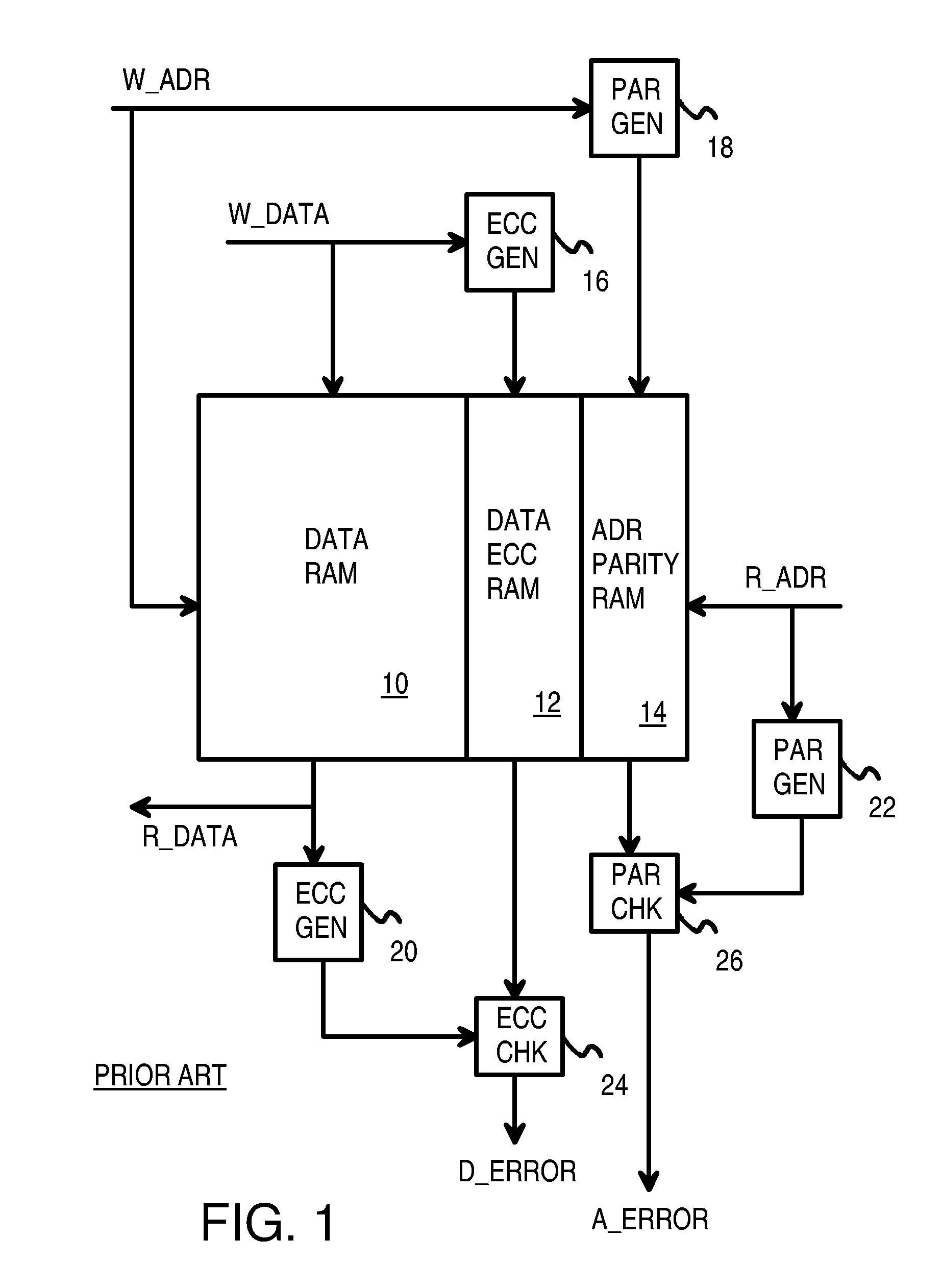

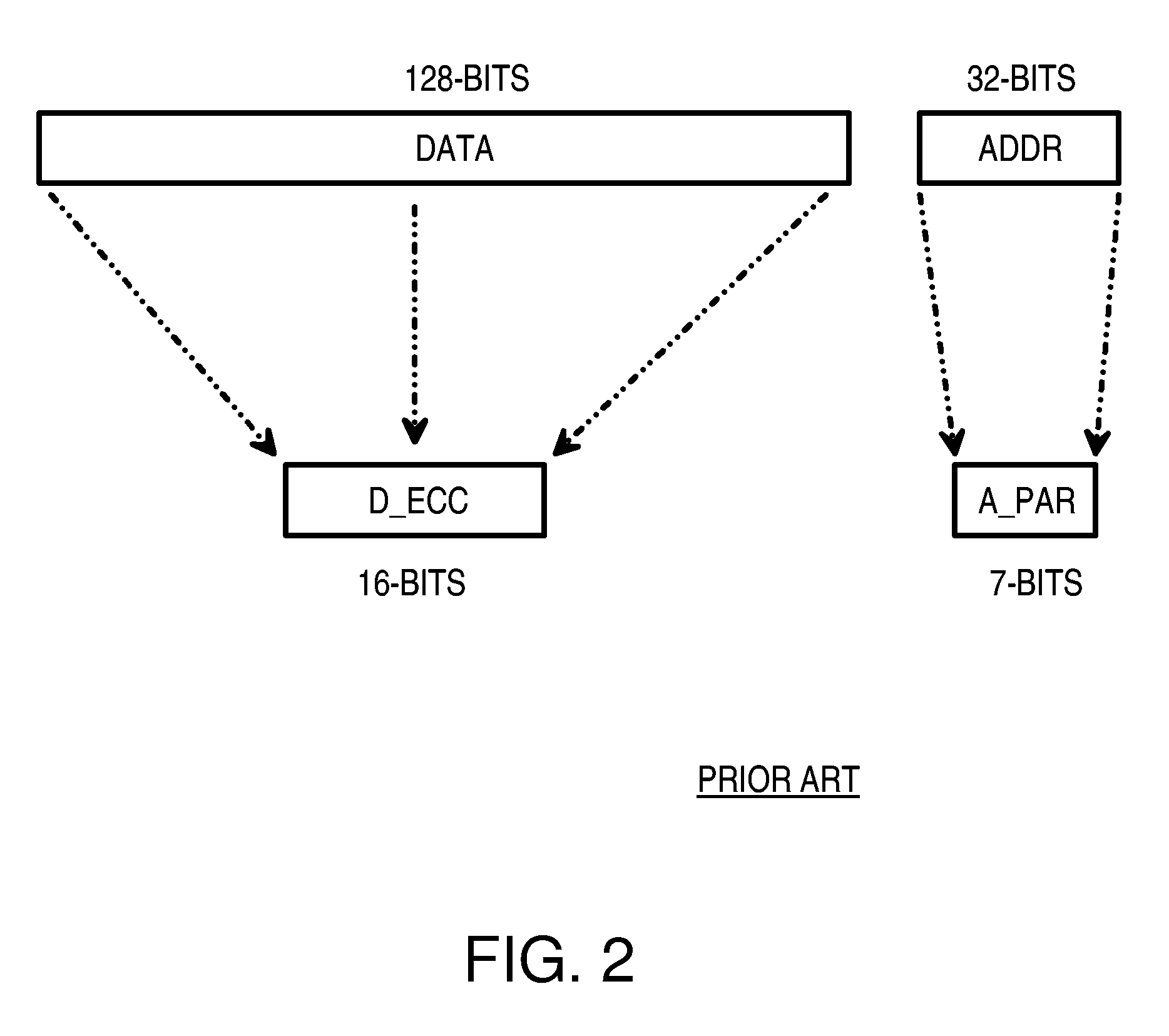

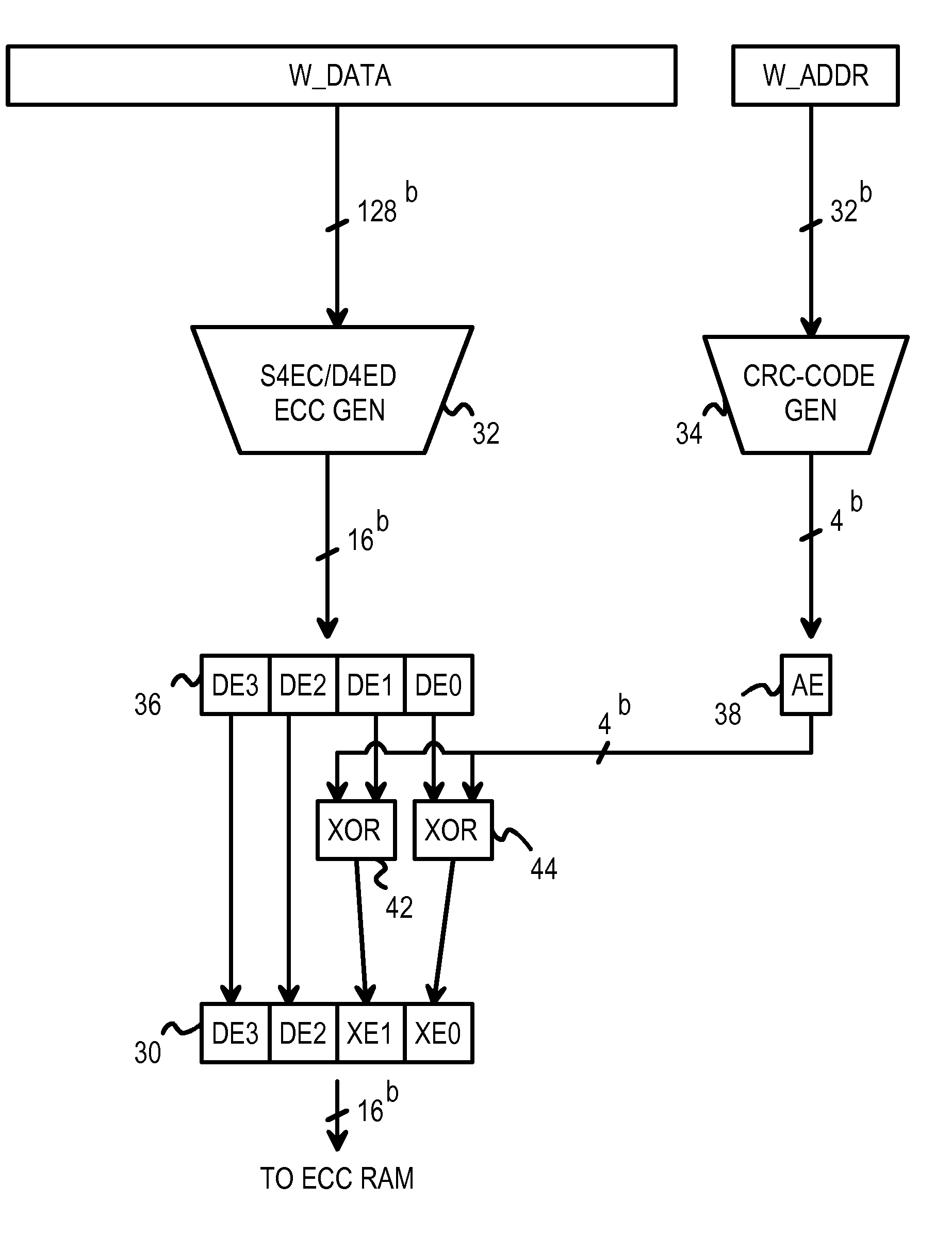

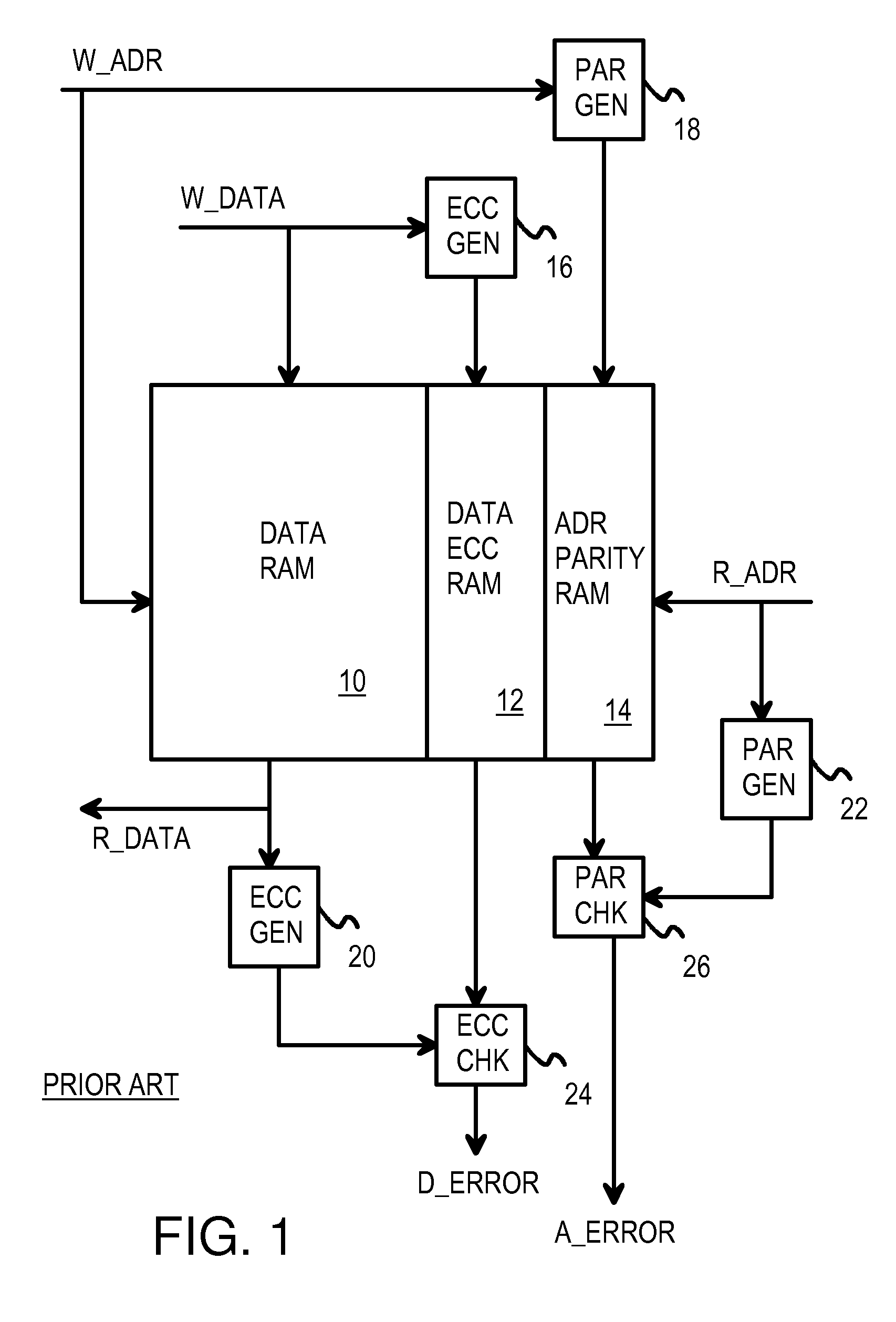

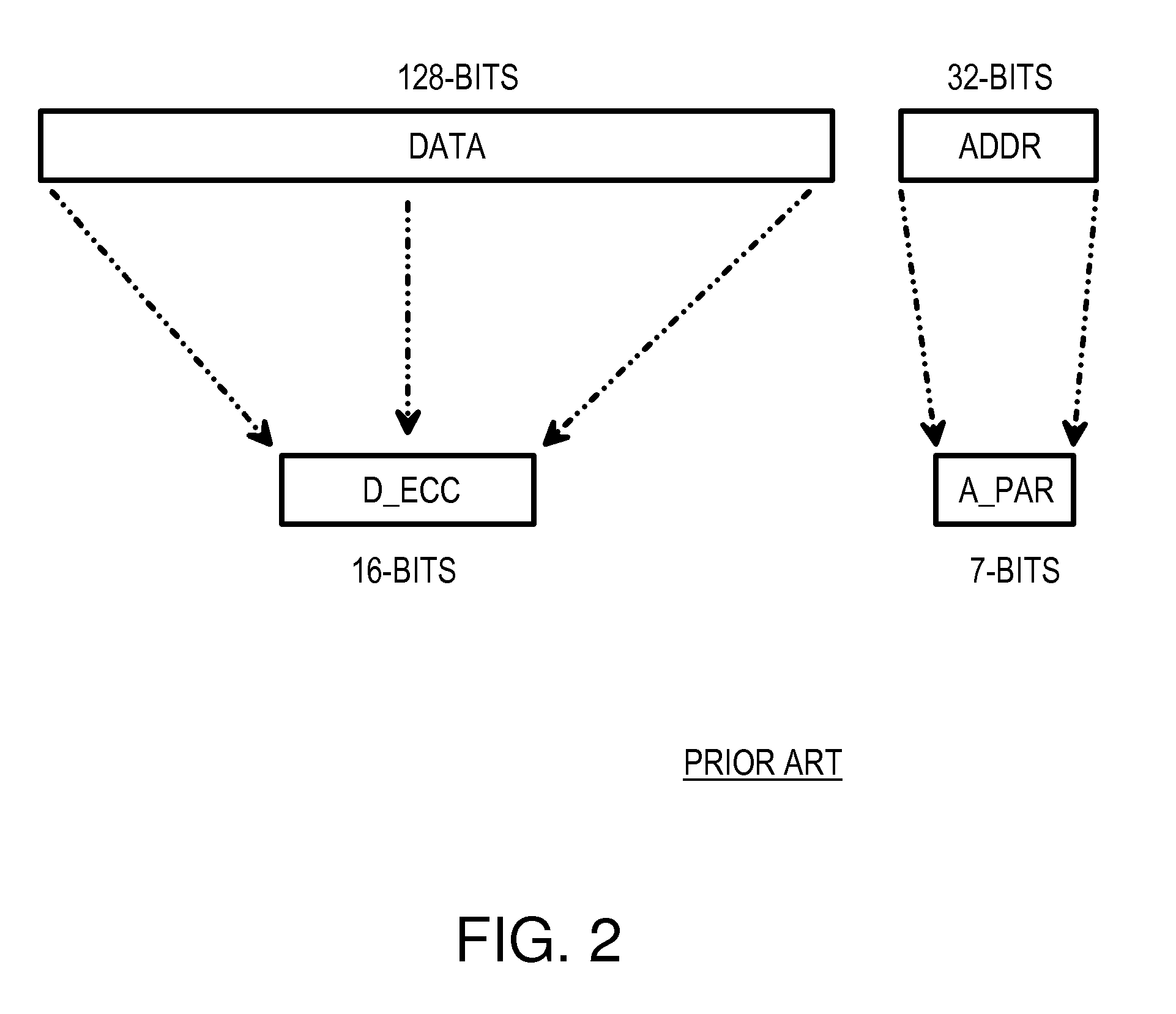

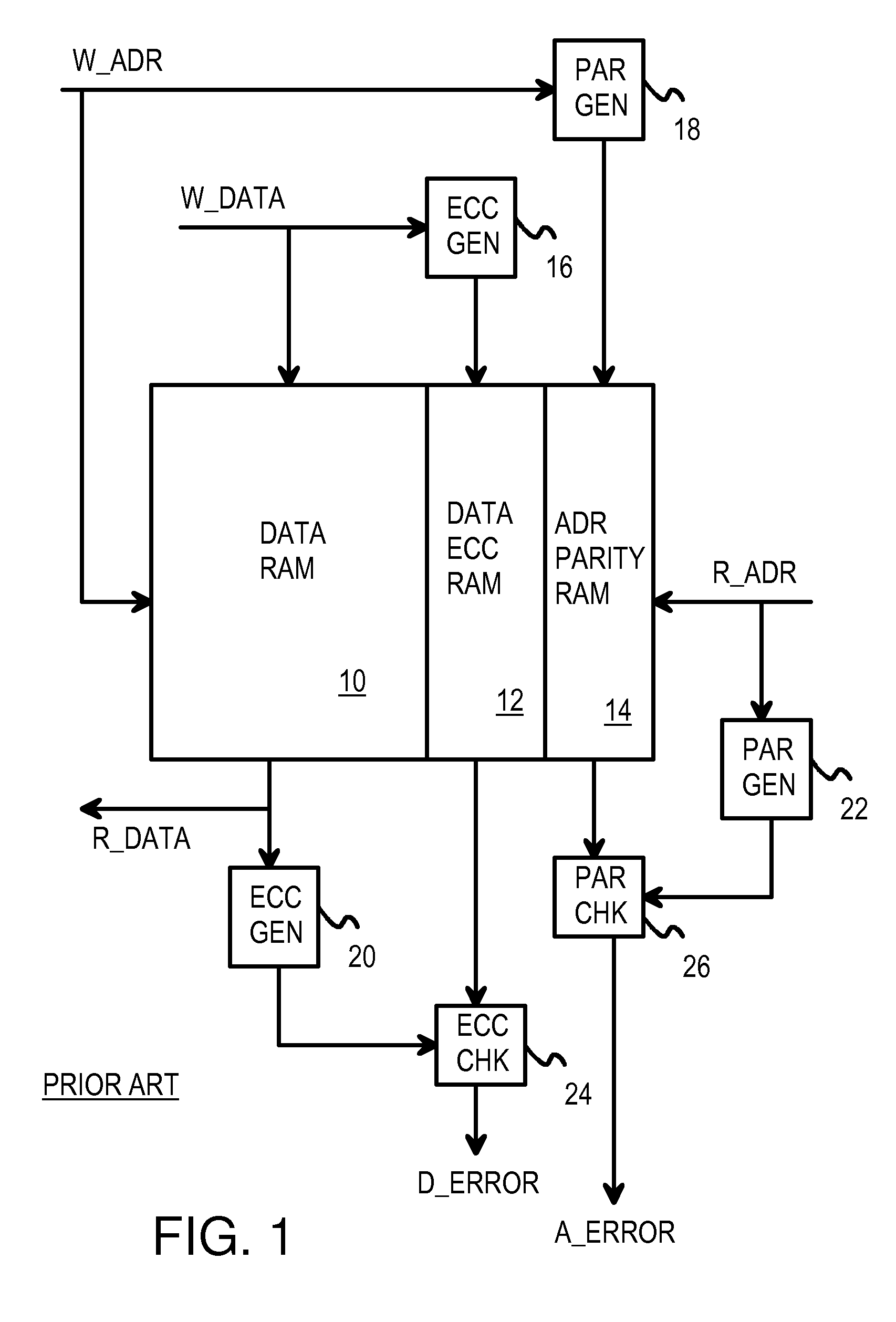

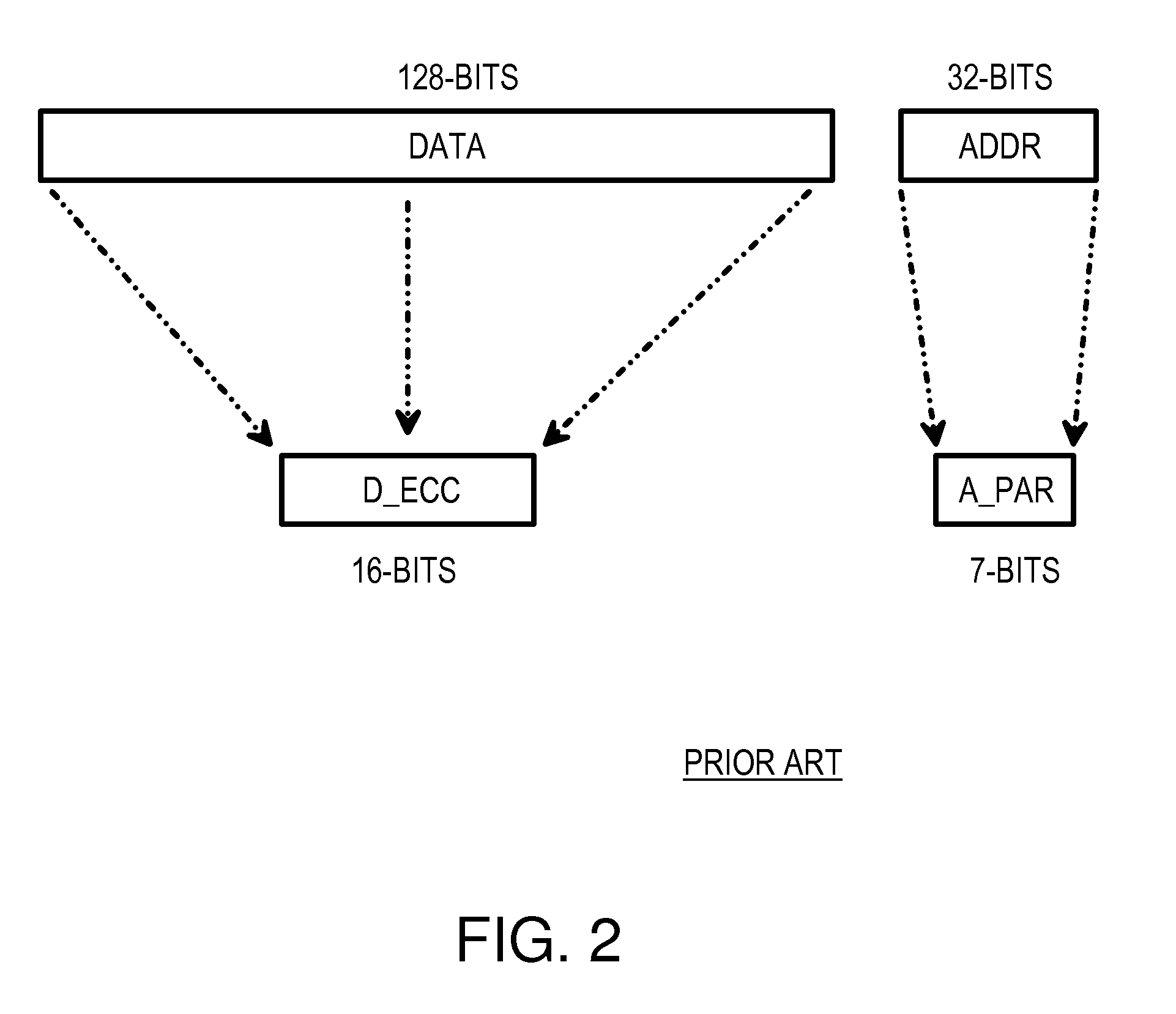

Address error detection by merging a polynomial-based CRC code of address bits with two nibbles of data or data ECC bits

A memory system provides data error detection and correction and address error detection. A Single-byte Error-Correcting / Double-byte Error-Detecting (SbEC / DbED) code with the byte being a 4-bit nibble is used to detect up to 8-bit errors and correct data errors of 4 bits or less. Rather than generating address parity, which is poor at detecting even numbers of errors, a cyclical-redundancy-check (CRC) code generates address check bits. A 32-bit address is compressed to just 4 address check bits using the CRC code. The 4 address check bits are merged (XOR'ed) with two 4-bit nibbles of the data SbEC / DbED code to generate a merged ECC codeword that is stored in memory. An address error causes a 2-nibble mis-match due to the redundant merging of the 4 address check bits with 2 nibbles of data correction code. The CRC code is ideal for detecting even numbers of errors common with multiplexed-address DRAMs.

Owner:AZUL SYSTEMS

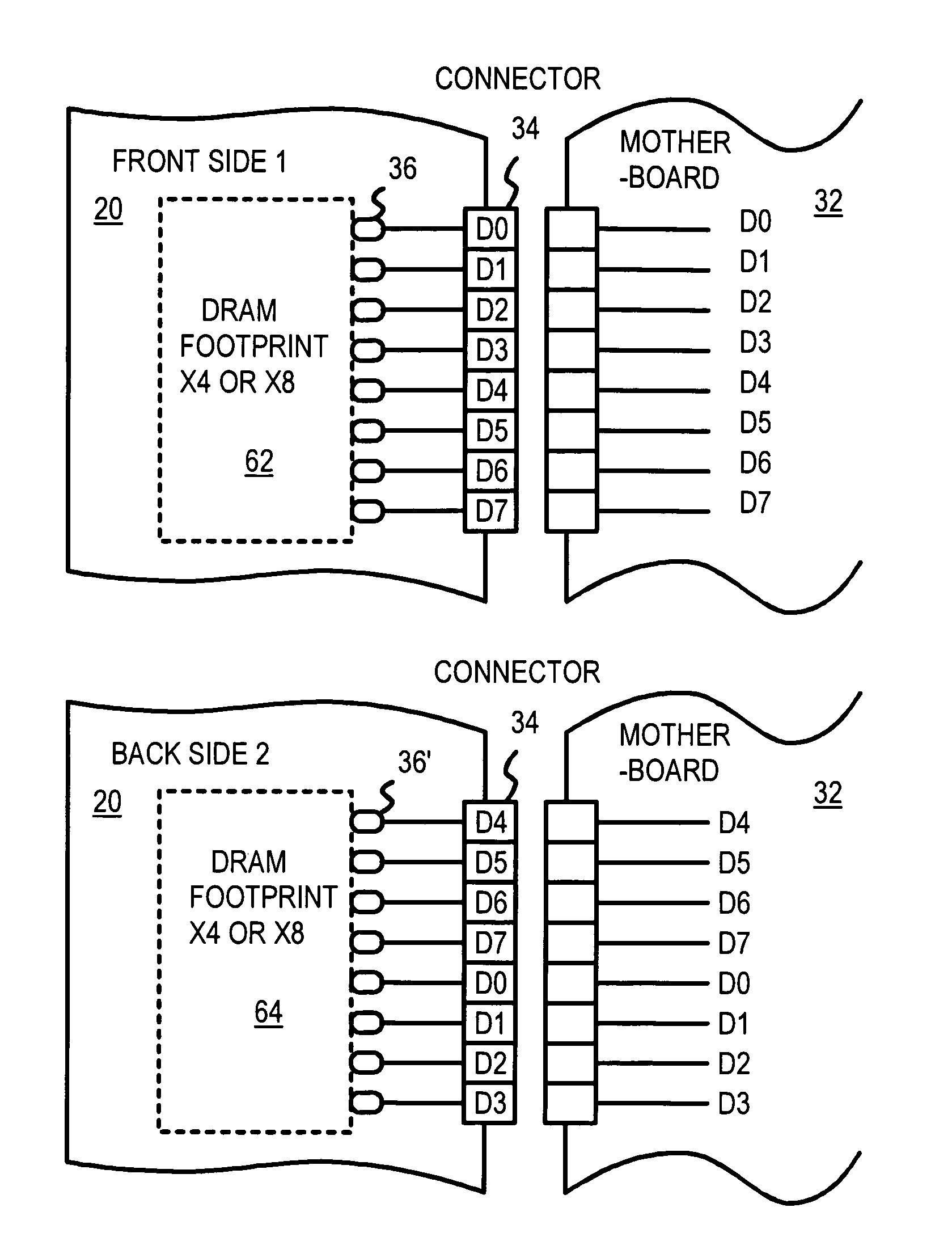

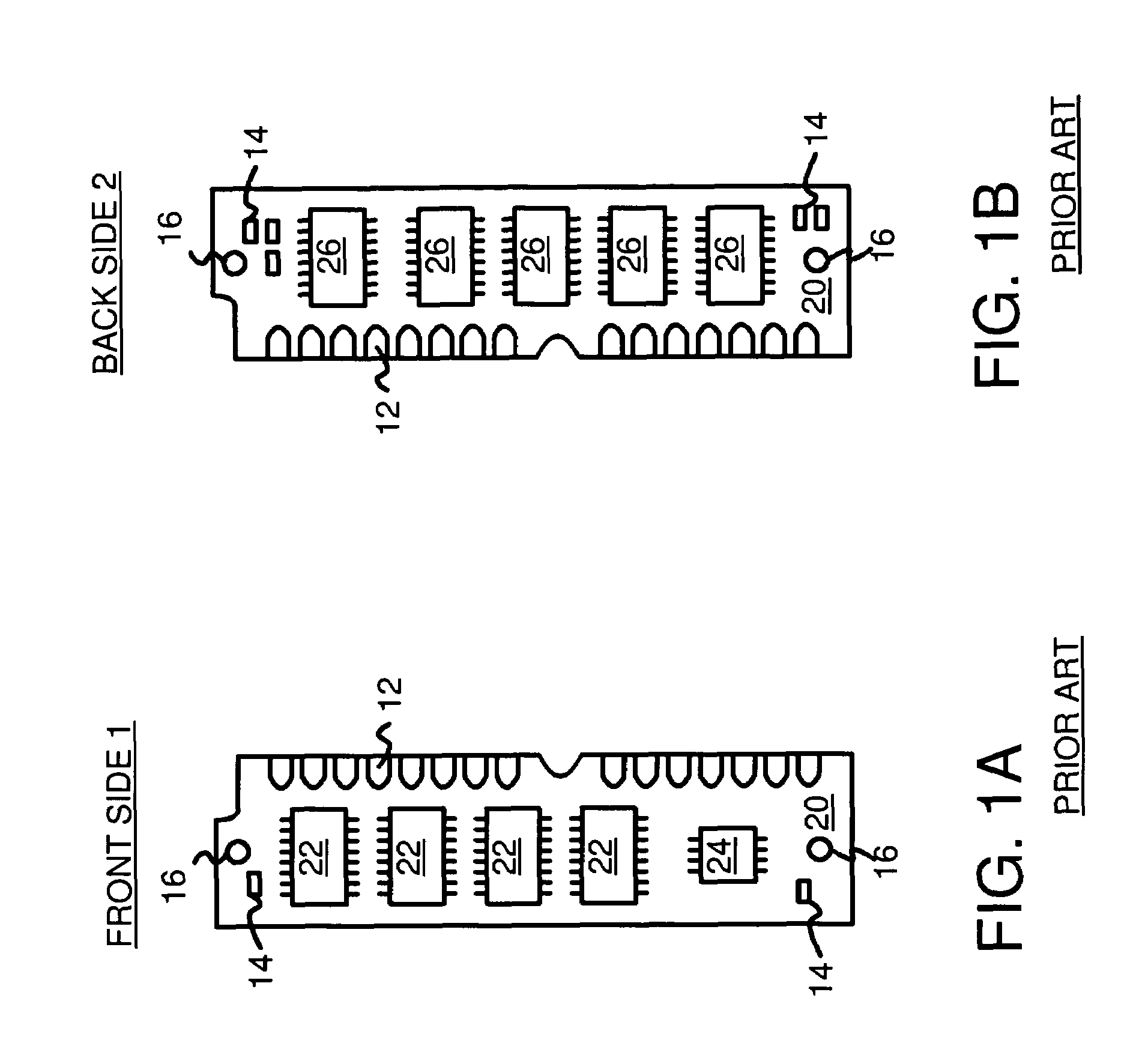

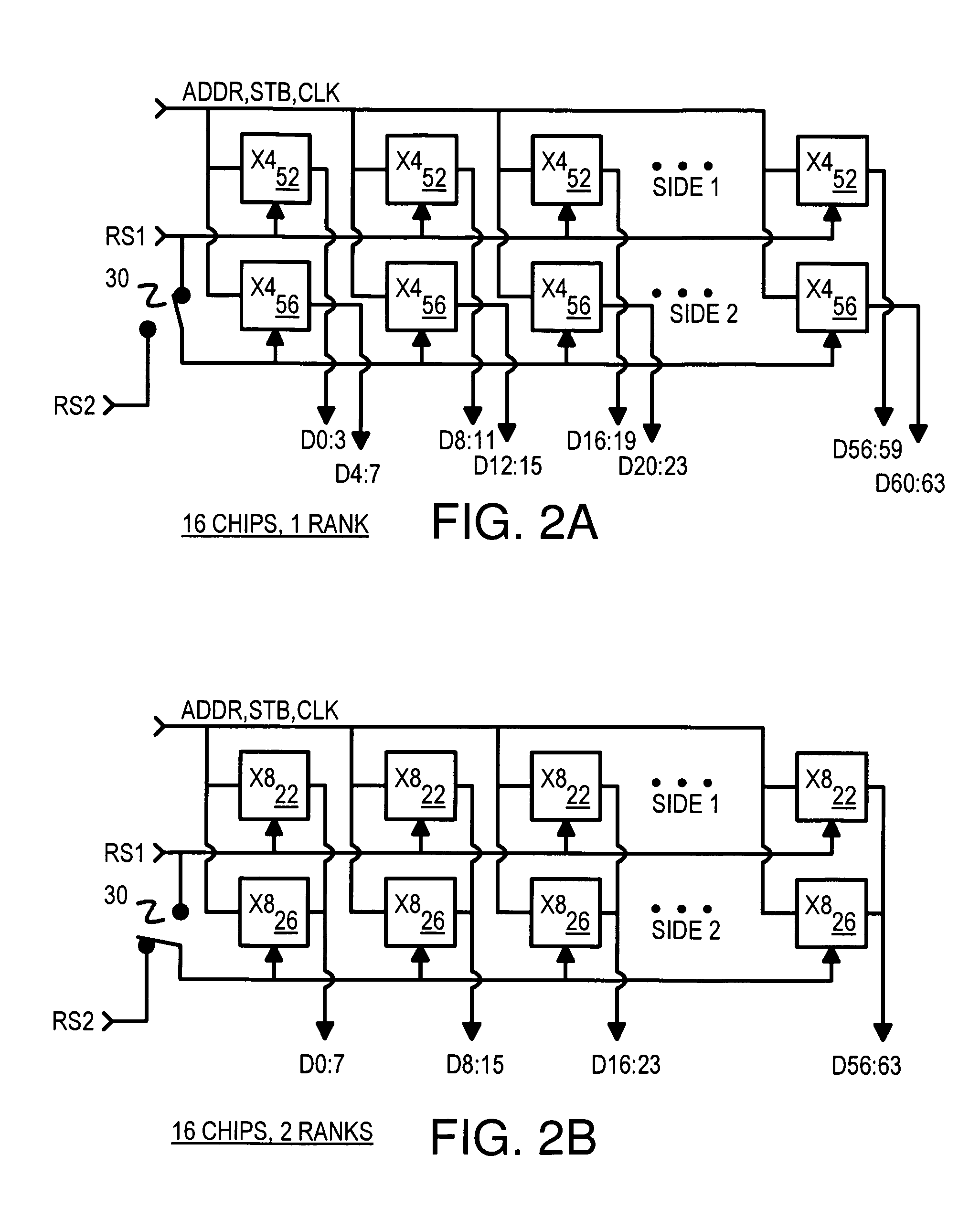

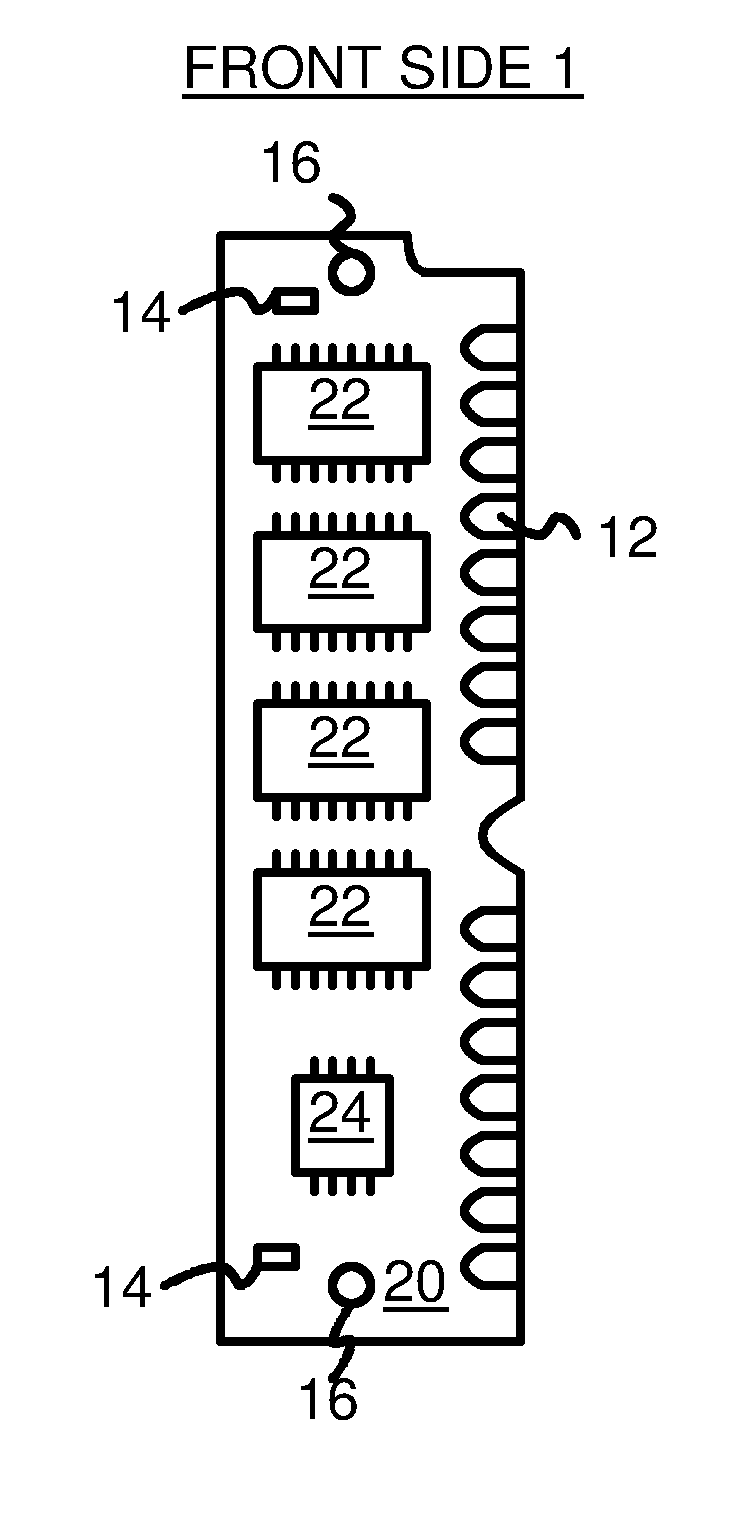

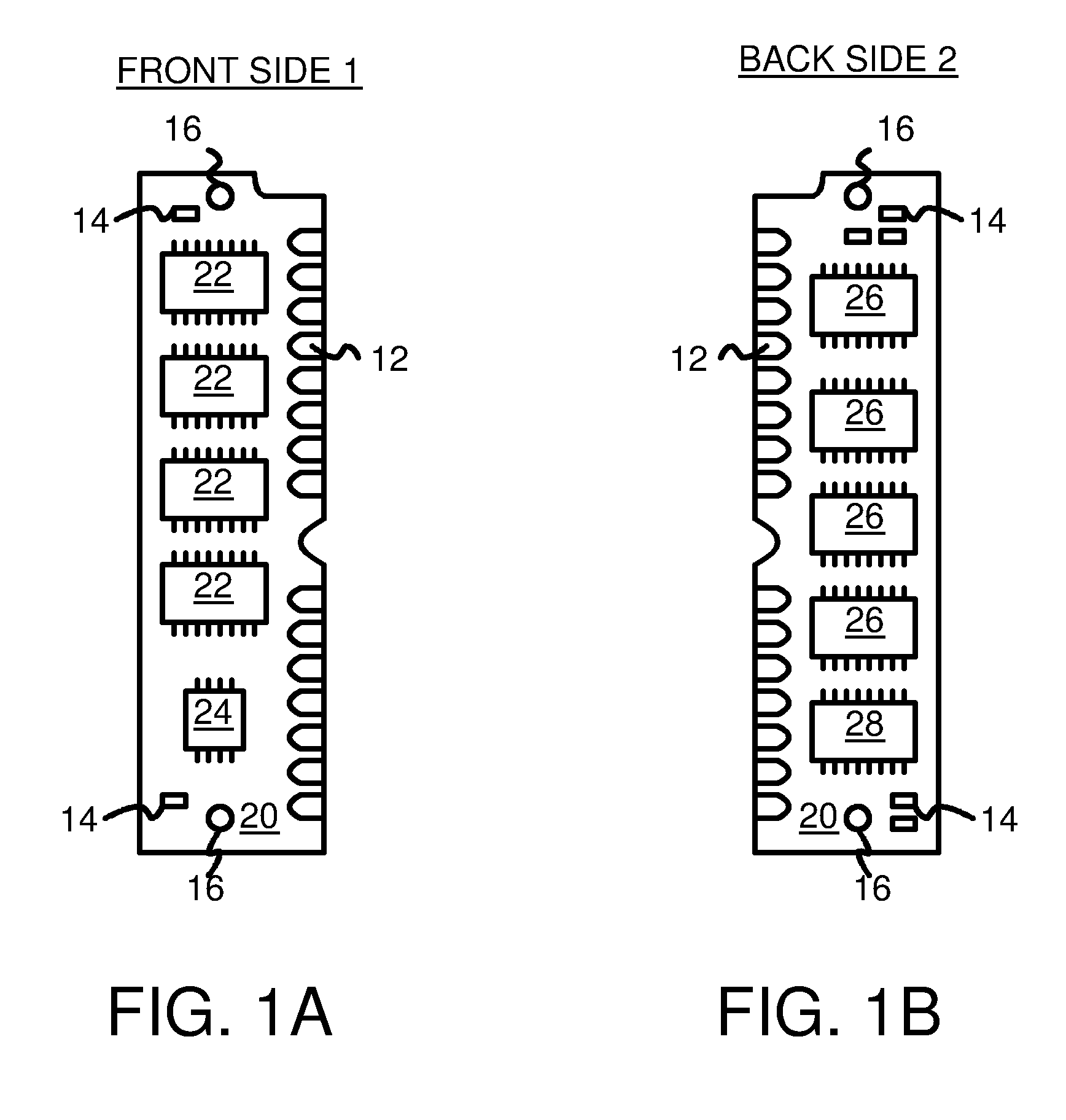

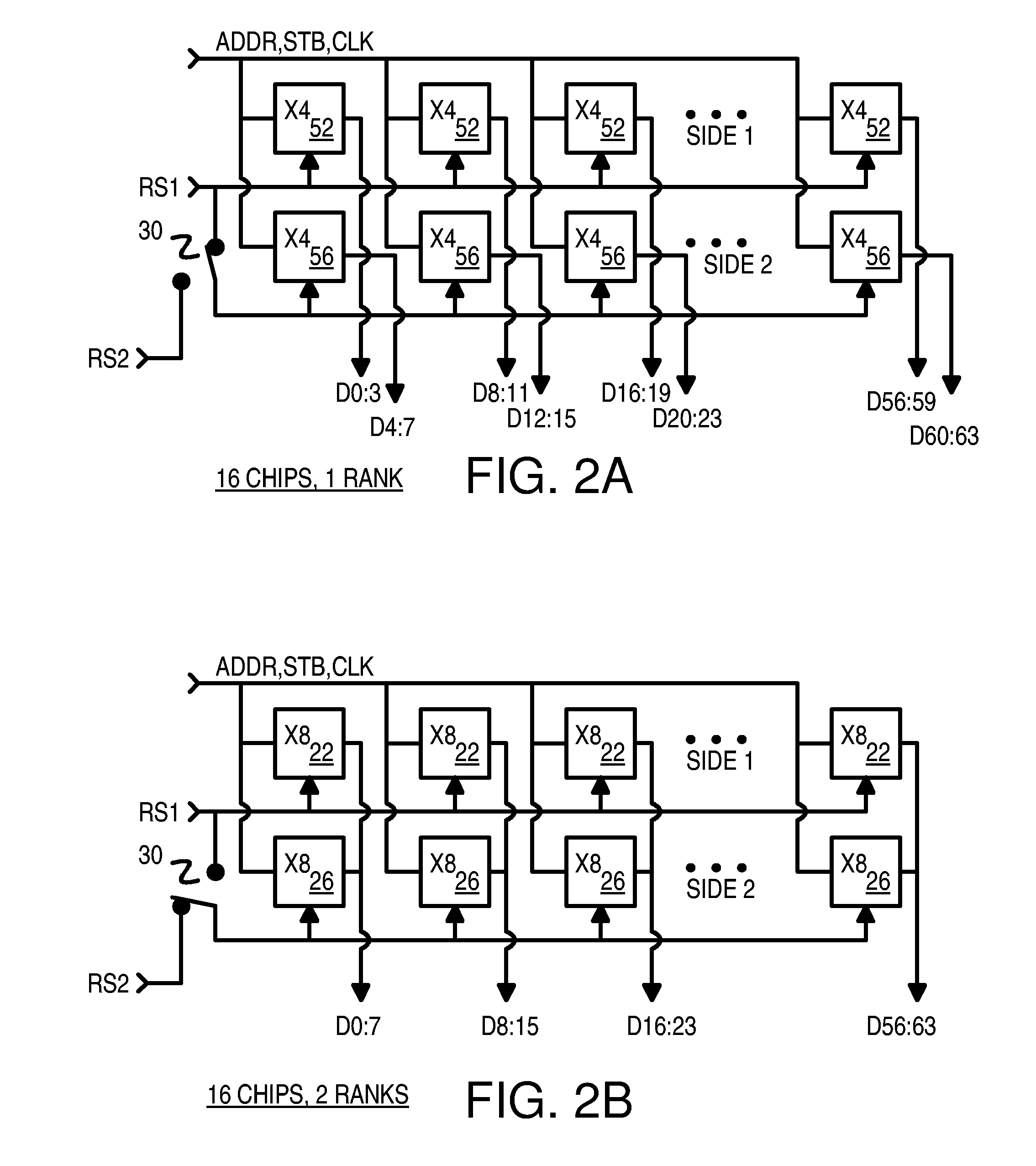

Memory-module board layout for use with memory chips of different data widths

A memory module substrate printed-circuit board (PCB) has multi-type footprints and an edge connector for mating with a memory module socket on a motherboard. Two or more kinds of dynamic-random-access memory (DRAM) chips with different data I / O widths can be soldered to solder pads around the multi-type footprints. When ×4 DRAM chips with 4 data I / O pins are soldered over the multi-type footprints, the memory module has a rank-select signal that drives chip-select inputs to all DRAM chips. When ×8 DRAM chips with 8 data I / O pins are soldered over the multi-type footprints, the memory module has two rank-select signals. One rank-select drives chip-select inputs to front-side DRAM chips while the second rank-select drives chip-select inputs to back-side DRAM chips. Wiring traces on the PCB cross-over data nibbles between the solder pads and the connector to allow two ×4 chips to drive a byte driven by only one ×8 chip.

Owner:KINGSTON DIGITAL CO LTD

Memory-Module Board Layout for Use With Memory Chips of Different Data Widths

ActiveUS20060267172A1Final product manufactureSemiconductor/solid-state device detailsMemory chipNibble

A memory module substrate printed-circuit board (PCB) has multi-type footprints and an edge connector for mating with a memory module socket on a motherboard. Two or more kinds of dynamic-random-access memory (DRAM) chips with different data I / O widths can be soldered to solder pads around the multi-type footprints. When ×4 DRAM chips with 4 data I / O pins are soldered over the multi-type footprints, the memory module has a rank-select signal that drives chip-select inputs to all DRAM chips. When ×8 DRAM chips with 8 data I / O pins are soldered over the multi-type footprints, the memory module has two rank-select signals. One rank-select drives chip-select inputs to front-side DRAM chips while the second rank-select drives chip-select inputs to back-side DRAM chips. Wiring traces on the PCB cross-over data nibbles between the solder pads and the connector to allow two ×4 chips to drive a byte driven by only one ×8 chip.

Owner:KINGSTON DIGITAL CO LTD

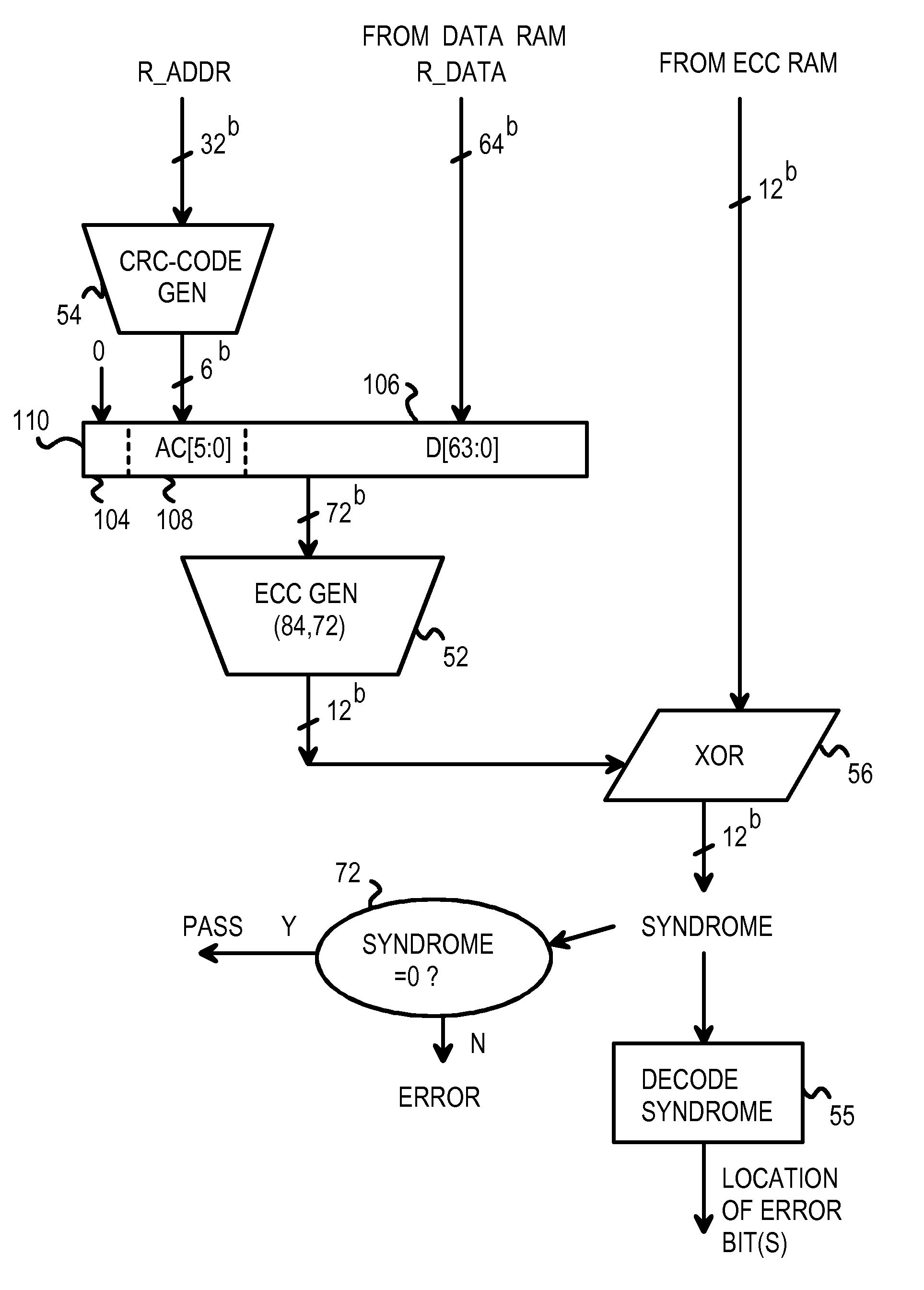

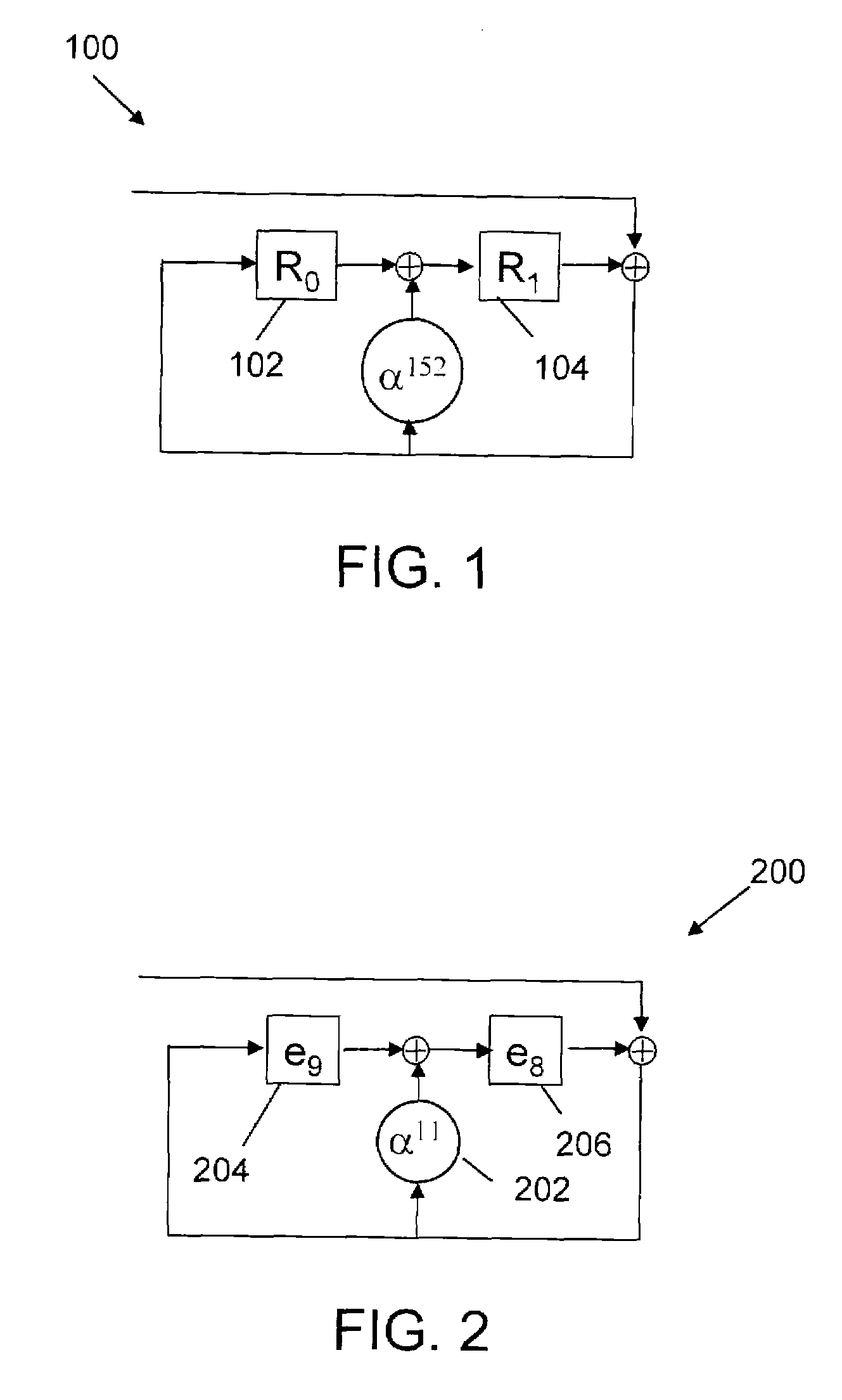

Encoding 64-bit data nibble error correct and cyclic-redundancy code (CRC) address error detect for use on a 76-bit memory module

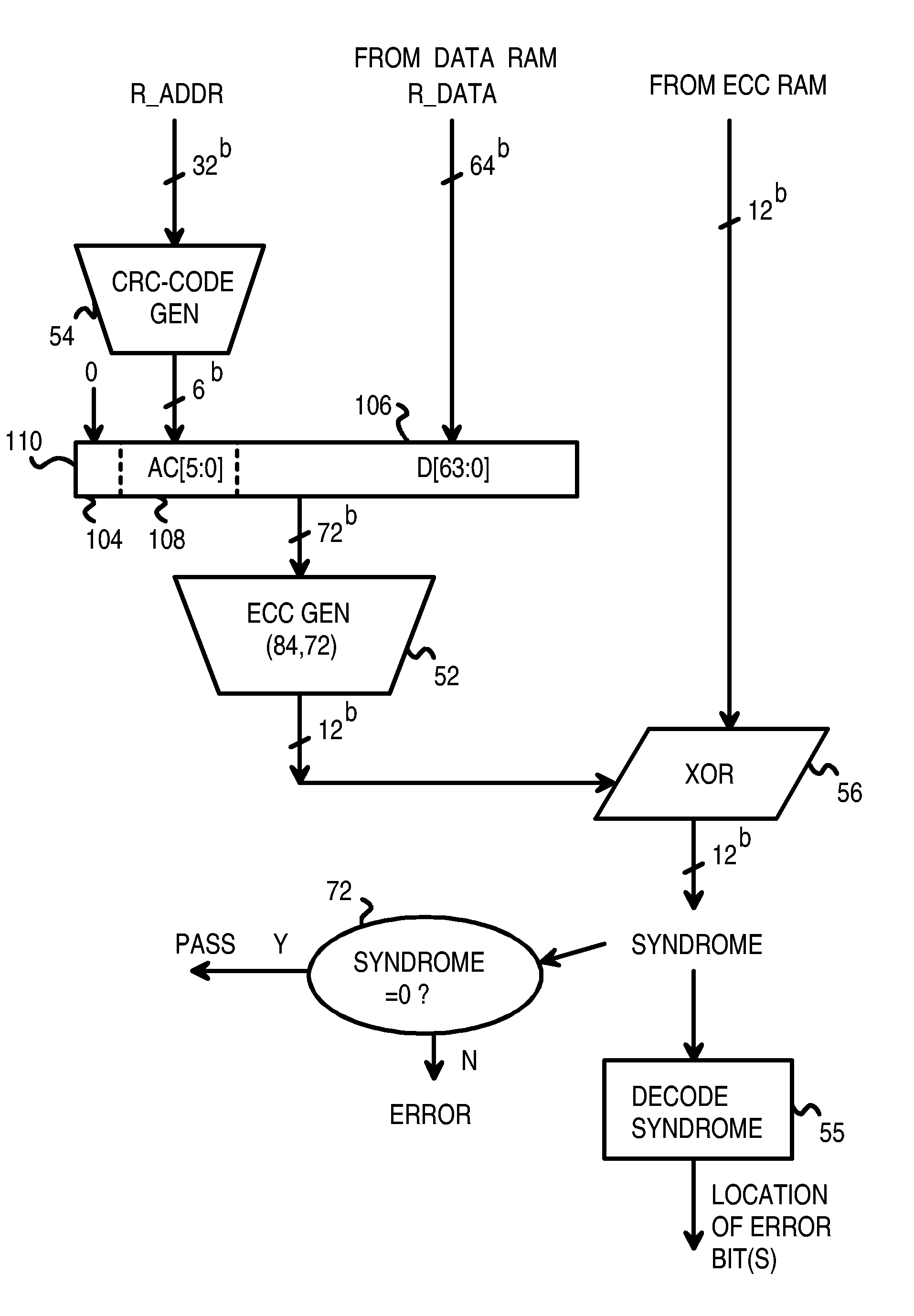

A memory system provides data error detection and correction and address error detection. A cyclical-redundancy-check (CRC) code generates address check bits. A 32-bit address is compressed to 6 address check bits using the CRC code. The 6 address check bits are concatenated with 64 data bits and 2 flag bits to generate a 72-bit check word. The 72-bit check word is input to an error-correction code (ECC) generator that generates 12 check bits that are stored in memory with the 64 data bits. A 76-bit memory module can store the 64 data and 12 check bits. Nibble errors can be corrected, and all nibble+1 bit errors can be detected. Also, a 6-bit error in a sequence of bits can be detected. This allows all errors in the 6-bit CRC of the address to be detected. The CRC code and ECC are ideal for detecting double-bit errors common with multiplexed-address DRAMs.

Owner:AZUL SYSTEMS

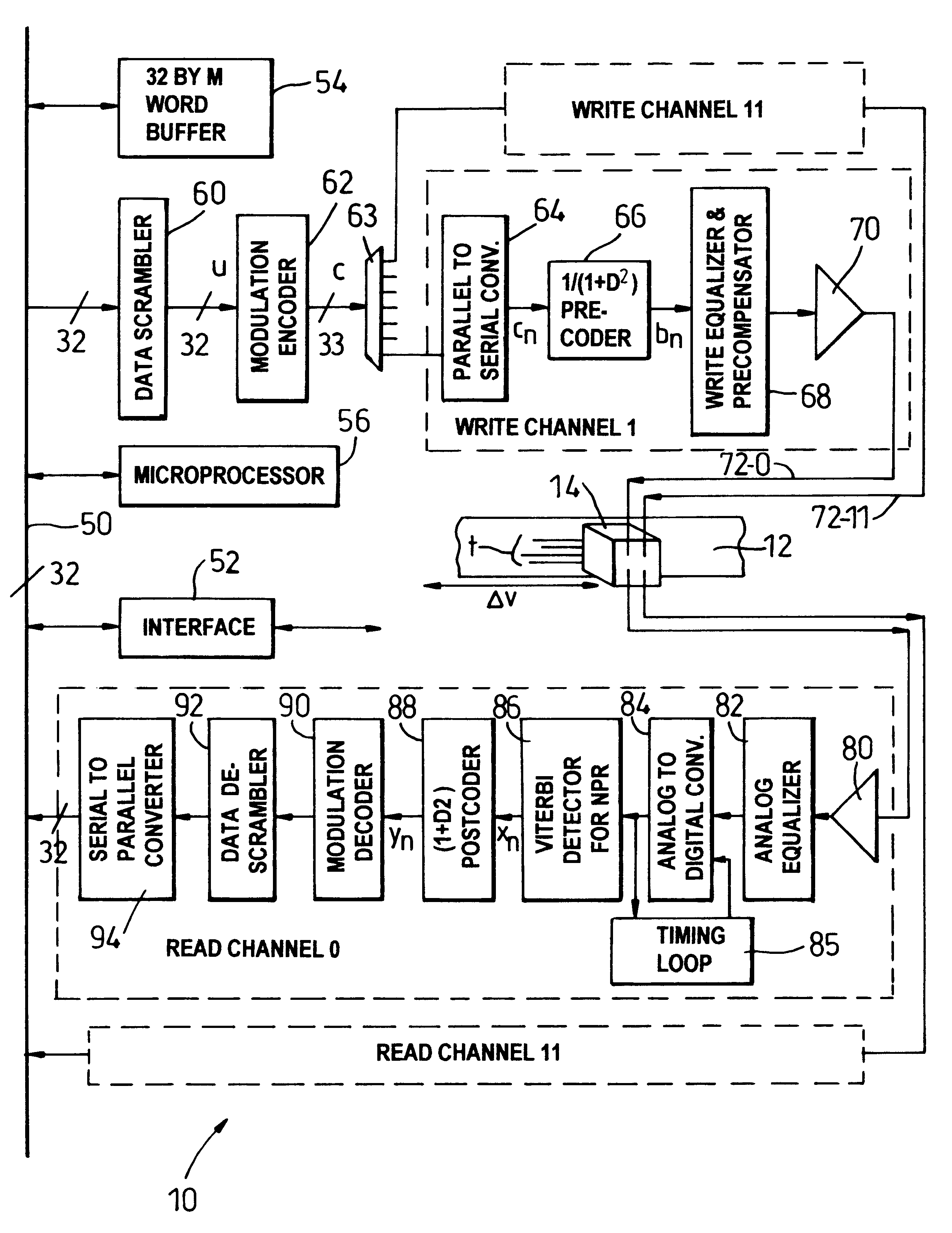

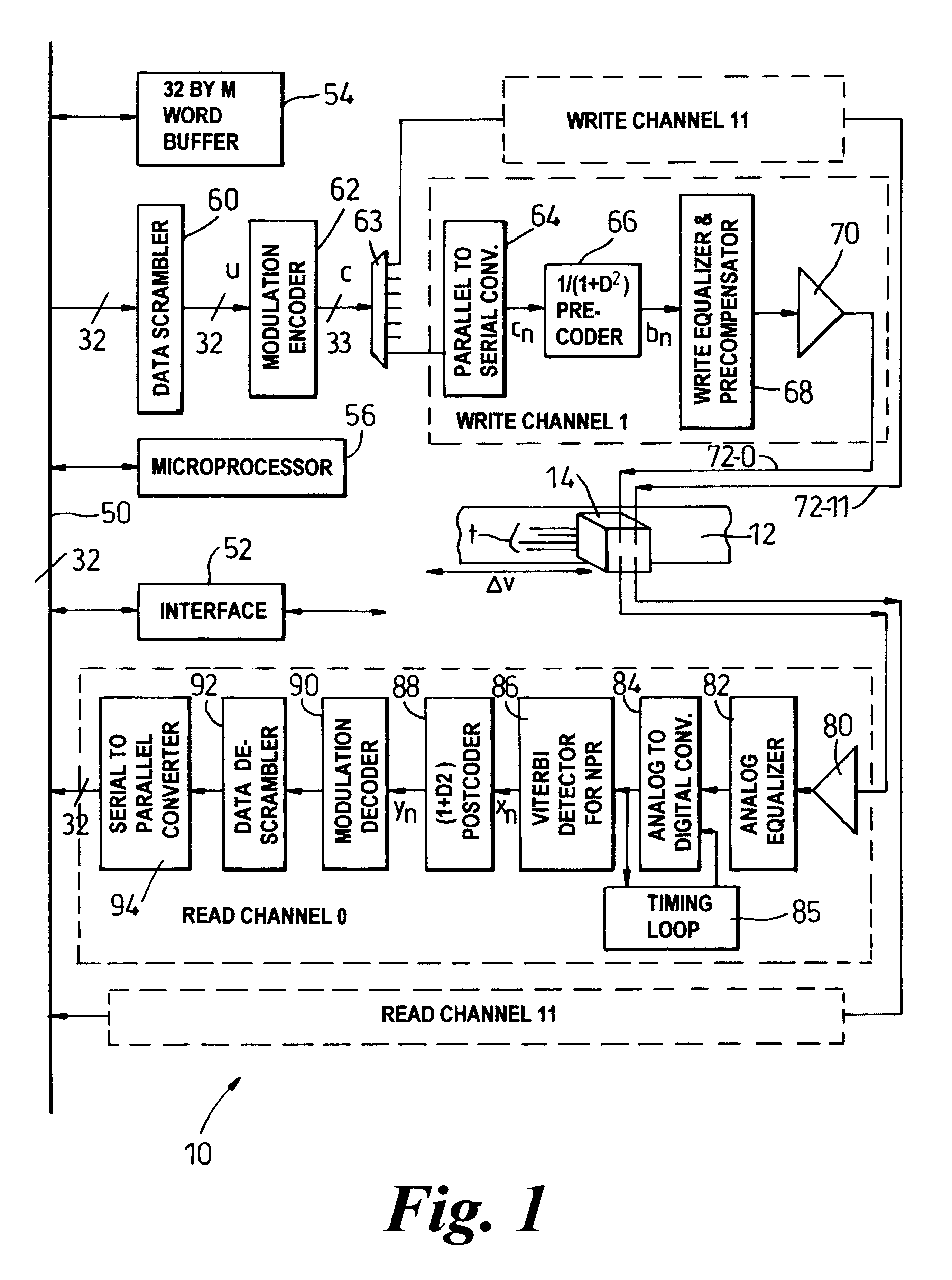

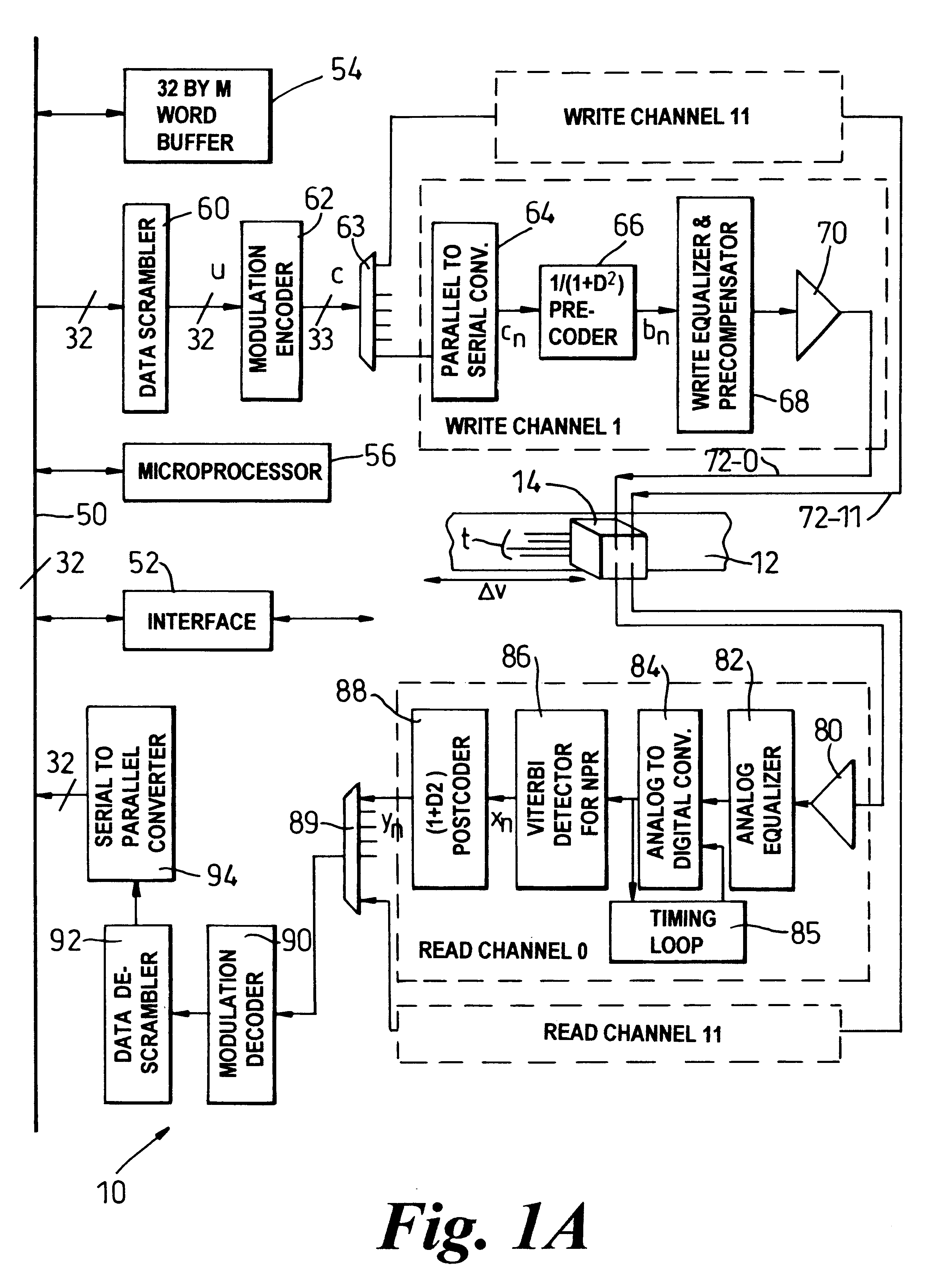

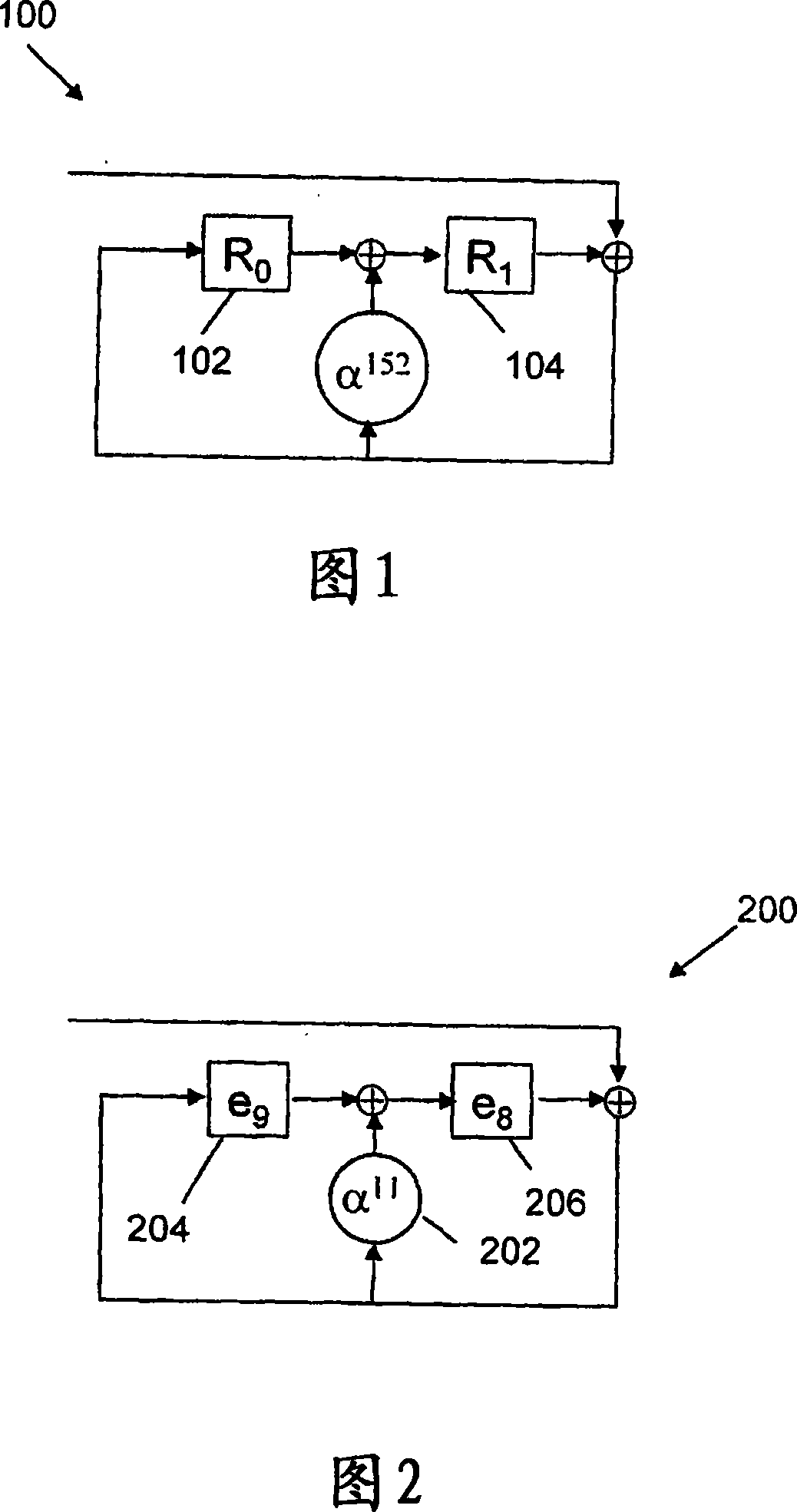

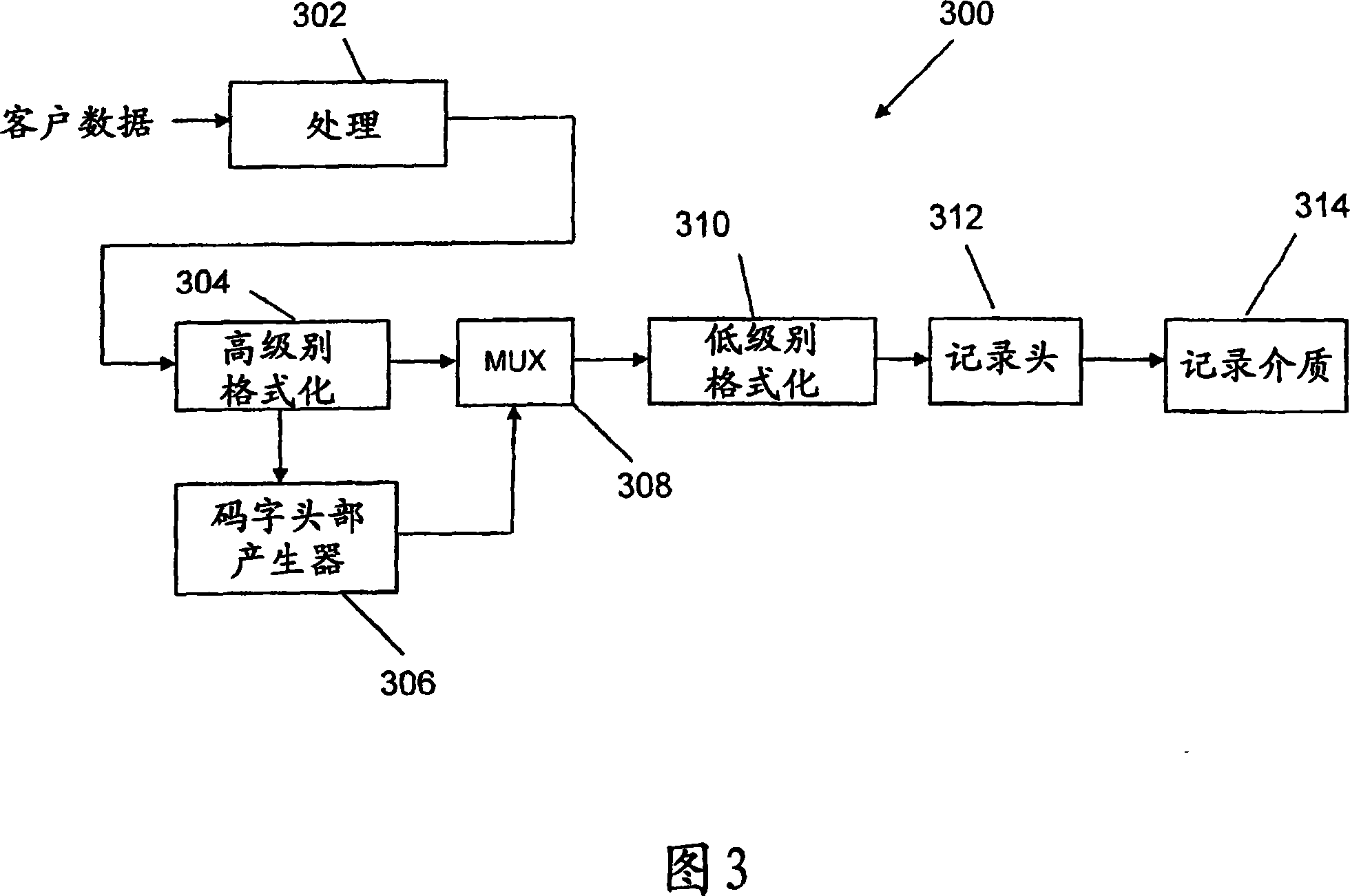

Rate 32/33 (D=0, K=6) run length limited modulation code having optimized error propagation

InactiveUS6184806B1High bit rateSimplified and reliable encodingModification of read/write signalsRecord information storageDigital dataMagnetic media

A method and apparatus for encoding a sequence of 32 bit digital data words into a sequence of 33 bit code words in consonance with predetermined minimum zero run length (d) and predetermined maximum zero run length (k) for recording upon a magnetic medium within a magnetic recording channel is disclosed. The method comprises steps of dividing each data word into eight data nibbles, determining whether any data nibble contains all zeros. If no code violation, mapping the eight data nibbles to seven code nibbles and to four bits of a five bit code sub-word and setting a fifth control bit to one. If one or more code violations are present, embedding code violation locations within at least the five bit code sub-word and other code nibbles if necessary and remapping data nibbles ordinarily directed to the code sub-word and nibble locations to code locations otherwise containing the data nibbles determined to be code violations.

Owner:QUANTUM CORP

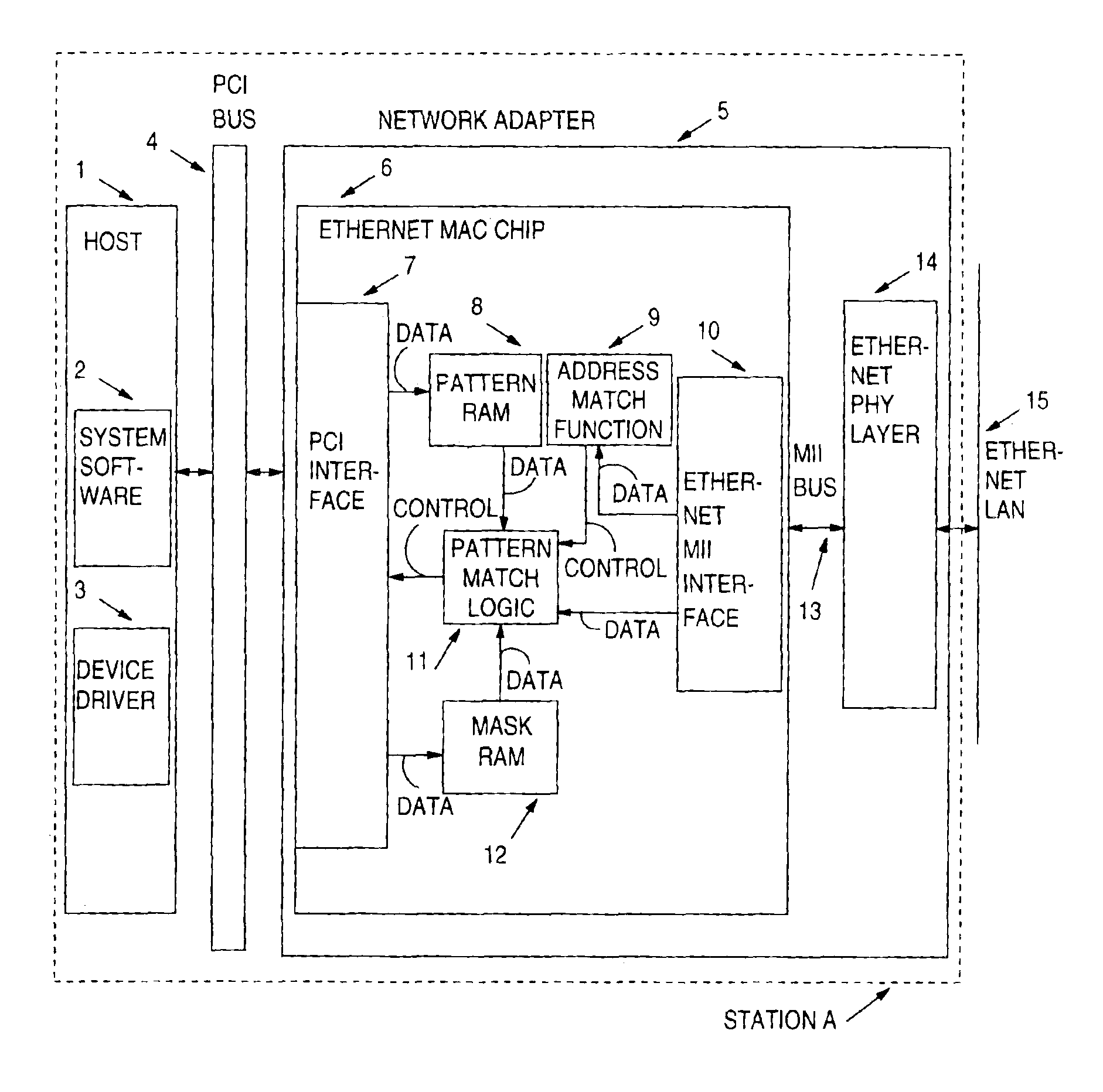

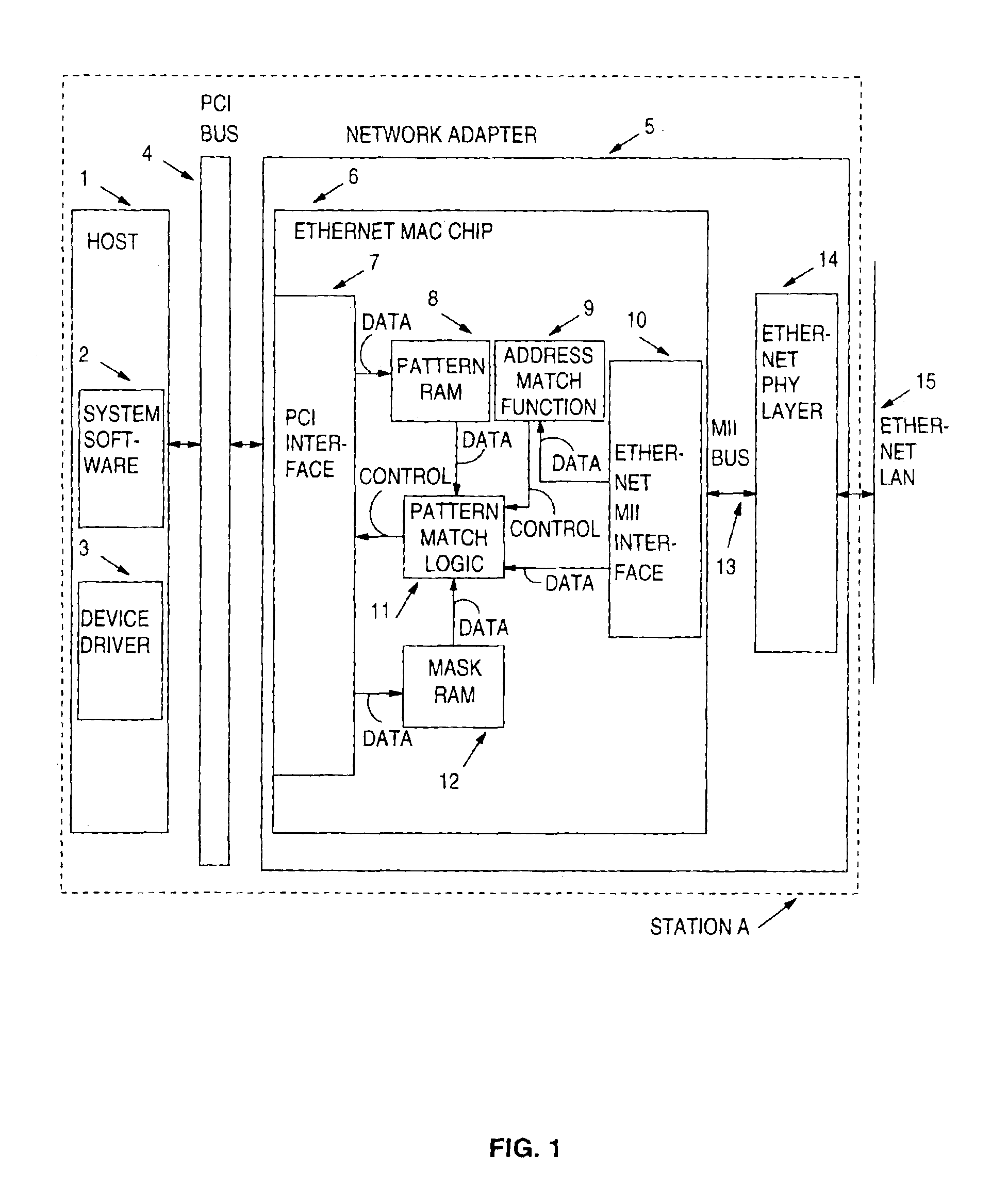

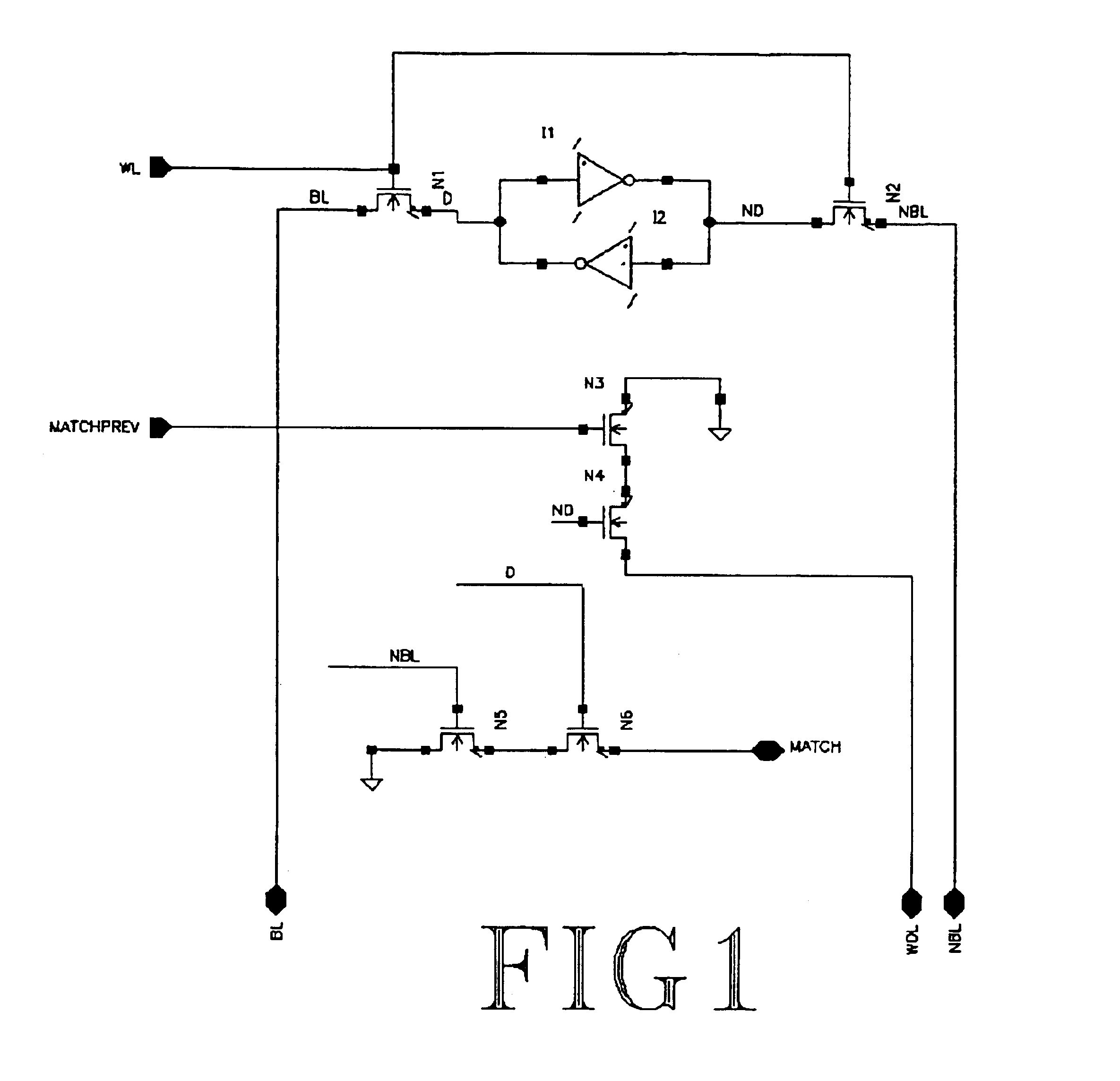

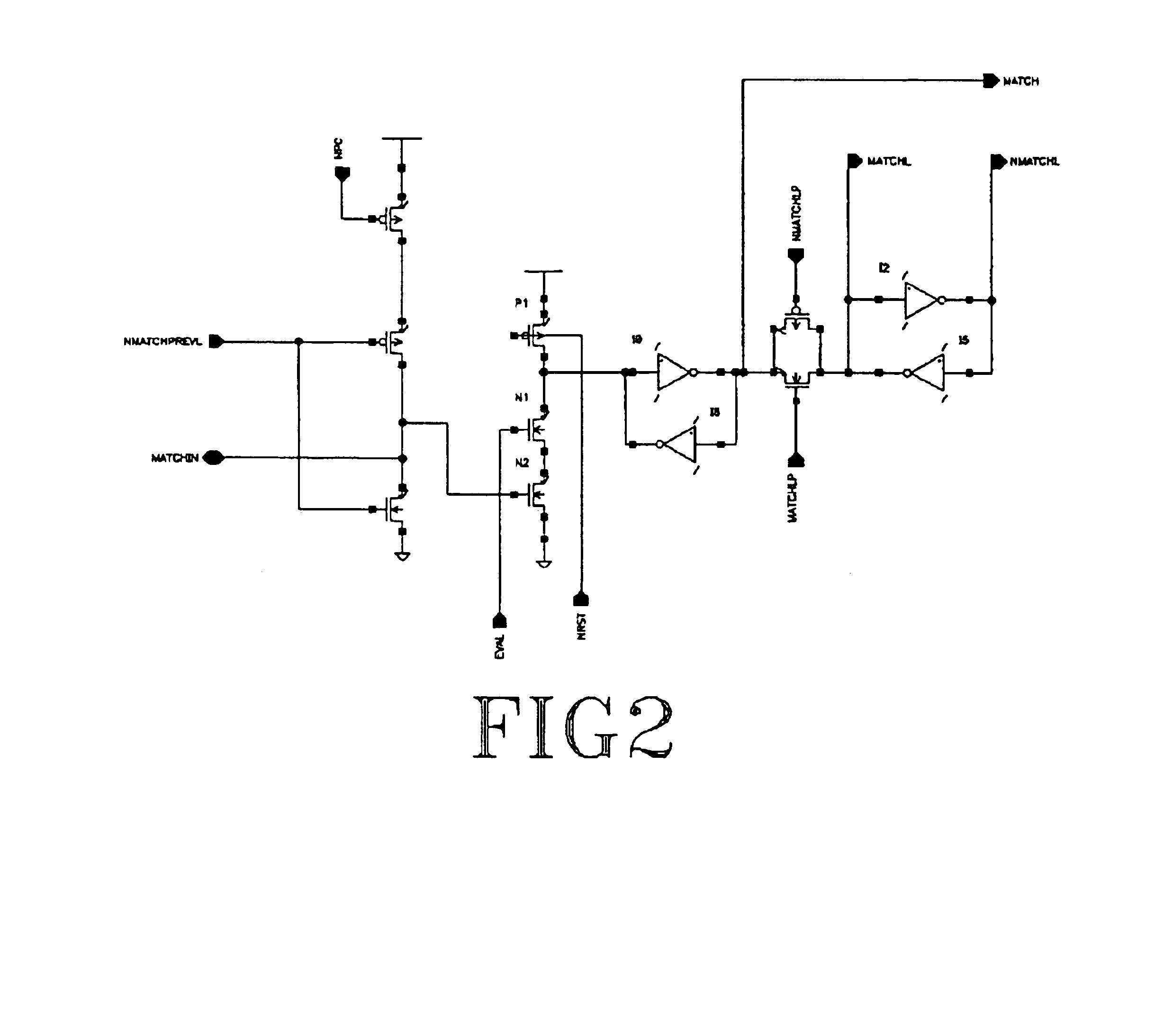

Pattern matching in communications network where first memory stores set of patterns, and second memory stores mask data identifying patterns in the first memory

InactiveUS6938040B2Energy efficient ICTDigital data processing detailsTelecommunicationsPattern matching

Stations in a communications network are awakened by matching a pattern received from the communications network with patterns in the stations. When a match occurs, the stations are awakened. The patterns are arranged contiguously on word boundaries. A nibble (4 bits) in a mask word identifies the part of the pattern word to be used in the comparison.

Owner:IBM CORP

Formatting packet headers in a communications adapter

InactiveUS20050078708A1Fast communicationCloser ”Time-division multiplexData switching by path configurationInternal memoryNibble

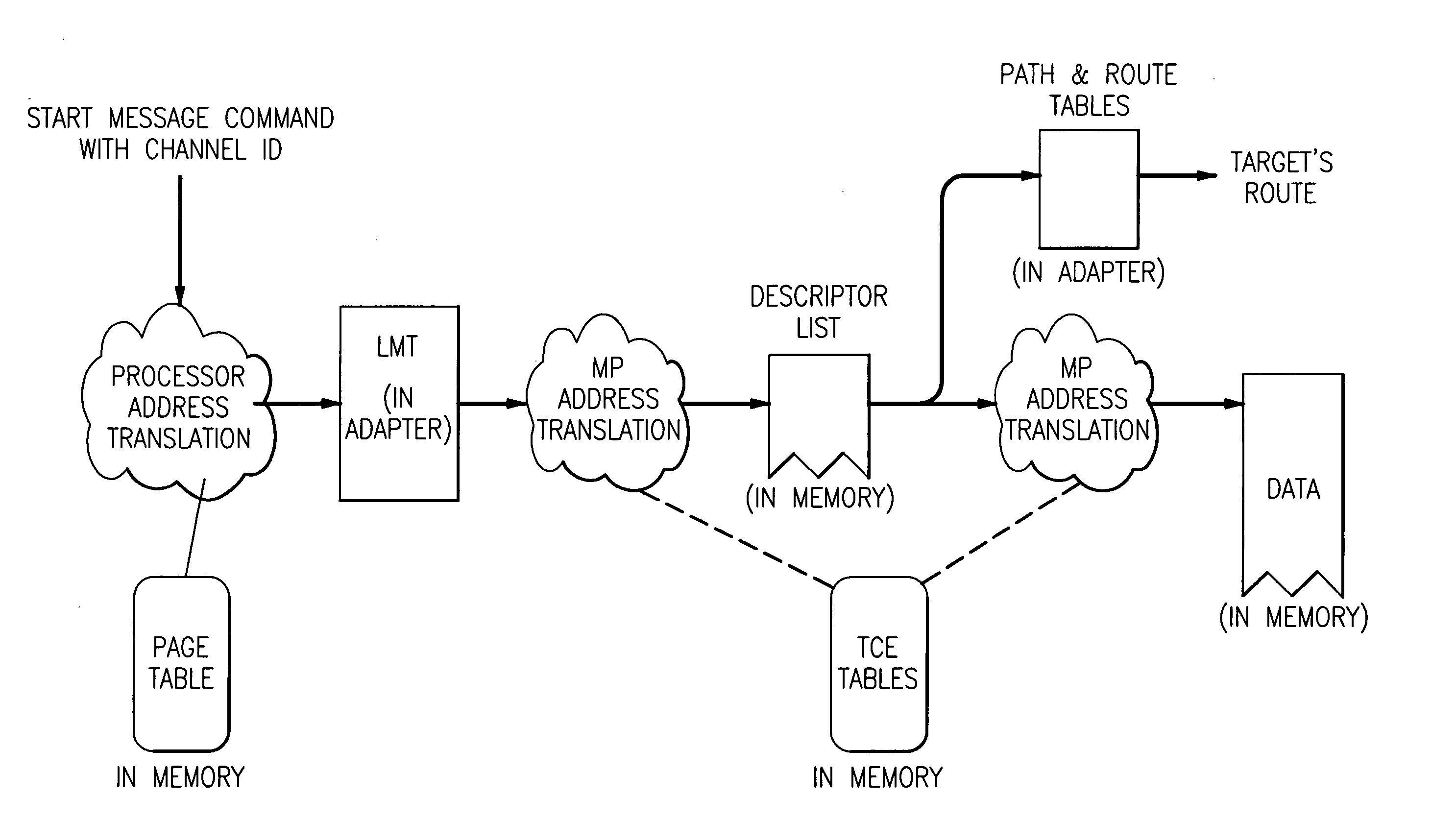

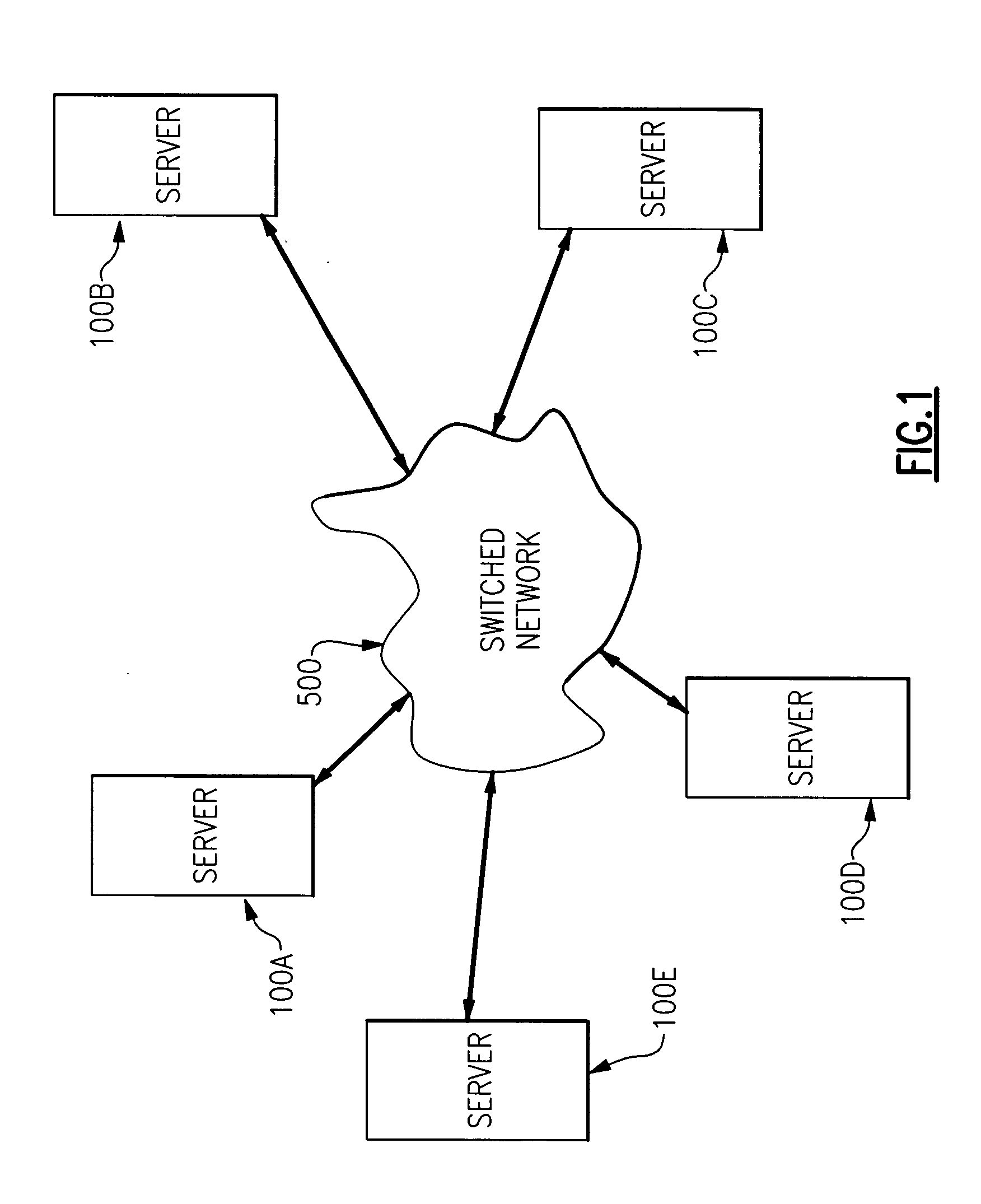

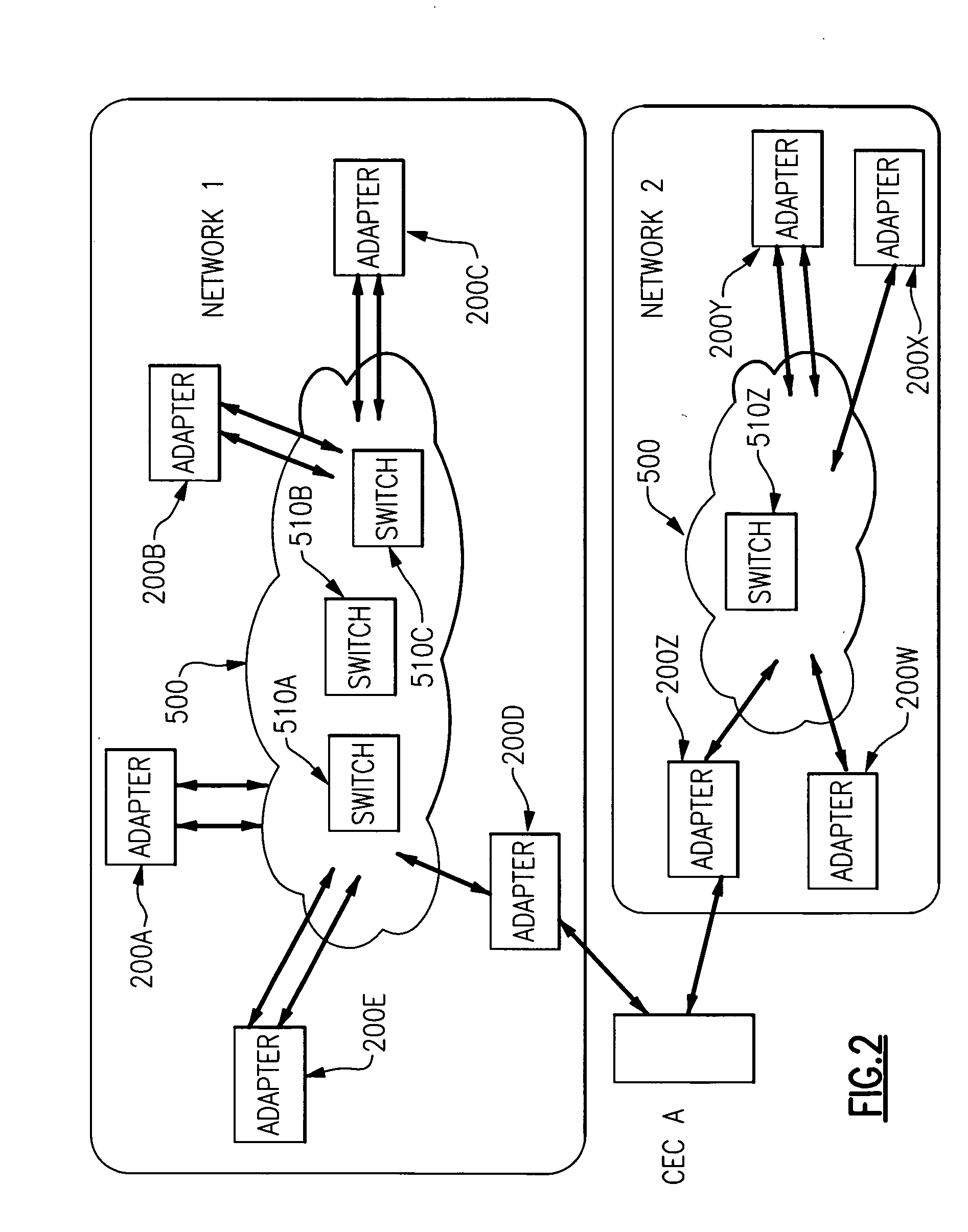

A system and method are provided in which message packet header information is rapidly formatted via communications adapter hardware using script commands supplied from the internal memory of the adapter. The formatter gathers specified header information and reassembles into appropriately positioned nibbles and bytes.

Owner:IBM CORP

Subsystem and Method for Encoding 64-bit Data Nibble Error Correct and Cyclic-Redundancy Code (CRC) Address Error Detect for Use in a 76-bit Memory Module

A memory system provides data error detection and correction and address error detection. A cyclical-redundancy-check (CRC) code generates address check bits. A 32-bit address is compressed to 6 address check bits using the CRC code. The 6 address check bits are concatenated with 64 data bits and 2 flag bits to generate a 72-bit check word. The 72-bit check word is input to an error-correction code (ECC) generator that generates 12 check bits that are stored in memory with the 64 data bits. A 76-bit memory module can store the 64 data and 12 check bits. Nibble errors can be corrected, and all nibble+1 bit errors can be detected. Also, a 6-bit error in a sequence of bits can be detected. This allows all errors in the 6-bit CRC of the address to be detected. The CRC code and ECC are ideal for detecting double-bit errors common with multiplexed-address DRAMs.

Owner:AZUL SYSTEMS

Subsystem and method for encoding 64-bit data nibble error correct and cyclic-redundancy code (CRC) address error detect for use in a 76-bit memory module

A memory system provides data error detection and correction and address error detection. A cyclical-redundancy-check (CRC) code generates address check bits. A 32-bit address is compressed to 6 address check bits using the CRC code. The 6 address check bits are concatenated with 64 data bits and 2 flag bits to generate a 72-bit check word. The 72-bit check word is input to an error-correction code (ECC) generator that generates 12 check bits that are stored in memory with the 64 data bits. A 76-bit memory module can store the 64 data and 12 check bits. Nibble errors can be corrected, and all nibble+1 bit errors can be detected. Also, a 6-bit error in a sequence of bits can be detected. This allows all errors in the 6-bit CRC of the address to be detected. The CRC code and ECC are ideal for detecting double-bit errors common with multiplexed-address DRAMs.

Owner:AZUL SYSTEMS

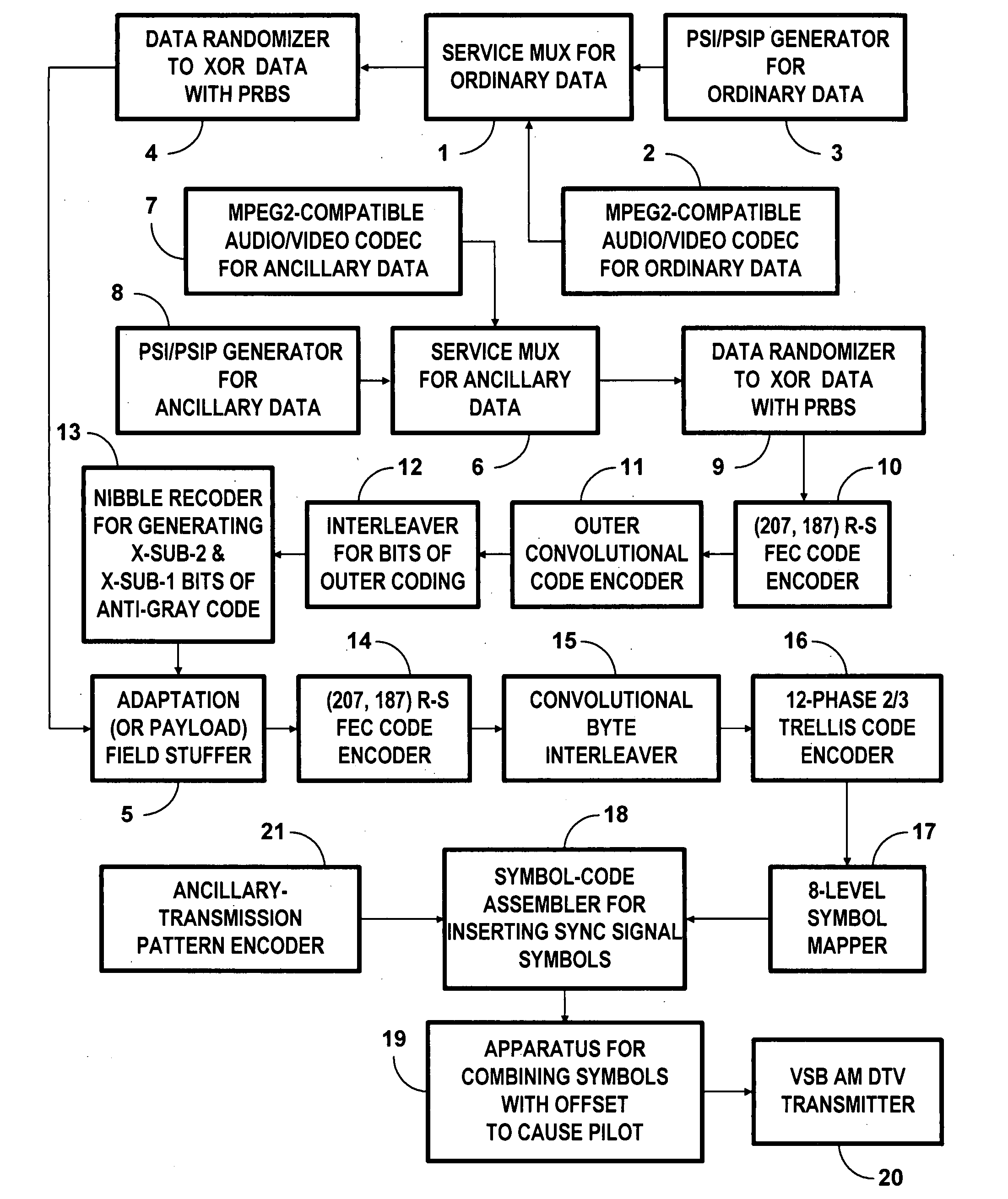

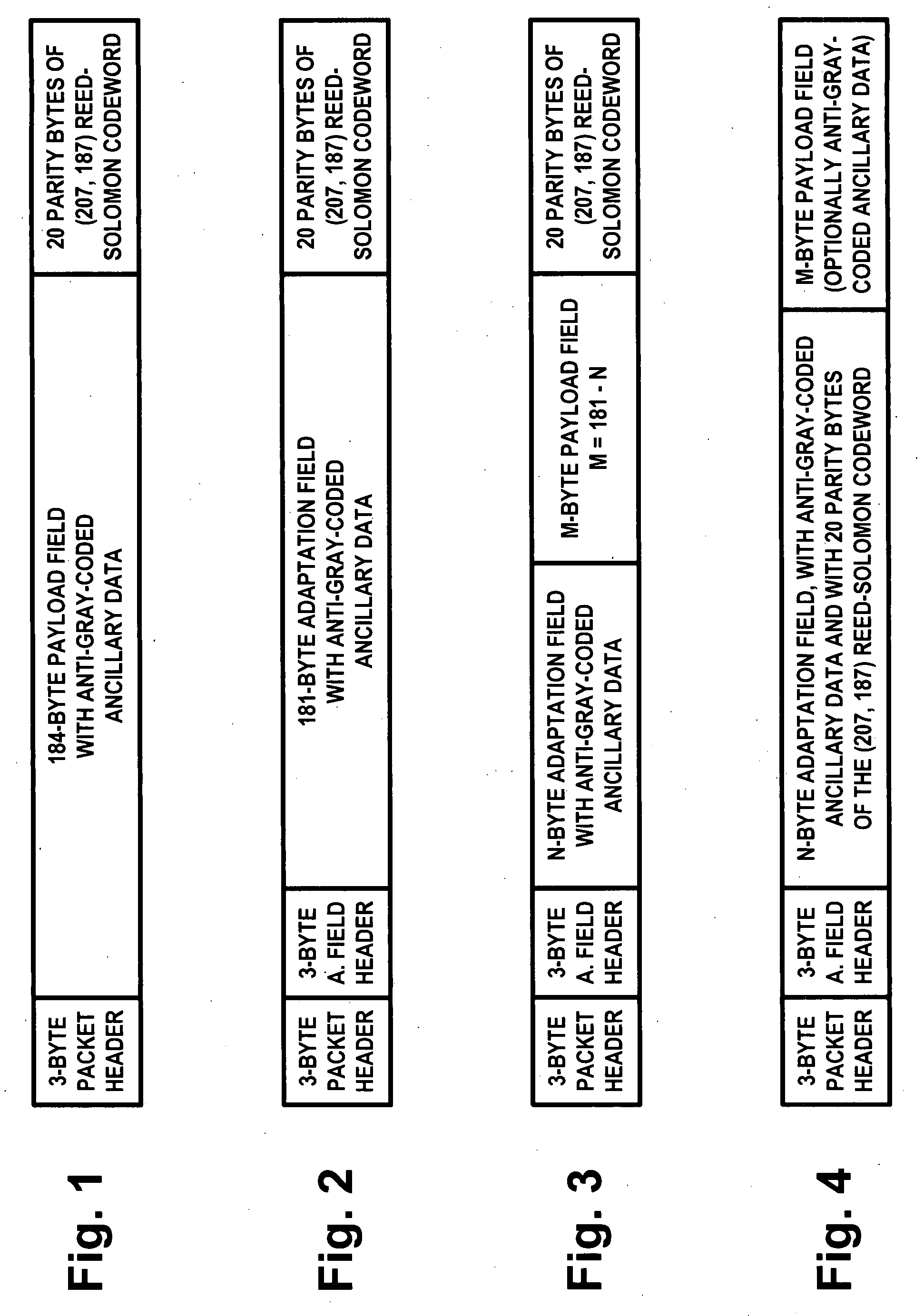

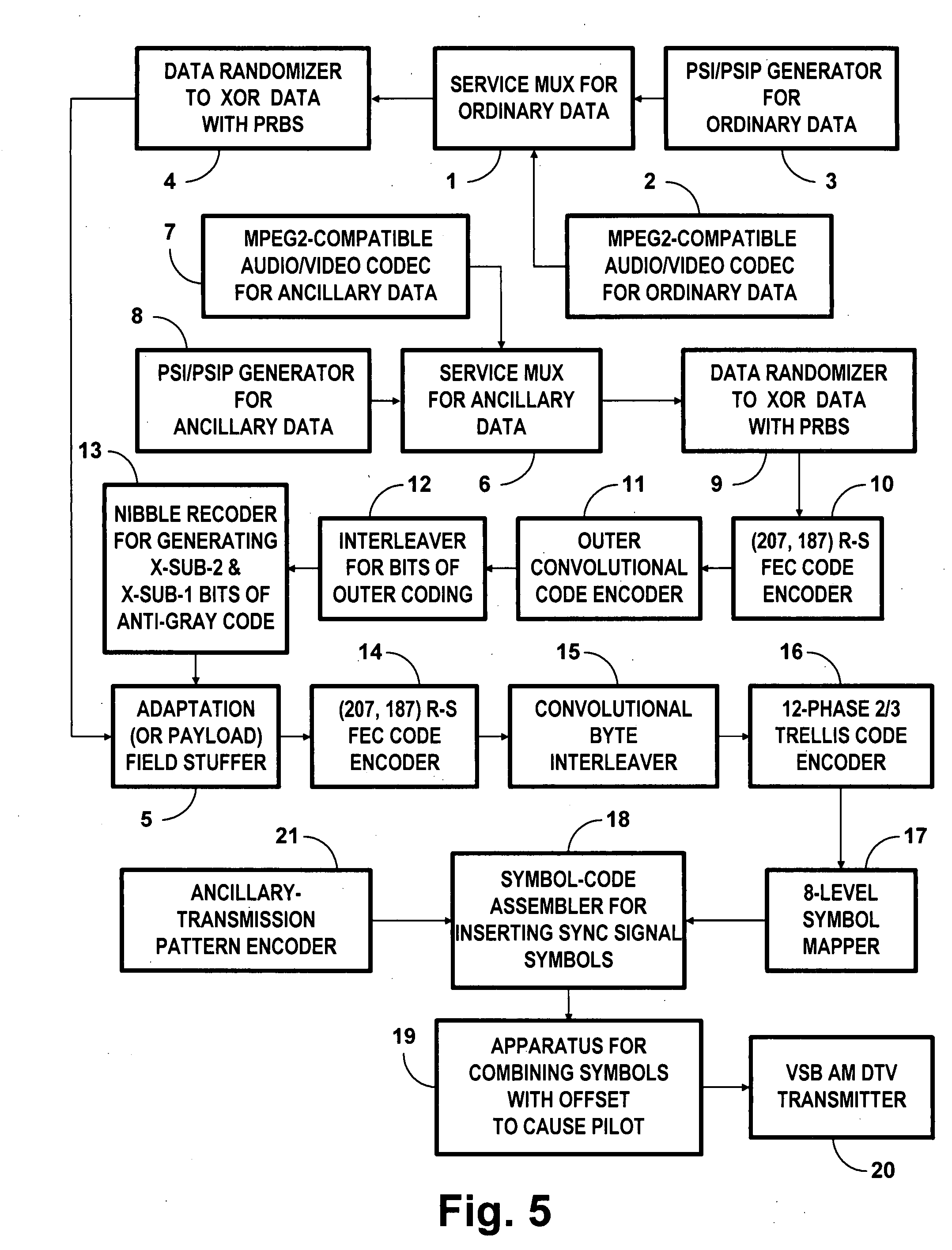

System for digital television broadcasting using modified 2/3 trellis coding

InactiveUS20080112502A1For signal receptionError correction/detection using concatenated codesBroadcast-related systemsNibbleDTV receiver

8VSB-compatible DTV broadcasting that employs outer coding of a sort in which interleaved data and outer coding parity are inner coded by the ⅔ trellis code encoder is improved. This is done by recoding each nibble of the interleaved data and outer coding parity in accordance with an anti-Gray code before being inner coded by the ⅔ trellis code encoder. Accordingly, in the DTV receiver an adjacent-bin error during data slicing may generate a double-bit error in a nibble as received, but this is reduced to a single-bit error after the nibble is recoded in accordance with a Gray coding procedure. In one example of such recoding, 10 and 11 nibbles of the interleaved data and outer coding parity are recoded to 11 and 10 nibbles respectively, but the 00 and 01 nibbles are not recoded. In another example of such recoding, 00 and 01 nibbles of the interleaved data and outer coding parity are recoded to 01 and 00 nibbles respectively, but the 10 and 11 nibbles are not recoded. Eight different types of recoding are possible.

Owner:SAMSUNG ELECTRONICS CO LTD

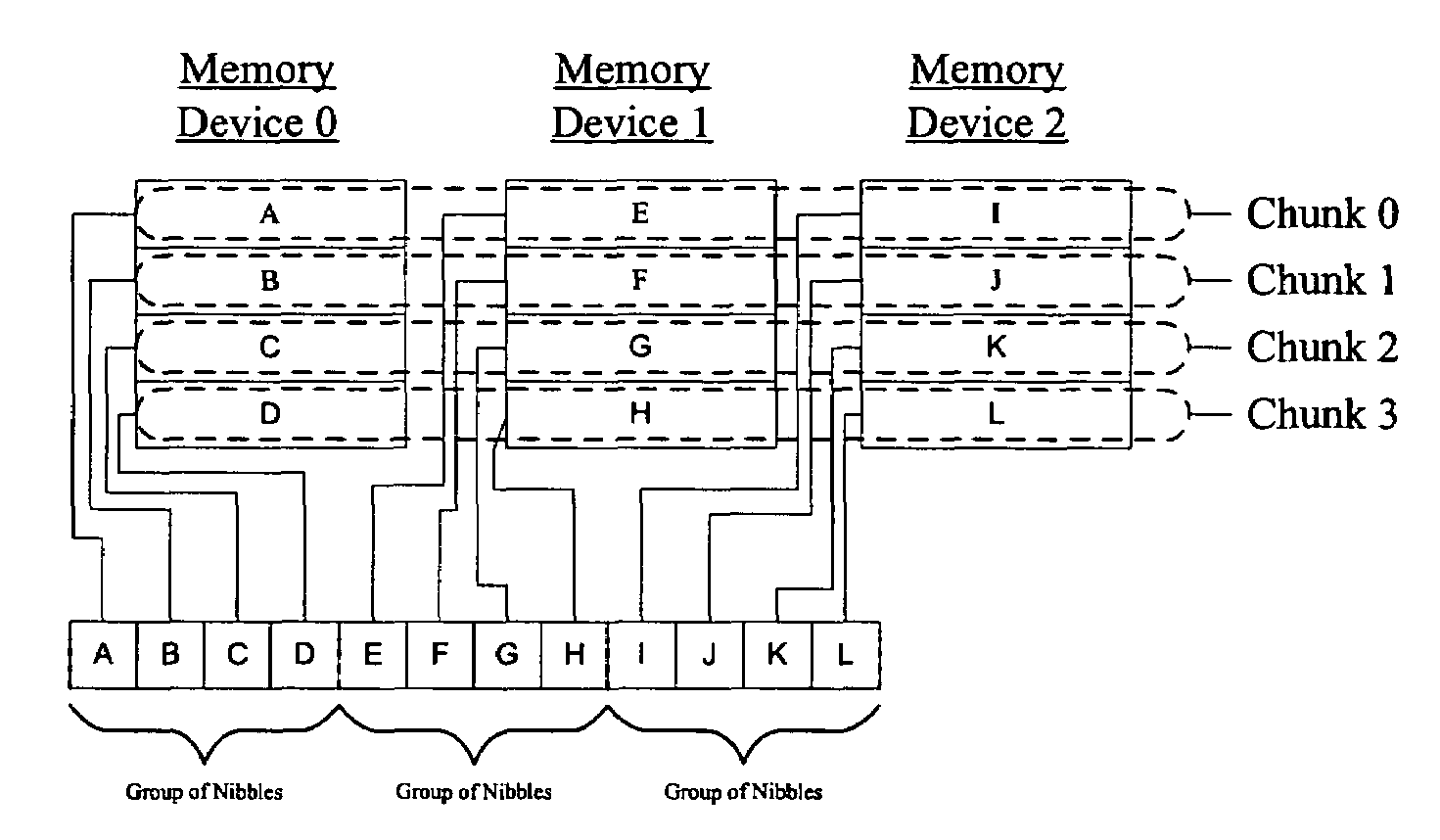

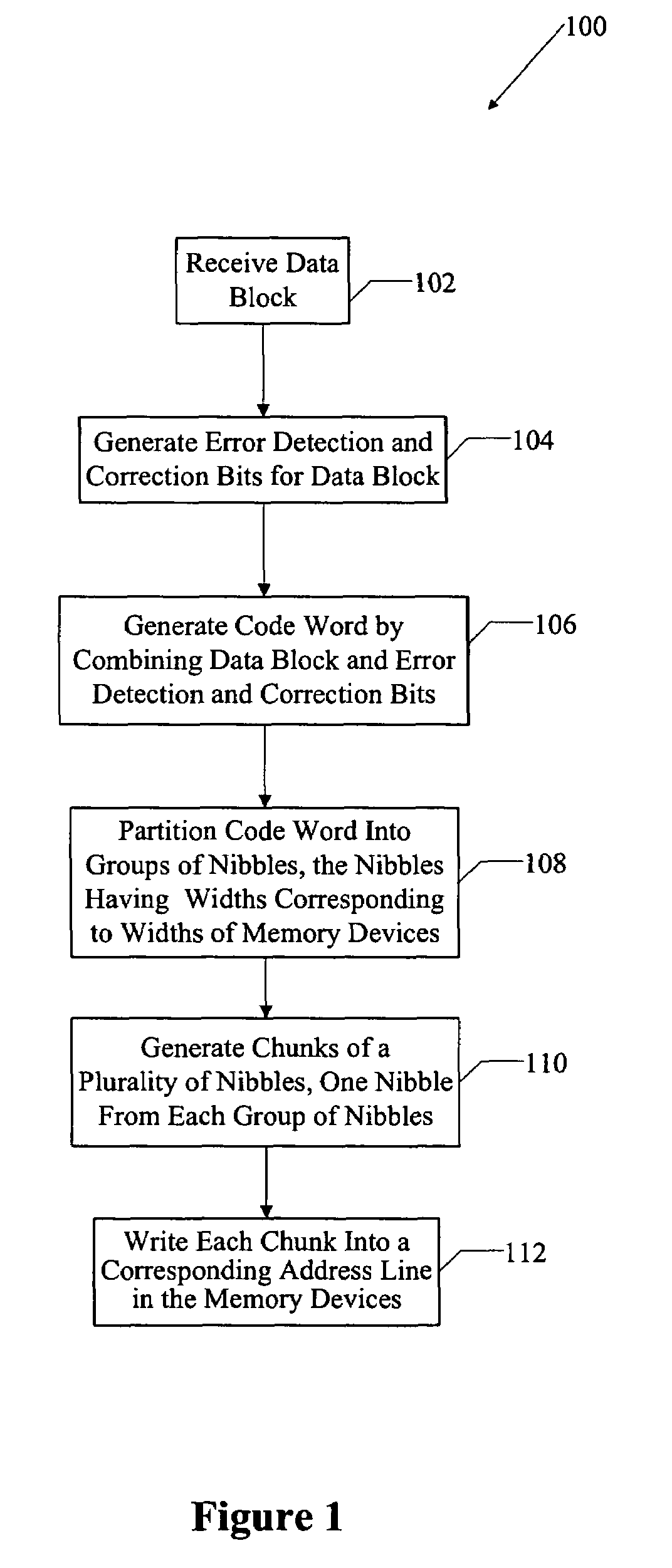

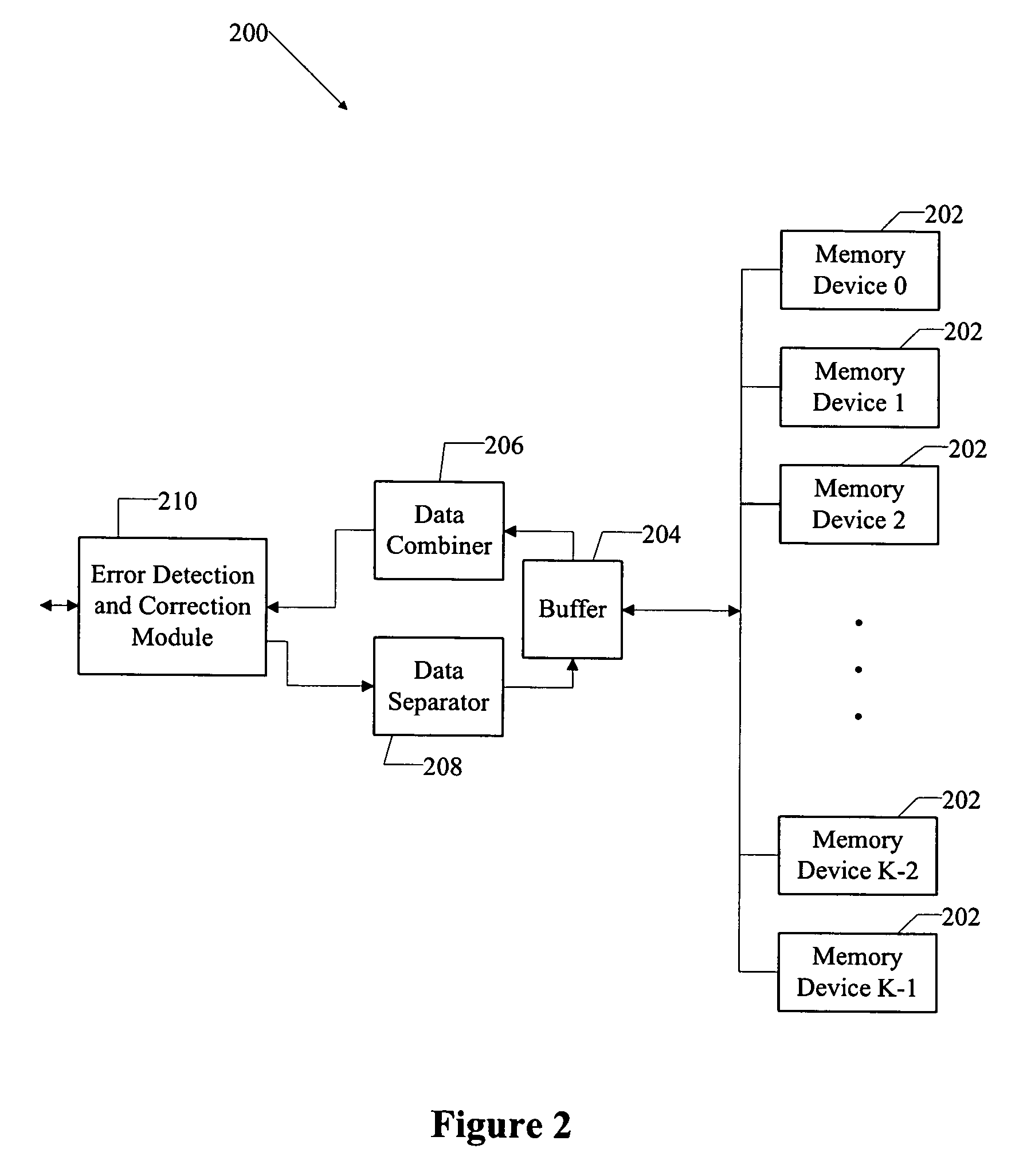

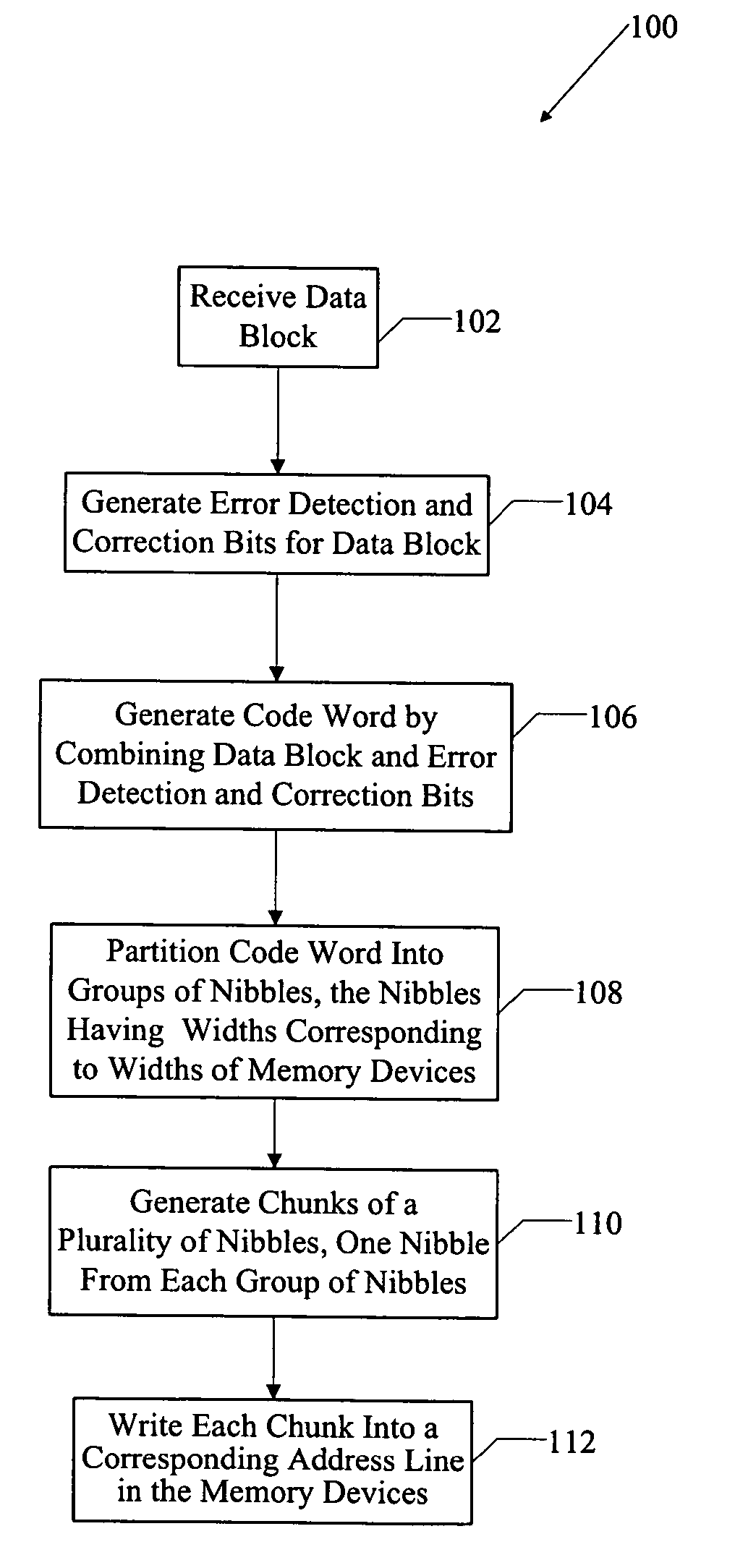

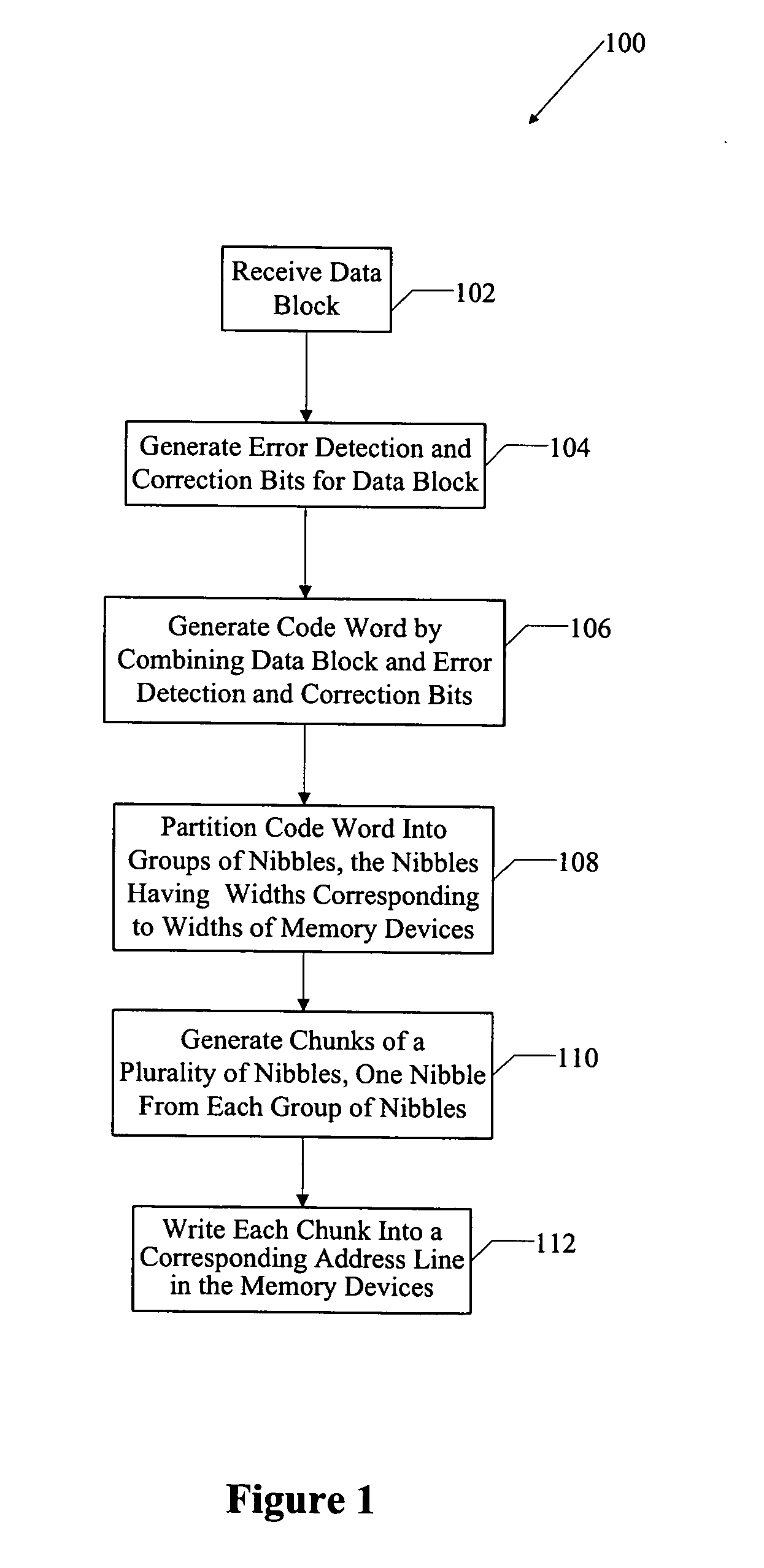

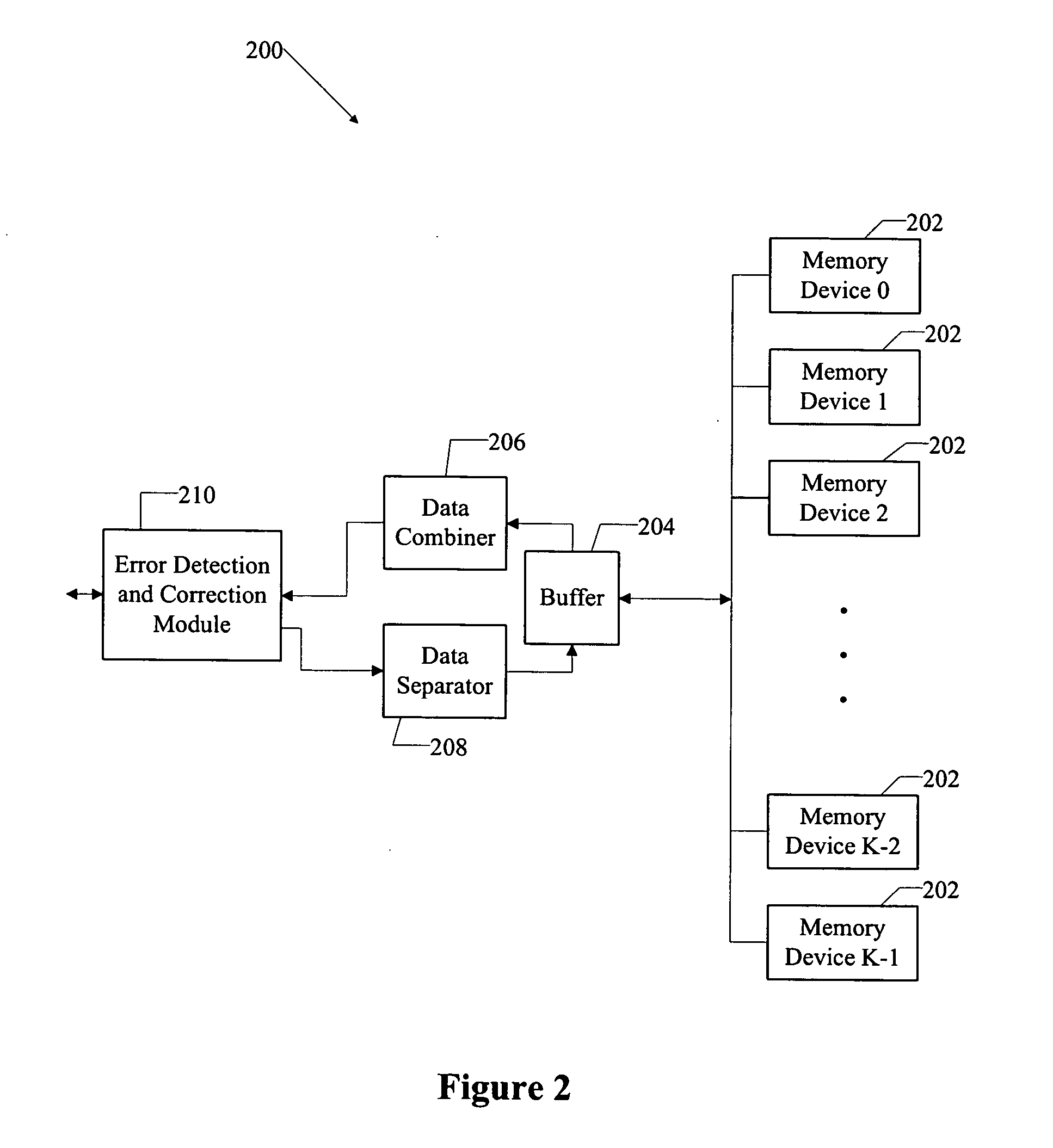

Partitioning data for error correction

Owner:HEWLETT PACKARD DEV CO LP

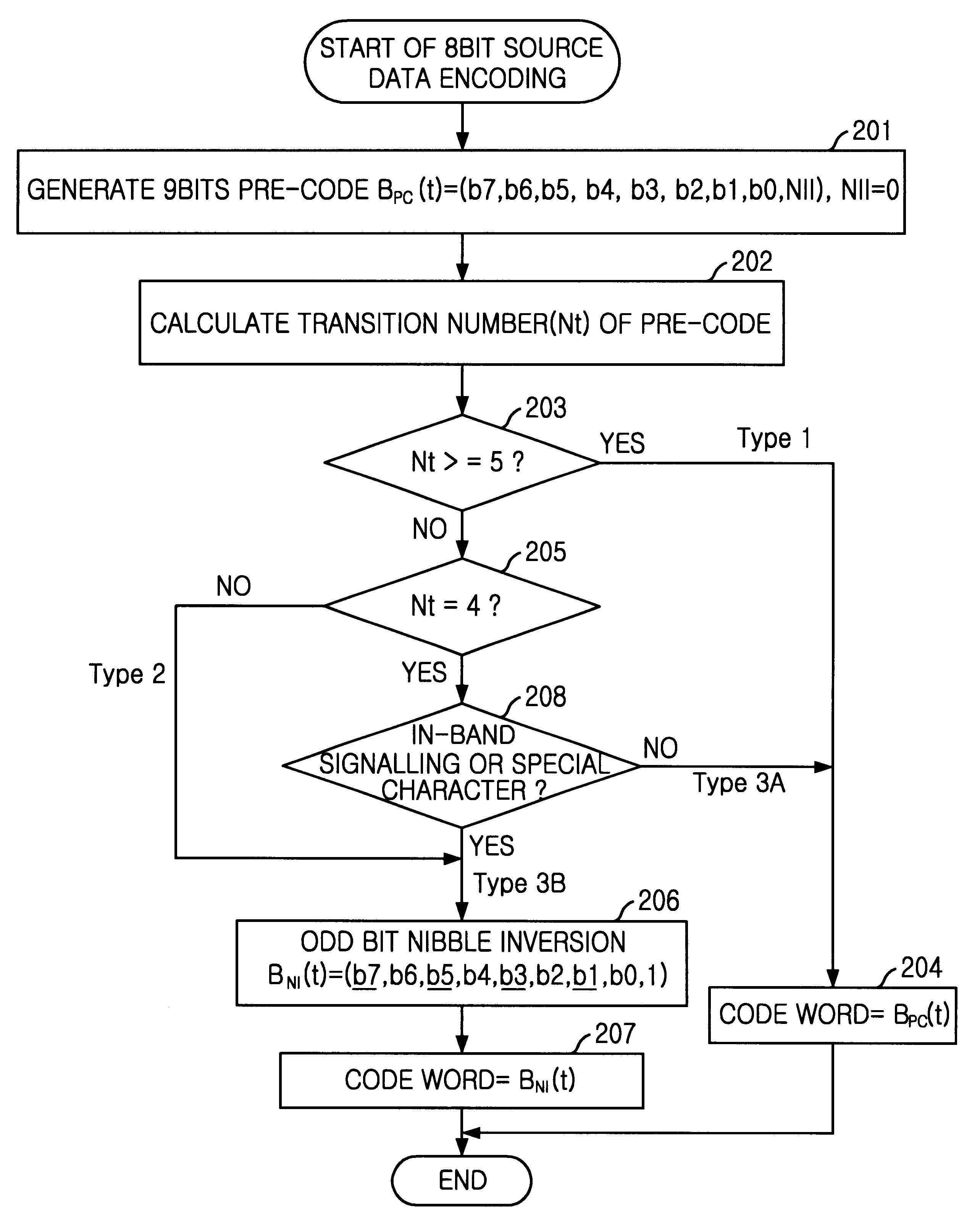

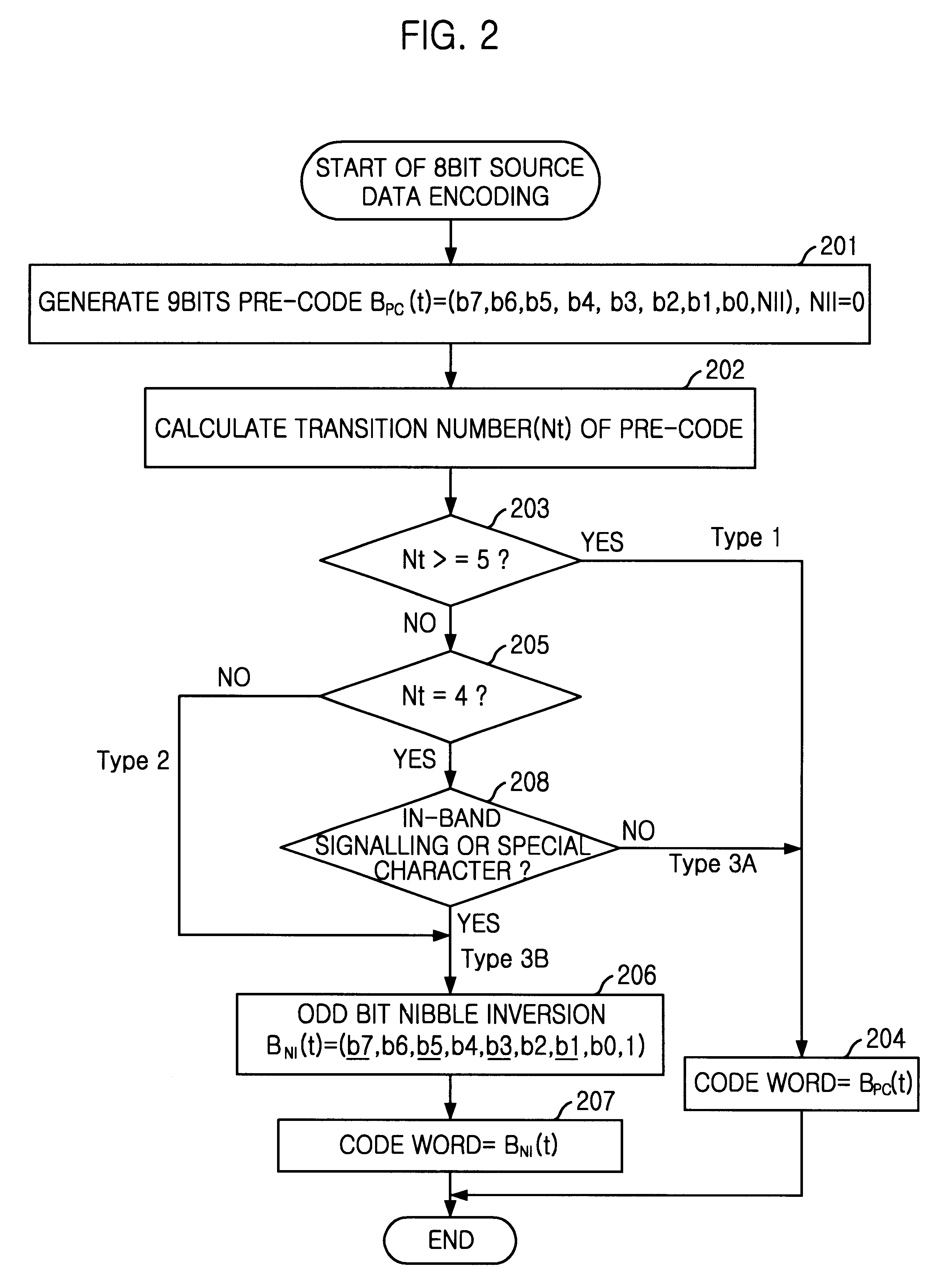

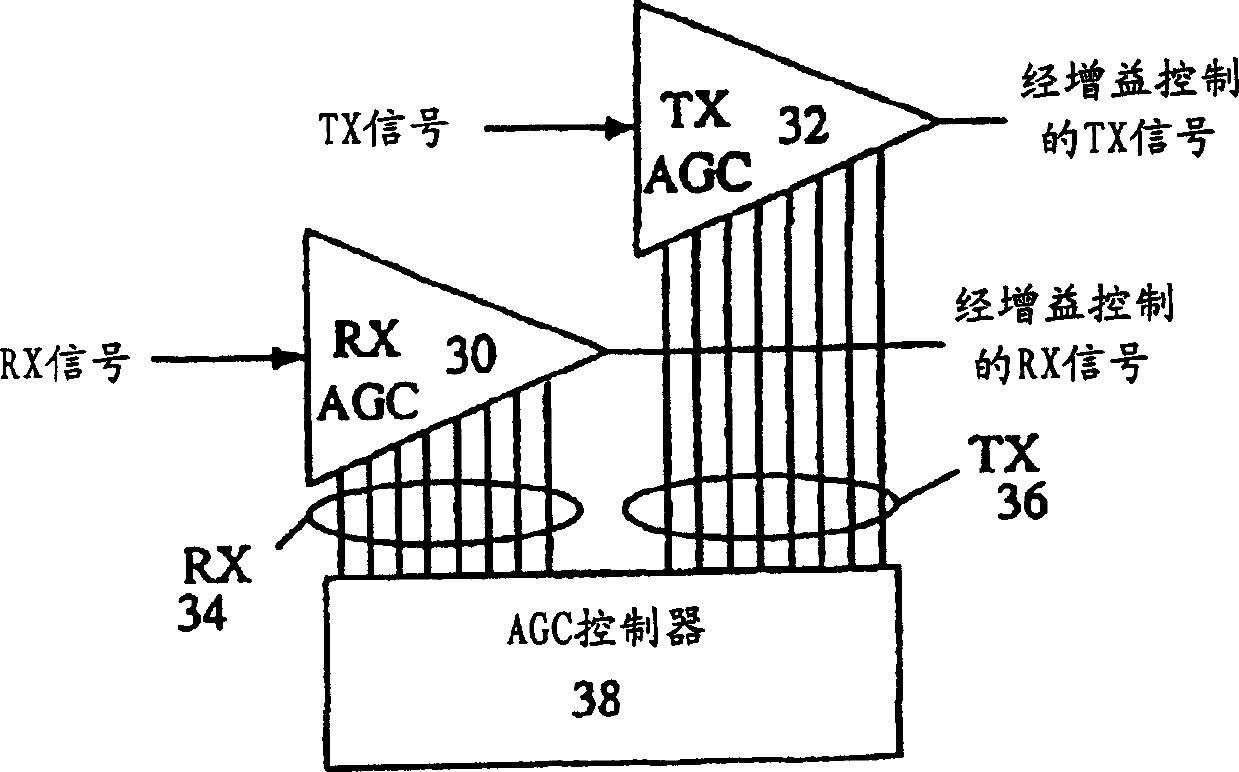

Apparatus and method for using nibble inversion code

A method for using a nibble(partial bits of word) inversion code in a network system includes the steps of: a) adding 1 redundancy bit to n bit source data and generating a pre-code, n being an even number of 2 or over; b) deciding the number of transitions in the generated pre-code; c) determining the pre-code as a code word if the number of transitions in the pre-code is greater than or equal to 1+n / 2 in a deciding result; d) inverting alternate bits including the redundancy bit among bits constructing the pre-code and generating the code word, if the number of transitions in the pre-code is less than n / 2 in the deciding result; e) determining the pre-code as the code word in case that the number of transitions in the pre-code is equal to n / 2 and simultaneously the source data is not an in-band signaling and not a special word in the deciding result; and f) inverting the nibble among the bits constructing the pre-code and generating the code word, in case that the number of transitions in the pre-code is equal to n / 2 and simultaneously the source data is an in-band signaling or is a special word in the deciding result.

Owner:ELECTRONICS & TELECOMM RES INST +1

Methods and devices for binary object serialization

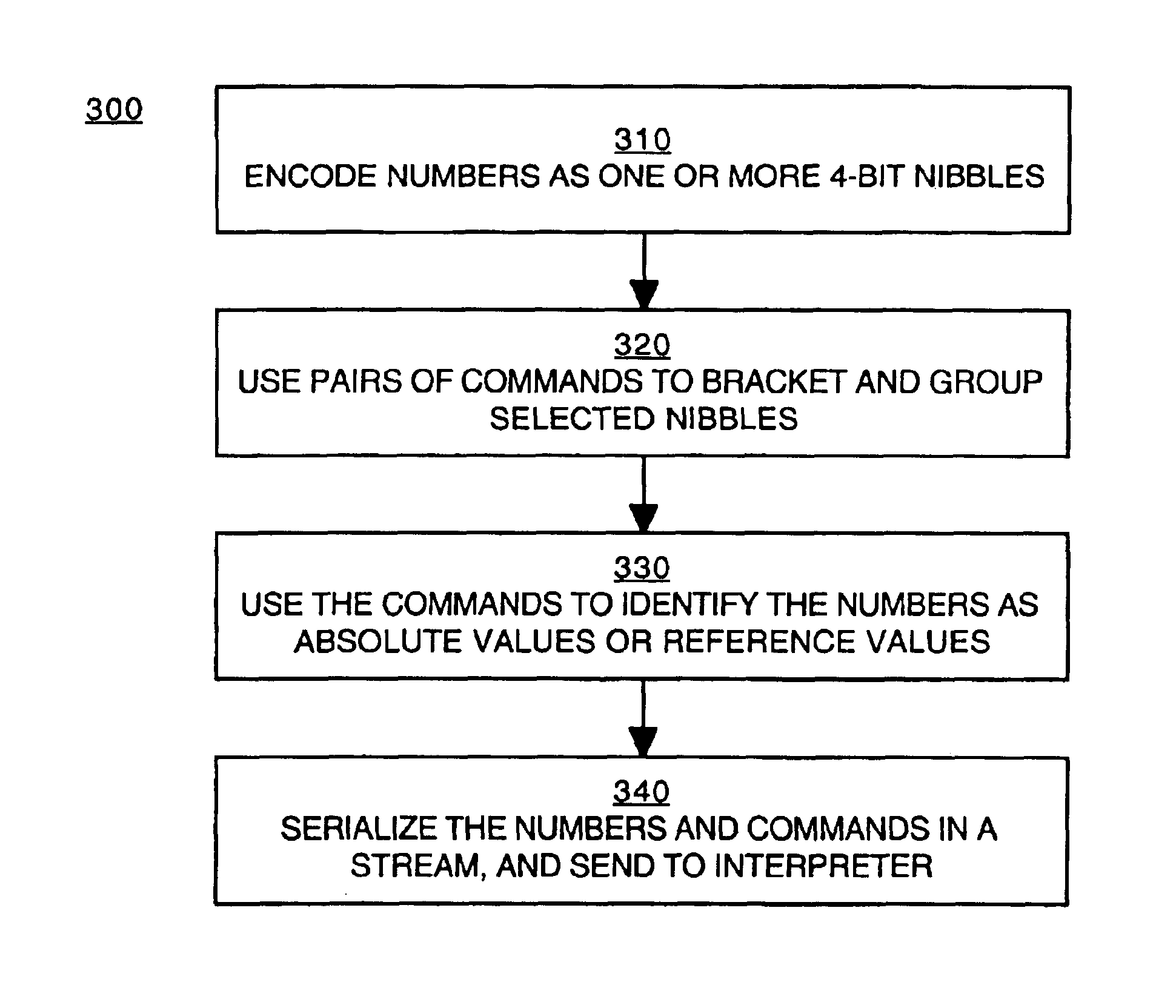

Methods and devices for data serialization are described. Numbers are each encoded as one or more four-bit nibbles. Three bits of a nibble are for encoding some portion of a number and one bit of the nibble is for indicating whether encoding of the number is continued to another nibble. A begin command and an end command are used to bracket and thereby group selected nibbles. The numbers and the commands are serialized in a stream. An interpreter of the stream reads the numbers into data fields of a data object starting at the begin command. The interpreter automatically skips to the end command when the data fields are filled. As such, a newer version of an interpreter can read data serialized using an older version of an encoder, and an older version of an interpreter can read data serialized using a newer version of an encoder.

Owner:ACCESS

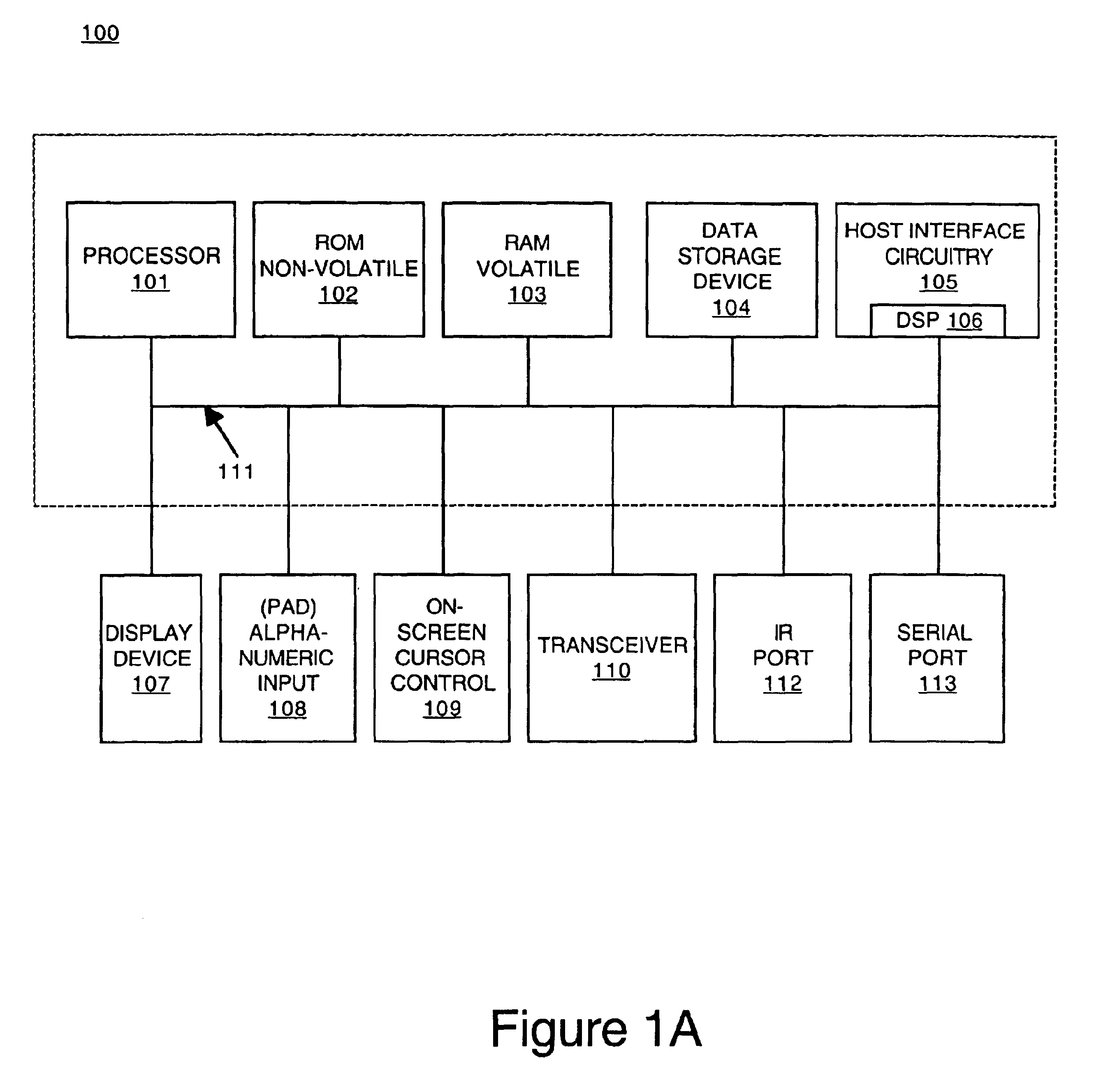

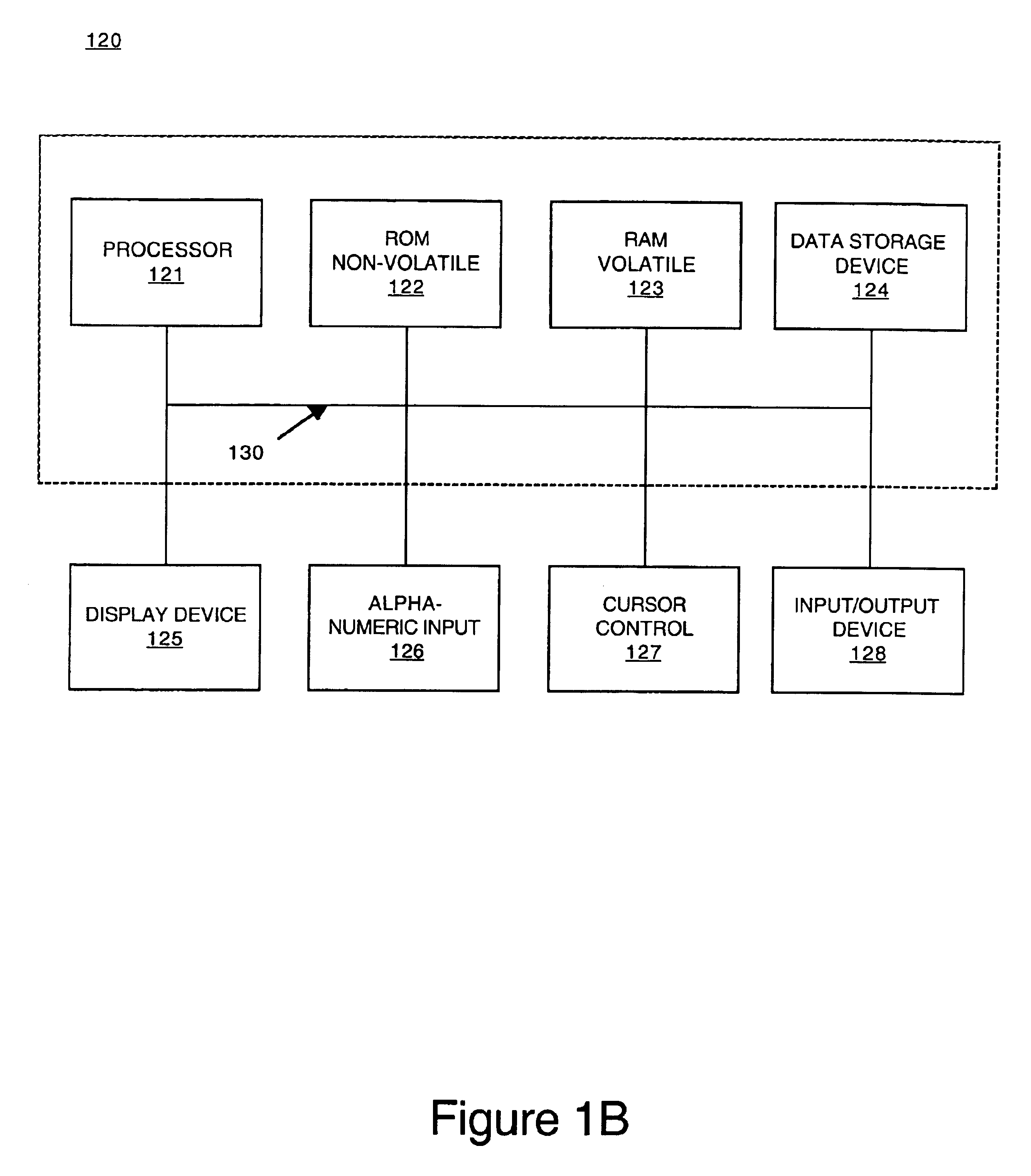

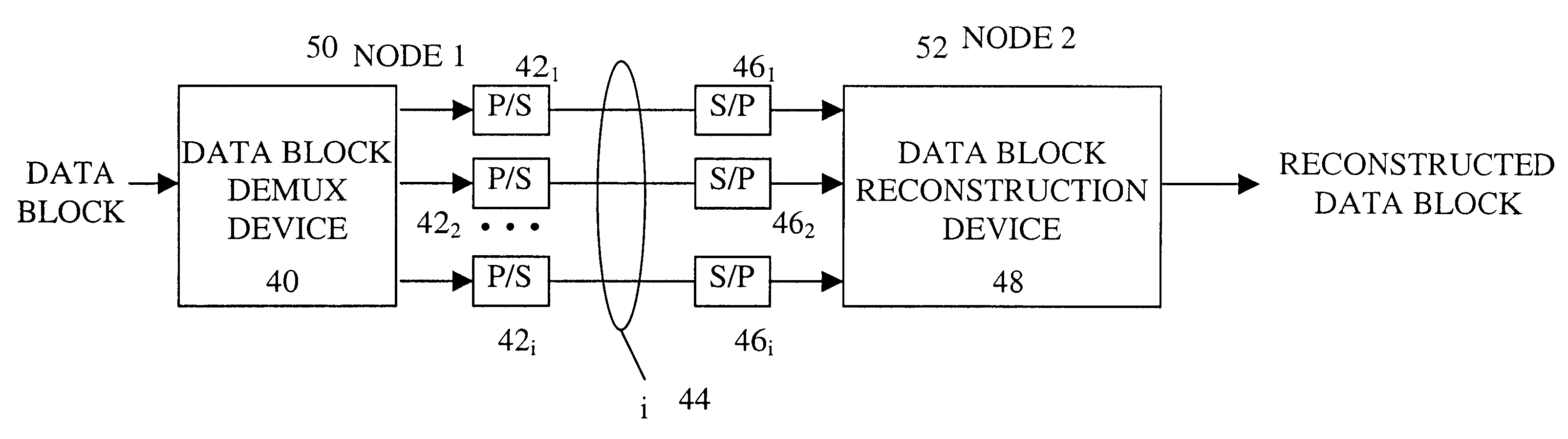

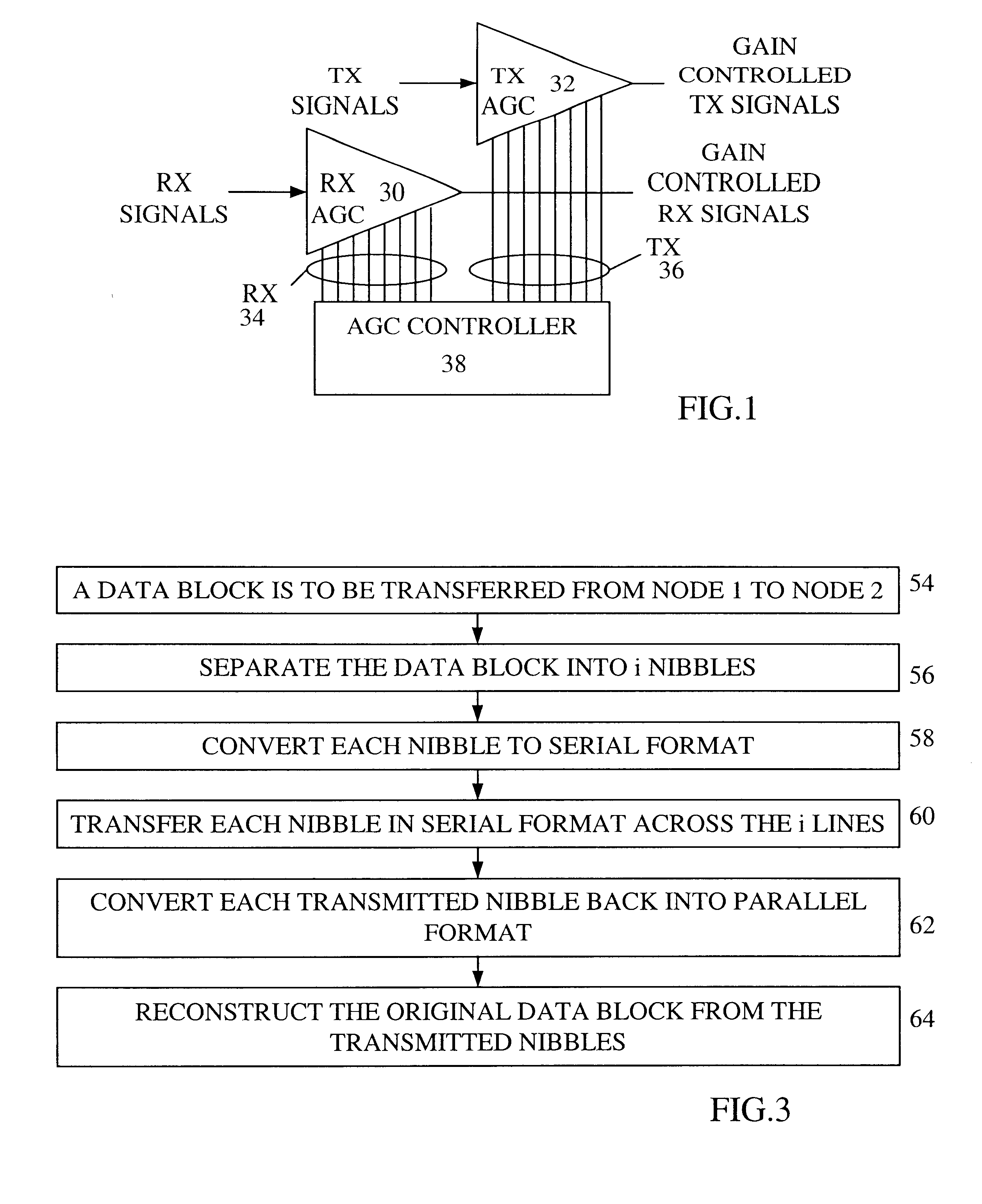

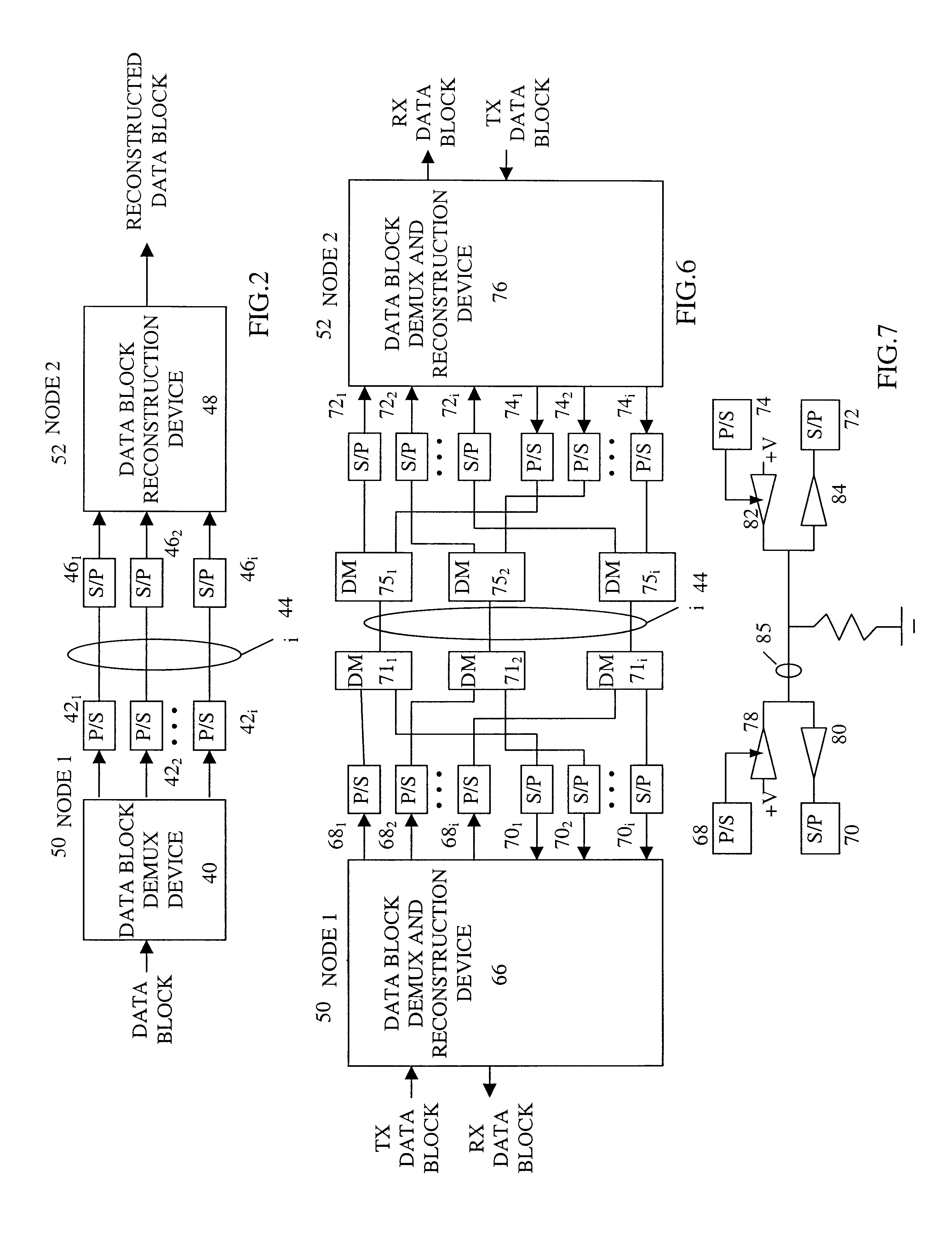

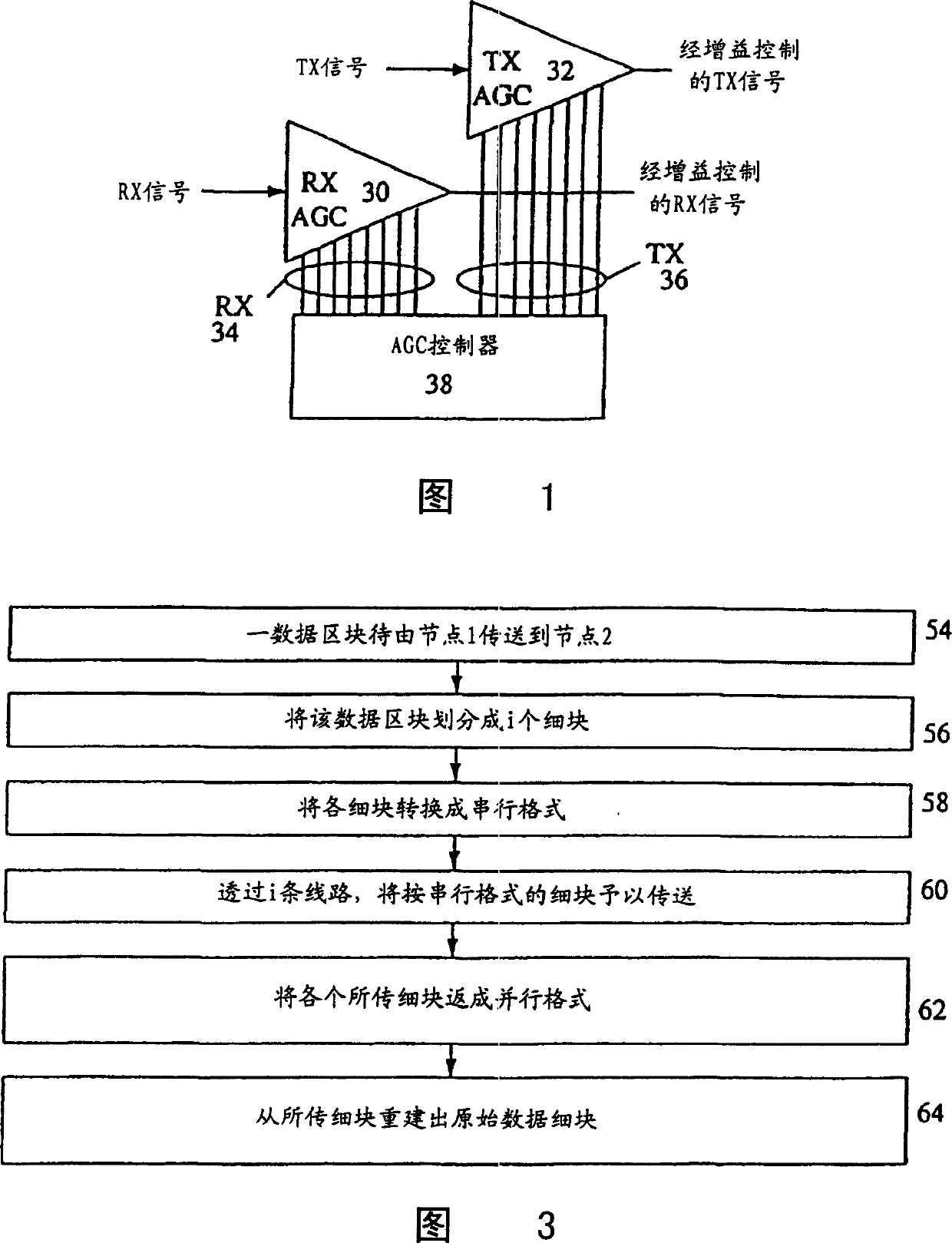

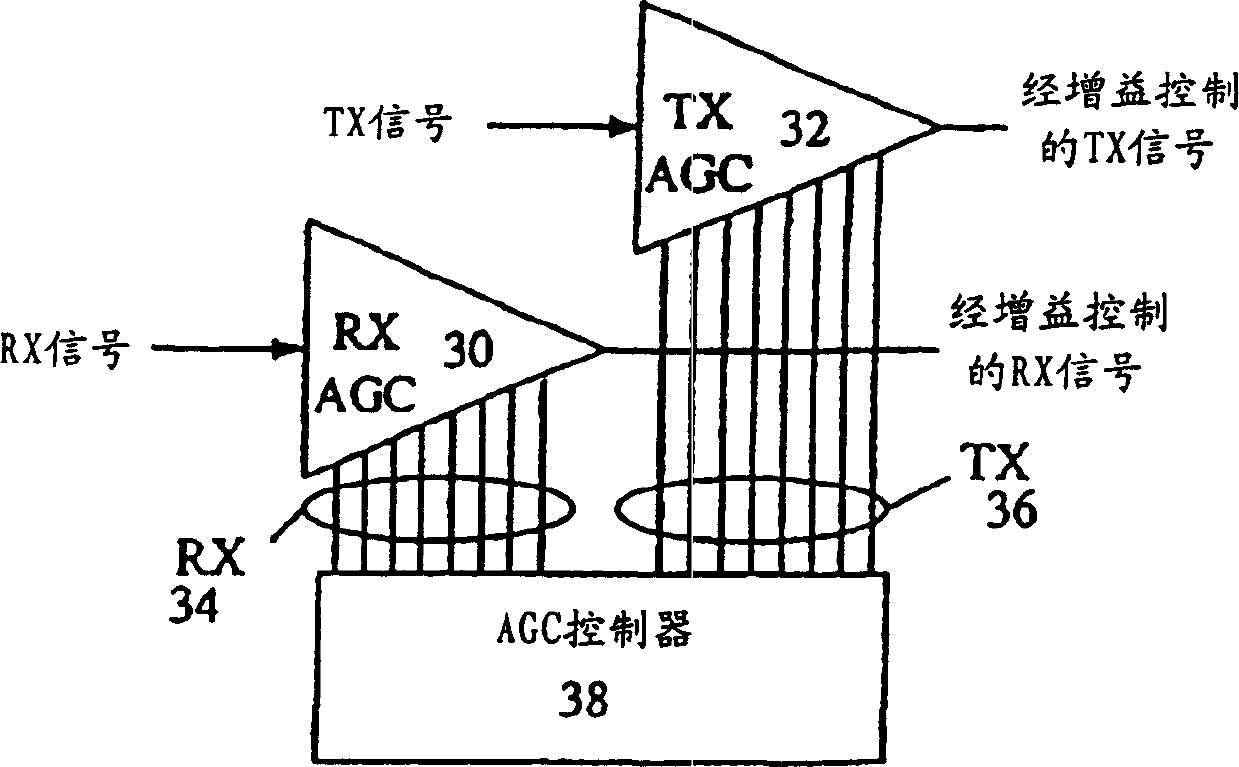

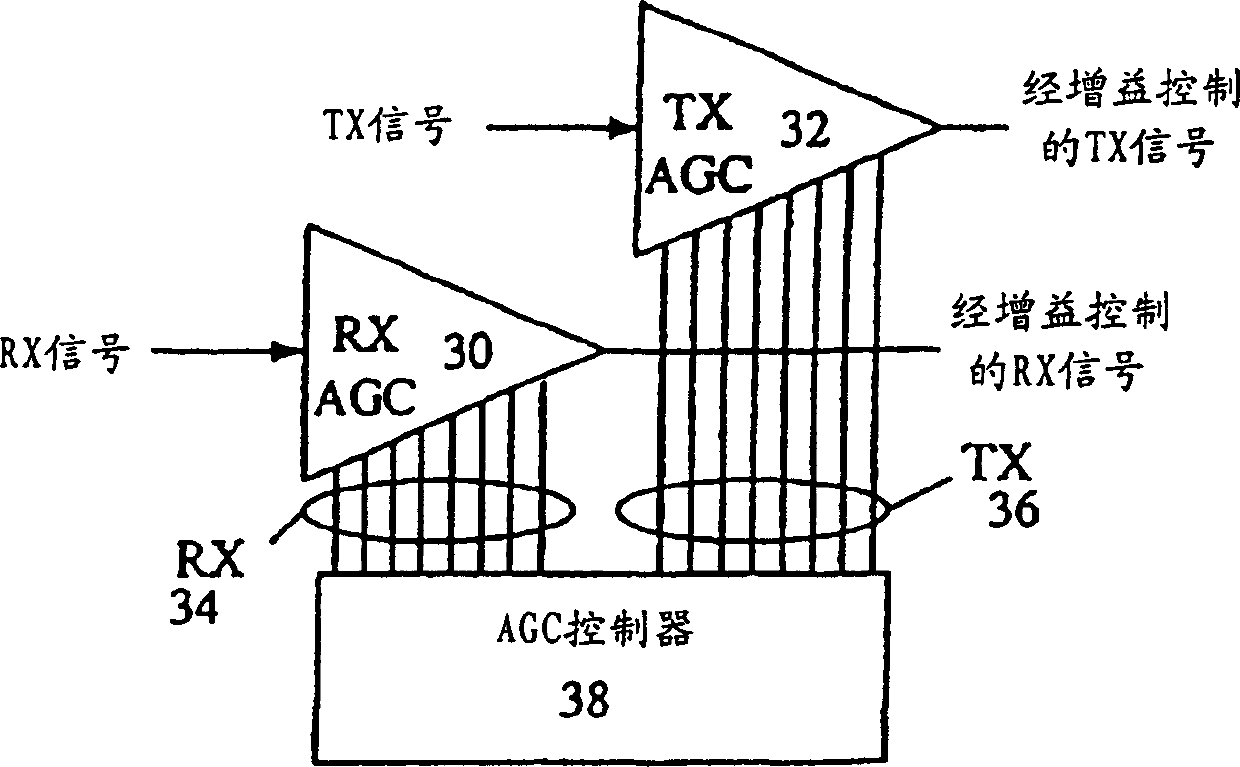

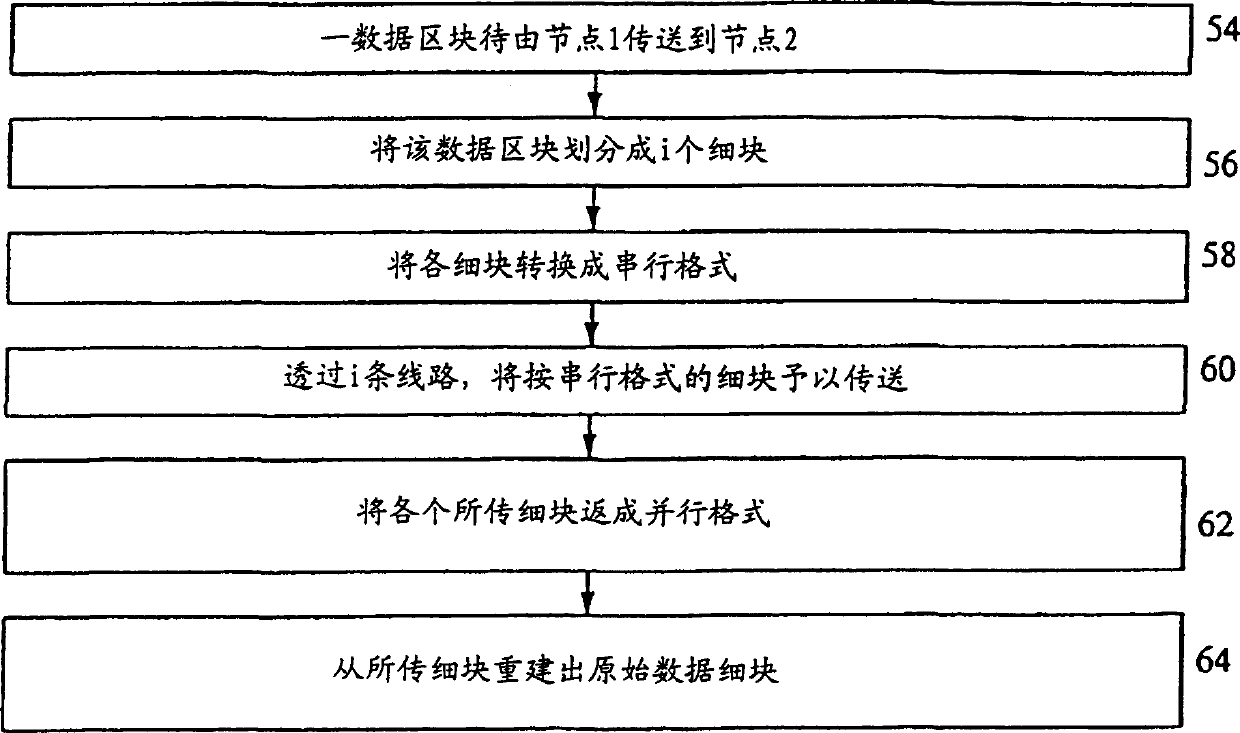

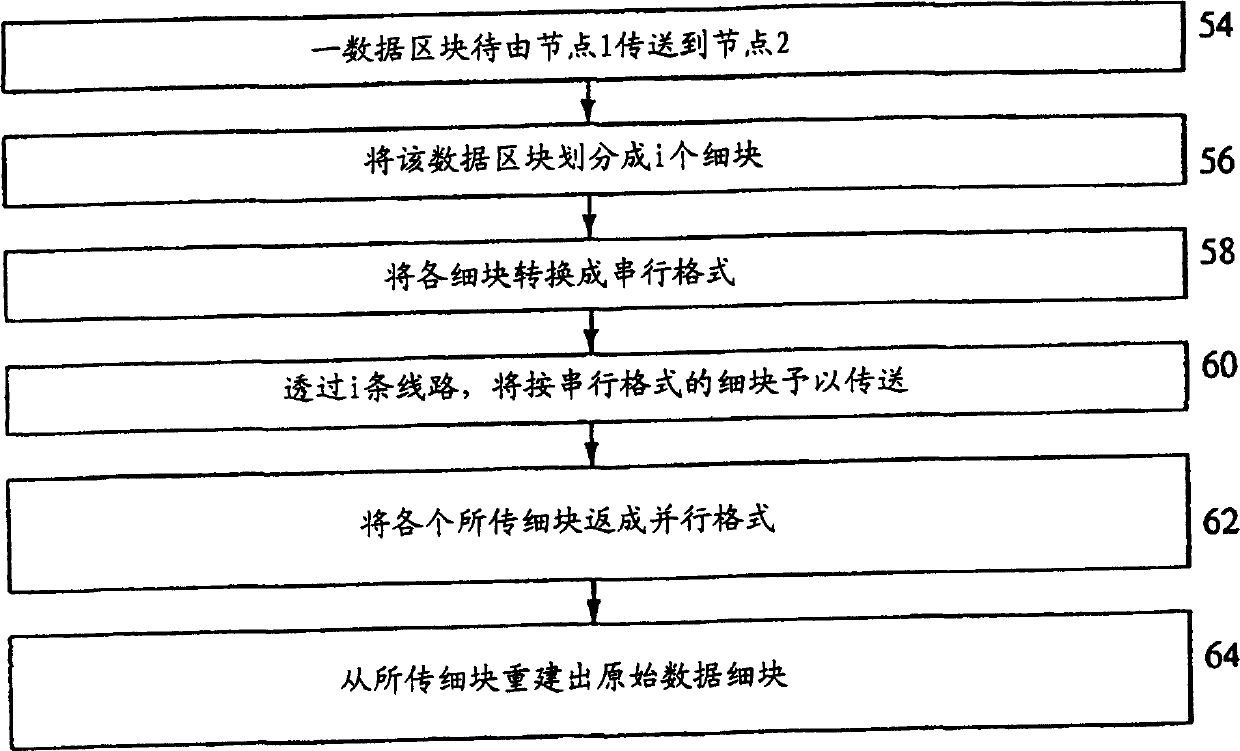

Method employed by a base station for transferring data

A hybrid serial / parallel bus interface method for a base station has a data block demultiplexing device. The data block demultiplexing device has an input configured to receive a data block and demultiplexes the data block into a plurality of nibbles. For each nibble, a parallel to serial converter converts the nibble into serial data. A line transfers each nibble's serial data. A serial to parallel converter converts each nibble's serial data to recover that nibble. A data block reconstruction device combines the recovered nibbles into the data block.

Owner:INTERDIGITAL TECH CORP

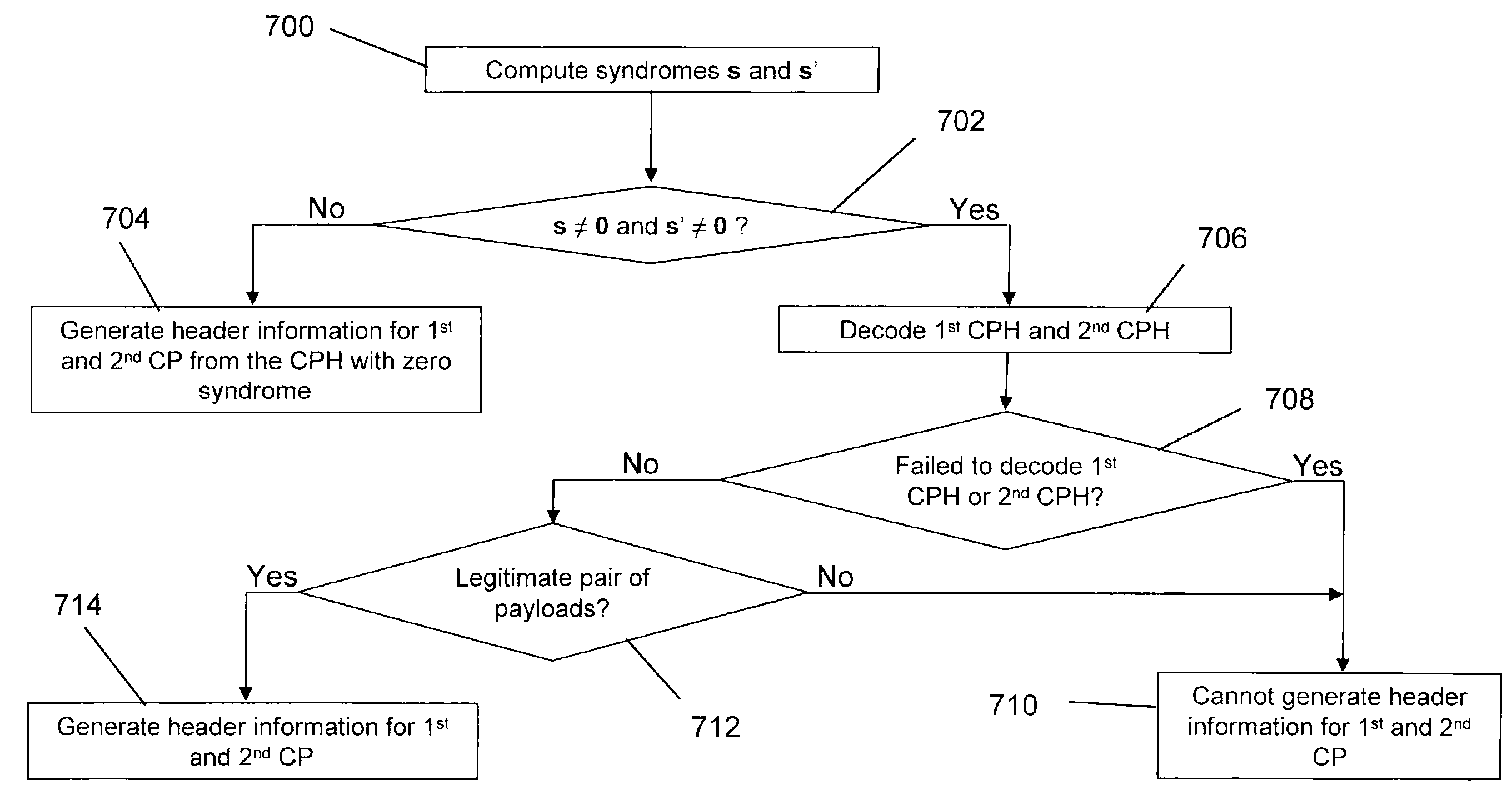

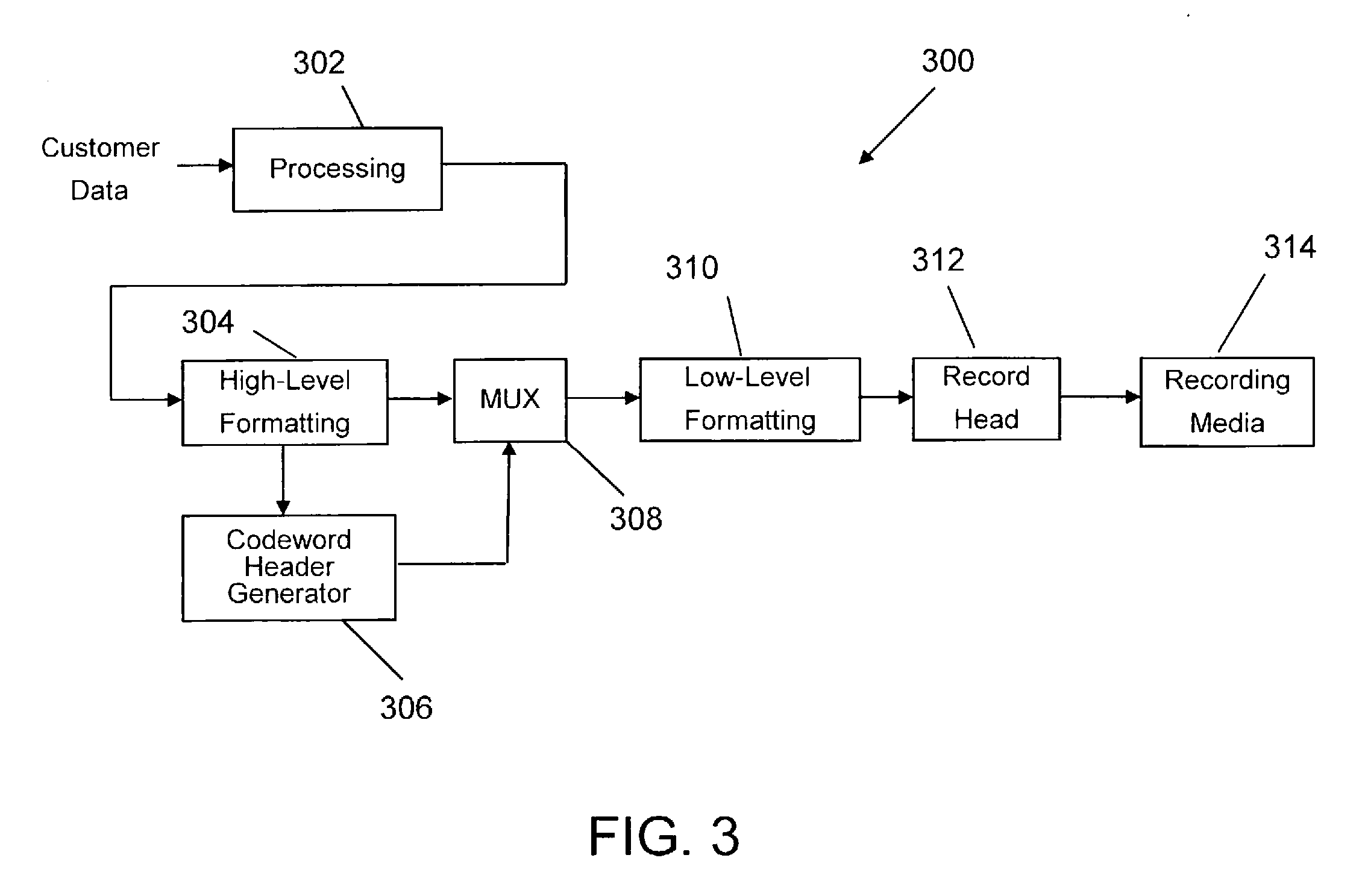

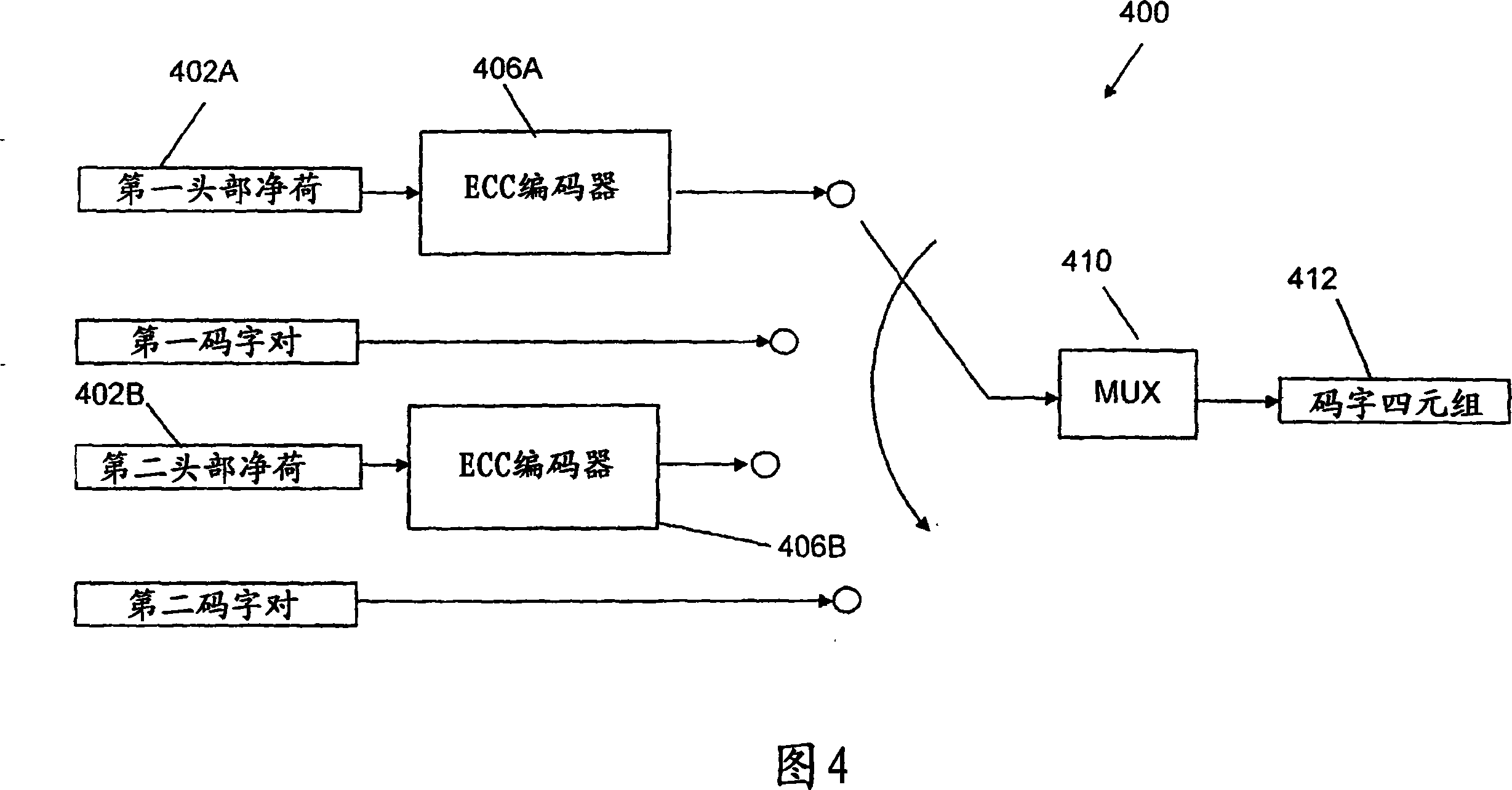

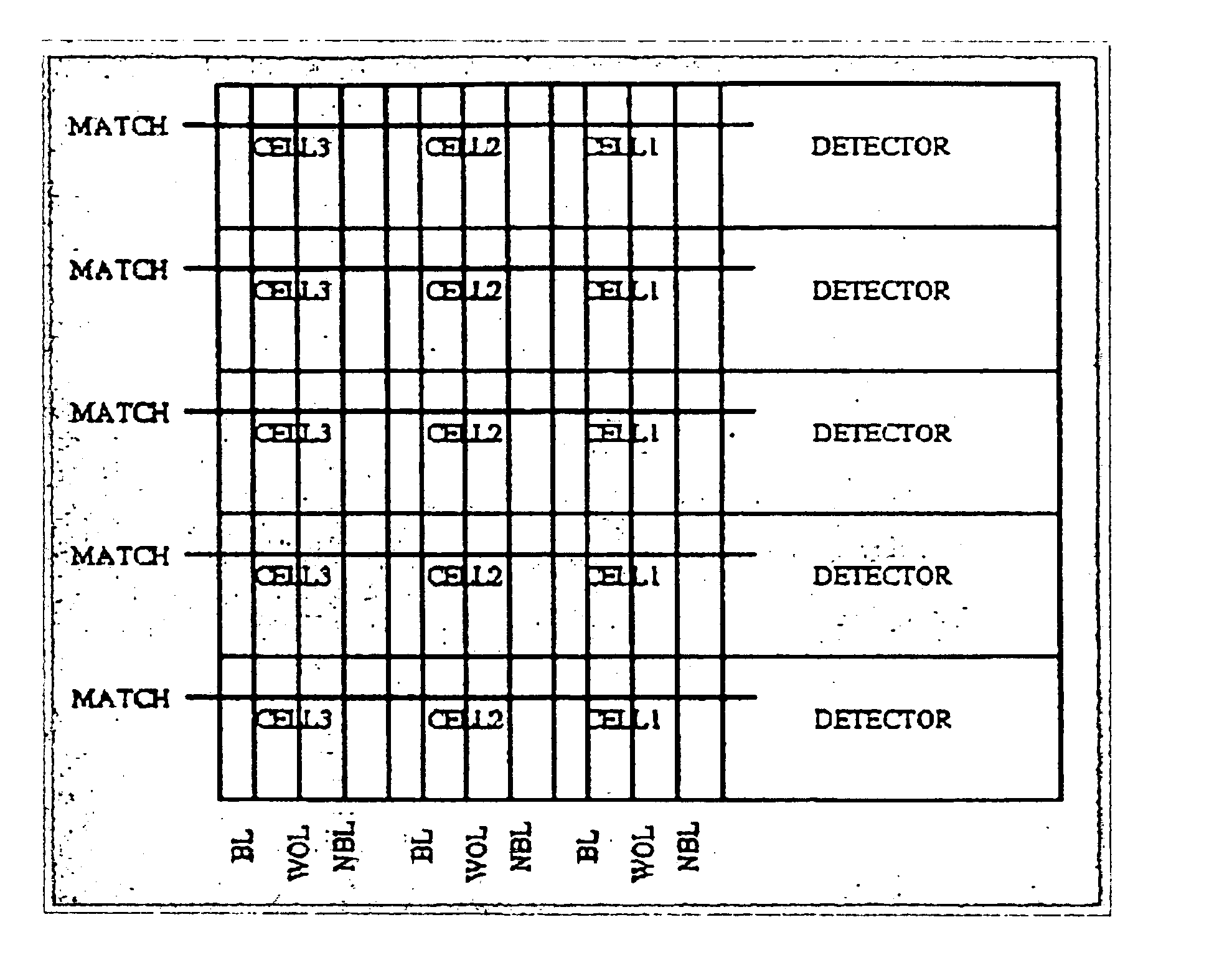

Error correction in codeword pair headers in a data storage tape format

Error correction coding is provided for codeword headers in a data tape format, such as a Linear Tape-Open, Generation 4 (LTO-4) data tape format. The data tape format defines a codeword quad as having first and second codeword headers interleaved with first and second codeword pairs, each codeword header comprising N bytes Ck=C0, C1, . . . , CN−2, CN−1 wherein K bytes C0-CK−1 of the first and second headers in a codeword quad differ such that if one is known the other can be inferred. Each header byte Ck of a codeword quad is redefined as comprising two interleaved (M / 2)-bit nibbles, ek, ok. For each header, nibbles ek-eN−1 and nibbles ok-oN−1 are generated as a function of nibbles, e0-EK−1 and o0-oK−1, respectively. A codeword is assembled with the redefined headers the codeword quad is then recorded onto a recording medium.

Owner:IBM CORP

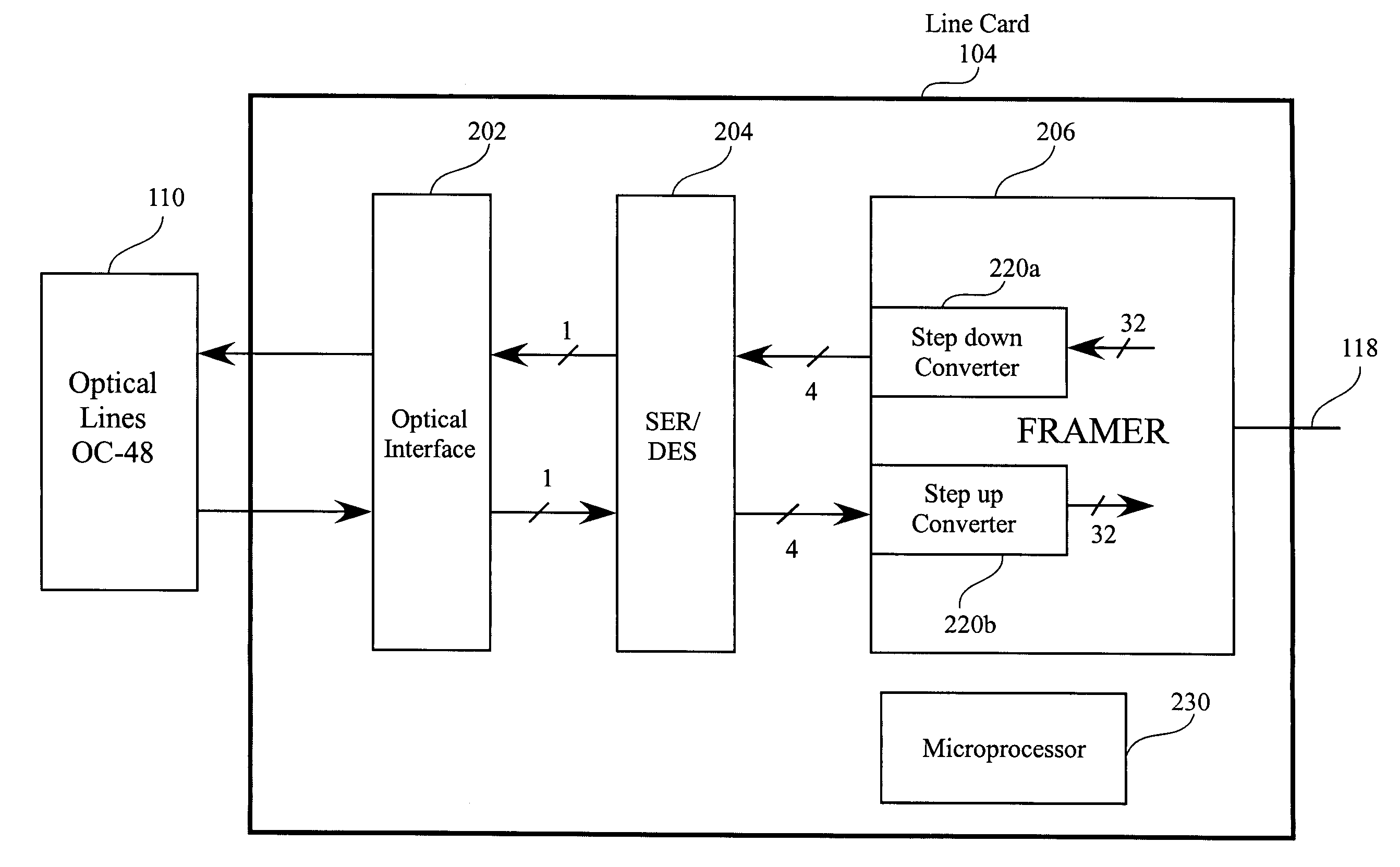

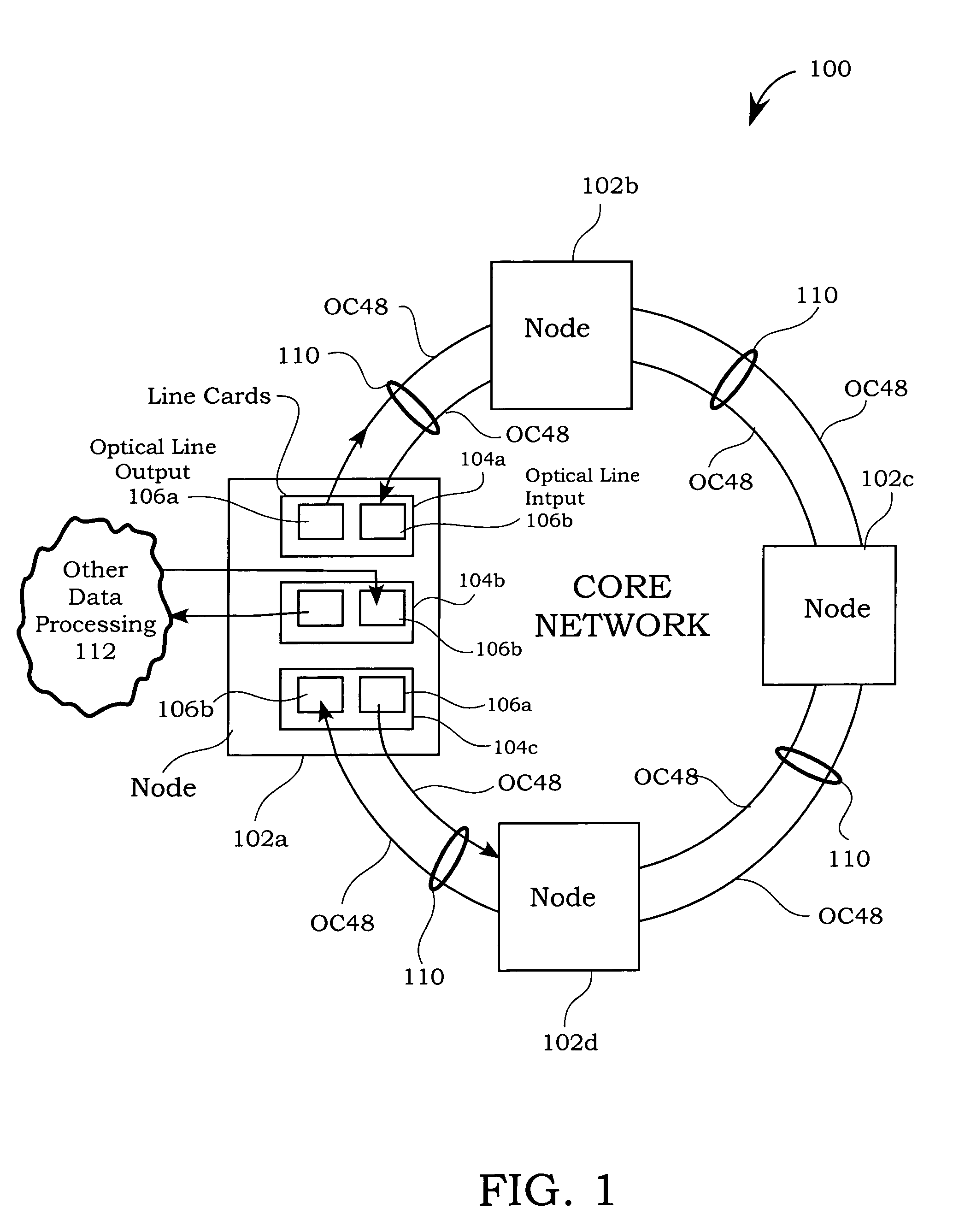

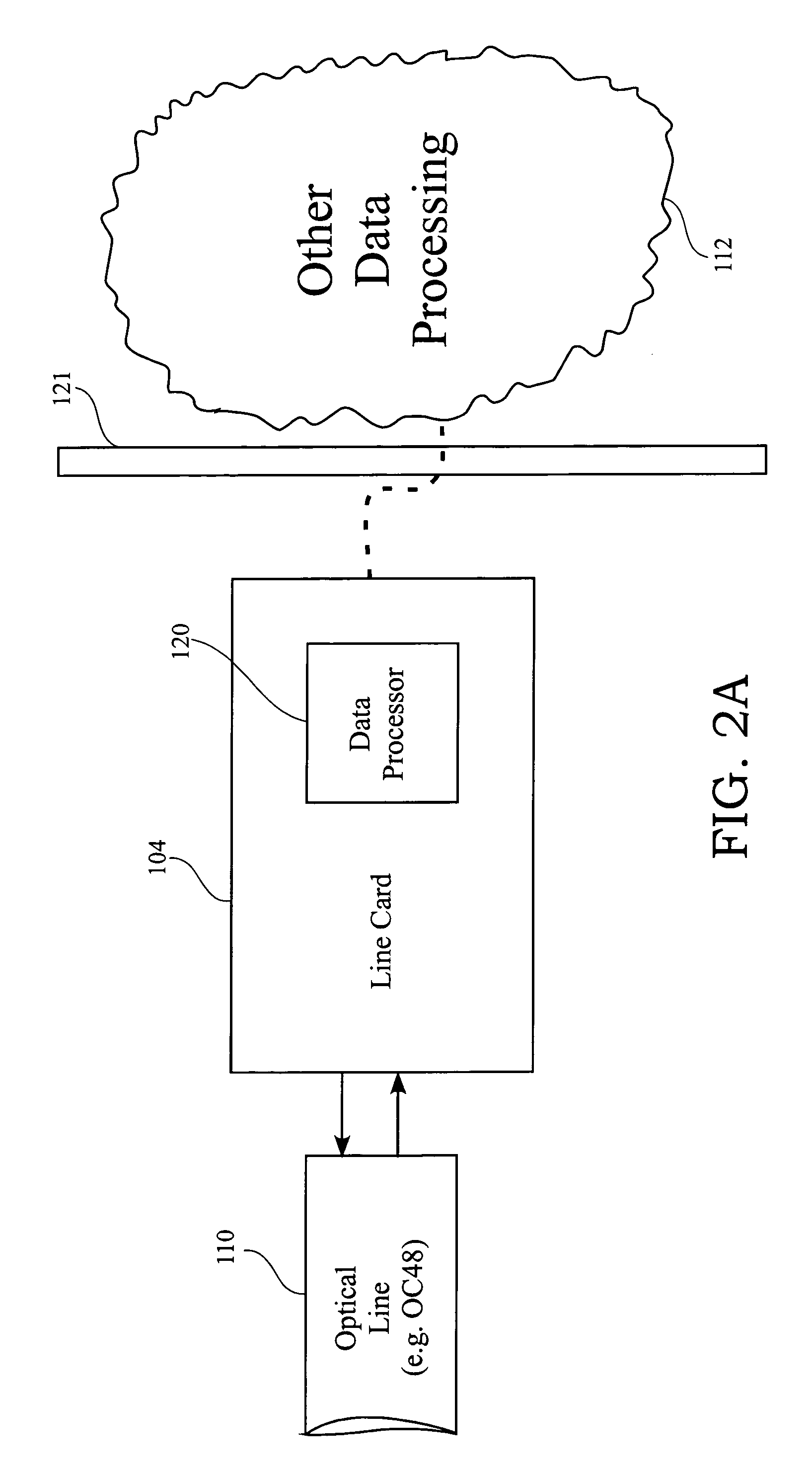

Interfacing 622.08 MHz line interface to a 77.76 MHz SONET framer

A line card for use in a node of a network to connect to optical network lines is provided. The line card includes an optical interface, and a serializer / deserializer (SERDES) operating at a first frequency. The line card also includes a framer operating at a second frequency where the first frequency is higher than the second frequency. The framer includes a digital step up converter to receive data from the SERDES and a digital step down converter to supply data to the SERDES. The step down converter includes a set of input buffers where each input buffer receives a word of nibbles from the framer. The input buffers are loaded one after another, but extraction from each of the input buffers to a multi-stage multiplexer is triggered so long as a non-reset window is preserved. The step up converter includes a set of input buffers and a register array where each input buffer receives a word of nibbles from the register array. The input buffers are loaded one after another, but extraction from the input buffers to a multi-stage multiplexer is triggered so long as a non-reset window is preserved.

Owner:SYNAPTICS INC +1

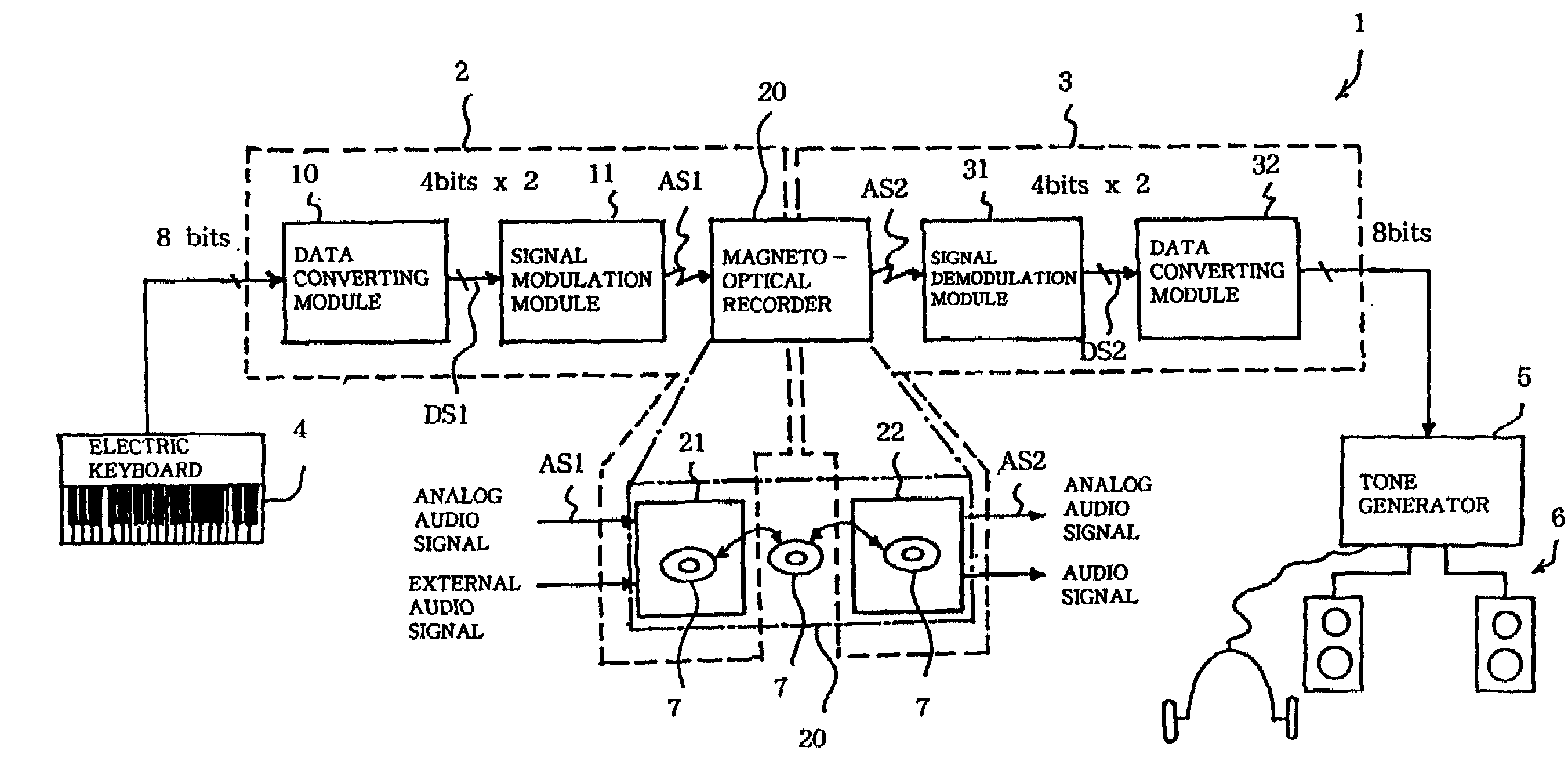

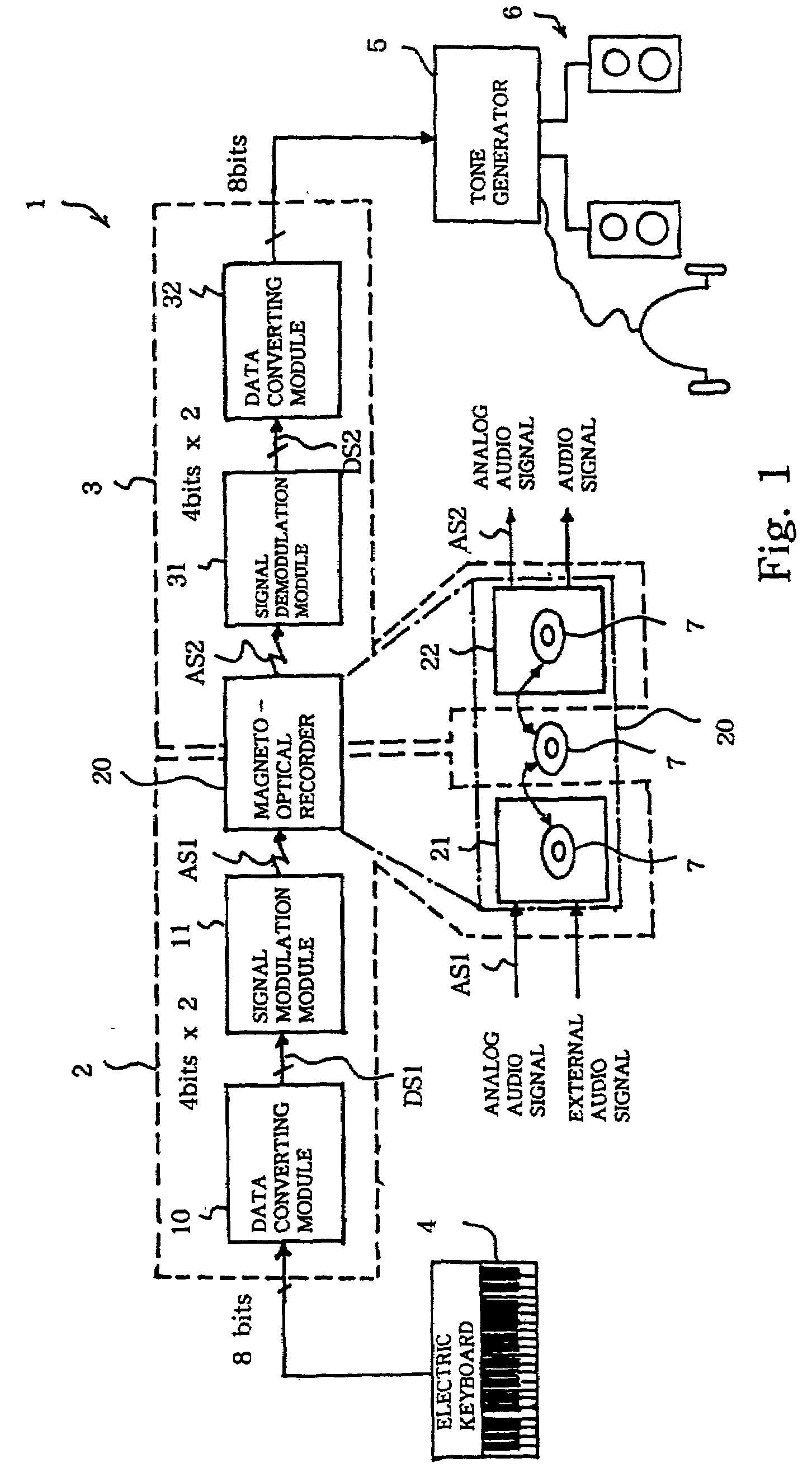

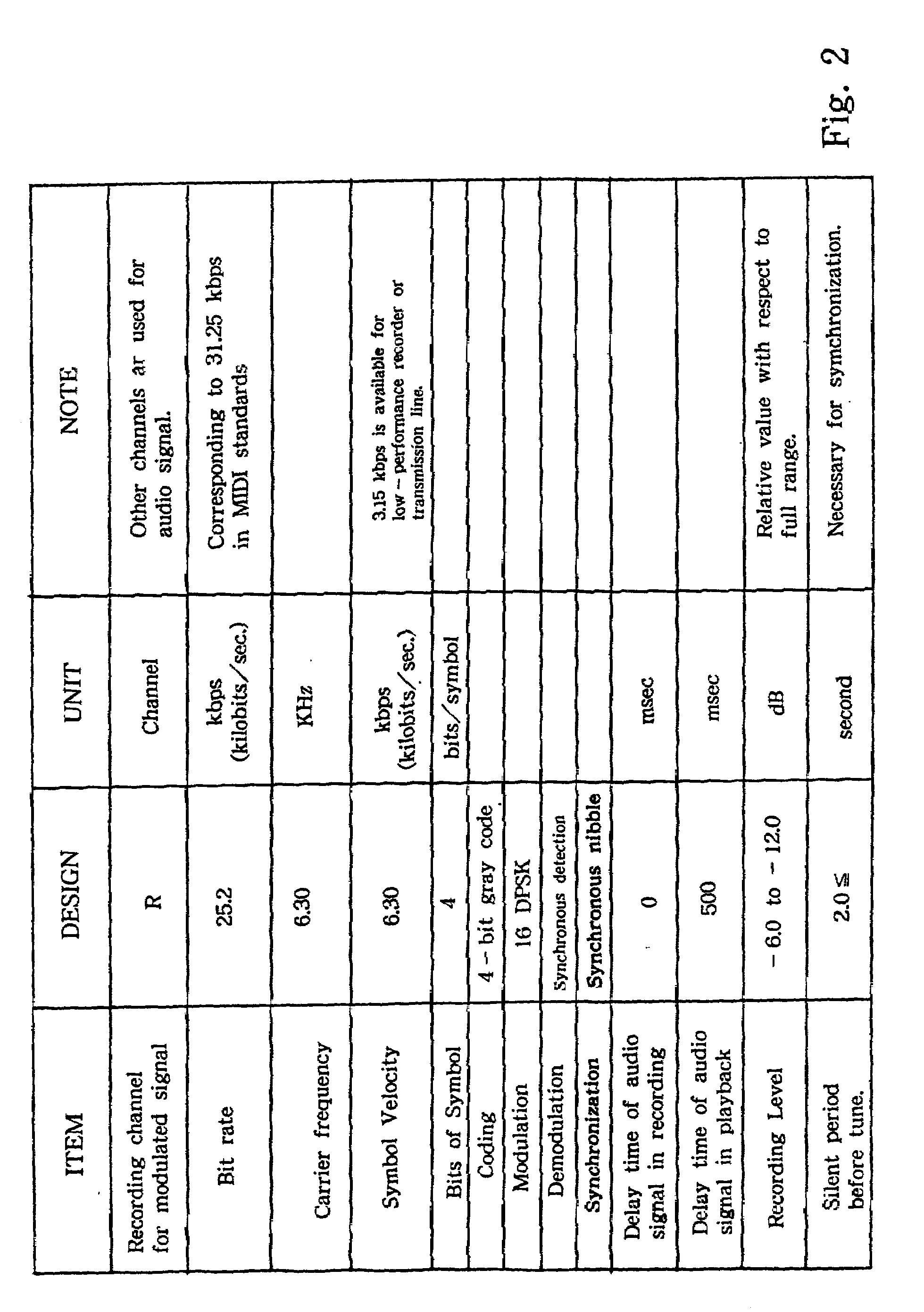

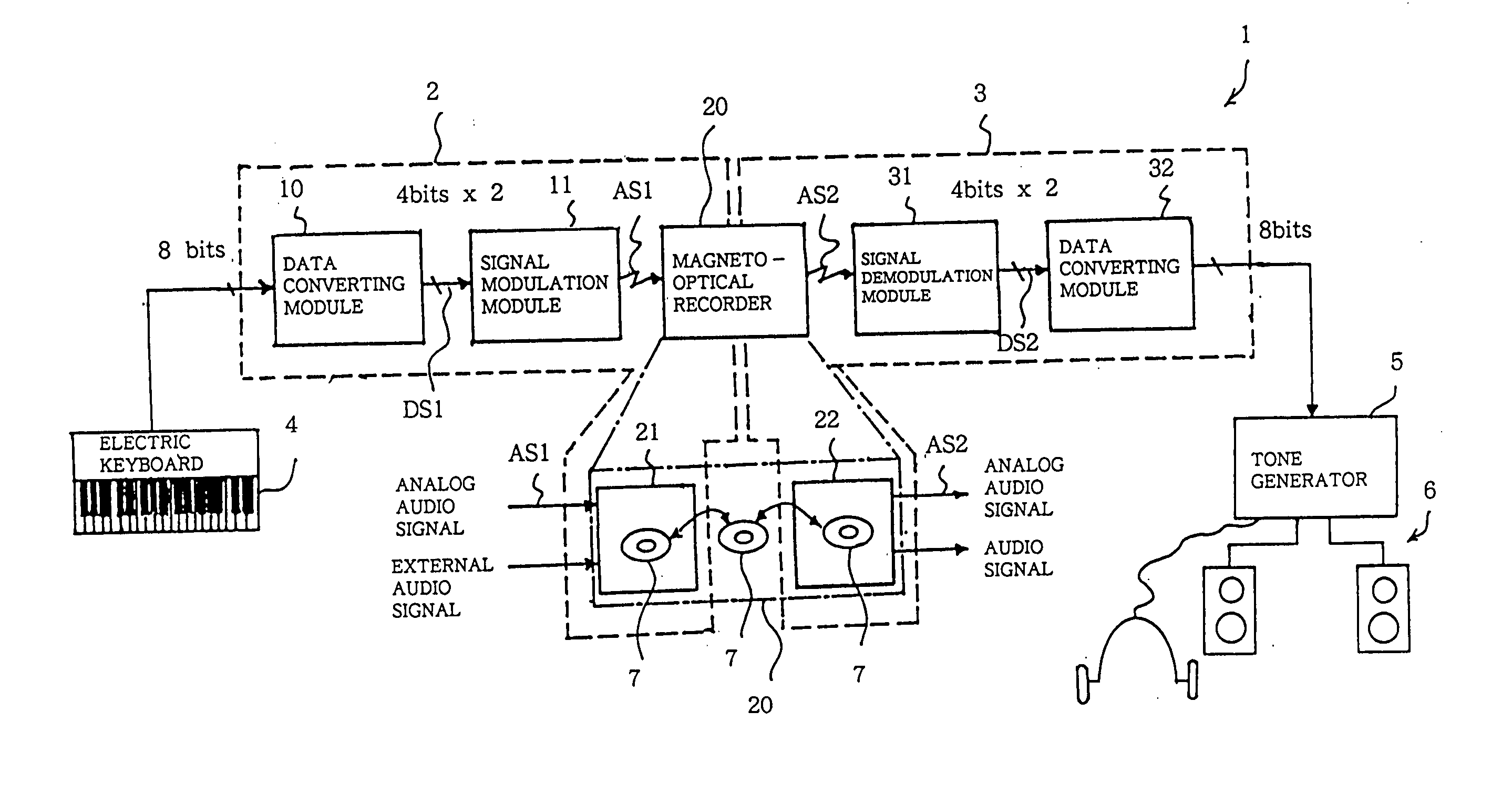

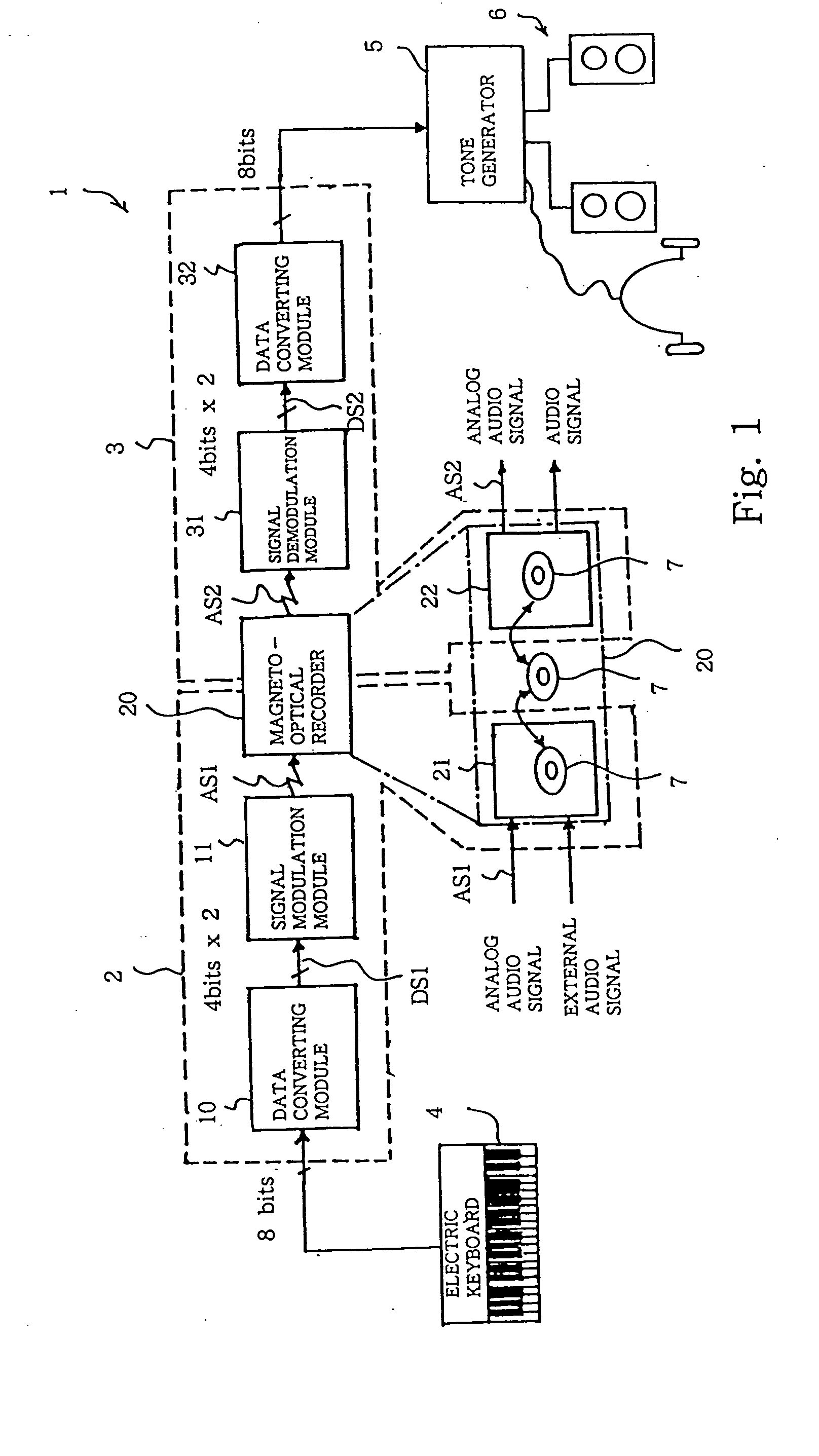

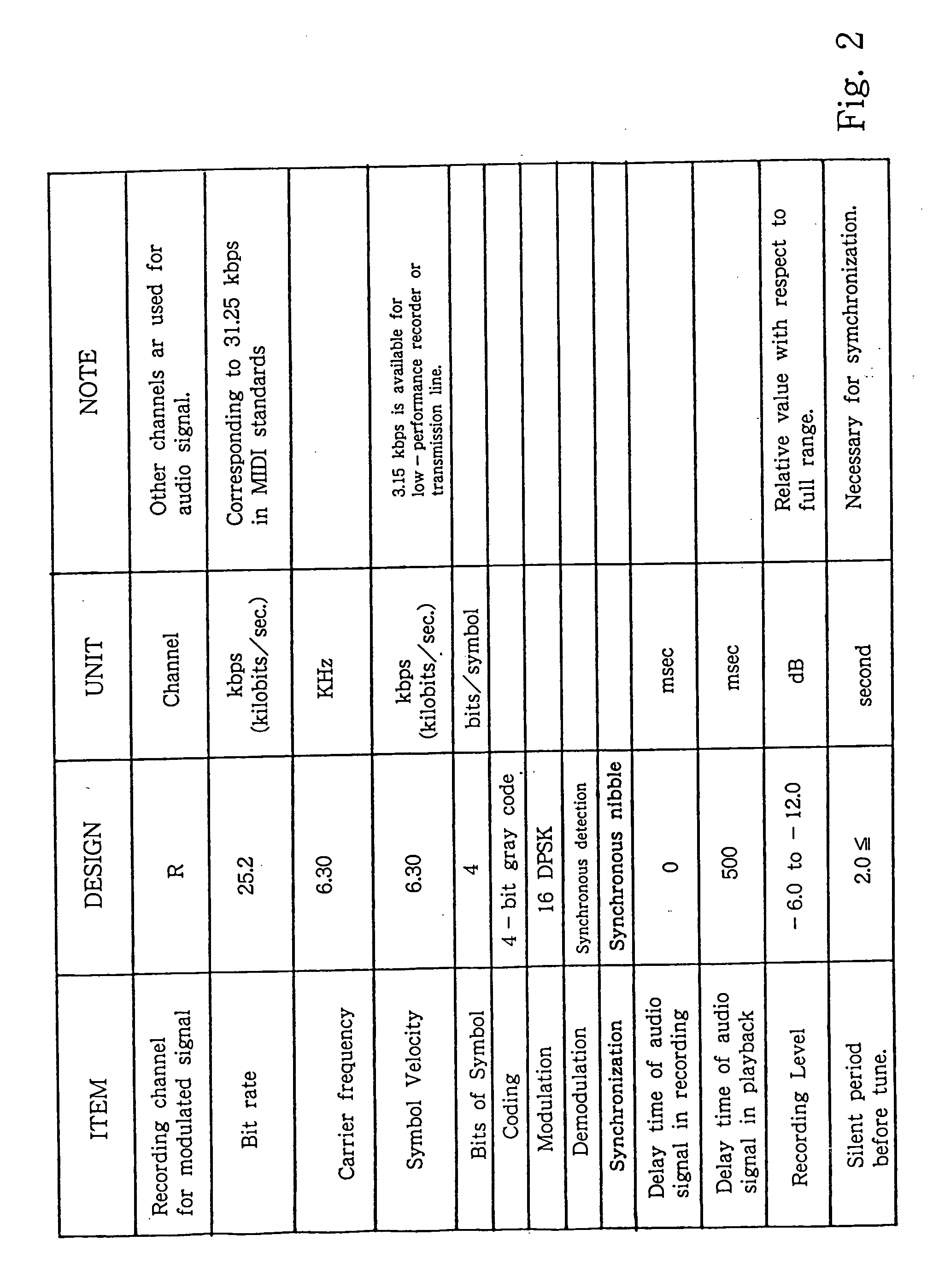

Method for recording asynchronously produced digital data codes, recording unit used for the method, method for reproducing the digital data codes, playback unit used for the method and information storage medium

A recording and reproducing system is broken down into a recording unit for producing a digital audio data signal from MIDI music data words asynchronously produced at irregular intervals and a playback unit for reproducing the MIDI music data codes from the digital audio data signal, wherein synchronous data nibbles are supplemented in the irregular intervals among the MIDI music data words for producing a data stream, and the digital audio data signal is produced from the data stream through a differential phase shift keying and a phase code modulation so as to record the MIDI messages in a digital versatile disk at high dense.

Owner:YAMAHA CORP

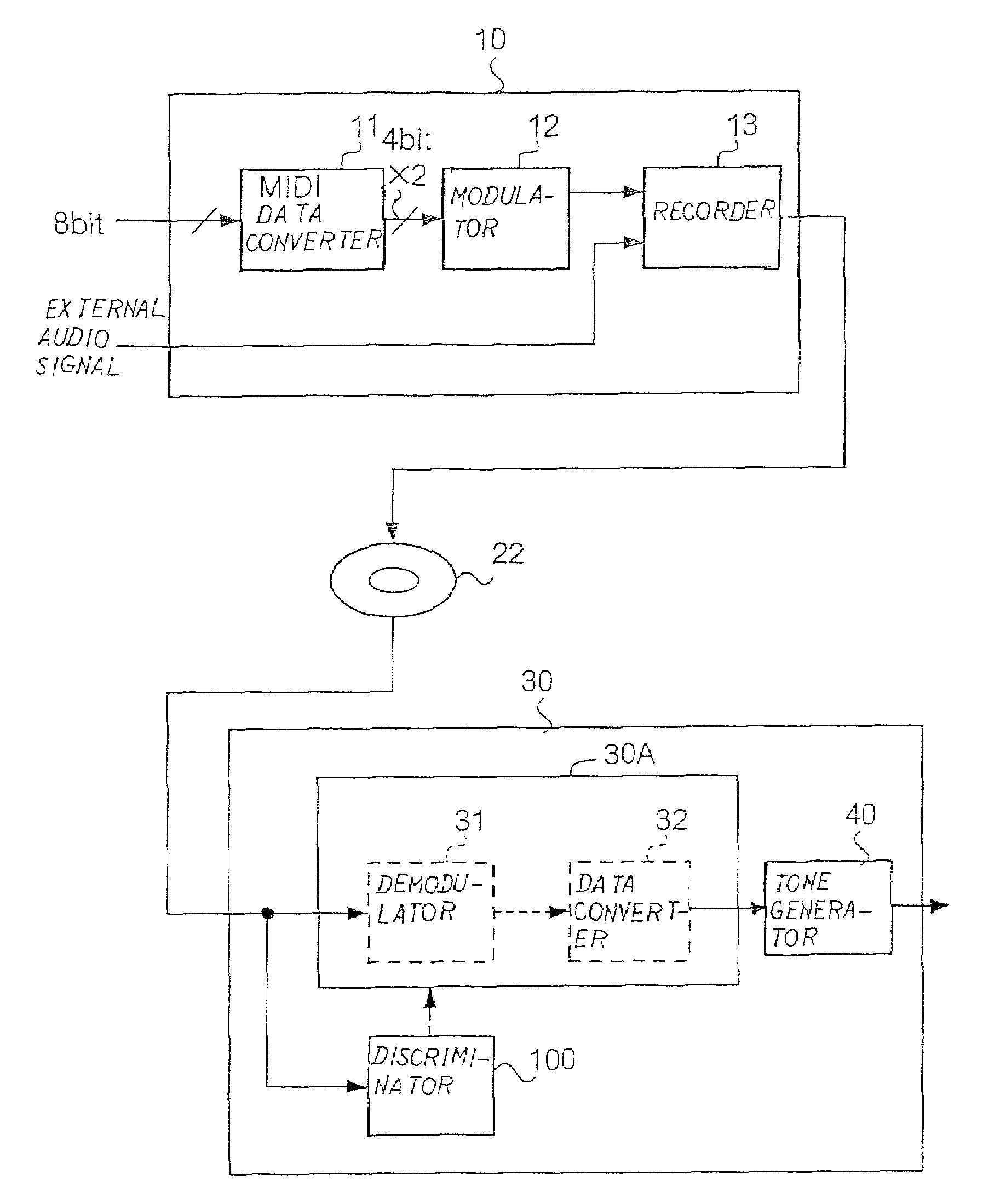

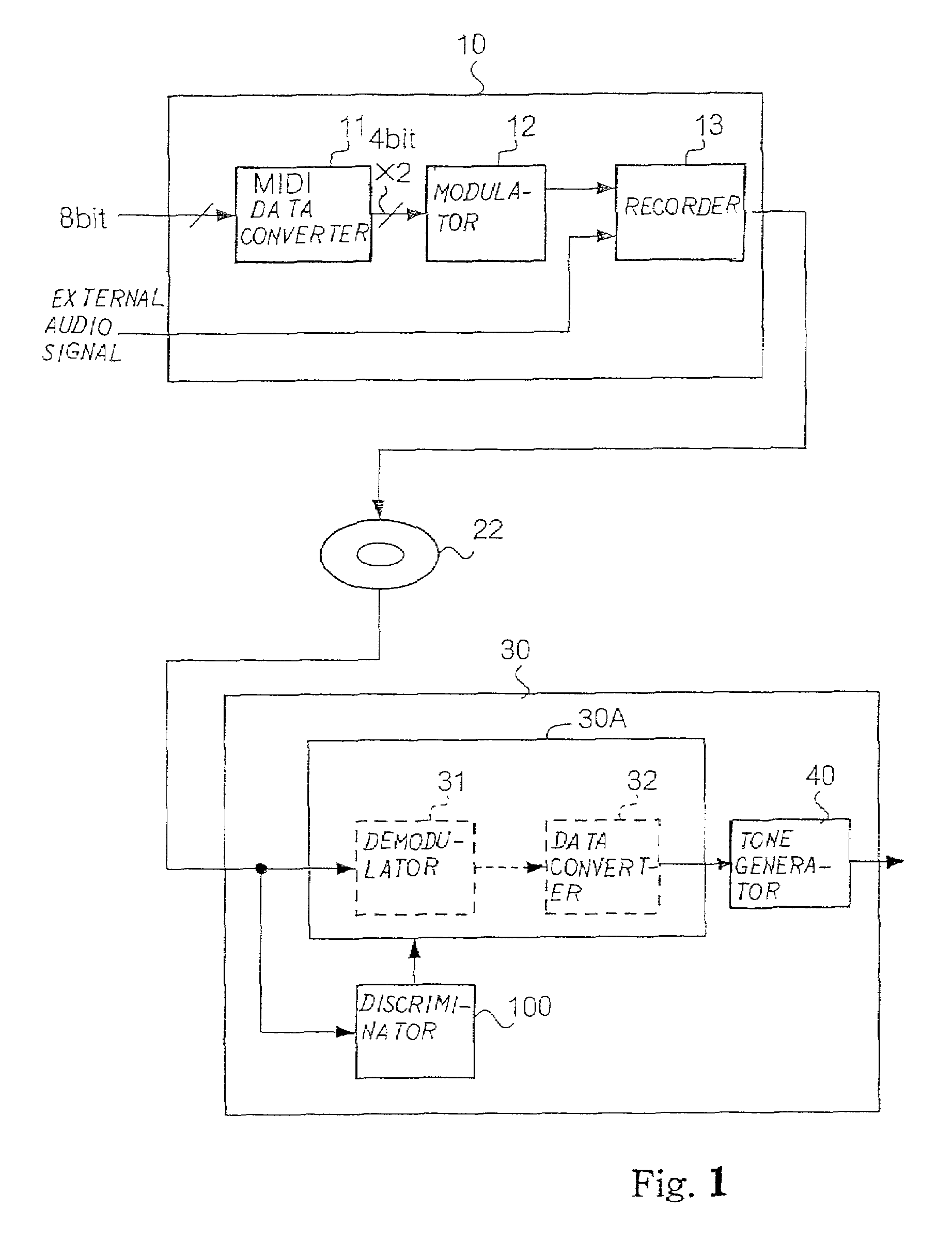

Discriminator for differently modulated signals, method used therein, demodulator equipped therewith, method used therein, sound reproducing apparatus and method for reproducing original music data code

A nibble stream containing MIDI music data words and synchronous nibbles and an external audio signal are selectively converted to an audio-frequency signal, which in turn is converted to a set of PCM codes for storing it in a compact disc; and the audio frequency signal, which is demodulated from the PCM data codes, is analyzed to see which is the origin of the audio frequency signal on the basis of the signal level and what sort of modulation technique was employed on the basis of features of the audio frequency signal such as peak-to-peak intervals and similarity to reference waveforms so that the nibble stream or the external audio signal is exactly reproduced from the audio frequency signal.

Owner:YAMAHA CORP

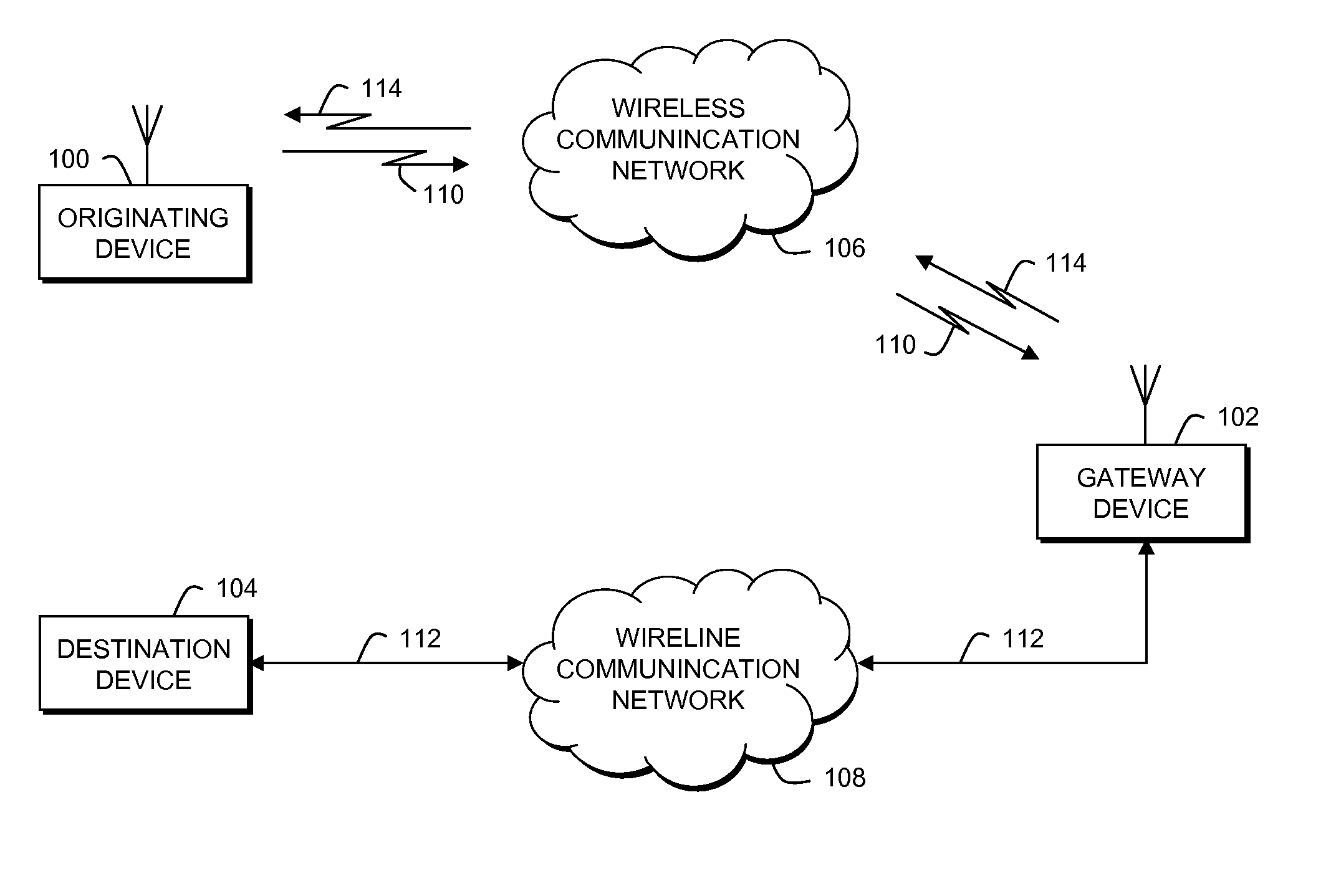

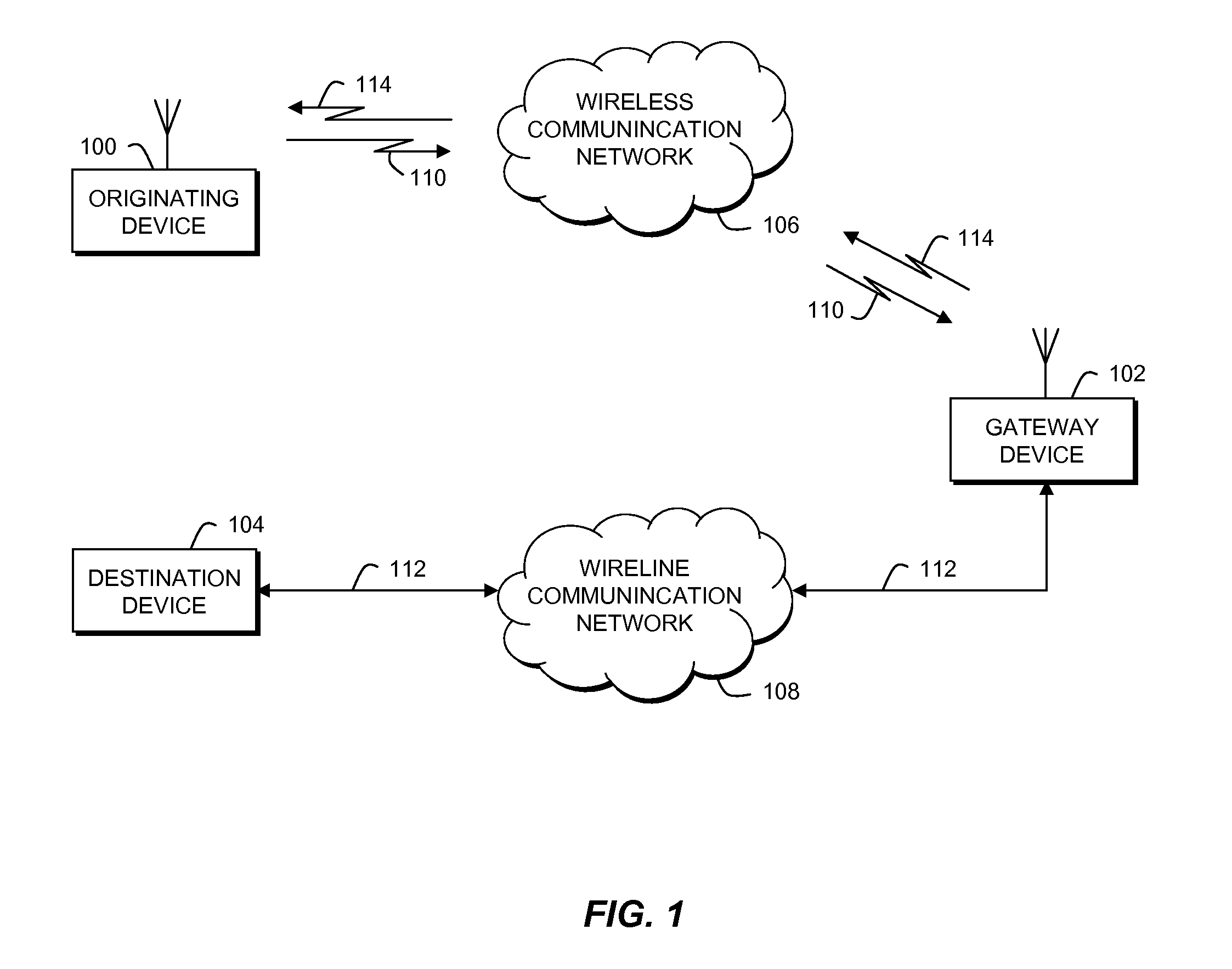

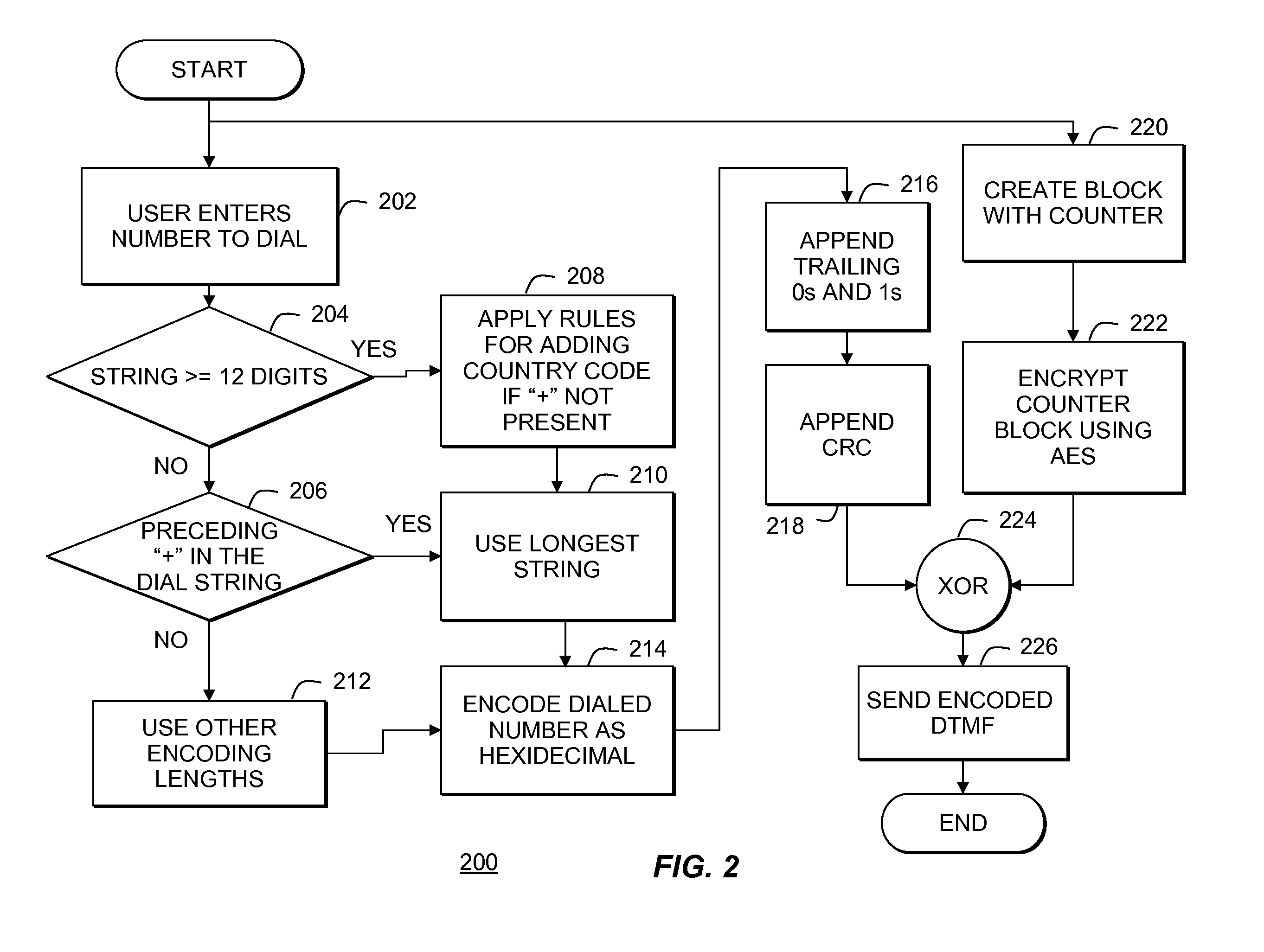

Secure call dtmf signaling

A method and system for secure call Dual-Tone Multi-Frequency (DTMF) signaling includes entering (202) dial string of a telephone number of a destination device, assigning (210, 212) the dial string to a predefined string having a total length that is greater than the dial string such that there will be at least one leading hexadecimal bit in the predefined string length that is not used when the entered dial string is converted to a hexadecimal, converting (214) the dial string to hexadecimal, reversing the order of the hexadecimal, and placing the reversed hexadecimal at the beginning of the predefined string, appending (216) “one” bits to the predefined string length indicating how many nibbles of the predefined string length are unused, if any, and appending the remaining intervening unused bits in the predefined string length to “zero” bits, and sending (226) the encoded string length.

Owner:SYMBOL TECH LLC

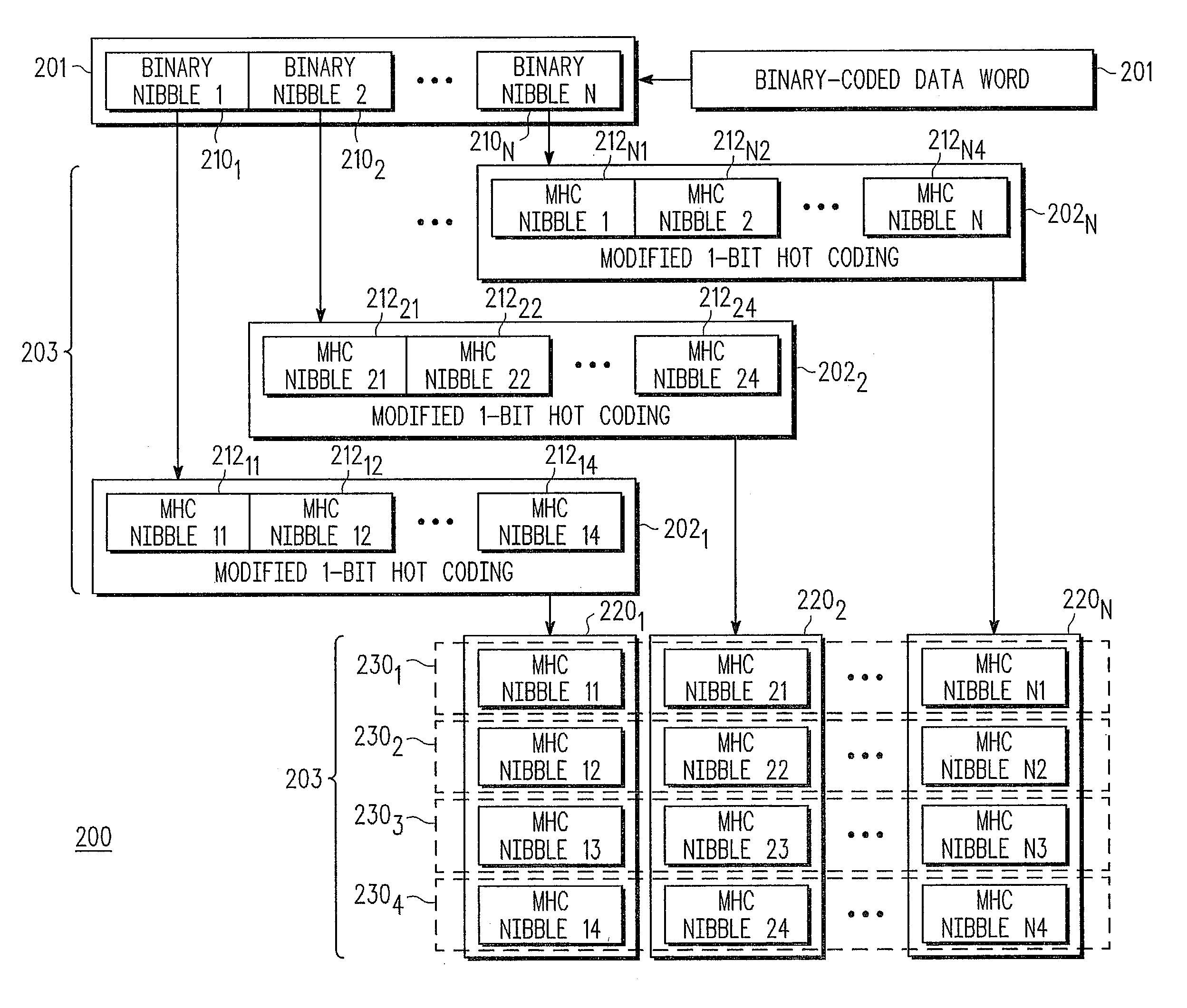

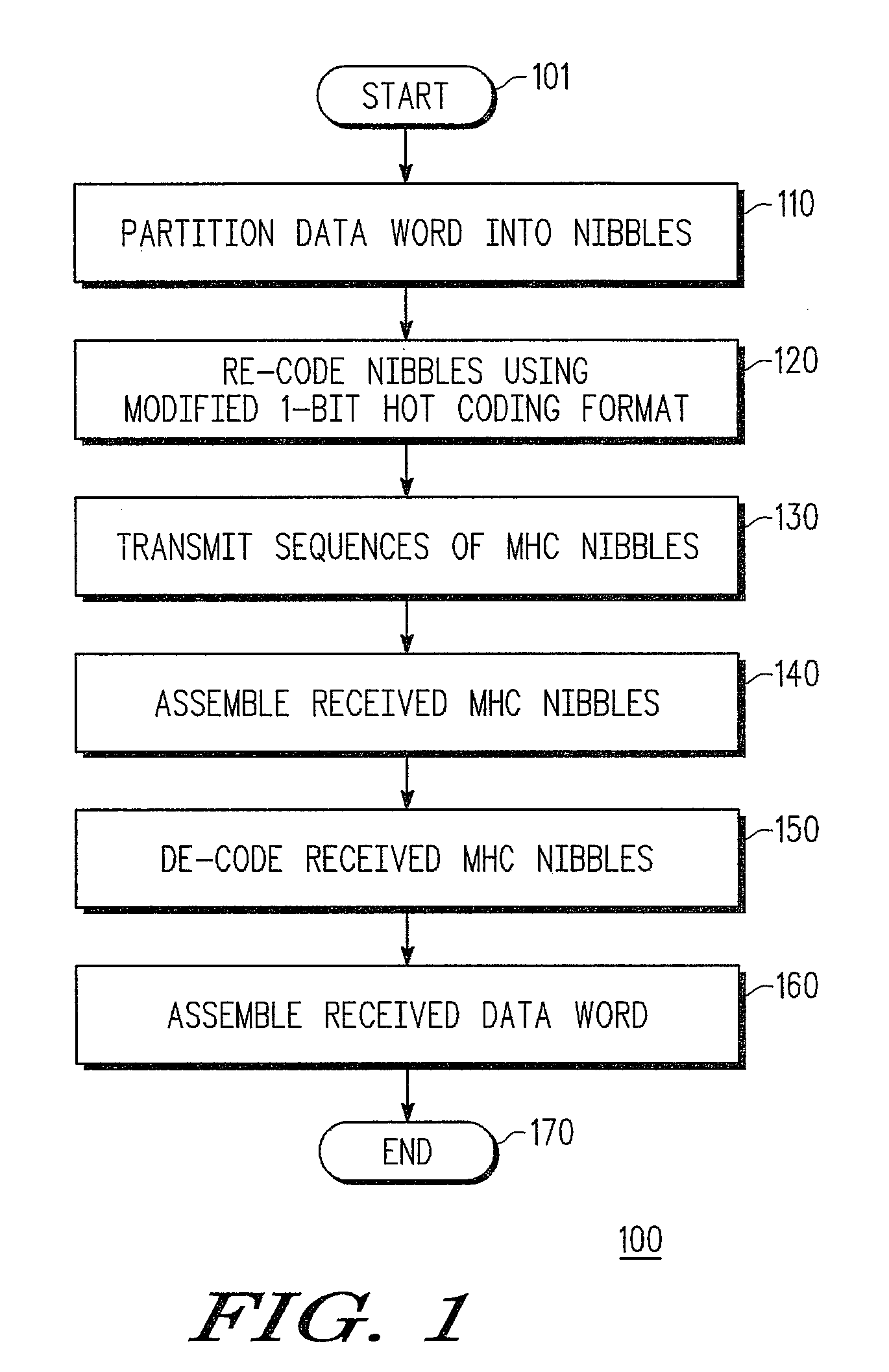

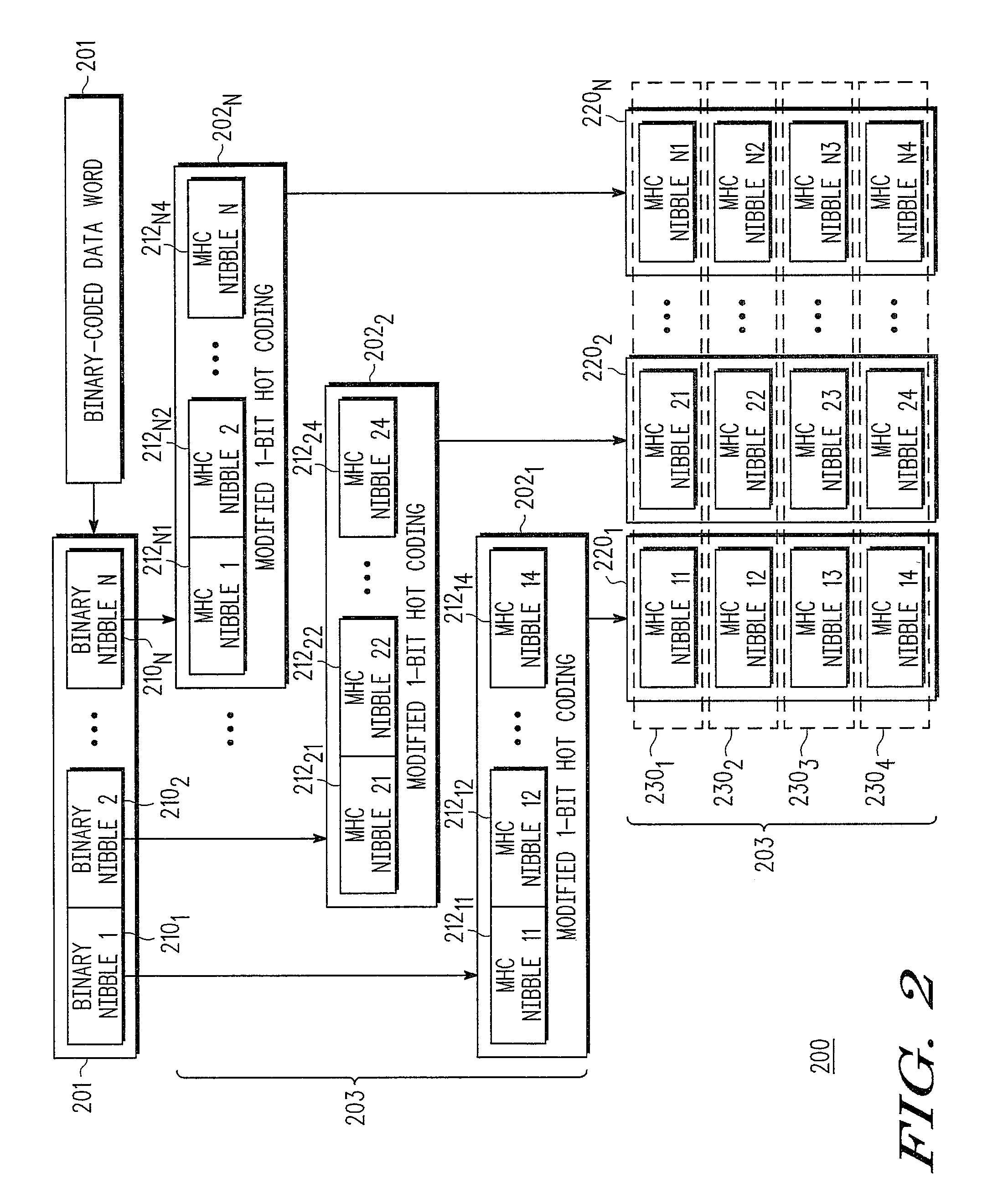

Method and system for transmitting data

A method and system for transmitting binary-coded data use partitioning of data words in a plurality of data nibbles. The data nibbles are coded using modified a 1-bit hot coding format that transforms a data nibble in a data segment including a plurality of bit groups. A change in a digital state at a bit position in a more significant bit group is maintained at that bit position in less significant bit groups, and information is transmitted in a form of a transition between digital states. The data segments are transmitted in phases each including one bit group from each data segment. At a receiving terminal, the bit groups are converted back in the binary-coded data words. In one application, the invention is used to reduce power consumption during data transmissions to and from an integrated circuit device.

Owner:NXP USA INC

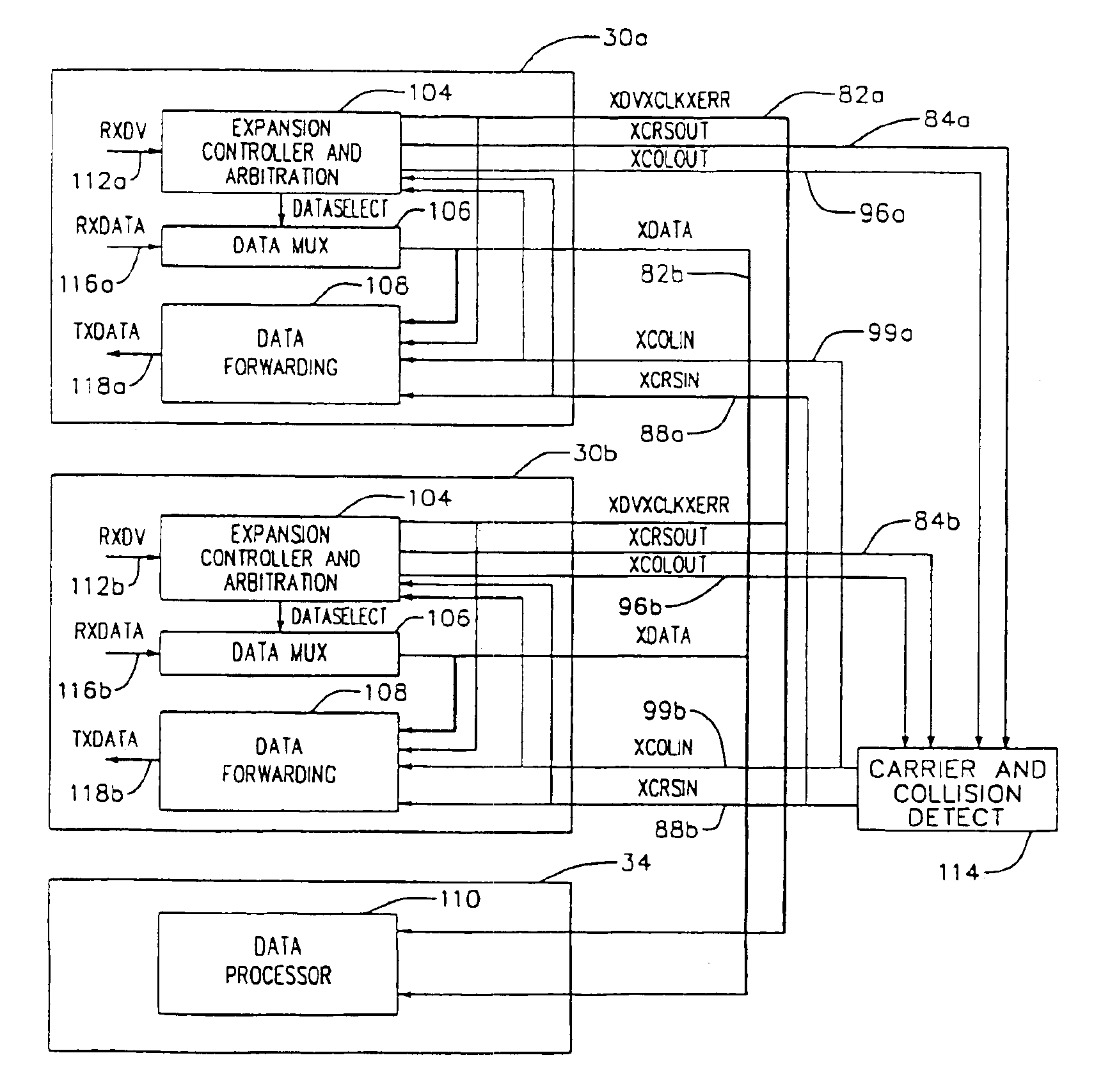

System for and method of providing a header and a trailer in data packets

Owner:AVAGO TECH INT SALES PTE LTD

Base station having a hybrid parallel/serial bus interface

A hybrid serial / parallel bus interface for a base station has a data block demultiplexing device. The data block demultiplexing device has an input configured to receive a data block and demultiplexes the data block into a plurality of nibbles. For each nibble, a parallel to serial converter converts the nibble into serial data. A line transfers each nibble's serial data. A serial to parallel converter converts each nibble's serial data to recover that nibble. A data block reconstruction device combines the recovered nibbles into the data block.

Owner:INTERDIGITAL TECH CORP

Hybrid parallel/serial bus interface

Owner:INTERDIGITAL TECH CORP

Method for proving error correction in codeword and method and system for error correction

Owner:INT BUSINESS MASCH CORP

Method for the prioritization of database entries

InactiveUS6839799B2Process economyIncrease speedDigital data information retrievalDigital data processing detailsExact matchNibble

A method is provided for prioritizing the entries in a database, where each entry is composed of multiple dimensions. Prioritization is required when there are multiple matches in the database. The number of matches can be the same as the number of entries in the database. To prioritize such a huge number of entries in a minimum number of clock cycles, a distributed prioritizer is implemented by partitioning stored binary data into half nibbles comprising of two bits of data each. Each half nibble is encoded into an expanded format allotting priority value to the stored encoded half nibbles. The stored encoded half nibbles are compared across a word array to determine an exact match.

Owner:IDT CANADA

Method for recording asynchronously produced digital data codes, recording unit used for the method, method for reproducing the digital data codes, playback unit used for the method and information storage medium

InactiveUS20050018581A1Exclude dataTelevision system detailsElectrophonic musical instrumentsDigital dataData stream

A recording and reproducing system is broken down into a recording unit for producing a digital audio data signal from MIDI music data words asynchronously produced at irregular intervals and a playback unit for reproducing the MIDI music data codes from the digital audio data signal, wherein synchronous data nibbles are supplemented in the irregular intervals among the MIDI music data words for producing a data stream, and the digital audio data signal is produced from the data stream through a differential phase shift keying and a phase code modulation so as to record the MIDI messages in a digital versatile disk at high dense.

Owner:YAMAHA CORP

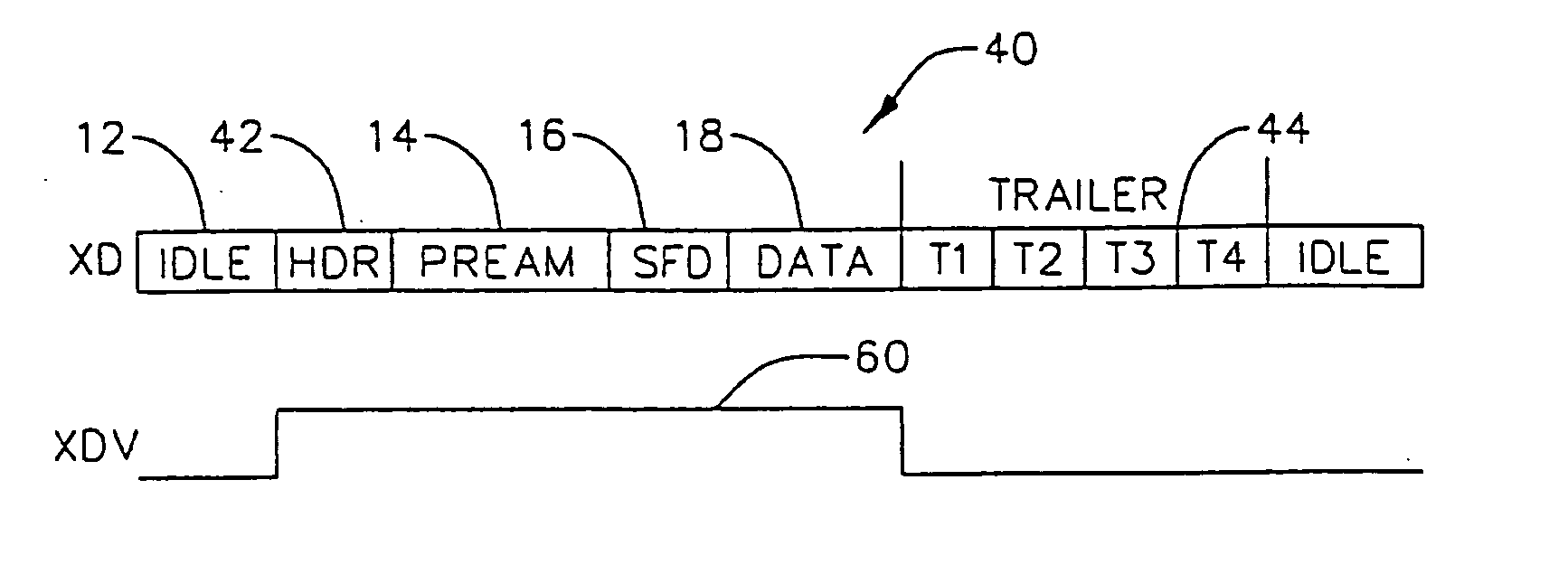

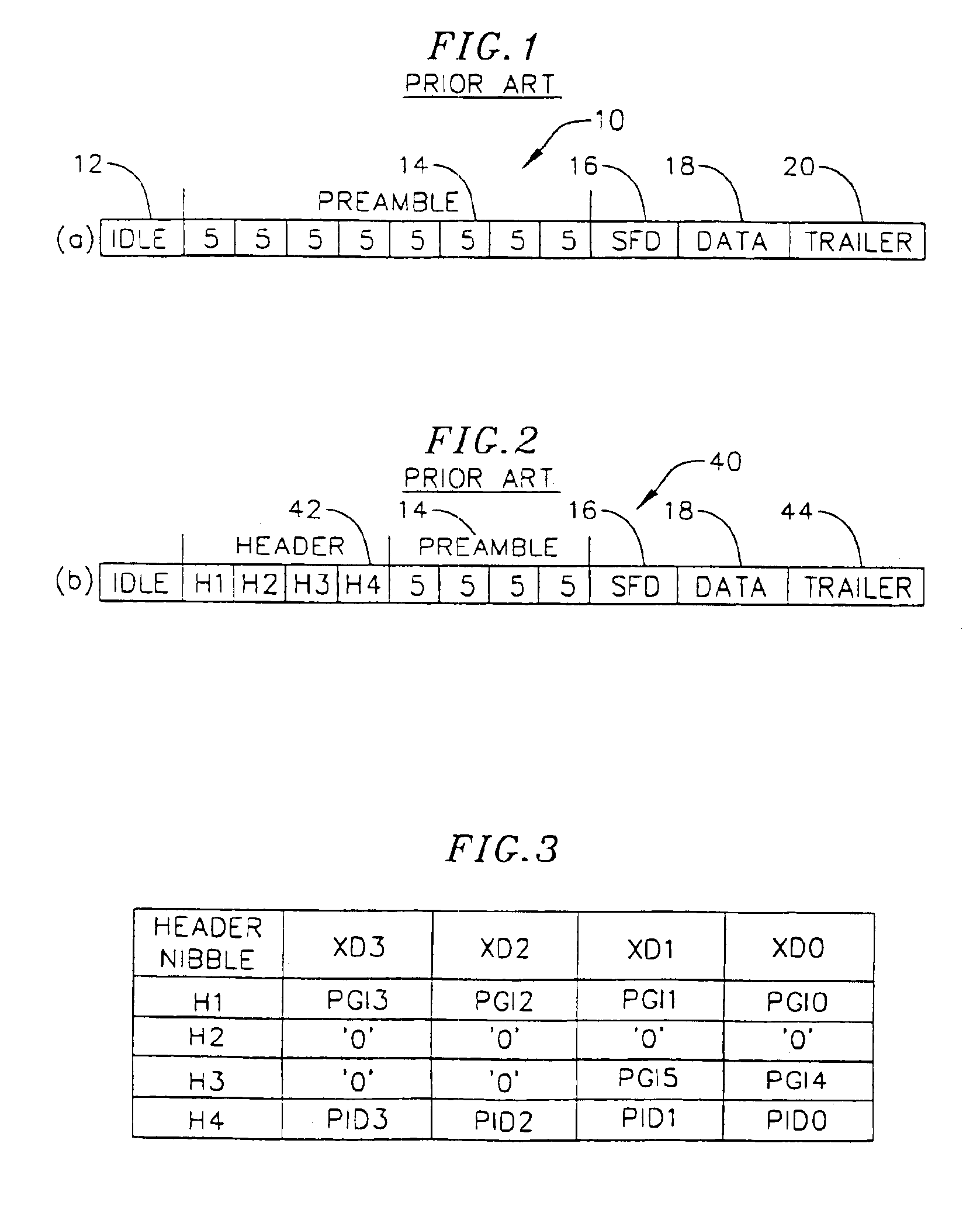

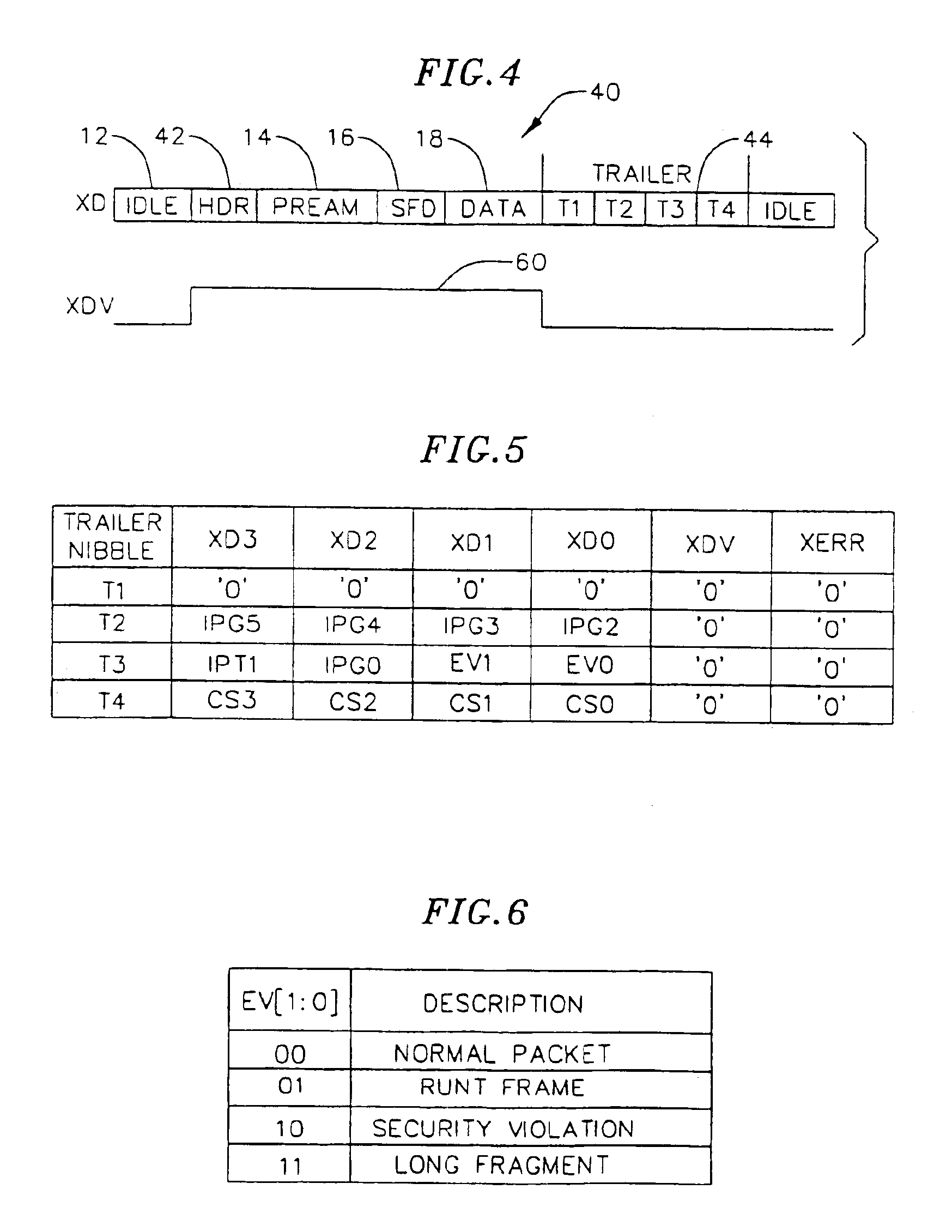

System for and method of providing a header and a trailer in data packets

InactiveUS6909712B2Multiplex system selection arrangementsTime-division multiplexNetwork packetNibble

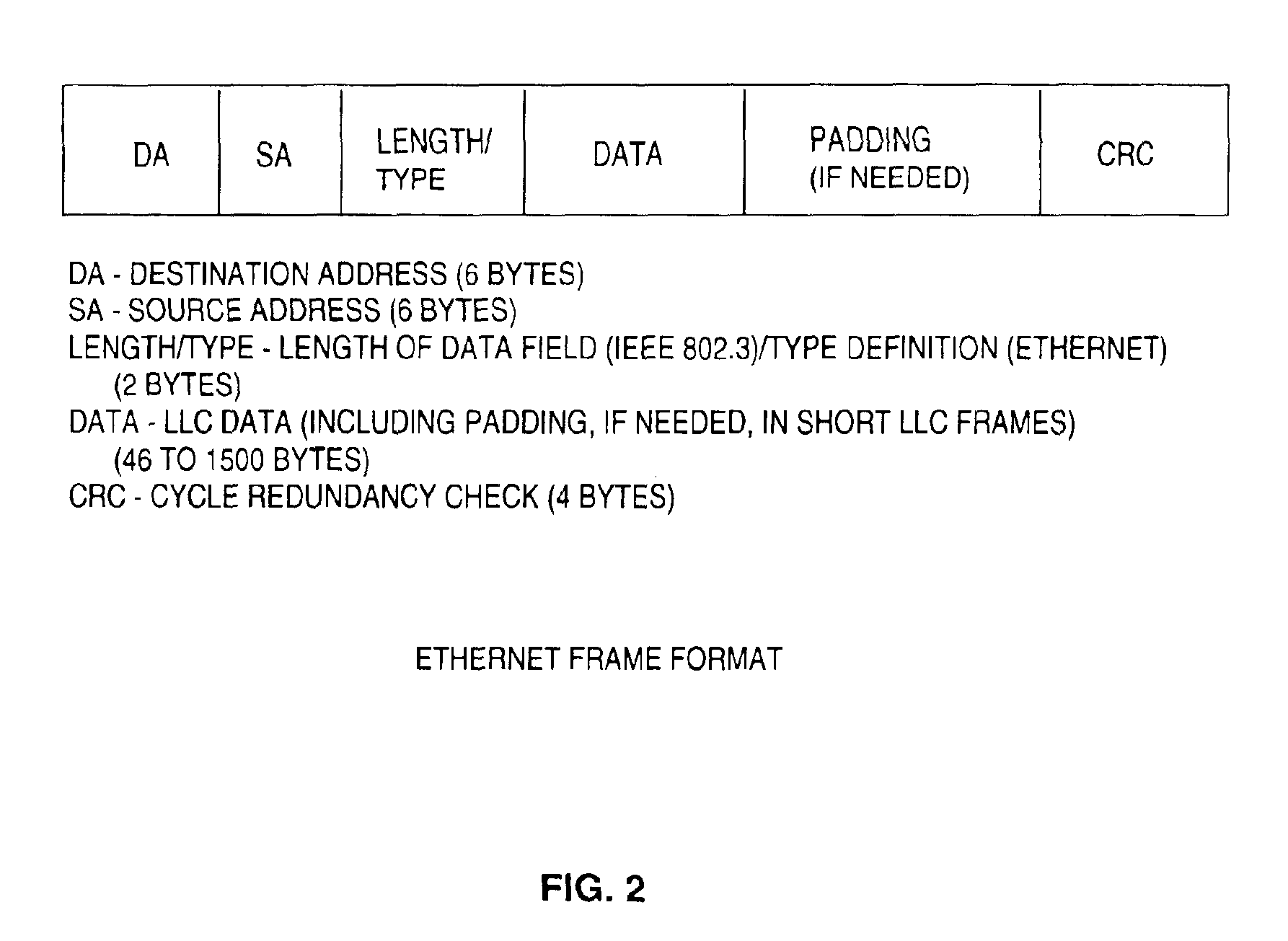

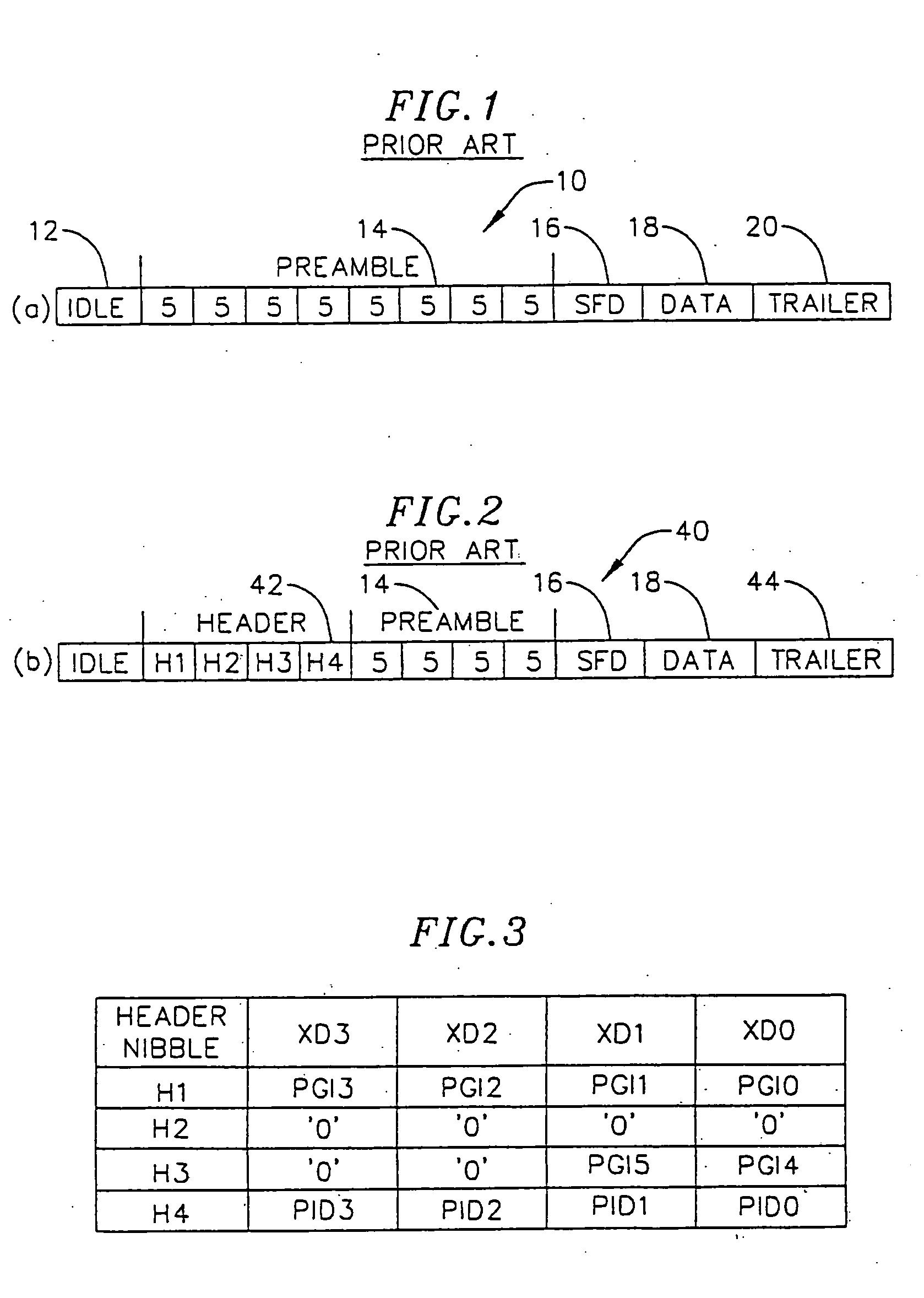

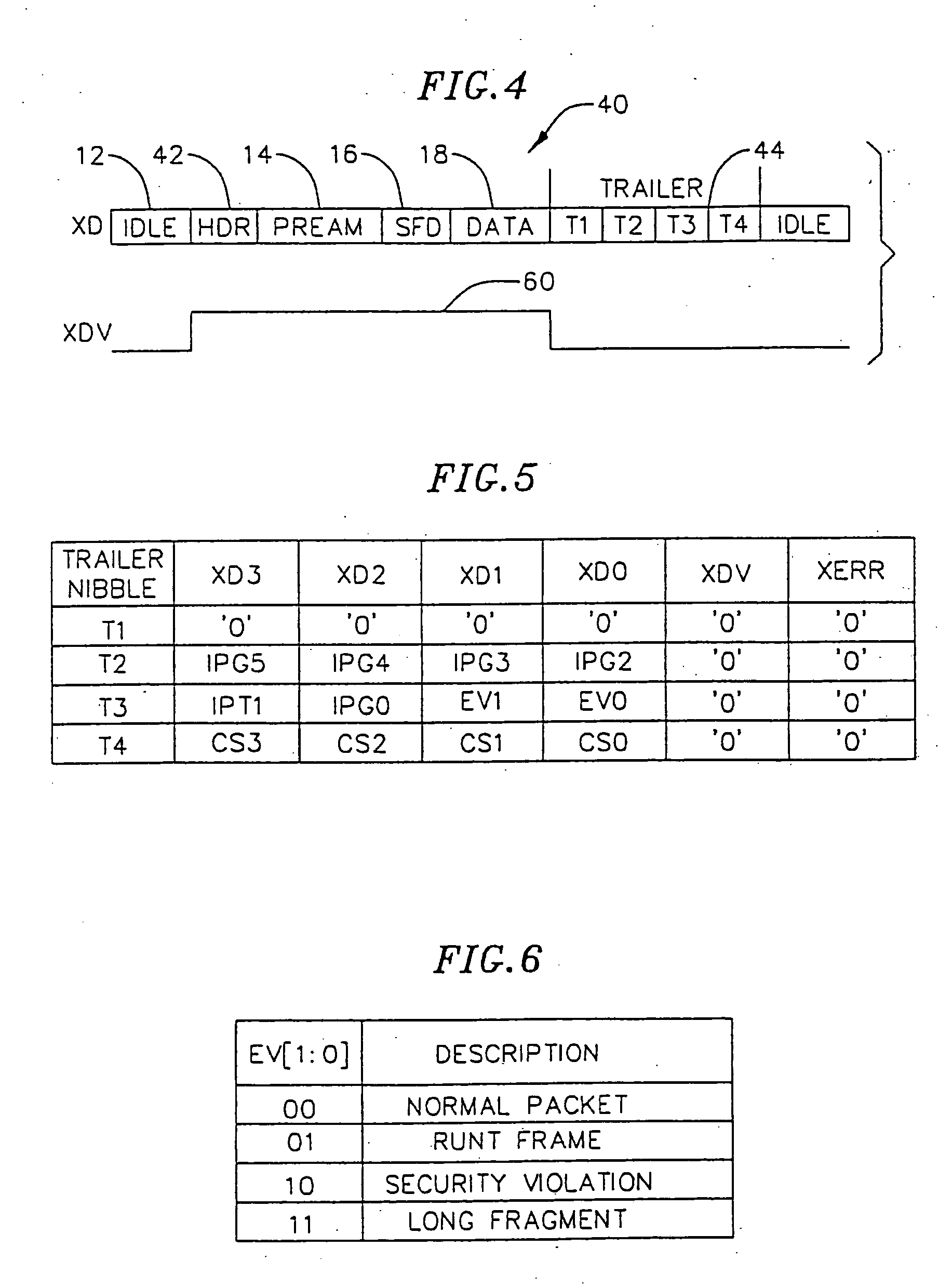

Each packet normally consists of a preamble, start-of-frame delimiter and data. The preamble has nibbles each having a particular format. A header substituted for preamble nibbles by an individual one of the originating devices in a plurality, and an individual one of the ports in such originating device, indicates such originating device and such port. Such port in such originating device sends such modified packet to others of the originating devices and to an observing station. The header format is such that the last nibble in the header and the remaining preamble portion will not be confused with any two (2) nibbles in the header. A particular one of the originating devices indicated in the data converts the header back to the preamble format and transmits the converted packet to a receiving station. The observing station records the individual originating device, and the individual port in such device, indicated in the header. Each packet includes at its end a trailer formed from a plurality of nibbles and indicating whether or not a collision has occurred between such packet and a packet from another one of the originating devices. The trailer in each packet may also indicate additional information—e.g. whether the packet (a) is a normal packet originally formed, (b) is a runt packet, (c) is from an unacceptable source and (d) the delay between each packet end and the next packet start. The information in the trailer for each packet passes to the observing station.

Owner:AVAGO TECH INT SALES PTE LTD

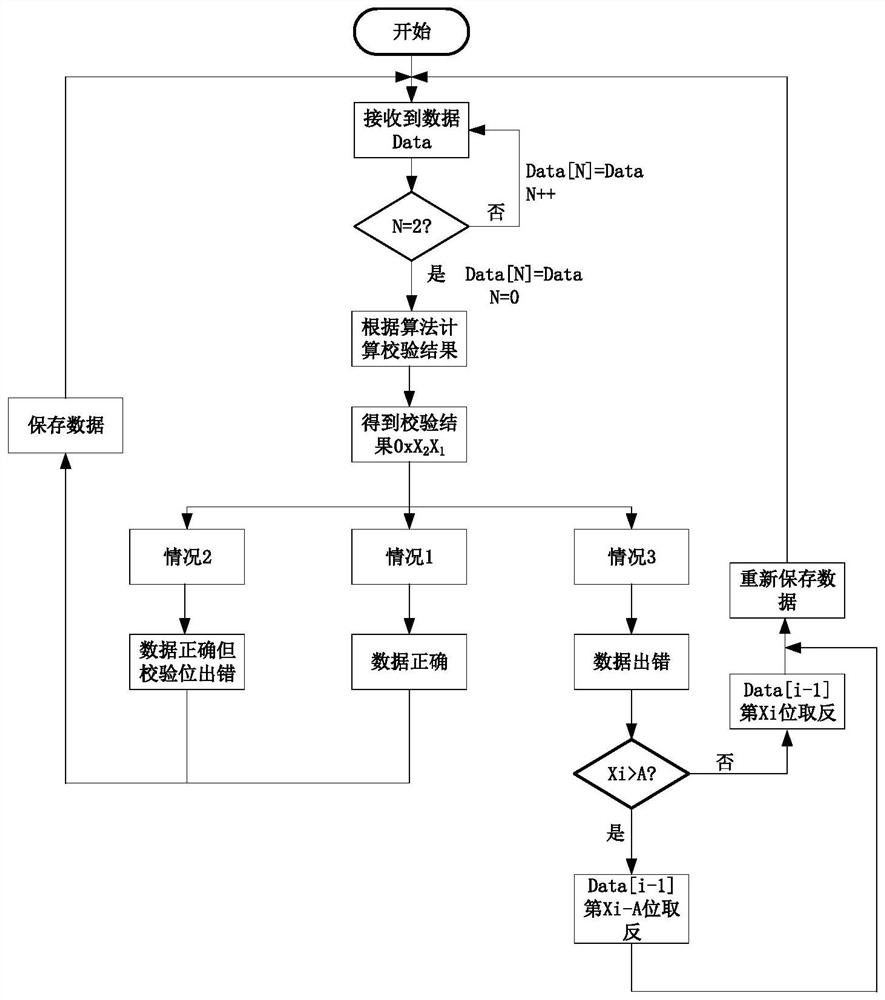

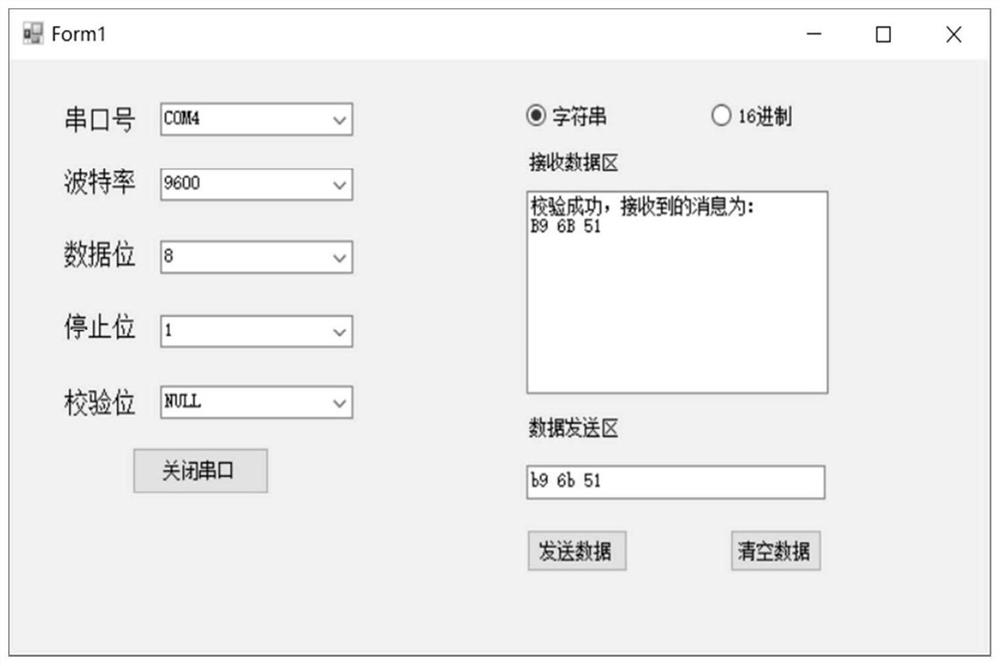

A serial communication error detection and correction method and device

ActiveCN111459707BImprove efficiencyOvercome the problem that the length cannot be sent through the serial portRedundant data error correctionHamming codeNibble

Owner:HUAZHONG UNIV OF SCI & TECH

User equipment having a hybrid parallel/serial bus interface

A hybrid serial / parallel bus interface for a user equipment (UE) has a data block demultiplexing device. The data block demultiplexing device has an input configured to receive a data block and demultiplexes the data block into a plurality of nibbles. For each nibble, a parallel to serial converter converts the nibble into serial data. A line transfers each nibble's serial data. A serial to parallel converter converts each nibble's serial data to recover that nibble. A data block reconstruction device combines the recovered nibbles into the data block.

Owner:INTERDIGITAL TECH CORP