Test graphic generator of integrated circuit and test method thereof

A technology of integrated circuits and test patterns, which is applied in the fields of instruments, measuring circuits, measuring devices, etc., can solve the problems of increasing the difficulty of verifying circuit performance, complex structure, and high hardware overhead, and achieves improved test quality, product yield, and fault coverage. The effect of high test rate and reduced test power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

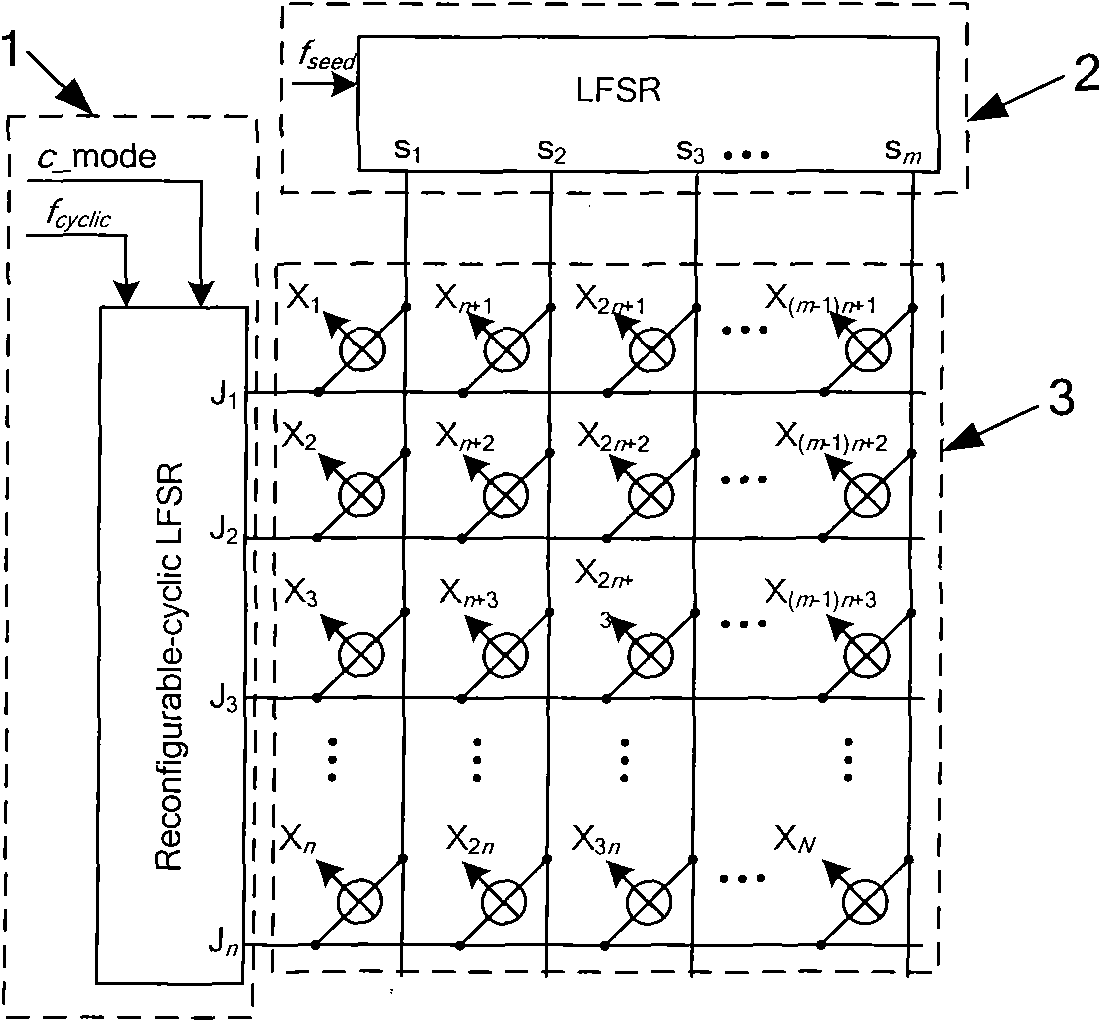

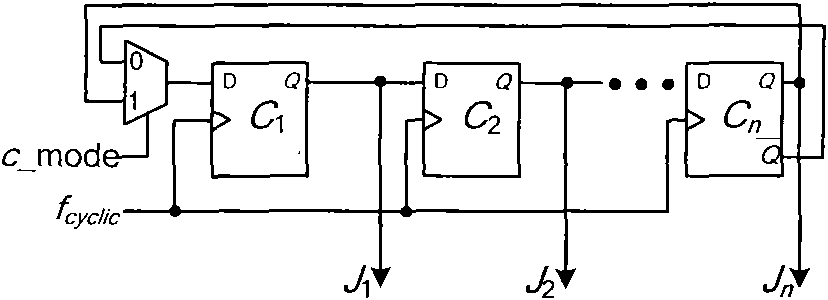

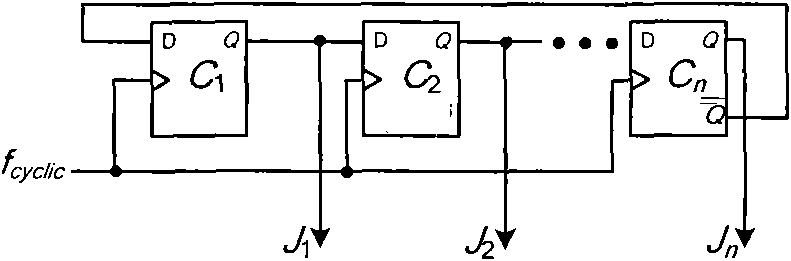

[0024] refer to figure 1 , is the test pattern generator of integrated circuit of the present invention, mainly comprises: the cyclic code linear feedback shift register (Reconfigurable-cyclic LFSR) 1 of reconfigurable single bit change, linear feedback shift register (LFSR) 2 and two Two-dimensional bit-XOR array (two-dimensional bit-XORarray)3.

[0025] Reconfigurable-cyclic LFSR (Reconfigurable-cyclicLFSR) 1 clocked at f cyclic , which generates a Johnson sequence J=[J 1 J 2 ...J n ], where n is a natural number. The generating end of the Johnson sequence is correspondingly connected to the lateral input end of the two-dimensional XOR gate array.

[0026] A linear feedback shift register (LFSR)2 based on primitive polynomials is used to generate the seed sequence, and its clock frequency is f seed , generate seed sequence S=[S 1 S 2 ... S m ], m is a natural number. The generating end of the seed sequence is correspondingly connected to the vertical input end of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More