Patents

Literature

769 results about "Minimum time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

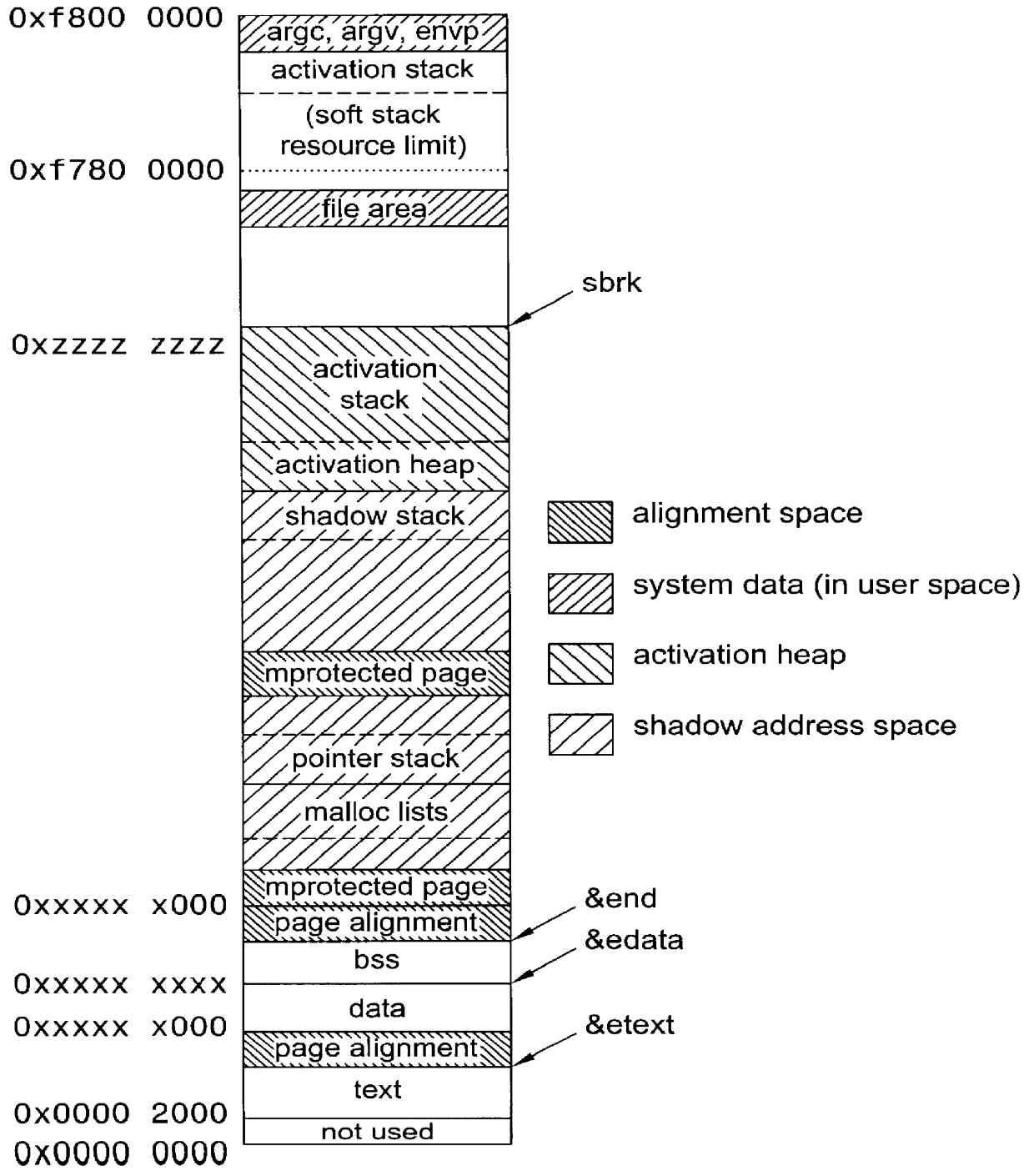

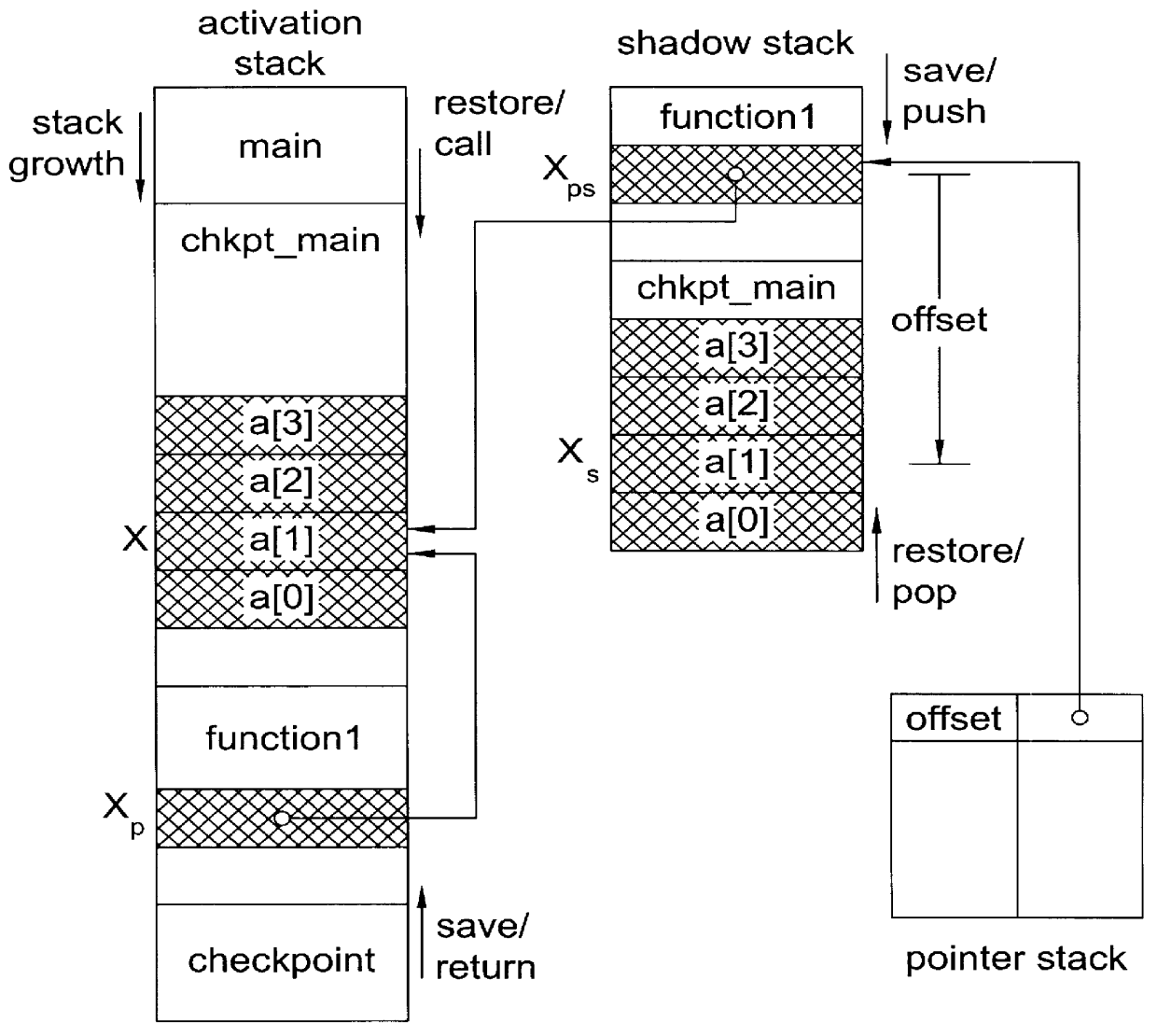

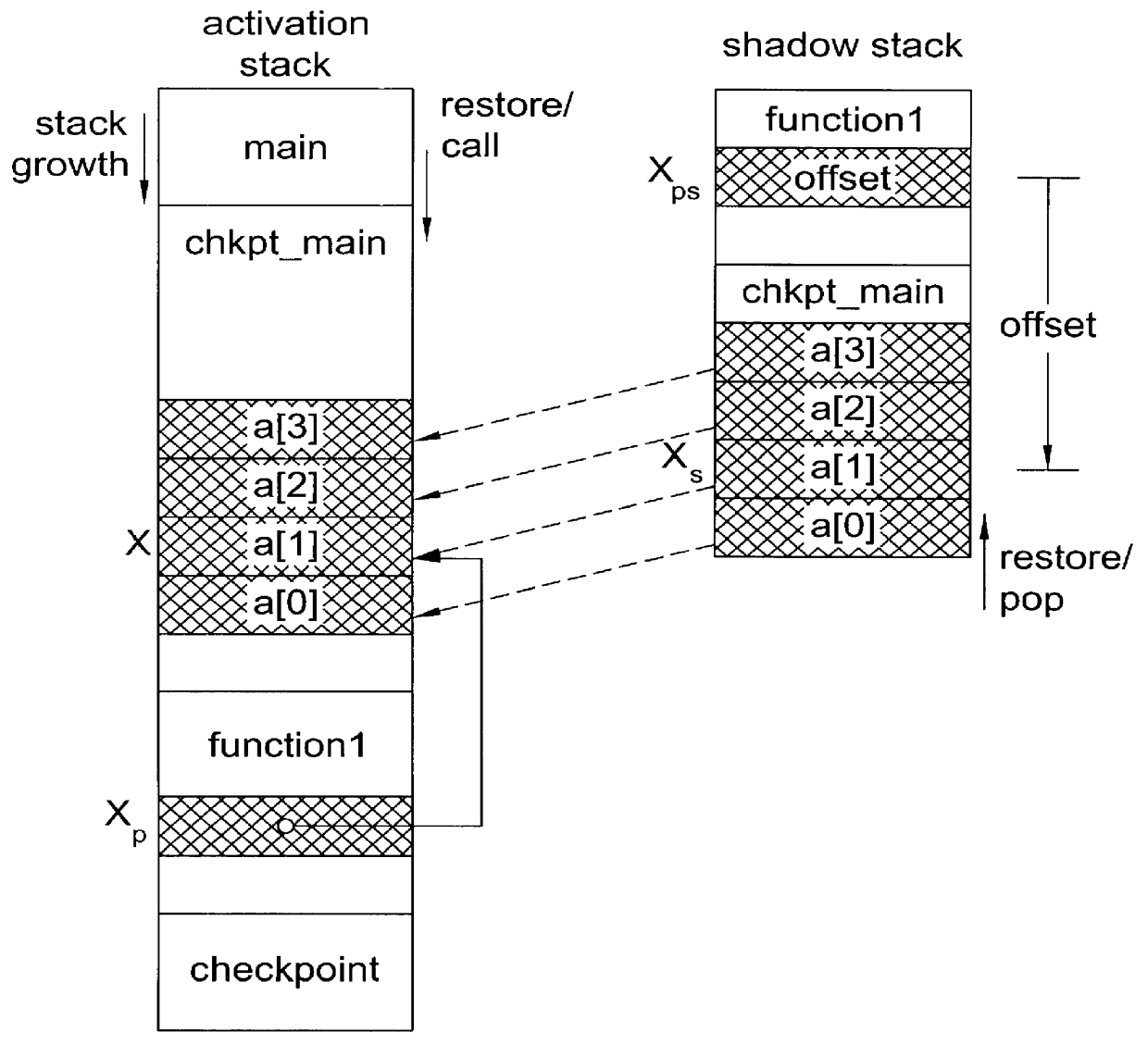

System and method for providing checkpointing with precompile directives and supporting software to produce checkpoints, independent of environment constraints

InactiveUS6161219AReduce overheadViable and practicalSoftware testing/debuggingSpecific program execution arrangementsOperational systemMinimum time

A method for portable checkpointing comprising the steps of: pre-compiling an input source code; and outputting an associated output source code which includes support for portable checkpointing. The portability of the checkpoints allows migration between systems with different hardware, software, and operating systems. The portable checkpoints are stored in a Universal Code Format (UCF) and are selectively activated at the next potential checkpoint marker after a MinTBC (Minimum Time Between Checkpoints) timer expires.

Owner:UNIV OF IOWA RES FOUND

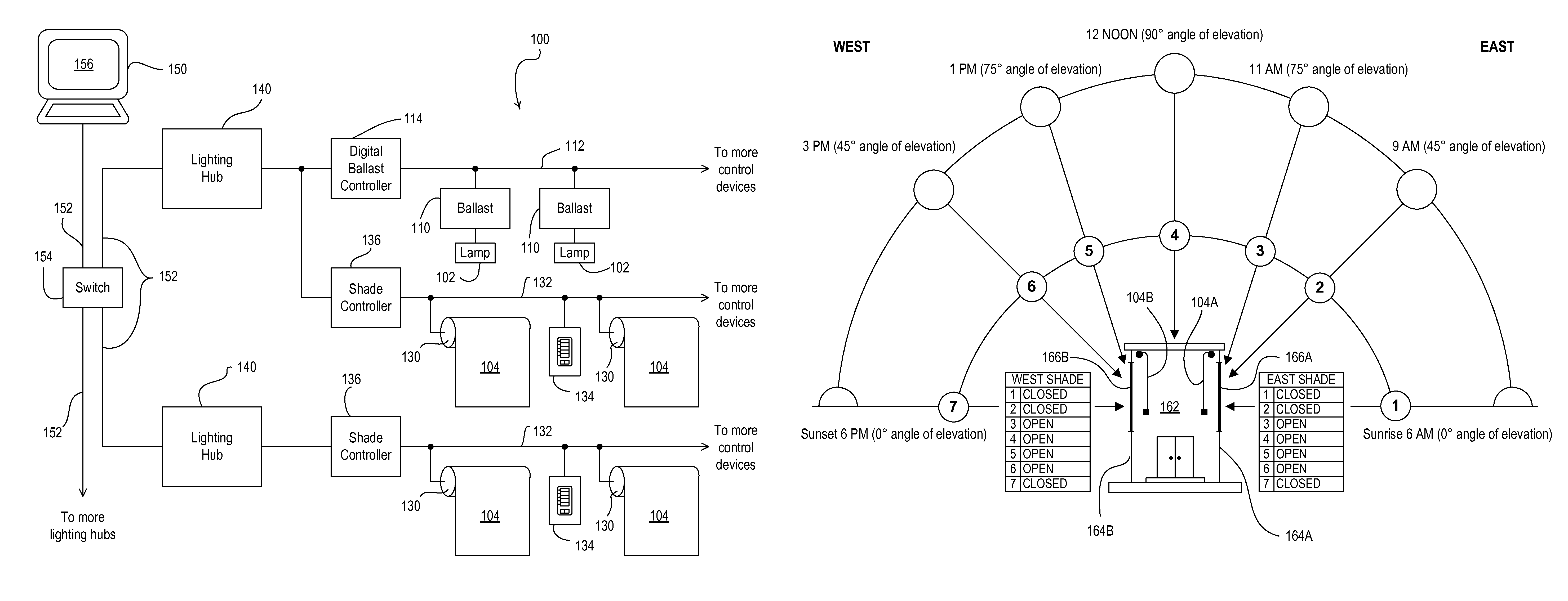

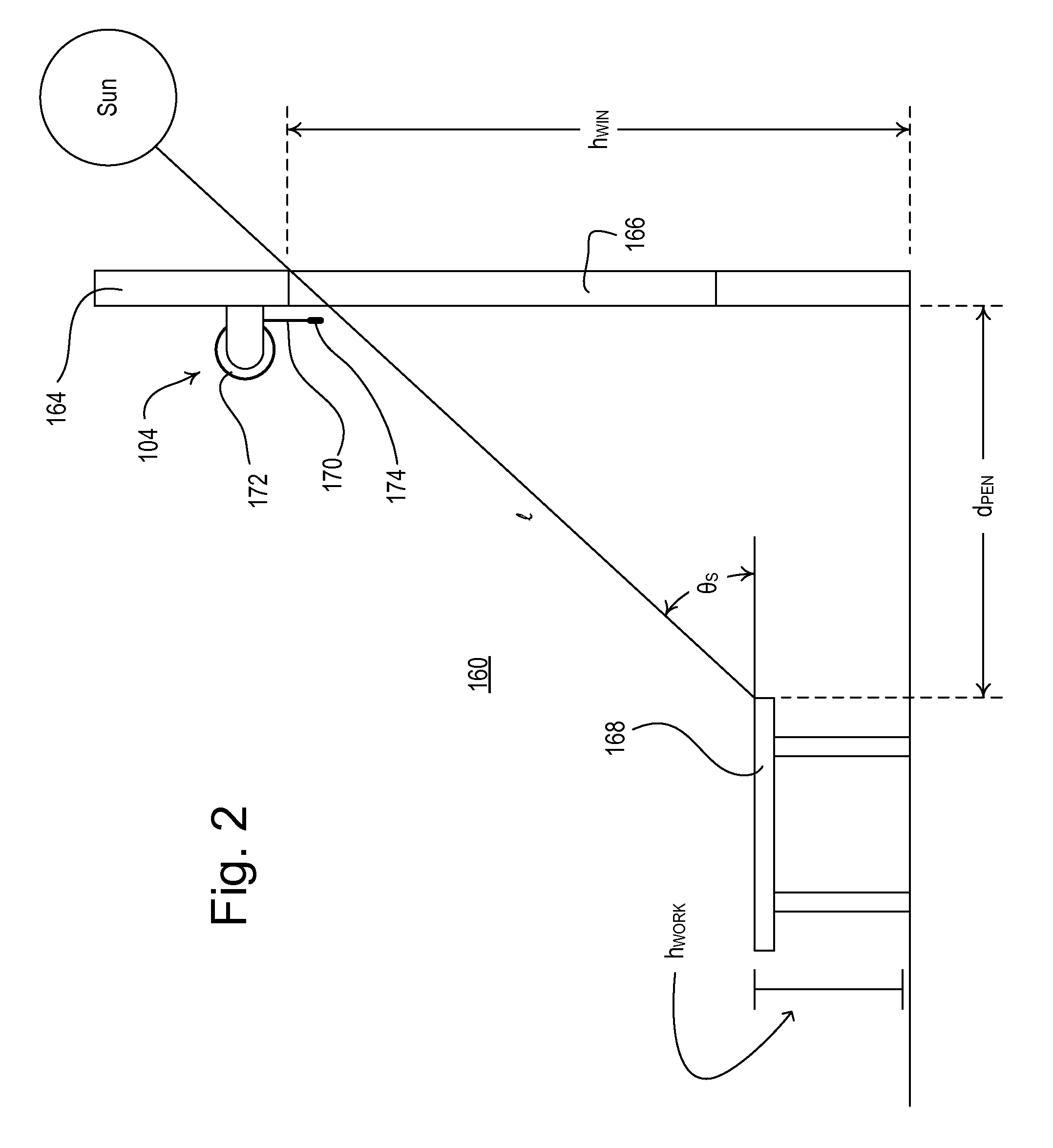

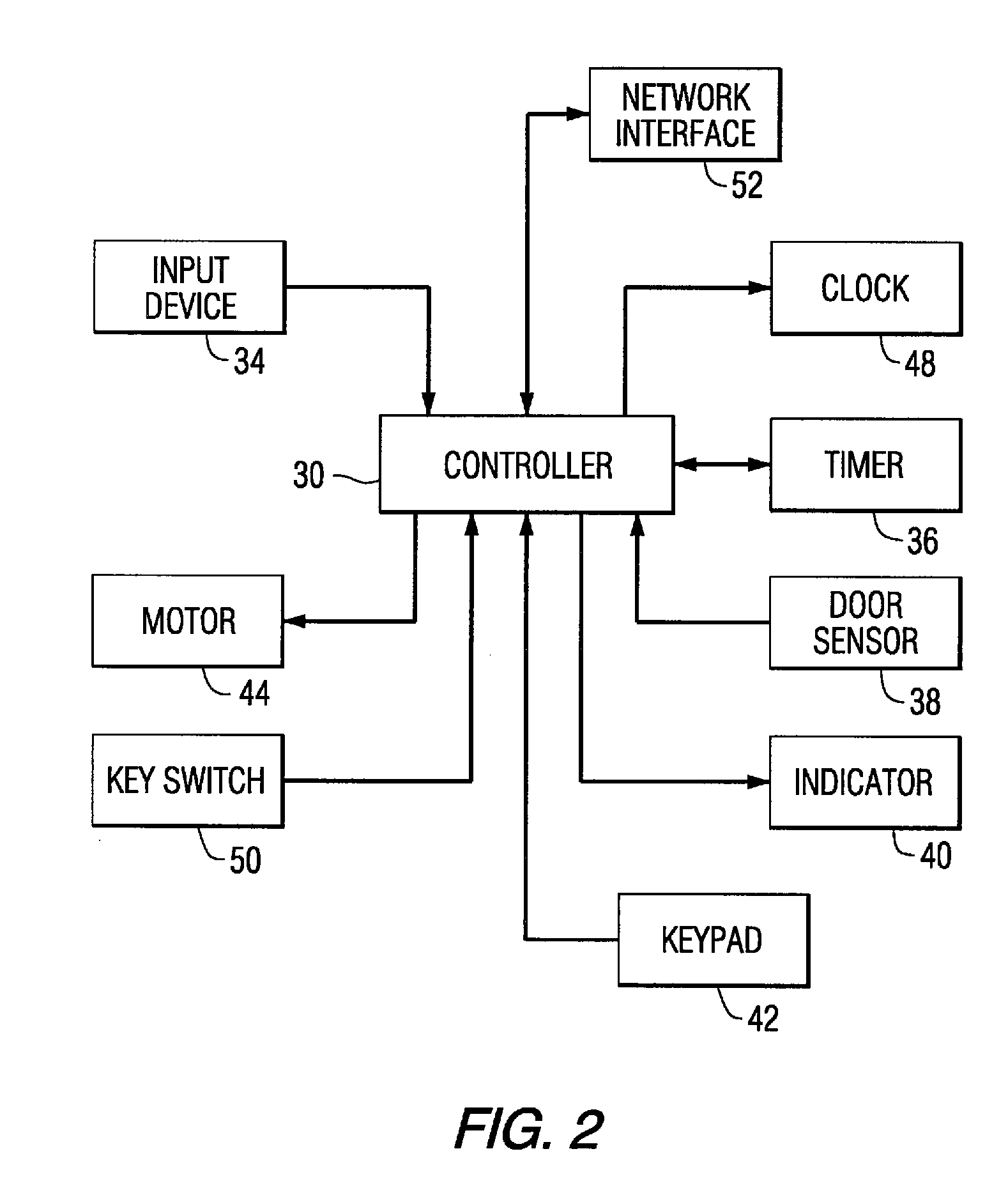

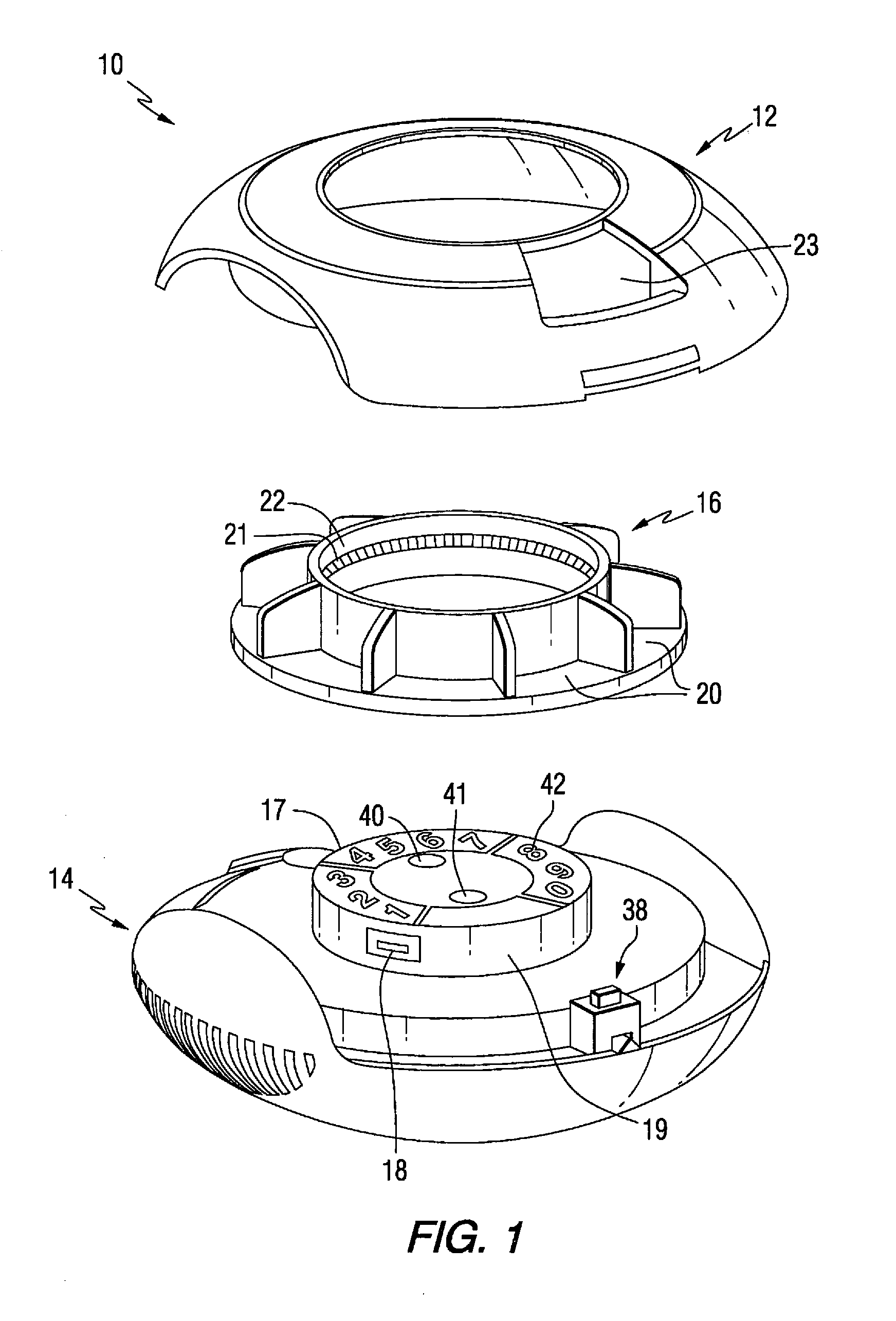

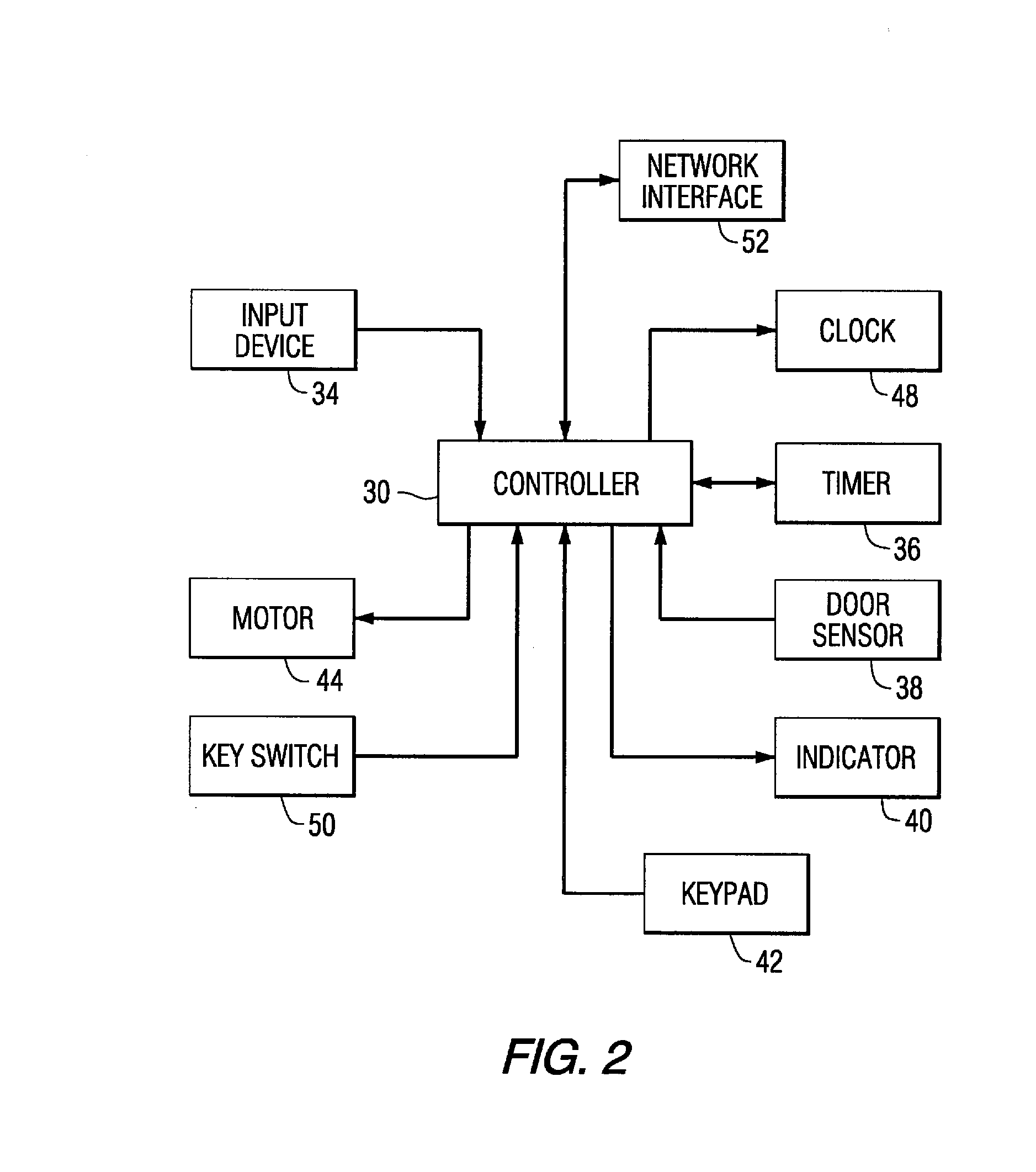

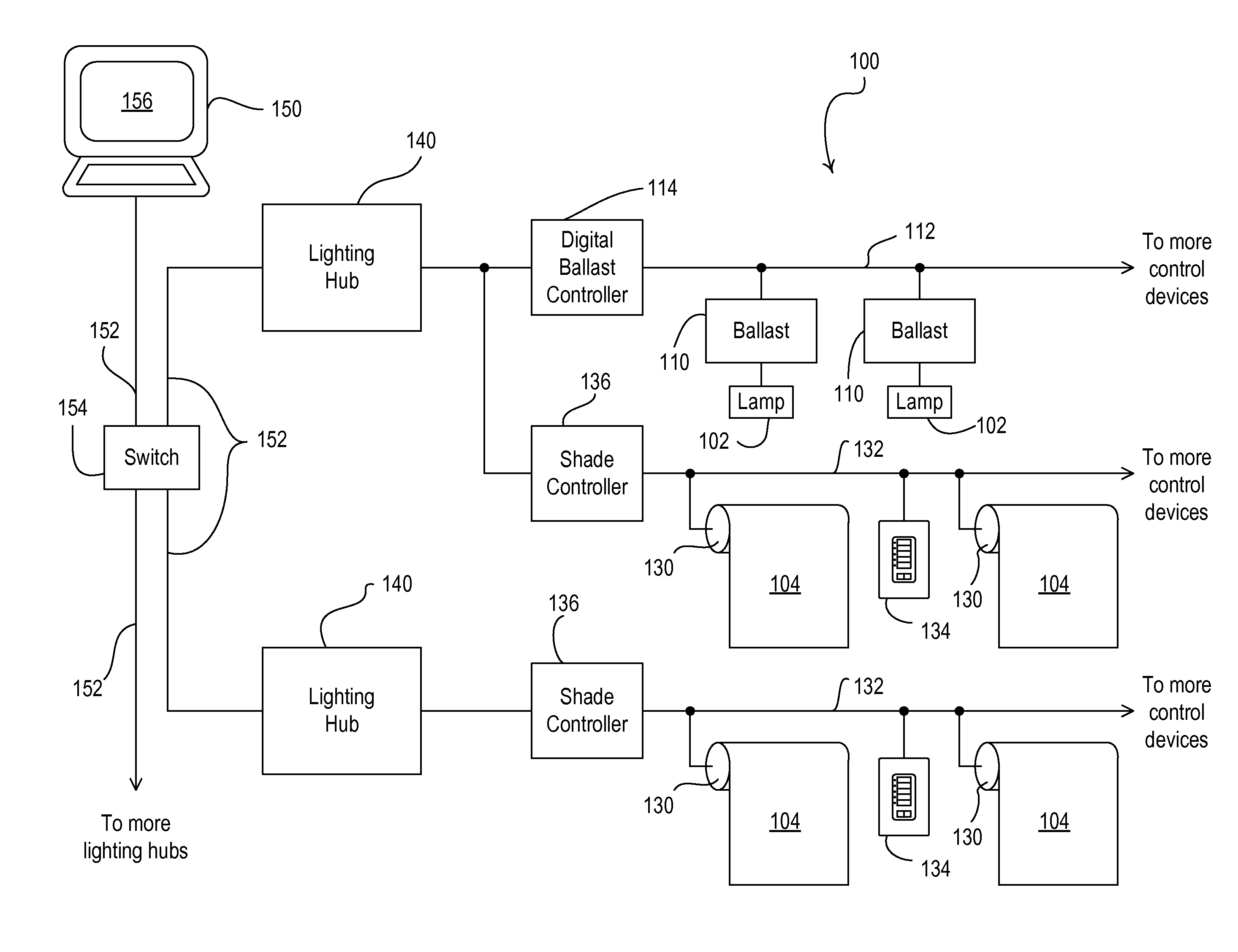

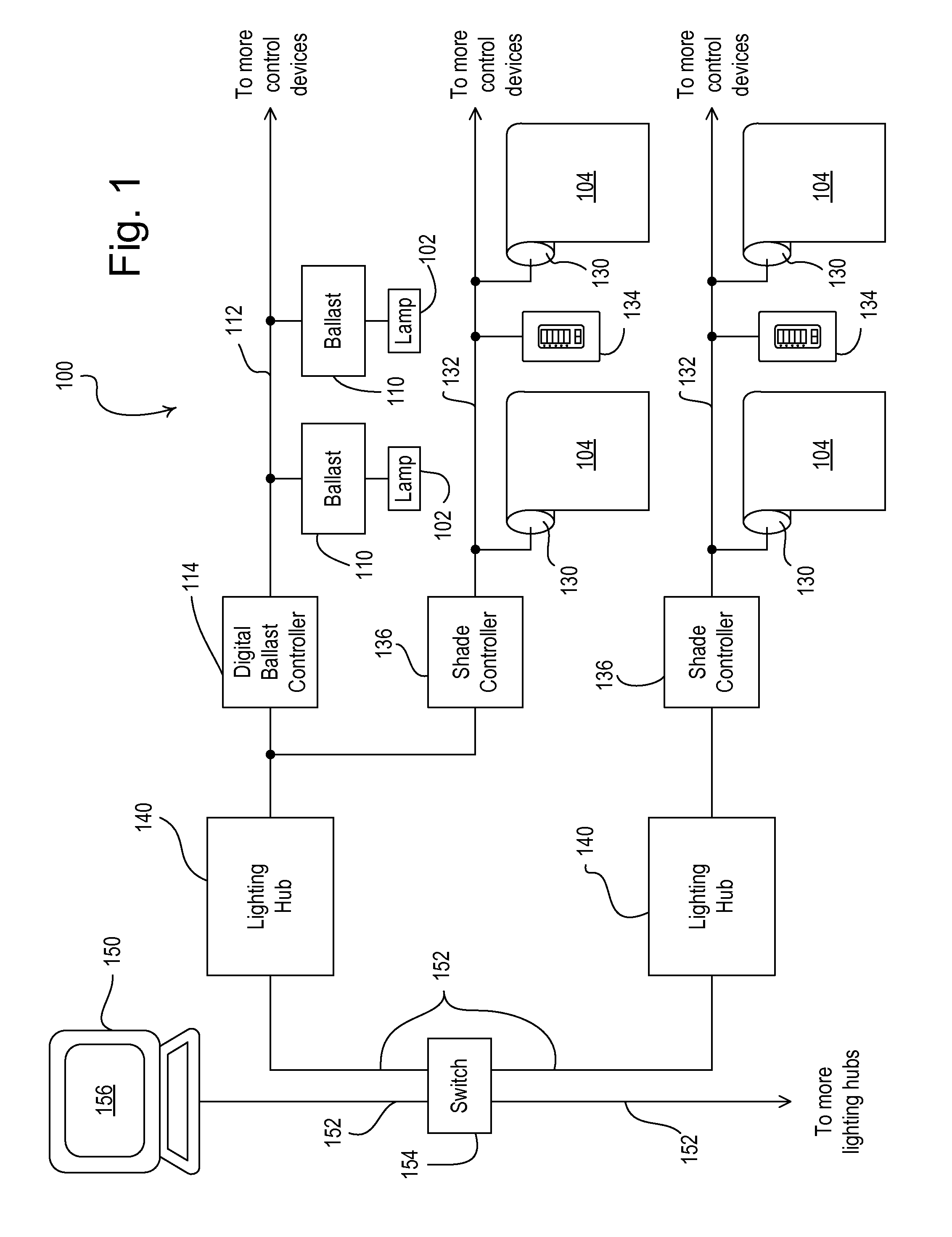

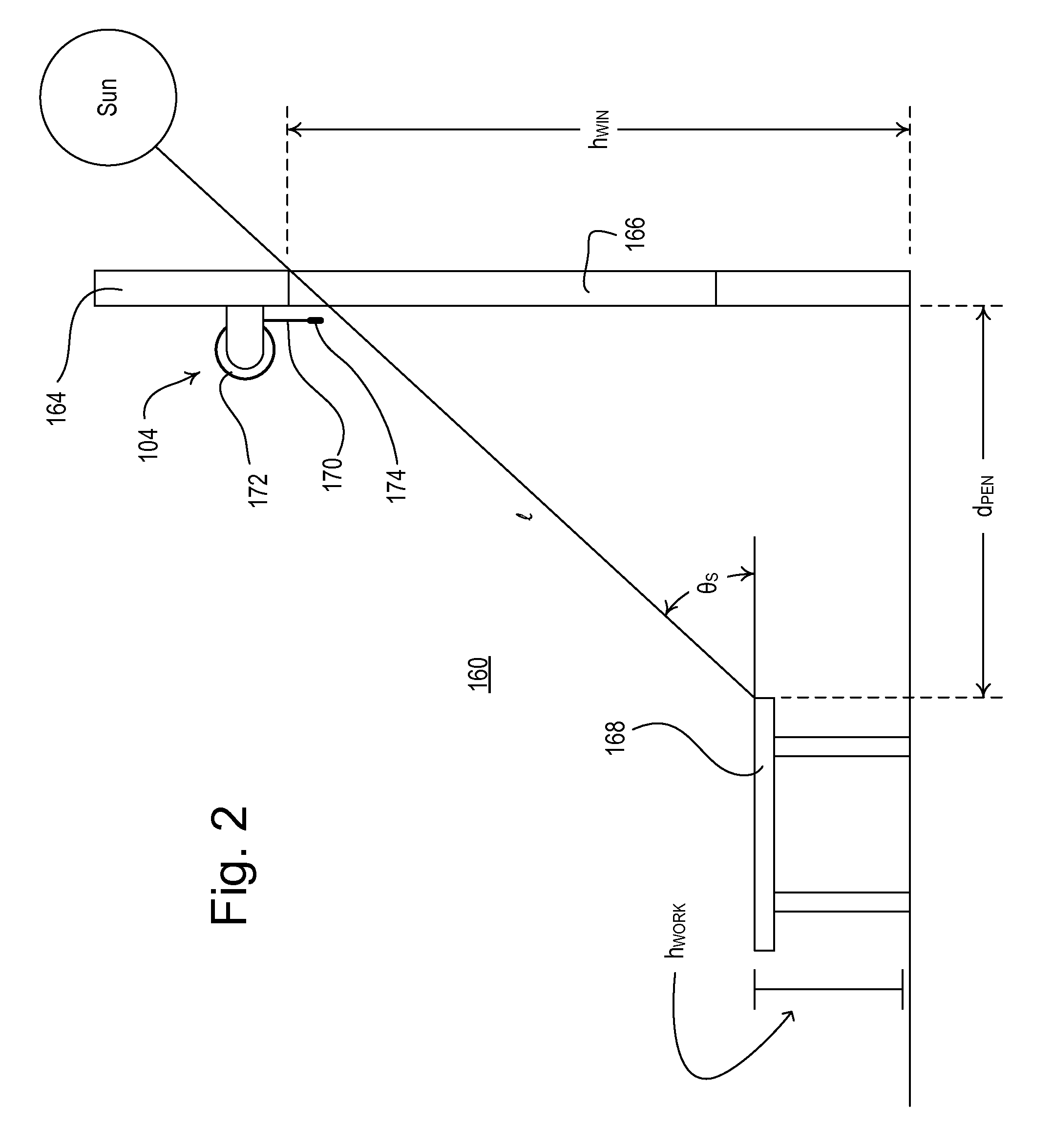

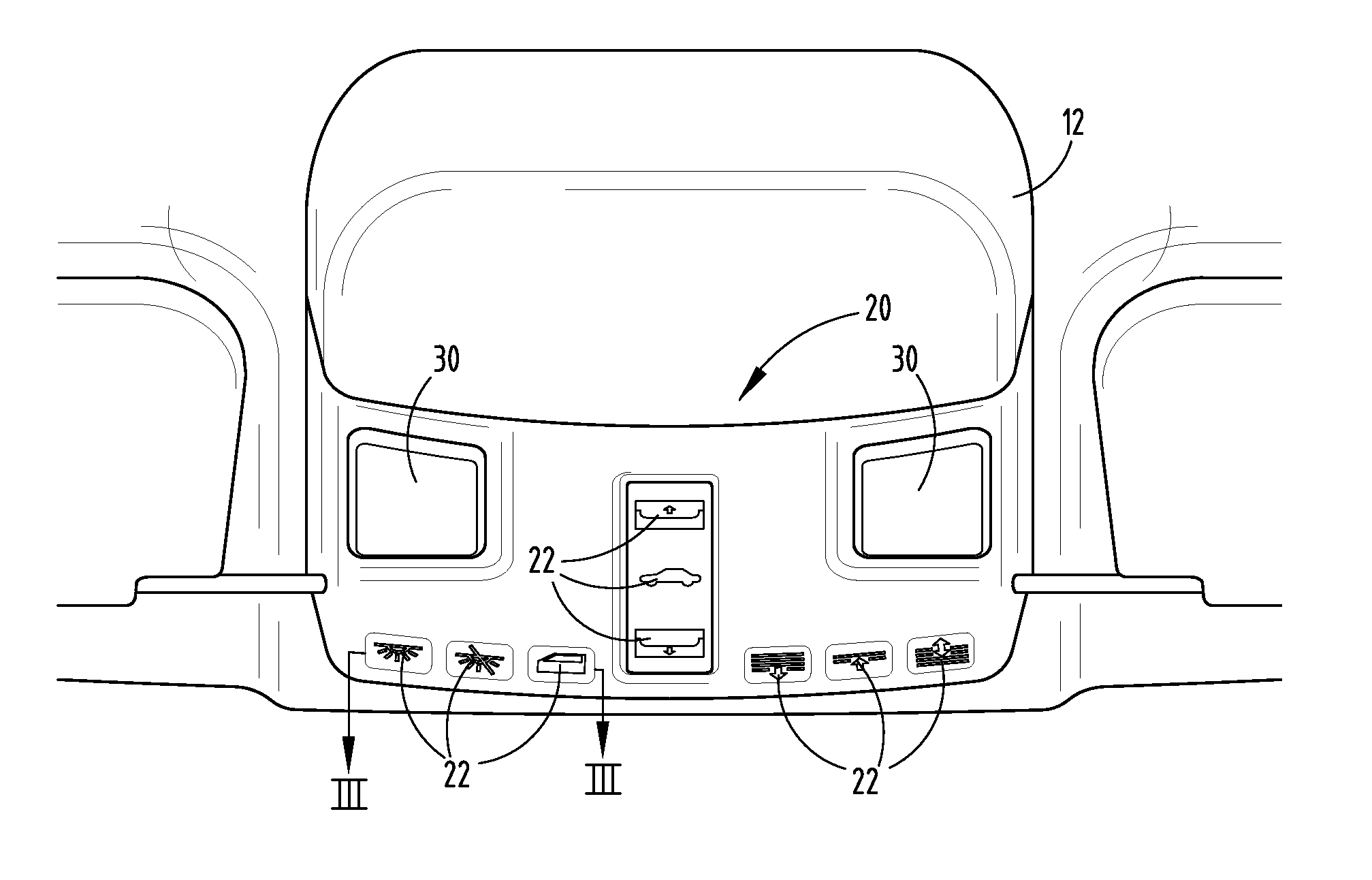

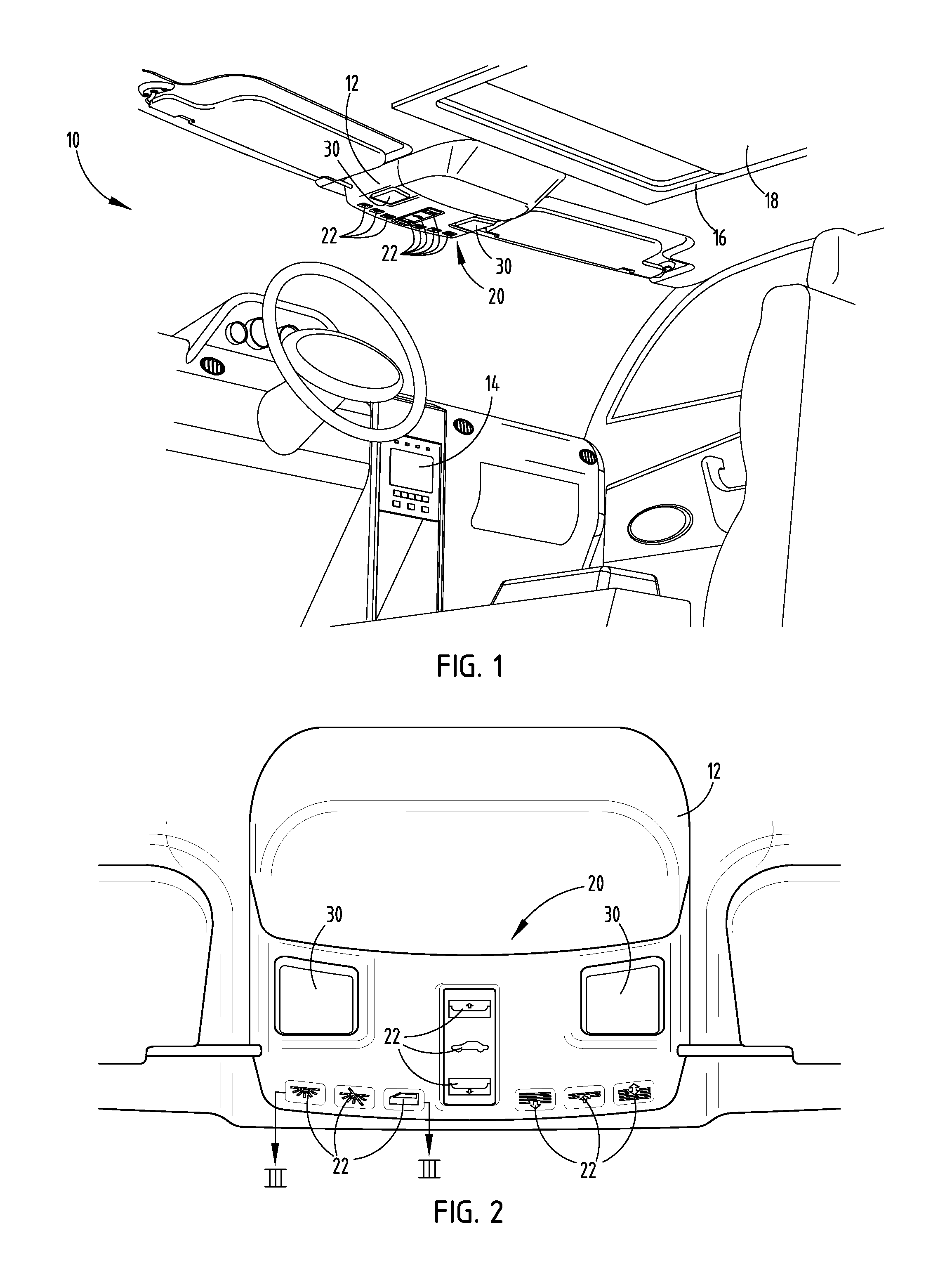

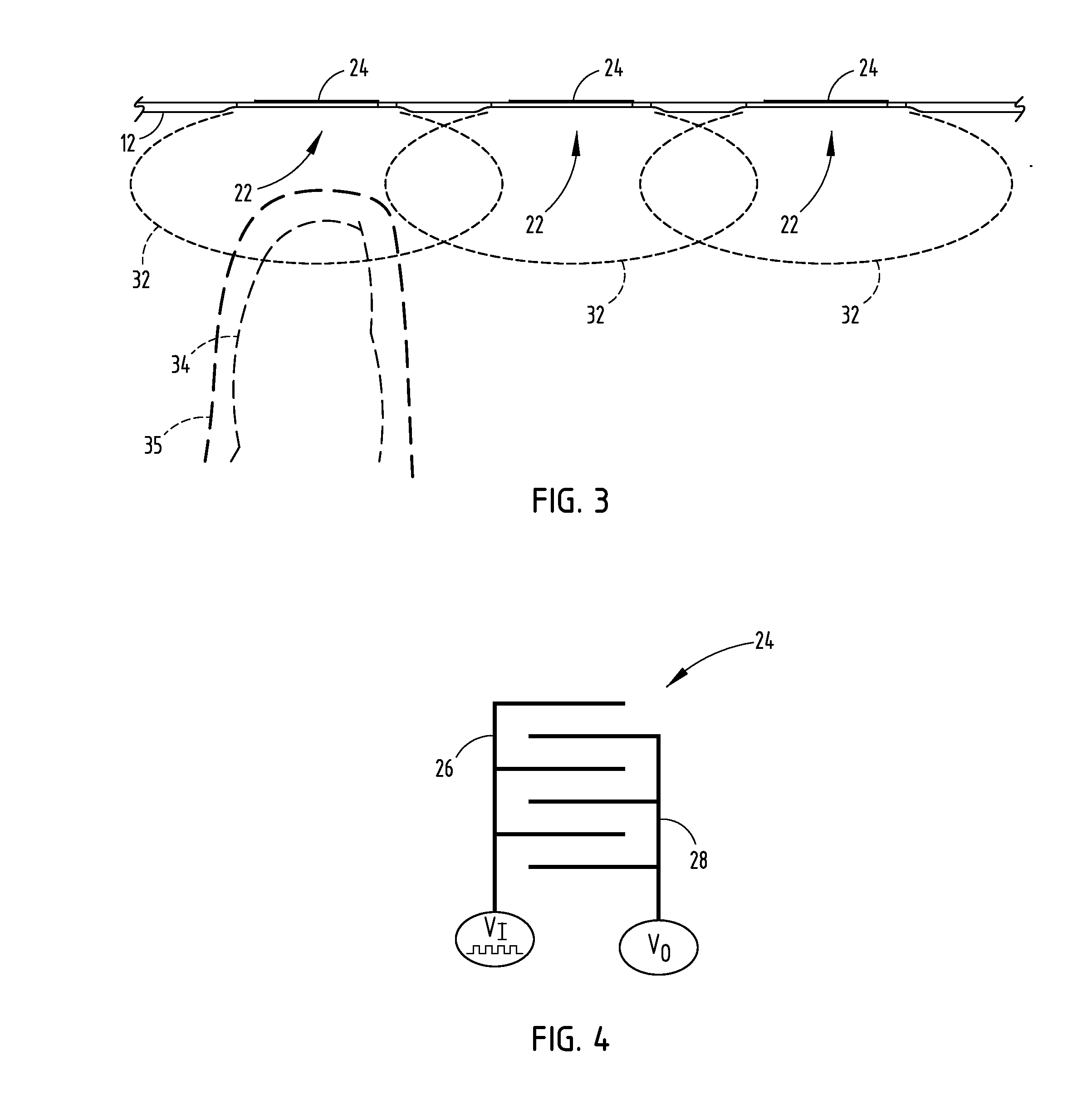

Method of automatically controlling a motorized window treatment while minimizing occupant distractions

ActiveUS8288981B2Minimize distractionDC motor speed/torque controlDoor/window protective devicesPresent dayDistraction

A load control system provides for automatically controlling a position of a motorized window treatment to control the amount of sunlight entering a space of a building through a window located in a façade of the building in order to control a sunlight penetration distance within the space and minimize occupant distractions. The load control system automatically generates a timeclock schedule having a number of timeclock events for controlling the position of the motorized window treatment during the present day. A user is able to select a desired maximum sunlight penetration distance for the space and a minimum time period that may occur between any two consecutive timeclock events. In addition, a maximum number of movements that may occur during the timeclock schedule may also be entered. The load control system uses these inputs to determine event times and corresponding positions of the motorized window treatment for each timeclock event of the timeclock schedule.

Owner:LUTRON TECH CO LLC

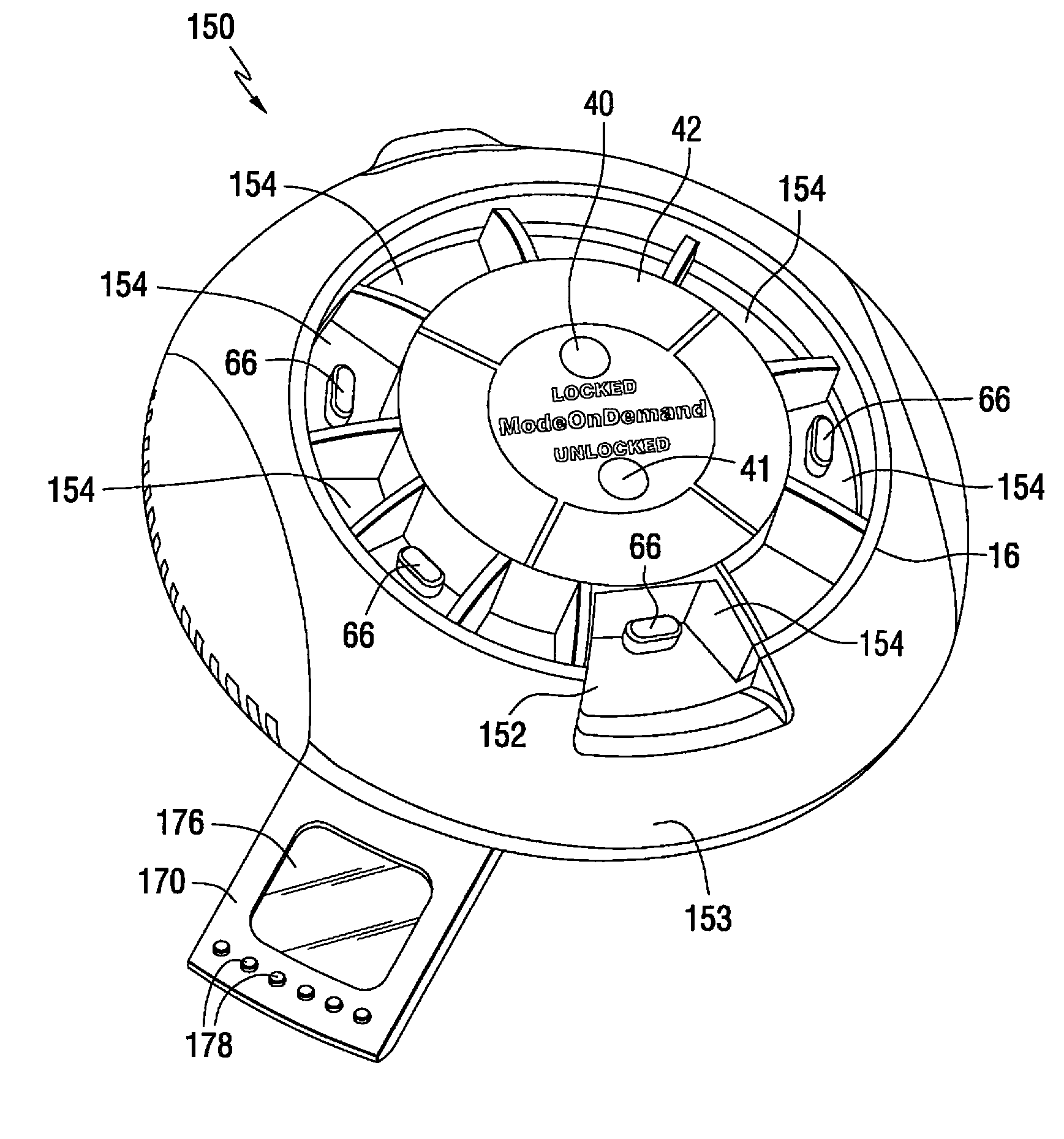

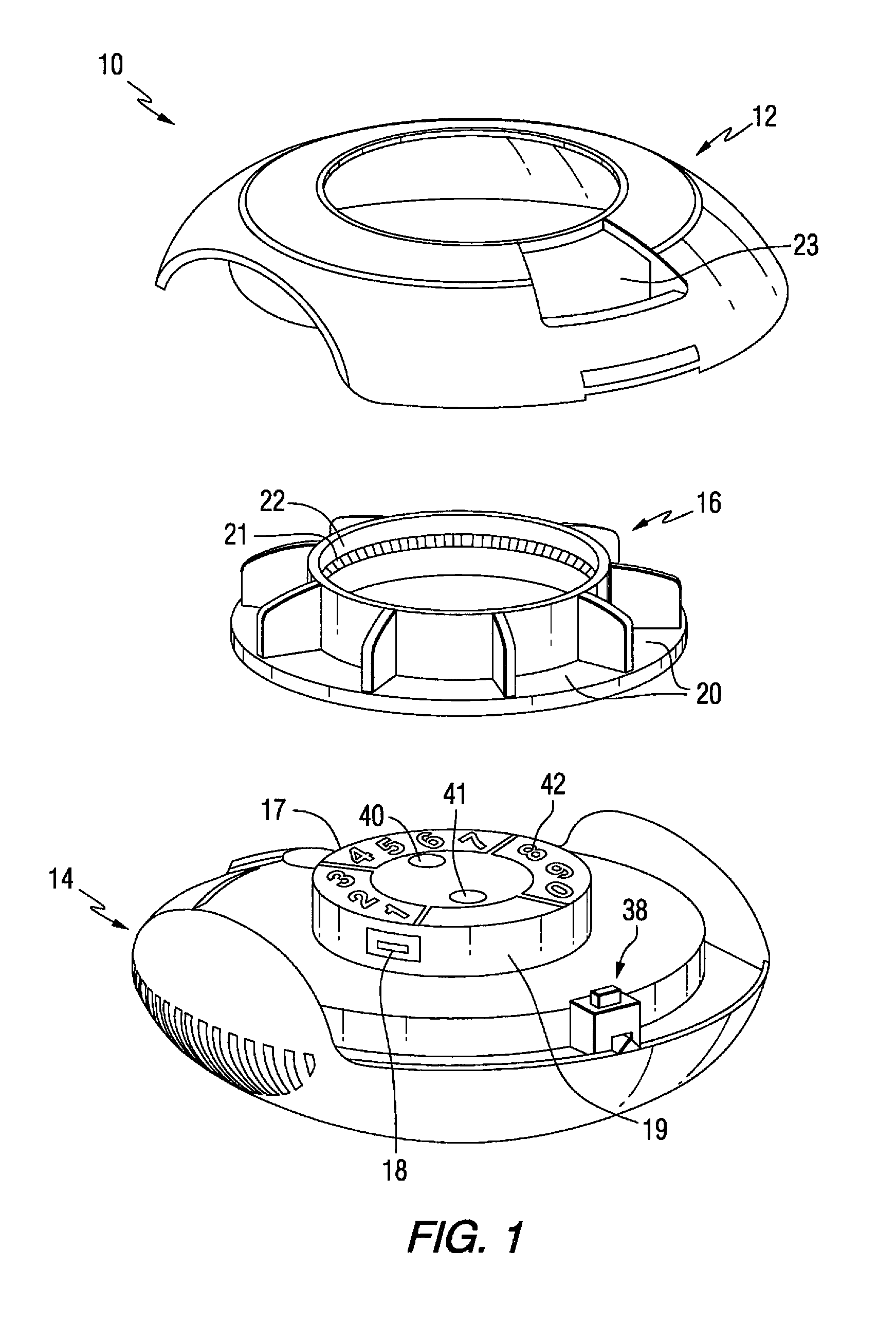

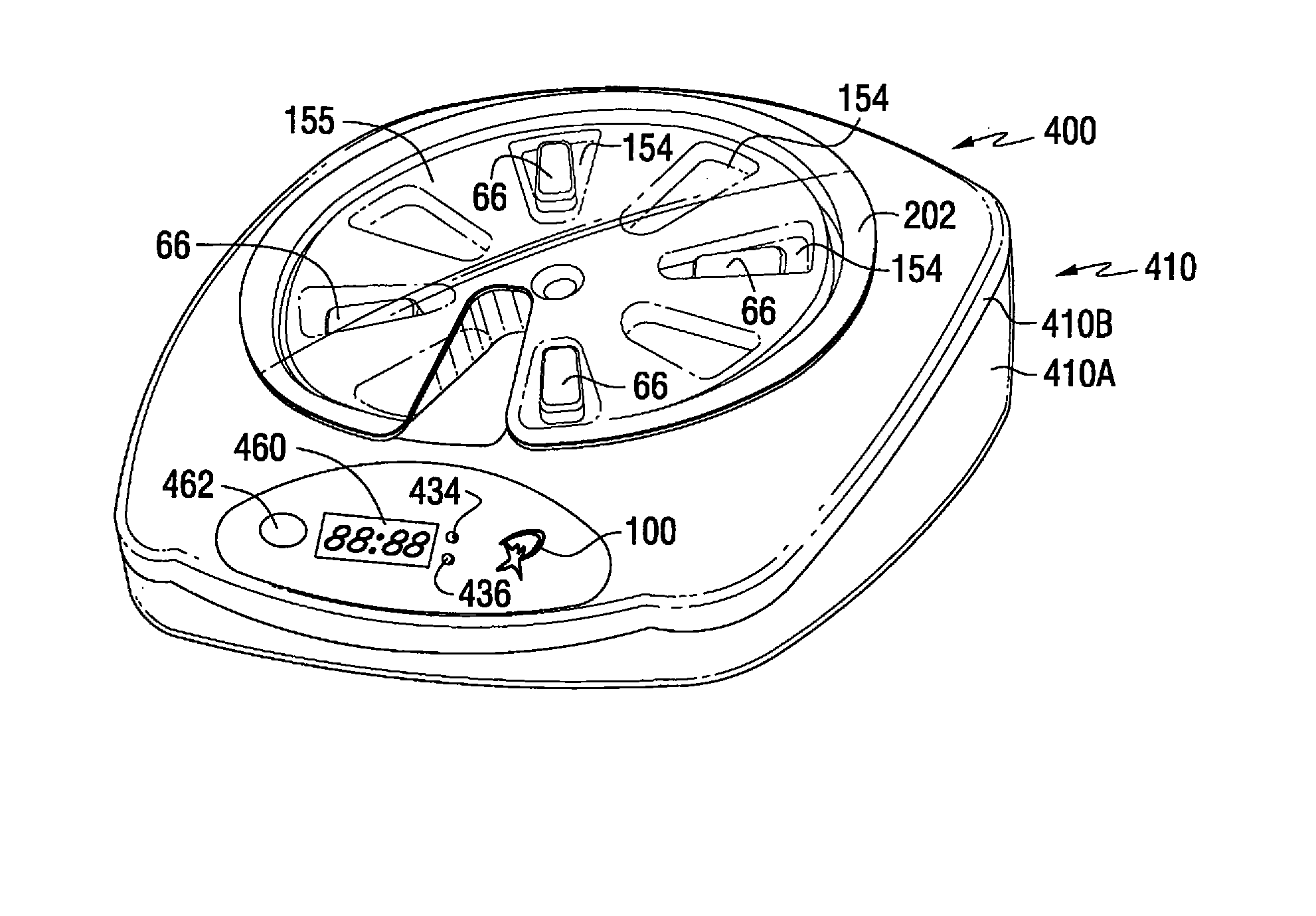

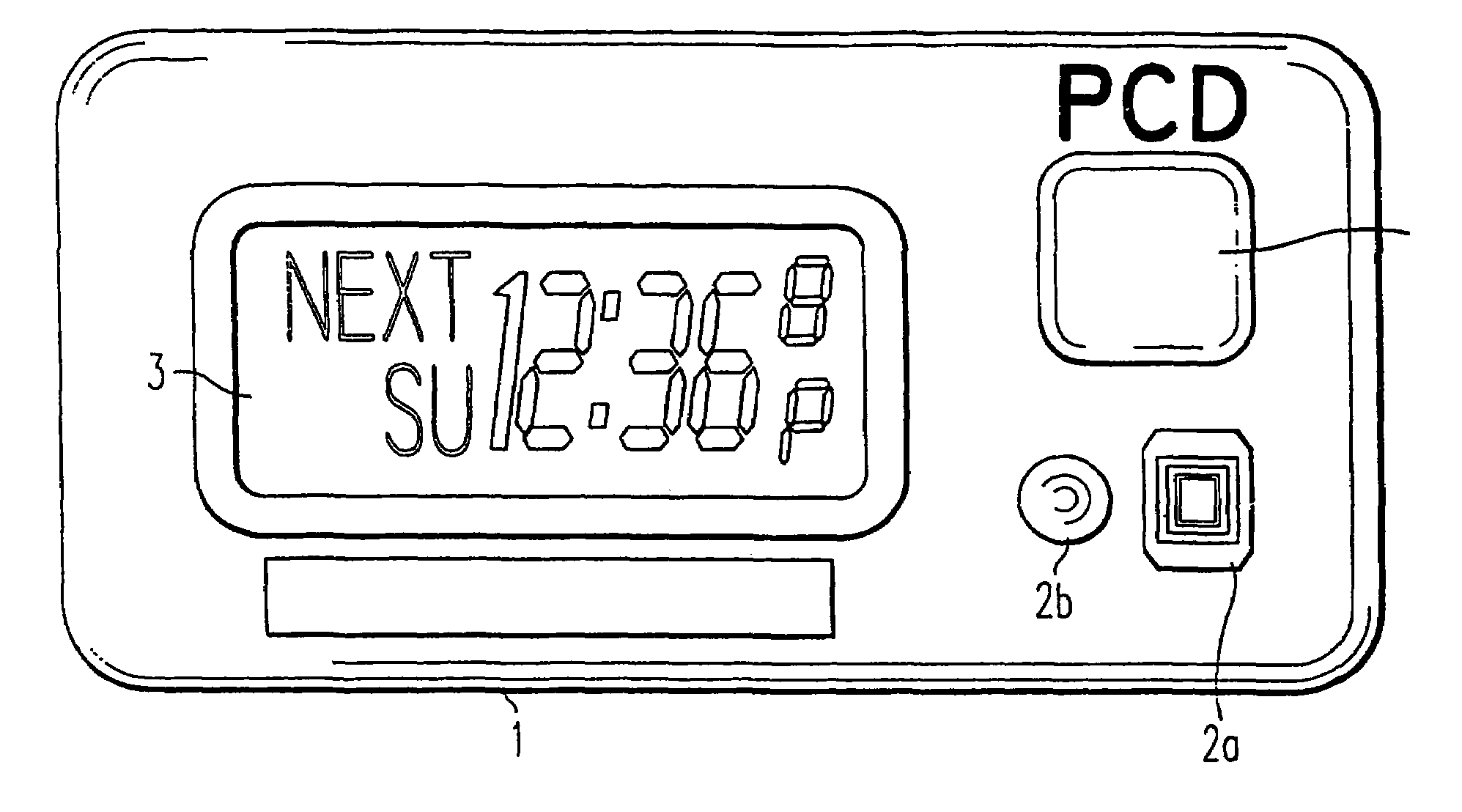

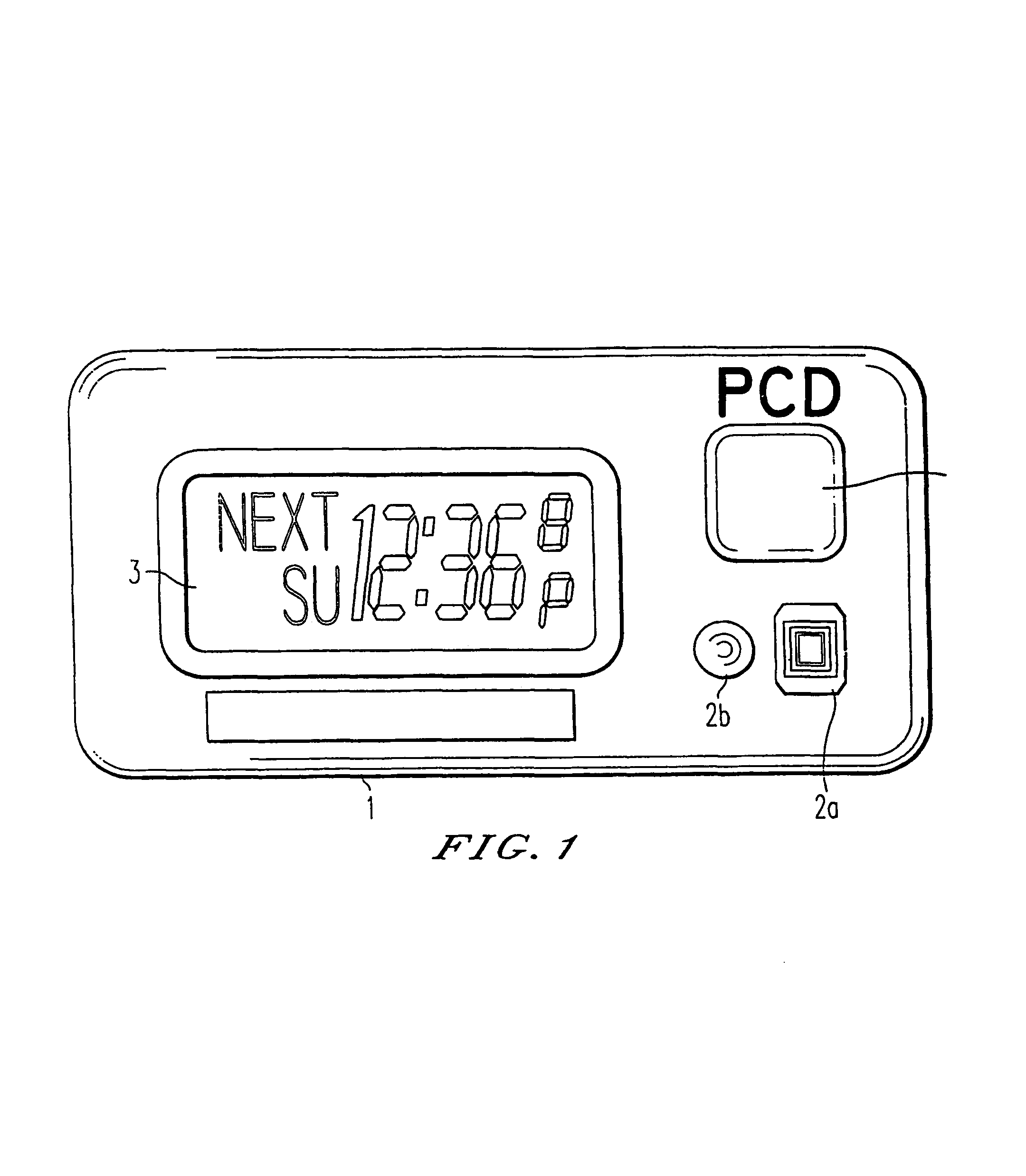

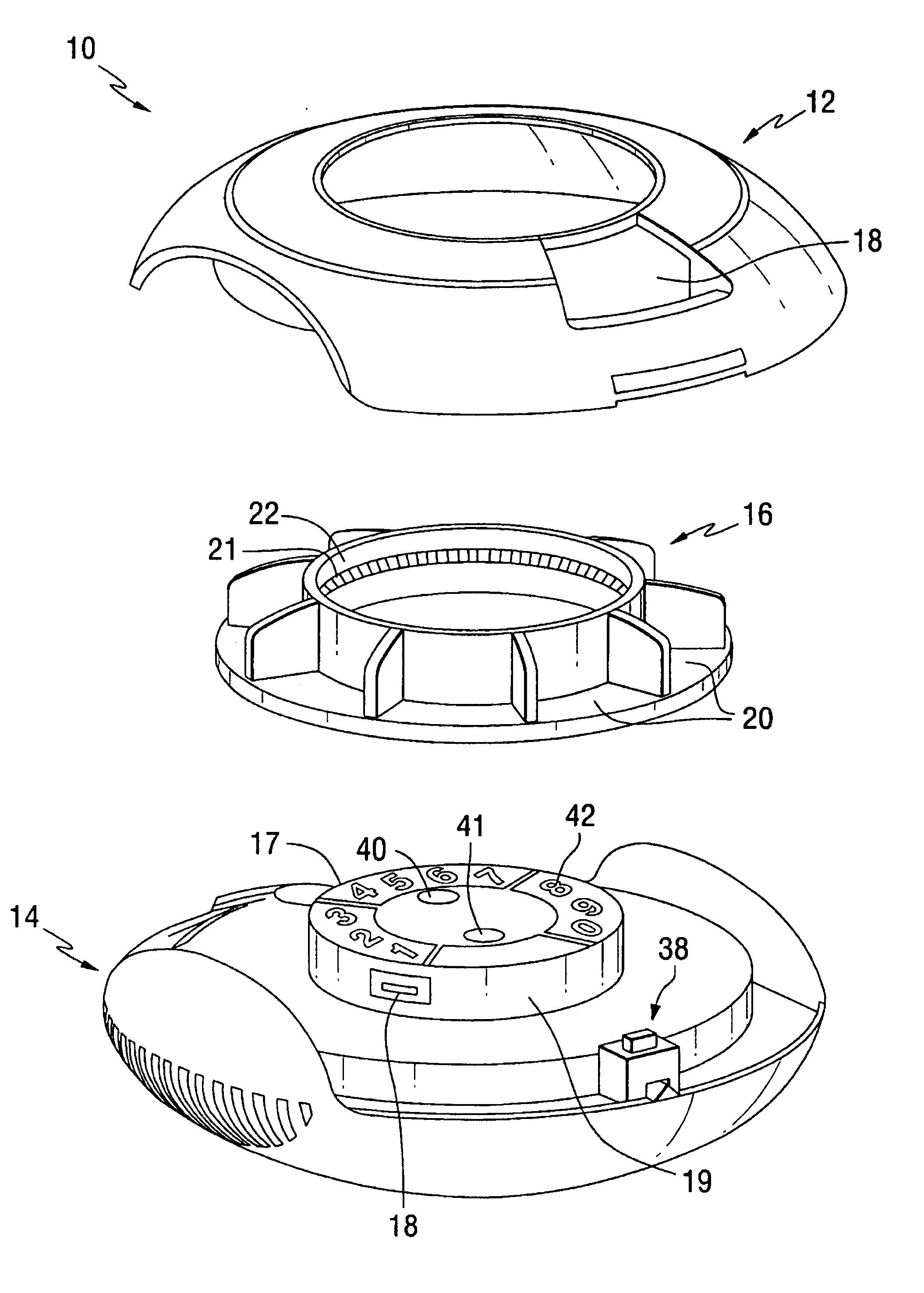

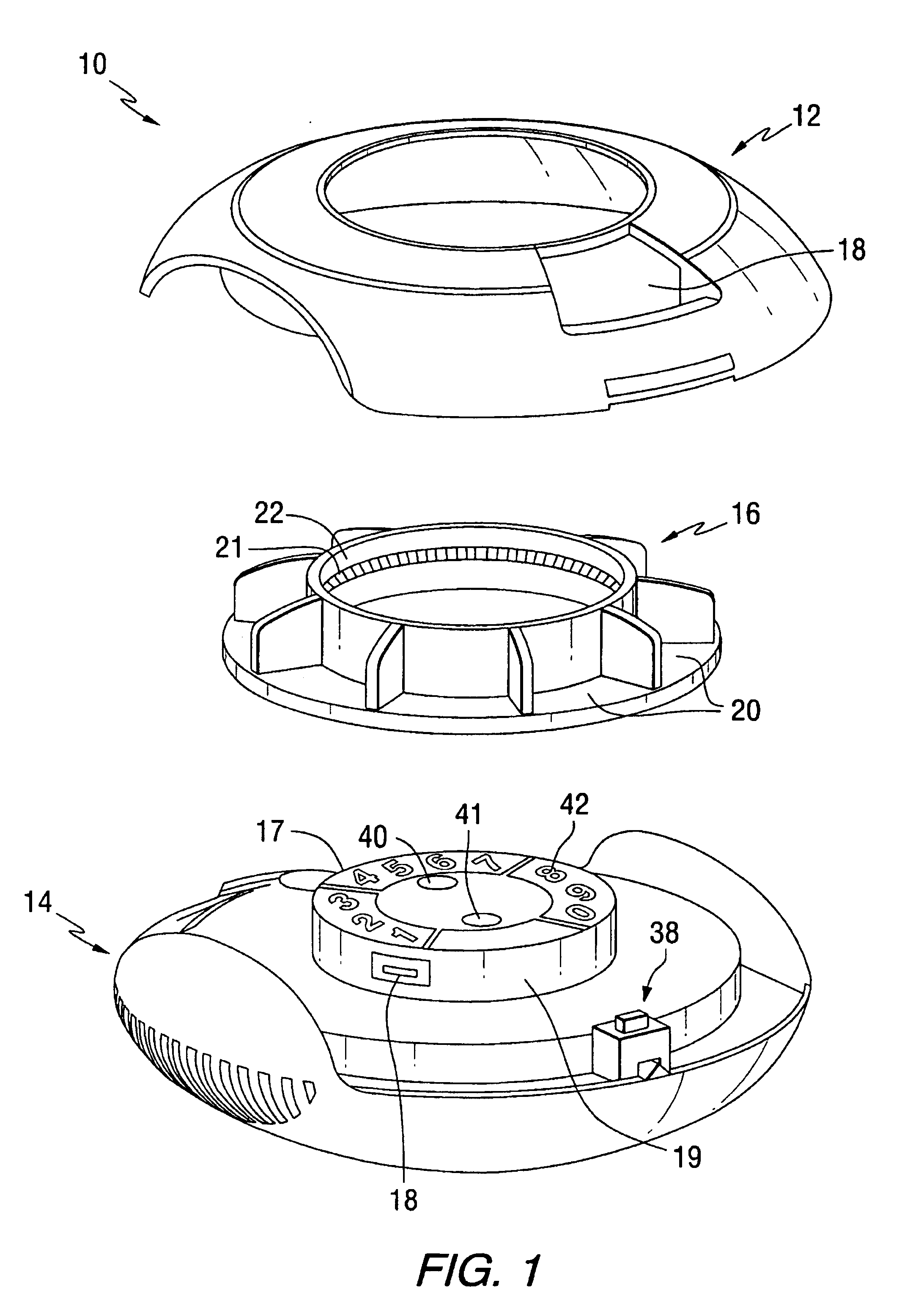

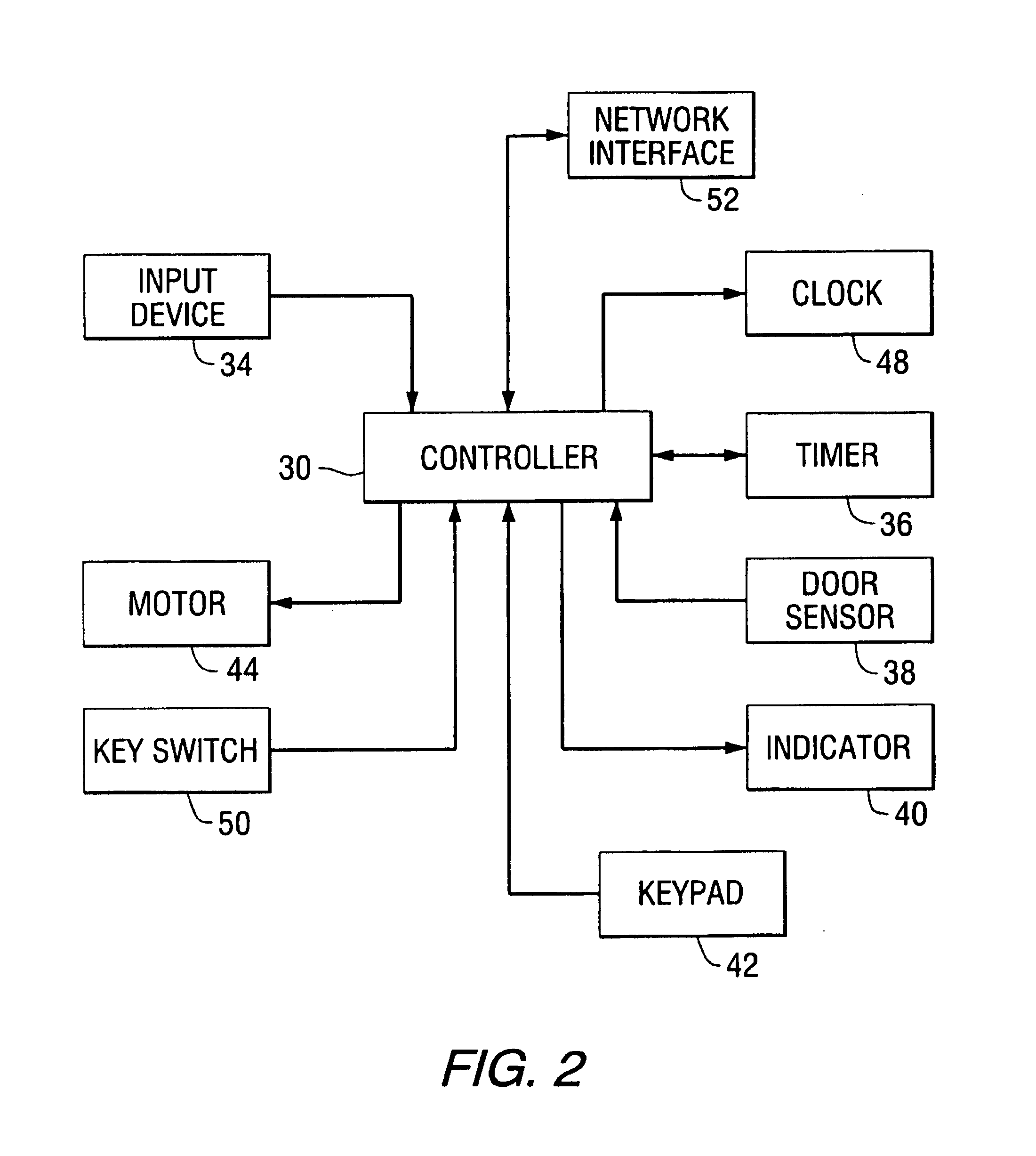

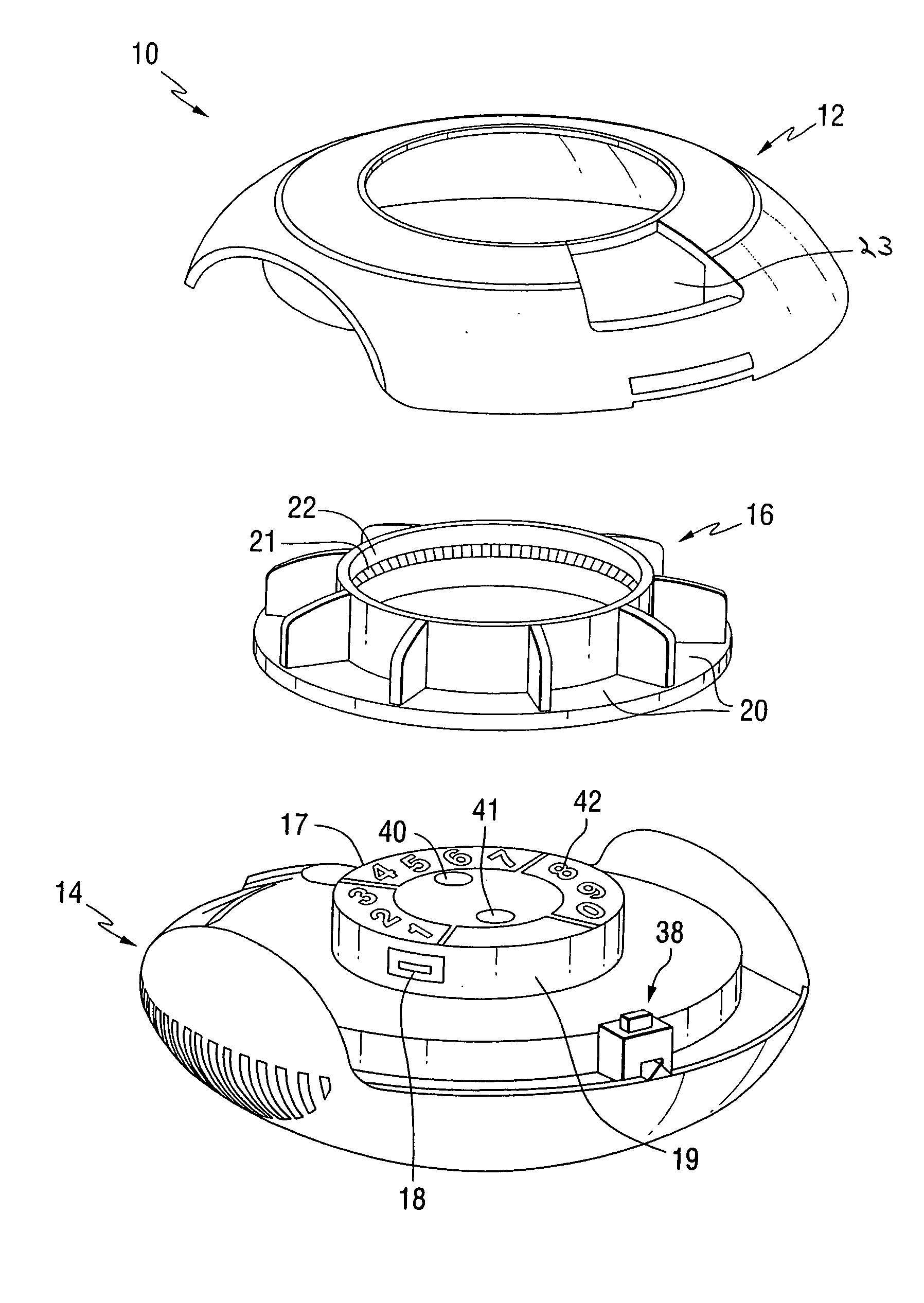

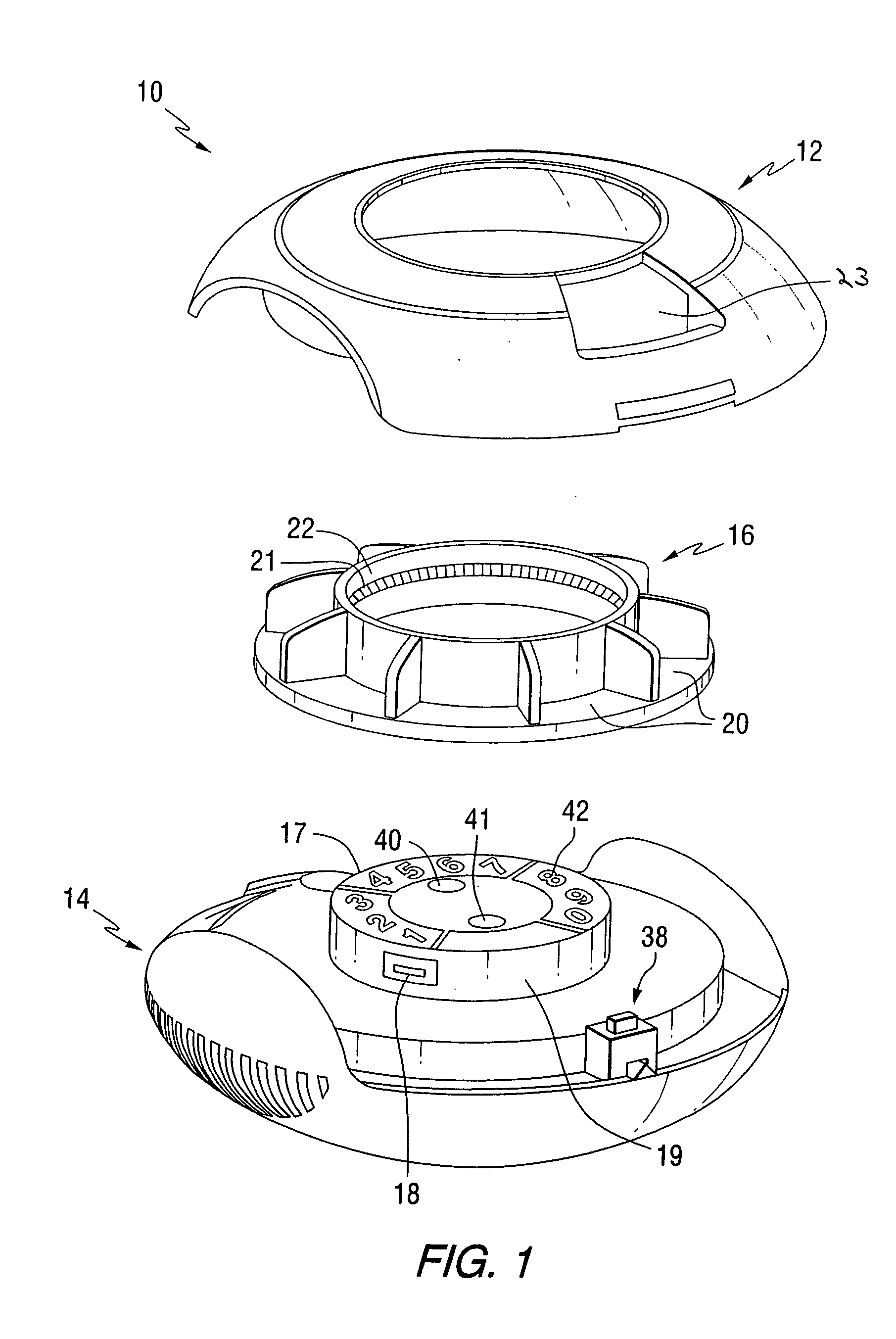

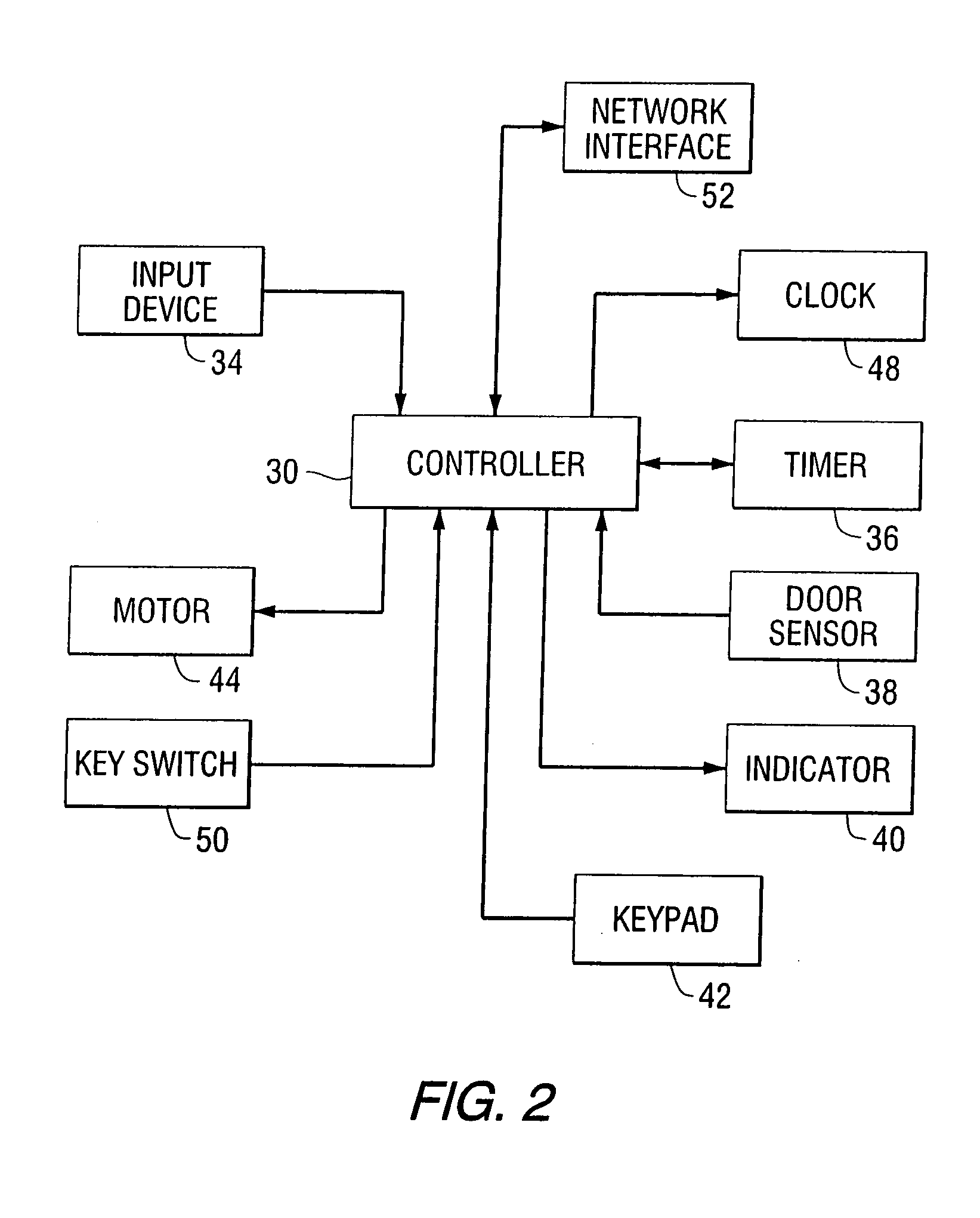

Patient controlled timed medication dispenser

InactiveUS7896192B2Small article dispensingContainer/bottle contructionMedication DispenserMedication dose

A medication on demand dispenser. The dispenser provides patient access to medications prescribed to be available on an as-needed basis but with a prescribed minimum time interval between doses. The dispenser permits access to a single medication dose after each minimum time interval has elapsed. After a drug dose is presented to the patient, the dispenser prevents access to the next dose until the minimum time interval has elapsed.

Owner:AVANCEN MOD

Patient controlled timed medication dispenser

InactiveUS20080203107A1Small article dispensingContainer/bottle contructionMedication DispenserMedication dose

A medication on demand dispenser. The dispenser provides patient access to medications prescribed to be available on an as-needed basis but with a prescribed minimum time interval between doses. The dispenser permits access to a single medication dose after each minimum time interval has elapsed. After a drug dose is presented to the patient, the dispenser prevents access to the next dose until the minimum time interval has elapsed.

Owner:AVANCEN MOD

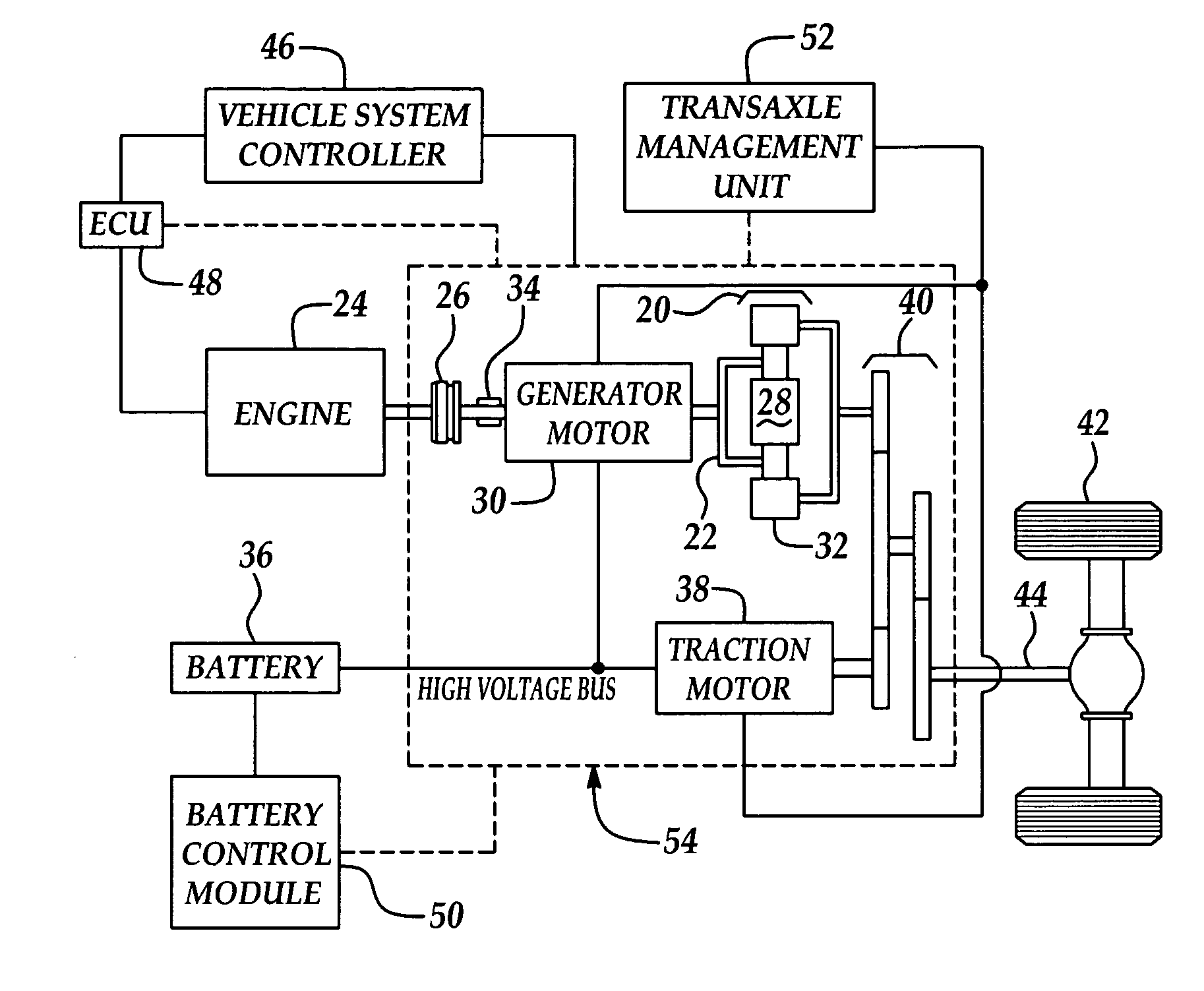

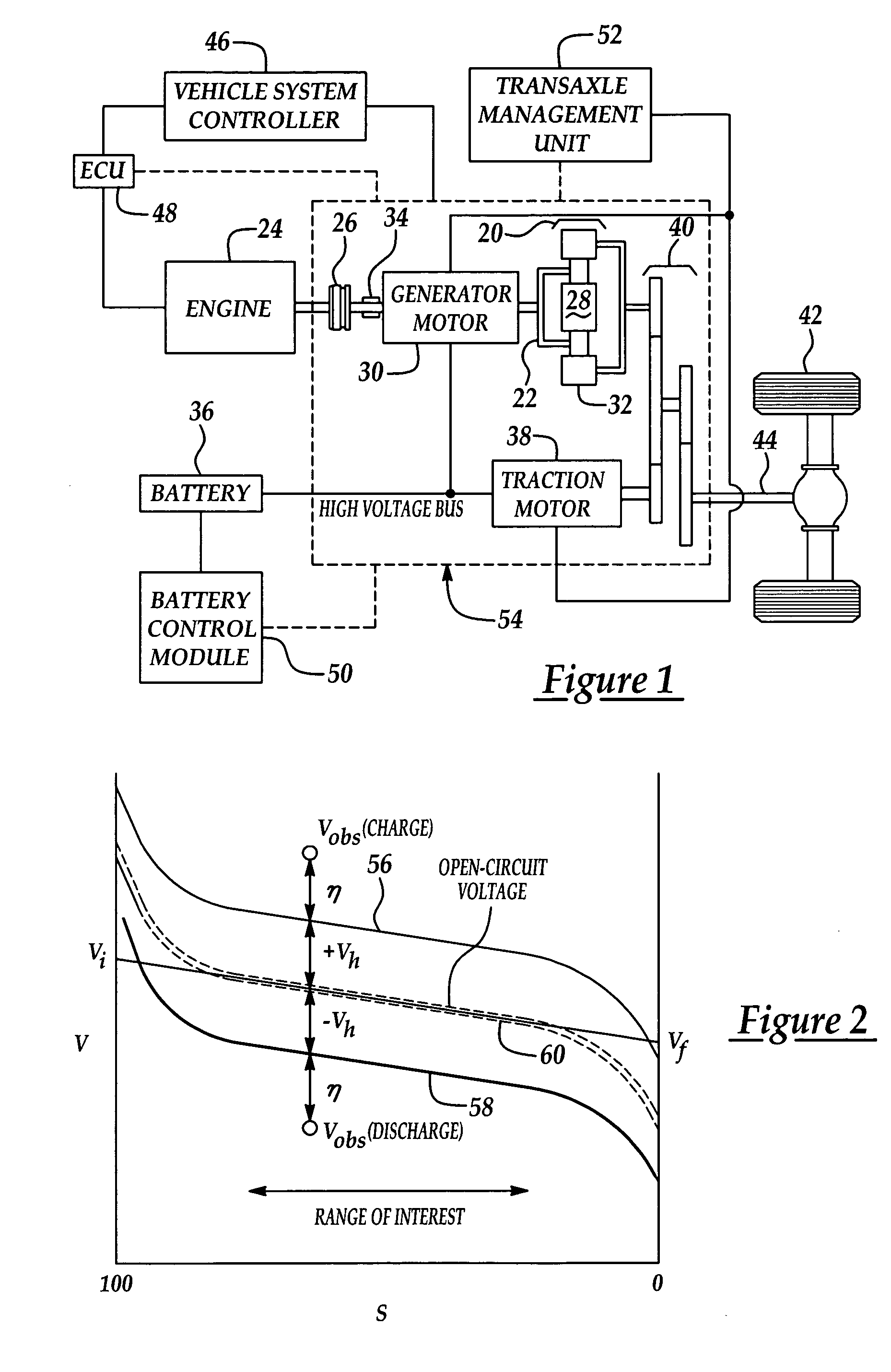

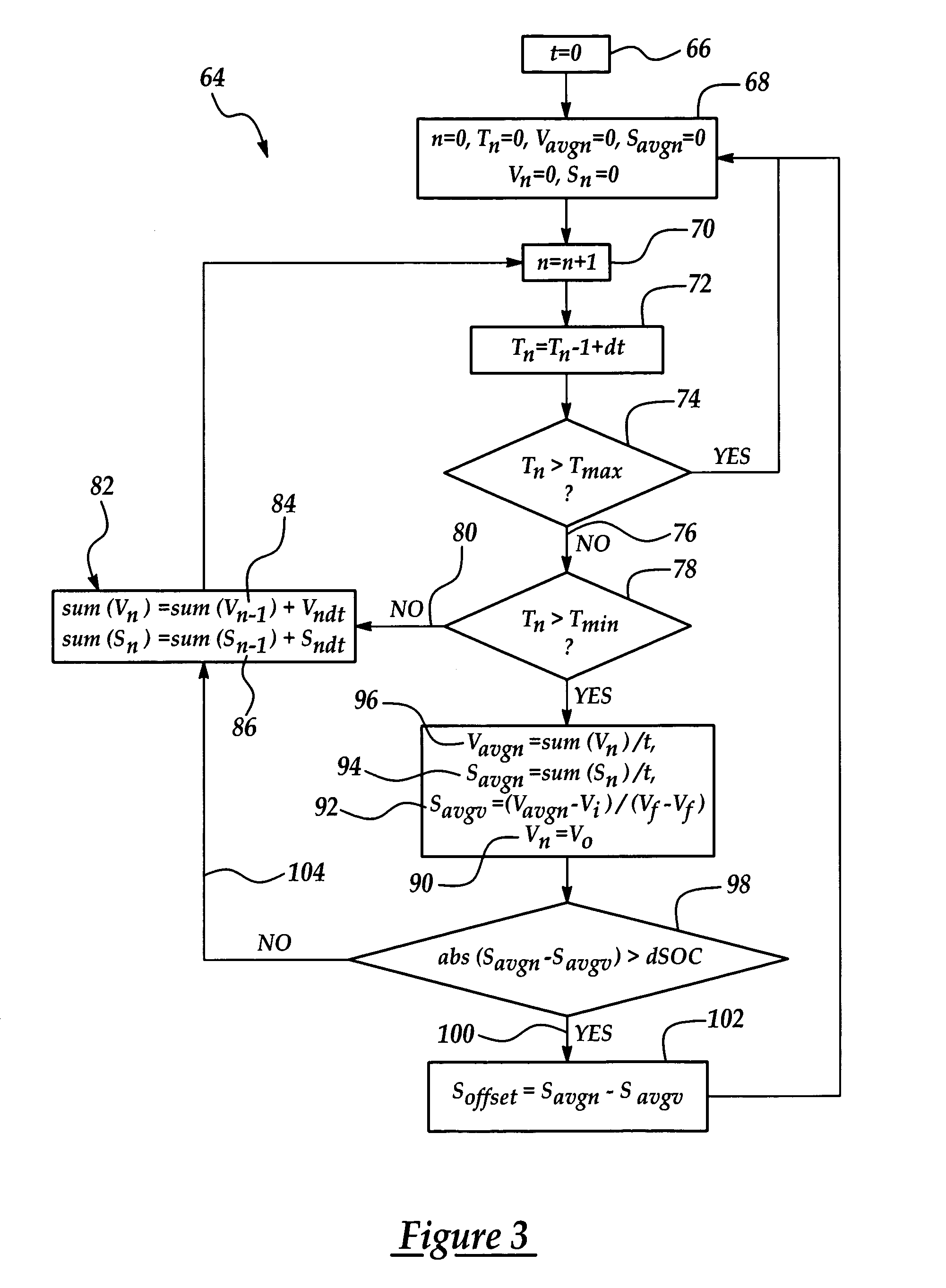

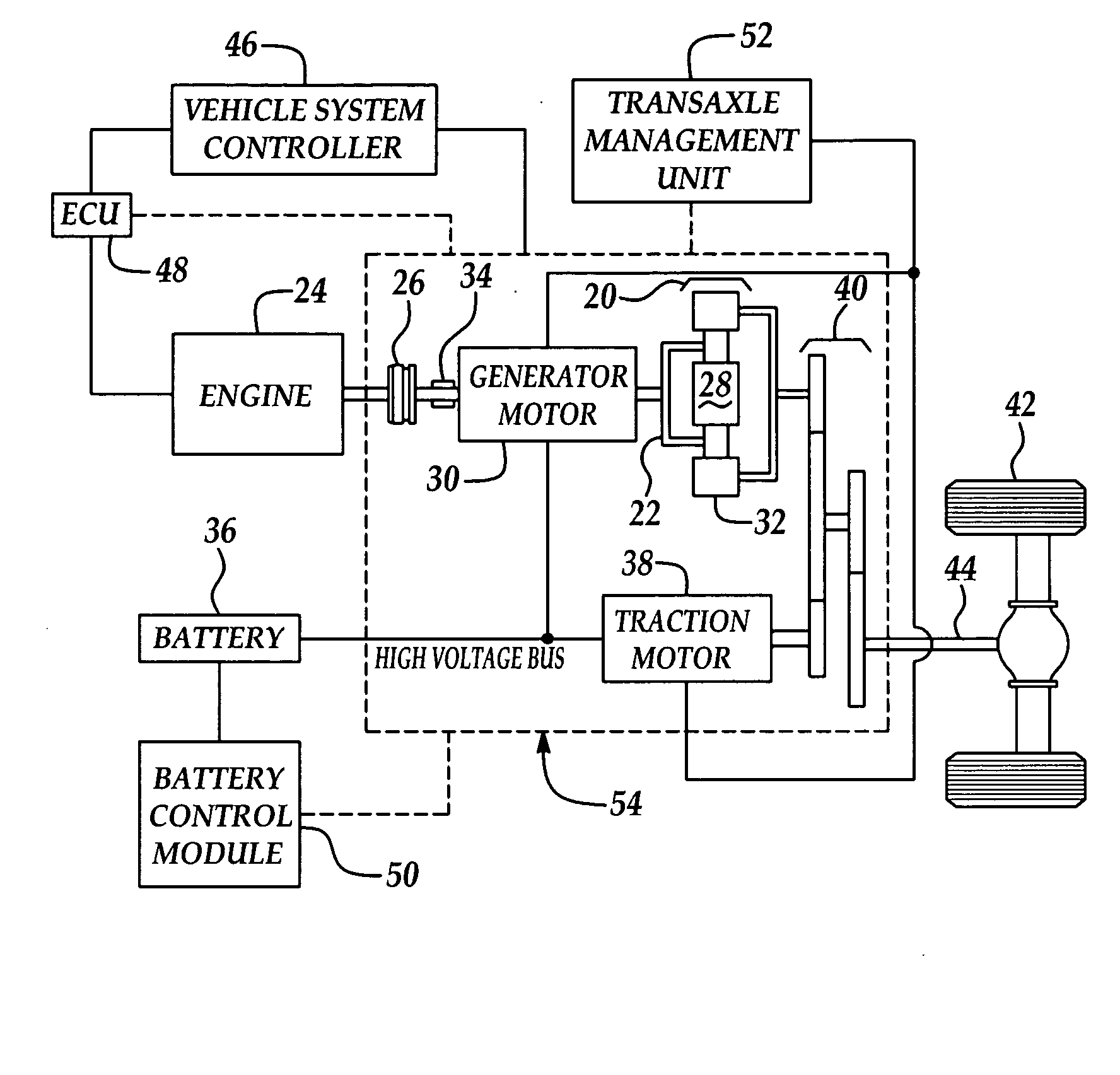

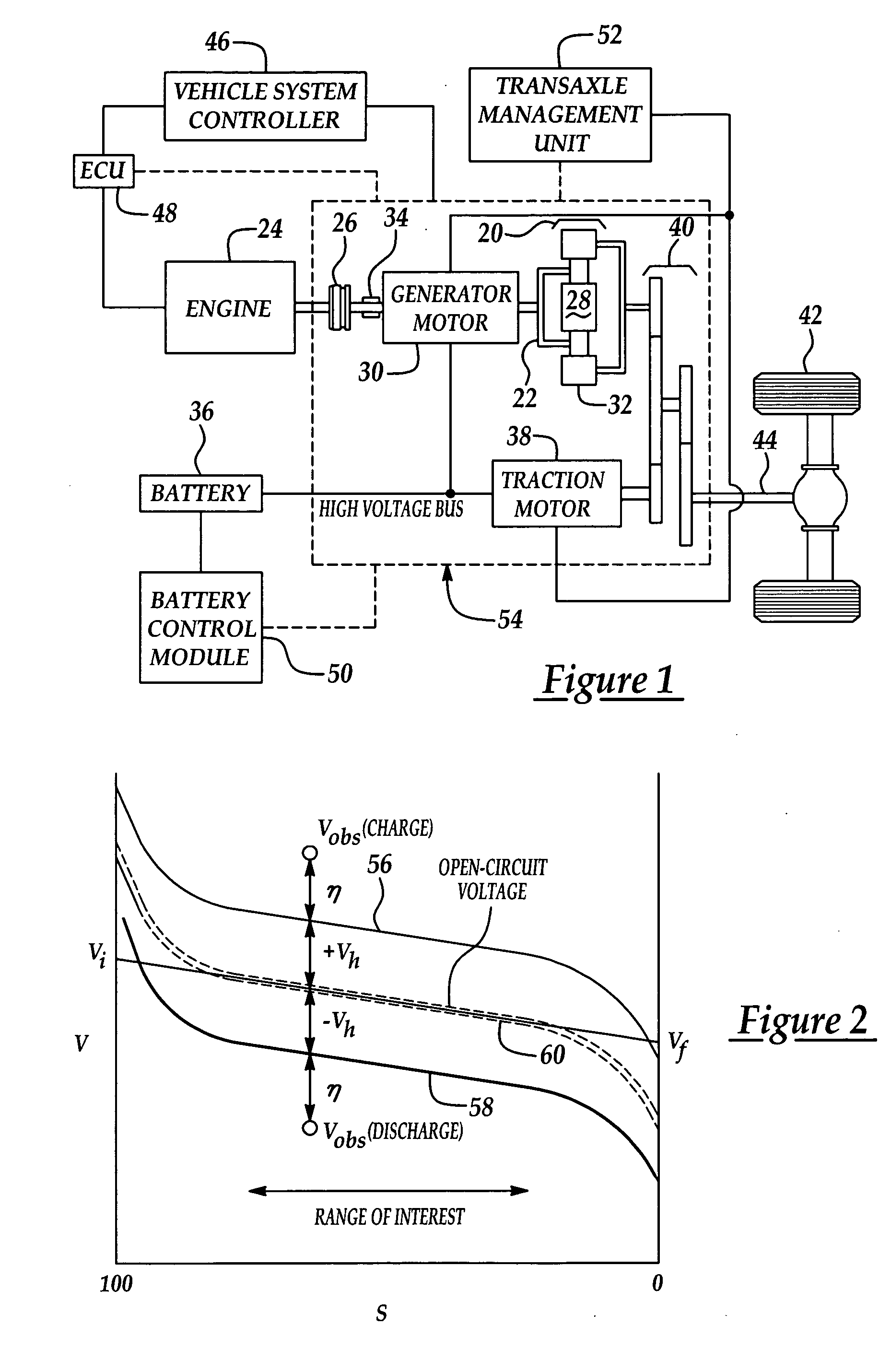

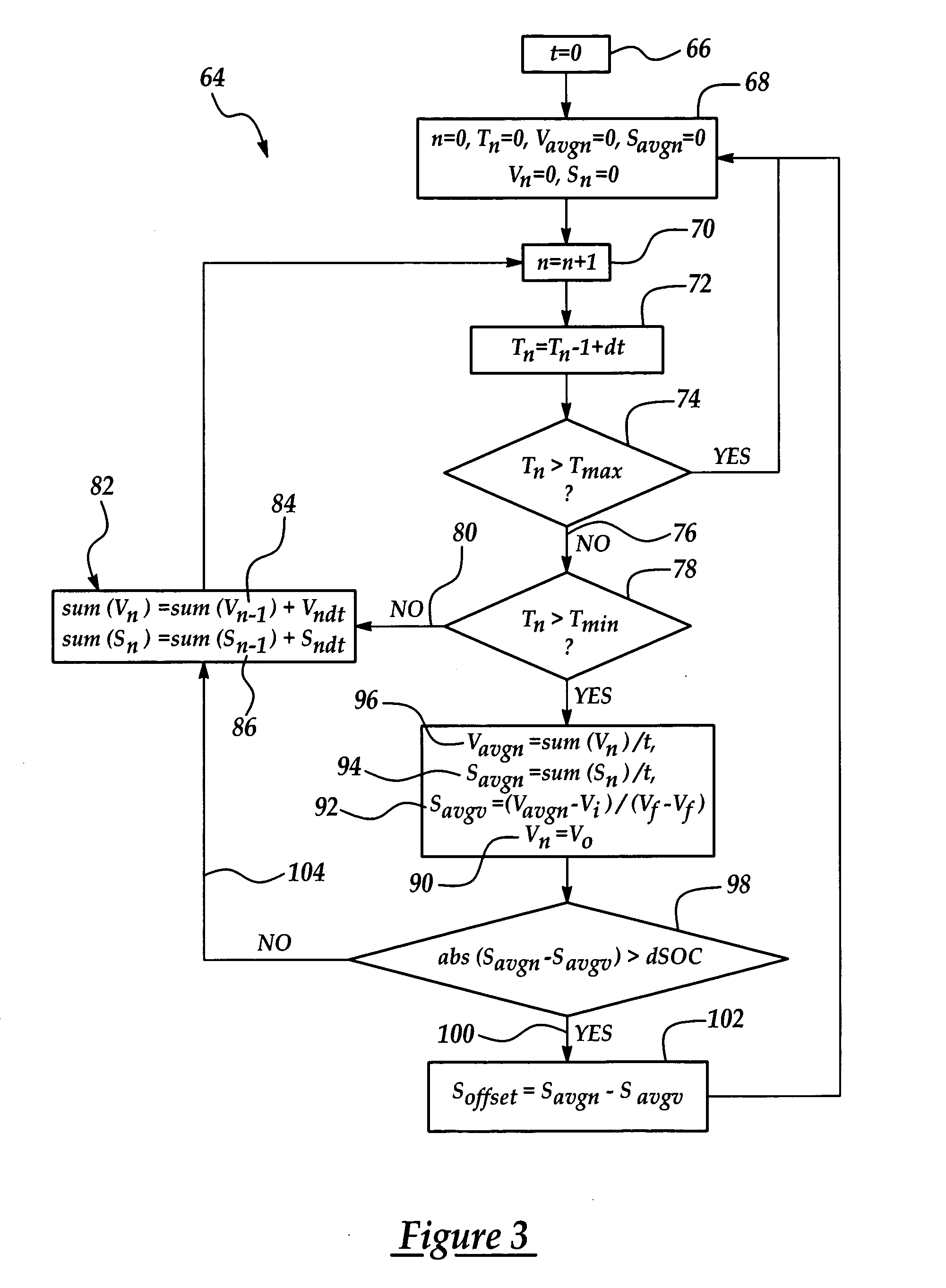

Calculation of state of charge offset using a closed integral method

InactiveUS7233128B2Eliminate hysteresisCircuit monitoring/indicationEmergency protective circuit arrangementsHysteresisBattery state of charge

Owner:FORD GLOBAL TECH LLC

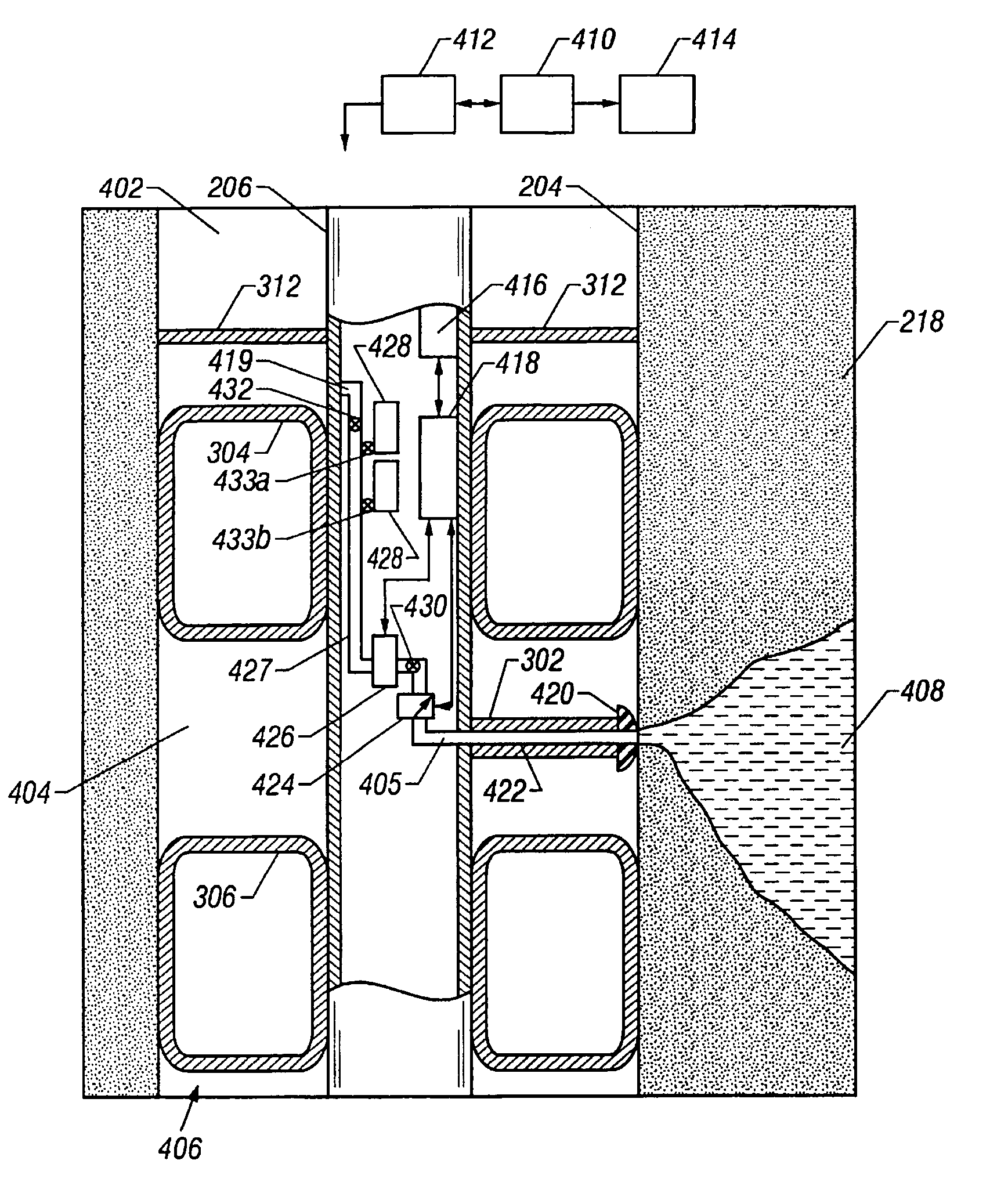

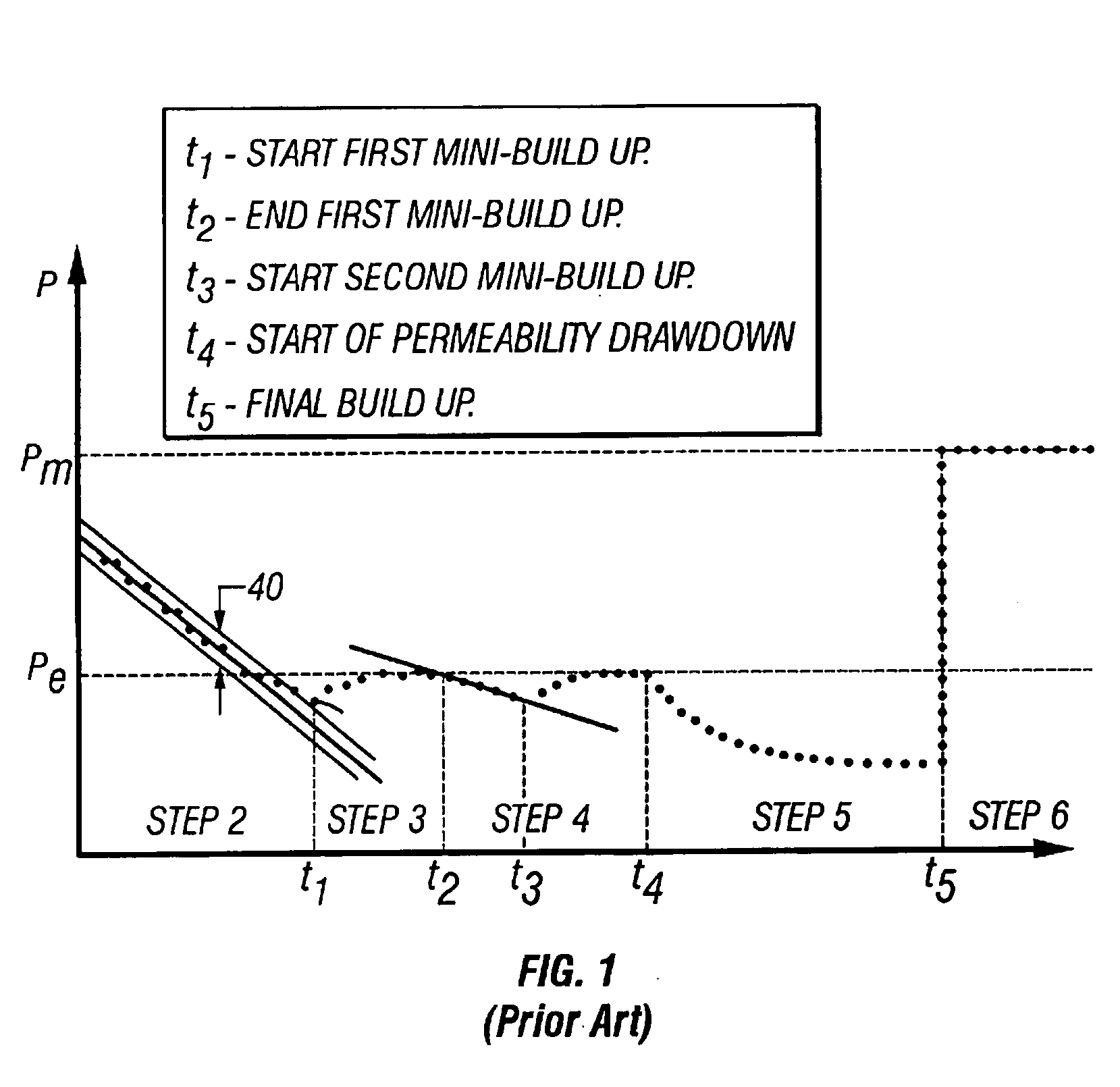

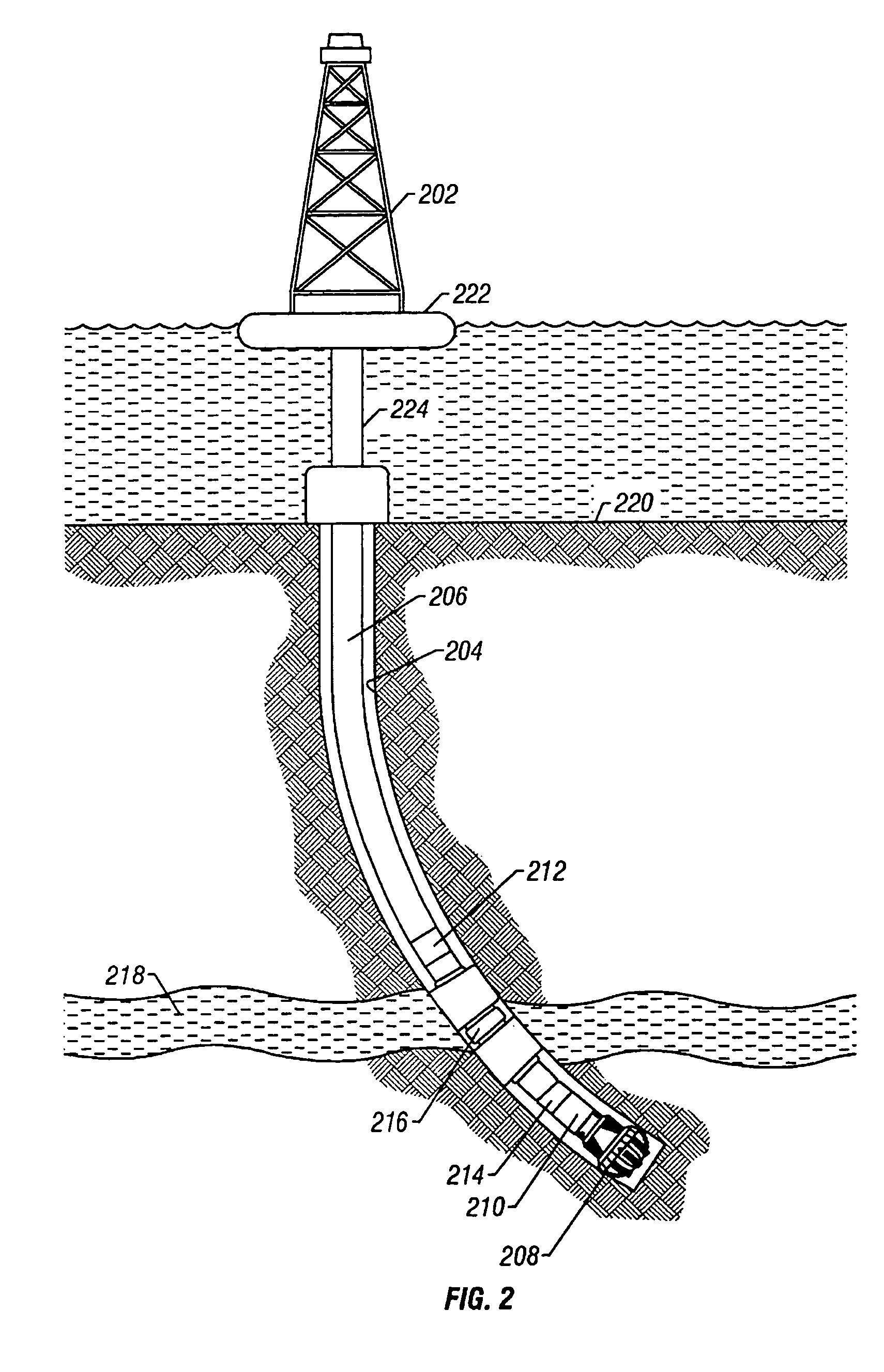

Method and apparatus for pumping quality control through formation rate analysis techniques

InactiveUS20040231842A1Enhance well operation efficiencyImprove securitySurveyFluid removalMinimum timeQuality control

The present invention provides a method and apparatus for determination of the quality of a formation fluid sample including monitoring permeability and mobililty versus time to determine a filtrate contamination level, single phase state without gas and solids in the formation fluid, as it existed in the formation and the determination of laminar flow from the formation. The present invention also enables determination of an optimal pumping rate to match the ability of a subsurface formation to produce a single phase formation fluid sample in minimum time. The method and apparatus also detect pumping problems such as sanding and loss of seal with borehole.

Owner:BAKER HUGHES INC

Method of Automatically Controlling a Motorized Window Treatment While Minimizing Occupant Distractions

ActiveUS20100071856A1Minimize distractionLimited penetration distanceDC motor speed/torque controlCurtain accessoriesPresent dayDistraction

A load control system provides for automatically controlling a position of a motorized window treatment to control the amount of sunlight entering a space of a building through a window located in a façade of the building in order to control a sunlight penetration distance within the space and minimize occupant distractions. The load control system automatically generates a timeclock schedule having a number of timeclock events for controlling the position of the motorized window treatment during the present day. A user is able to select a desired maximum sunlight penetration distance for the space and a minimum time period that may occur between any two consecutive timeclock events. In addition, a maximum number of movements that may occur during the timeclock schedule may also be entered. The load control system uses these inputs to determine event times and corresponding positions of the motorized window treatment for each timeclock event of the timeclock schedule.

Owner:LUTRON TECH CO LLC

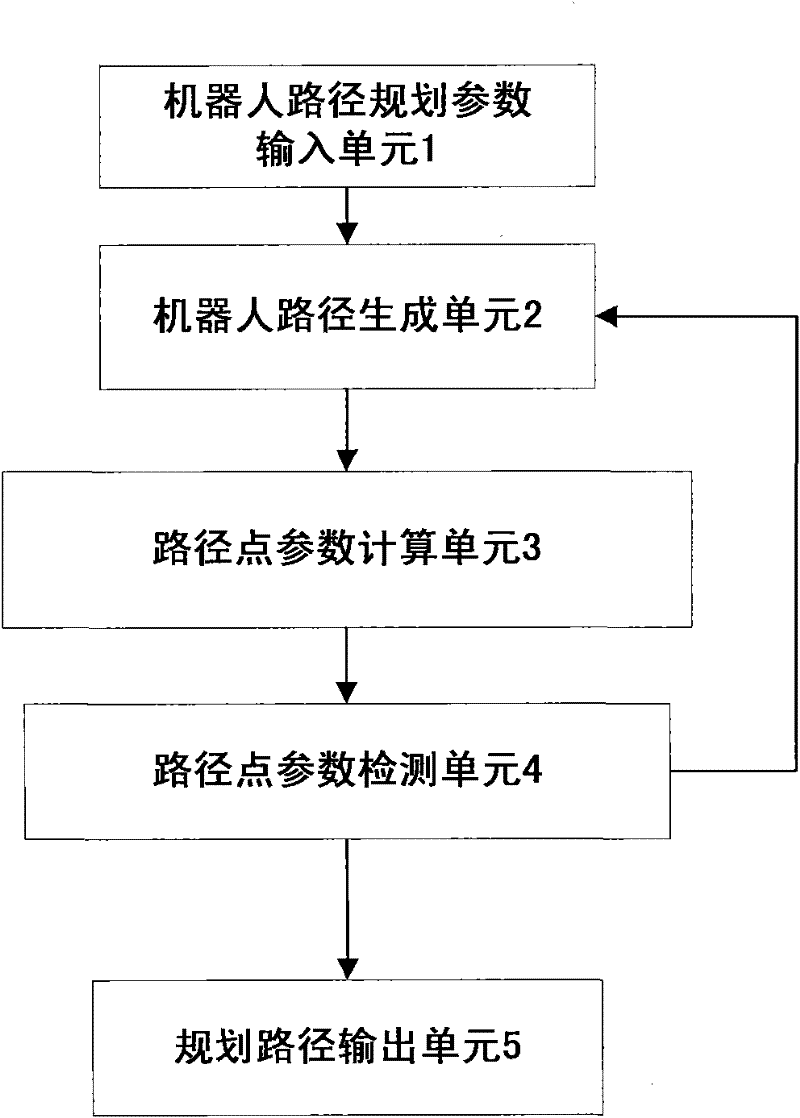

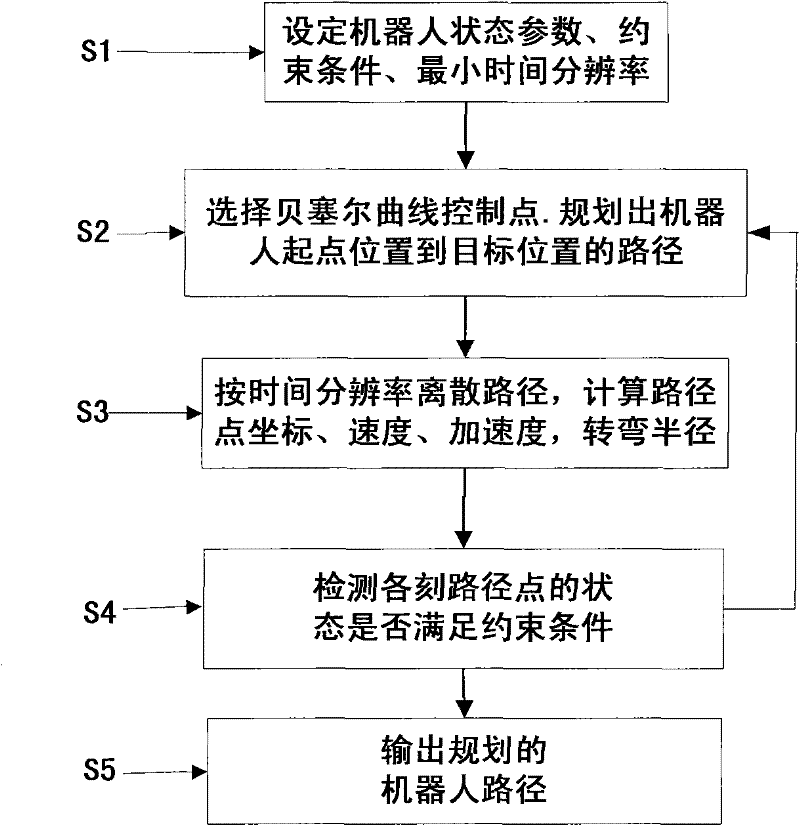

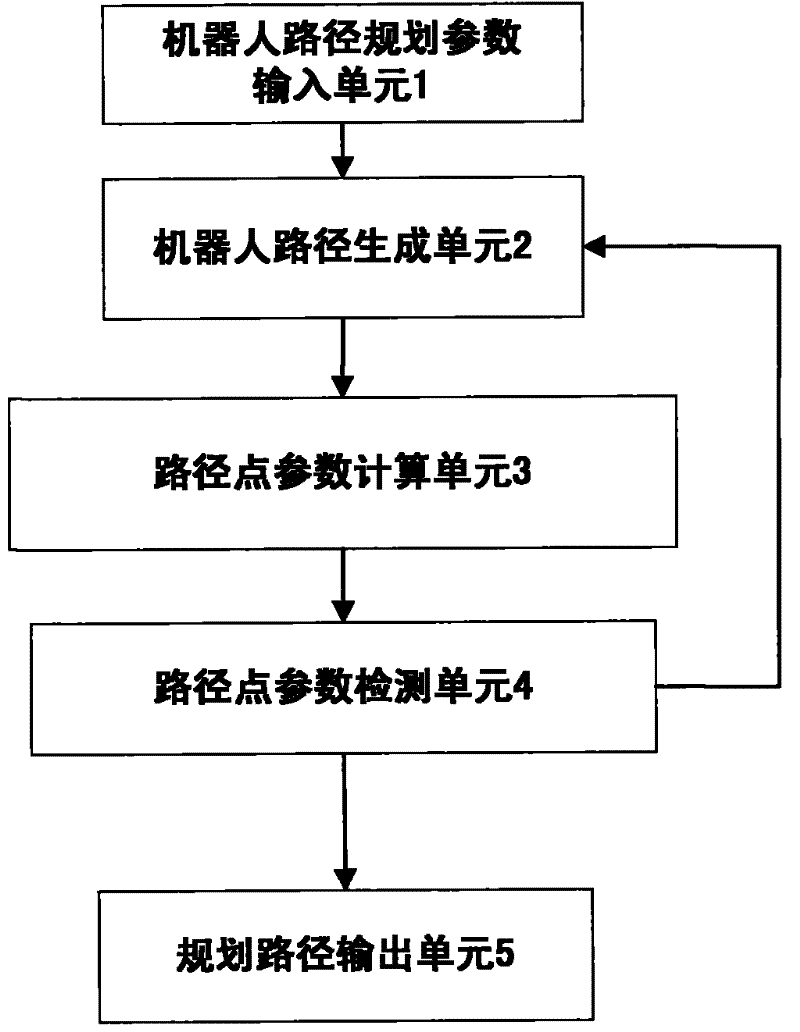

Robot path planning method and apparatus thereof based on Bezier curve

ActiveCN102207736ARealize path planningSolving Path Planning ProblemsVehicle position/course/altitude controlPosition/direction controlImage resolutionMinimum time

The invention provides a robot path planning method and an apparatus thereof based on a Bezier curve. The method comprises the following steps that: a robot path planning parameter input unit receives and sets a robot state parameter, a constraint condition, a path discretization minimum time resolution; a robot path generation unit generates a group of Bezier curve control points consisting of four 4-dimension vectors according to the robot state parameter and plans out a continuous path between an origin position to a target position of the robot; the robot path generation unit forms a timepoint sequence according to the path discretization minimum time resolution and calculates a discretization path according to the continuous path; a path point parameter detection unit detects whether a speed, an acceleration and a turn radius of each path point which is corresponding to the time points satisfy the constraint condition; if the speed, the acceleration and the turn radius of each path point do not satisfy the constraint condition, the control points are regenerated; otherwise, a planning path output unit receives and outputs a robot path which is planed by the path point parameter detection unit and satisfies the constraint condition.

Owner:INST OF AUTOMATION CHINESE ACAD OF SCI

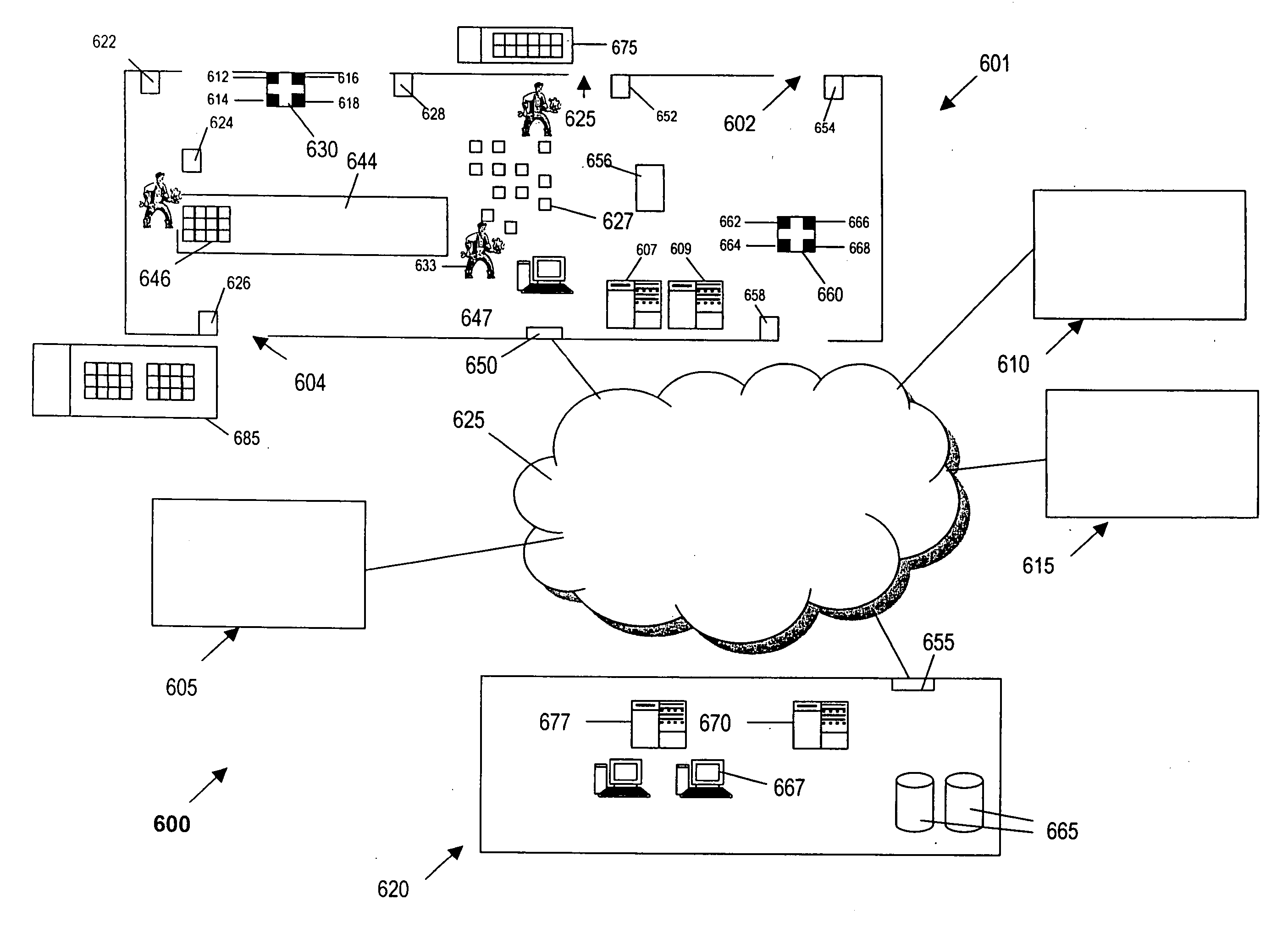

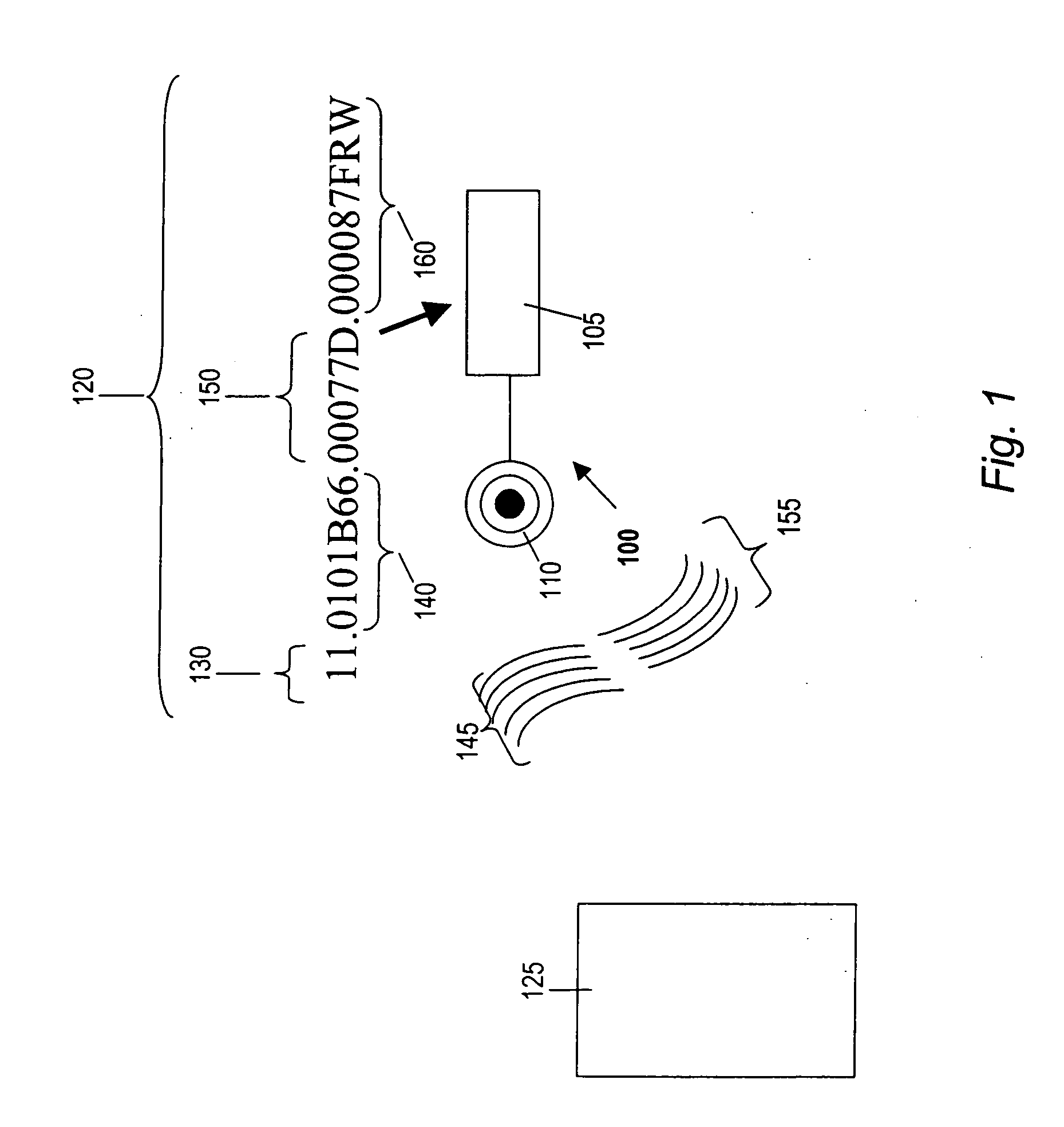

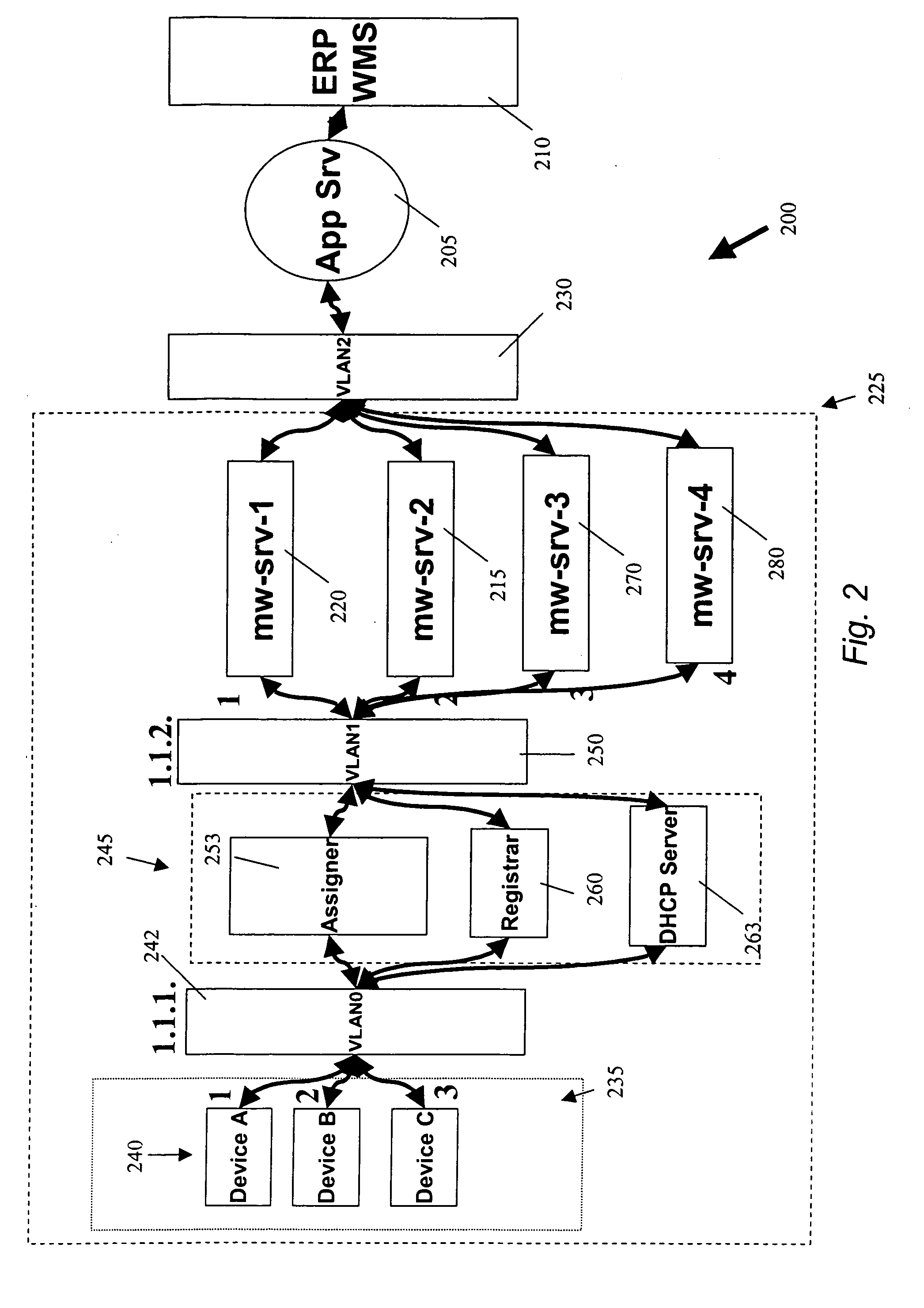

Using syslog and SNMP for scalable monitoring of networked devices

InactiveUS20060091999A1Electric signal transmission systemsDigital data processing detailsMinimum timeThrottle

Methods and devices are provided for determining the status of a networked device. Messages from such devices may include information indicating the health, accuracy and / or reliability of a device and / or of the network that includes the device. Multiple message formats may be supported, e.g., heartbeat only, partial statistics, full statistics, etc. Transmission of such messages may be triggered by the occurrence of various conditions, such as the passage of a predetermined time interval, a predetermined change in one or more criteria, etc. In some implementations, a time-based message throttle establishes a minimum time interval between messages. Messages may be created in a format that is compatible with SNMP. Messages may be transmitted in more than one packet, if necessary. Messages may be sent to one or more devices, e.g., to one or more servers, according to various criteria.

Owner:CISCO TECH INC

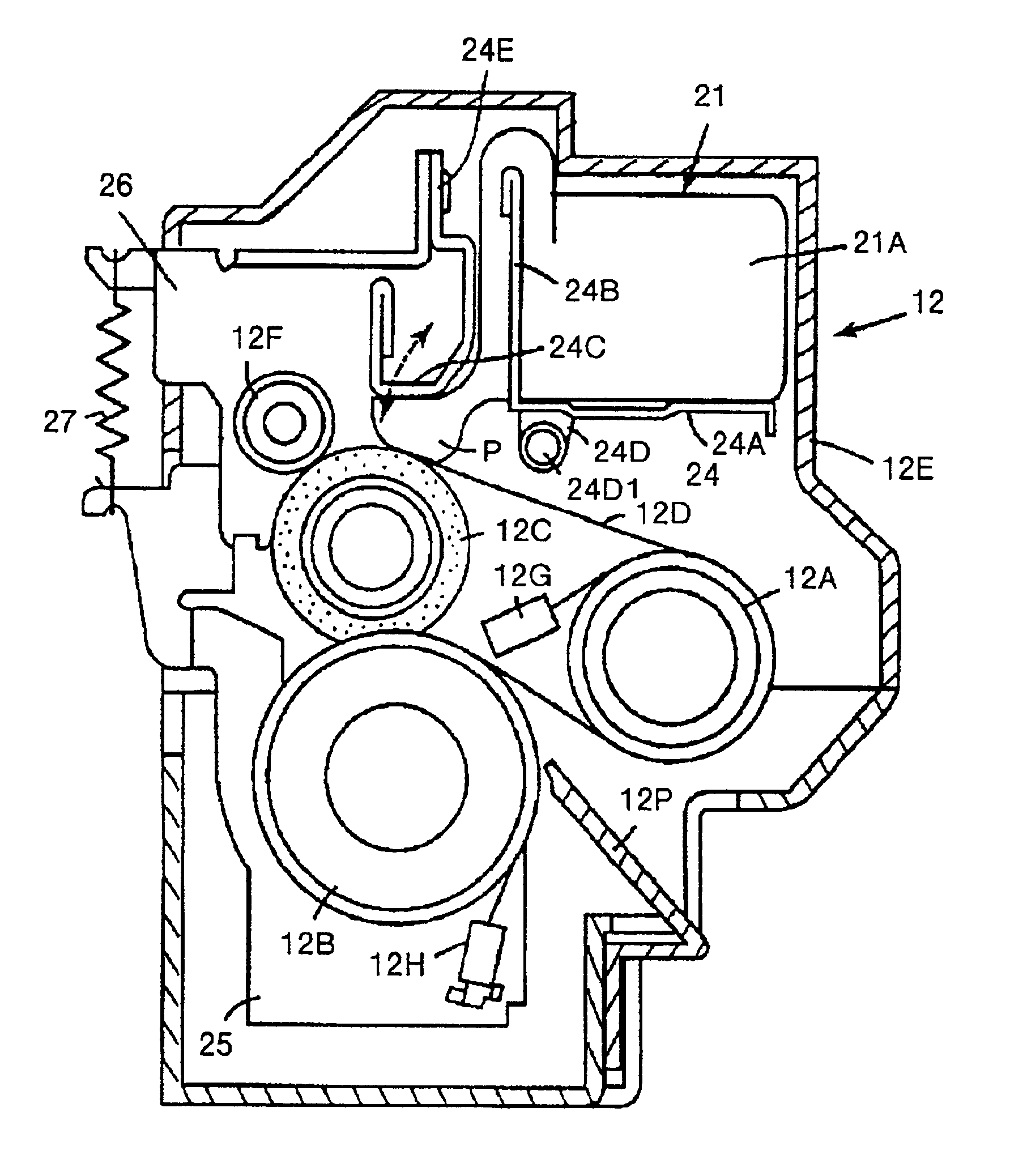

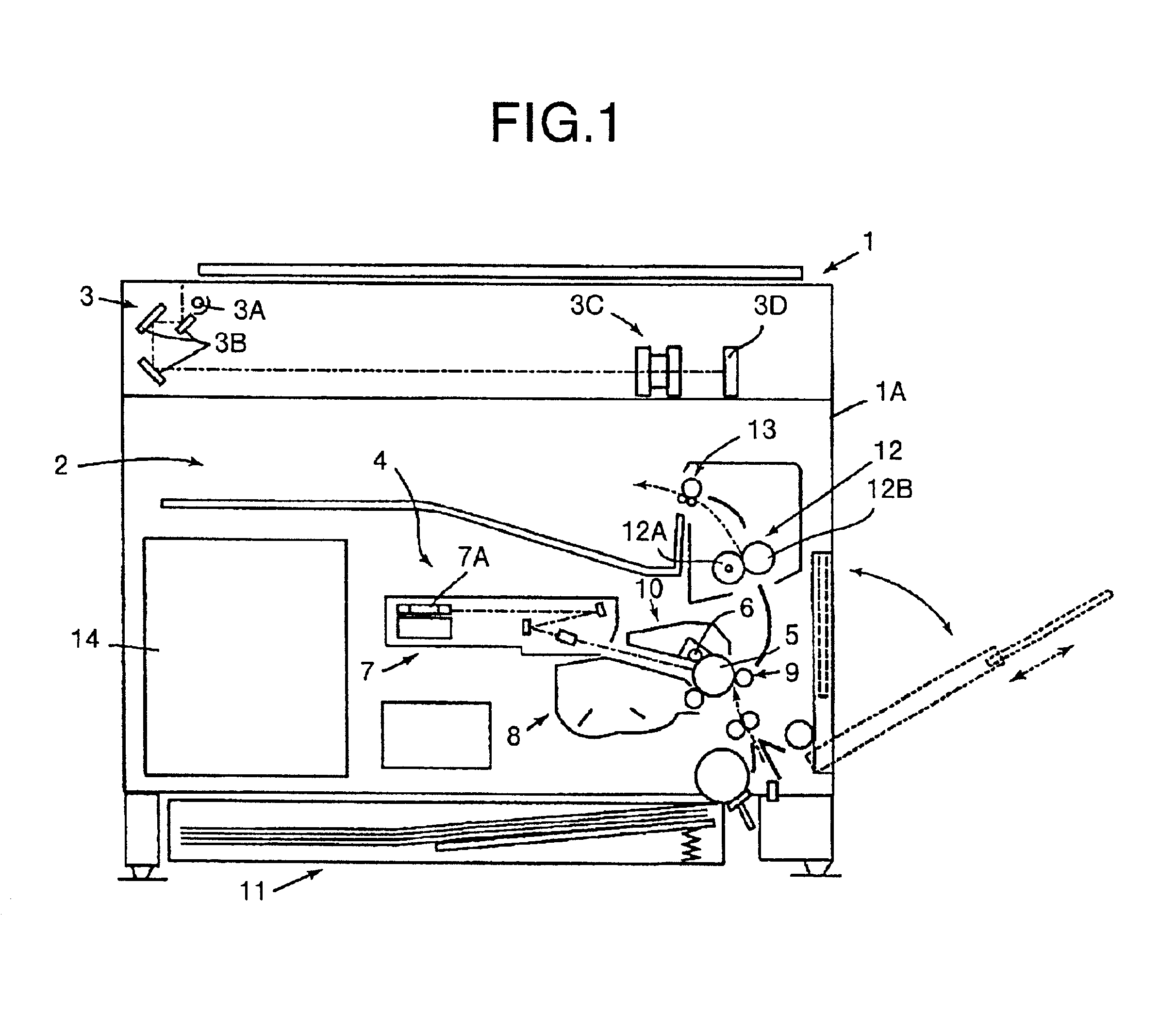

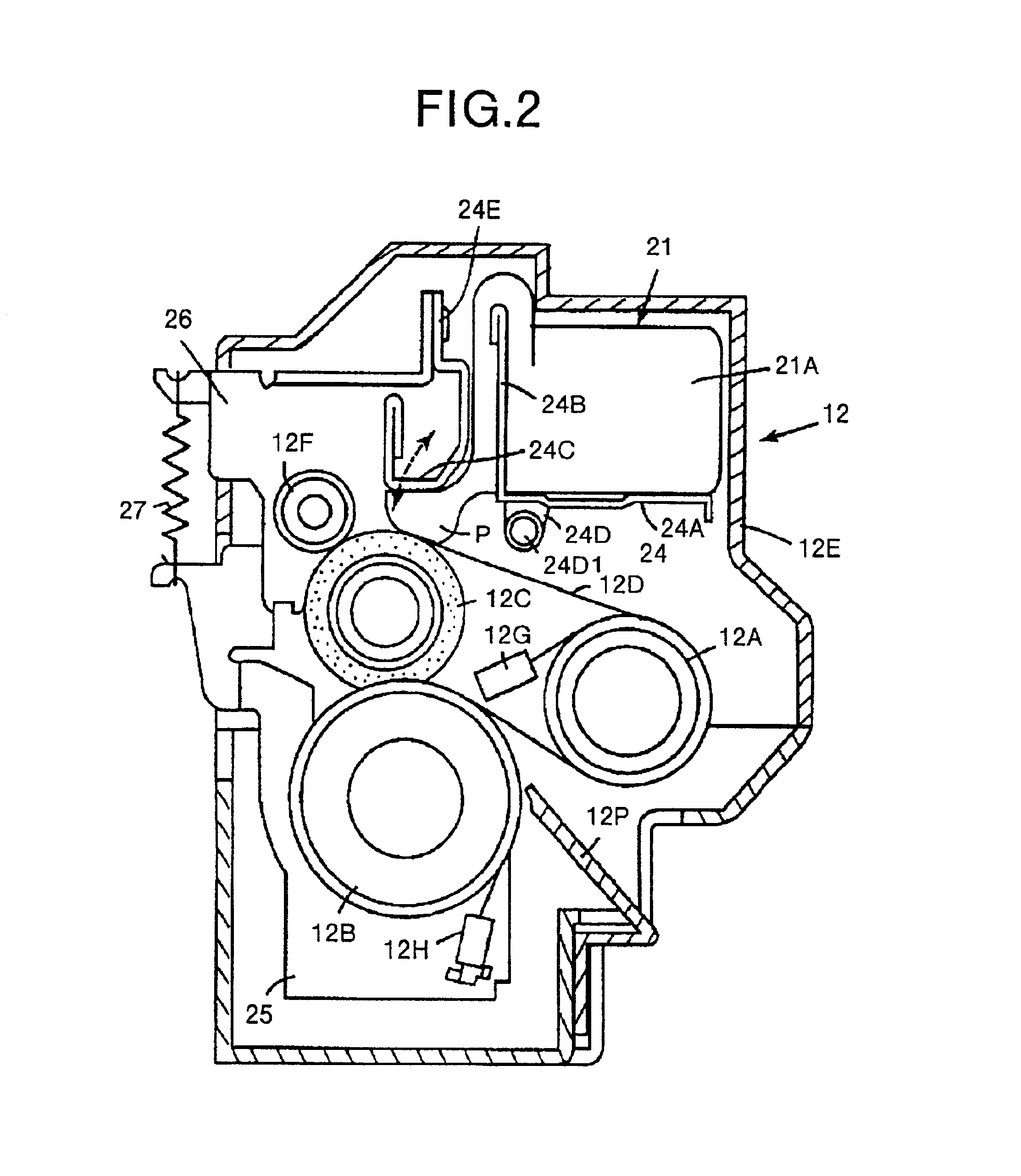

Liquid application apparatus and image formation apparatus

InactiveUS6892044B2Avoid damageLiquid surface applicatorsElectrographic process apparatusMinimum timeImage formation

A liquid application apparatus includes a target to which a liquid is to be applied and an application unit arranged to come in contact or get separated from the target and which applies the liquid to the target when in contact. The target performs cycle motion. A minimum time for which the application unit comes in contact with the target is equal to or greater than a period of the cycle motion of the target.

Owner:RICOH KK

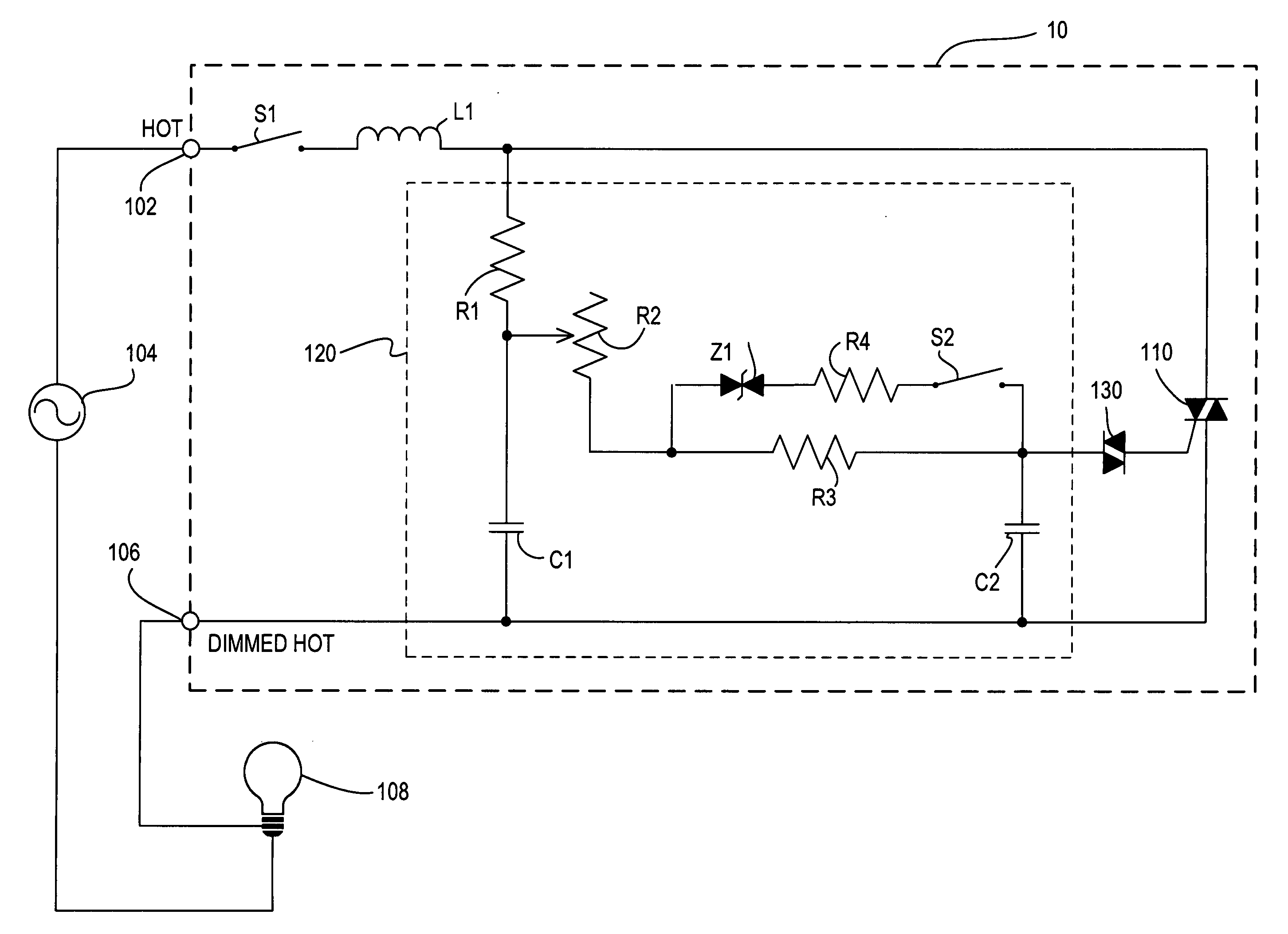

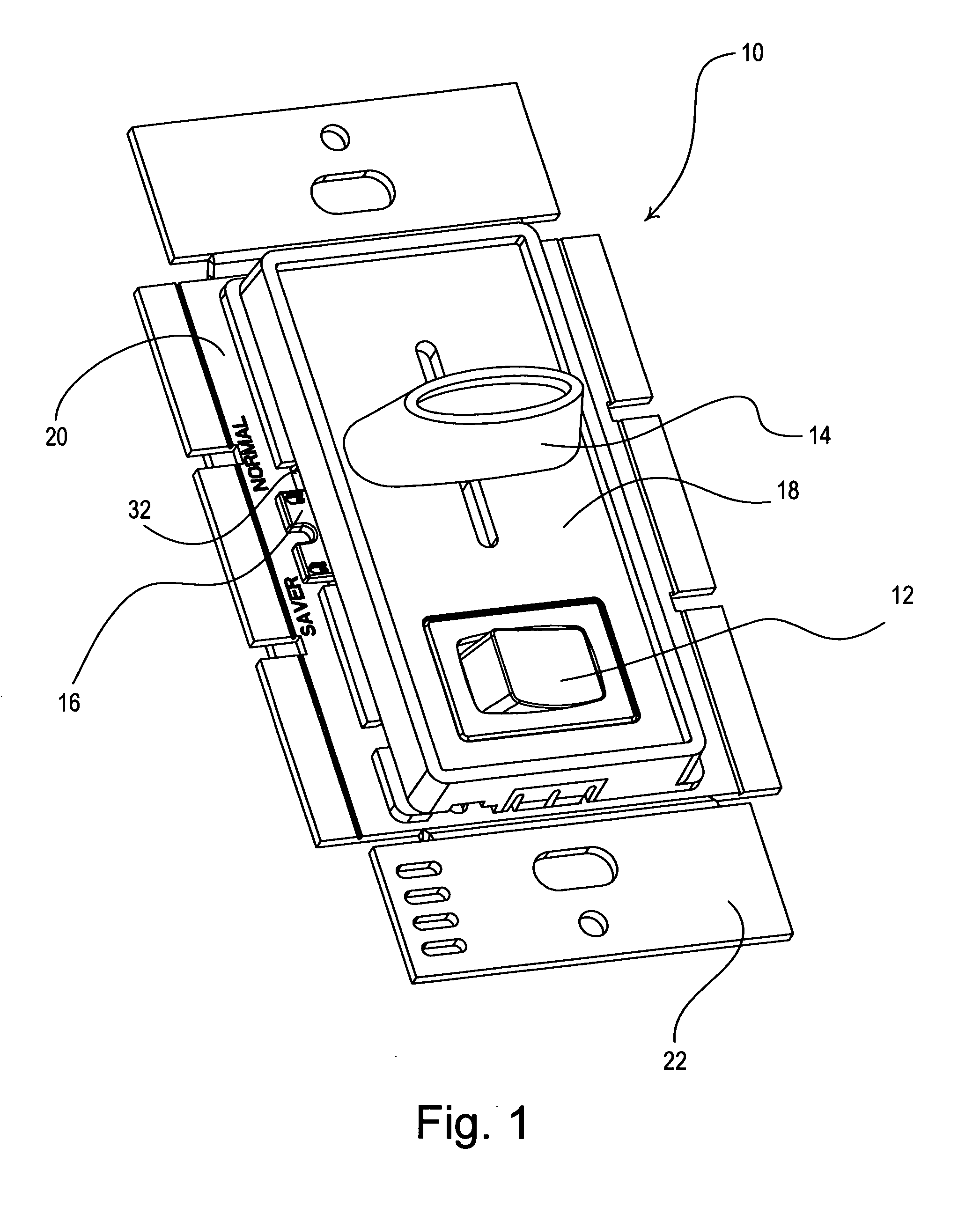

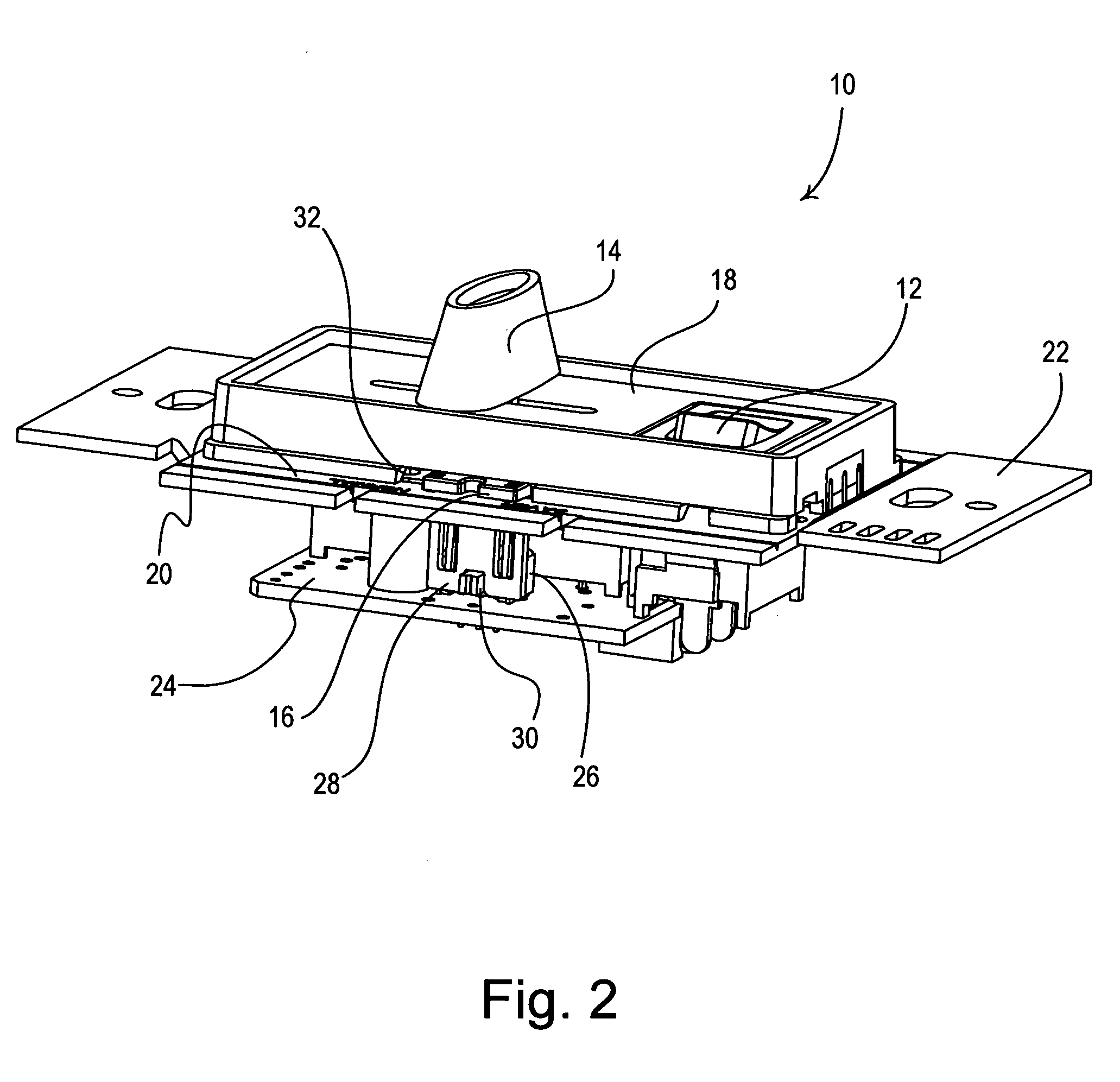

Dimmer switch with adjustable high-end trim

InactiveUS20070285027A1Reducing high-end trimReducing having substantially no affectElectric ignition installationSwitch power arrangementsMinimum timeTRIAC

A dimmer switch has a user adjustable high-end trim. The dimmer switch includes a bidirectional semiconductor switch, such as a triac, for controlling the amount of power delivered from a source of alternating current power to a lighting load, such as an electric lamp. A user-adjustable timing circuit controls the conduction time of the triac from a minimum time to a maximum time. The maximum possible conduction time of the triac is the high-end trim. The minimum possible conduction time of the triac is the low-end trim. The timing circuit includes a user-accessible switch that allows a user to reduce the high-end trim from a first nominal level to a second reduced level, lower than the first level, without substantially affecting the low-end trim. The switch allows a user to switch a transient voltage suppressor into and out of parallel connection with a resistor that is part of an RC timing circuit for the triac. The dimmer switch advantageously uses less energy and the lifetime of the lamp is extended when the second reduced level of the high-end trim is selected.

Owner:LUTRON TECH CO LLC

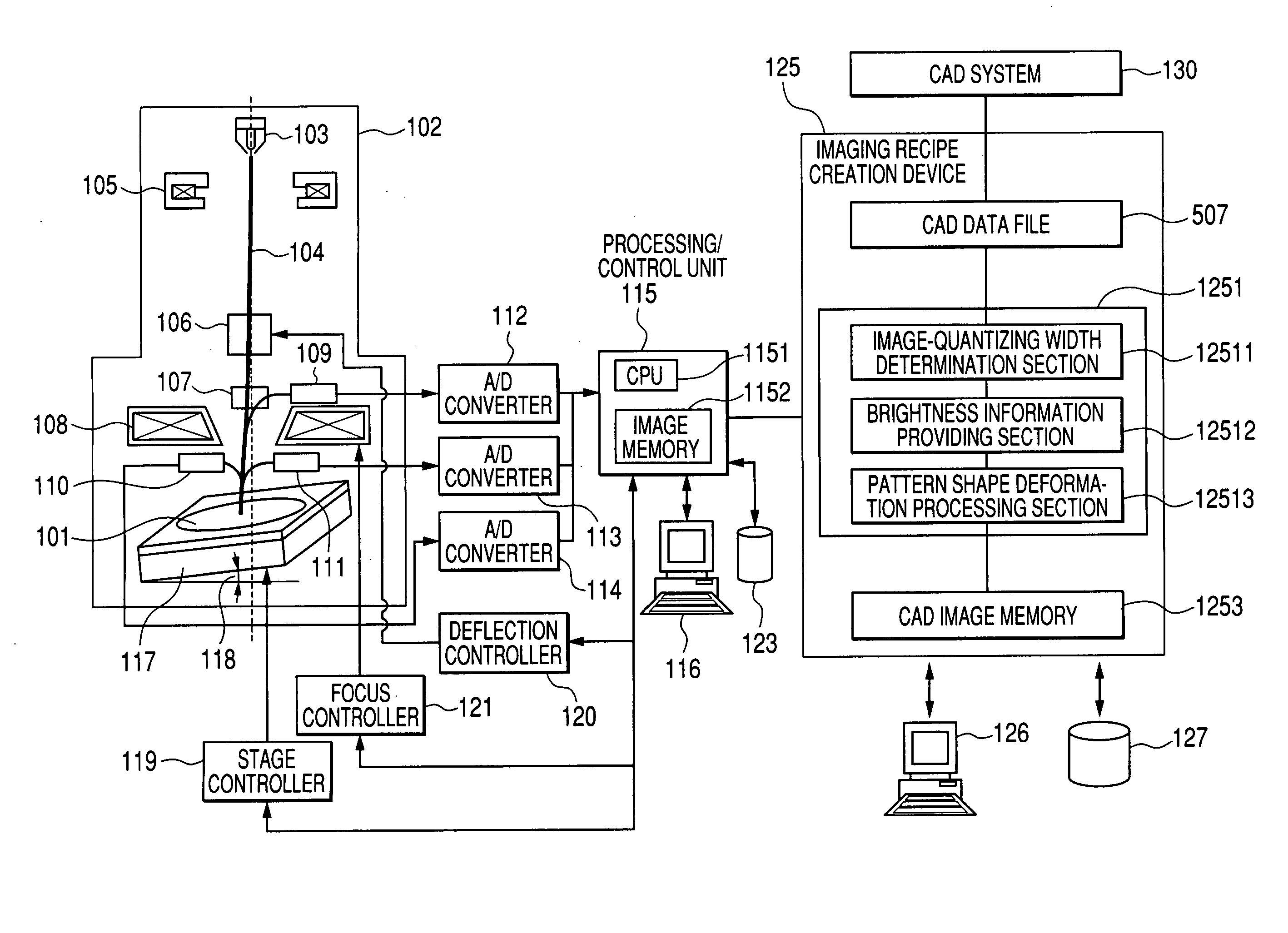

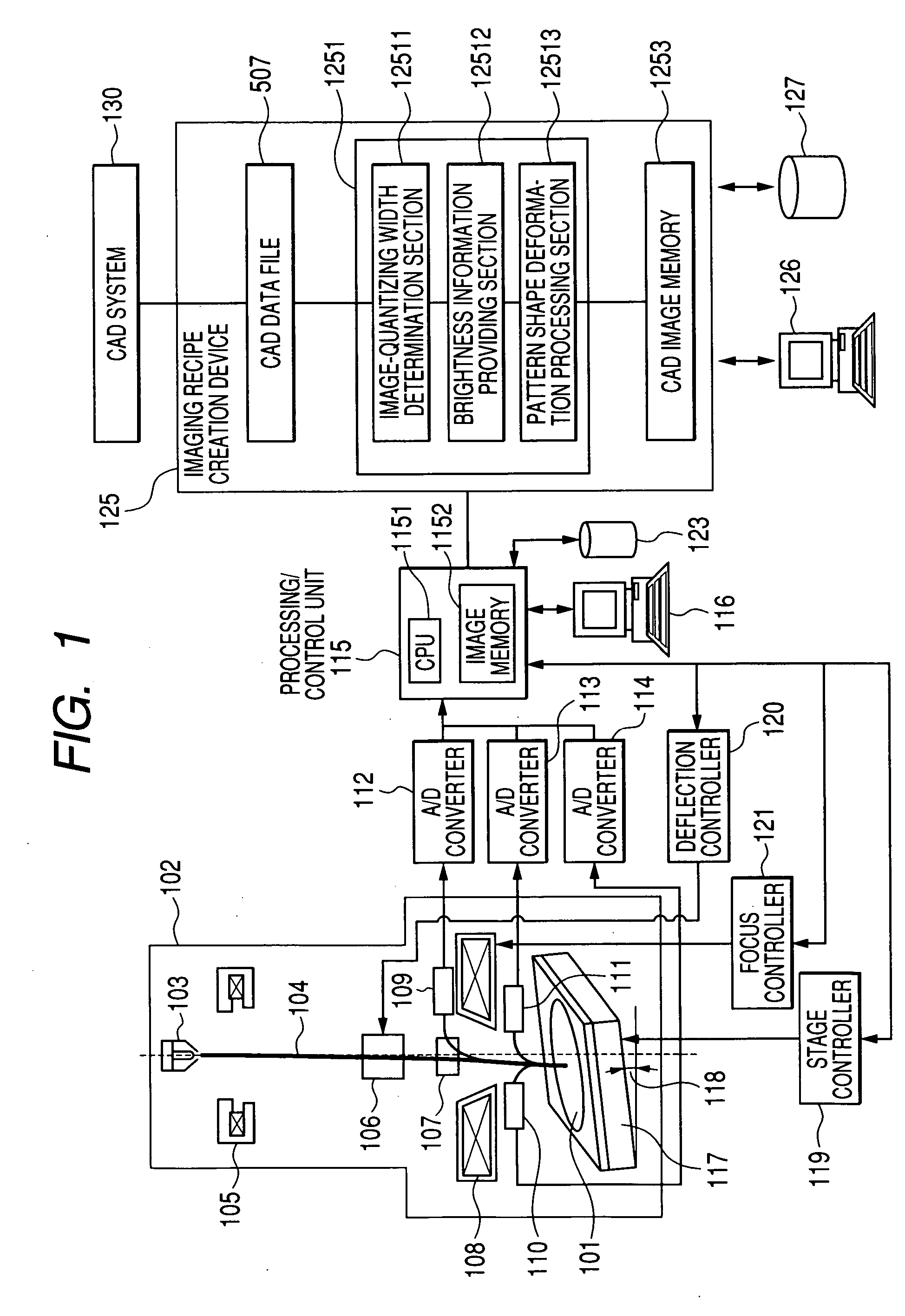

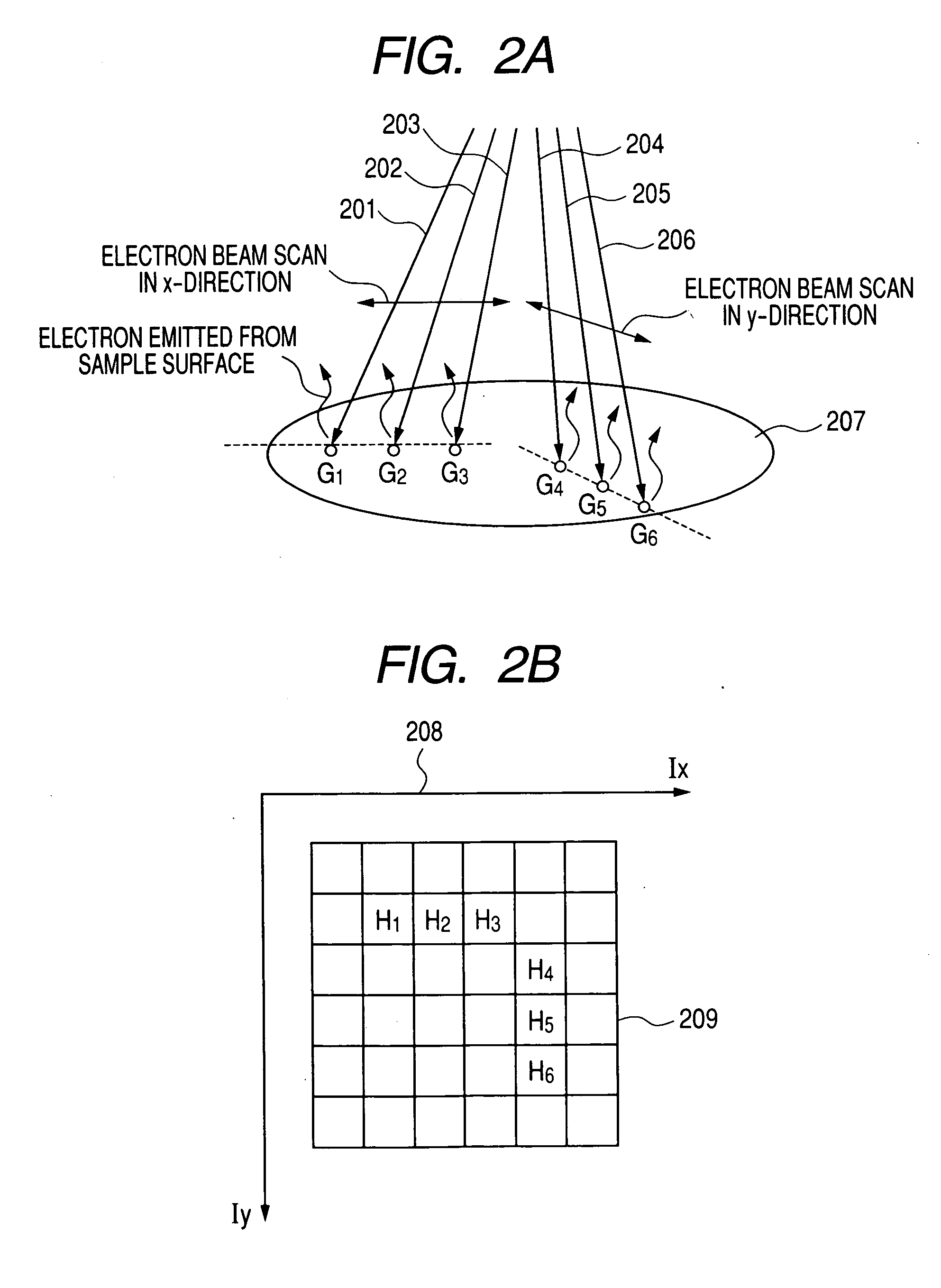

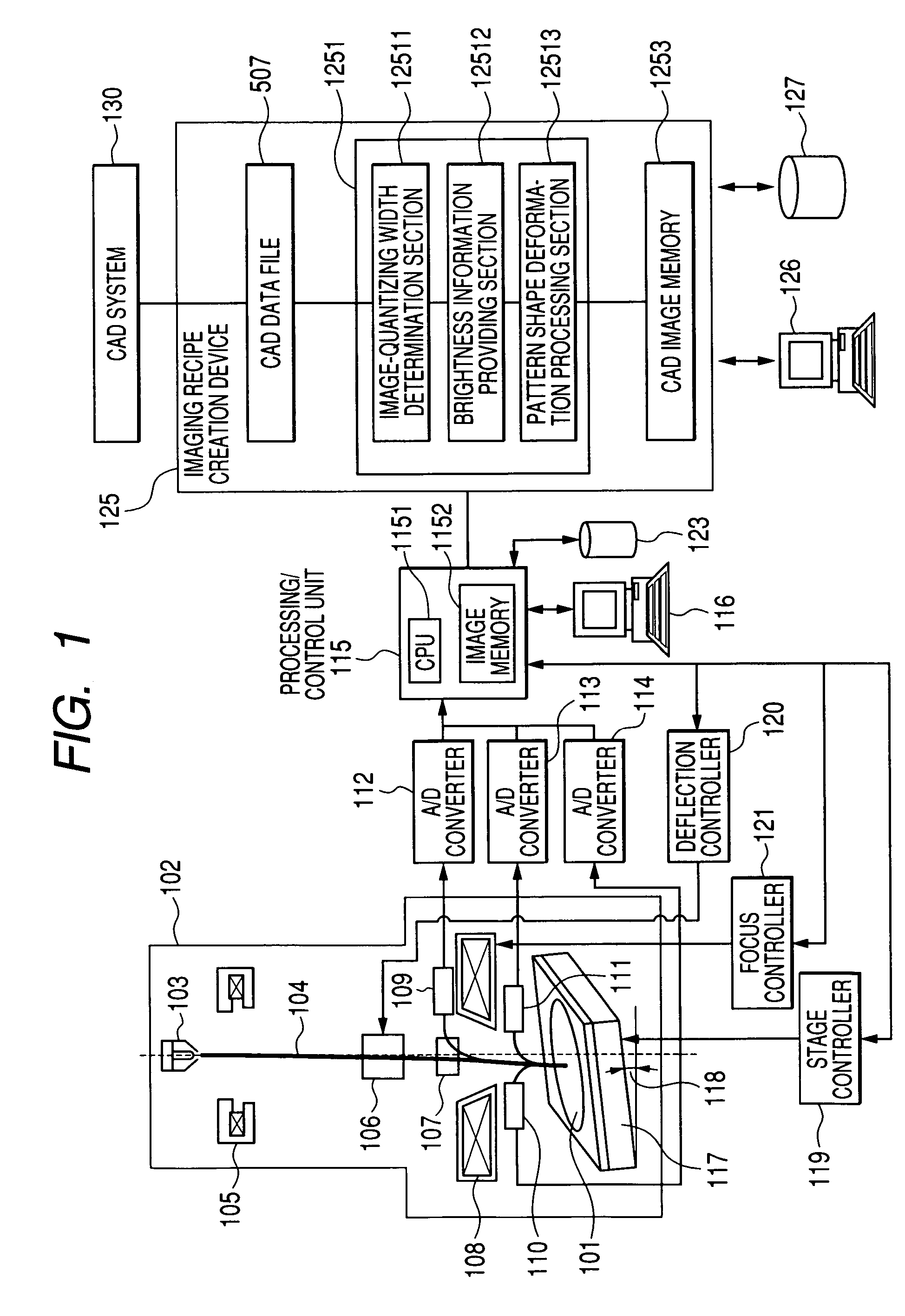

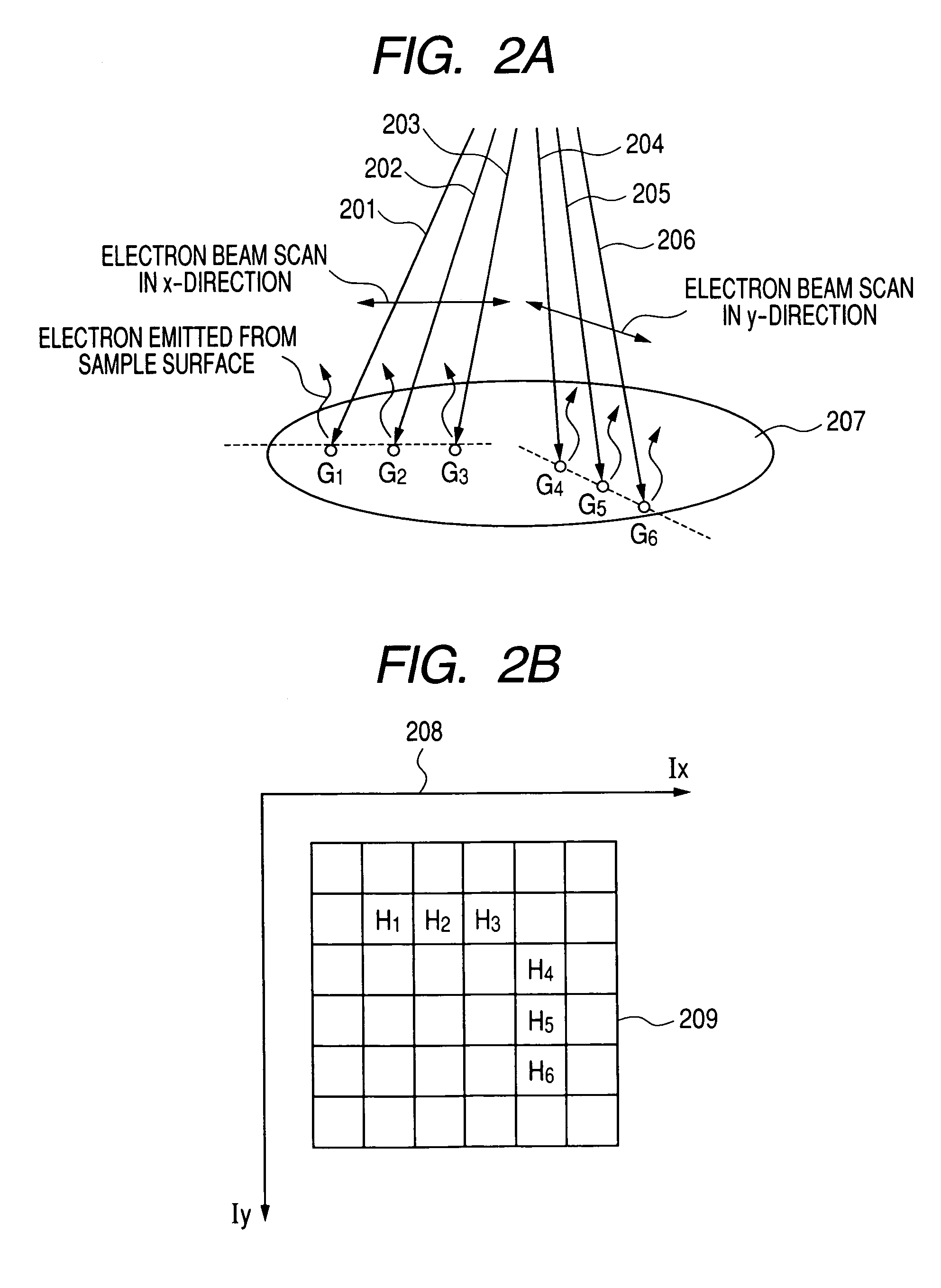

Method and apparatus for measuring dimension of a pattern formed on a semiconductor wafer

ActiveUS20060288325A1Minimal timePossible to generatePhotomechanical apparatusCharacter and pattern recognitionGraphicsMinimum time

In an imaging recipe creating apparatus that uses a scanning electron microscope to create an imaging recipe for SEM observation of a semiconductor pattern, in order that the imaging recipe for measuring the wiring width and other various dimension values of the pattern from an observation image and thus evaluating the shape of the pattern is automatically generated within a minimum time by the analysis using the CAD image obtained by conversion from CAD data, an CAD image creation unit that creates the CAD image by converting the CAD data into an image format includes an image-quantizing width determining section, a brightness information providing section, and a pattern shape deformation processing section; the imaging recipe being created using the CAD image created by the CAD image creation unit.

Owner:HITACHI HIGH-TECH CORP

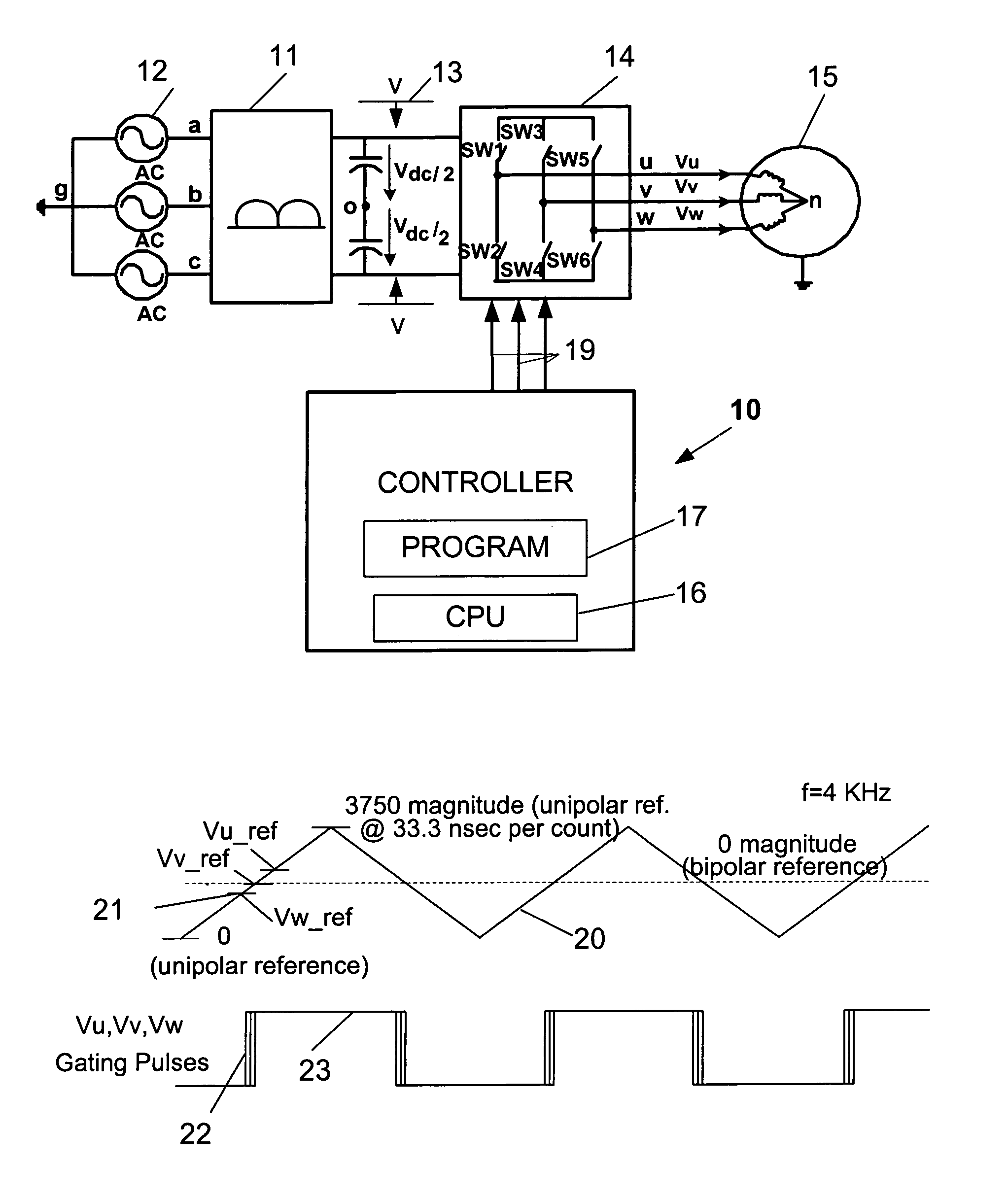

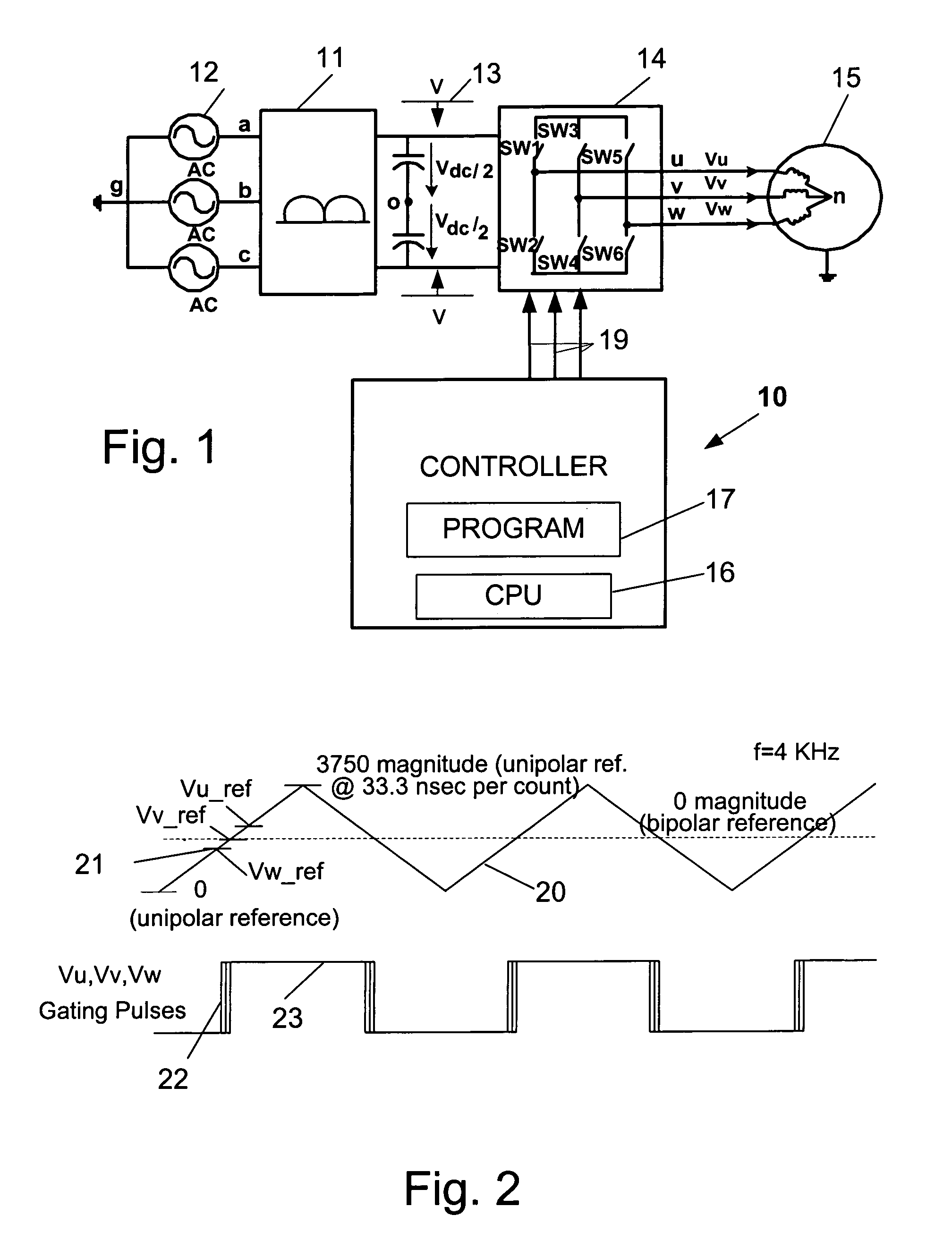

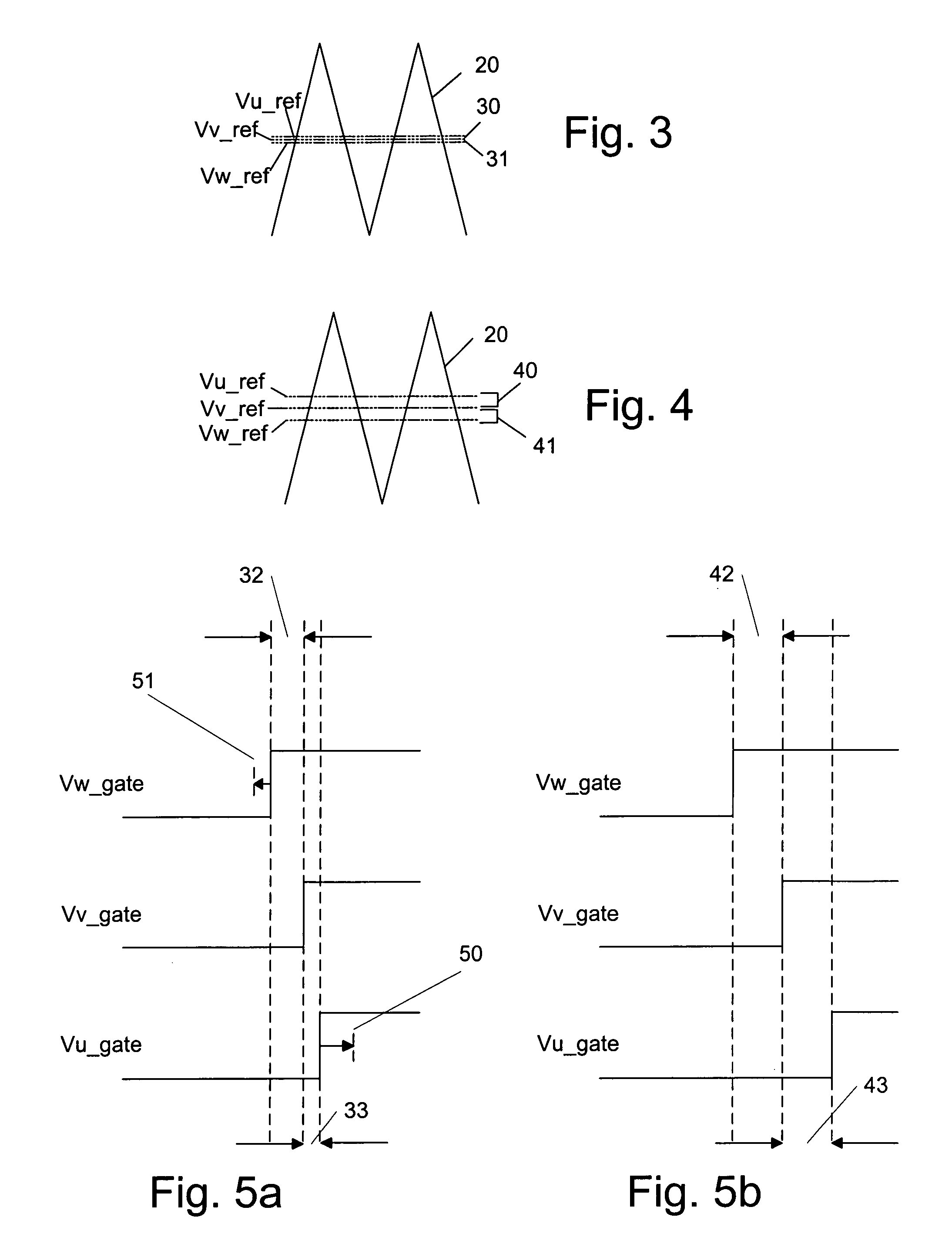

Adjusting gate pulse time intervals for reflected wave mitigation

ActiveUS7034501B1Reduce the impactReduce impactMotor/generator/converter stoppersAC motor controlOvervoltageMinimum time

Methods and apparatus for controlling switching in a DC-to-AC inverter to prevent overvoltages applied to an AC motor by determining the switching order of the phase voltage signals, providing gating signals at switching intervals by modulating a carrier wave with the phase voltage signals, comparing the switching intervals to a predetermined minimum time interval sufficient for reflected wave transients to dissipate, and adjusting the switching intervals to be at least equal to the predetermined minimum time interval.

Owner:ROCKWELL AUTOMATION TECH

Prescription compliance device and method of using device

Owner:BAREHOLDTECH LLC

Calculation of state of charge offset using a closed integral method

InactiveUS20060022643A1Eliminate hysteresisCircuit monitoring/indicationEmergency protective circuit arrangementsBattery state of chargeHysteresis

A state of charge control system and method uses a region of voltage linearity and a long-term average voltage to estimate an average battery state of charge for storage batteries and to eliminate errors due to hysteresis, drift and sensor noncompliance. An average state of charge Sn is calculated using a current integral method and an average state of charge Sv based on an average observed voltage Vn for a time period exceeding a predefined minimum time but before a predefined maximum time has elapsed is also calculated. If the absolute value of the difference between the Sv and Sn are not are within an acceptable error band, then an offset value is calculated to correct the Sn by subtracting the Sv from the Sn, and thus, to maintain a more accurate Sn. Additionally, a closed current integral method is used to reduce errors due to hysteresis.

Owner:FORD GLOBAL TECH LLC

Patient controlled timed oral medication dispenser

ActiveUS7044302B2Promotes autonomyPromotes patient autonomySmall article dispensingContainer/bottle contructionMedication DispenserOral medication

The oral medication delivery device provides patient access to medications prescribed to be available on an as-needed basis, but with a minimum time intervals between doses. The required time interval between drug accessibility is programmed into the device when the medication tray carrying the multiple doses is loaded into the device. The device allows access to a single dose of the medication after each minimum time interval has elapsed. When the drug dose is removed from the device, the medication tray locks until the next minimum time interval has elapsed.

Owner:AVANCEN MOD

Patient controlled timed medication dispenser

ActiveUS20050258066A1Small article dispensingCoin-freed apparatus detailsMedication DispenserMinimum time

The medication delivery device provides patient access to medications prescribed to be available on an as-needed basis, but with a minimum time intervals between doses. The device permits access to a single dose of the medication after each minimum time interval has elapsed. When the drug dose is removed from the device, the medication tray locks until the next minimum dosage time interval has elapsed.

Owner:AVANCEN MOD

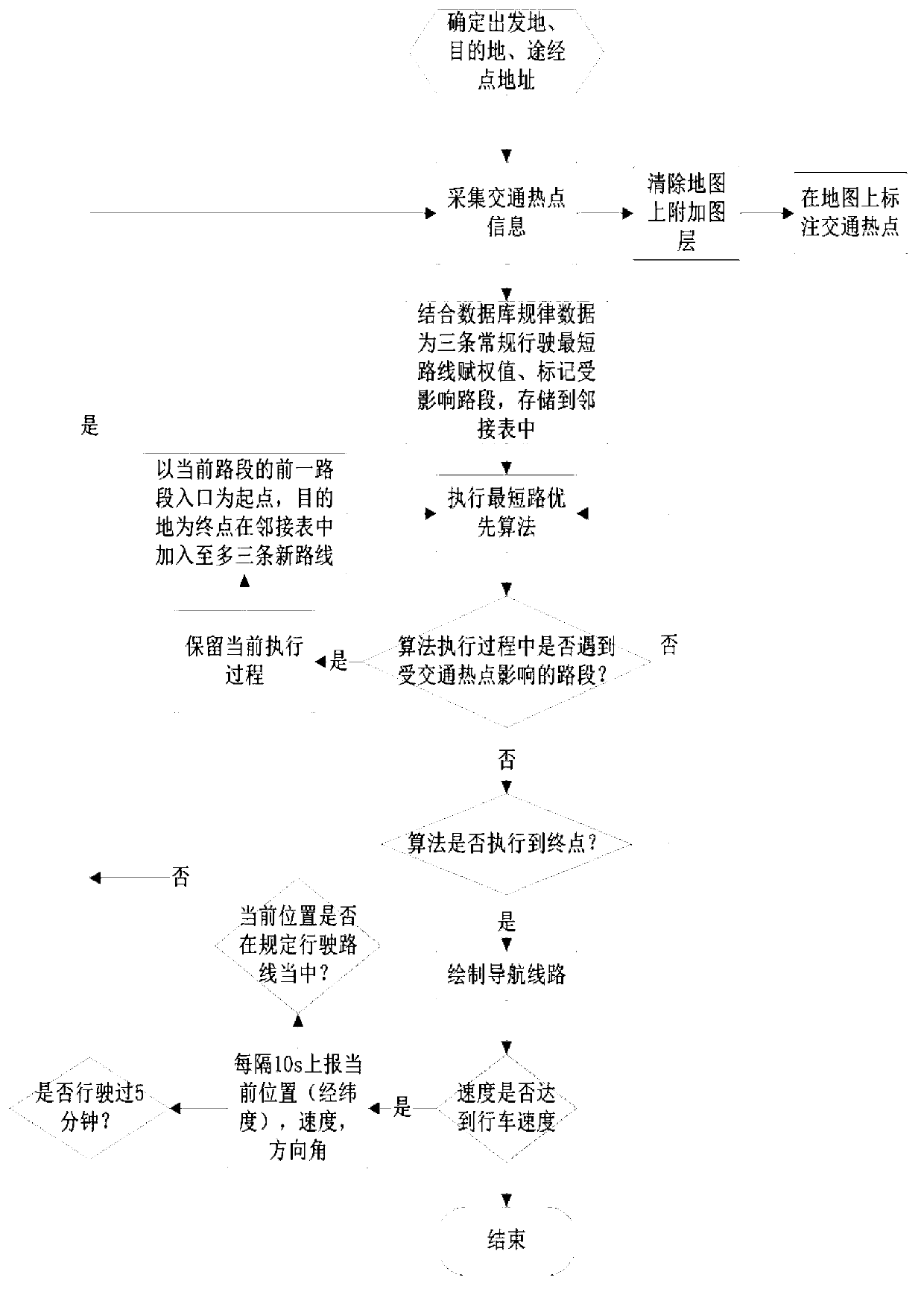

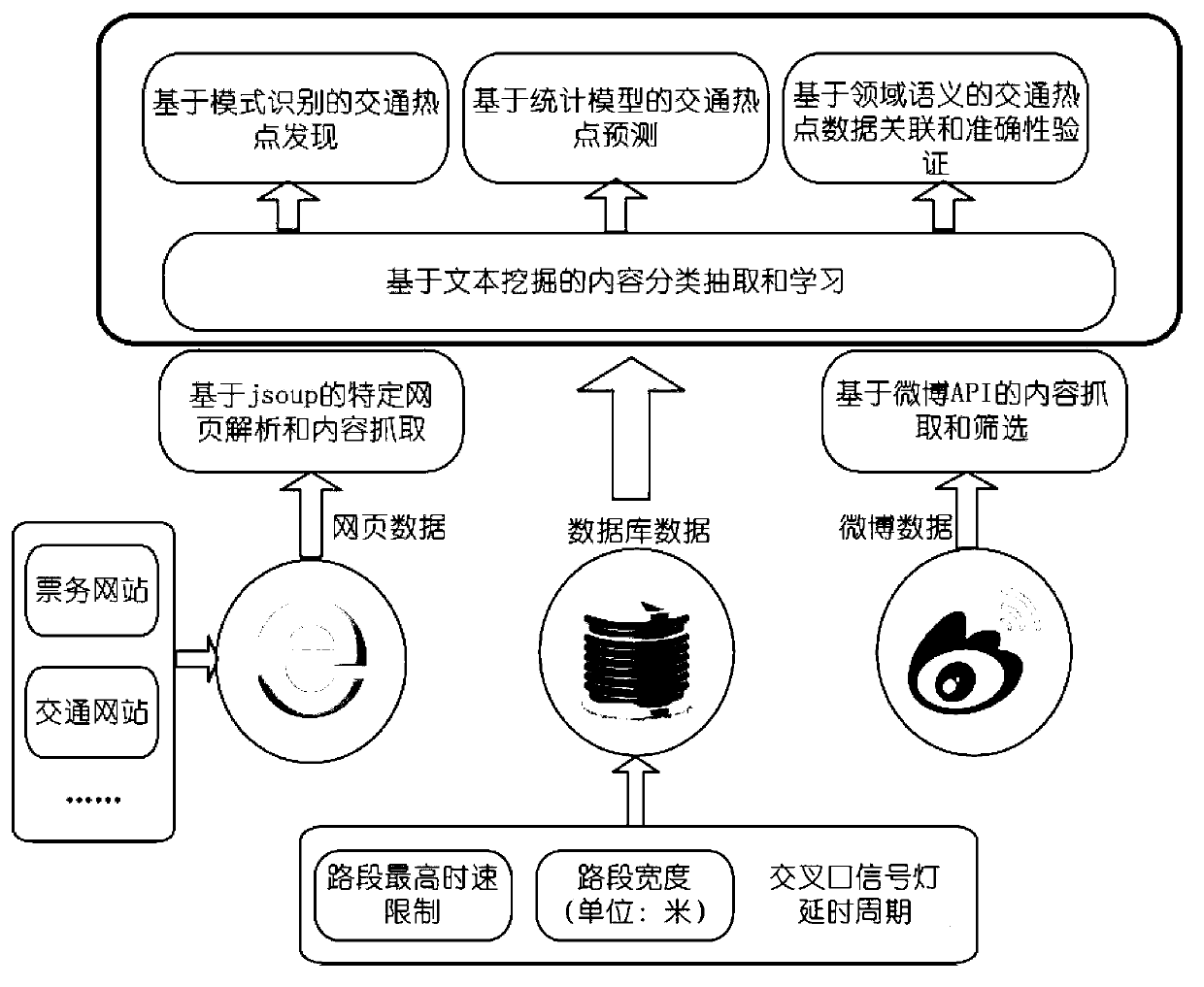

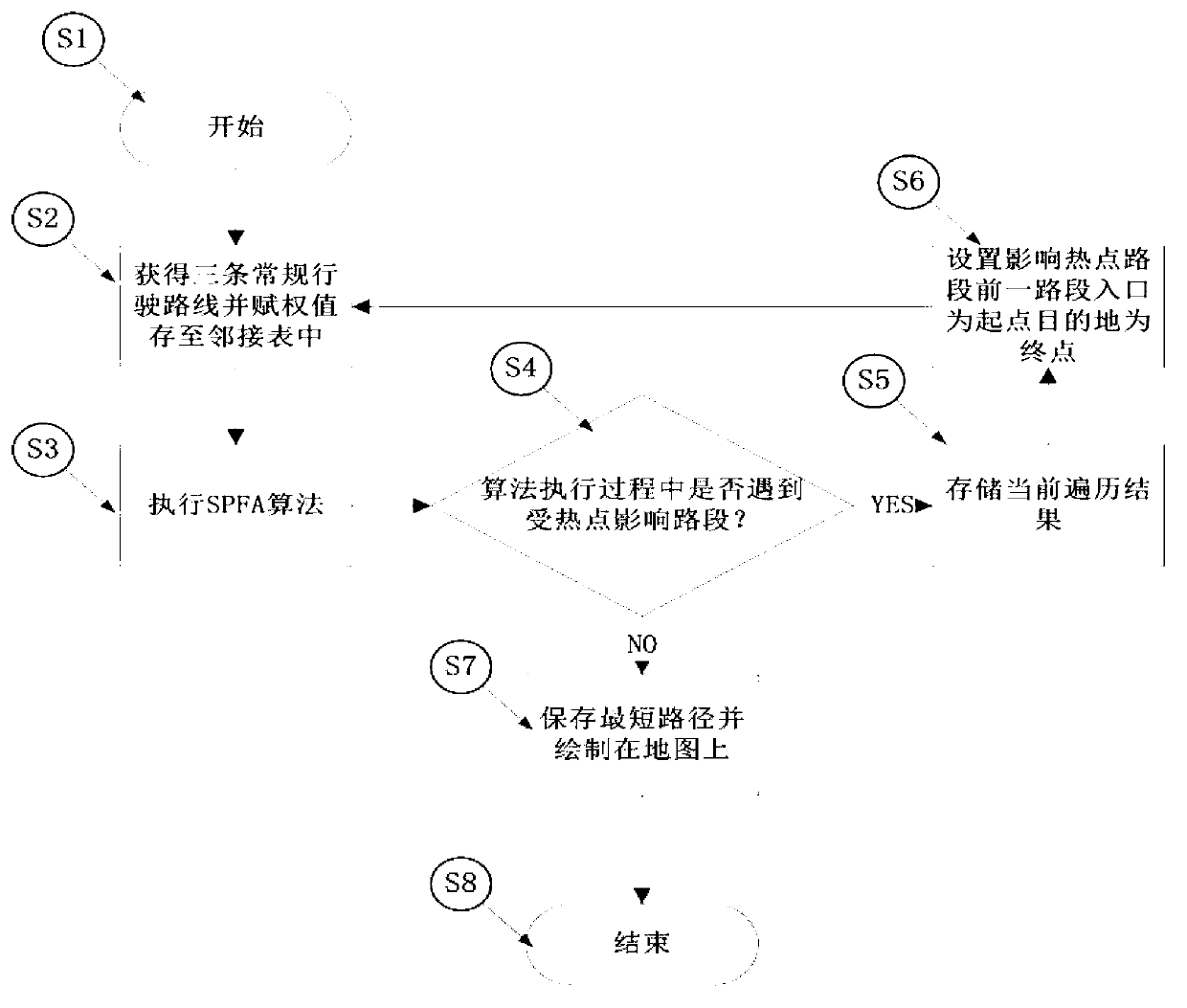

Path planning method for avoiding of traffic hotspots

InactiveCN103278168AExtensive sources of dataIncrease credibilityInstruments for road network navigationFast pathMinimum time

A path planning method for avoiding of traffic hotspots helps to realize an intelligent path planning method with a purpose of the shortest journey time, by dynamical planning of paths with an avoiding property, based on a destination where a driving user goes. The traffic hotspot information, such as large-scale activities, traffic accidents, traffic-peak block roads, school time or commuter time of large-scale units, weather information and the like, are mined continually from a plurality of data sources comprising webpages, microblogs, real-time reported traffic information, historical regularity information and the like. By acquisition of the traffic hotspot information in real time, and combination with influences of a road maximum speed limit, road width and traffic light delay at intersections to driving as well as whether a main road containing a non-motor vehicle zone, a rapid navigation route with an avoiding function is planed, and also a dynamic path planning can be carried out in real time base on a current position. The method helps to provide a fastest path to the destination for drivers and alleviate city traffic jam in certain degree.

Owner:BEIHANG UNIV

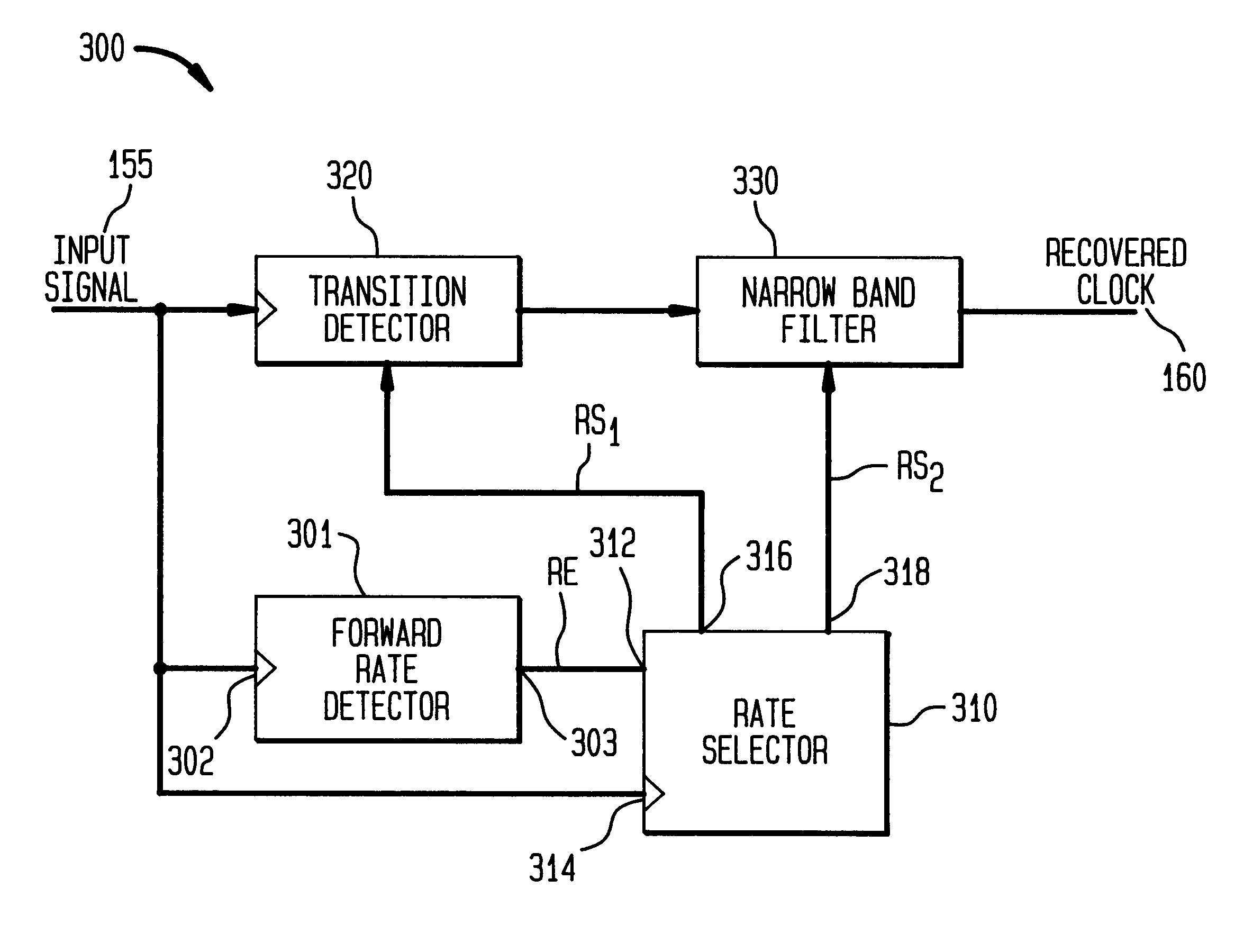

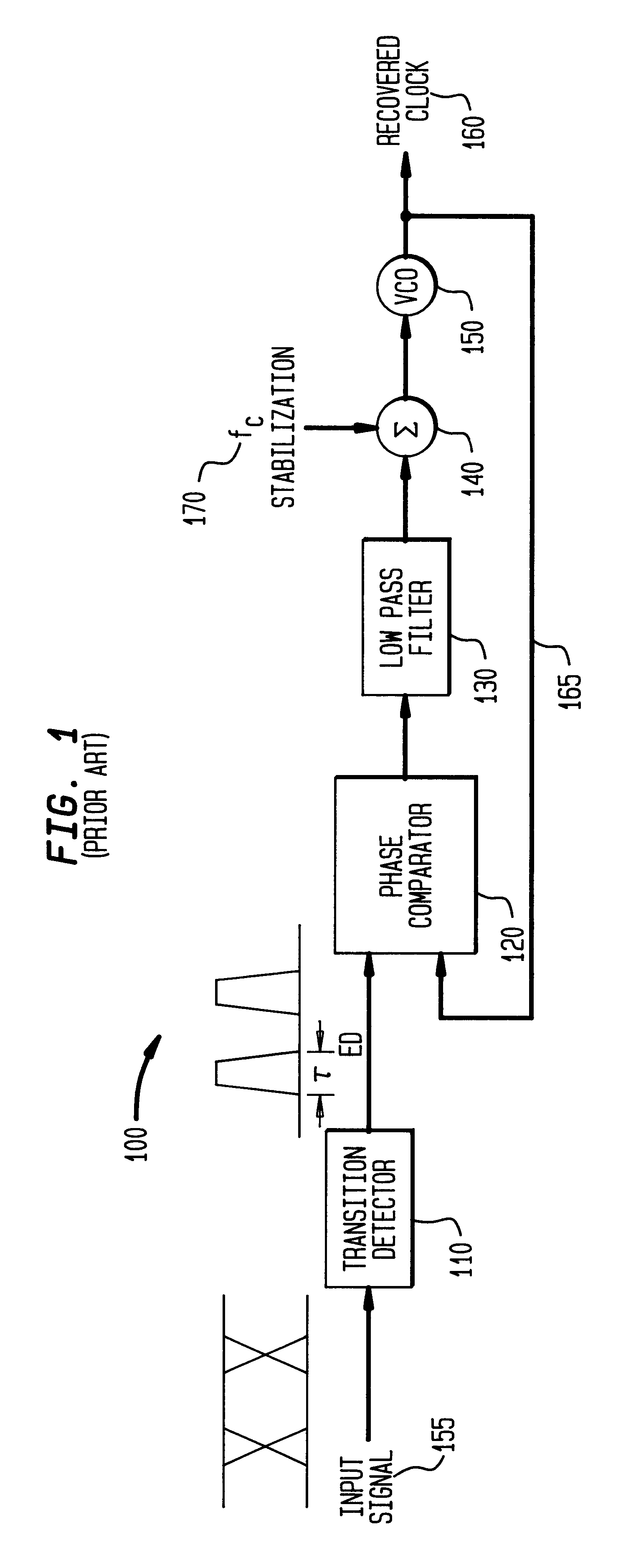

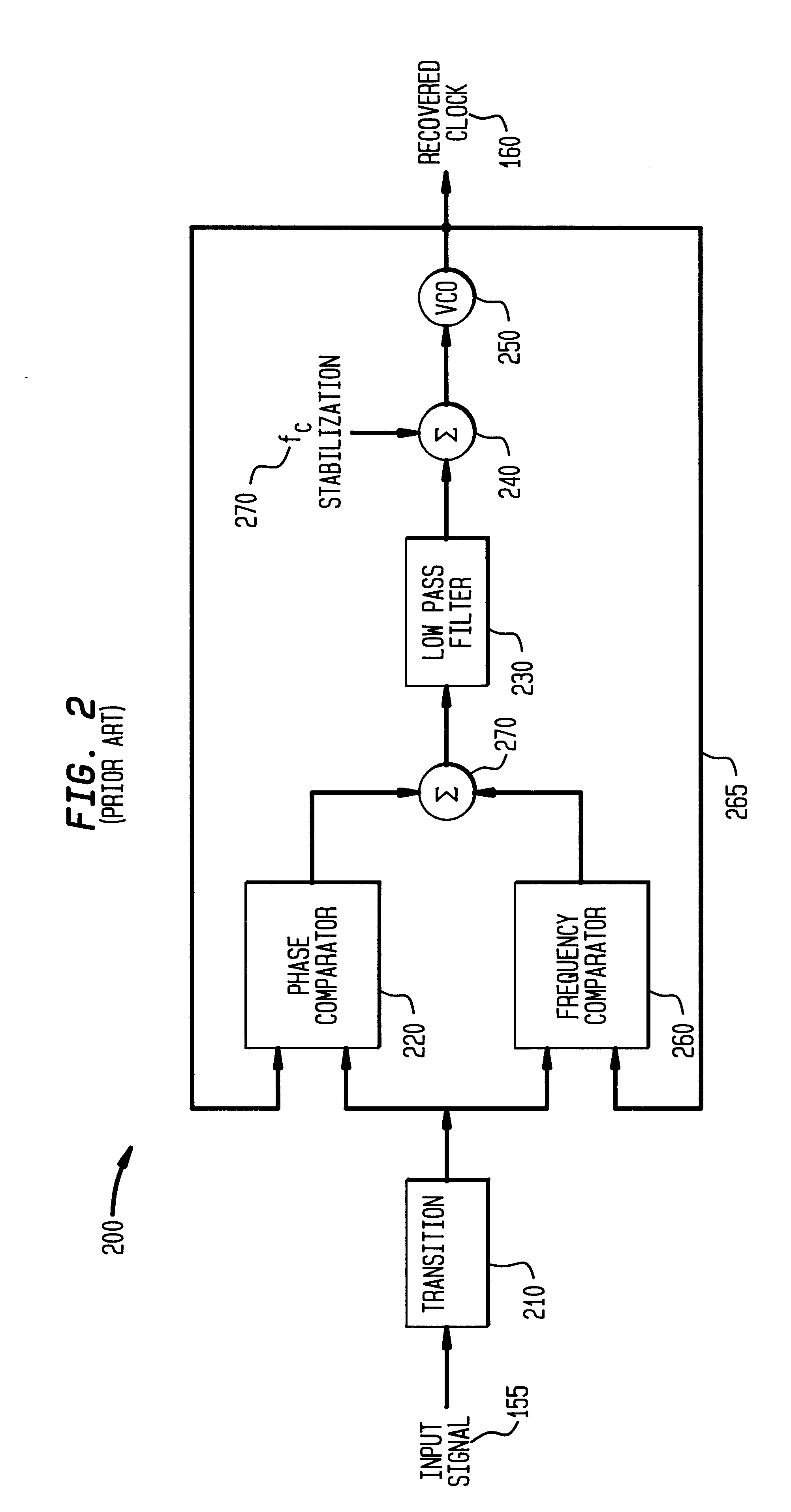

Method and apparatus for variable bit rate clock recovery

Methods and apparatuses consistent with the present invention recover a clock signal from a variable bit rate data signal by estimating, in the time domain, the bit rate of the data signal, and based on the estimated variable bit rate, determining a center frequency of a narrow-band filter for extracting the clock signal from the data signal. A clock recovery circuit consistent with the present invention extracts a clock signal from a variable bit rate data signal by estimating a minimum time interval between transitions in the data signal, generating a plurality of pulses that correspond respectively to transitions in the data signal, adjusting the duration of each of the pulses based on the estimated minimum time interval and inputting into a narrow-band filter the adjusted pulses, determining a center frequency of the narrow-band filter based on the estimated minimum time interval, and extracting in the narrow-band filter the clock signal from the adjusted pulses.

Owner:HANGER SOLUTIONS LLC

Proximity switch and method of adjusting sensitivity therefor

A vehicle proximity switch and method are provided having sensitivity control. The switch includes a proximity sensor, such as a capacitive sensor, installed in a vehicle and providing a sense activation field. Control circuitry processes the activation field to sense user activation of the switch by comparing the activation field to a threshold. The threshold is adjusted down when a substantially stable sensor signal is detected below the threshold for a minimum time period, and the threshold is adjusted up when a sensor signal greater than the threshold by a predetermined value is detected.

Owner:FORD GLOBAL TECH LLC

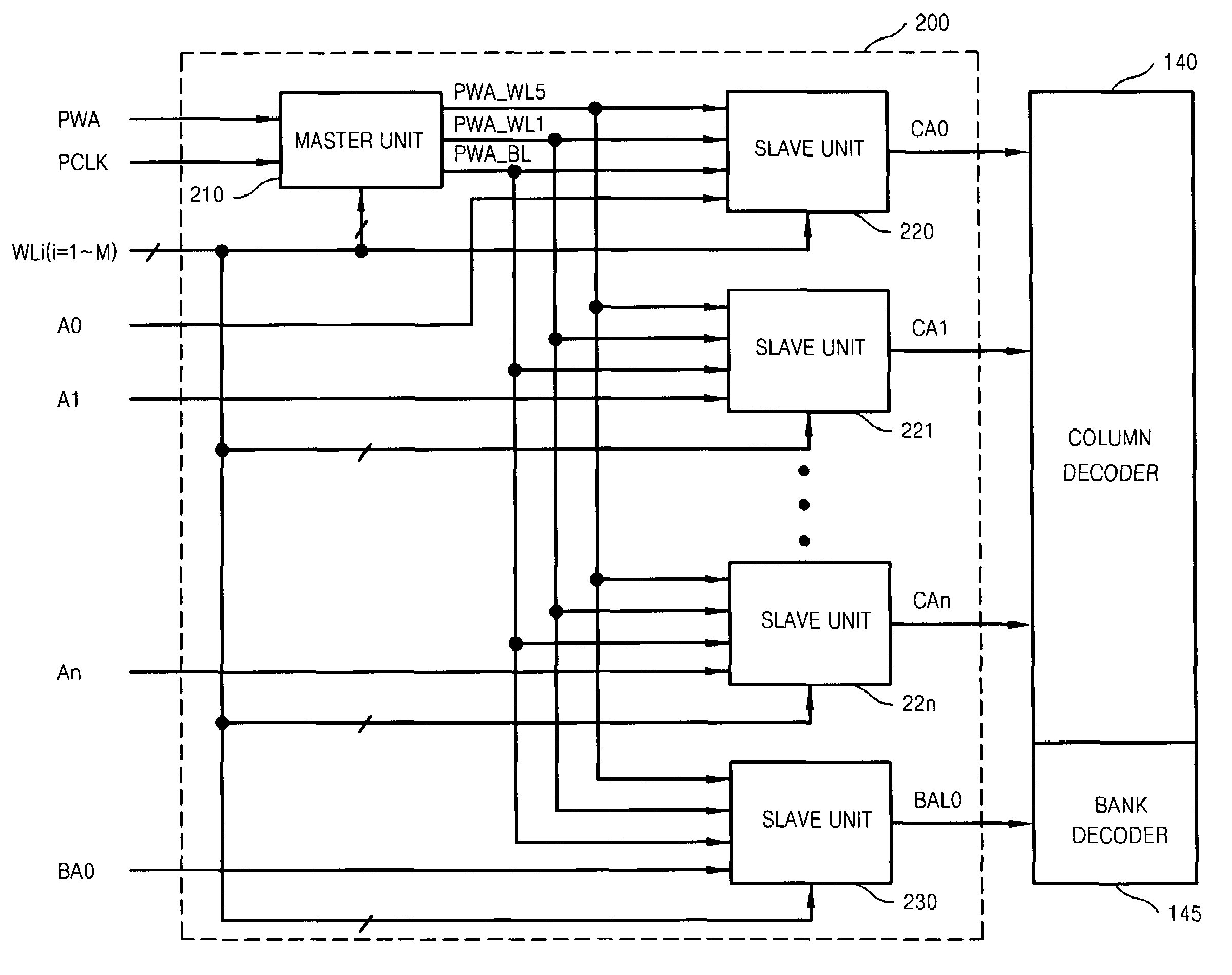

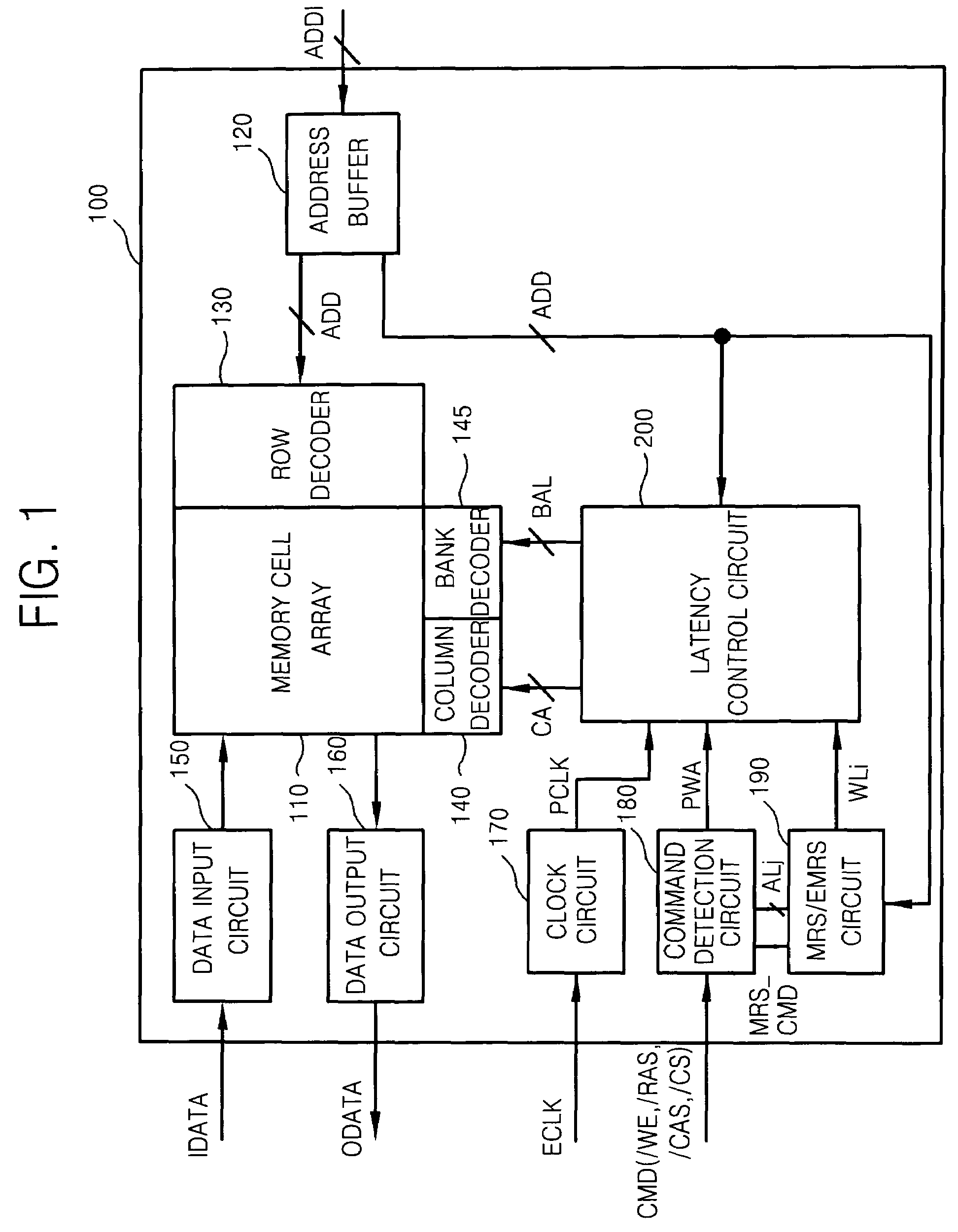

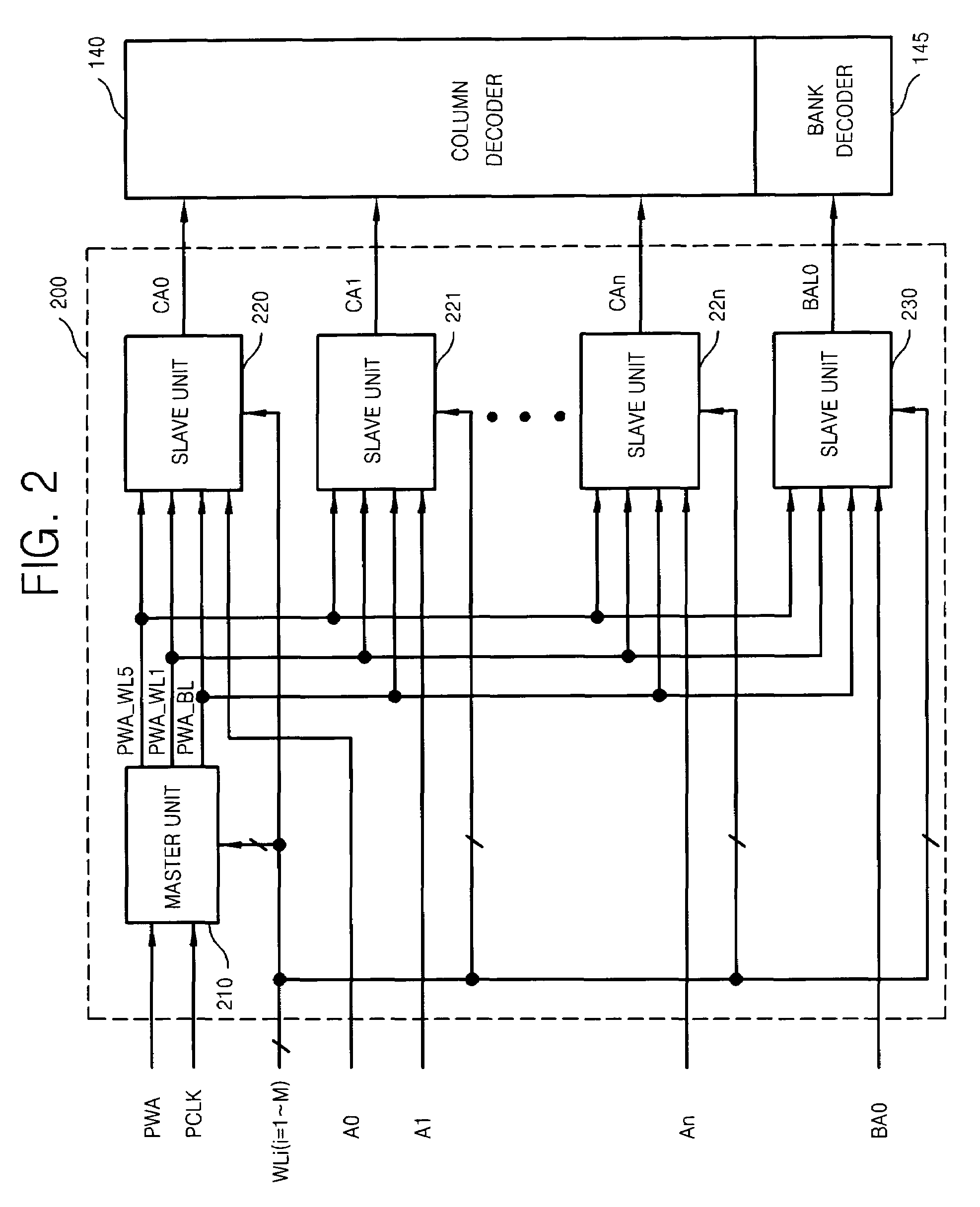

Latency control circuit and method thereof and an auto-precharge control circuit and method thereof

InactiveUS7609584B2Decreasing routing complexity and circuit area and delayReduced footprintDigital storageMinimum timeMemory bank

A latency control circuit and method thereof and auto-precharge control circuit and method thereof are provided. The example latency control circuit may include a master unit activating at least one master signal based on a reference signal and an internal clock signal and a plurality of slave units receiving the at least one master signal, each of the plurality of slave units receiving a plurality of signals and outputting an output signal based at least in part upon one of the received plurality of signals. The example method of latency control may include receiving at least one master signal, the received at least one master signal activated based on a reference signal and an internal clock signal and receiving a plurality of signals and outputting an output signal based at least in part upon one of the received plurality of signals and latency information. The example auto-precharge control circuit may include a precharge command delay unit generating a plurality of first precharge command delay signals in response to an internal clock signal and a write auto-precharge command signal, at least one bank address delay unit outputting a delayed bank address signal and a precharge main signal generator outputting a precharge main signal to banks based on the delayed bank address signal. The method of performing a precharging operation with the auto-precharge control circuit may include delaying a bank address signal based on a minimum time interval between executed memory commands and outputting a precharge main signal to one or more memory banks based on the delayed bank address signal.

Owner:SAMSUNG ELECTRONICS CO LTD

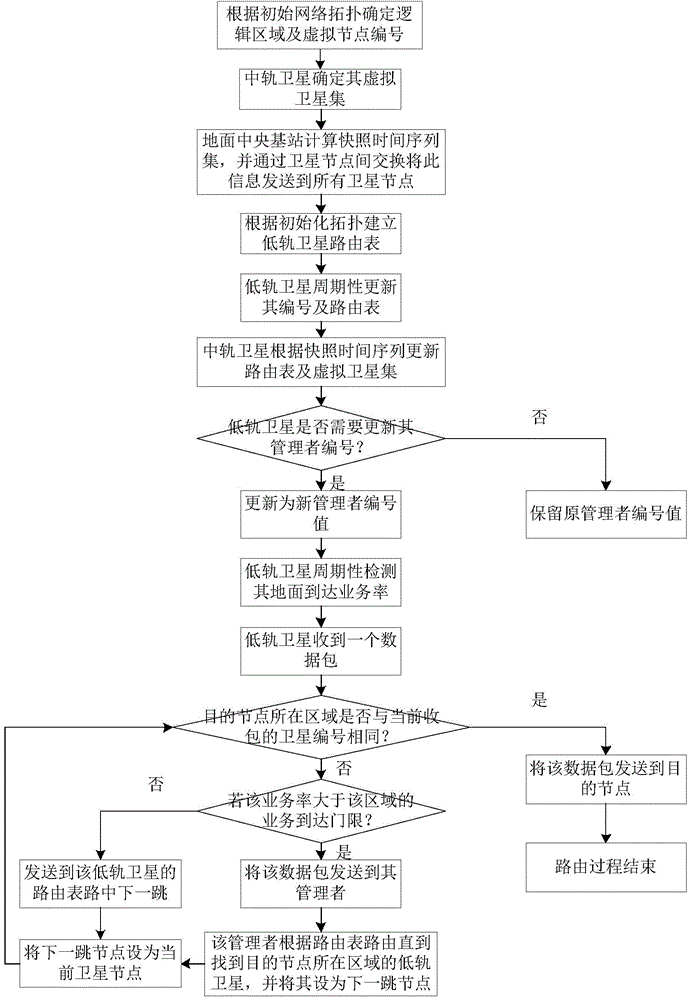

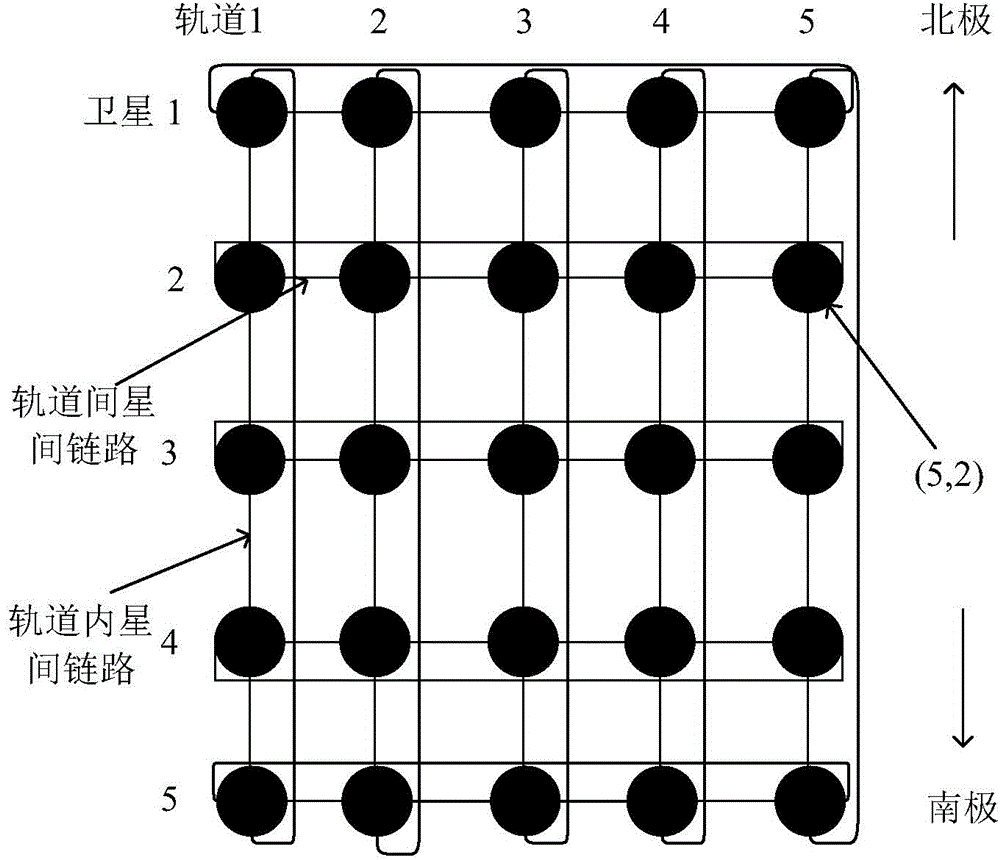

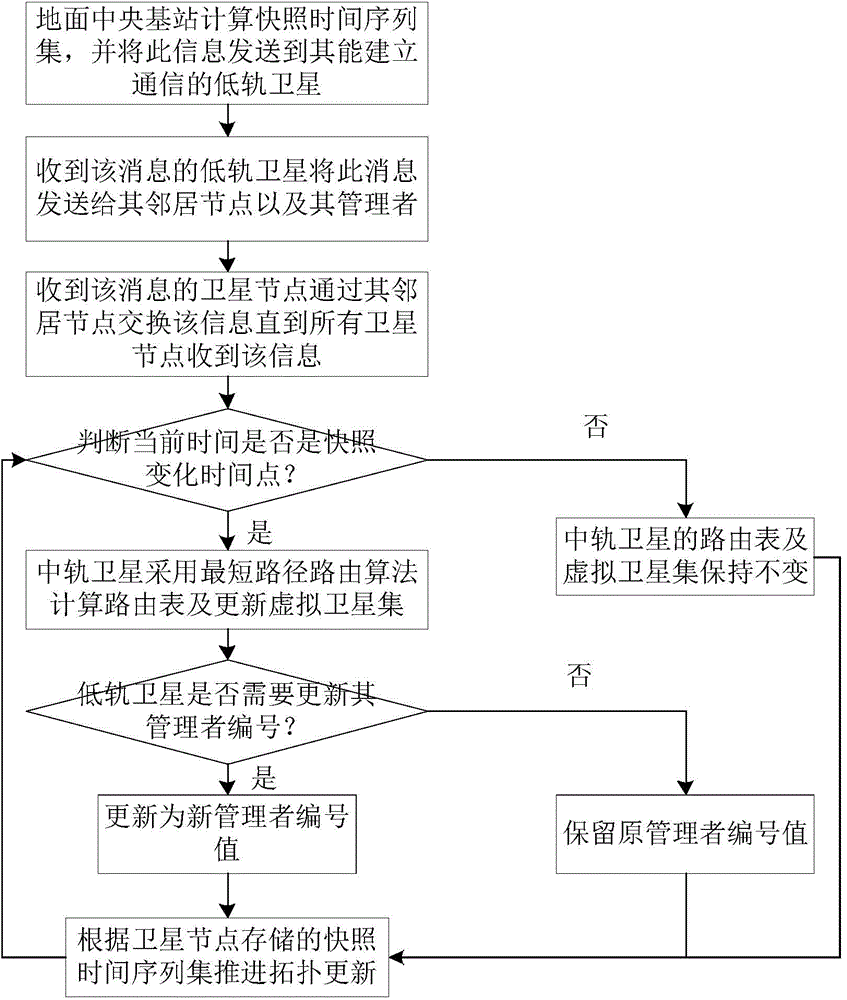

Method for distributing and routing optimal services of multi-layer satellite network based on minimum time delay

ActiveCN104683016ASolve congestionImprove throughputRadio transmissionData switching networksMinimum timeLow earth orbit

The invention discloses a method for distributing and routing optimal services of multi-layer satellite network based on minimum time delay, and aims to solve the problems of large end-to-end time delay, low handling capacity and insufficient utilization of network resource of a multi-layer satellite communication network routing method. The method comprises the following steps: determining a logic area, a virtual node number and a low-earth-orbit satellite routing list according to the initial network topology; periodically updating the node number and the routing list by a low earth orbit; updating a virtual satellite set and a member routing list according to the snapshot time sequence set by a medium earth orbit, and synchronously updating the number of an administrator by the low earth orbit; if the services arrive and the arrival rate of the current satellite area is less than the arrival rate threshold of the ground service supported by the area based on the minimum end-to-end time, transmitting the service in the low earth orbit, and otherwise, transferring the service to a high-level satellite to route, and finally sending a target node. With the adoption of the method, the performance of the multi-layer satellite communication network is improved; the method can be applied to the routing of the multi-layer satellite communication network.

Owner:XIDIAN UNIV

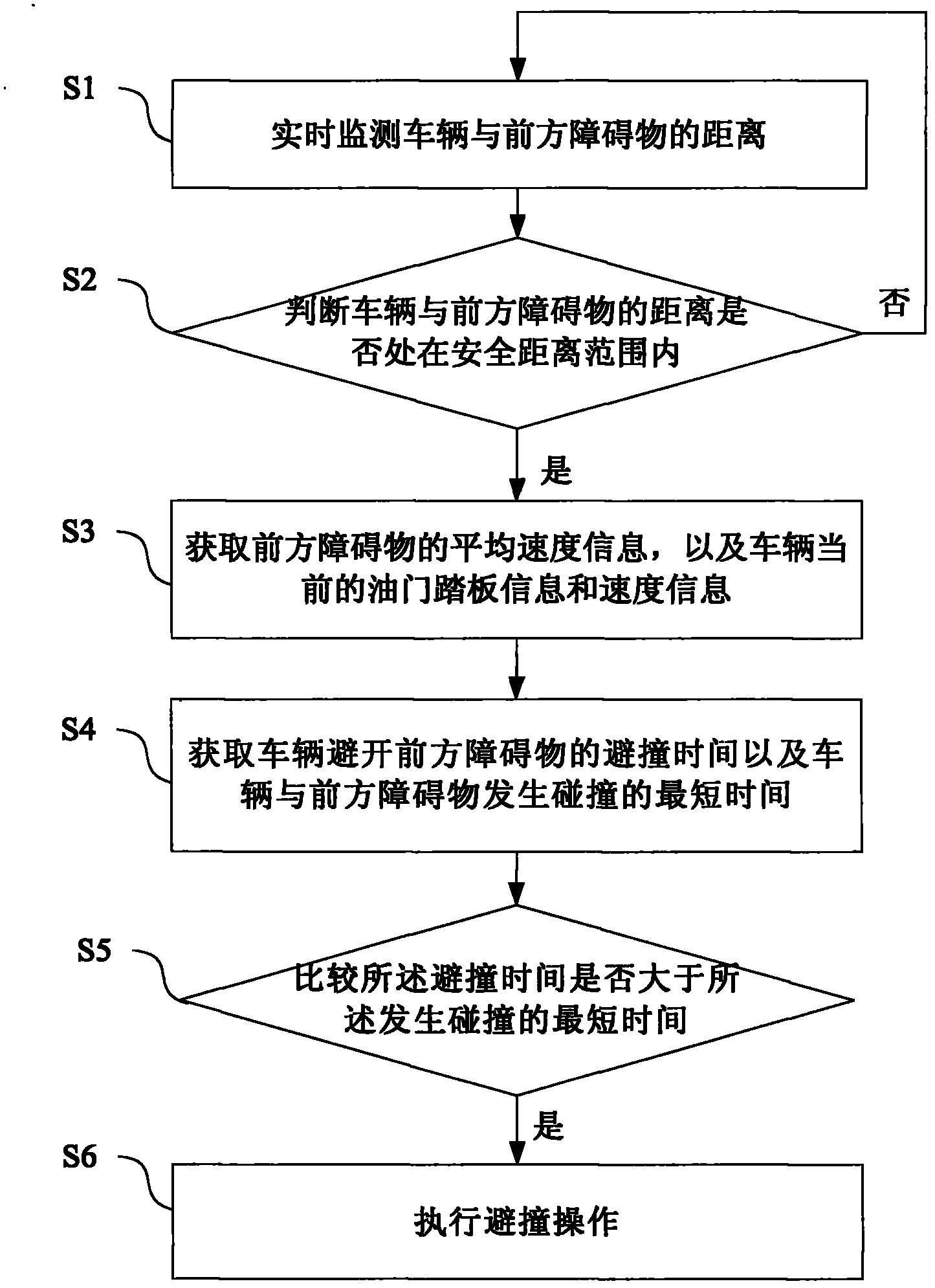

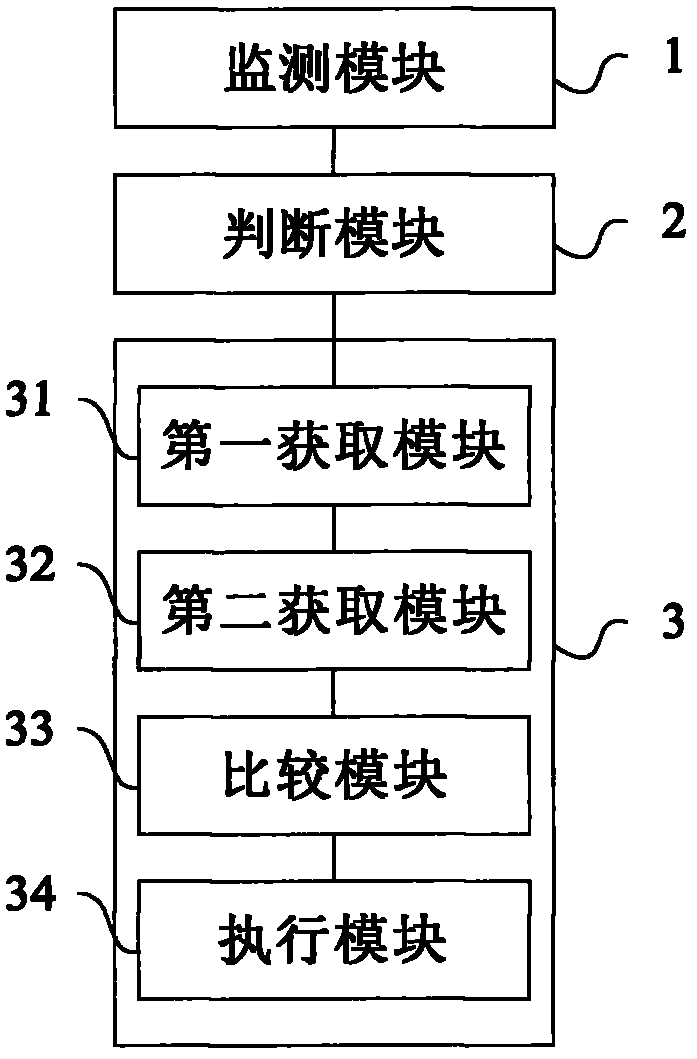

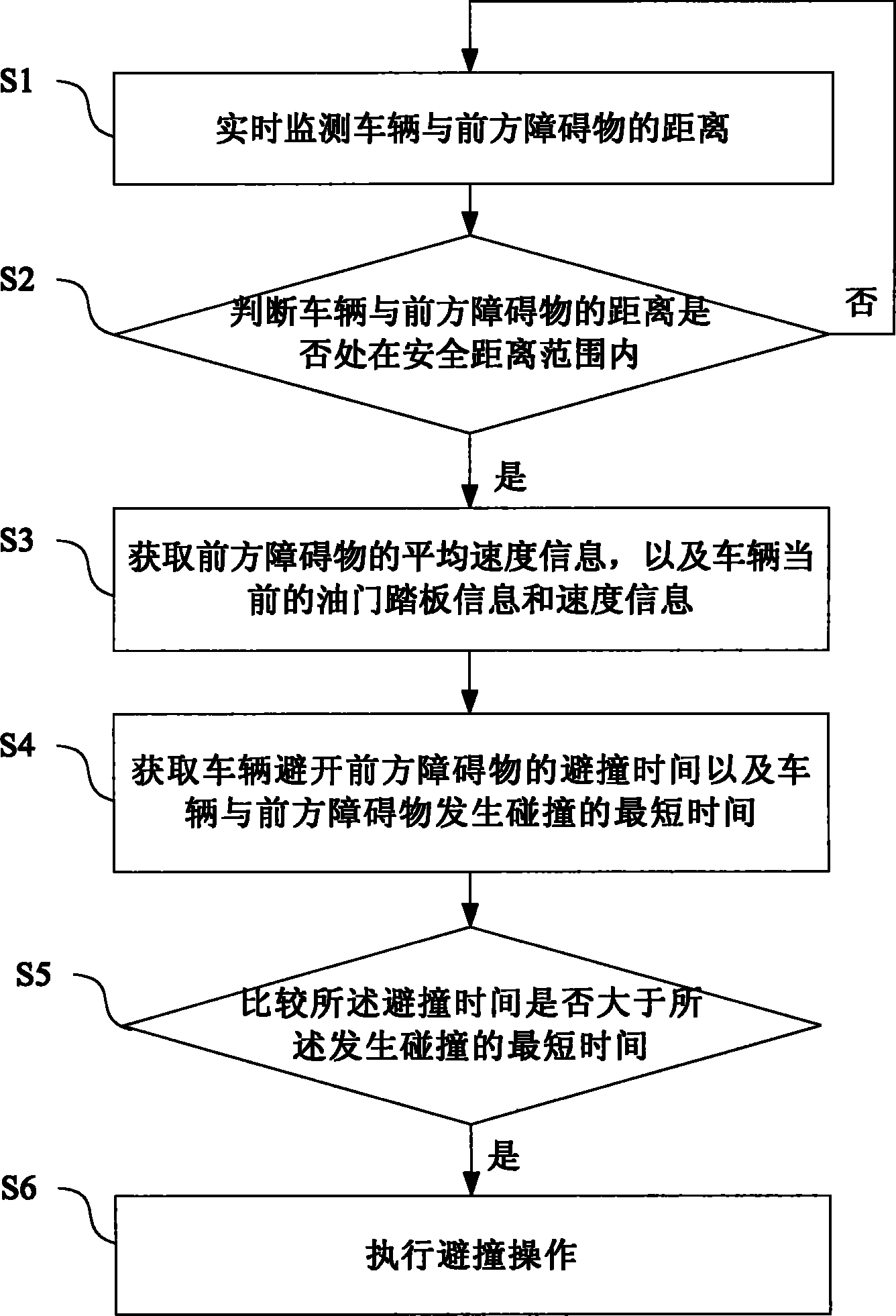

Vehicle running control method and control device

The invention provides a vehicle running control method and a control device. The control method comprises the following steps: carrying out real-time monitoring on the distance from a vehicle to a front barrier; judging whether the distance from the vehicle to the front barrier is within the safety distance range or not, and if yes, executing a speed control speed; if not, continuing to monitoring the distance from the vehicle to the front barrier; the speed control step comprises the following steps: acquiring the average speed information of the front barrier and the current accelerator pedal information and the speed information of the vehicle; acquiring the collision avoidance time for the vehicle to avoid the front barrier and the minimum time that the vehicle collides with the front barrier; comparing whether the collision avoidance time is greater than the minimum time of generating collision or not; and if yes, executing a collision avoidance operation. By adopting the control method and the control device, the vehicle can be prevented from colliding with the front barrier, and thereby, the vehicle running safety is improved.

Owner:CHERY AUTOMOBILE CO LTD

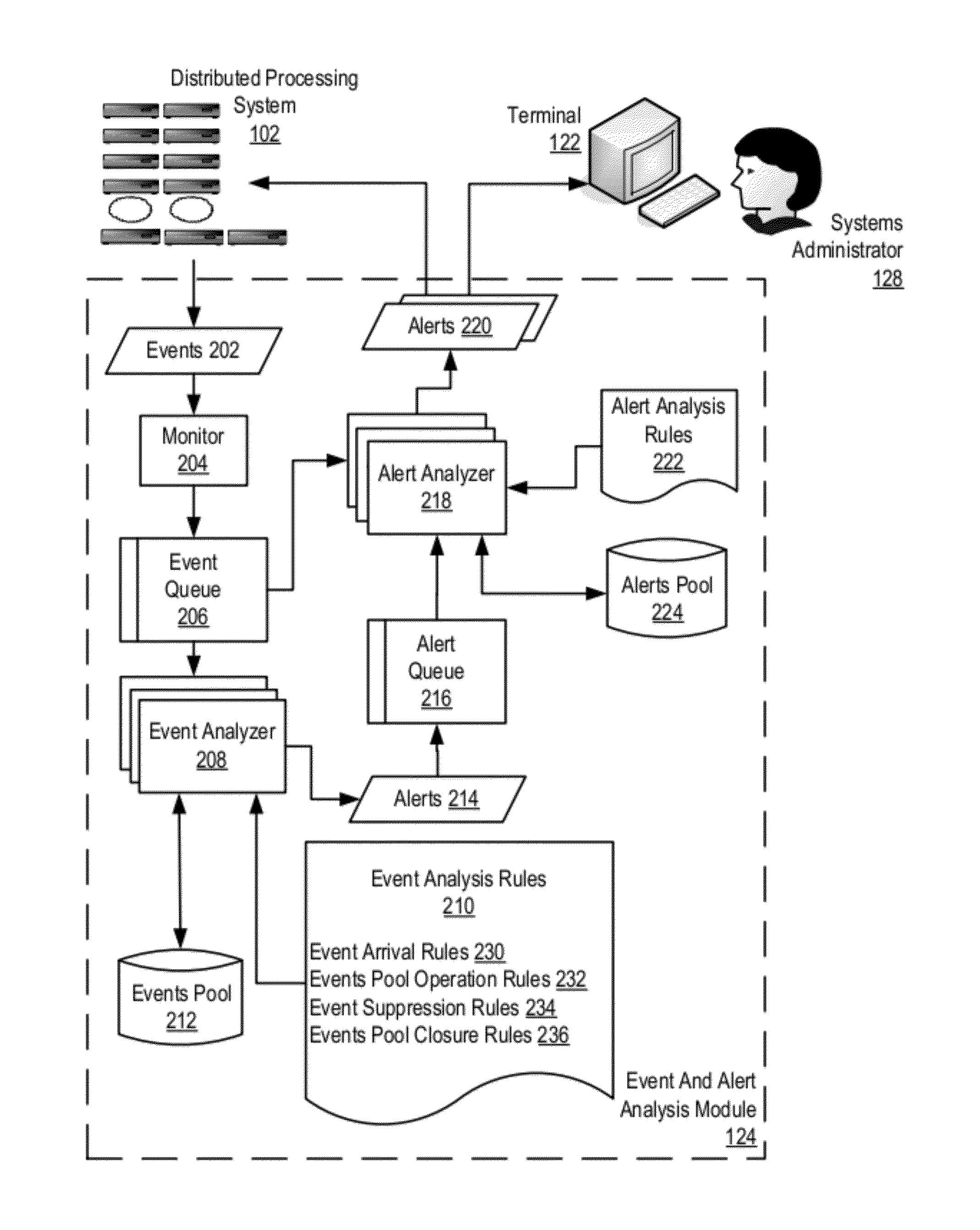

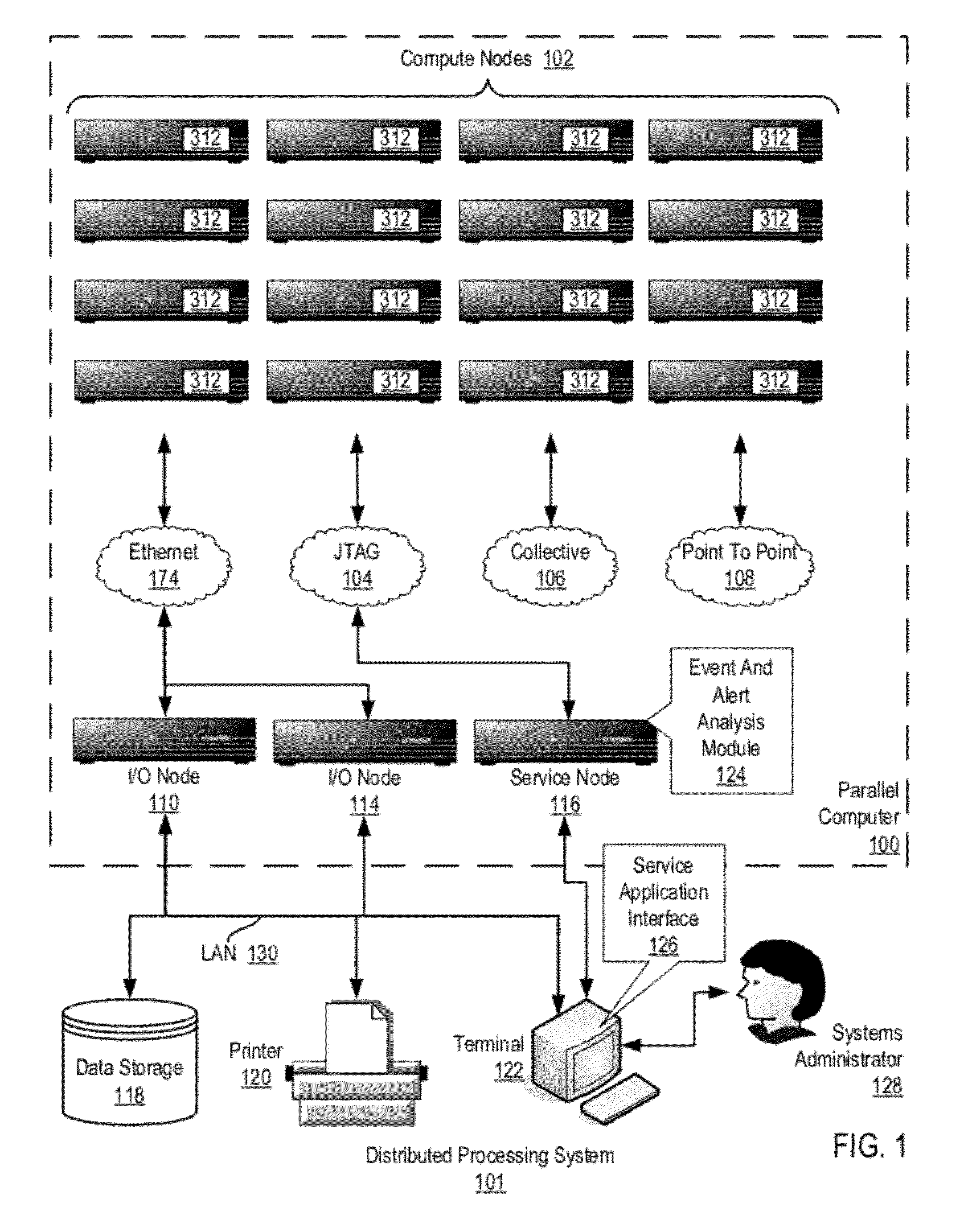

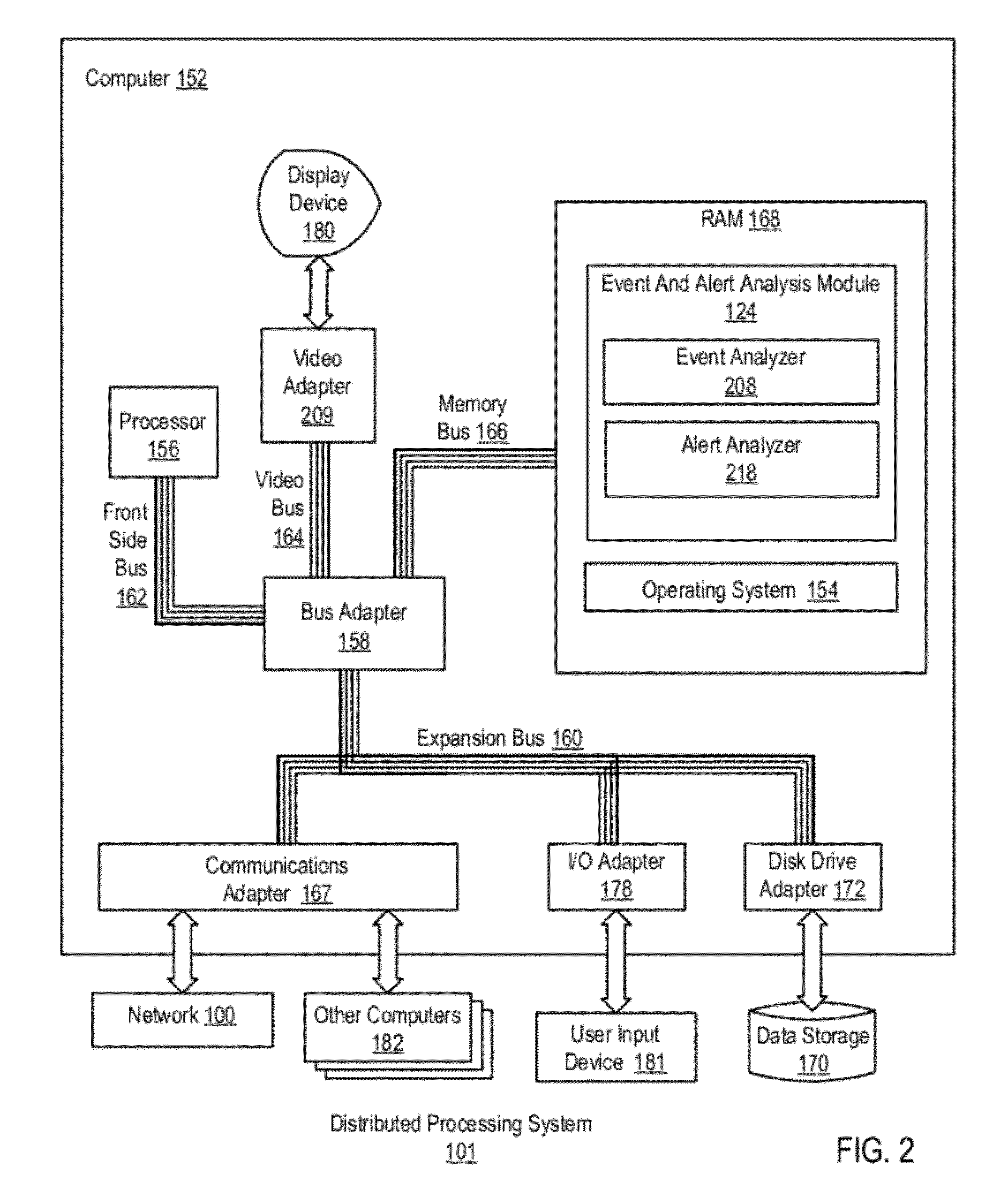

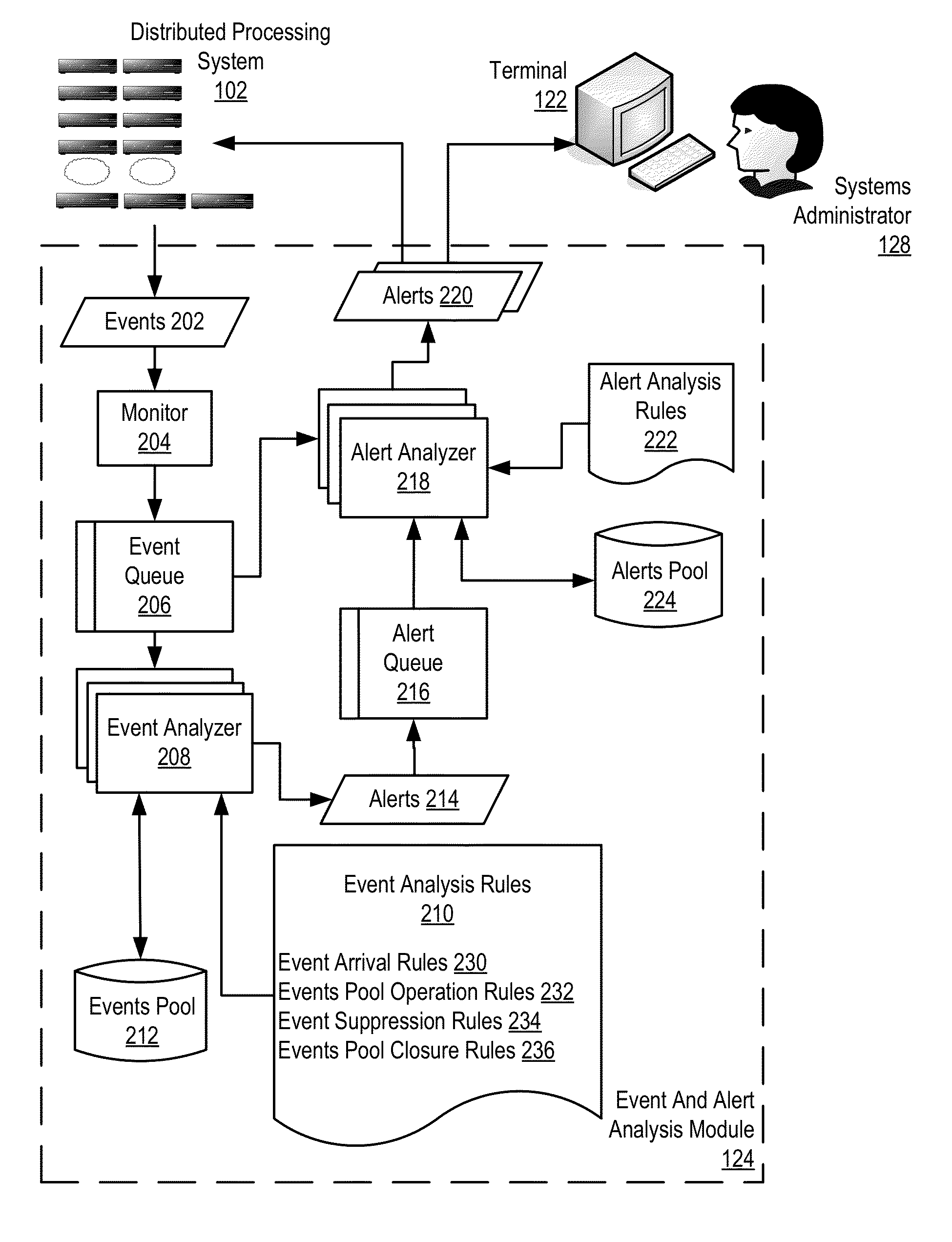

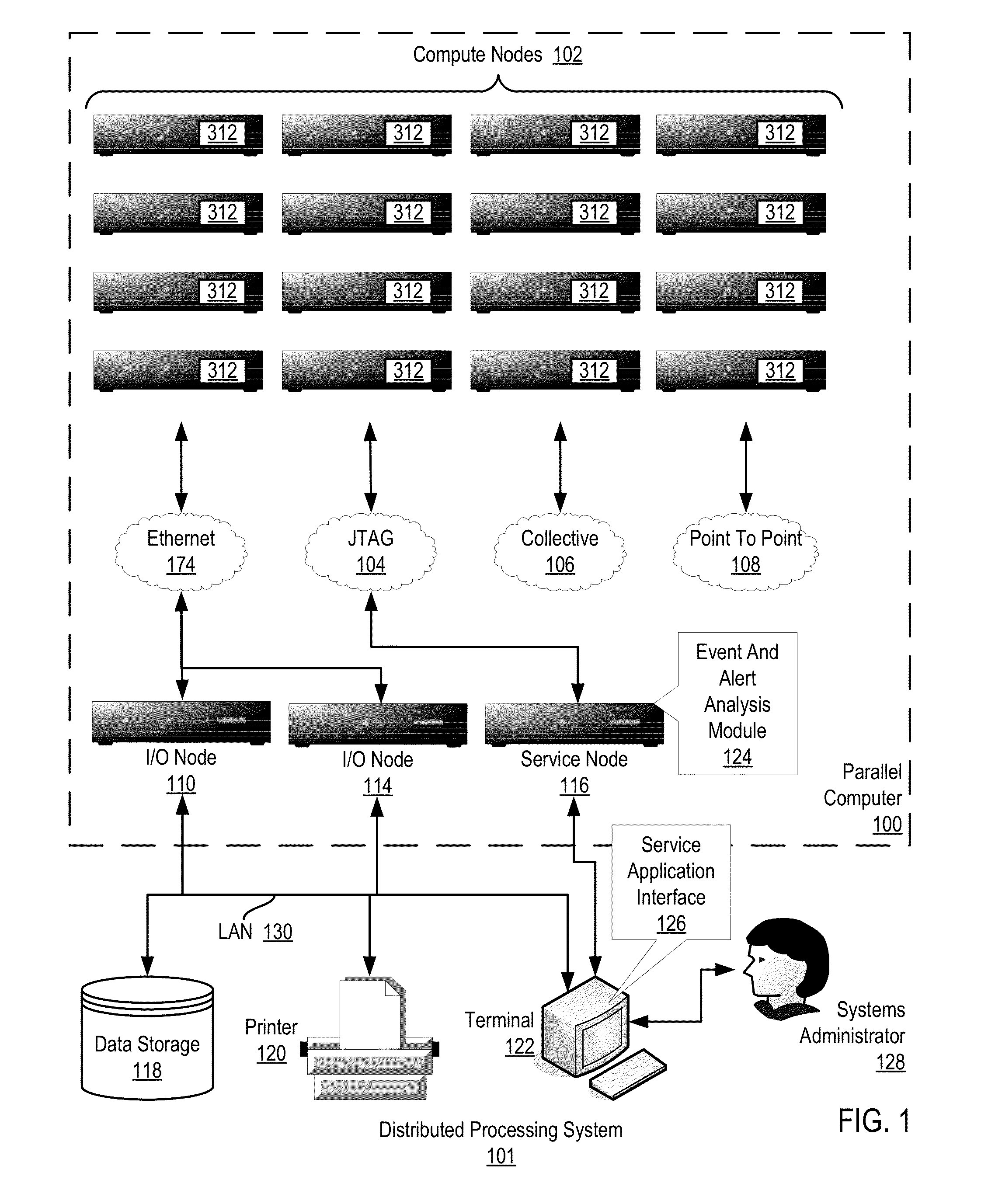

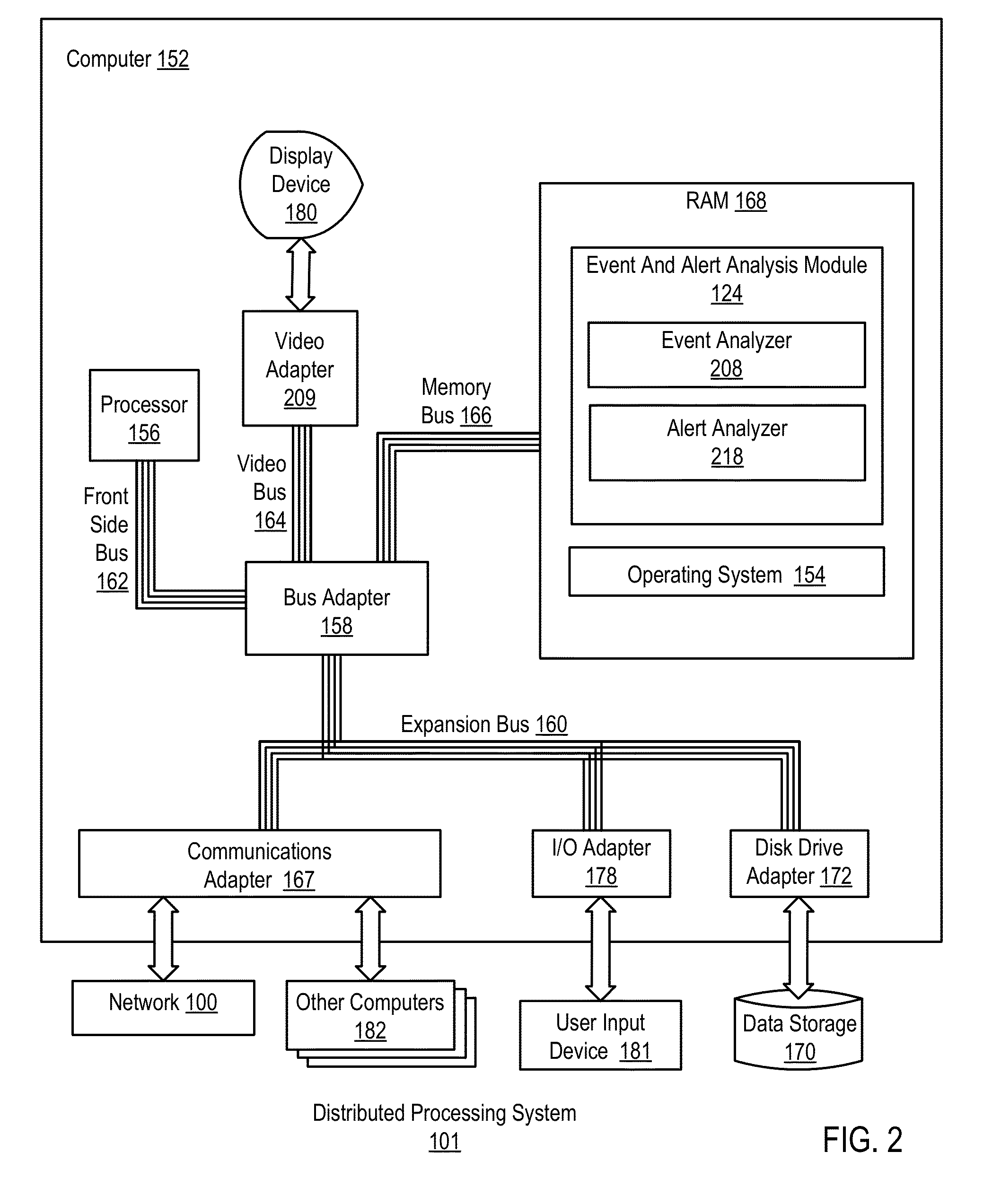

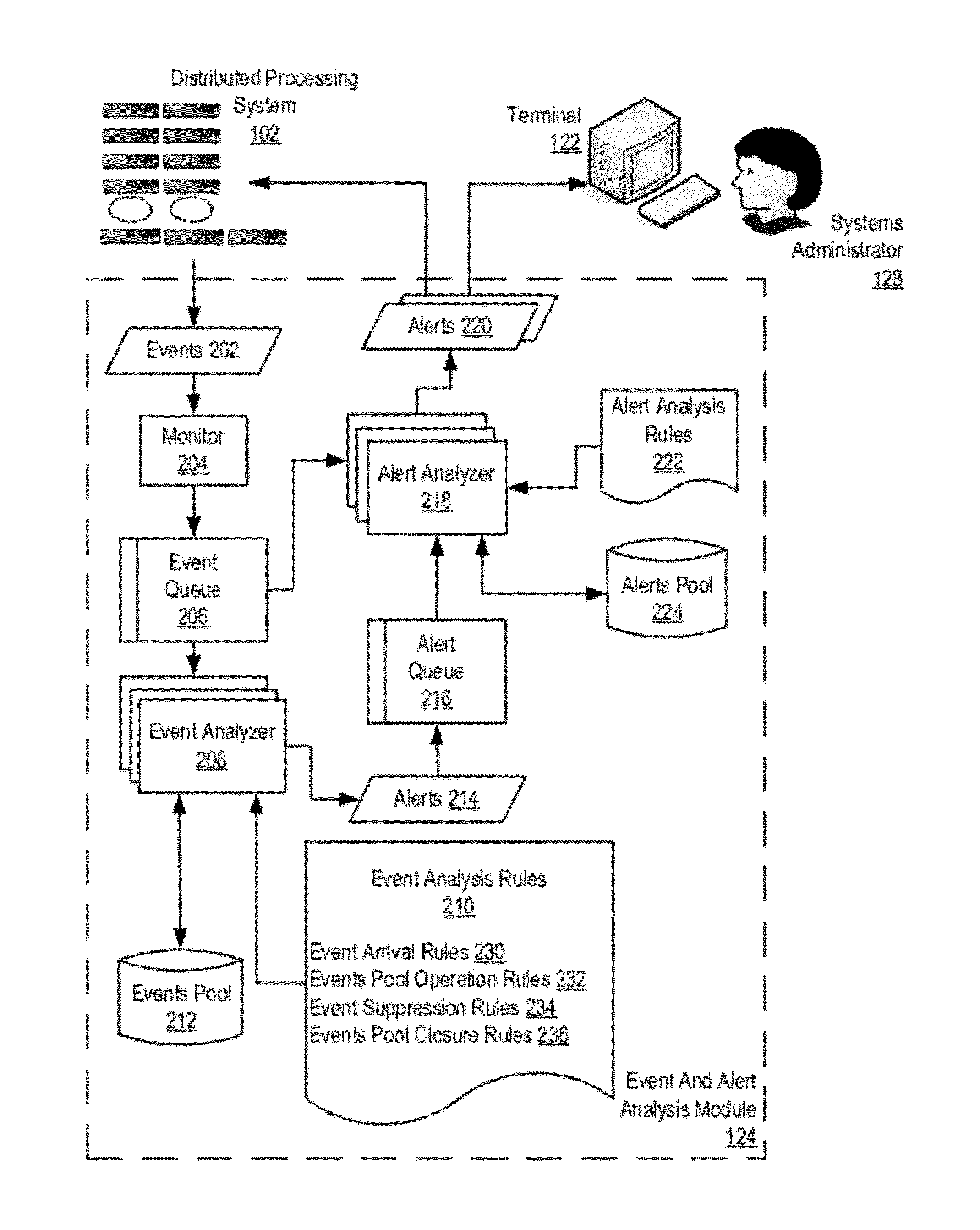

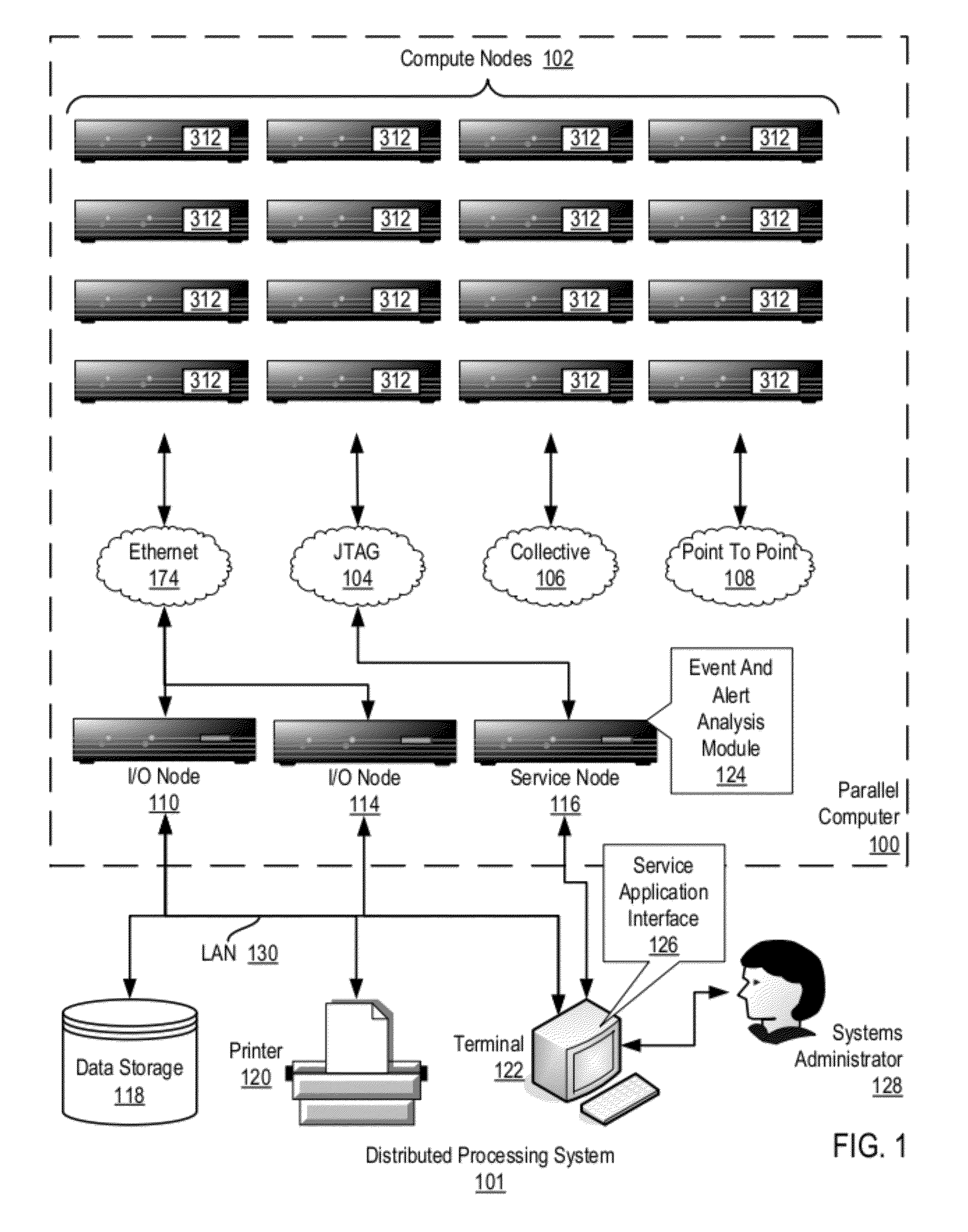

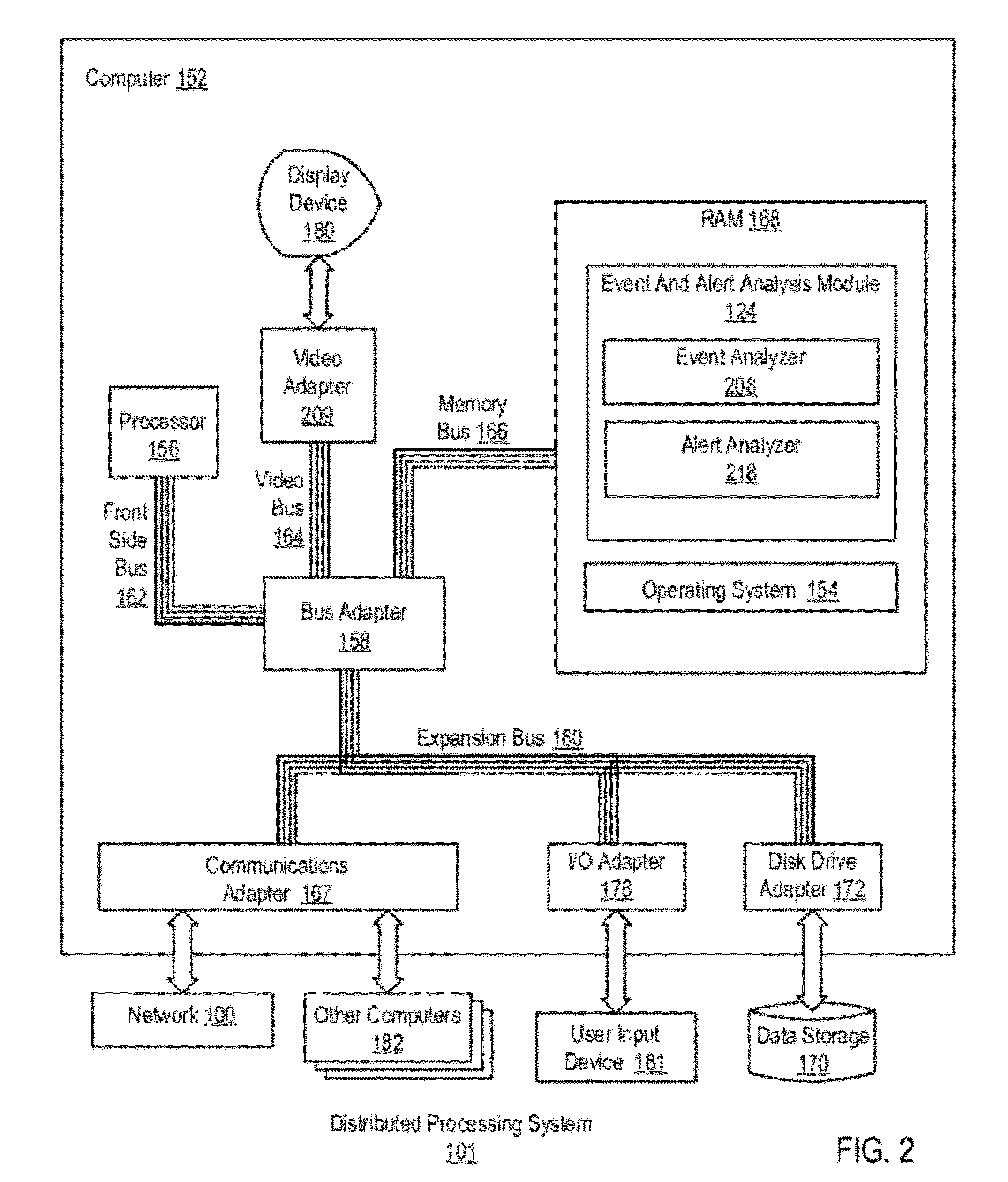

Administering Incident Pools For Event And Alert Analysis

Administering incident pools including creating a pool of incidents, the pool having a predetermined initial period of time; assigning each received incident to the pool; assigning, by the incident analyzer, to each incident a predetermined minimum time for inclusion in a pool; extending for one or more of the incidents the predetermined initial period of time of the pool by a particular period of time assigned to the incident; determining whether conditions have been met to close the pool; and if conditions have been met to close the pool determining for each incident in the pool whether the incident has been in the pool for its predetermined minimum time for inclusion in a pool; and if the incident has not been in the pool for its predetermined minimum time, evicting the incident from the closed pool and including the incident in a next pool.

Owner:IBM CORP

Administering Incident Pools For Event And Alert Analysis

Administering incident pools including assigning an incident received from one or more components of the distributed processing system to a pool of incidents; assigning to each incident a particular combined minimum time for inclusion of the incident in the pool; in response to the pool closing, determining for each incident in the pool whether the incident has met its combined minimum time for inclusion in the pool; if the incident has been in the pool for its combined minimum time, including the incident in the closed pool; if the incident has not been in the pool for its combined minimum time, moving the incident from the closed pool to a next pool; applying incident suppression rules using the incidents assigned to the next pool; and applying incident creation rules to the incidents that were assigned to the next pool, while omitting any duplicate incidents caused by the assignment.

Owner:IBM CORP

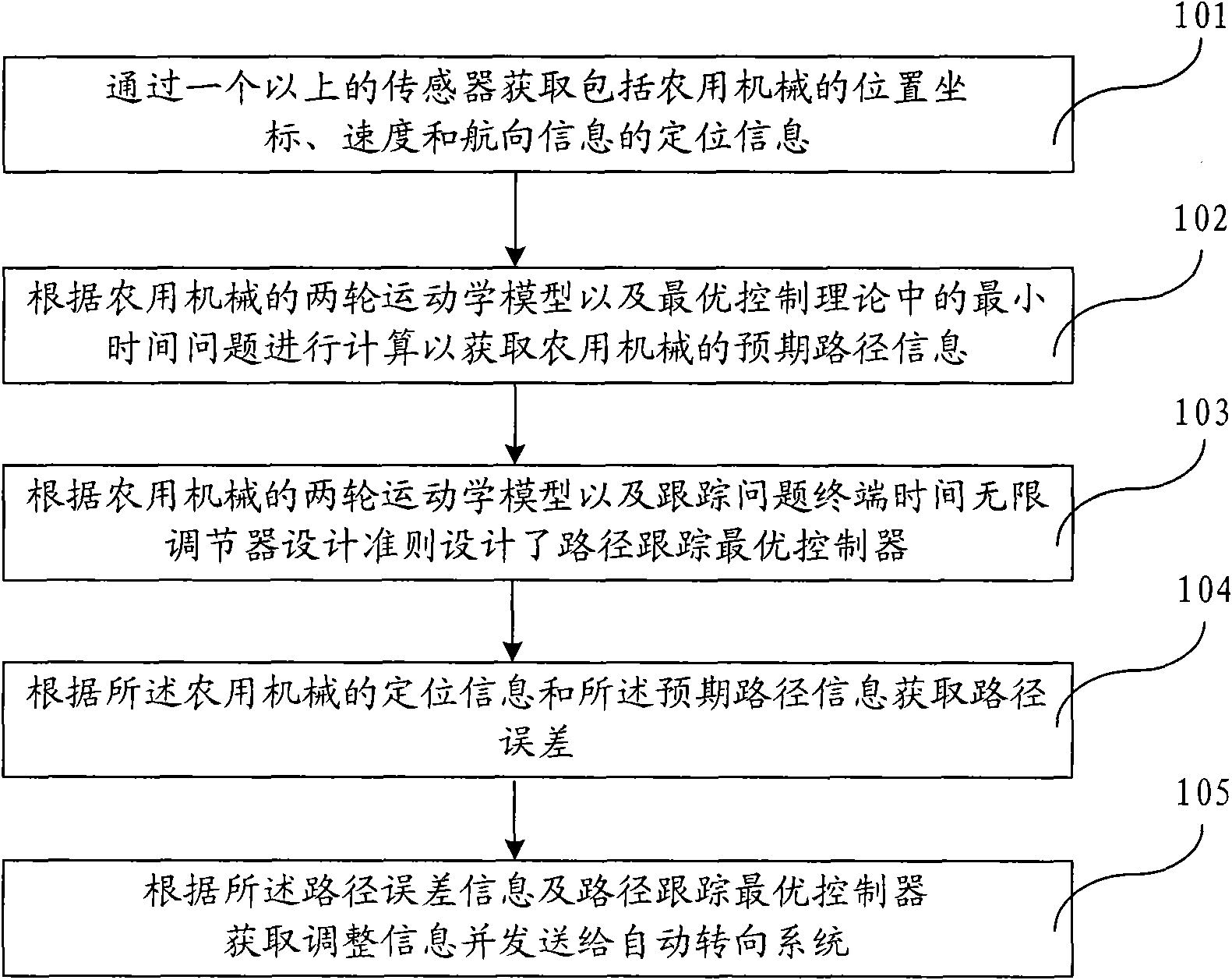

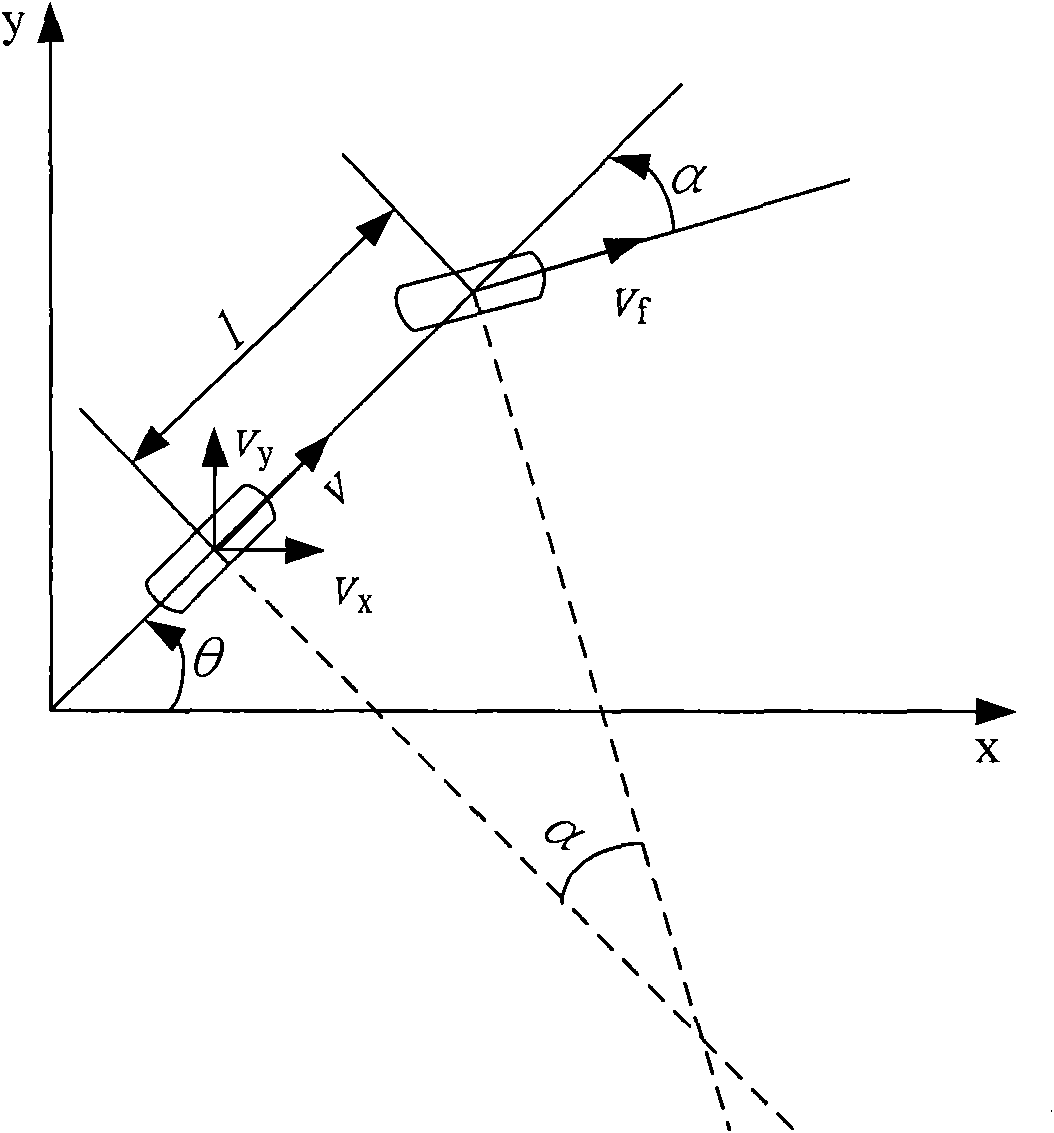

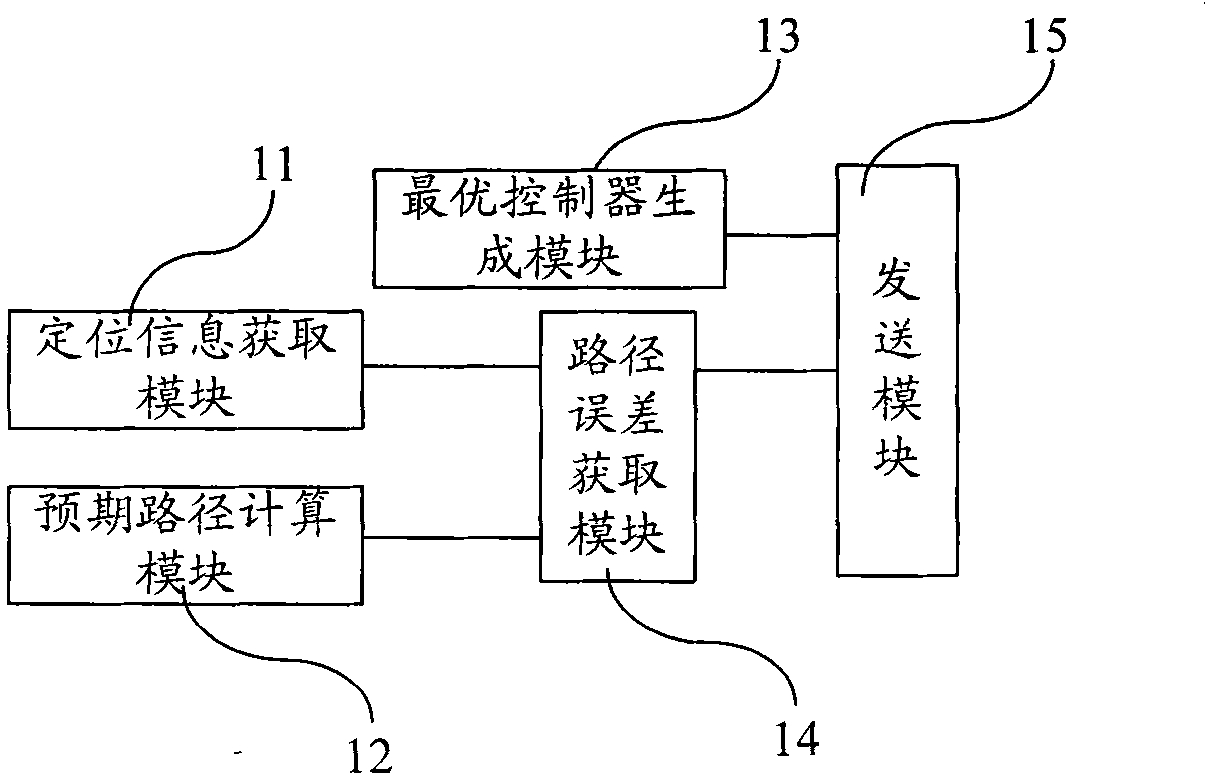

Navigation method and navigation device of agricultural machinery as well as agricultural machinery

InactiveCN101866181ARealize precise navigationInstruments for road network navigationPosition/course control in two dimensionsAutomatic steeringMinimum time

The invention provides a navigation method and a navigation device of agricultural machinery as well as agricultural machinery, wherein the navigation method of agricultural machinery comprises the following steps: acquiring positioning information comprising position coordinates, speed and course information of the agricultural machinery through more than one sensor; according to the two-wheel kinematics model of the agricultural machinery and the minimum time problem in the optimal control theory, acquiring the expected path information of the agricultural machinery by computing; designing a optimal controller of a path tracking according to the two-wheel kinematics model of the agricultural machinery and the design criteria on a terminal time unlimited regulator of a tracking problem; acquiring a path error according to the positioning information of the agricultural machinery and the expected path information; and acquiring path adjusting information according to the path error information and the path tracking optimal controller, and sending the path adjusting information to an automatic steering system. The embodiment of the invention also provides a navigation device of the agricultural machinery and the agricultural machinery provided with the navigation device. The method, the device and the equipment can improve the accuracy of navigation.

Owner:CHINA AGRI UNIV

Administering incident pools for event and alert analysis

Administering incident pools including creating a pool of incidents, the pool having a predetermined initial period of time; assigning each received incident to the pool; assigning, by the incident analyzer, to each incident a predetermined minimum time for inclusion in a pool; extending for one or more of the incidents the predetermined initial period of time of the pool by a particular period of time assigned to the incident; determining whether conditions have been met to close the pool; and if conditions have been met to close the pool determining for each incident in the pool whether the incident has been in the pool for its predetermined minimum time for inclusion in a pool; and if the incident has not been in the pool for its predetermined minimum time, evicting the incident from the closed pool and including the incident in a next pool.

Owner:INT BUSINESS MASCH CORP

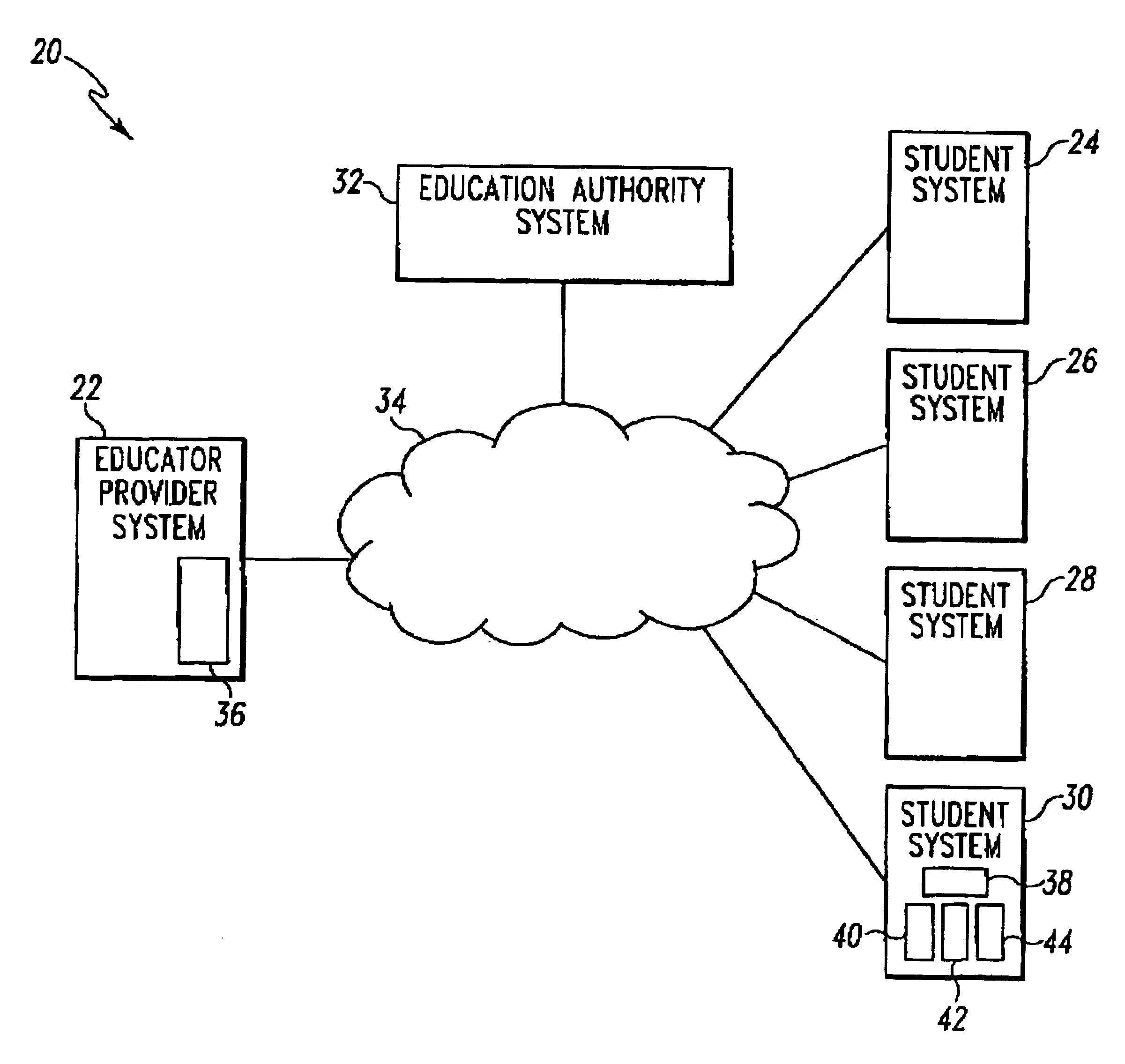

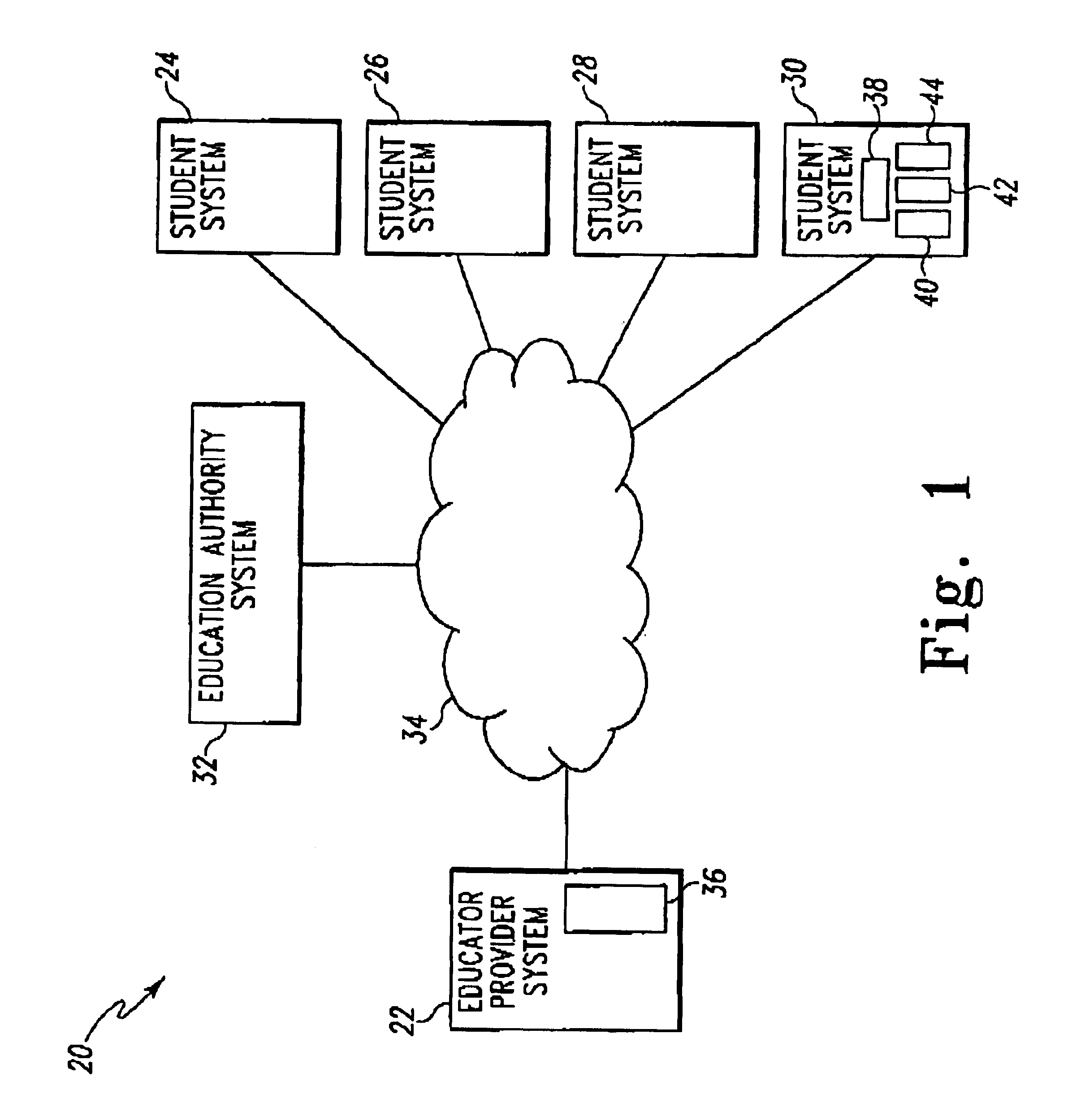

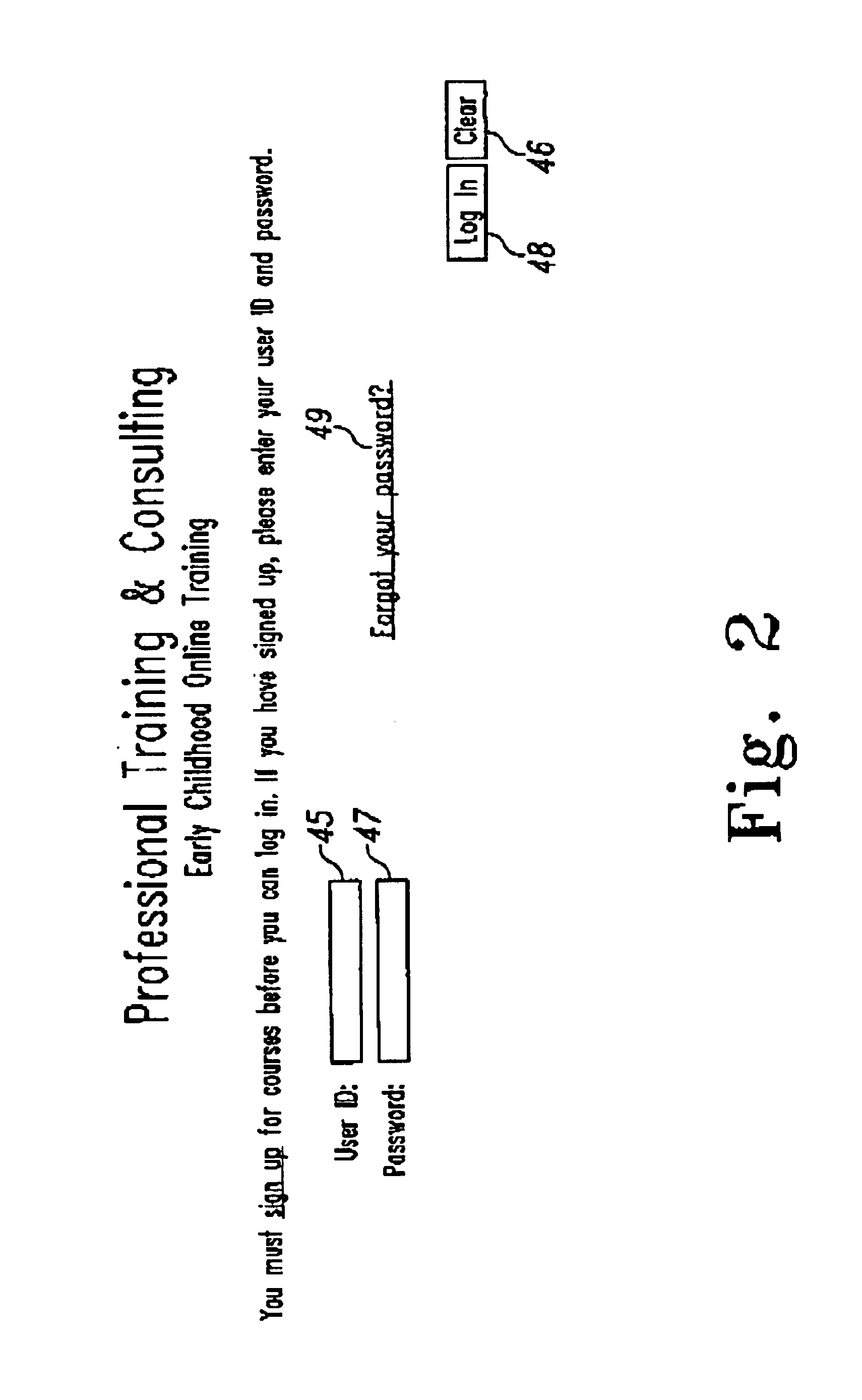

Online education system and method

A method and system for online education that includes an educator provider system and at least one student system connected via a network means so that at least one lesson can be transmitted from the provider system to the student system. One embodiment of the present invention uses an interactive lesson with at least one audio file that controls the pace of the presentation of the lesson. The present invention can further comprise a mechanism for generating a lesson completion record after a student has completed the lesson. The lesson completion record is immediately transmitted upon completion of the lesson to a student and / or an education authority in order to certify that the student has completed the lesson and has spent the requisite minimum time period on that lesson.

Owner:CHILDCARE EDUCATION INST

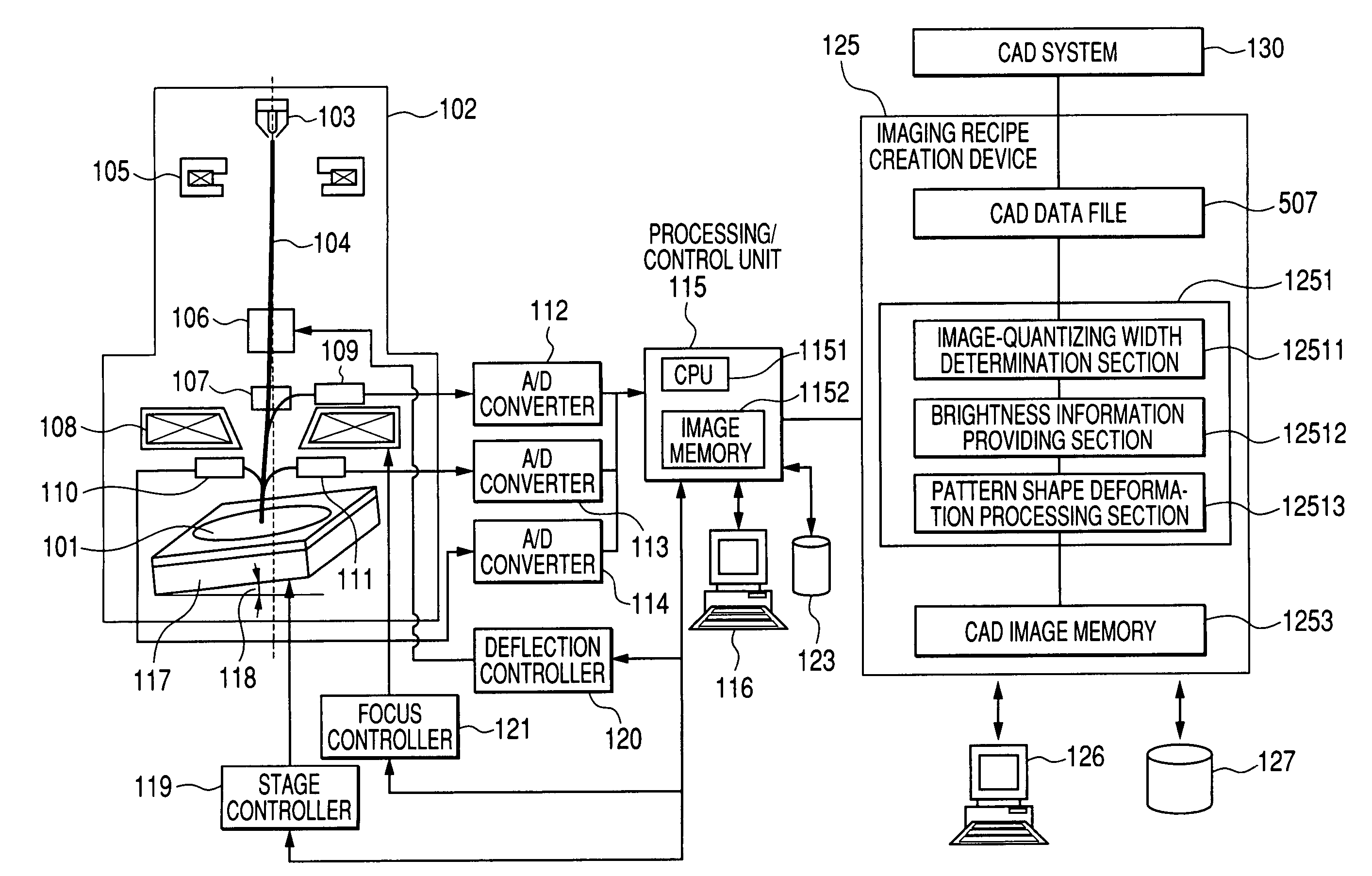

Method and apparatus for creating imaging recipe

ActiveUS7559047B2Possible to generateEasy to implementPhotomechanical apparatusCharacter and pattern recognitionMinimum timeScanning electron microscope

In an imaging recipe creating apparatus that uses a scanning electron microscope to create an imaging recipe for SEM observation of a semiconductor pattern, in order that the imaging recipe for measuring the wiring width and other various dimension values of the pattern from an observation image and thus evaluating the shape of the pattern is automatically generated within a minimum time by the analysis using the CAD image obtained by conversion from CAD data, an CAD image creation unit that creates the CAD image by converting the CAD data into an image format includes an image-quantizing width determining section, a brightness information providing section, and a pattern shape deformation processing section; the imaging recipe being created using the CAD image created by the CAD image creation unit.

Owner:HITACHI HIGH-TECH CORP

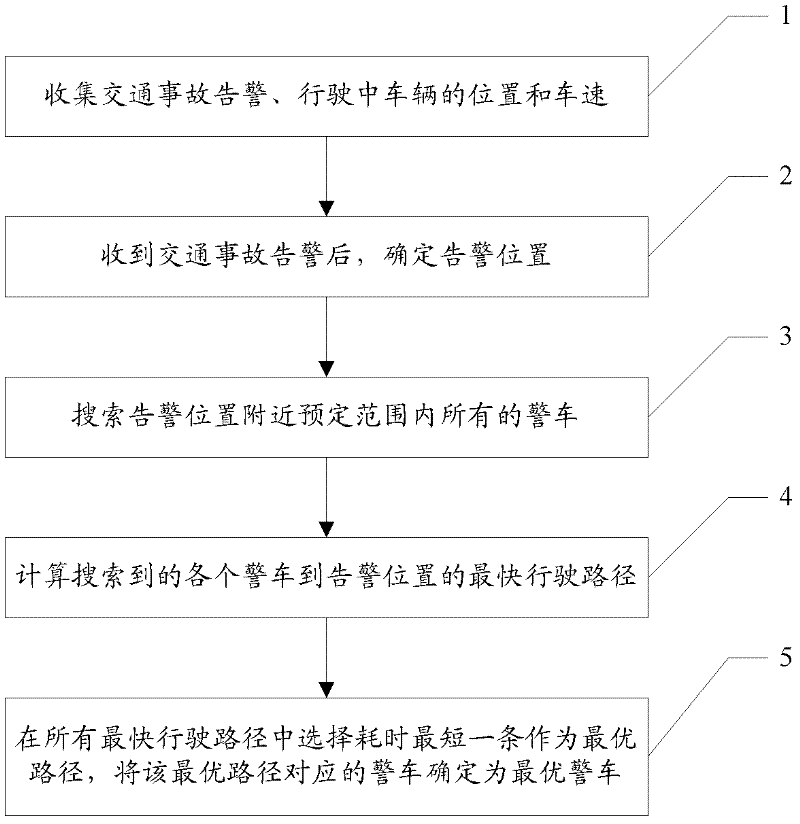

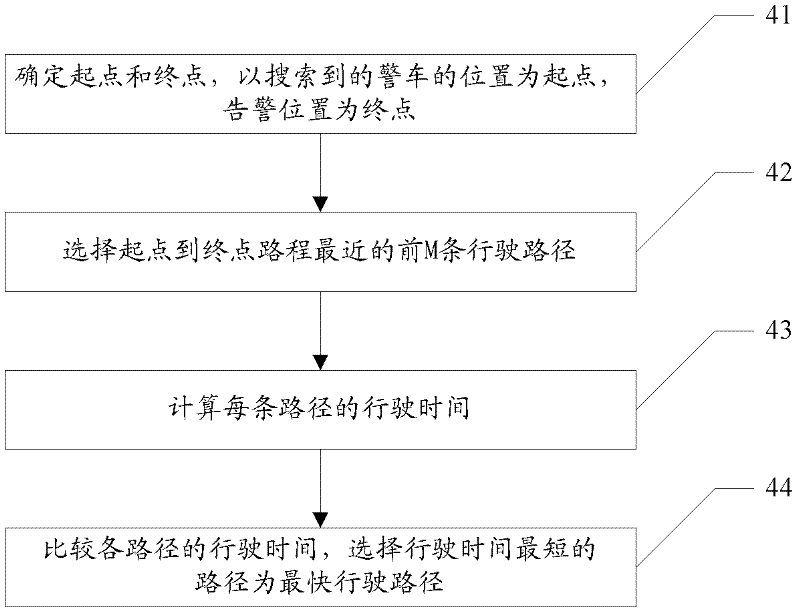

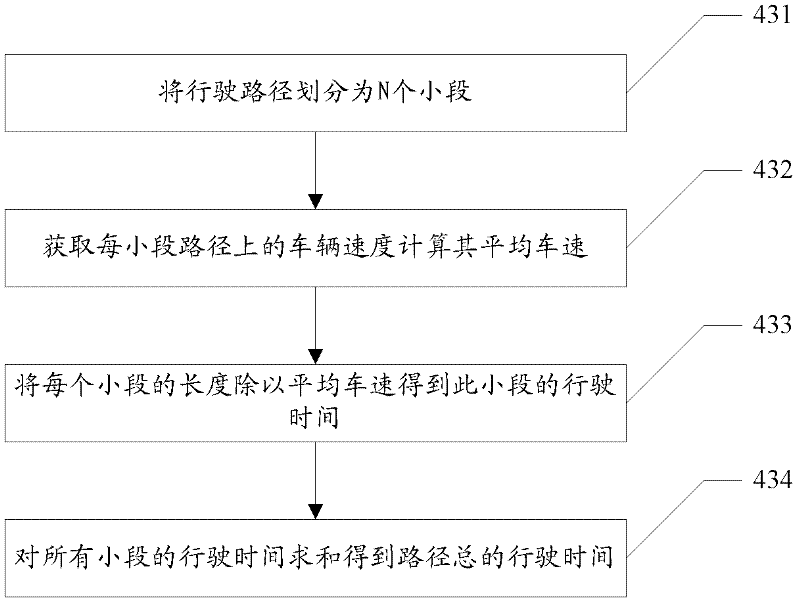

Method and device for obtaining optimal path to hurry to scene of traffic accident

InactiveCN102353381AAvoid spreadingReduce casualtiesInstruments for road network navigationFast pathMinimum time

The invention discloses a method and device for obtaining an optimal path to hurry to a scene of a traffic accident. The method comprises the following steps of: respectively calculating fastest paths for police cars around an accident scene to arrive at the accident scene and selecting one path which consumes the shortest time from all the fastest paths as the optimal path; and announcing the police car corresponding to the optimal path to hurry to the accident scene by adopting the optimal path, thus arriving at the accident scene in the shortest time. Therefore, by utilizing the method, the accident spread is avoided, the injuries and deaths can be reduced; and the time for processing the traffic accident is effectively saved by the method. In the method, when the fastest driving paths of the police cars are calculated, each driving path is segmented at first and then the driving time of the whole driving path is calculated through calculating an average car speed of each segment of the path, so that the fastest driving path is found out. As the path is segmented, the calculated average speed is more precise and more accurate. The invention also discloses a device corresponding to the method; and the method and the device are combined so that the police car can arrive at the accident scene in the shortest time.

Owner:GUANGDONG VTRON TECH CO LTD