Compression generation method for testing data of digital integrated circuit

A technology of integrated circuits and test data, applied in the direction of measuring electricity, measuring devices, electrical components, etc., can solve the problems of a large number of units, a sharp increase in circuit defects and soft errors, and a reduction in the amount of test data.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

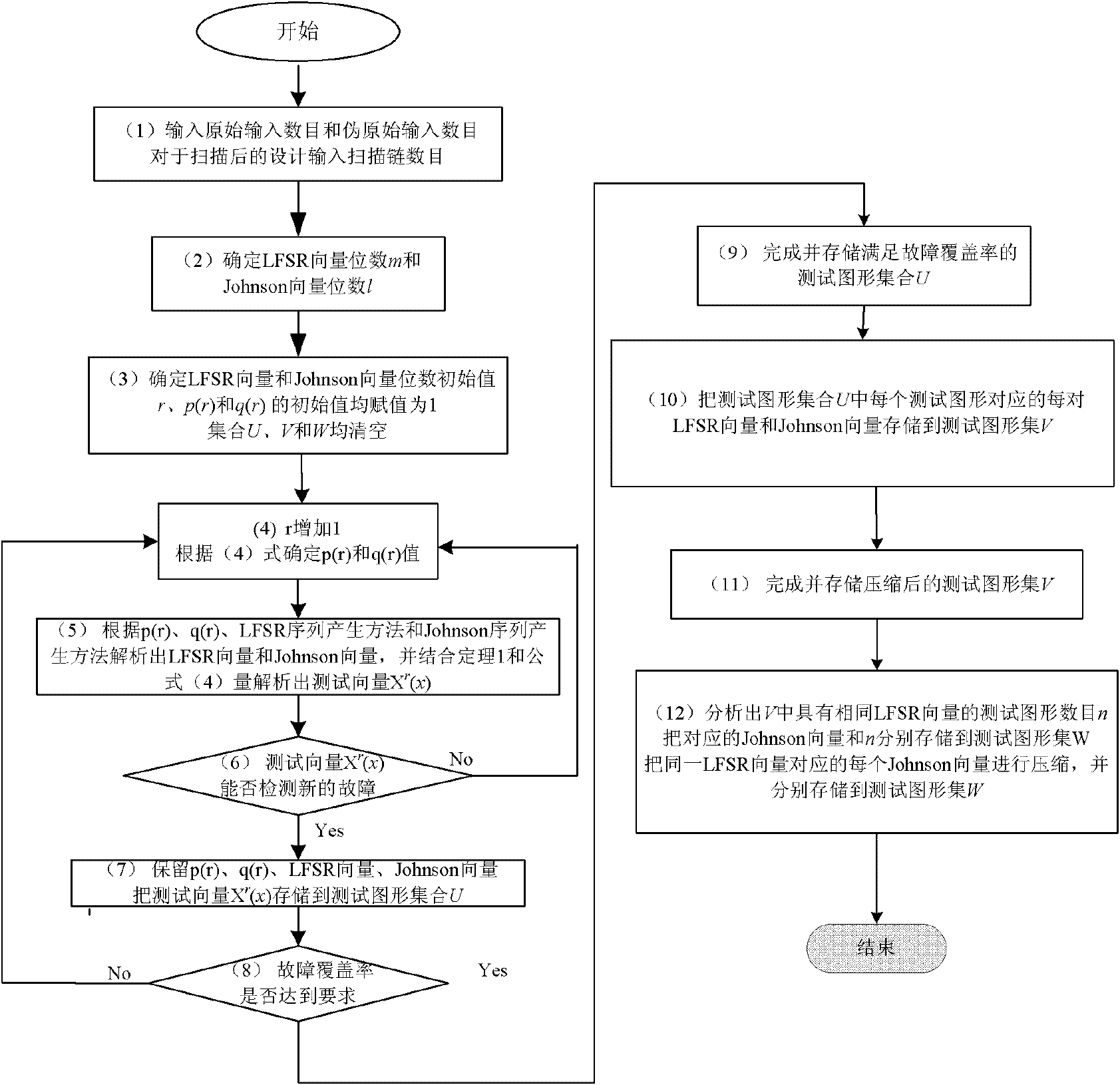

[0062] The method for compressing and generating test data proposed by the invention can be used in parallel testing and scanning testing of sequential circuits, and can be used in combination circuit testing.

[0063] 1. Analyze a class of single-input change test sequences with a linear relationship.

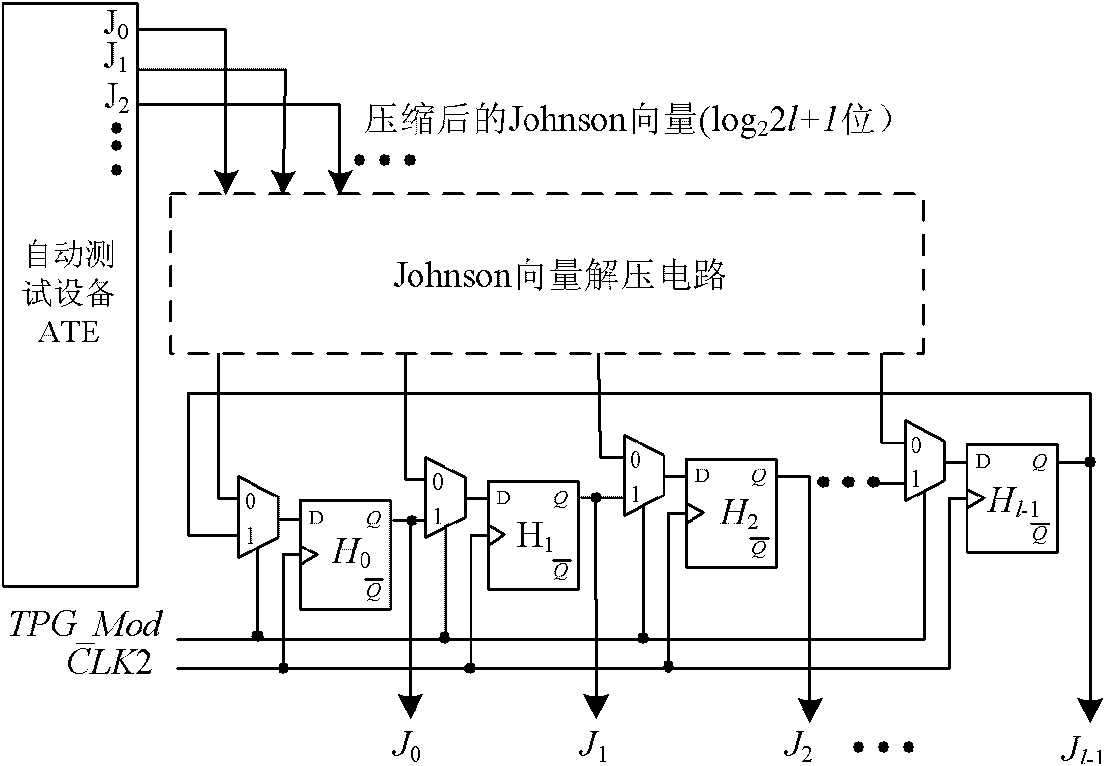

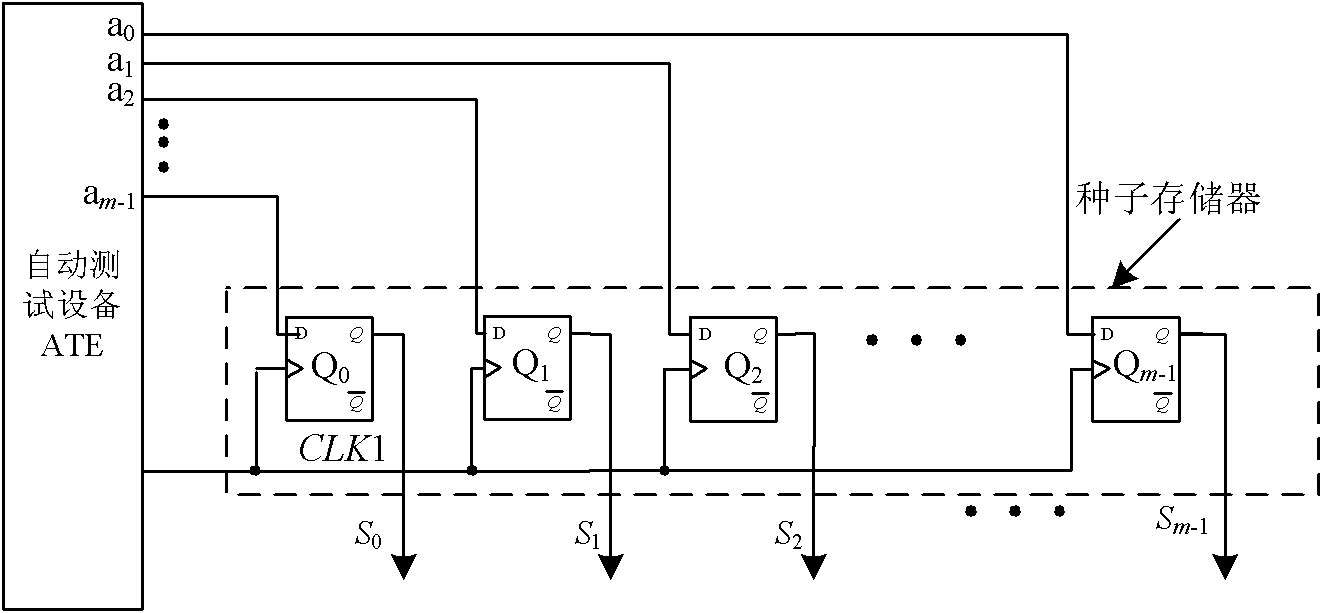

[0064] Divide the total original input of the circuit under test, including original input and pseudo original input, into M sections, and the number of original inputs in each section is L 1 , L 2 ,...,L M . The l-bit Johnson counter generates an l-bit Johnson sequence, and the vector at the rth moment is The polynomial of the vector formed after its cyclic shift is:

[0065] J r ( x , 1 ) = J 0 r + J 1 r x + J 2 r ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More