System for testing system internuclear wiring fault on integrated circuit chip and method thereof

A system-on-chip, integrated circuit technology, applied in the direction of measuring electricity, measuring devices, measuring electrical variables, etc., can solve the problem that the test system is not involved, and achieve the effect of shortening the test time, making full use of shortening, and shortening the test time.

Inactive Publication Date: 2010-12-22

SHANGHAI UNIV

View PDF5 Cites 23 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

The current research on SOC connection fault testing mainly focuses on the optimization algorithm of vector compression and test structure, but the hardware structure of the test system and the test search mechanism are not involved, and there is no research on the inter-core connection fault and the core fault test. consider together

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Embodiment 1

Embodiment 2

Embodiment 3

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More PUM

Login to View More

Login to View More Abstract

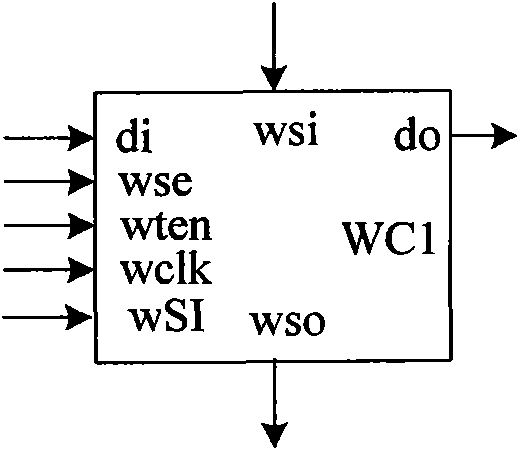

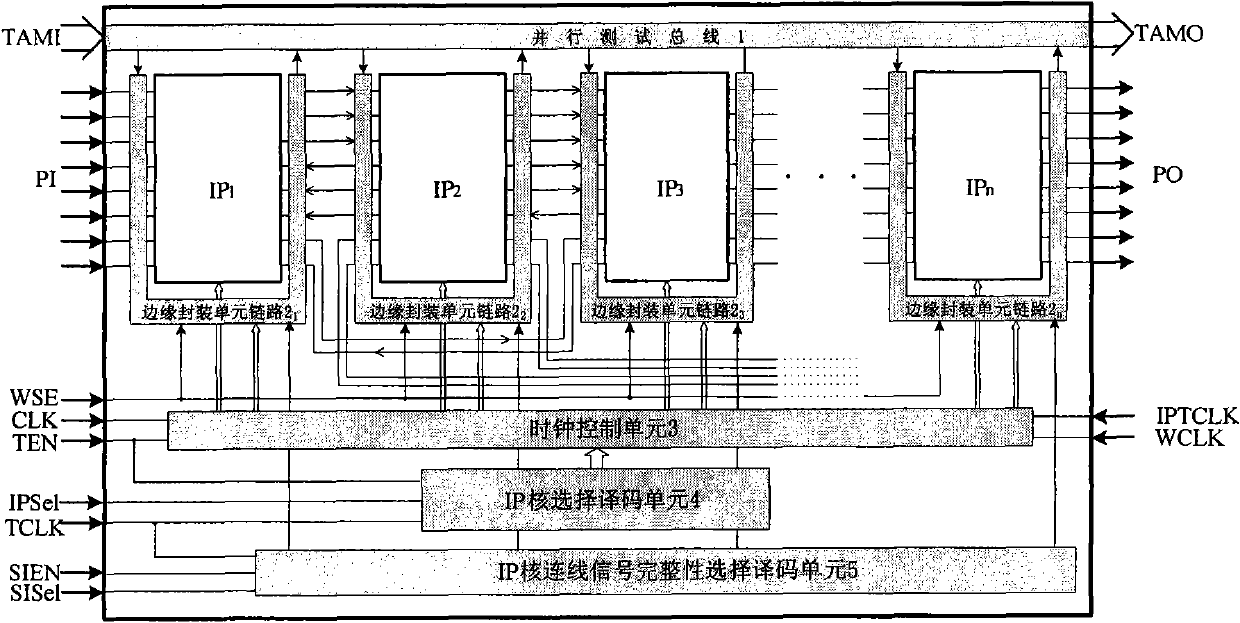

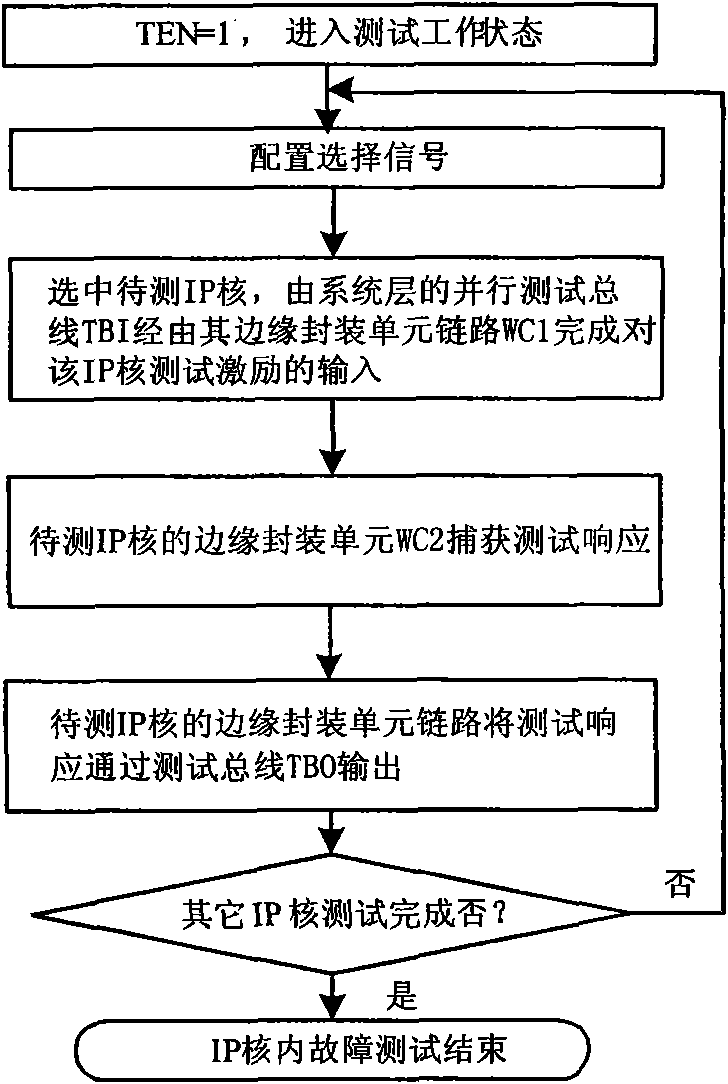

The invention relates to a system for testing a system internuclear wiring fault on an integrated circuit chip and a method thereof. The system comprises a circuit structure which is added for perfecting the IP internuclear wiring fault test and the IP intranuclear fault test in a system on the integrated circuit chip and a test inquiring mechanism which runs on the basis of the circuit structure. The invention can test the IP internuclear wiring of the system on the integrated circuit chip. The fault types of the test comprises the solid-zero fault, the solid-solid fault, the open circuit fault, the short circuit fault, the delaying fault and the noise fault. By adding a hardware structure, the invention decomposes a scanning chain of edge packing units, thereby making the best of a test buss and shortening the test time; with the output type edge packing unit, the invention automatically generates a test vector; with the input type edge packing unit, the invention further shortens the test time. The structure is compatible with the intranuclear test structure, thereby realizing the higher flexibility, making the best of the test resource, and further improving the fault coverage rate of the system of the whole integrated circuit chip. The invention is simple in circuit structure, convenient in test inquiring mechanism, and suitable for the various systems on the integrated circuit chips which are designed and built with the IP multiplexing technology.

Description

technical field The invention relates to an integrated circuit fault testing system and method, in particular to a testing system and method for inter-core connection faults applied to an integrated circuit system on chip (SOC System on a Chip). Background technique Now integrated circuit (IC) designers are developing towards better cost advantages and time-to-market, and seize market opportunities with the fastest speed and the best cost performance. The existence of these needs urgently makes multiple functions integrated into one chip. become possible, the system on a chip (SOC System on a chip) came into being. From an engineering point of view, integrating more functions into a single chip can indeed achieve cost savings, but from a testing point of view, a large number of SOC pins, multiple cores with different Features such as test vectors make the test of SOC much more complicated than that of a single chip. How to reduce the test difficulty and test cost of SOC ha...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More Patent Type & Authority Applications(China)

IPC IPC(8): G01R31/02

Inventor 李娇张金艺杨晓冬蔡万林施慧张冬黄徐辉翁寒一丁梦玲

Owner SHANGHAI UNIV