A delay locked loop and a delay locked method

A delay-locked loop and delay-locked technology, which is applied in the direction of electrical components and automatic power control, can solve problems such as poor accuracy and complex timing of delay-locked loops, and achieve loop stability, simplified debugging, and high reliability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

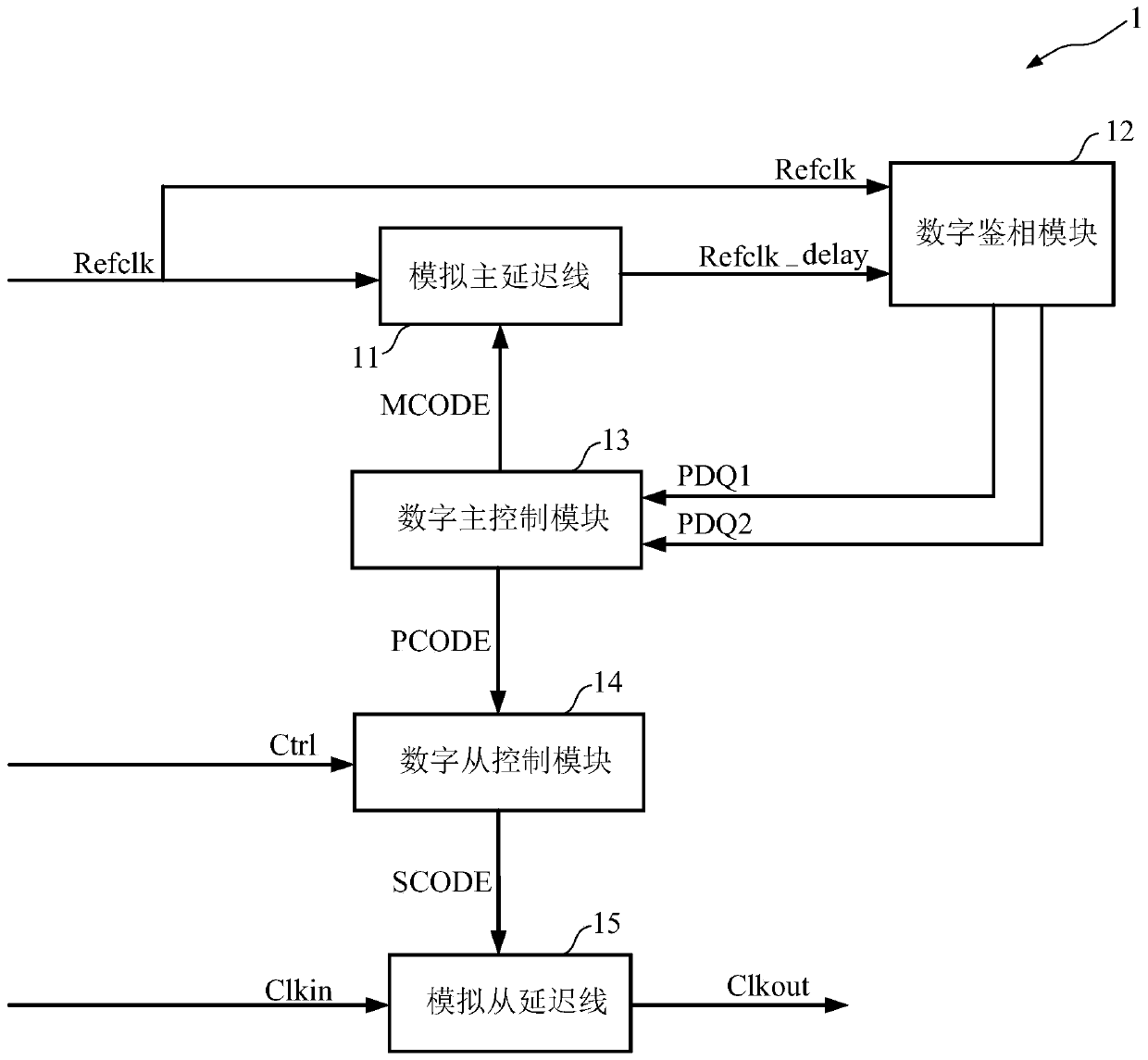

[0054] Such as figure 1 As shown, this embodiment provides a delay-locked loop 1, and the delay-locked loop 1 includes:

[0055] An analog master delay line 11 , a digital phase detection module 12 , a digital master control module 13 , a digital slave control module 14 and an analog slave delay line 15 .

[0056] Such as figure 1 As shown, the analog master delay line 11 is connected to the output end of the digital master control module 13, and receives a reference clock signal Refclk, and controls the reference clock based on the master delay control word MCODE output by the digital master control module 13 Signal Refclk delay.

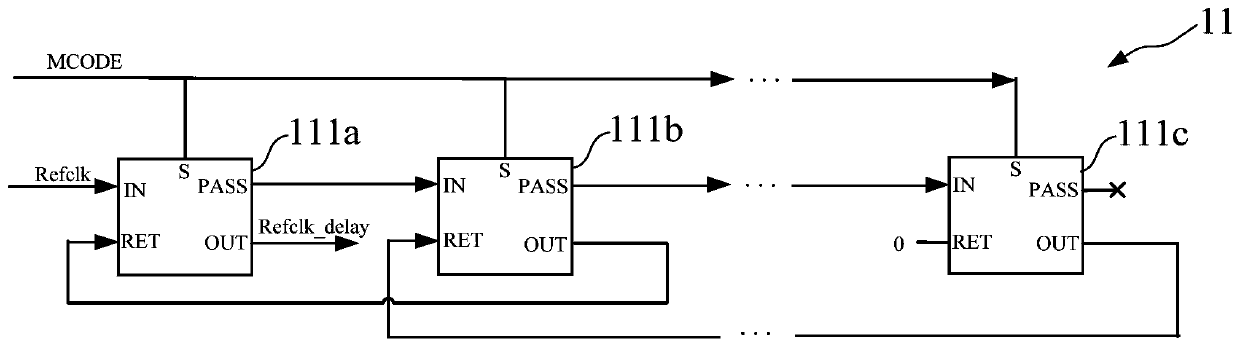

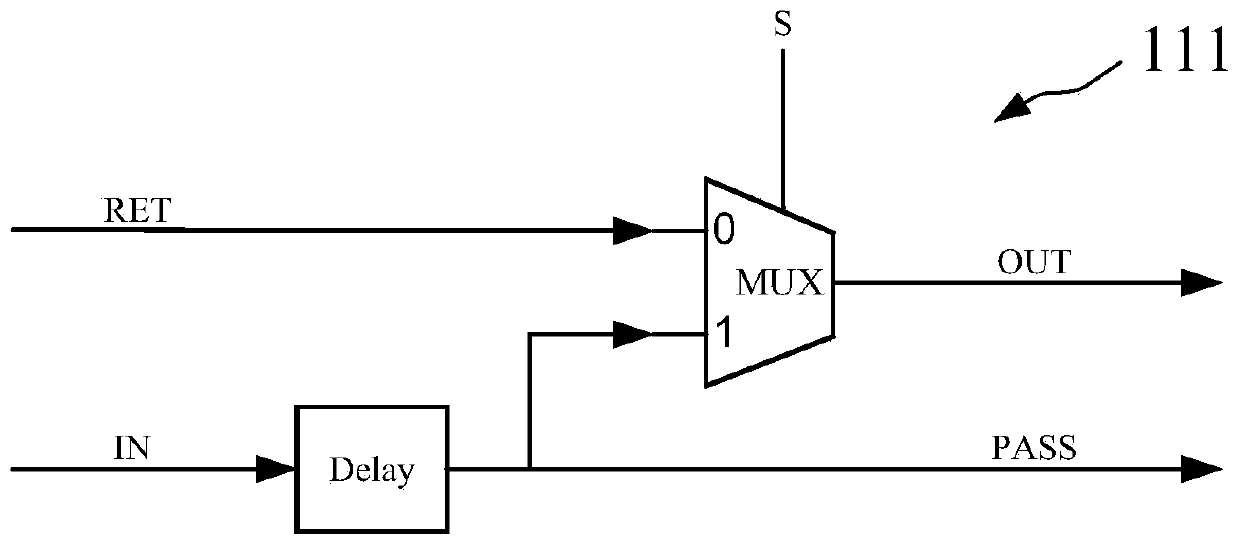

[0057] Specifically, the analog main delay line 11 includes a plurality of analog delay units 111, the first input terminal IN of each analog delay unit 111 is connected to the first output terminal PASS of the previous stage, and the second input terminal RET is connected to the second output terminal of the subsequent stage. The output termina...

Embodiment 2

[0074] This embodiment provides a delay locking method. In this embodiment, the delay locking method is implemented based on the delay locked loop 1 described in Embodiment 1. In practical applications, any structure that can realize the above method is applicable to the present invention The method is not limited to this embodiment. The delay locking method includes:

[0075] 1) Delay the reference clock signal, detect the phase difference of the reference clock signal before and after the delay, and generate a main delay control word based on the detected phase comparison result to adjust the delay time of the reference clock signal until the reference clock signal is delayed A cycle.

[0076] Specifically, such as figure 1 As shown, the reference clock signal Refclk is delayed based on the analog master delay line 11, and the master delay control word MCODE is a set value in an initial state.

[0077] Specifically, such as figure 1 As shown, the phase difference between...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More