Analog delay line receiver and implementation method thereof

A receiver and delay line technology, applied in the field of electronic warfare, can solve the problems of digital single-bit receiver two-tone dynamic and multi-tone dynamic difference, limited instantaneous dynamic range, missed detection, etc., to solve the problem of interpulse noise error detection. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

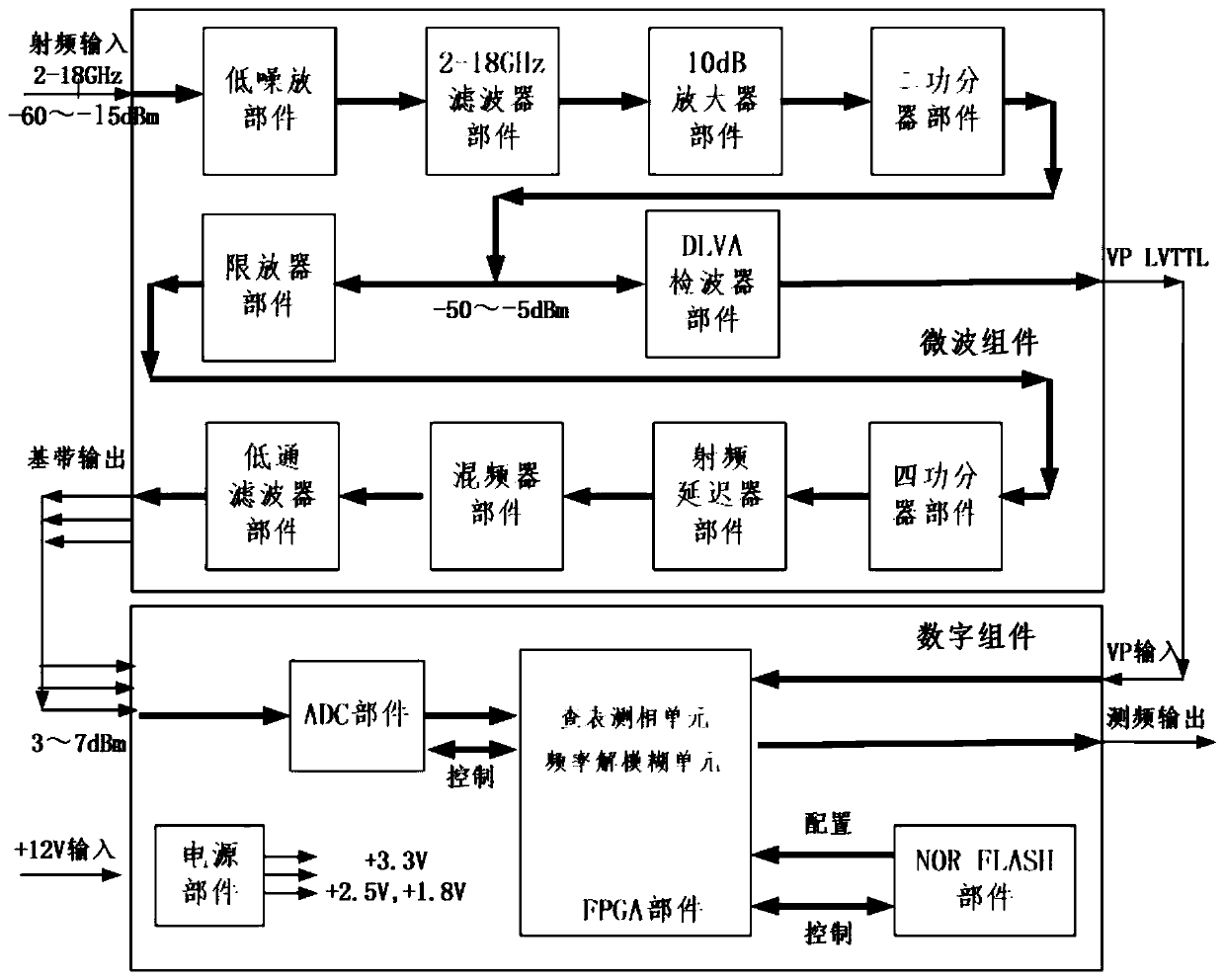

[0055] Such as figure 1 As shown, in this embodiment, an analog delay line receiver includes a low-noise amplifier component, a 2-18GHz filter component, a 10dB amplifier component, a two-power divider component, a DLVA detector component, and an amplifier limiter component, Four power splitter components, radio frequency delayer components, mixer components and low pass filter components;

[0056] The low noise amplifier component is connected to the 2-18GHz filter component;

[0057] The 2-18GHz filter part is connected to the 10dB amplifier part;

[0058] The 10dB amplifier part is connected to the two power divider parts;

[0059] The two power divider components, one of which is connected to the DLVA detector component, and the other is connected to the limiter component;

[0060] The limiter part is connected to the four-power splitter part;

[0061] The four power divider parts are connected to the radio frequency delayer part at the same time in four ways;

[006...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More