Patents

Literature

34results about How to "Reliability issue" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

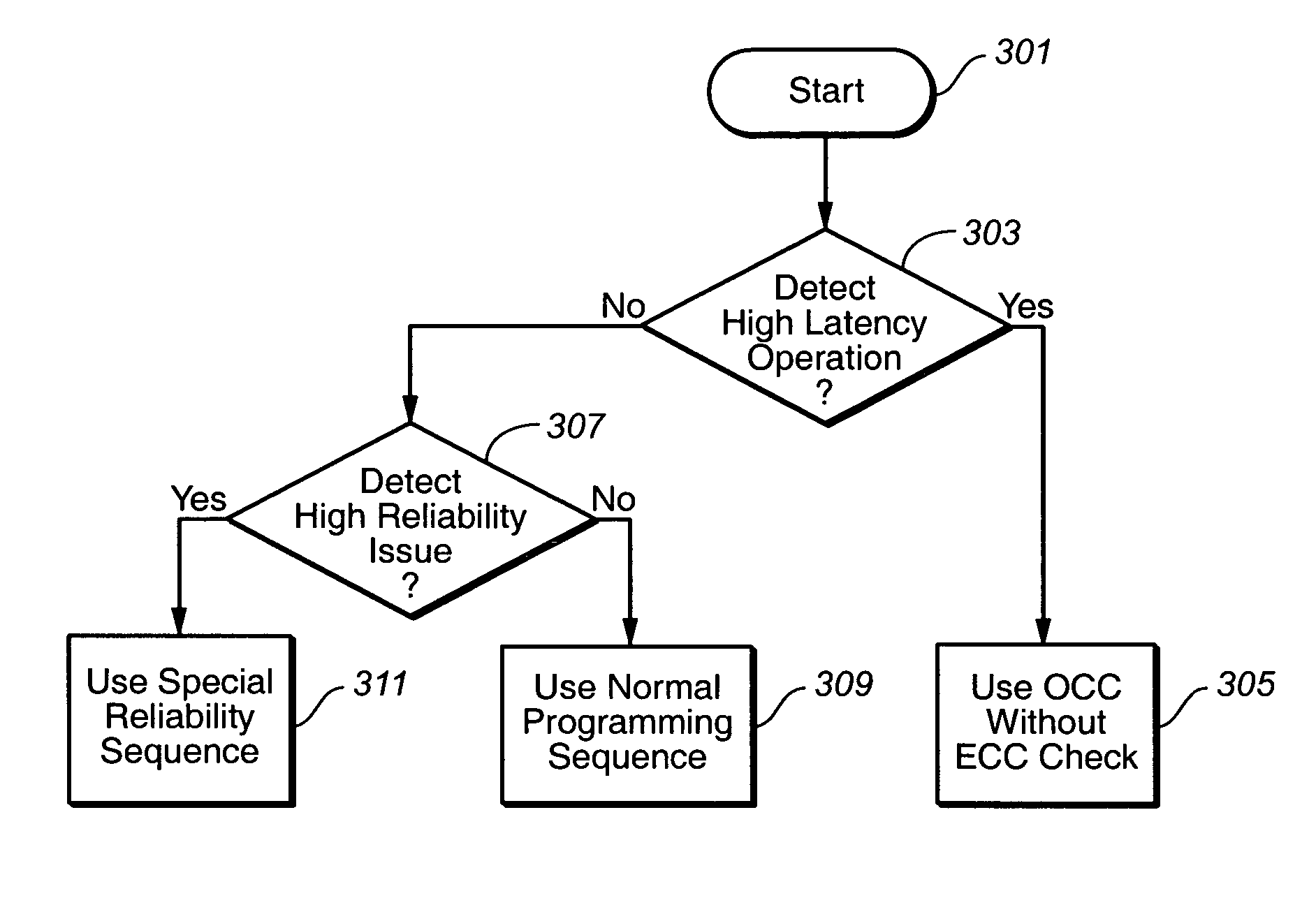

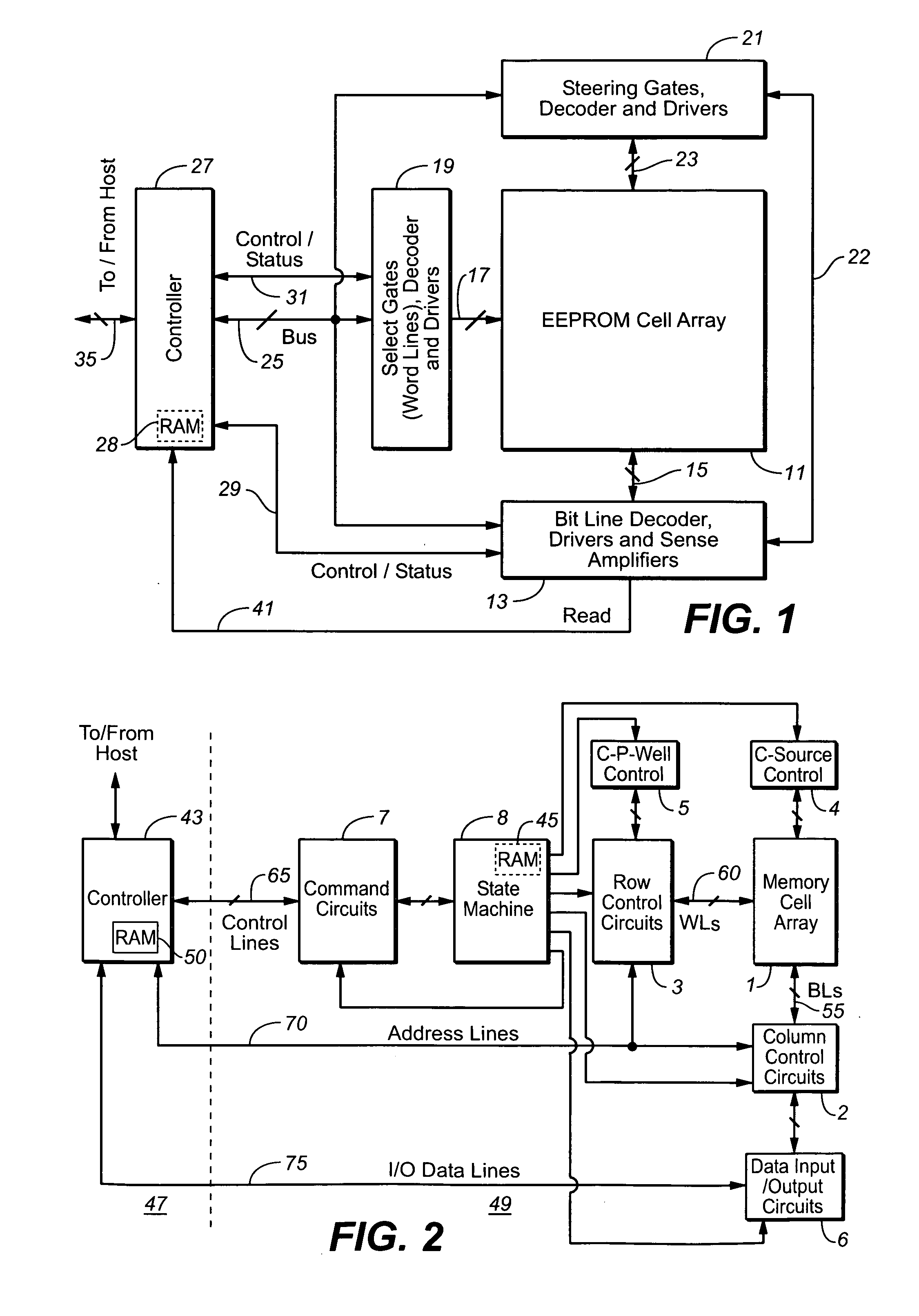

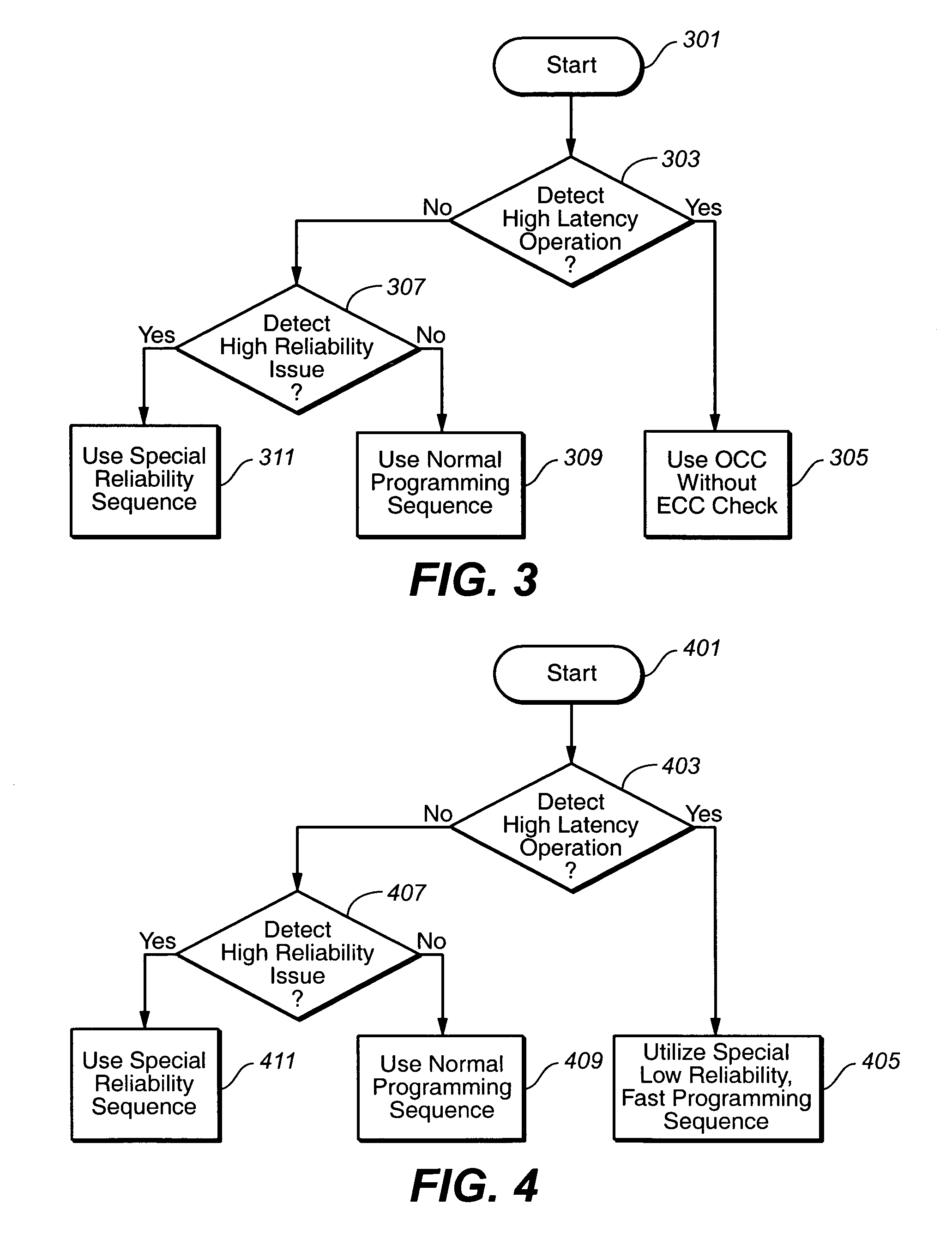

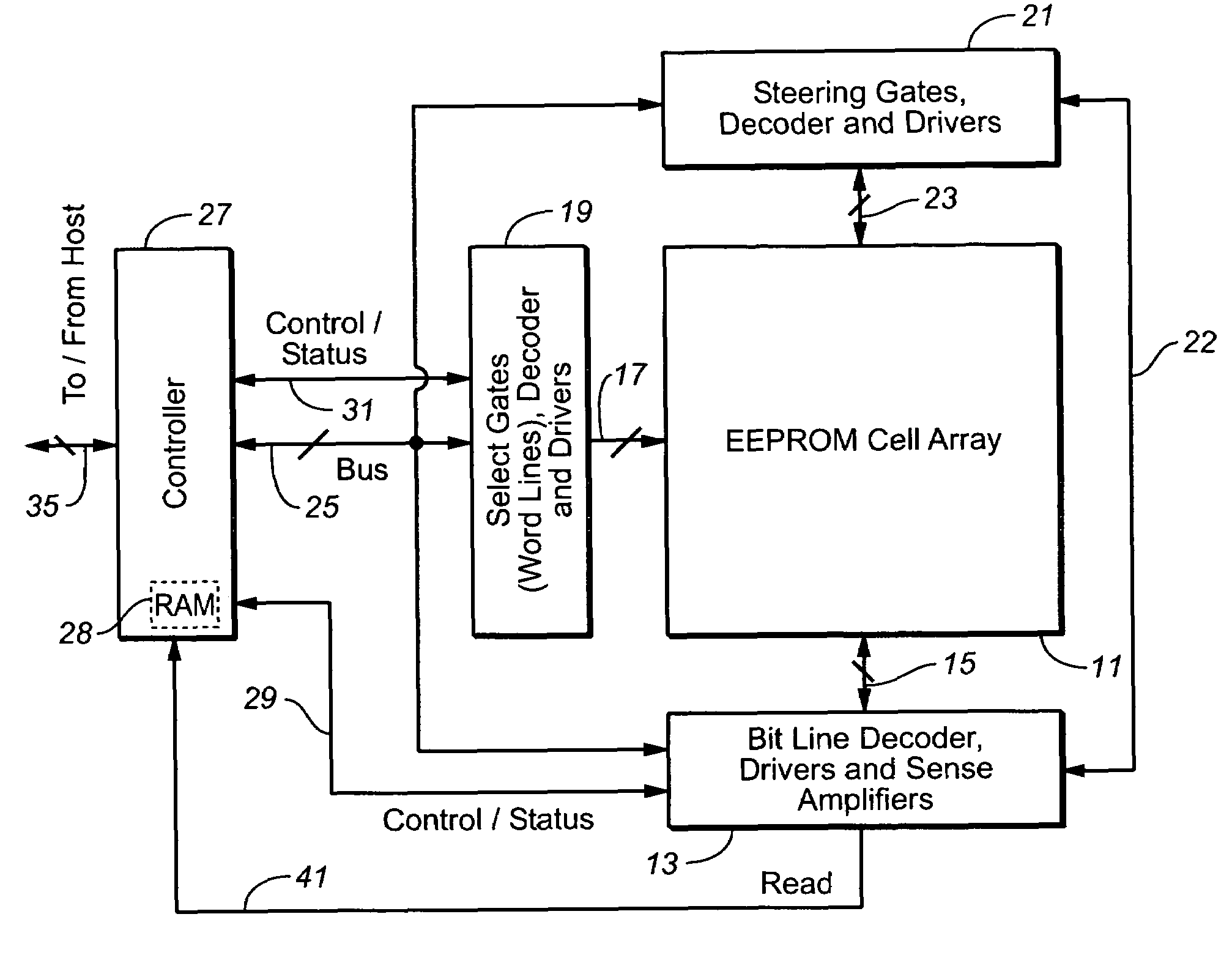

Situation sensitive memory performance

ActiveUS20070033581A1Avoid timeoutImprove programming speedEnergy efficient ICTVolume/mass flow measurementTerm memoryComputer science

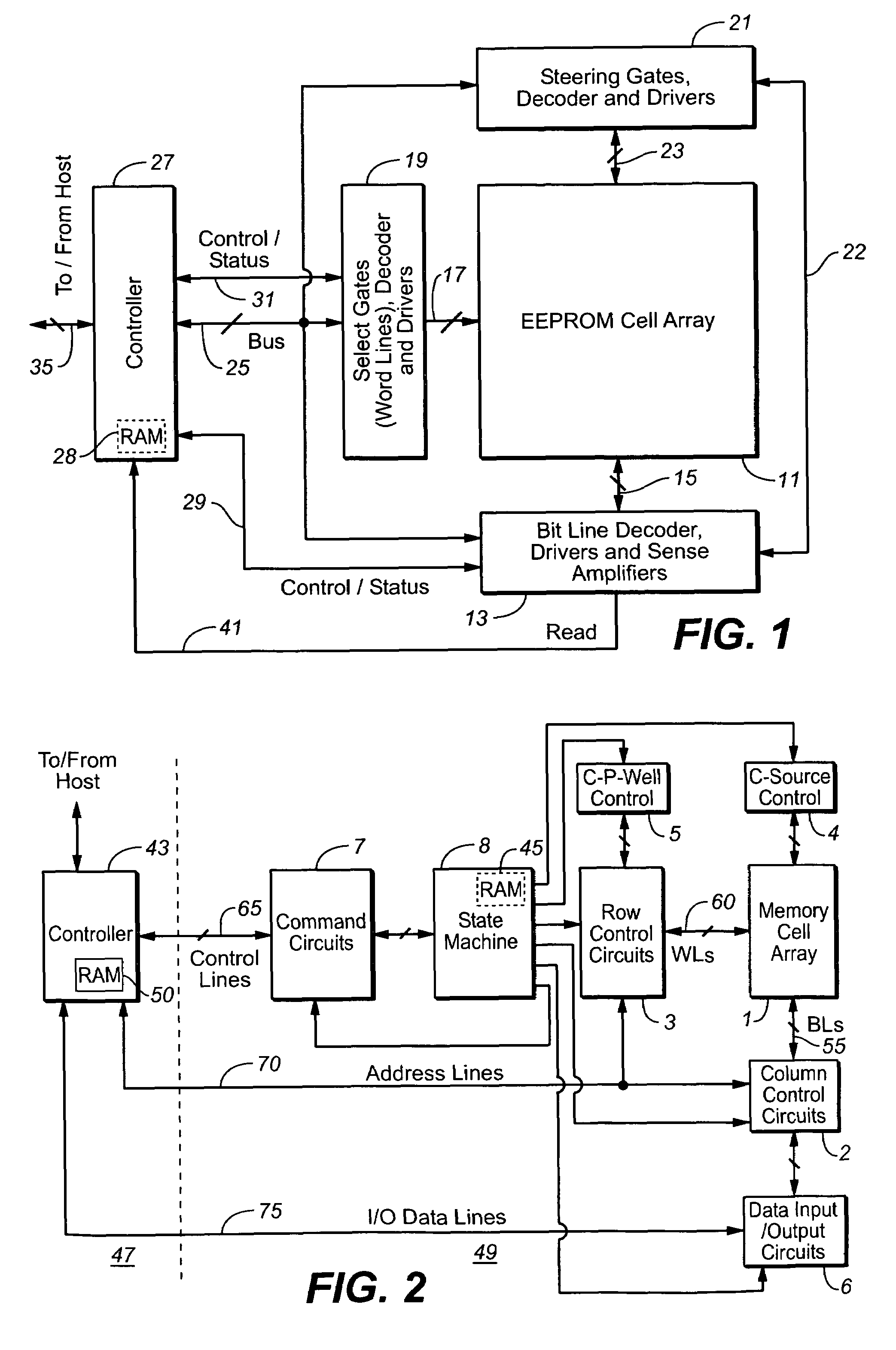

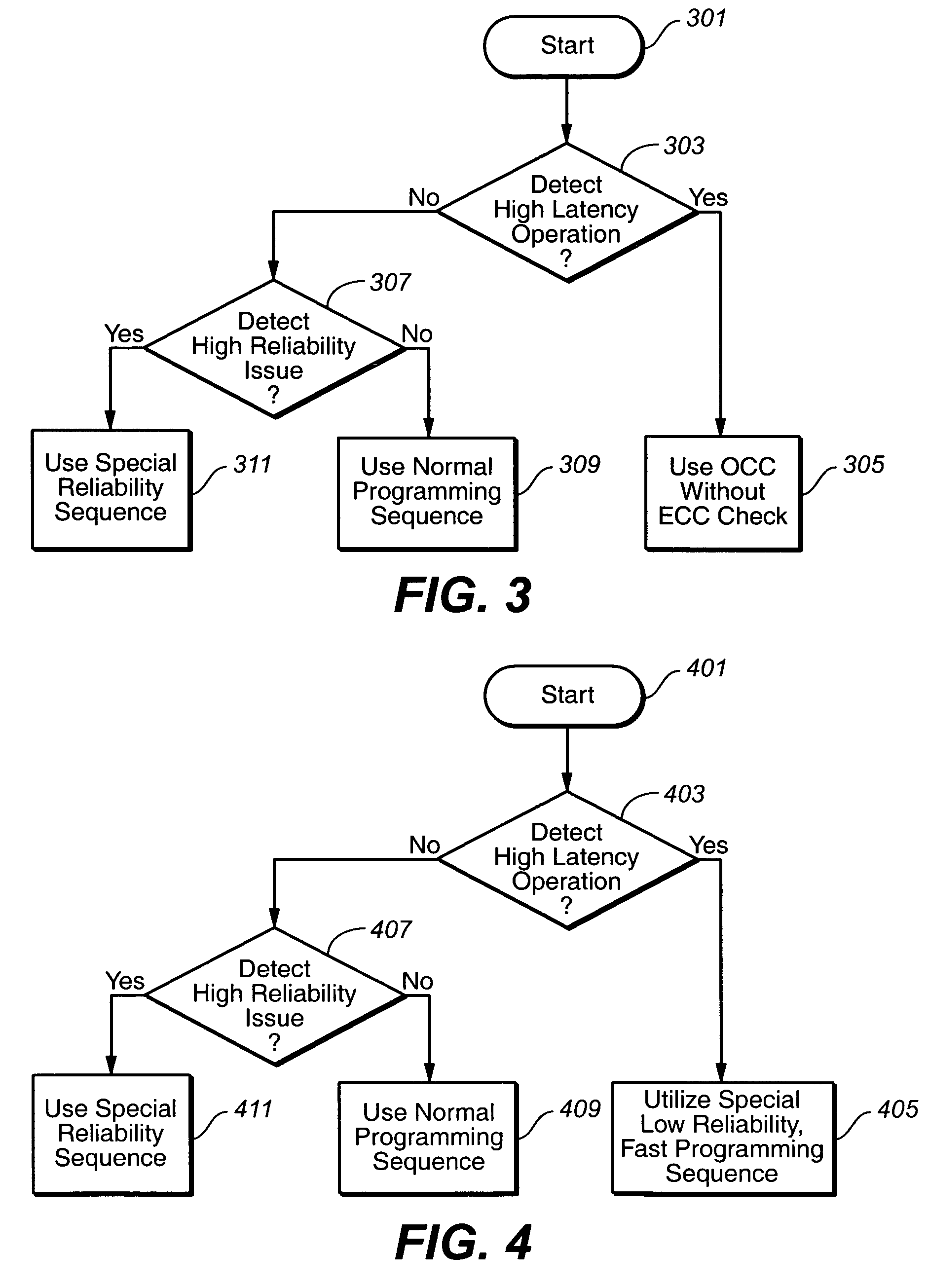

The present invention presents a non-volatile memory system that adapts its performance to one or more system related situation. If a situation occurs where the memory will require more than the allotted time for completing an operation, the memory can switch from its normal operating mode to a high performance mode in order to complete the operation quickly enough. Conversely, if a situation arises where reliability could be an issue (such as partial page programming), the controller could switch to a high reliability mode. In either case, once the trigging system situation has returned to normal, the memory reverts to the normal operation. The detection of such situations can be used both for programming and data relocation operations. An exemplary embodiment is based on firmware programmable performance.

Owner:SANDISK TECH LLC

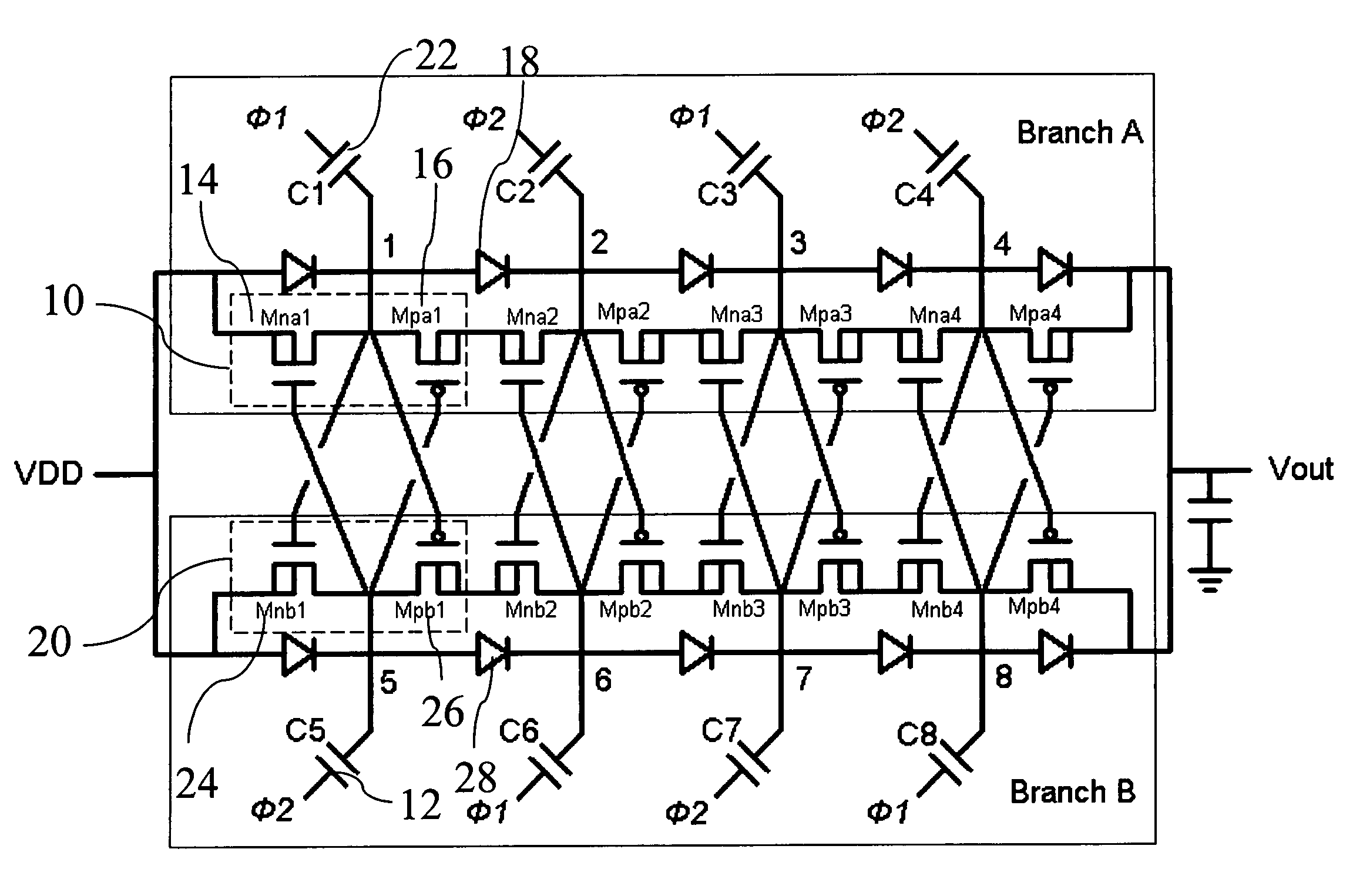

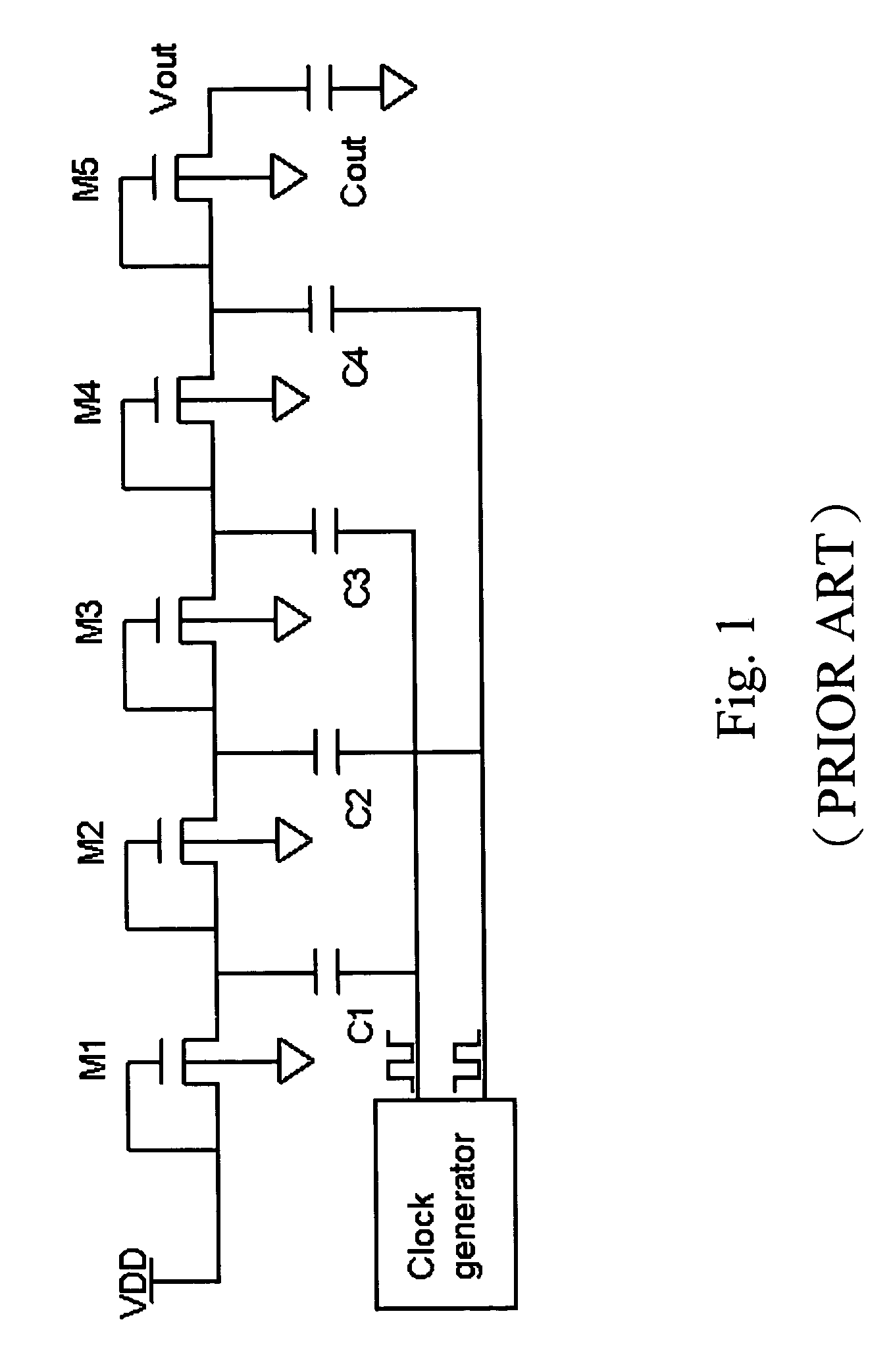

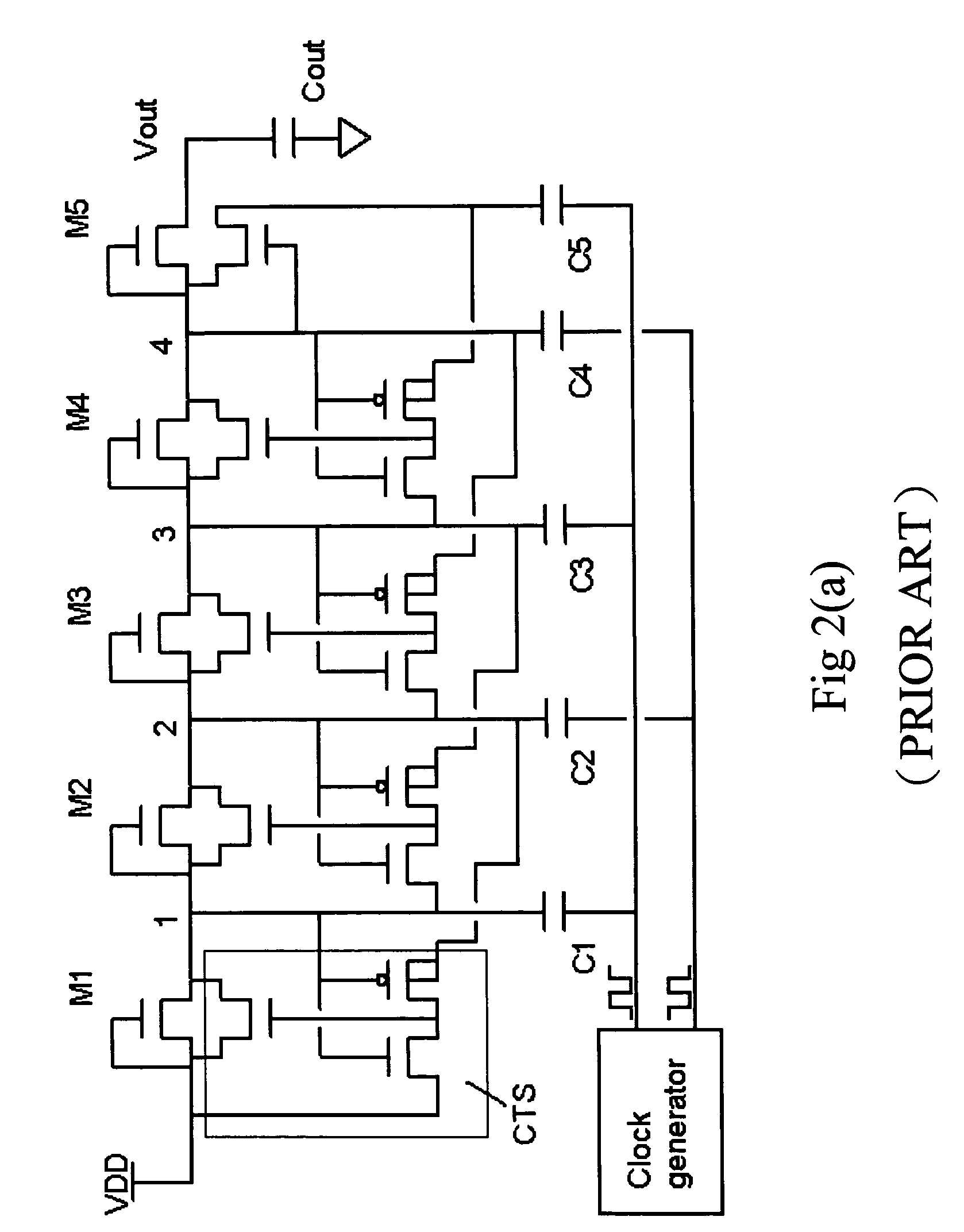

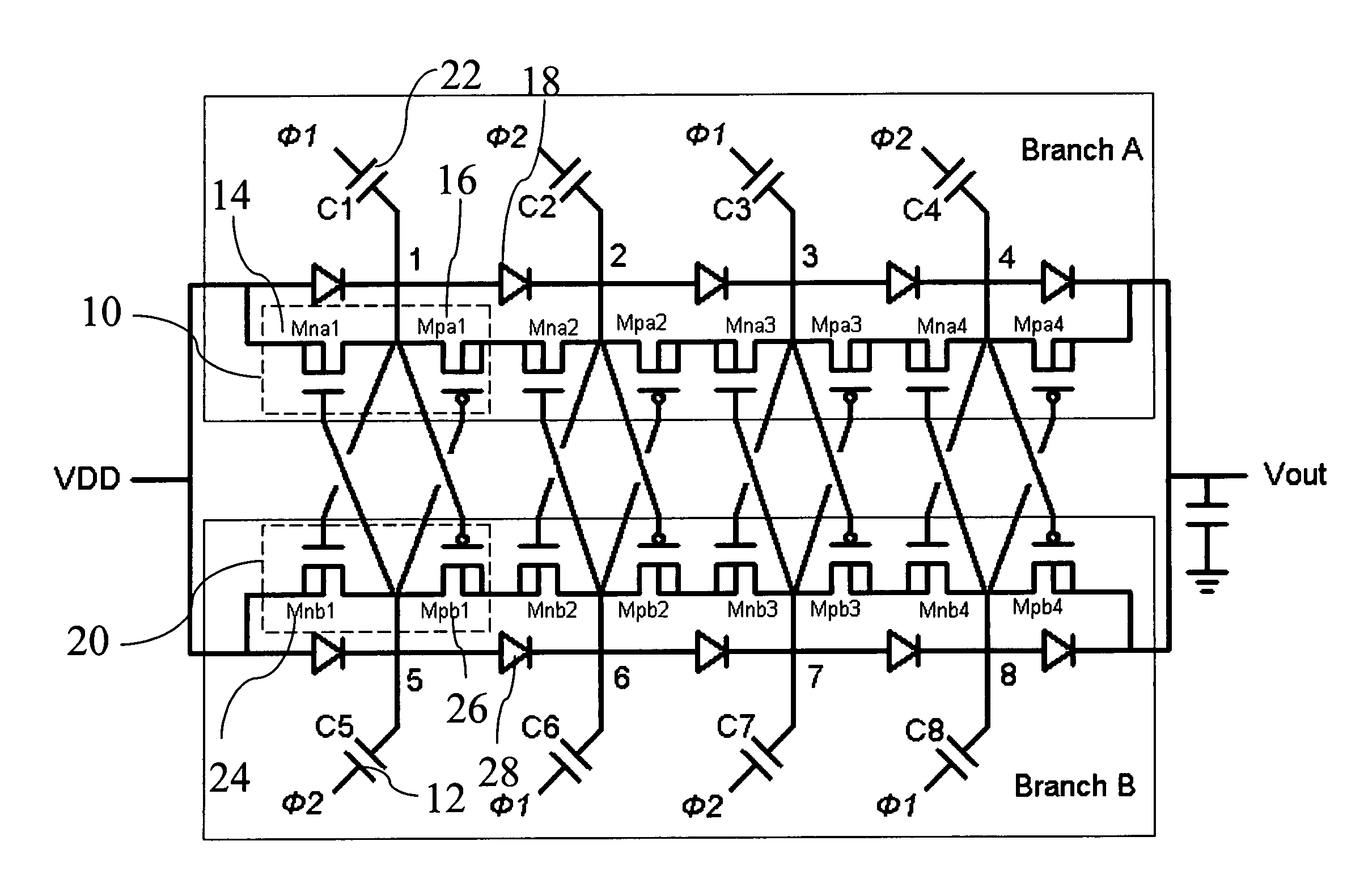

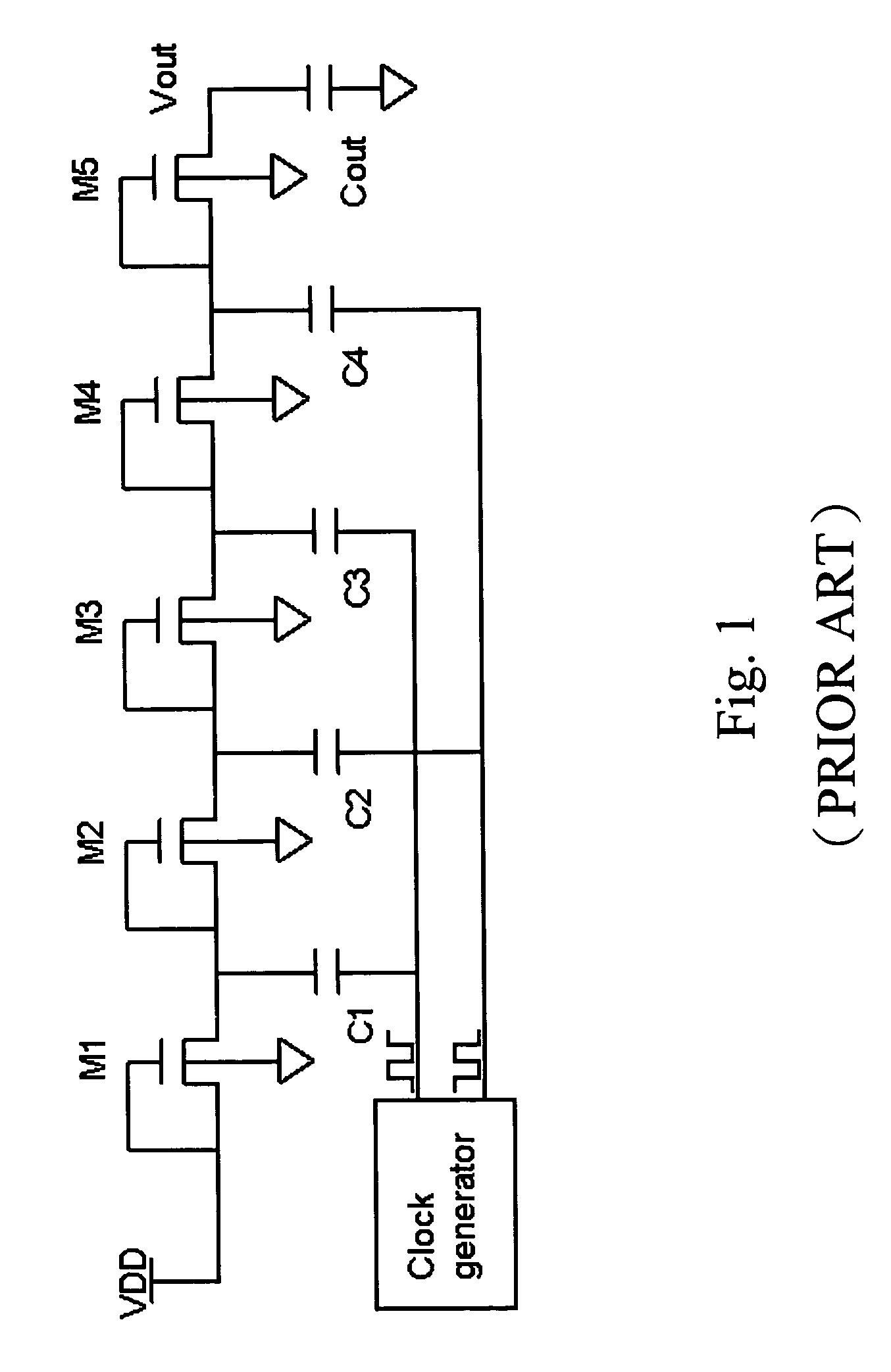

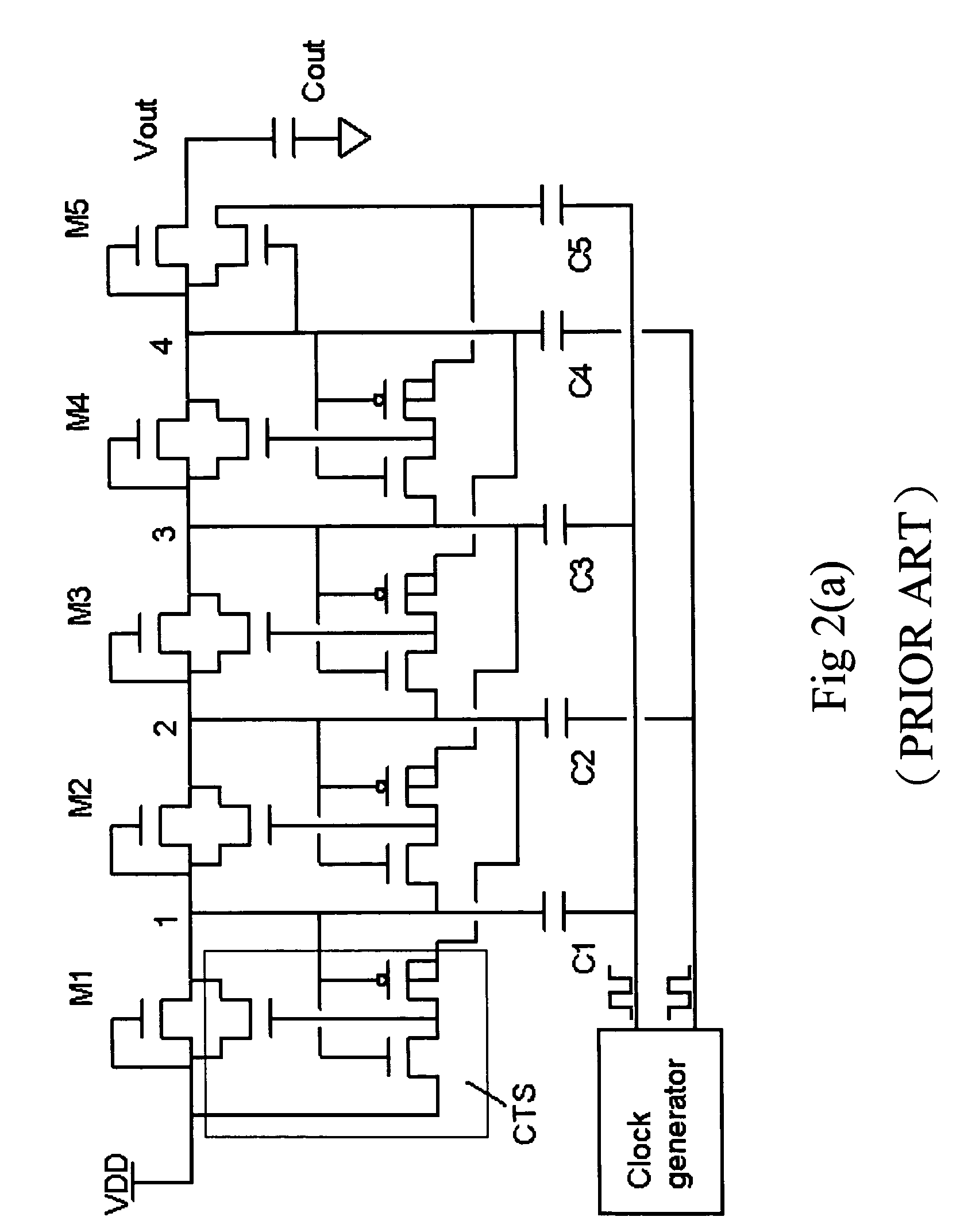

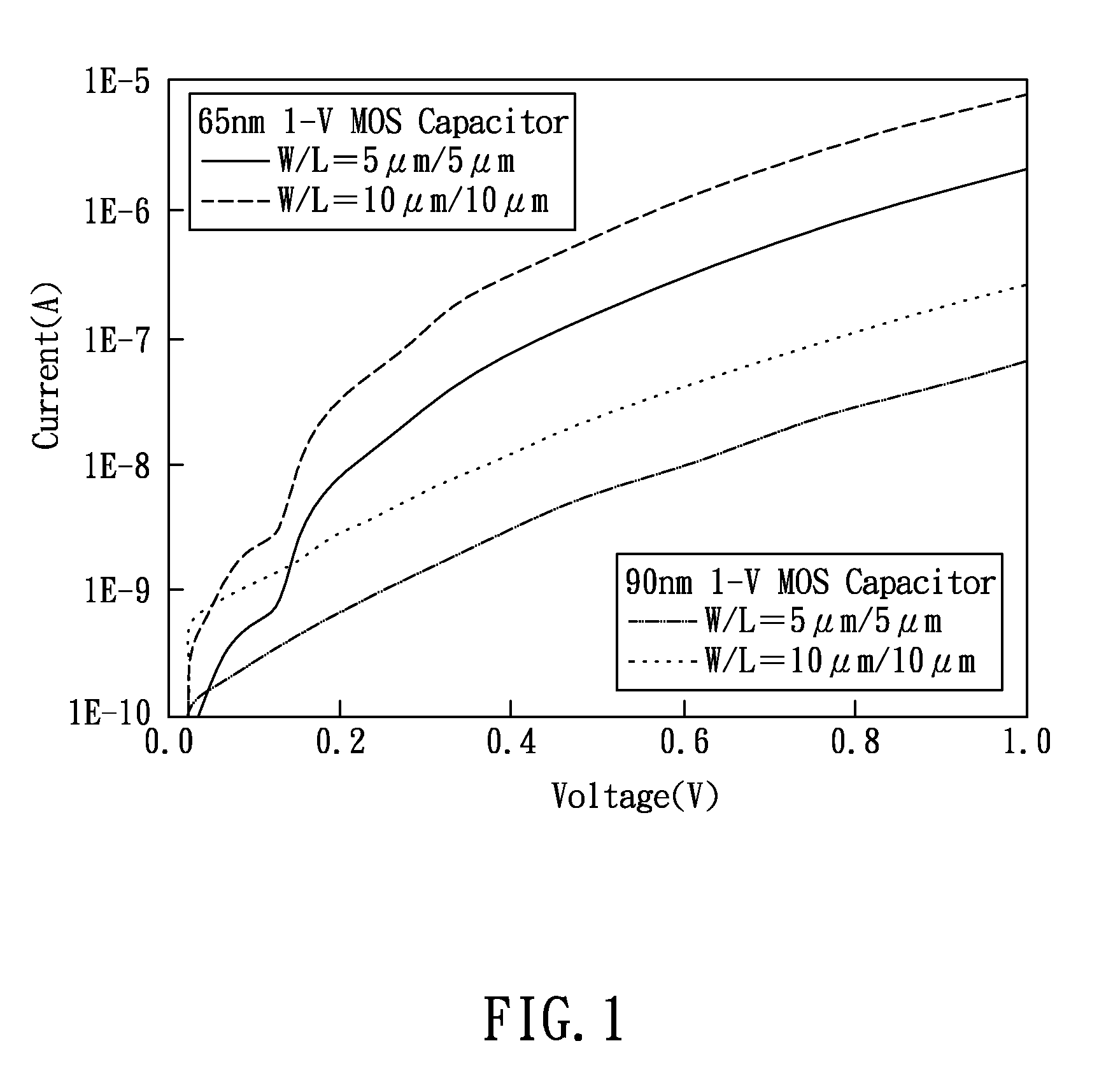

Charge pump circuit suitable for low-voltage process

InactiveUS7145382B2High pumping gainReliability issueRead-only memoriesApparatus without intermediate ac conversionCMOSLow voltage

The present invention discloses a charge pump circuit suitable for a low-voltage process. The charge pump circuit is composed of stages of the voltage amplifying circuits connected each other, and the operation of two adjacent stages of voltage amplifying circuit is controlled by two opposite set of the timing signals. Each stage of the voltage amplifying circuit has a coupled pair of a first complementary MOS (CMOS) transistor and a second CMOS transistor switching in accordance with a timing signal and an inverse timing signal inputted into the first and second capacitors. Then, two diode devices guide charges to next stage, and a voltage higher than the integrated circuit voltage source is outputted. The present invention has advantage of high pumping gain, and the reliability issue of the gate oxide layer in the low-voltage process can be also solved.

Owner:NAT CHIAO TUNG UNIV

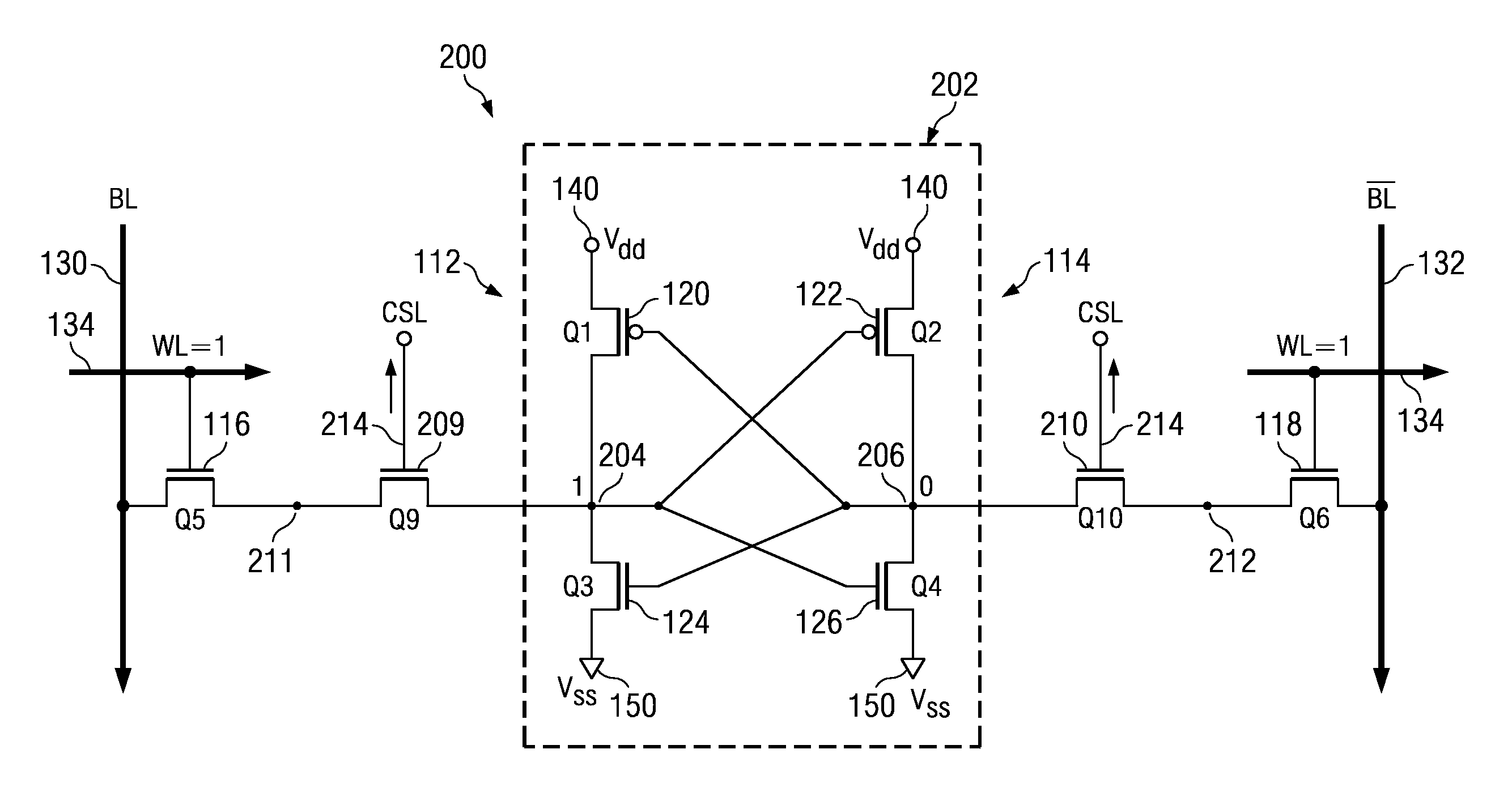

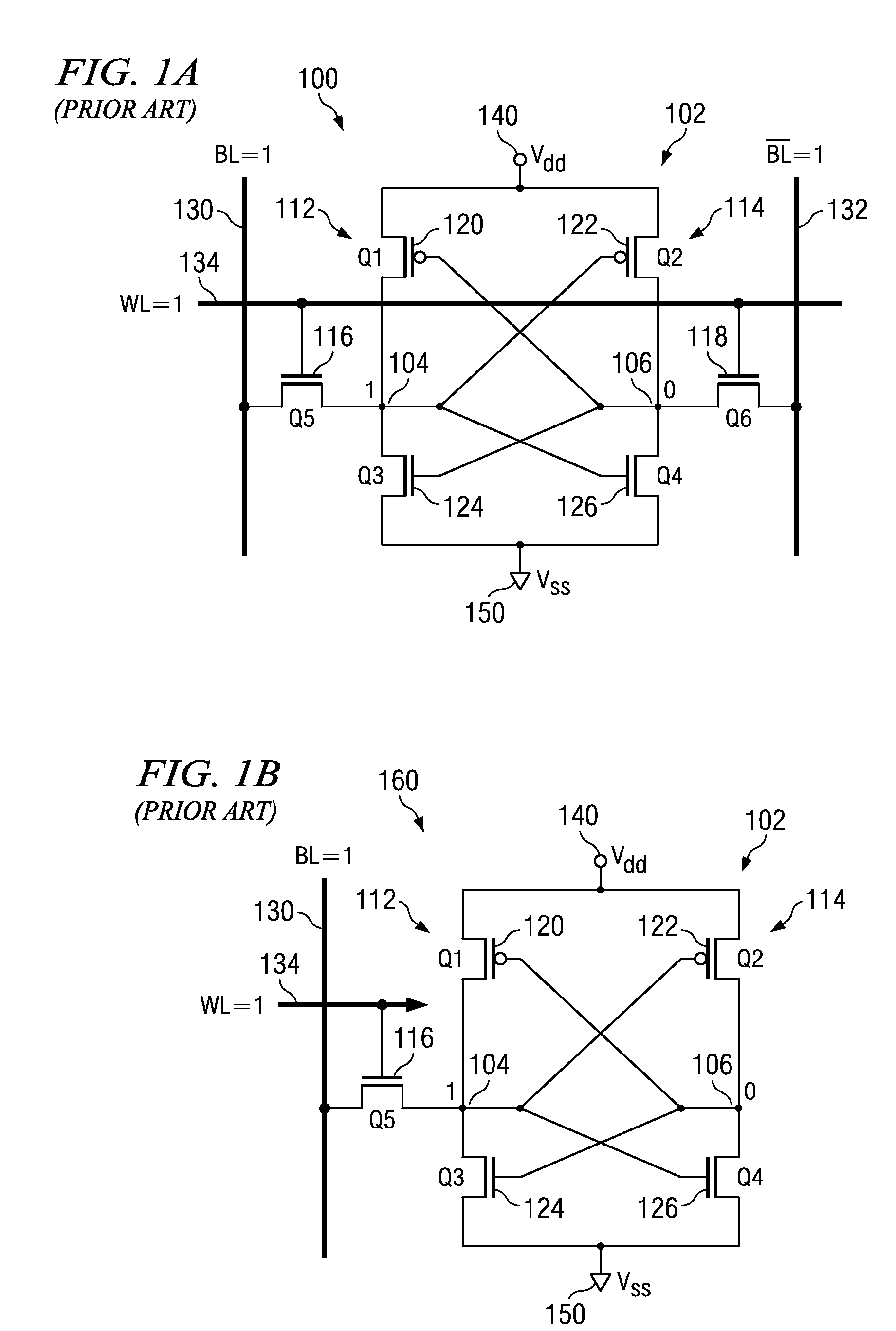

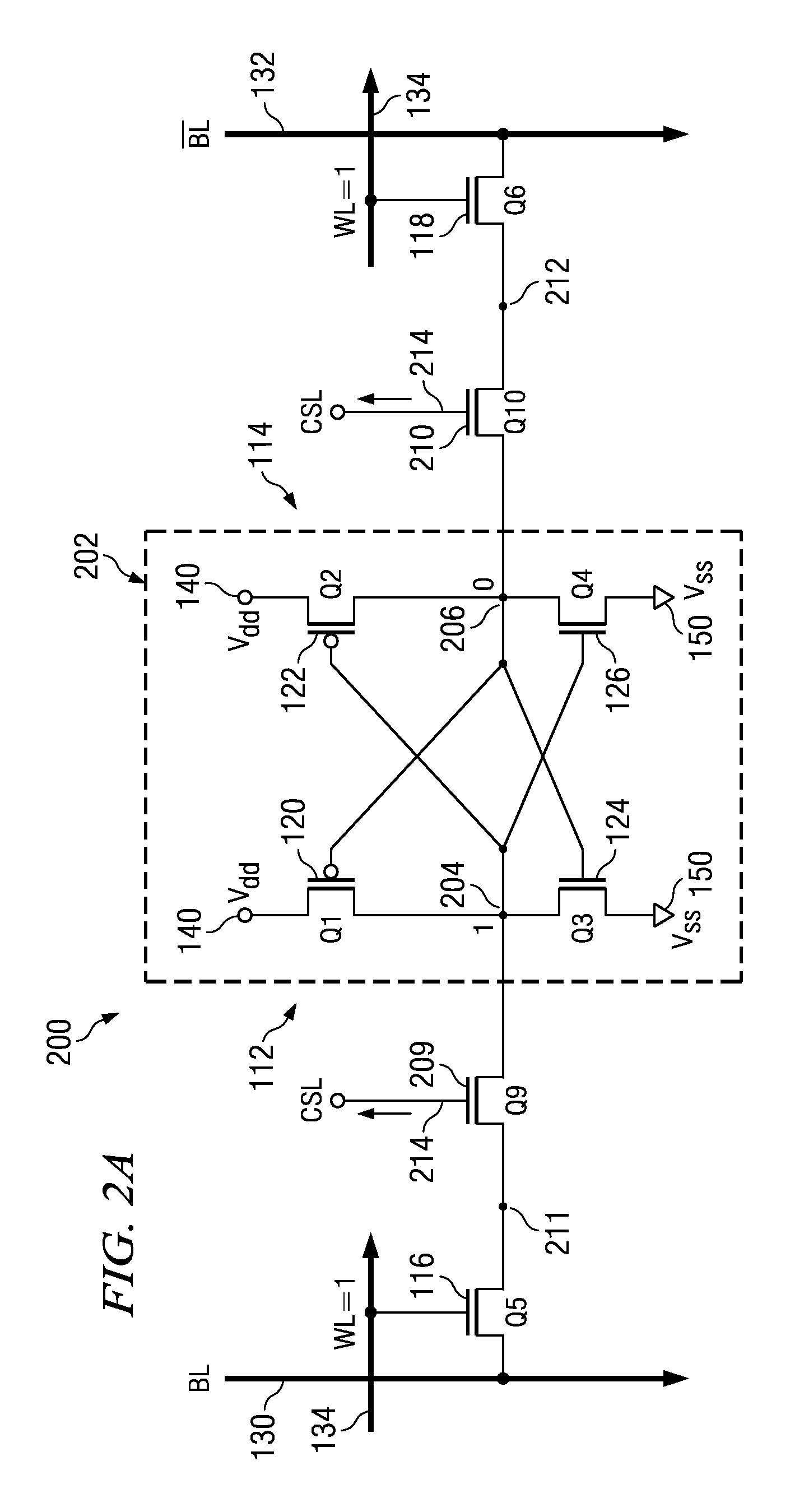

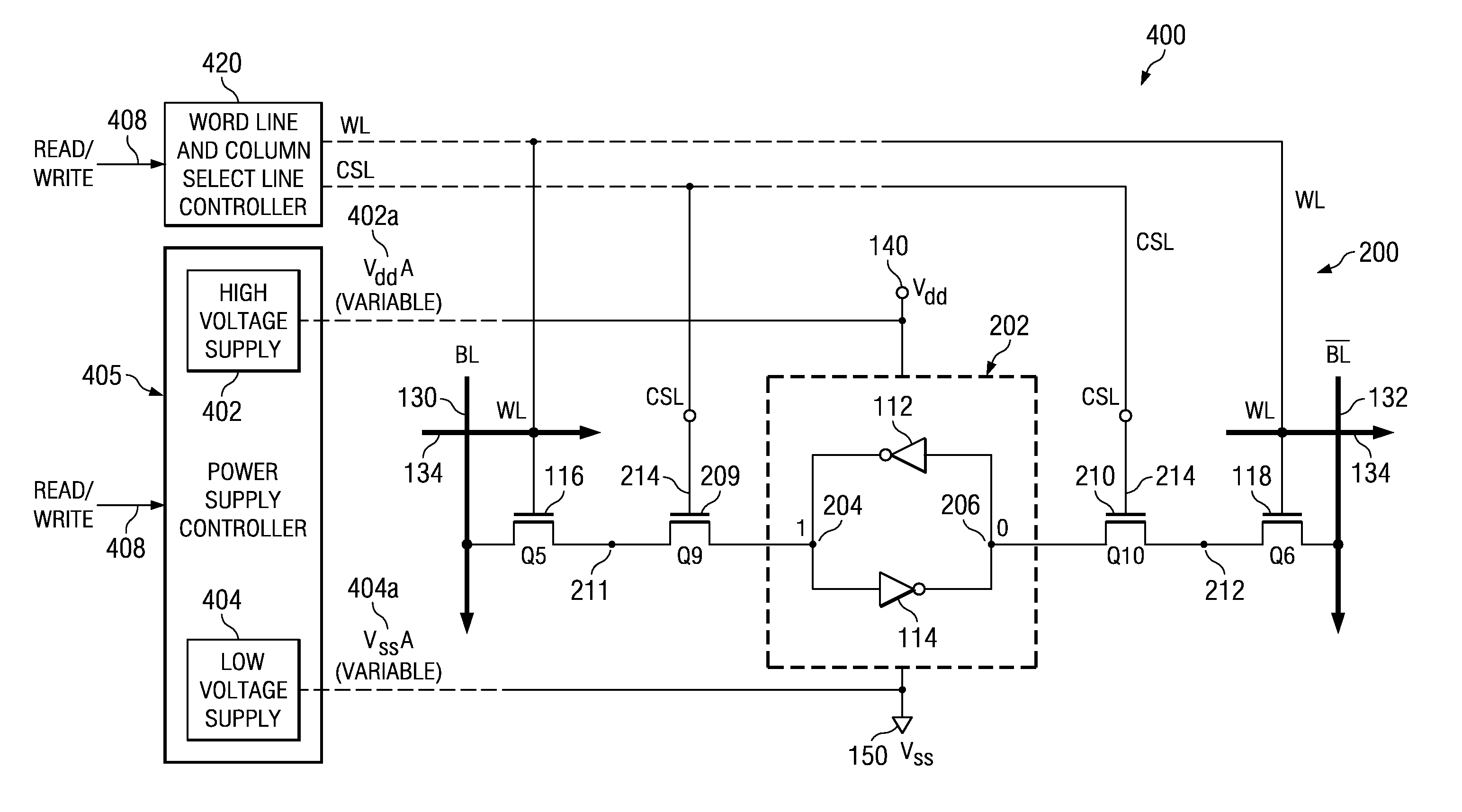

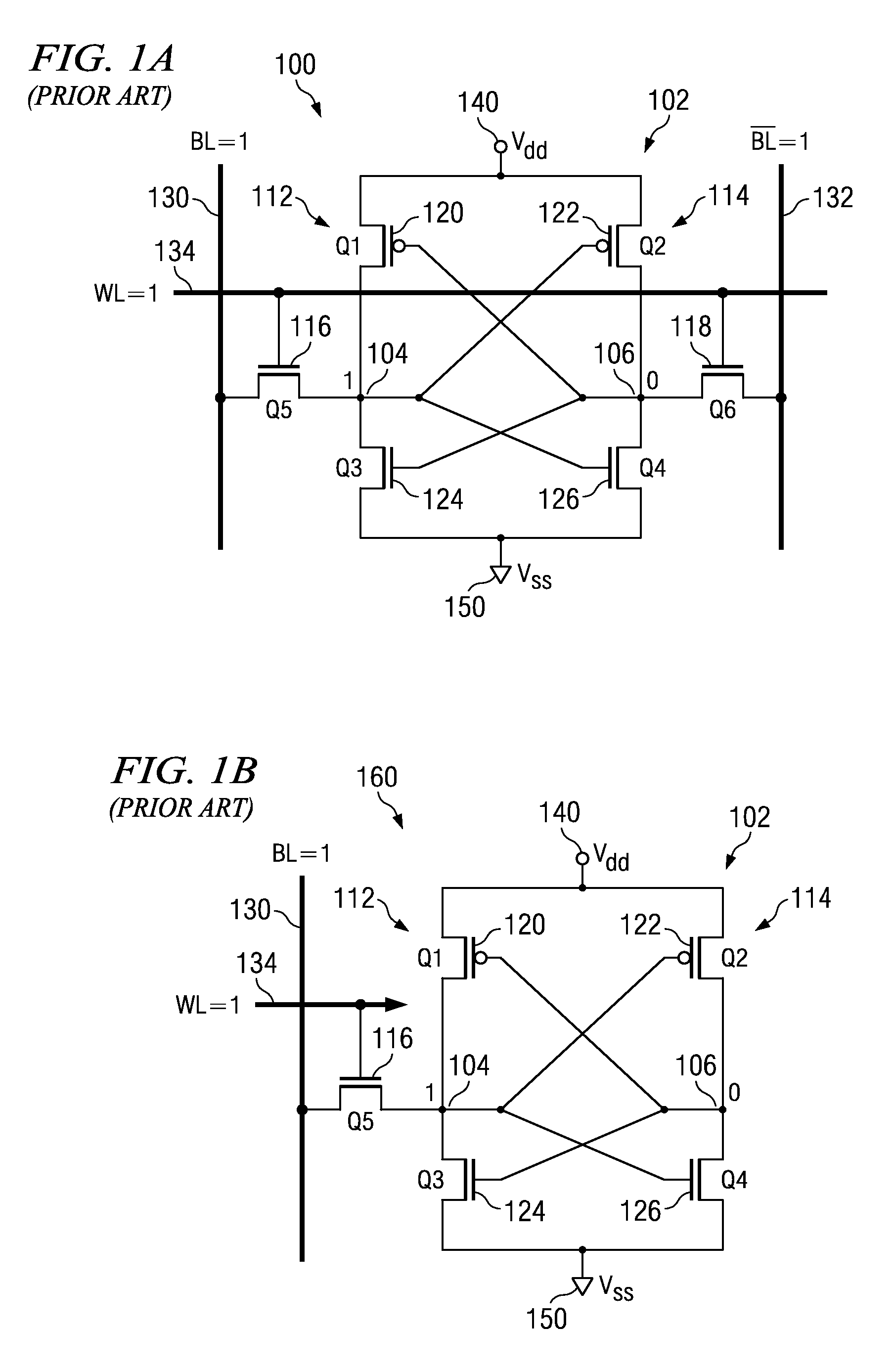

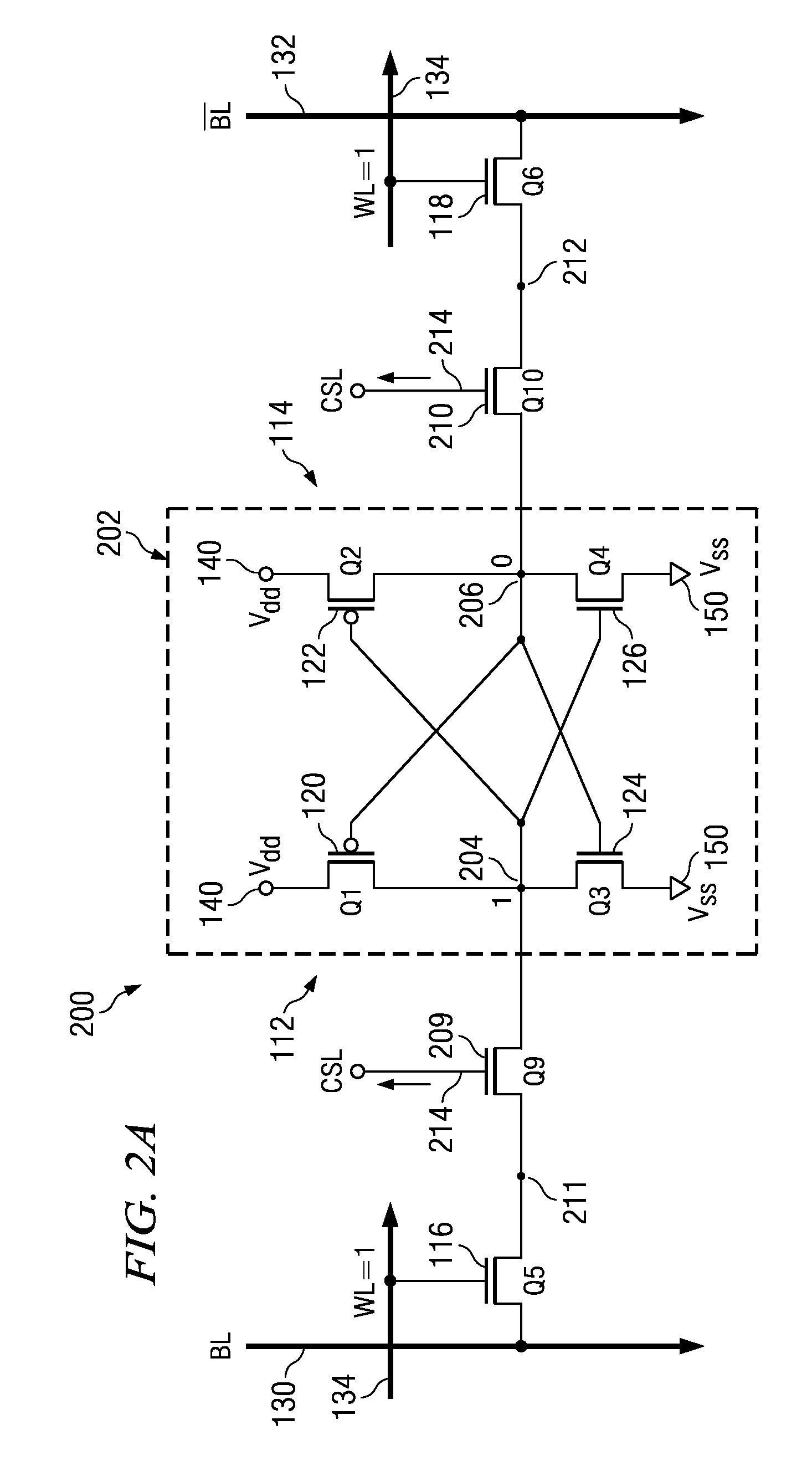

SRAM cell with column select line

ActiveUS7164596B1Optimum static noise marginMinimizing data upsetDigital storageLow voltageHigh pressure

An array of SRAM cells (e.g., 6T single-ended or 8T differential cells) and method is discussed having variable high and low voltage power supplies to provide to selected cells of the array a write bias condition during a write operation and a read bias condition to the array during a read operation, wherein the read bias condition is different from the write bias condition.

Owner:TEXAS INSTR INC

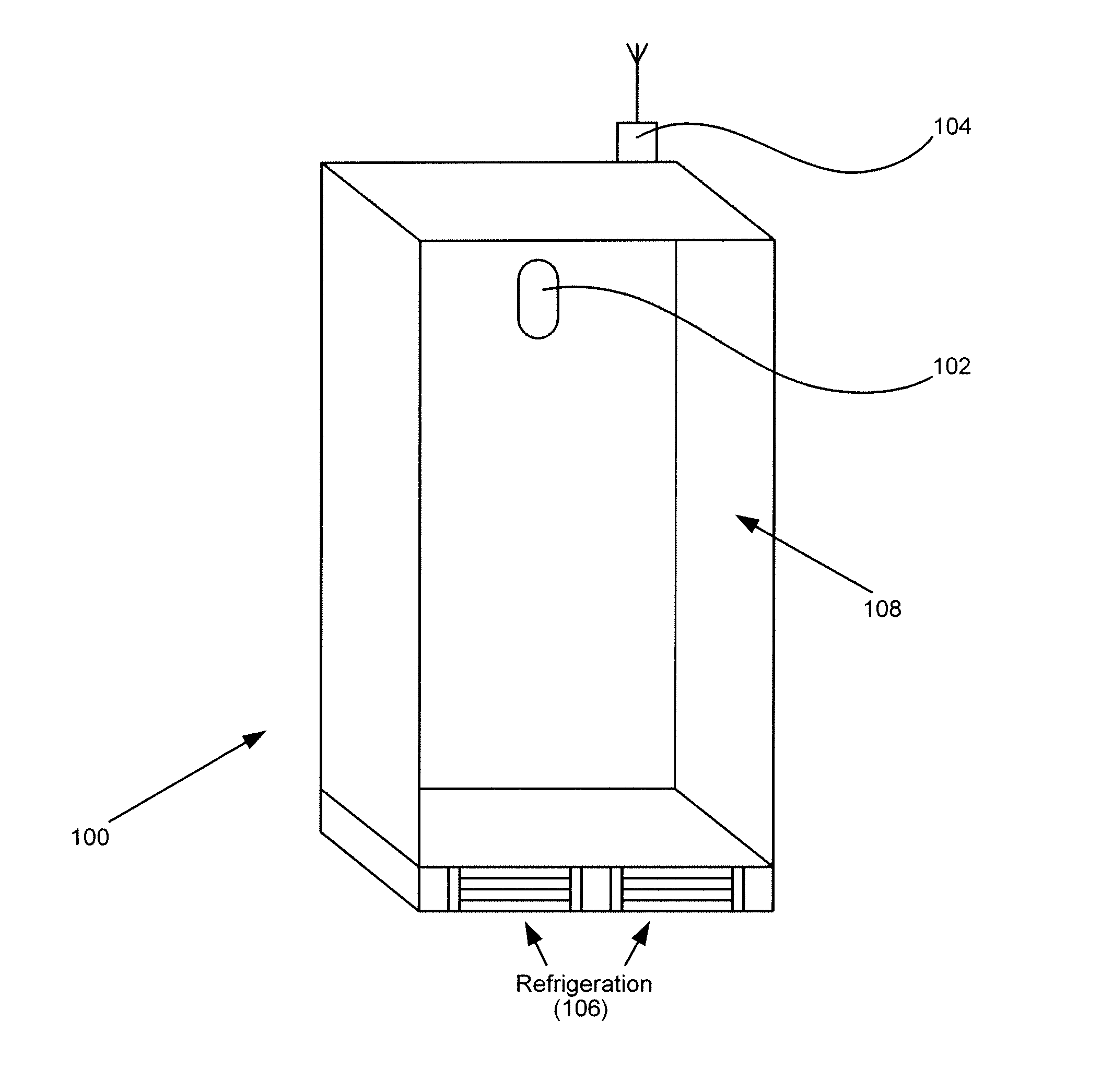

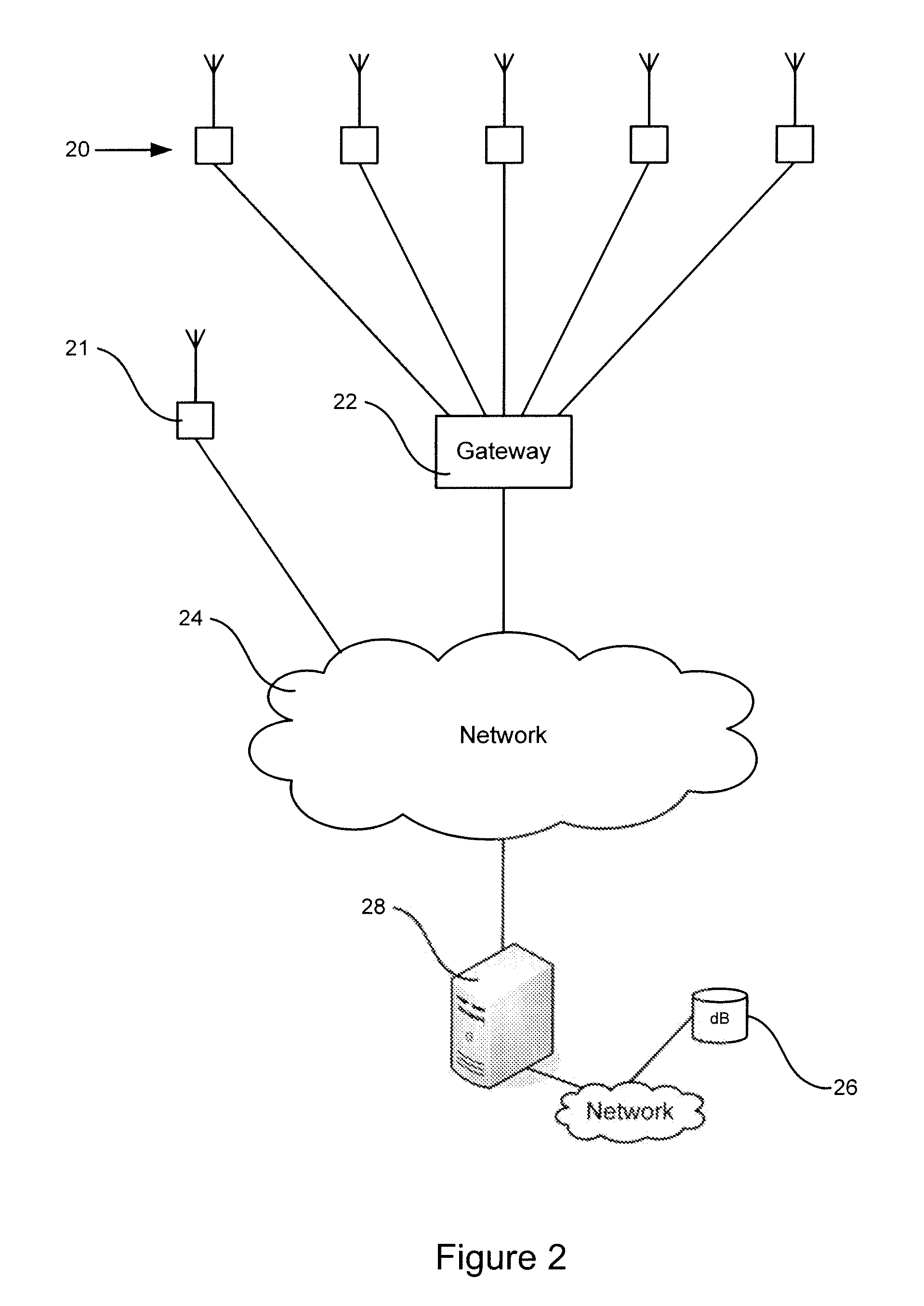

Systems and methods for monitoring, inferring state of health, and optimizing efficiency of refrigeration systems

ActiveUS20110224947A1Significant cost savingConvenient scheduleMaterial analysis using sonic/ultrasonic/infrasonic wavesMechanical apparatusMedicineIcebox

Systems and method for operating and monitoring refrigerators are described. Temperature cycles within the compartment are characterized using statistical, frequency and pattern analysis techniques to derive a steady-state characteristic of temperature within the compartment. A thermal sensor inside the conditioned area is monitored and temperature data sets can be analyzed to determine performance in comparison to a baseline, and energy consumption. Analysis of continuous temperature readings taken from individual or groups of freezers identifies patterns of variations in temperature cycles from which feedback on efficiency can be inferred. Electrical load can be determined by measuring or estimating current usage and identifying periods of time when compressors are active in the refrigerator.

Owner:KLATU NETWORKS

SRAM cell with column select line

An array of SRAM cells (e.g., 6T single-ended or 8T differential cells) and method is discussed having variable high and low voltage power supplies to provide to selected cells of the array a write bias condition during a write operation and a read bias condition to the array during a read operation, wherein the read bias condition is different from the write bias condition.

Owner:TEXAS INSTR INC

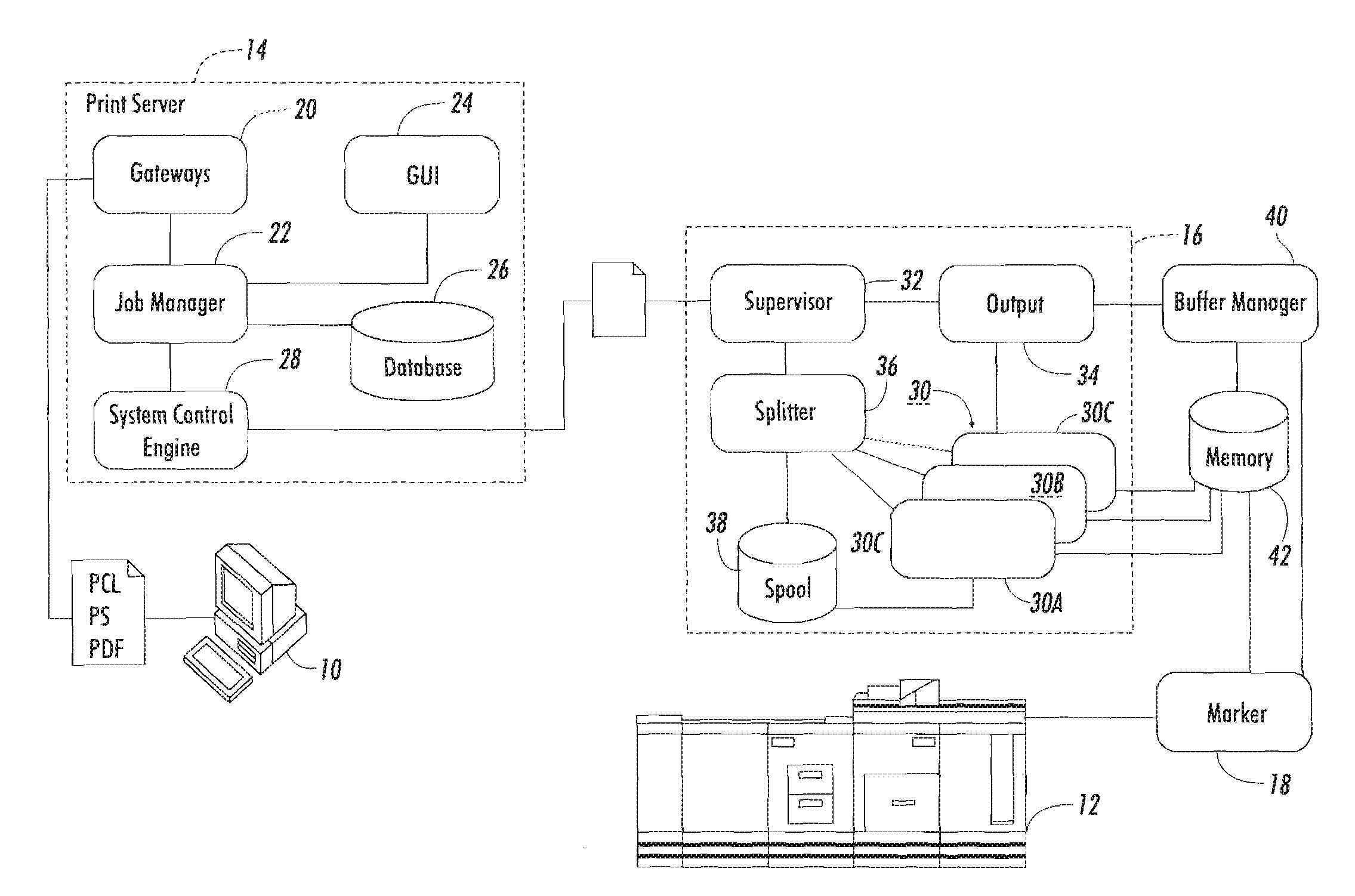

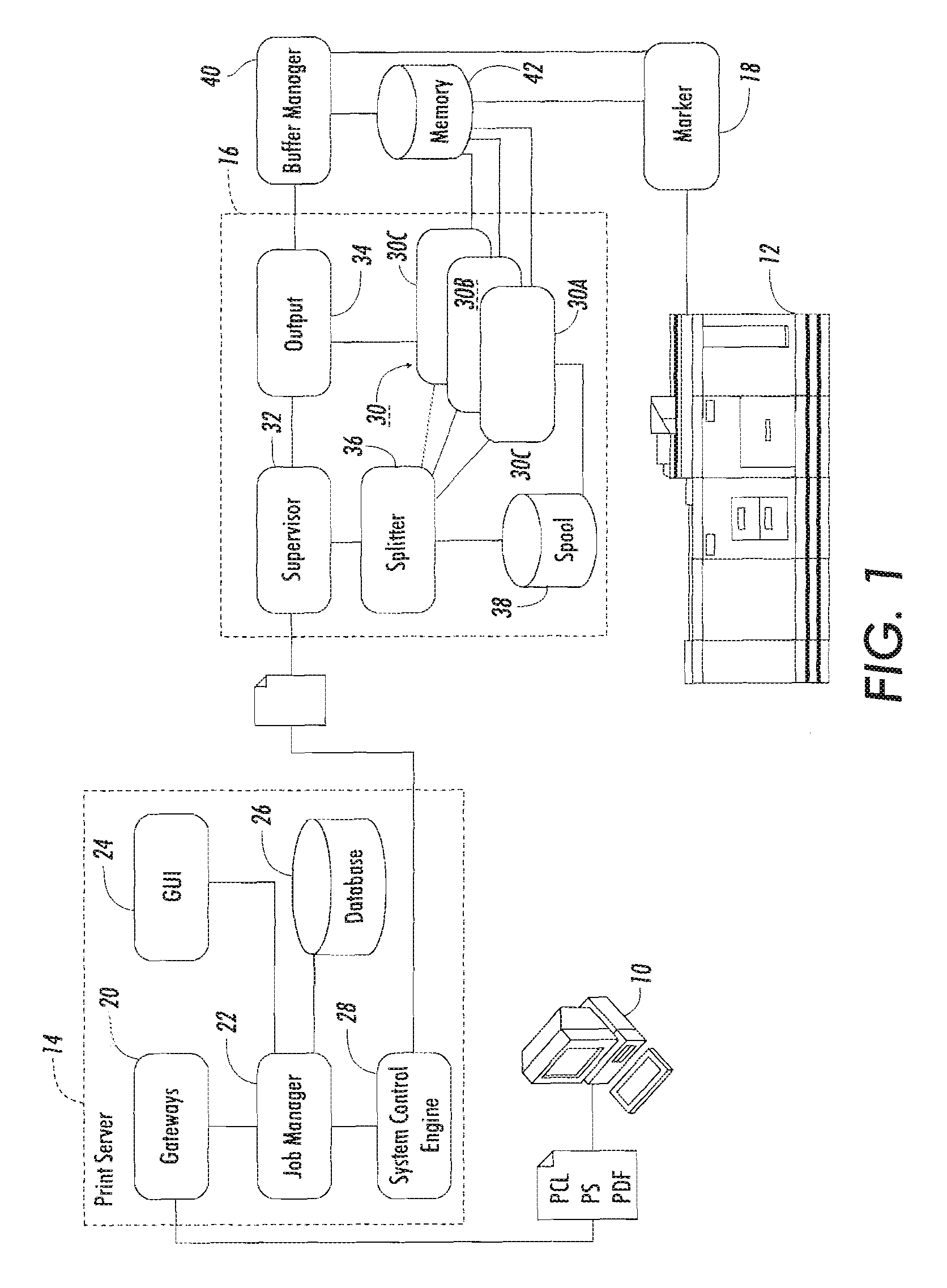

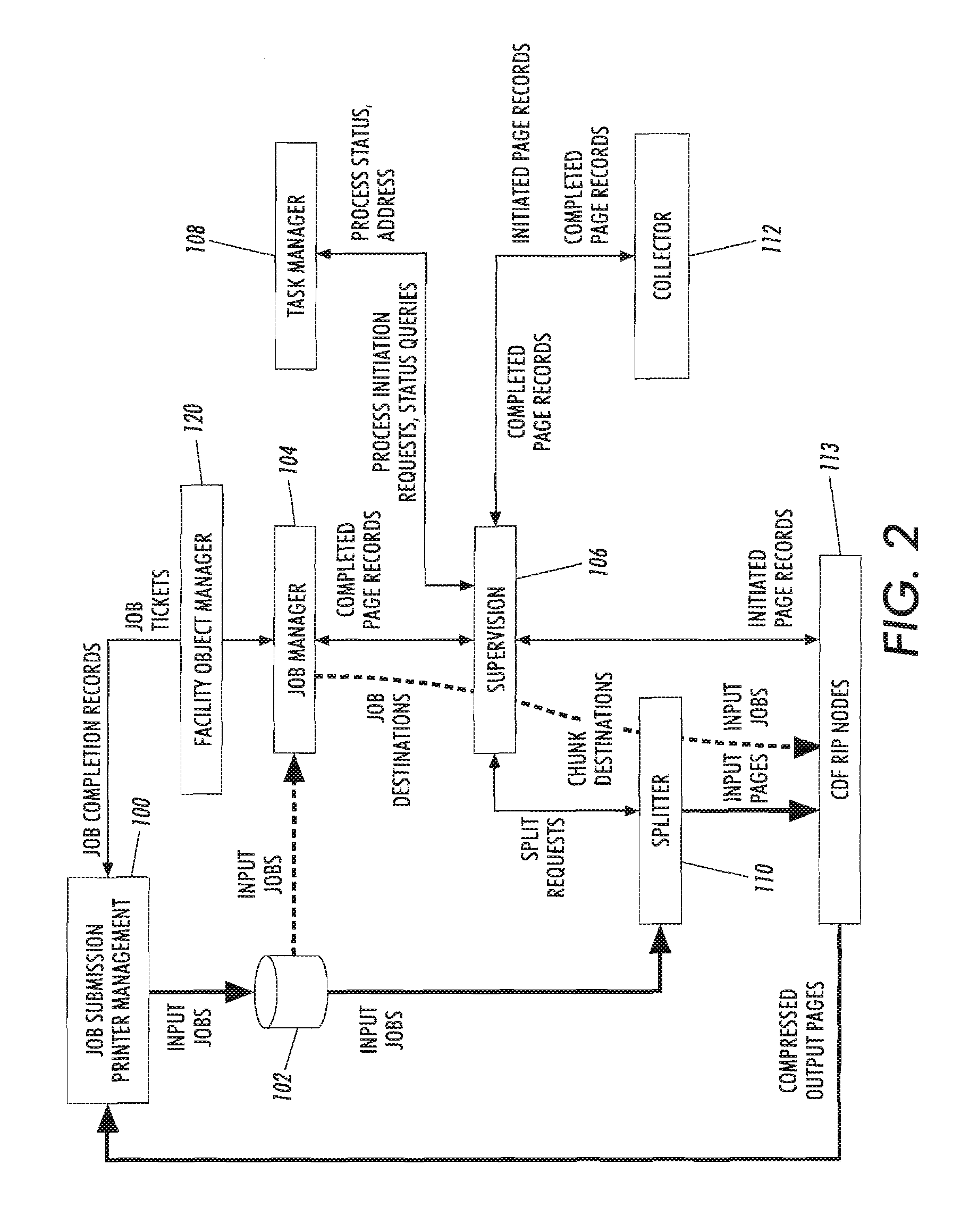

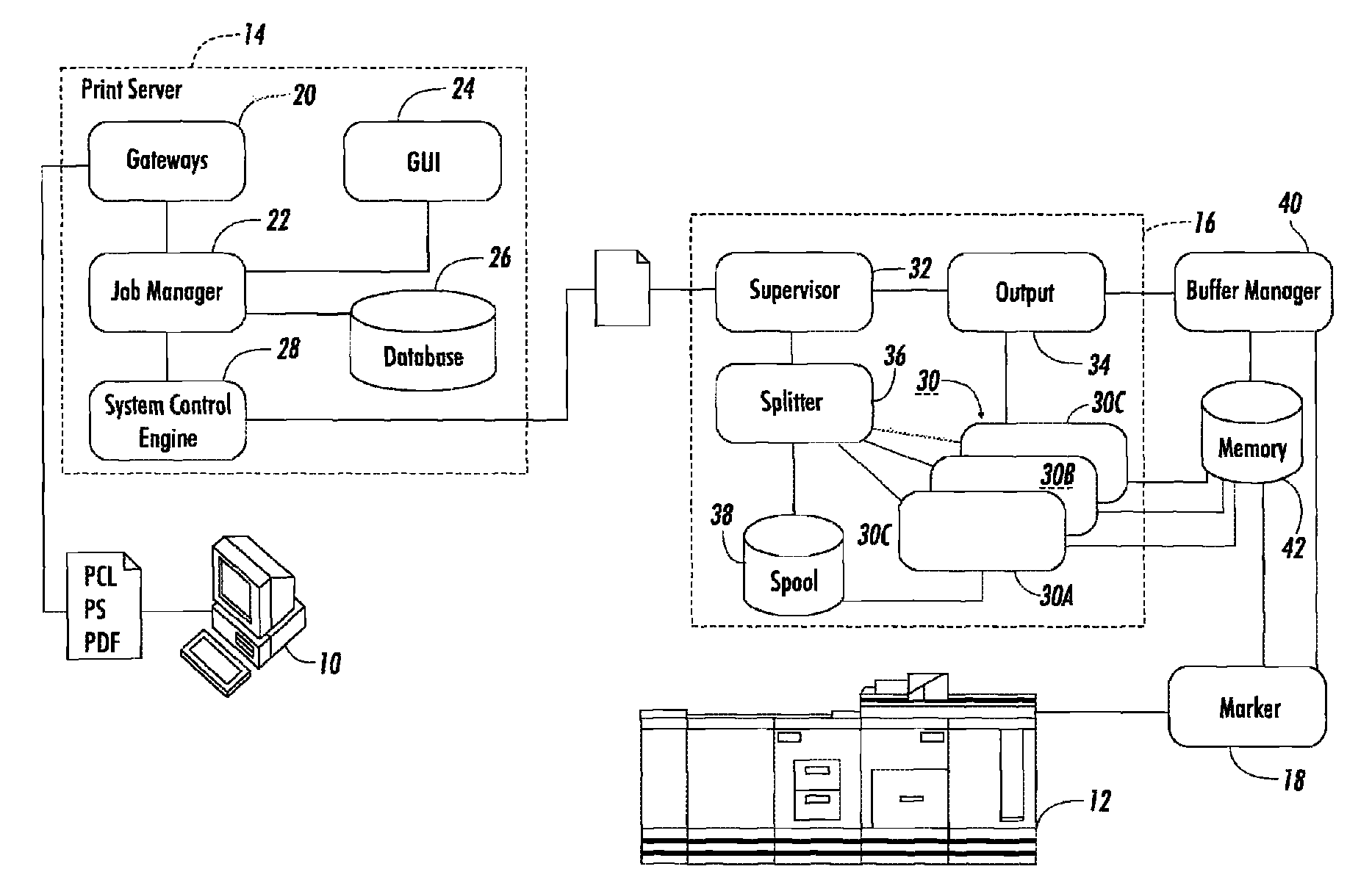

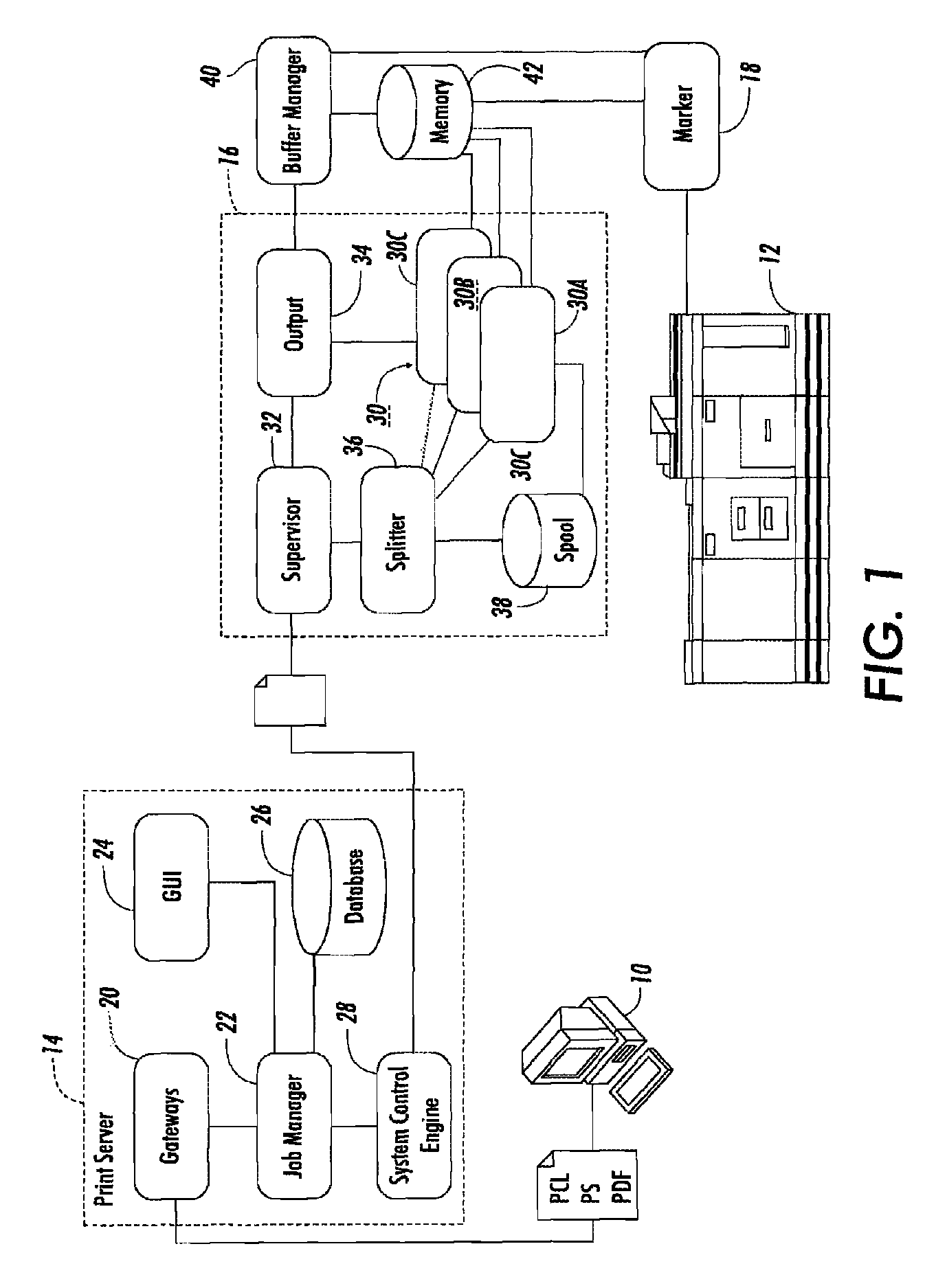

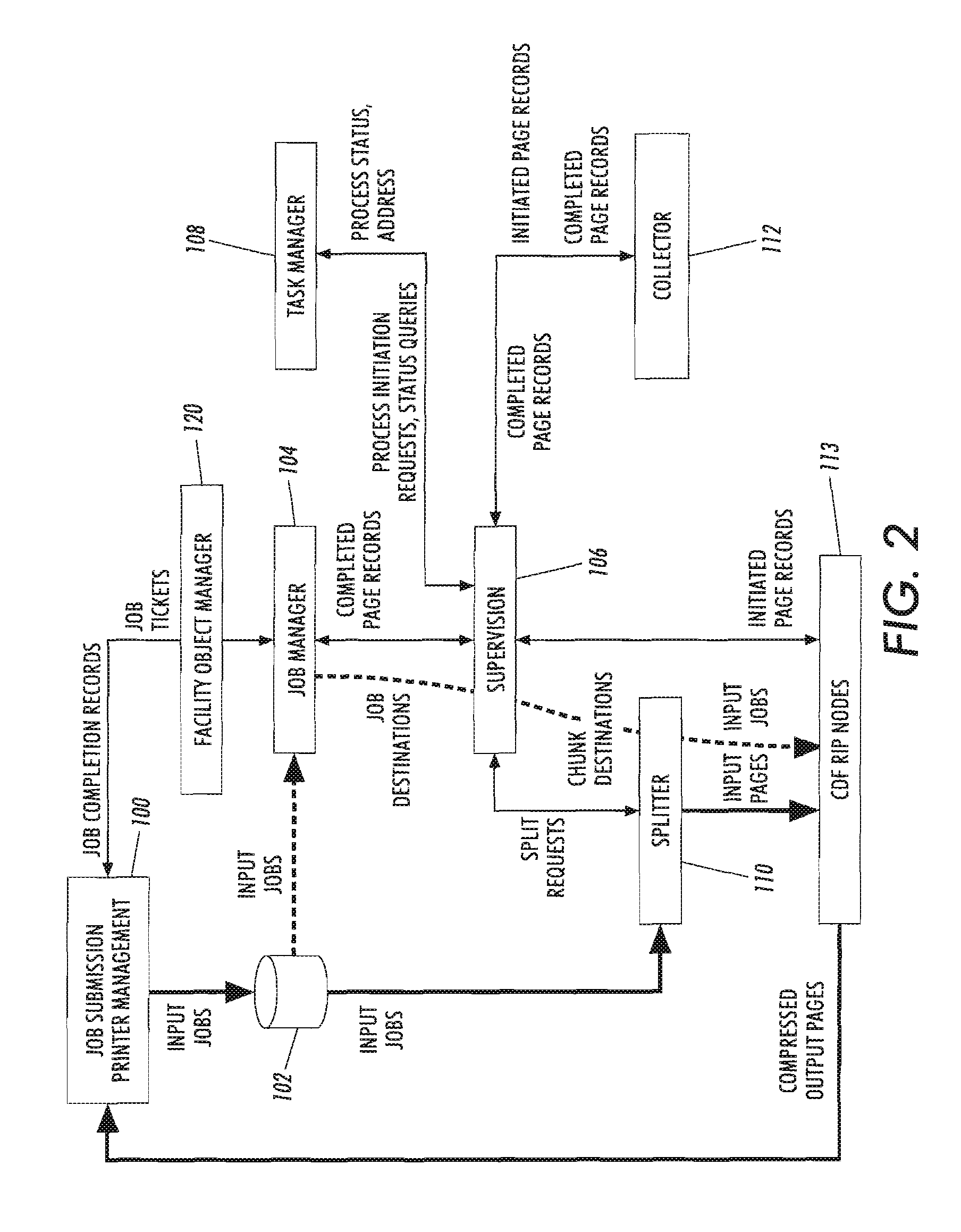

Parallel RIP with Preamble Caching

ActiveUS20090161163A1Avoid overheadEliminate overheadVisual presentationDigital output to print unitsTelecommunicationsPreamble

A method and system is provided for splitting a print job into its preamble and at least one chunk. The splitter maintains a collection of RIP node addresses to which chunks of the job currently being split have already been sent. When a new chunk is about to be sent, the splitter checks whether each RIP node address has already received a chunk. If the RIP node has not already received a chunk, the splitter sends the preamble as well as the chunk to an available RIP associated with the RIP node. If, however, the RIP node address has already received a chunk, only the portion of the chunk after the preamble is sent to an available RIP associated with the RIP node and communicate the location of the preamble to the available RIP node. The preamble may contain common content for each job.

Owner:XEROX CORP

Charge pump circuit suitable for low-voltage process

InactiveUS20050146375A1High pumping gainReliability issueRead-only memoriesApparatus without intermediate ac conversionCMOSIntegrated circuit

The present invention discloses a charge pump circuit suitable for a low-voltage process. The charge pump circuit is composed of stages of the voltage amplifying circuits connected each other, and the operation of two adjacent stages of voltage amplifying circuit is controlled by two opposite set of the timing signals. Each stage of the voltage amplifying circuit has a coupled pair of a first complementary MOS (CMOS) transistor and a second CMOS transistor switching in accordance with a timing signal and an inverse timing signal inputted into the first and second capacitors. Then, two diode devices guide charges to next stage, and a voltage higher than the integrated circuit voltage source is outputted. The present invention has advantage of high pumping gain, and the reliability issue of the gate oxide layer in the low-voltage process can be also solved.

Owner:NAT CHIAO TUNG UNIV

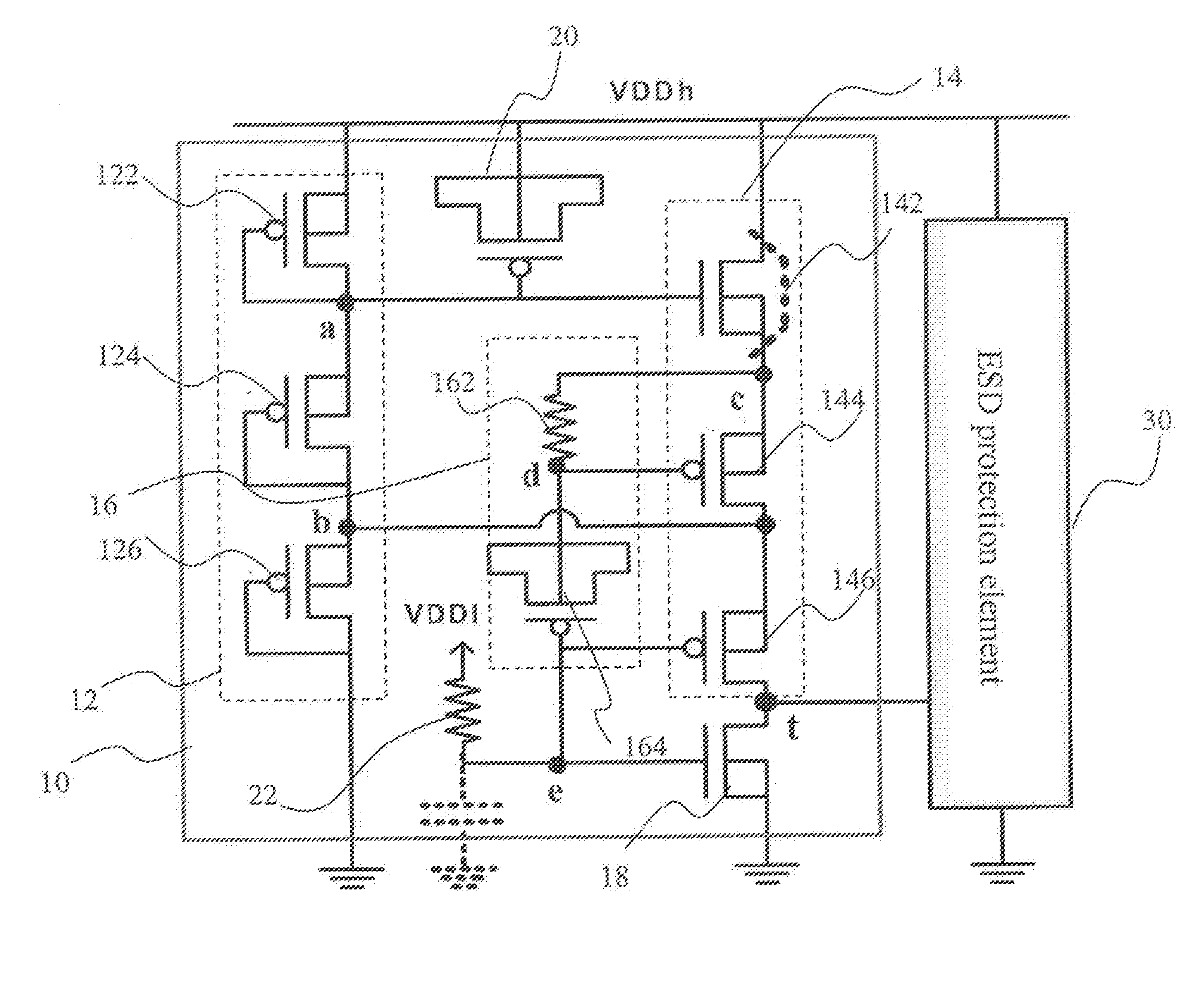

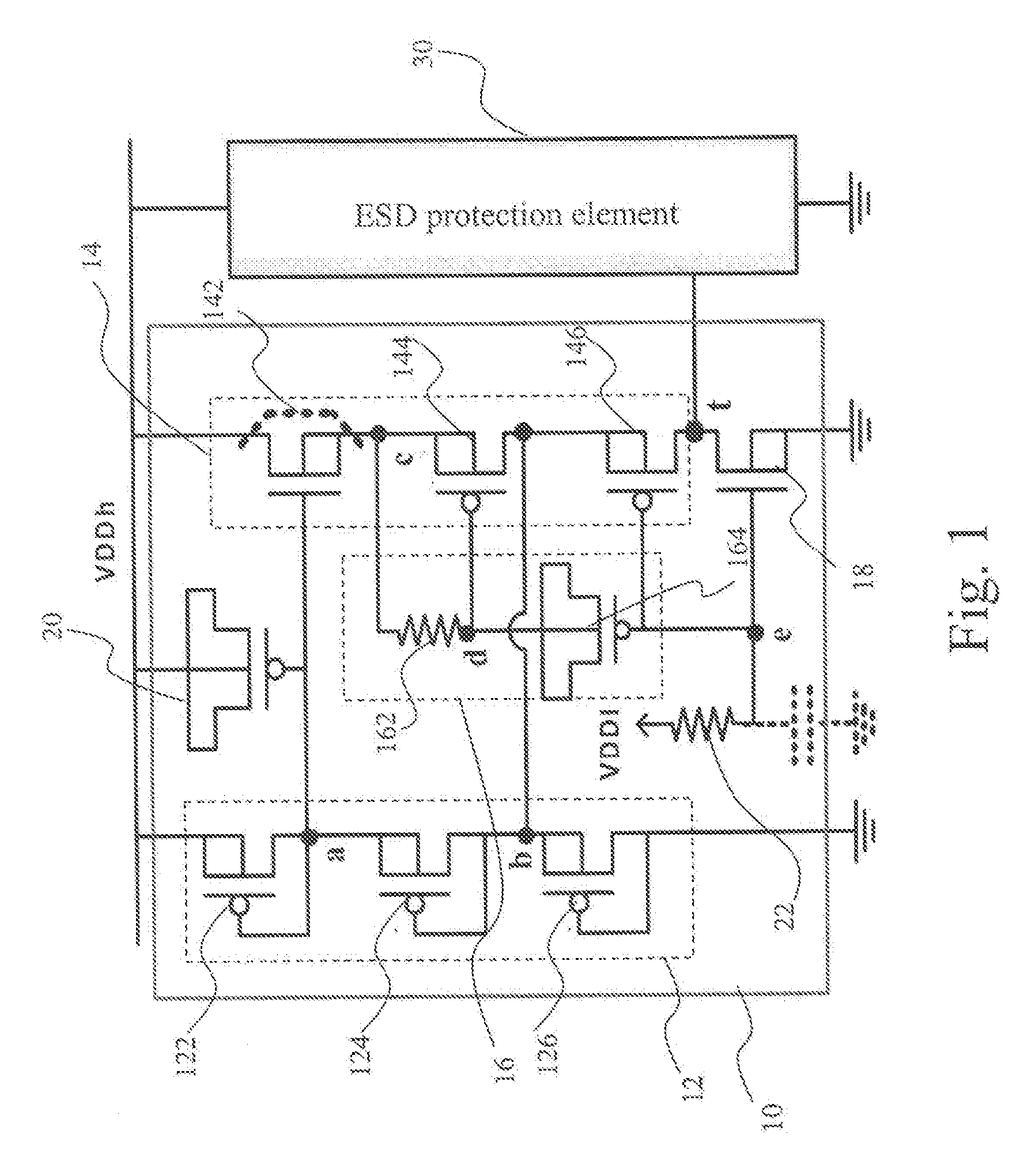

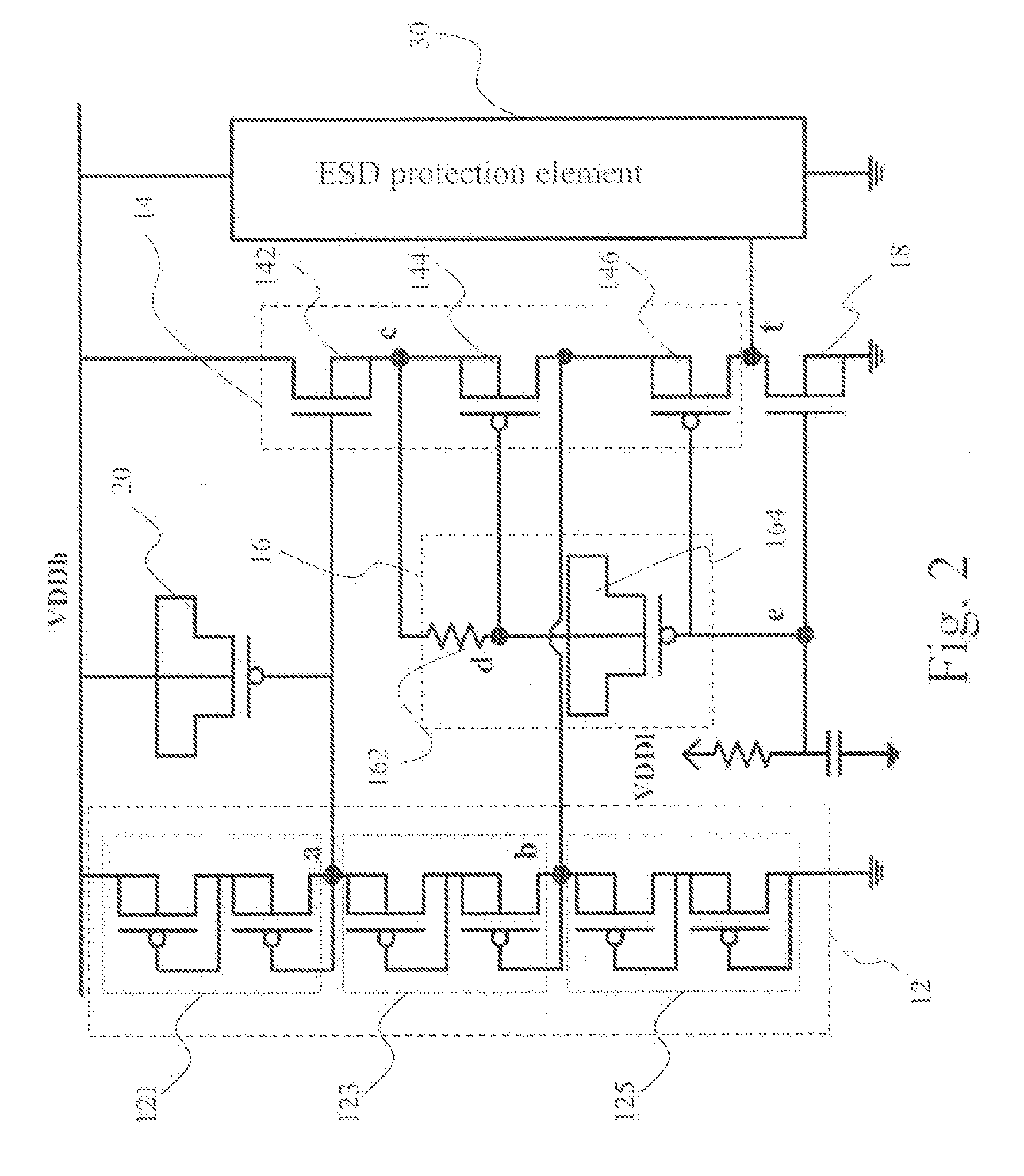

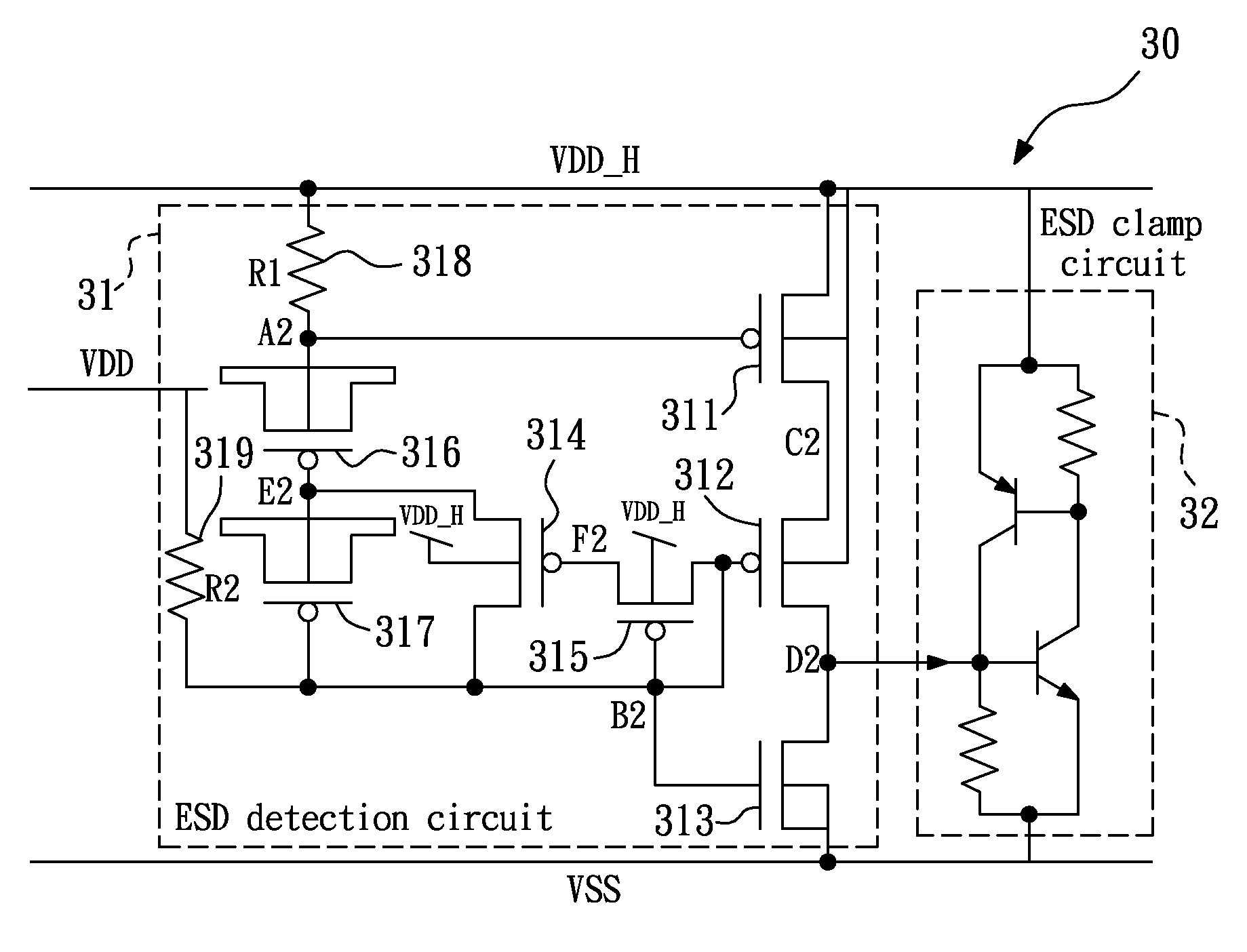

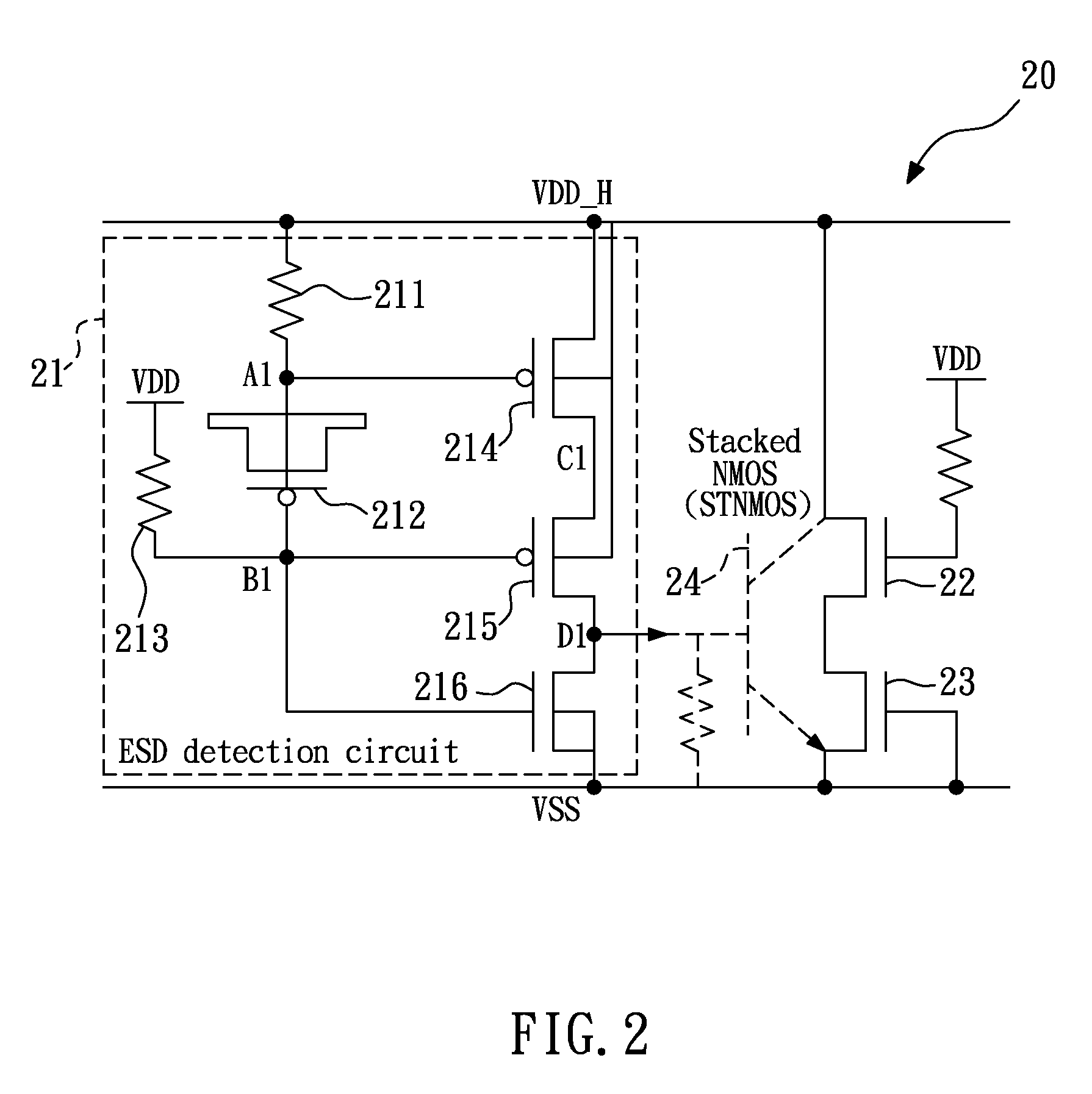

High-voltage tolerant power-rail ESD clamp circuit

ActiveUS20070230073A1Reliability issueIncrease speedTransistorEmergency protective arrangements for limiting excess voltage/currentEngineeringCost effectiveness

A high-voltage tolerant power-rail ESD clamp circuit is proposed, in which circuit devices can safely operate under the high power supply voltage that is three times larger than their process limitation without gate-oxide reliability issue. Moreover, an ESD detection circuit is used to effectively improve the whole ESD protection function by substrate-triggered technique. Because only low voltage (1*VDD) devices are used to achieve the object of high voltage (3*VDD) tolerance, the proposed design provides a cost effective power-rail ESD protection solution to chips with mixed-voltage interfaces.

Owner:NATIONAL CHIAO TUNG UNIVERSITY

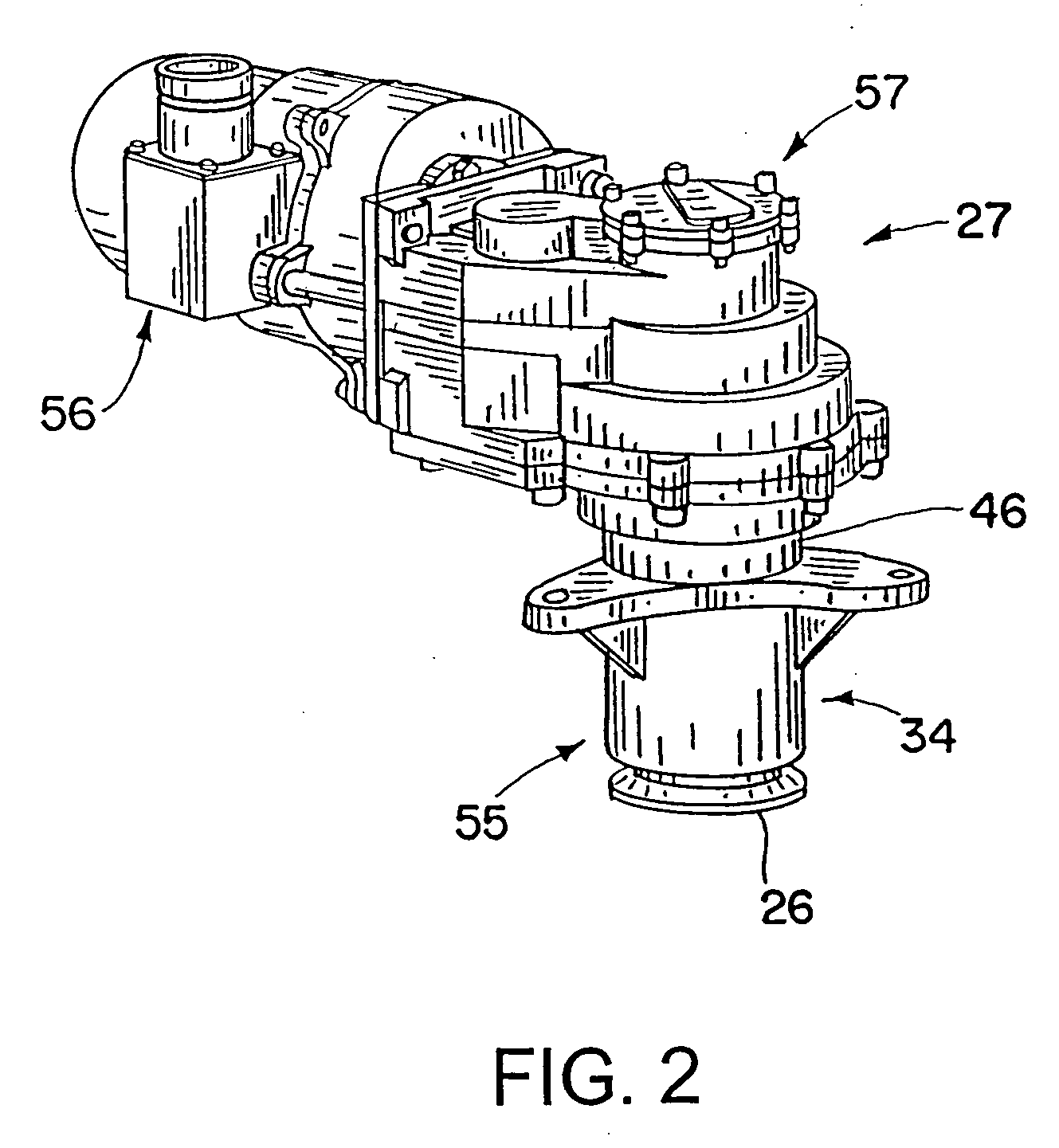

Stall controller and triggering condition control features for a wind turbine

InactiveUS7420288B2Increase torqueCost issueAC motor controlWind motor controlPartial lossControl theory

Control features for a wind turbine that control the turbine over a range of wind speeds and under triggering conditions with reduced noise, cost, and reliability issues associated with other such controls. Control is accomplished via control electronics, which adjust the torque produced by the electrical output generation device (e.g., alternator) within the wind turbine. During normal operation, torque is adjusted for optimum aerodynamic performance and maximum output of power. In winds above rated power, the control circuit regulates torque to lower aerodynamic performance, as necessary to maintain desired power level output. In triggering conditions, such as during simultaneous control circuit failure and loss of some portion of the electrical output generation device in extreme winds, wind turbine control is accomplished by increasing torque (e.g., via a separate controller) from the electrical output generation device via shorting of windings, so as to cause retardation of blade rotation.

Owner:WIND RESOURCE LLC

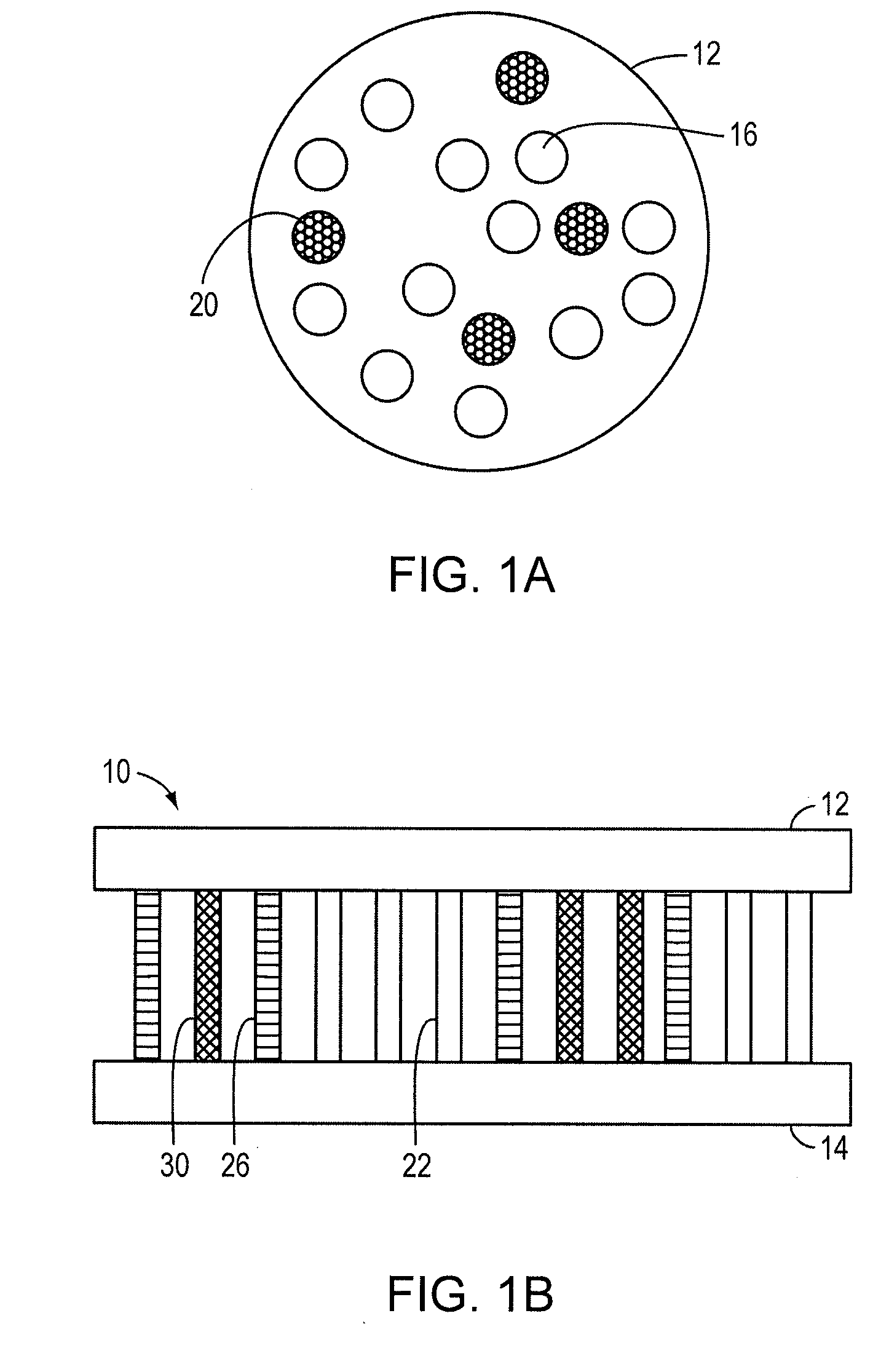

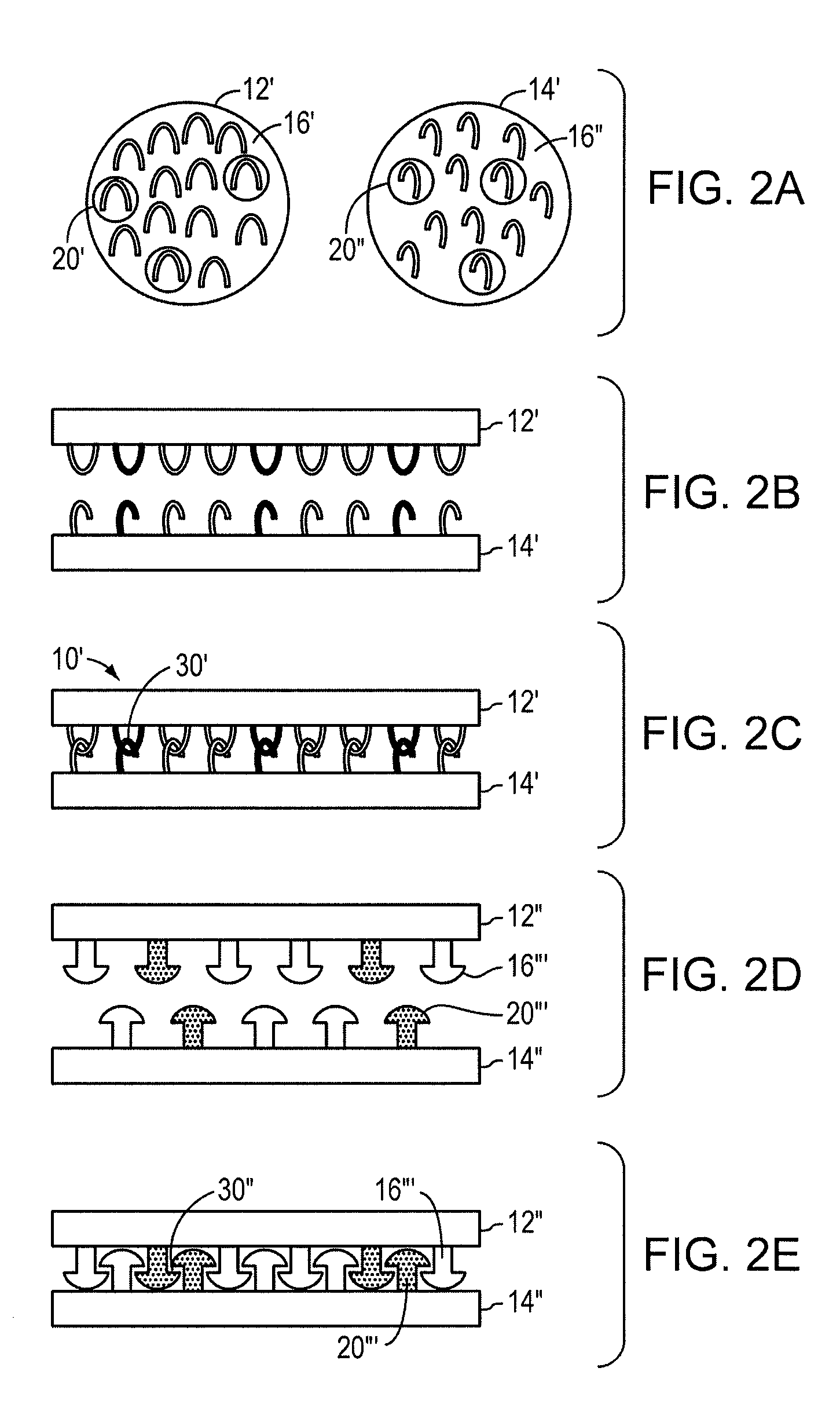

Intelligent, universal, reconfigurable electromechanical interface for modular systems assembly

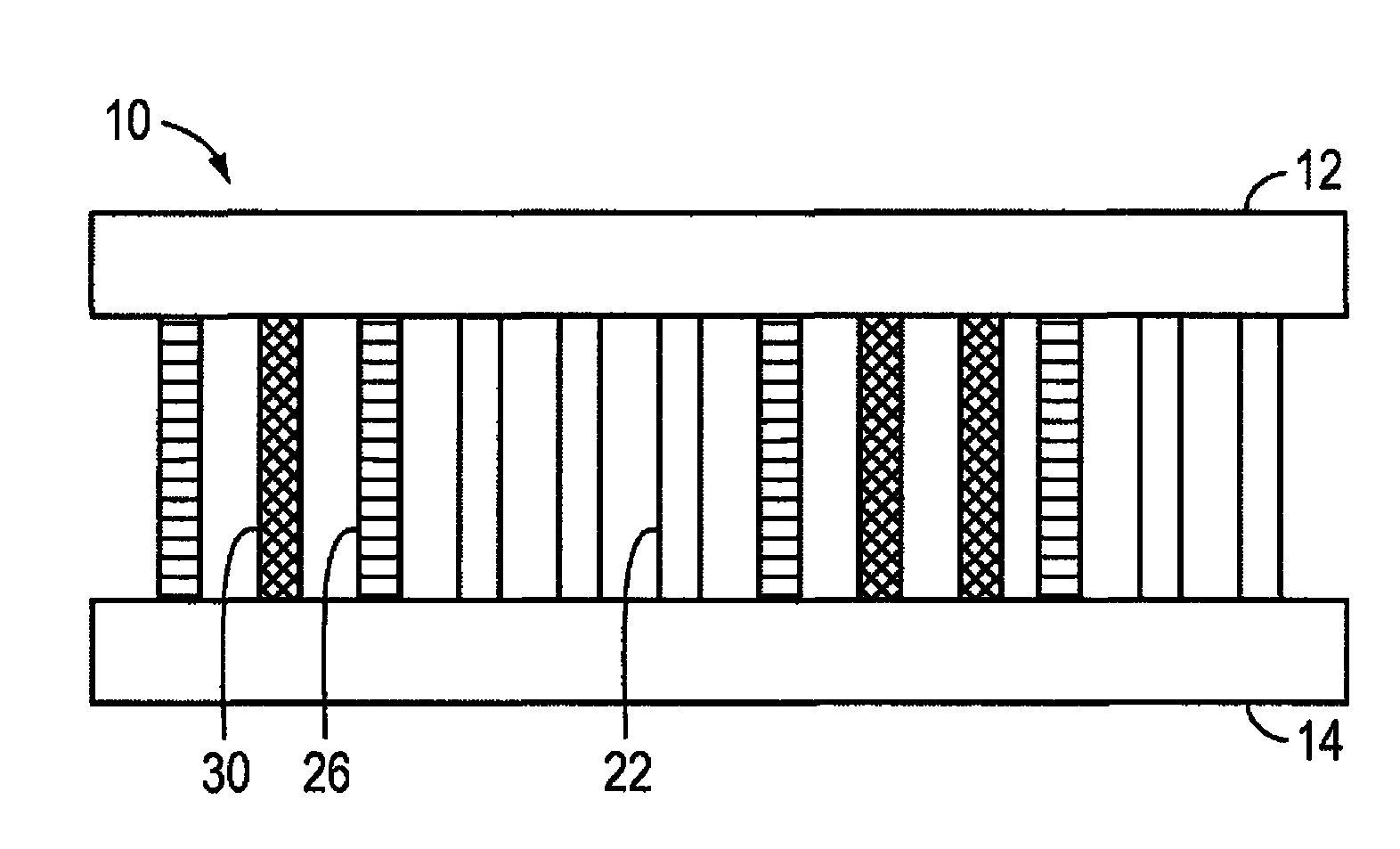

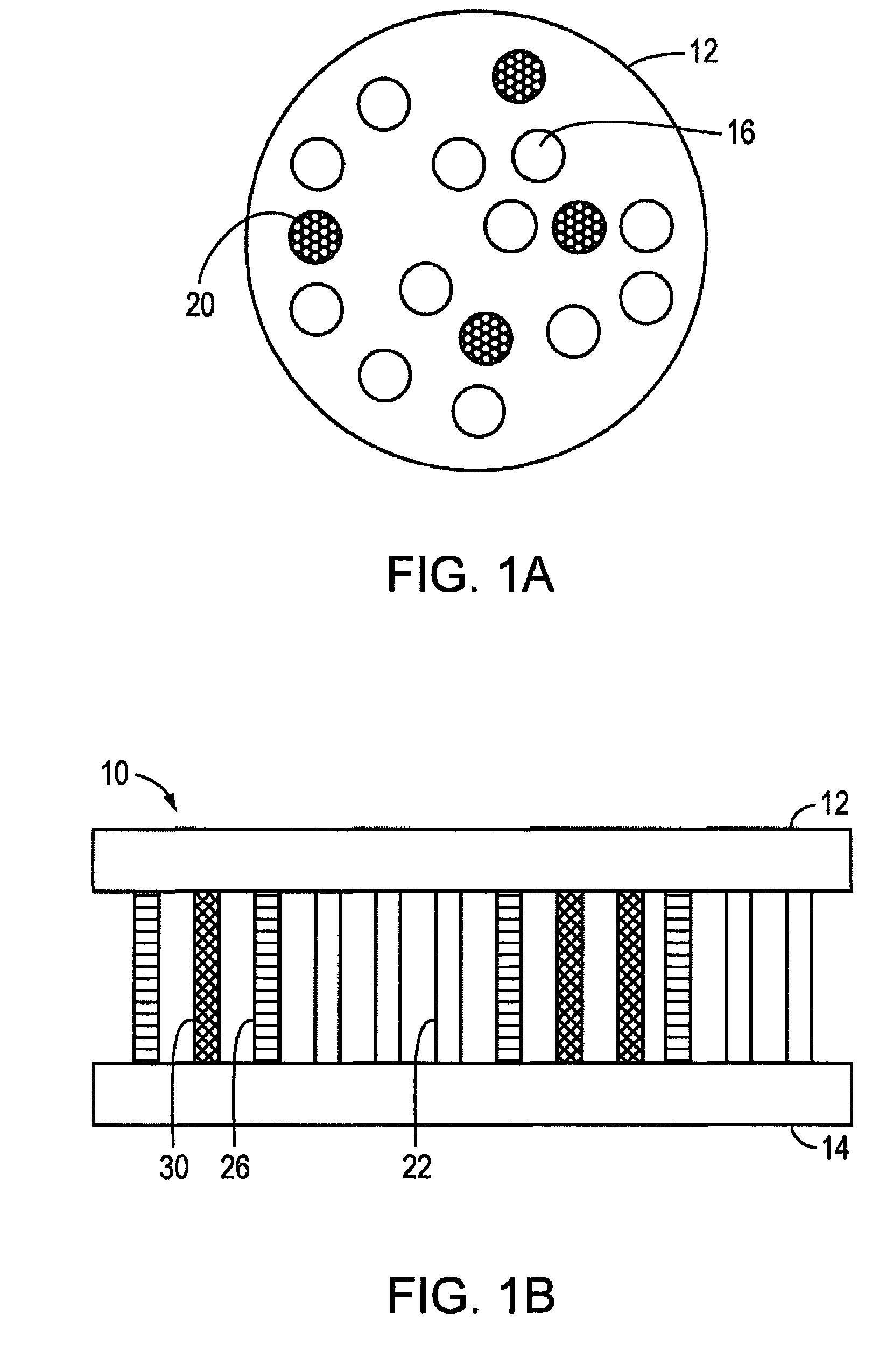

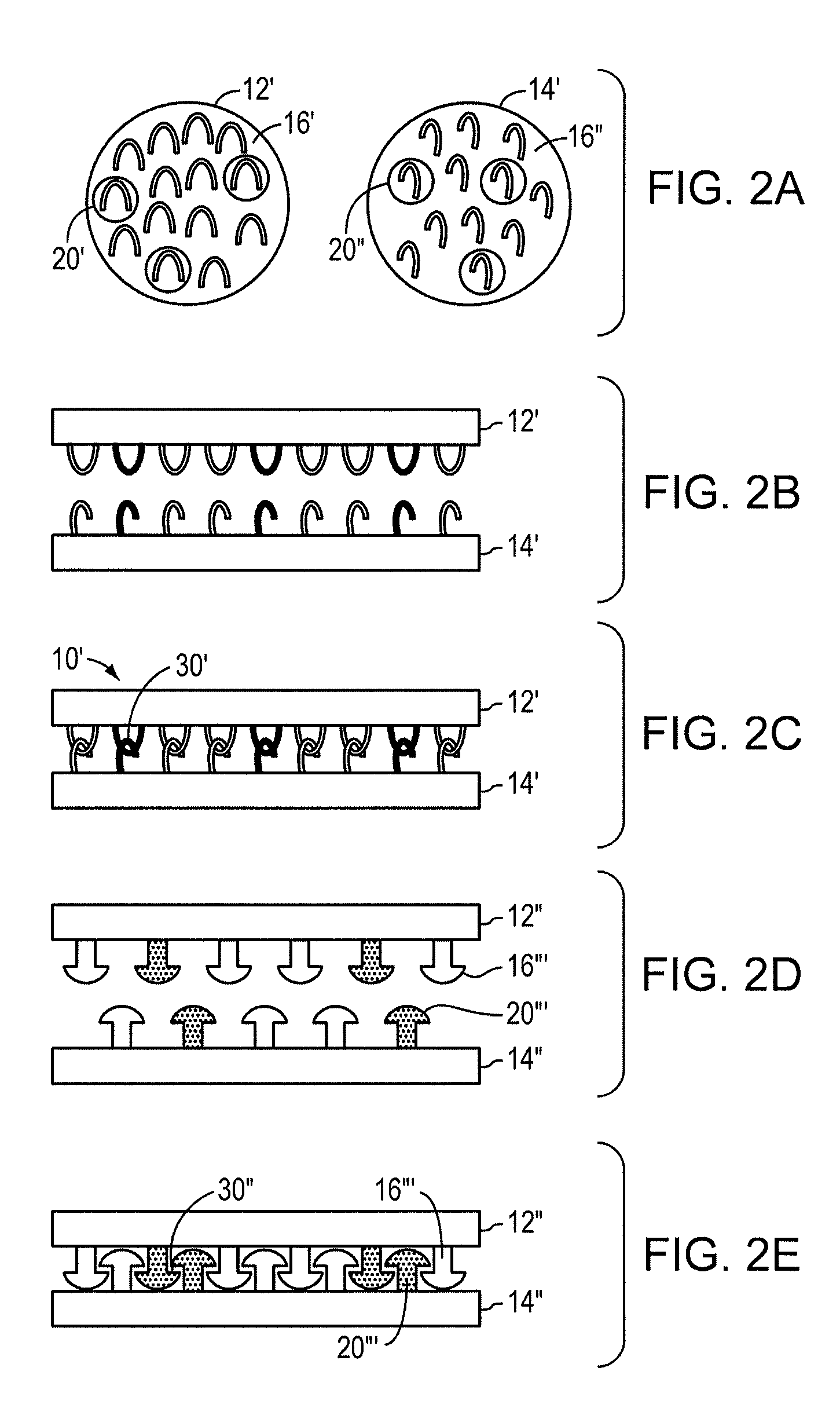

InactiveUS20080233768A1Reduce needReduce weightCoupling device connectionsBus-bar/wiring layoutsElectrical conductorModularity

An electromechanical connection includes a first conductor disposed in a first non-conductive array and a second conductor disposed in a second non-conductive array capable of mating with the first non-conductive array. The second conductor is capable of mating with the first conductor when the first non-conductive array and the second non-conductive array are mated. A processor associated with the first non-conductive array determines if an electrical connection is formed between the first conductor and the second conductor. The processor can assign a function to the electrical connection.

Owner:PHYSICAL SCI

Electrostatic discharge protecting circuit with ultra-low standby leakage current for twice supply voltage tolerance

InactiveUS20110026175A1High ESD robustnessEffective protectionTransistorSolid-state devicesNanometer cmosPower flow

The invention relates to an electrostatic discharge protecting circuit with ultra-low standby leakage current for twice supply voltage tolerance. The electrostatic discharge protecting circuit of the invention includes a substrate driver, a third transistor, a start-up circuit, a RC circuit and a second resistor. The substrate driver has a first transistor and a second transistor in serious connection. The start-up circuit has a fourth transistor and a fifth transistor with diode-connected. The RC circuit has a first resistor, a sixth transistor and a seventh transistor in serious connection. Compared with the prior art, the electrostatic discharge protecting circuit with ultra-low standby leakage current for twice supply voltage tolerance of the invention with advantages of low standby leakage current, high ESD robustness, and no gate-oxide reliability issue is an excellent circuit solution for on-chip ESD protection design for mixed-voltage I / O buffers in nanometer CMOS technologies.

Owner:NAT SUN YAT SEN UNIV

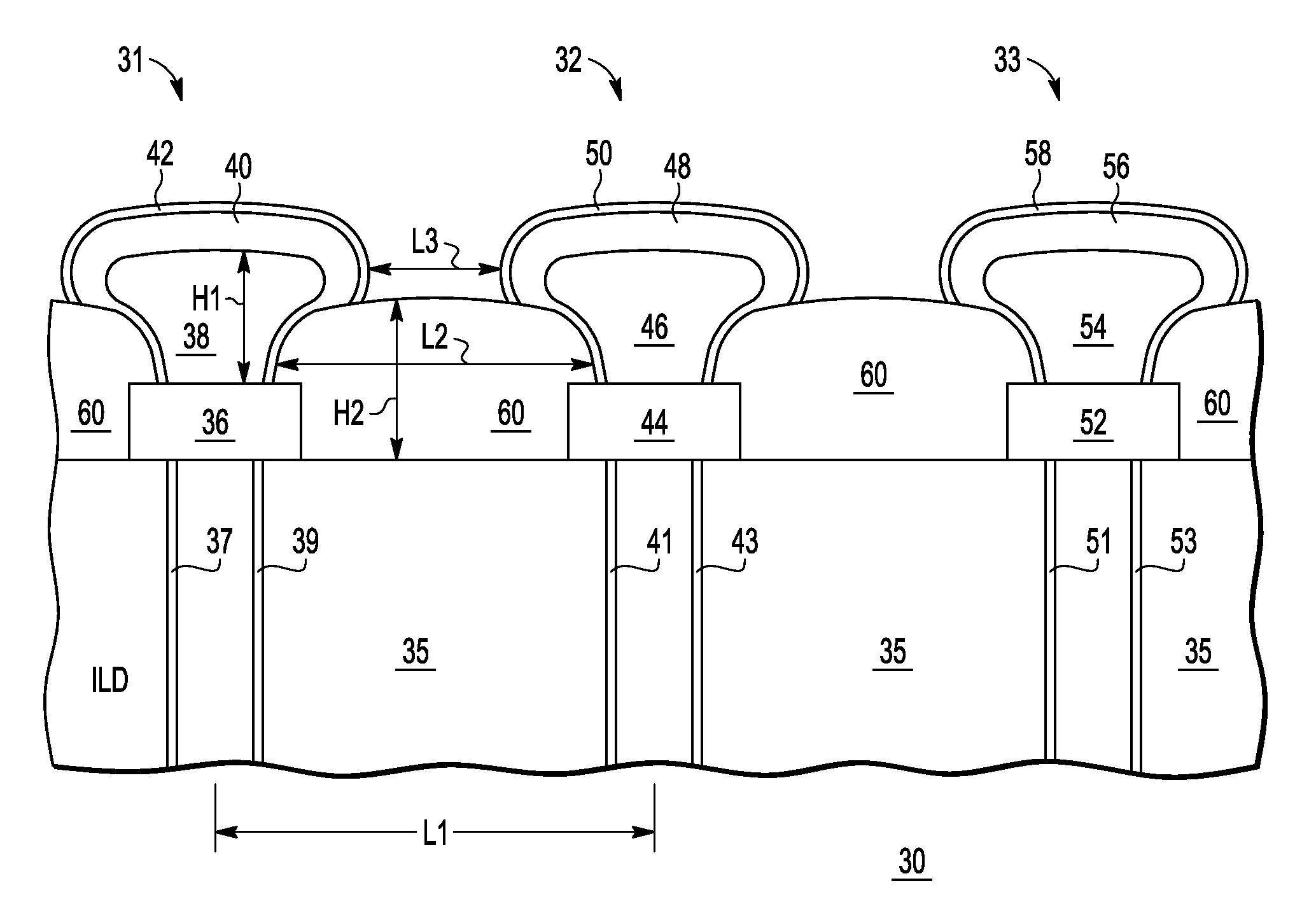

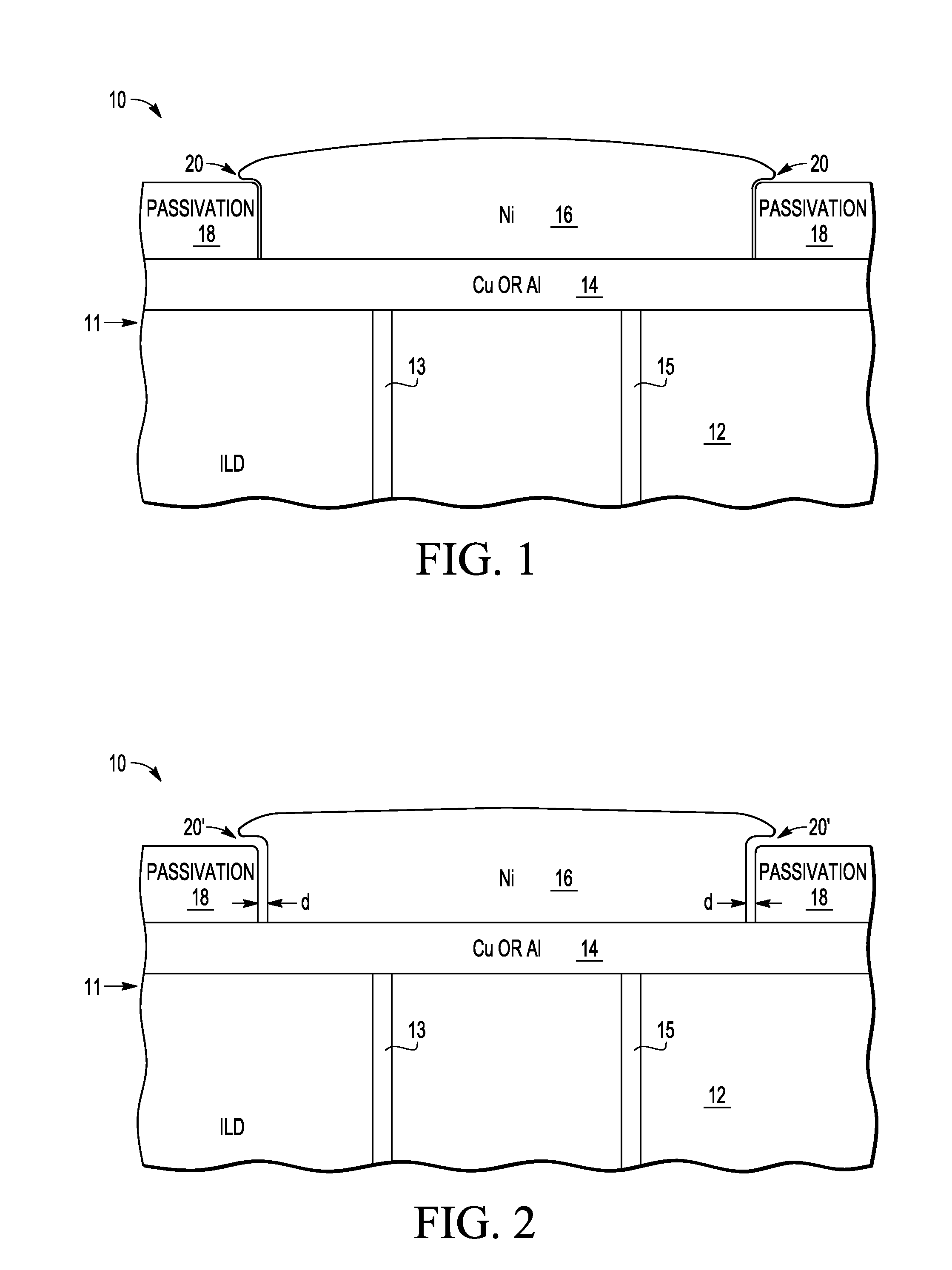

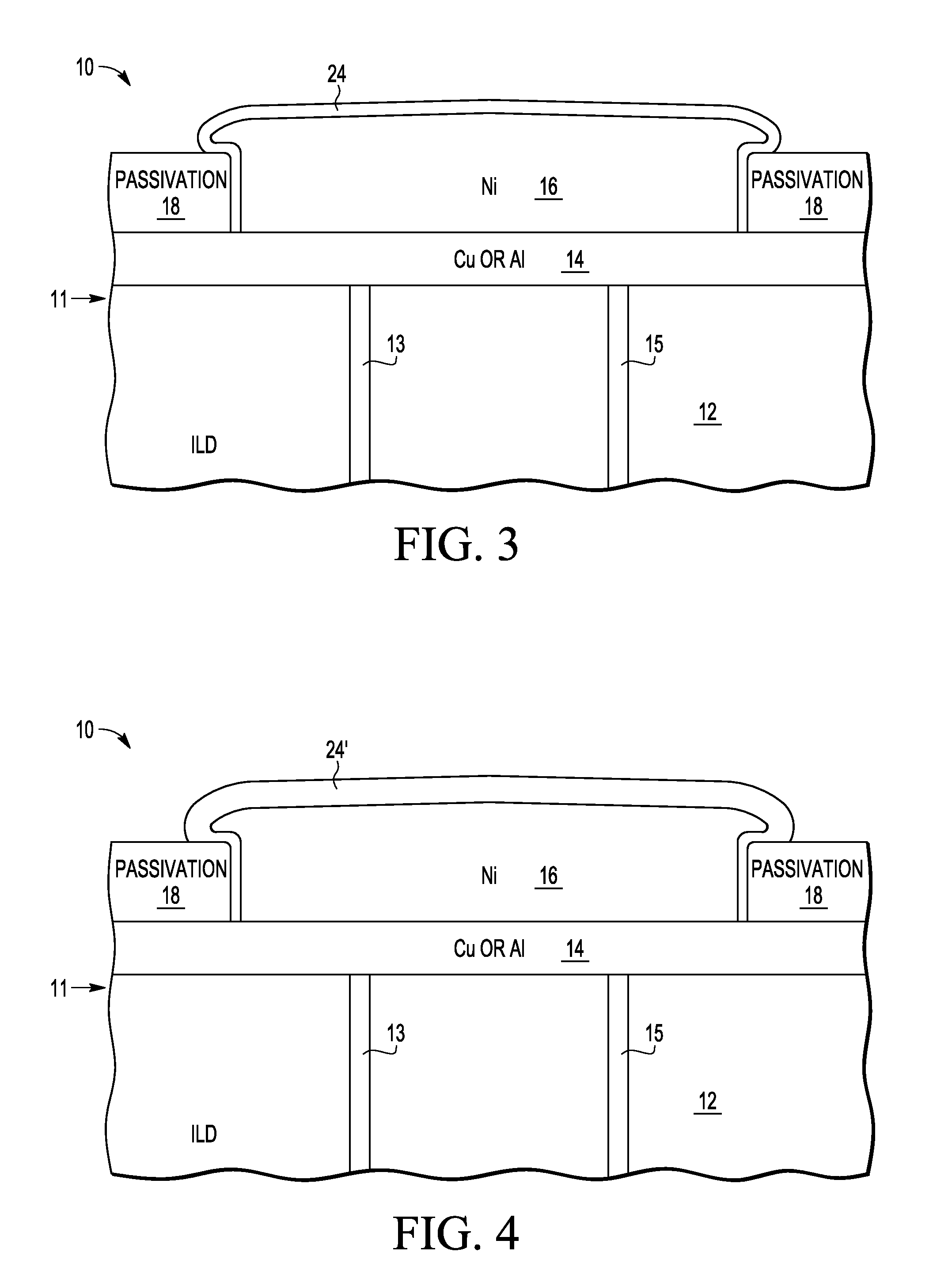

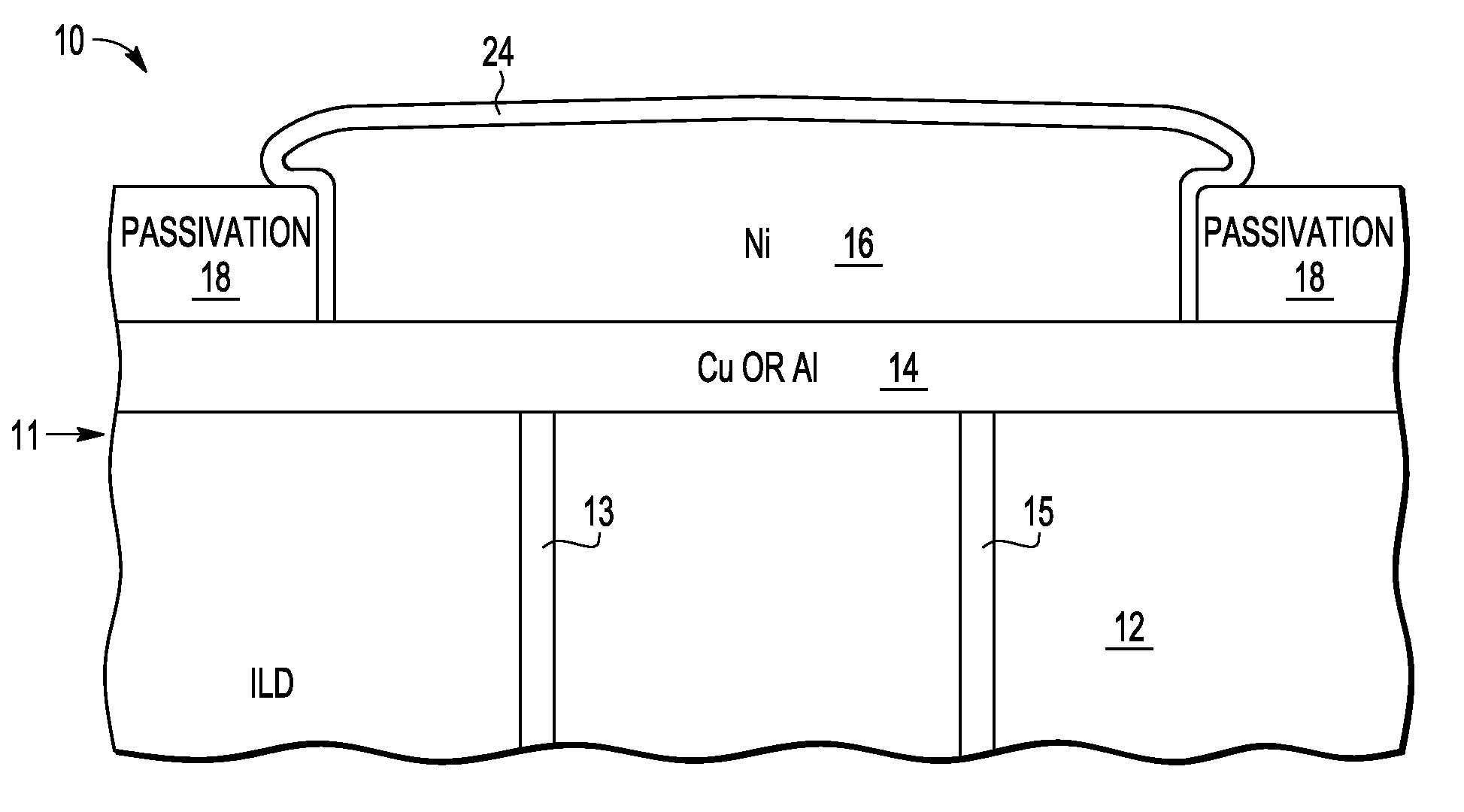

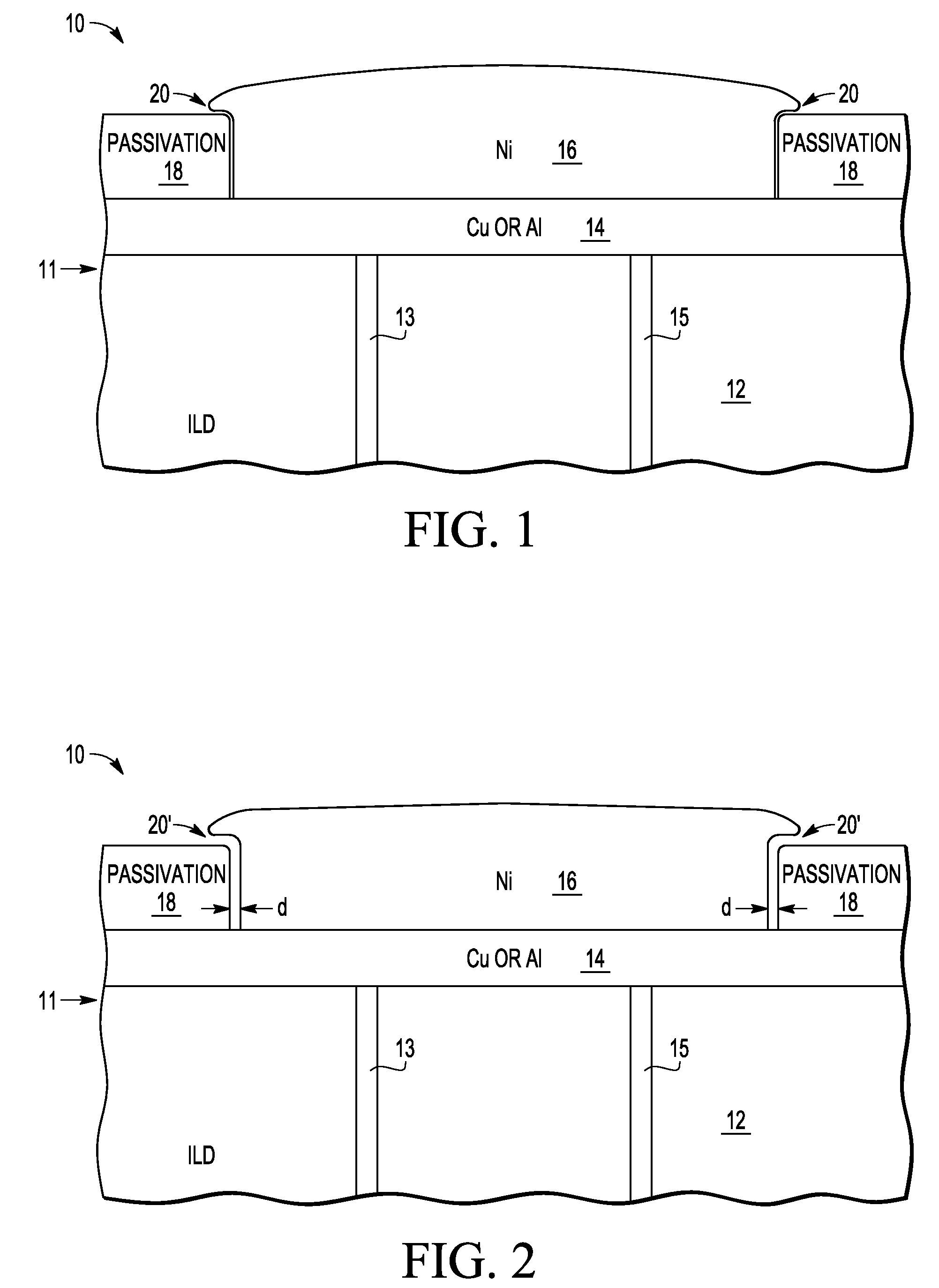

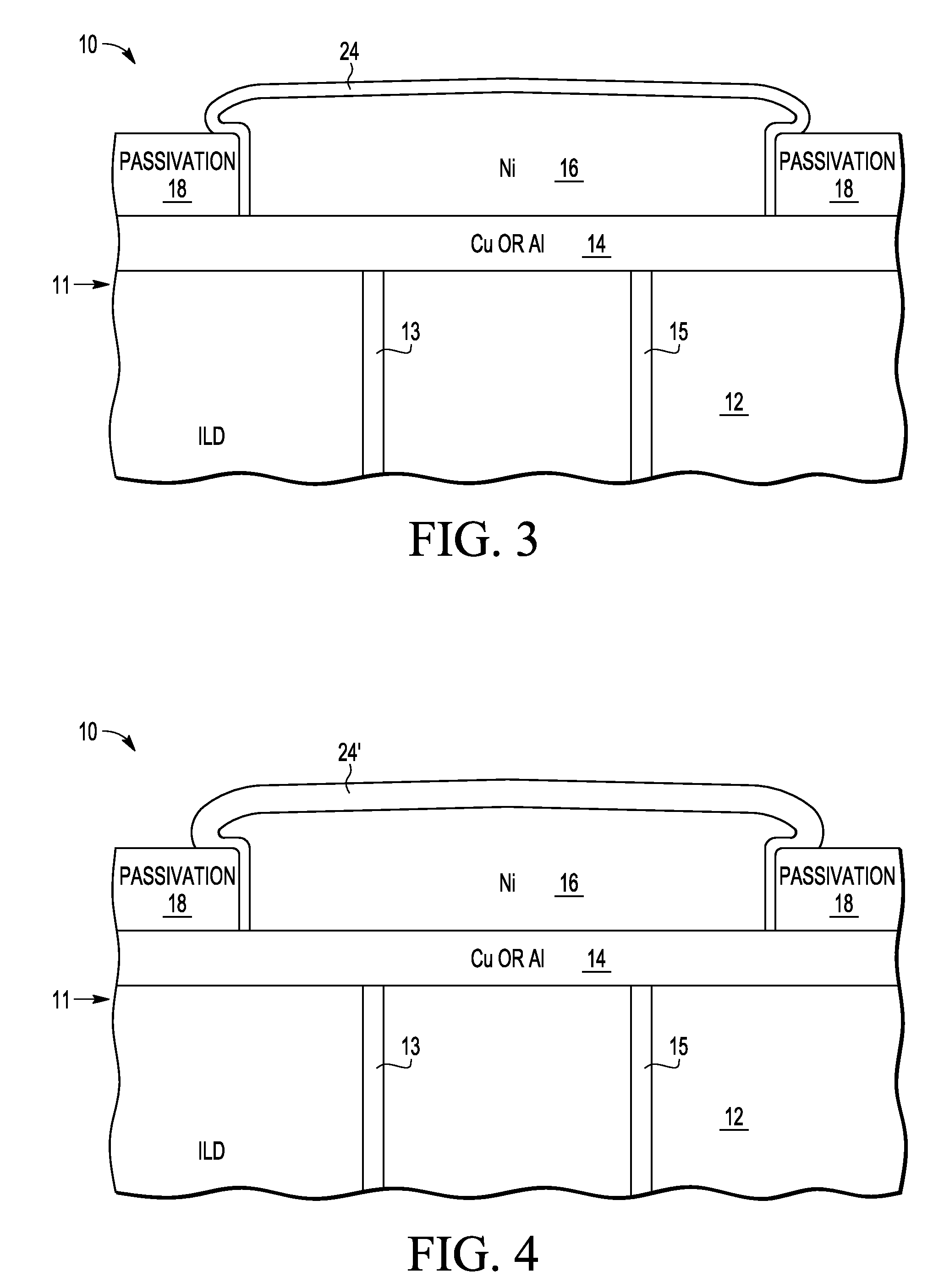

Bond pad with multiple layer over pad metallization and method of formation

ActiveUS20110198751A1Reliability issueSemiconductor/solid-state device detailsSolid-state devicesPalladiumSemiconductor

A semiconductor device structure has a semiconductor die that has a bond pad with a passivation layer surrounding a portion of the bond pad. A nickel layer, which is deposited, is on the inner portion. A space is between a sidewall of the nickel layer and the passivation layer and extends to the bond pad. A palladium layer is over the nickel layer and fills the space. The space is initially quite small but is widened by an isotropic etch so that when the palladium layer is deposited, the space is sufficiently large so that the deposition of palladium is able to fill the space. Filling the space results in a structure in which the palladium contacts the nickel layer, the passivation layer and the bond pad.

Owner:NXP USA INC

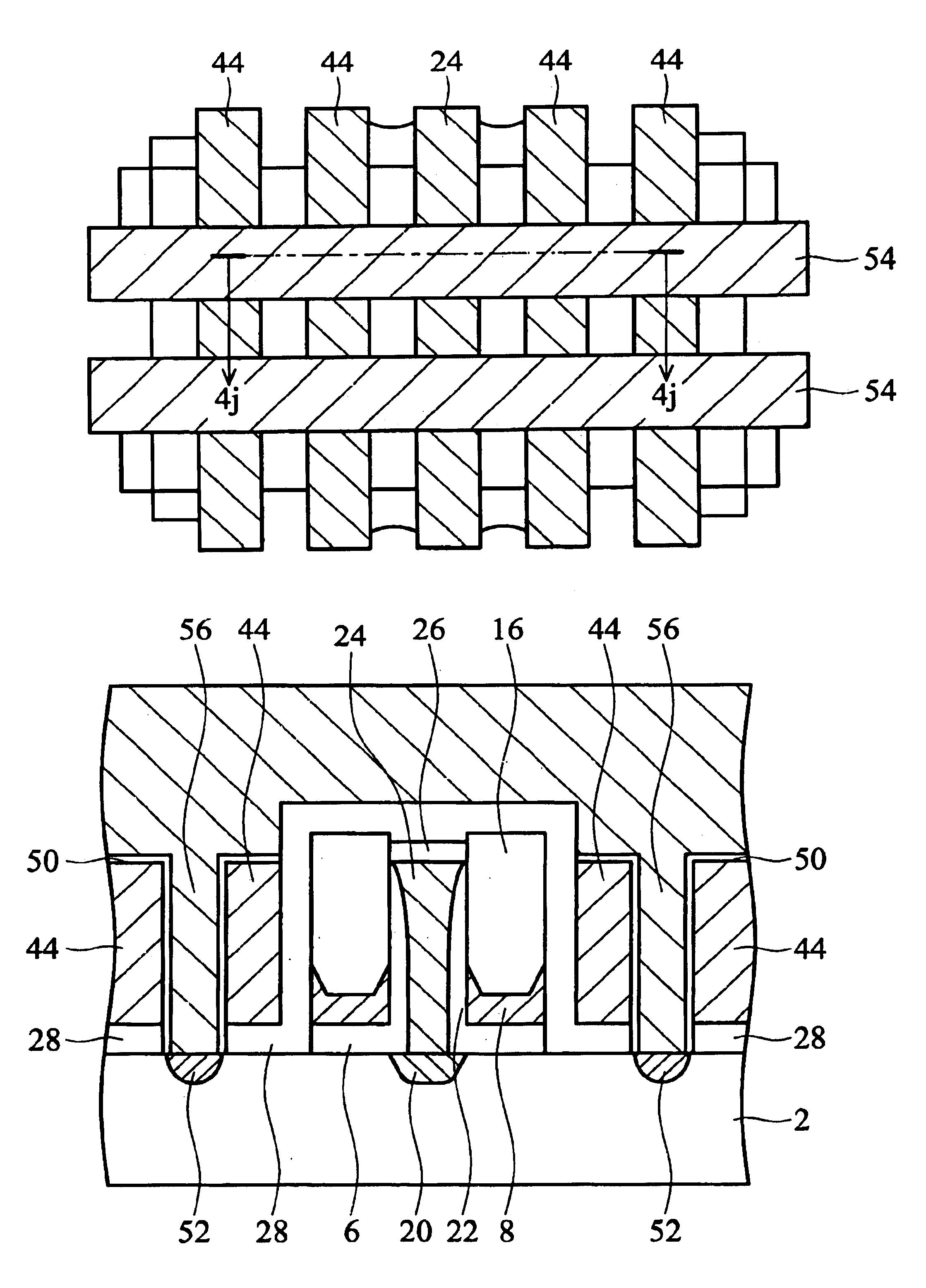

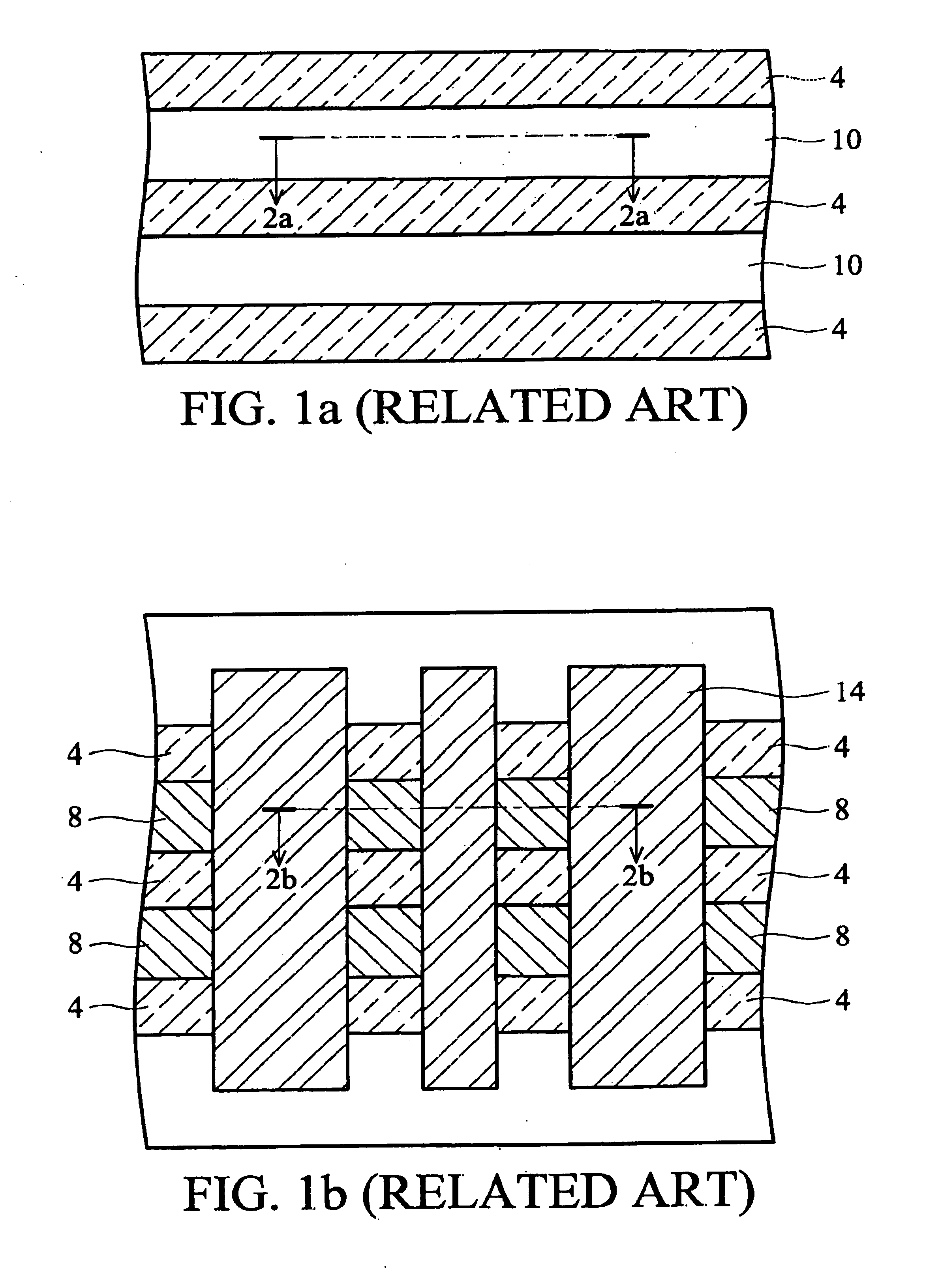

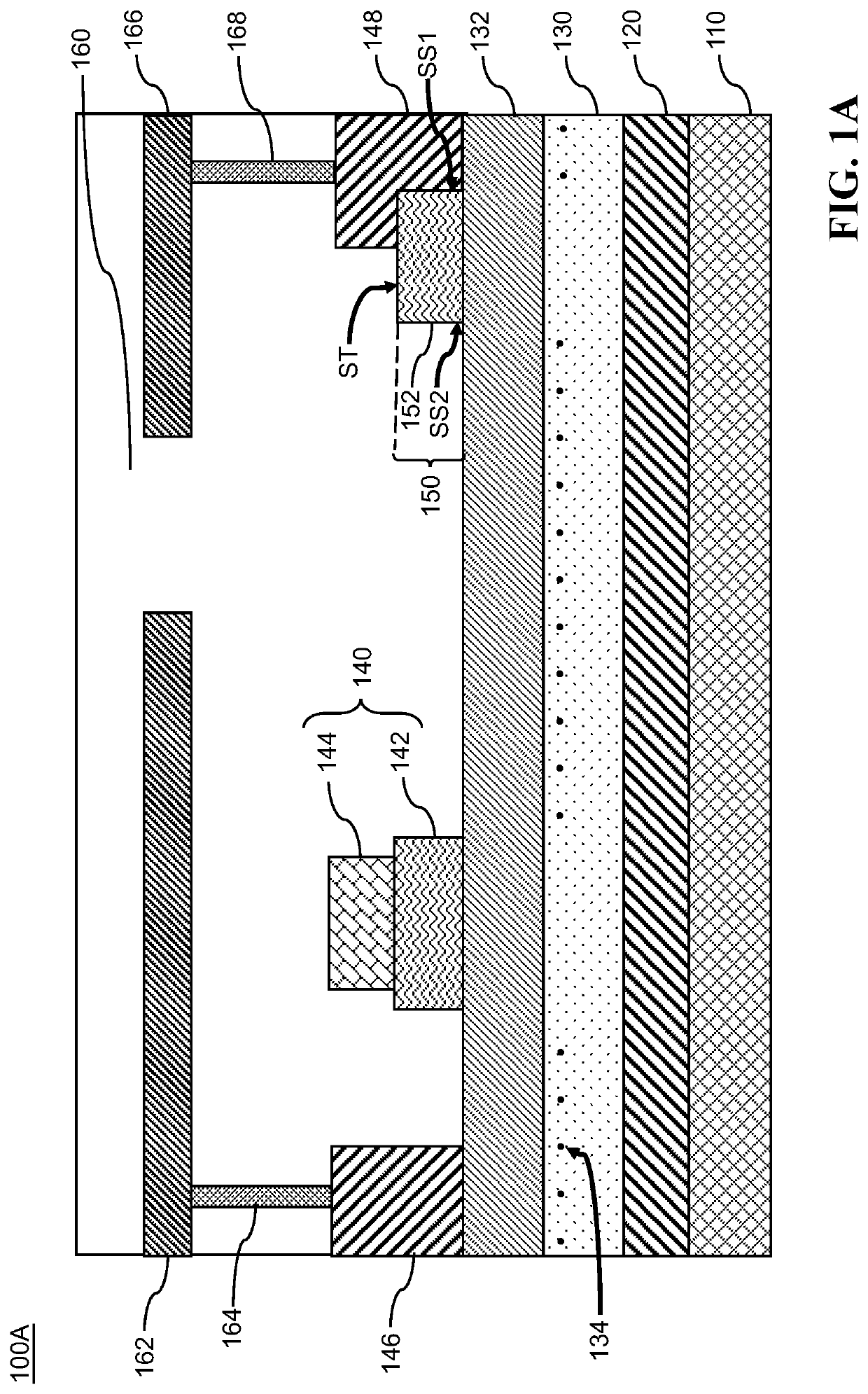

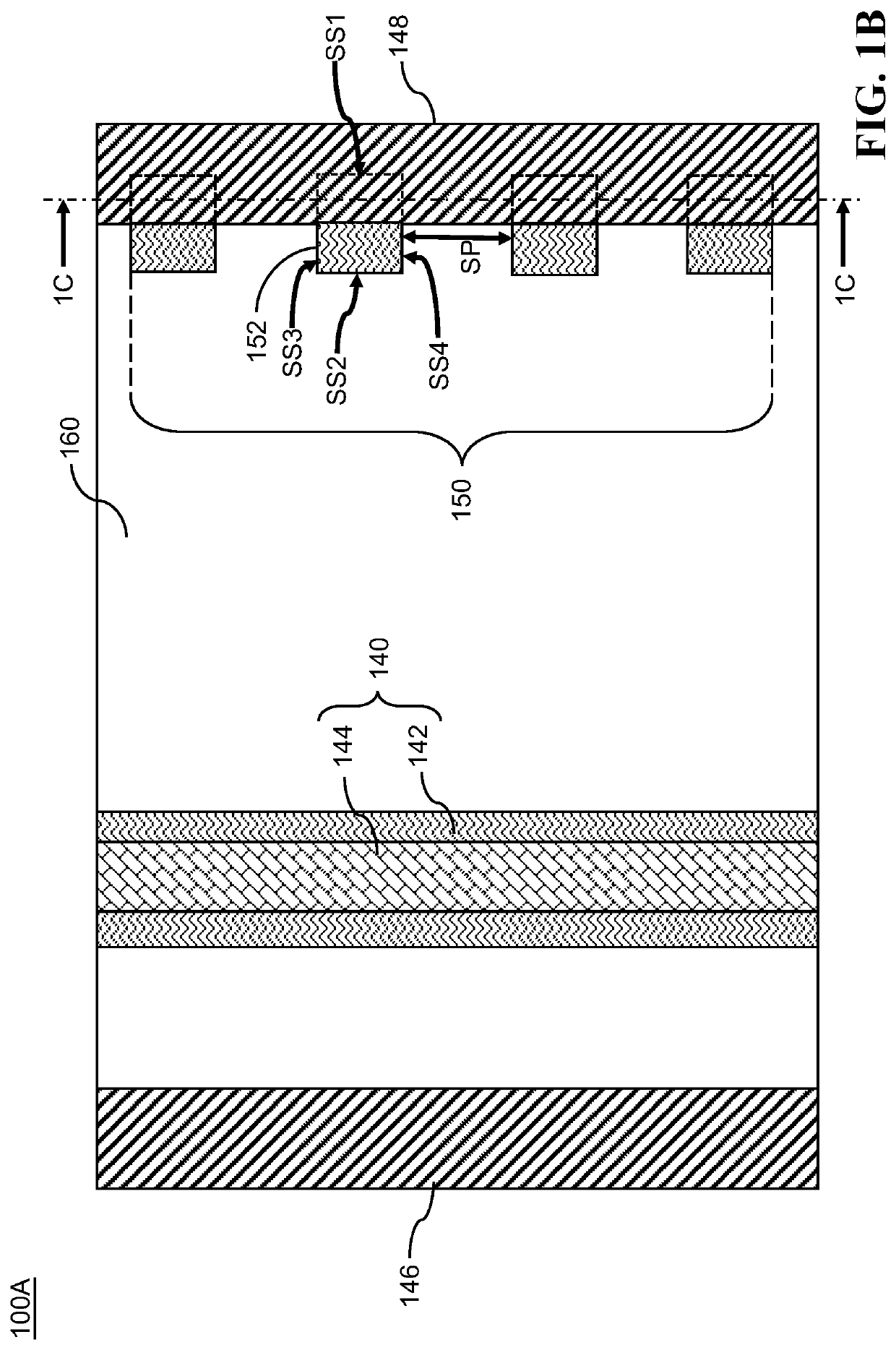

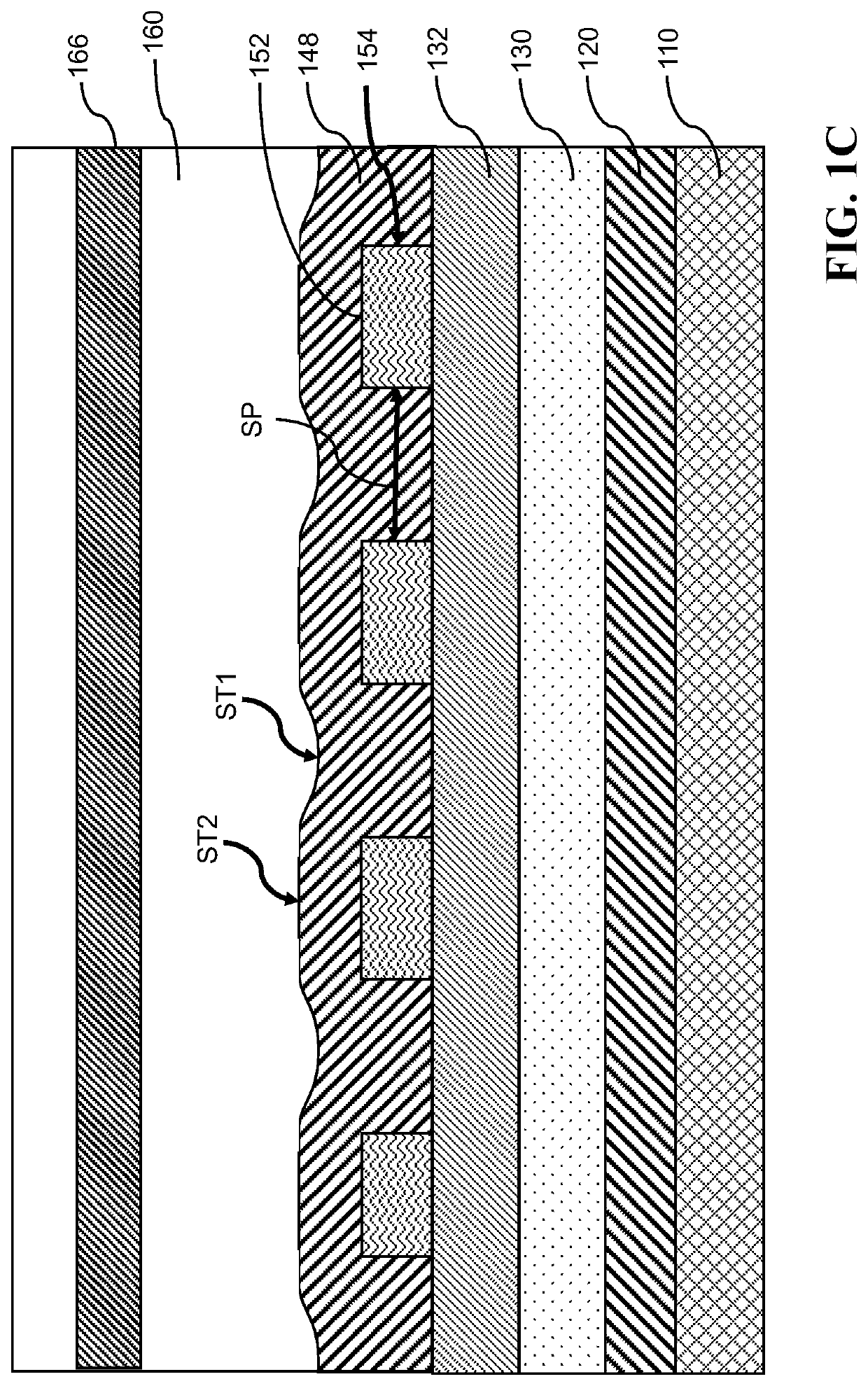

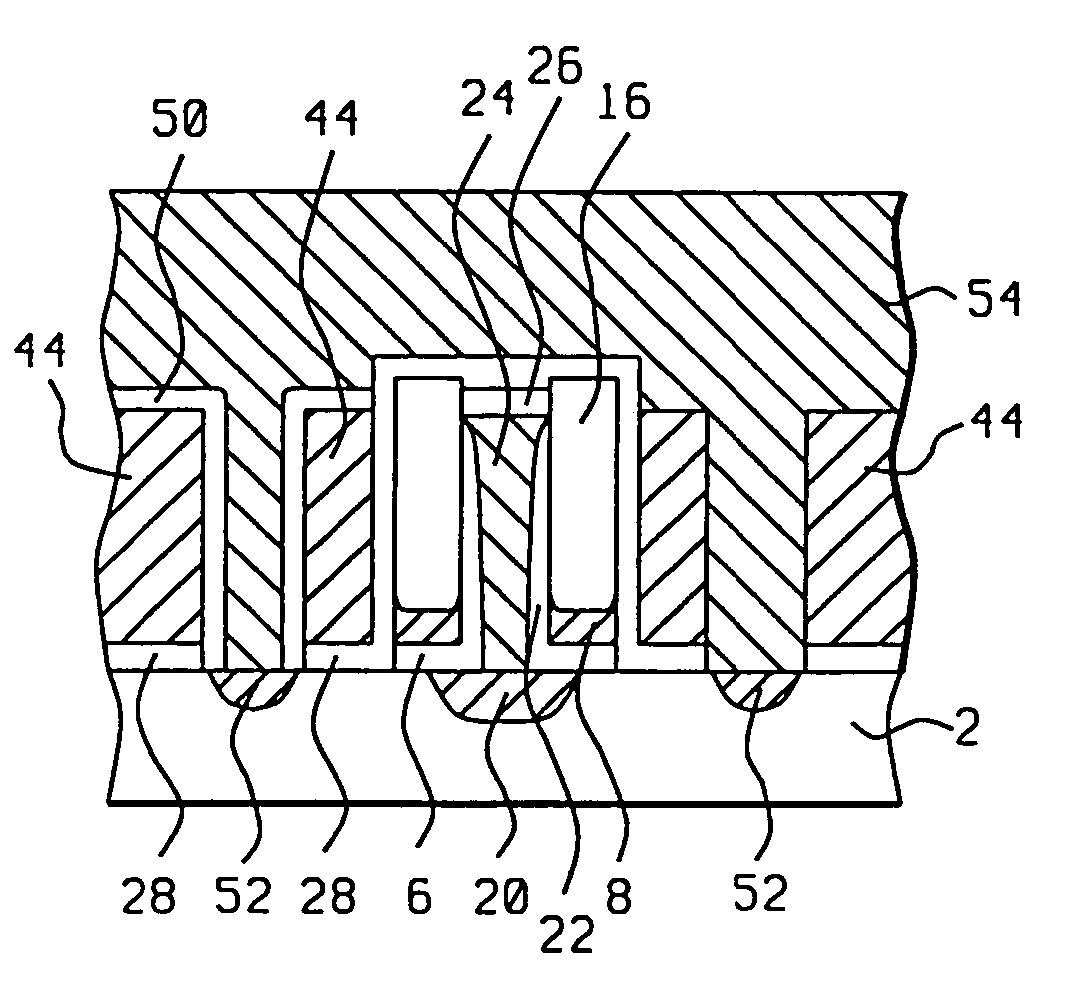

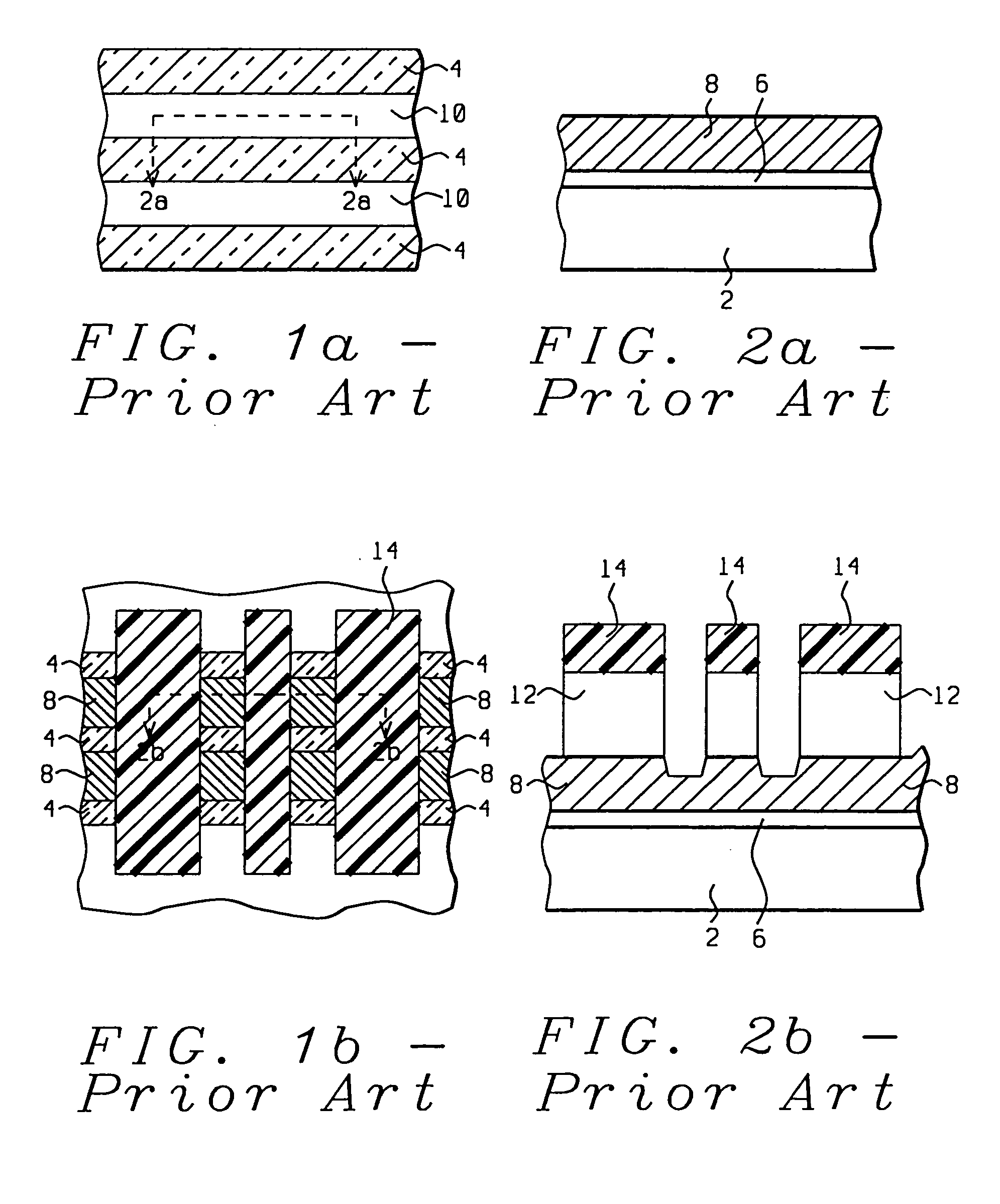

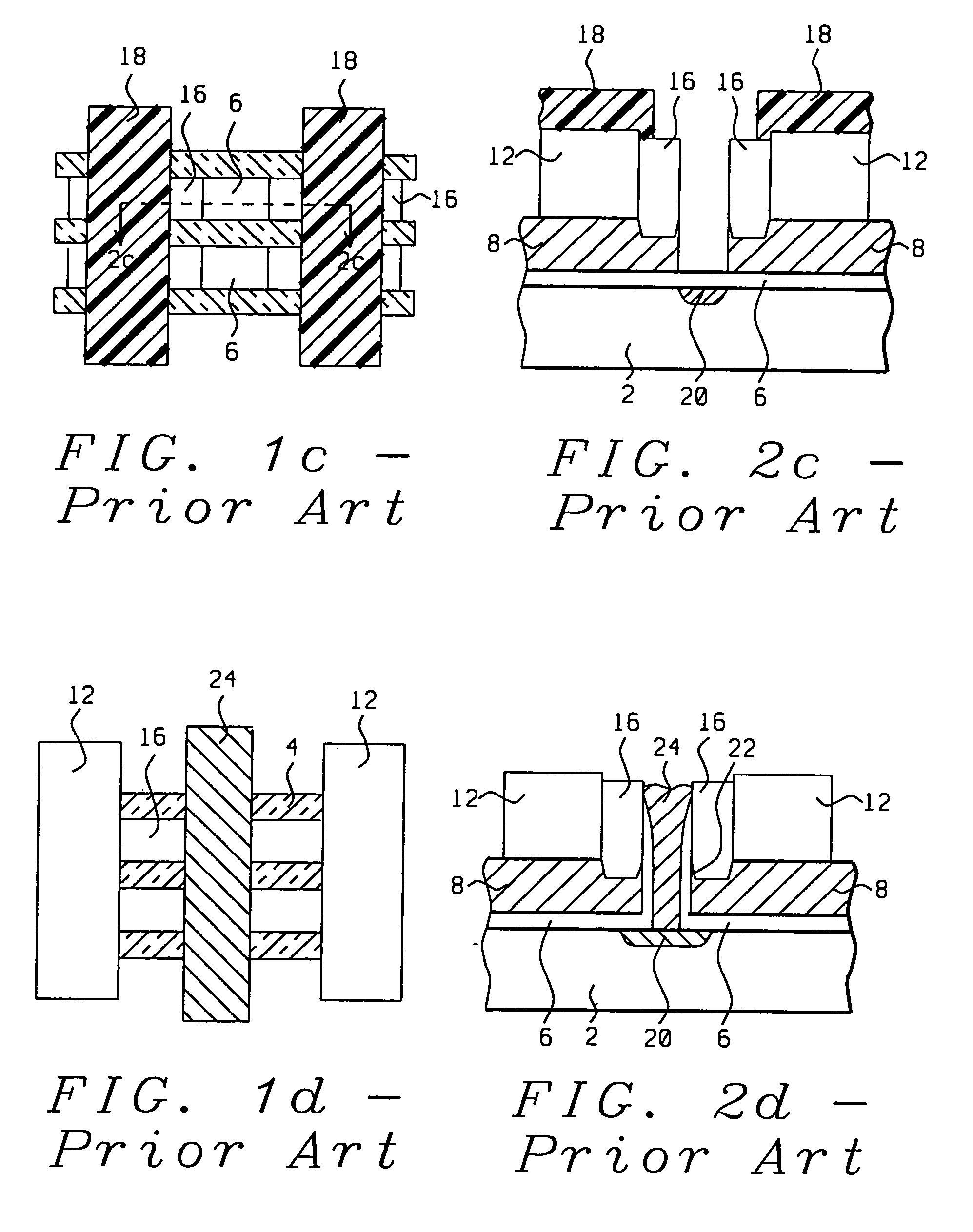

Structure and fabricating method with self-aligned bit line contact to word line in split gate flash

InactiveUS6858494B2Reduce areaIncrease widthSolid-state devicesSemiconductor/solid-state device manufacturingBit lineEngineering

A new structure is disclosed for semiconductor devices in which contact regions are self-aligned to conductive lines. Openings to a gate oxide layer, in partially fabricated devices on a silicon substrate, have insulating sidewalls. First polysilicon lines disposed against the insulating sidewalls extend from below the top of the openings to the gate oxide layer. Oxide layers are grown over the top and exposed sides of the first polysilicon lines serving to insulate the first polysilicon lines. Polysilicon contact regions are disposed directly over and connect to silicon substrate regions through openings in the gate oxide layer and fill the available volume of the openings. Second polysilicon lines connect to the contact regions and are disposed over the oxide layers grown on the first polysilicon lines.

Owner:TAIWAN SEMICON MFG CO LTD

Situation sensitive memory performance

ActiveUS7502921B2Avoid timeoutImprove programming speedEnergy efficient ICTVolume/mass flow measurementOperation modeComputer science

The present invention presents a non-volatile memory system that adapts its performance to one or more system related situation. If a situation occurs where the memory will require more than the allotted time for completing an operation, the memory can switch from its normal operating mode to a high performance mode in order to complete the operation quickly enough. Conversely, if a situation arises where reliability could be an issue (such as partial page programming), the controller could switch to a high reliability mode. In either case, once the trigging system situation has returned to normal, the memory reverts to the normal operation. The detection of such situations can be used both for programming and data relocation operations. An exemplary embodiment is based on firmware programmable performance.

Owner:SANDISK TECH LLC

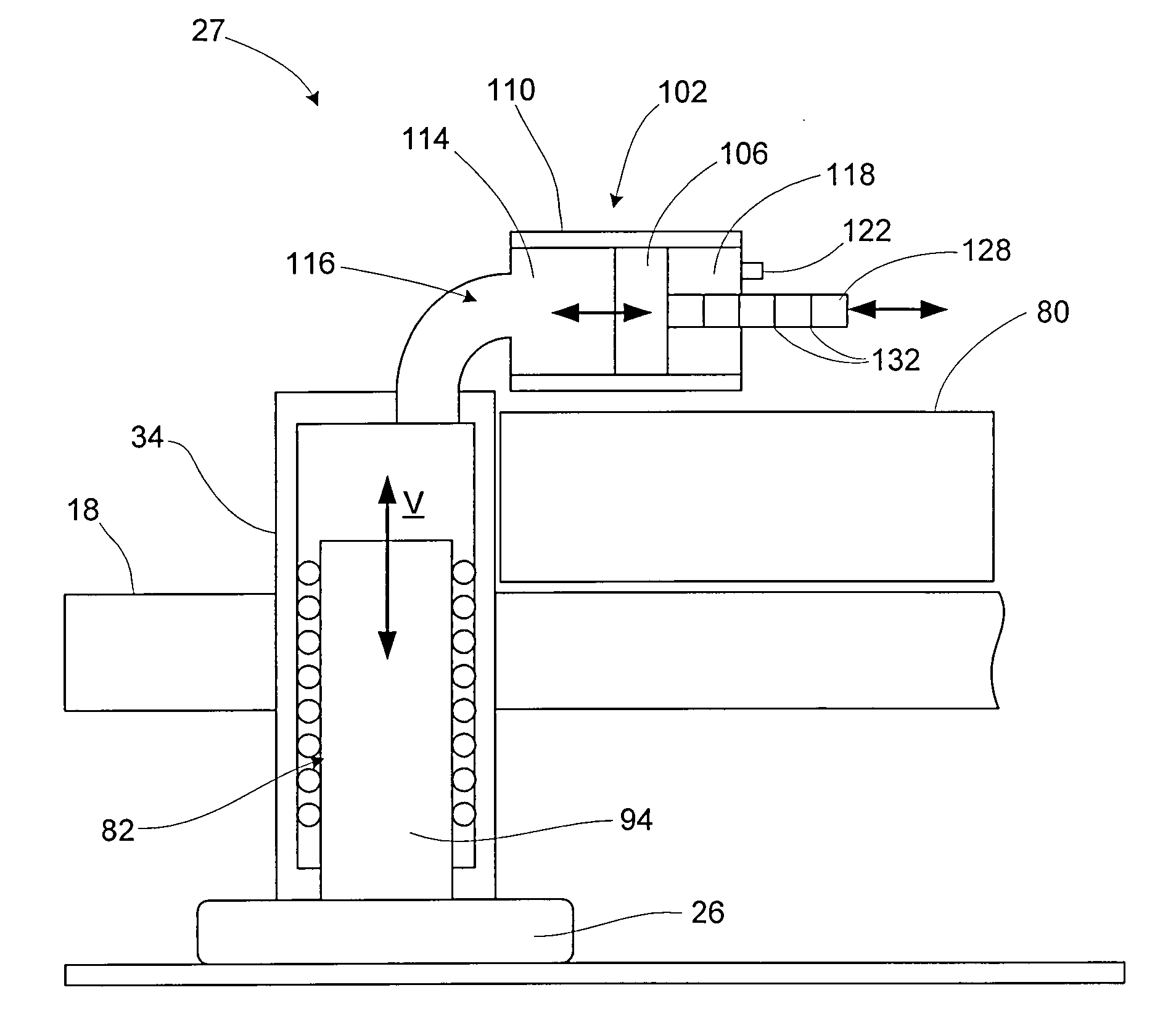

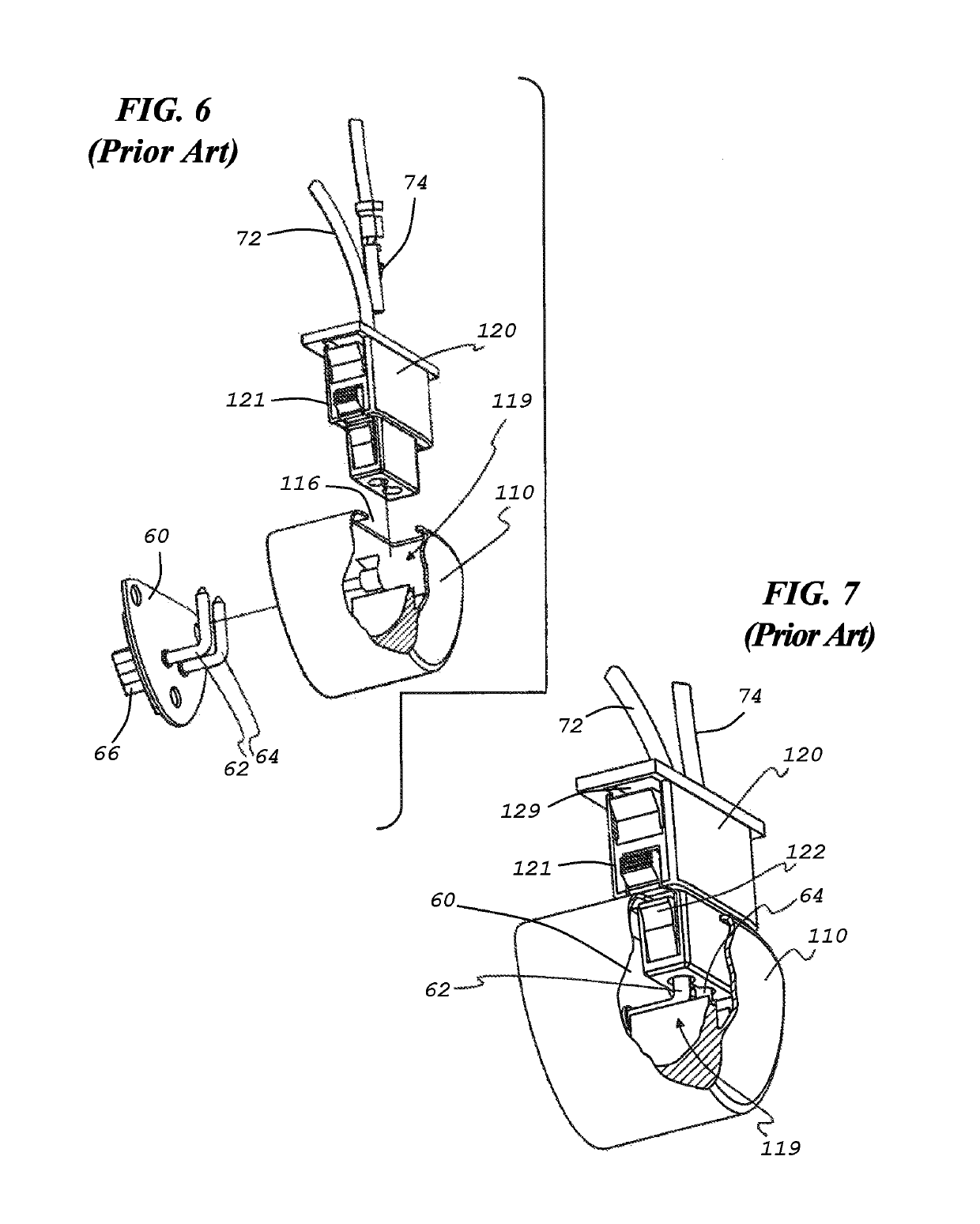

System to eliminate electric actuator contamination

InactiveUS20100276233A1Reduce and eliminate actuator contaminationExtending actuator service lifeAxially engaging brakesBraking componentsActuatorControl theory

A system to reduce or eliminate brake actuator contamination by providing a clean air source for the actuator such that a volume of a void in the actuator can vary without introducing moisture and / or contaminants into the actuator. A movable wall moves in response to changes in the volume of the void of the actuator to compensate for the changes without drawing moisture or contaminants into the actuator housing. By reducing or eliminating actuator contamination the service life of the actuator can be extended.

Owner:THE BF GOODRICH CO

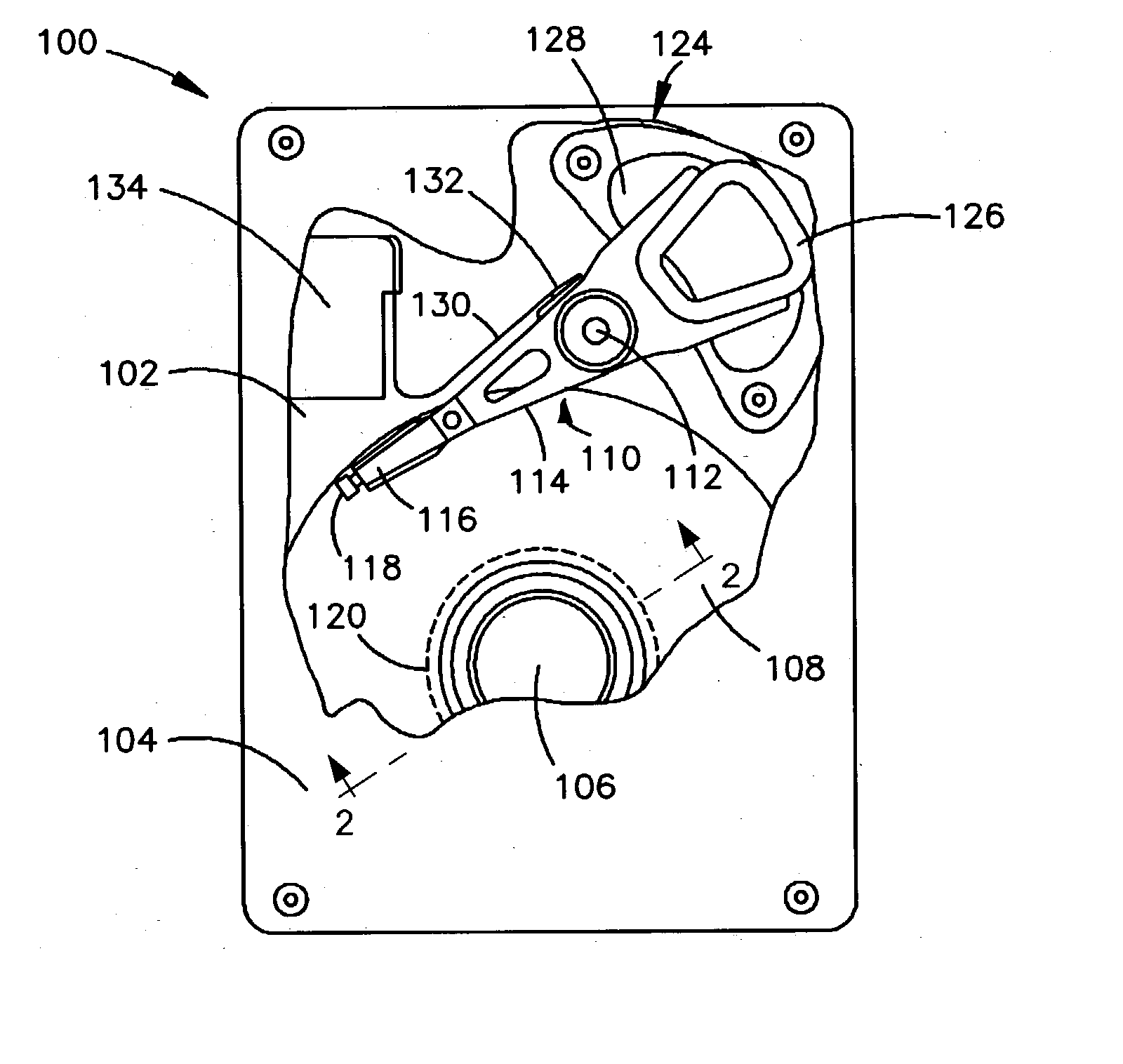

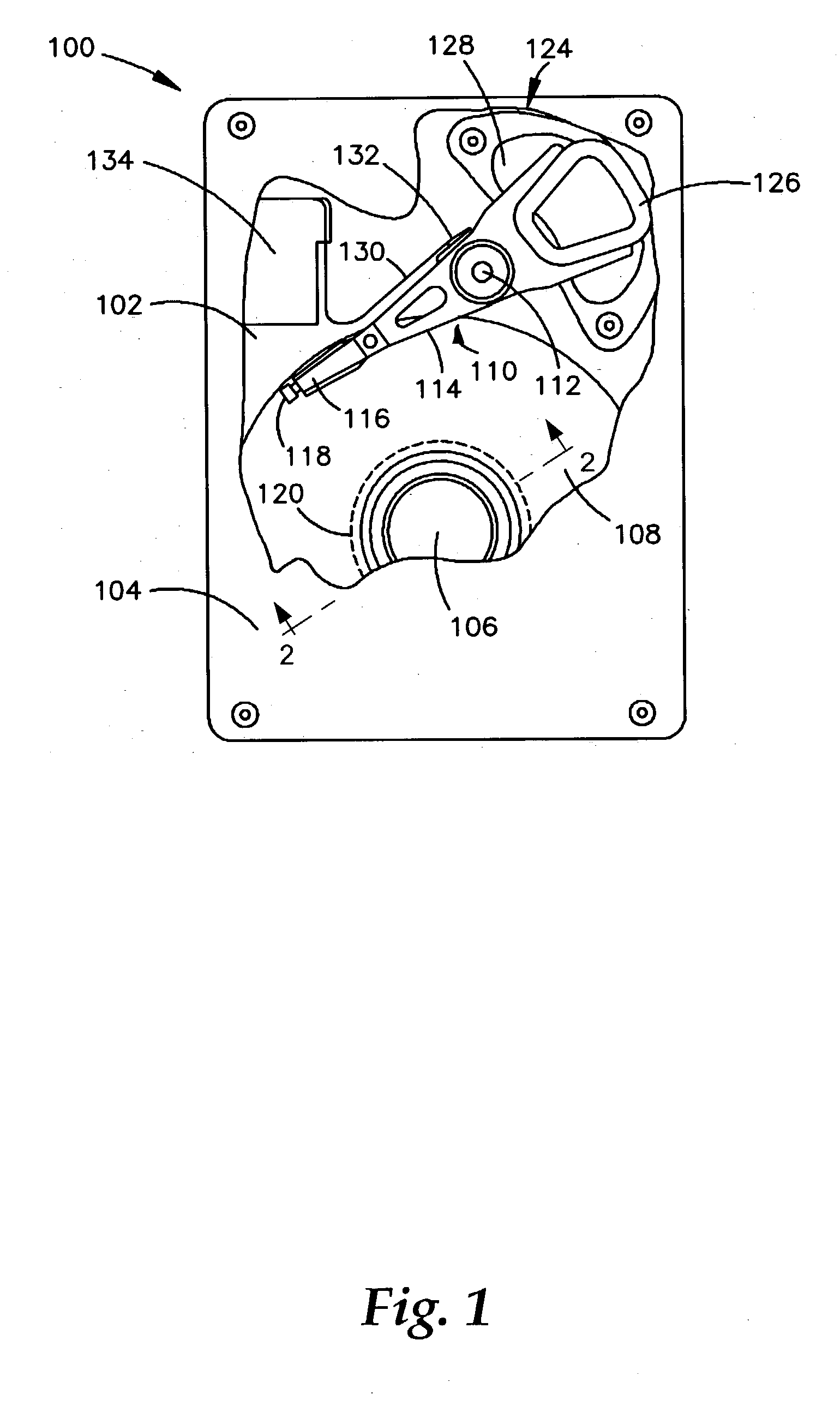

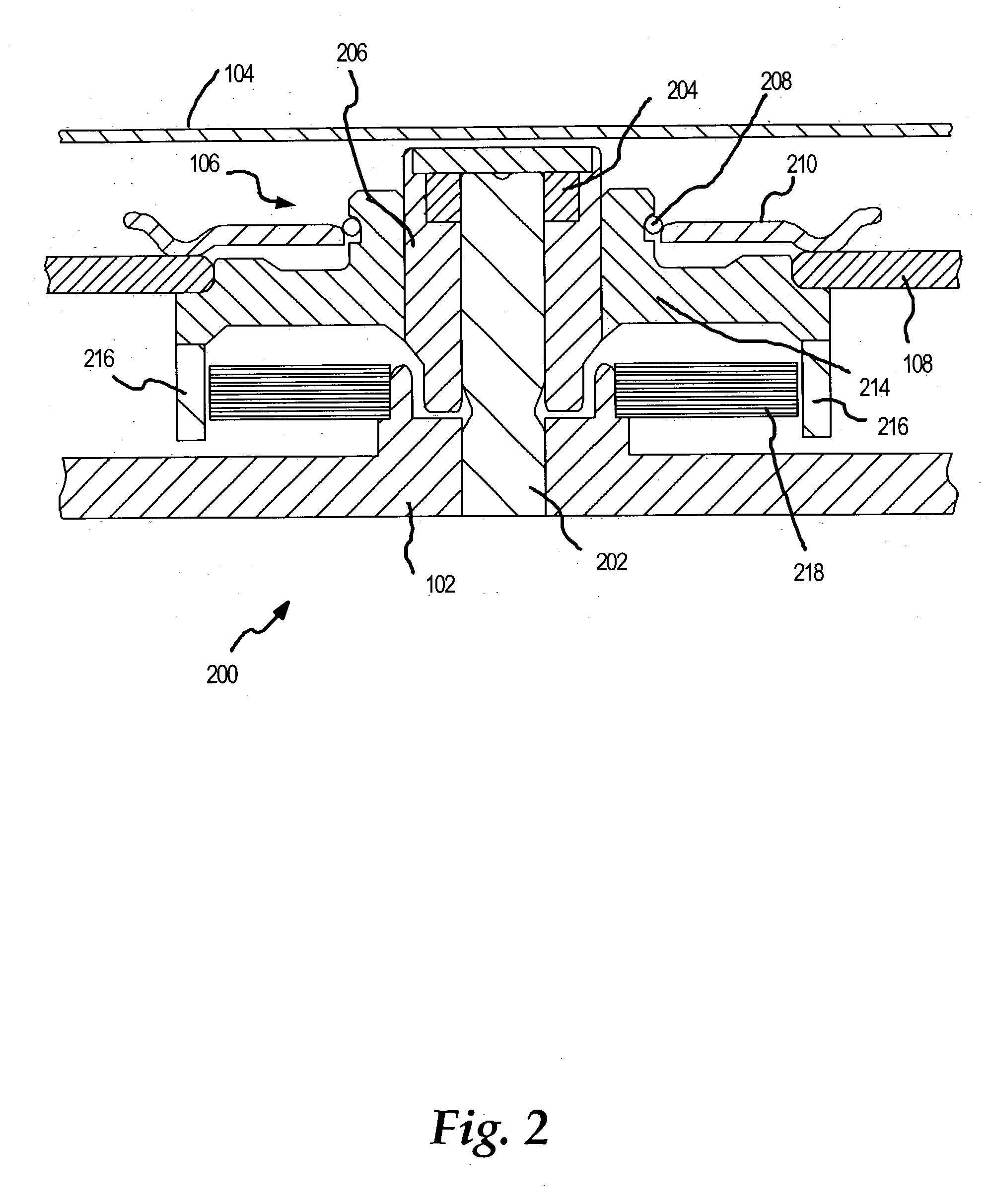

Method and system for of compensating for data storage disc stack imbalance during disc drive assembly

InactiveUS20050018338A1Permit optimizationReliability issueRecord information storageDigital recordingMoving averageCircular disc

A method and system of compensating for imbalance in a data storage disc stack during assembly of the data storage device. The method introduces an optical measurement system downstream of the disc clamp installation operation. The system measures multiple parameters of a most recent N incoming disc-stacks produced on the assembly line, where N is a suitable sample size, such as 30 disc stacks. The measured parameters can comprise disc clamp offset, clamp offset angle, and ring outer diameter. After measuring parameters for a suitable sample size N, the optical system calculates a dynamic or moving average of the most recent N disc stack component offsets and / or offset angles. The calculated averages are then utilized to determine a component configuration type that will compensate for the disc stack imbalance according to the offset trend. The system then feeds back the clamp configuration type to a clamp installation operation where the configuration type is installed during assembly of the next disc stack.

Owner:SEAGATE TECH LLC

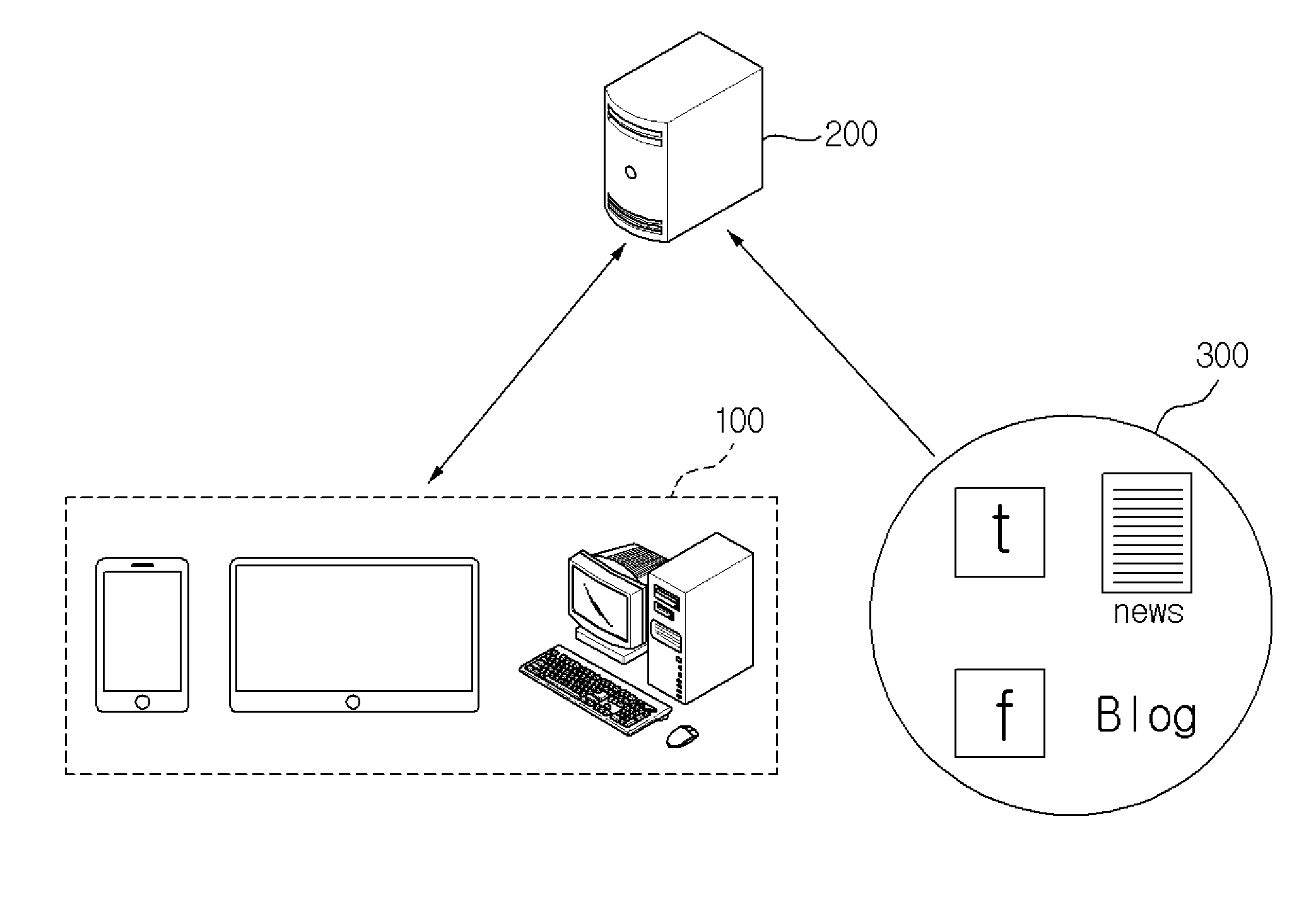

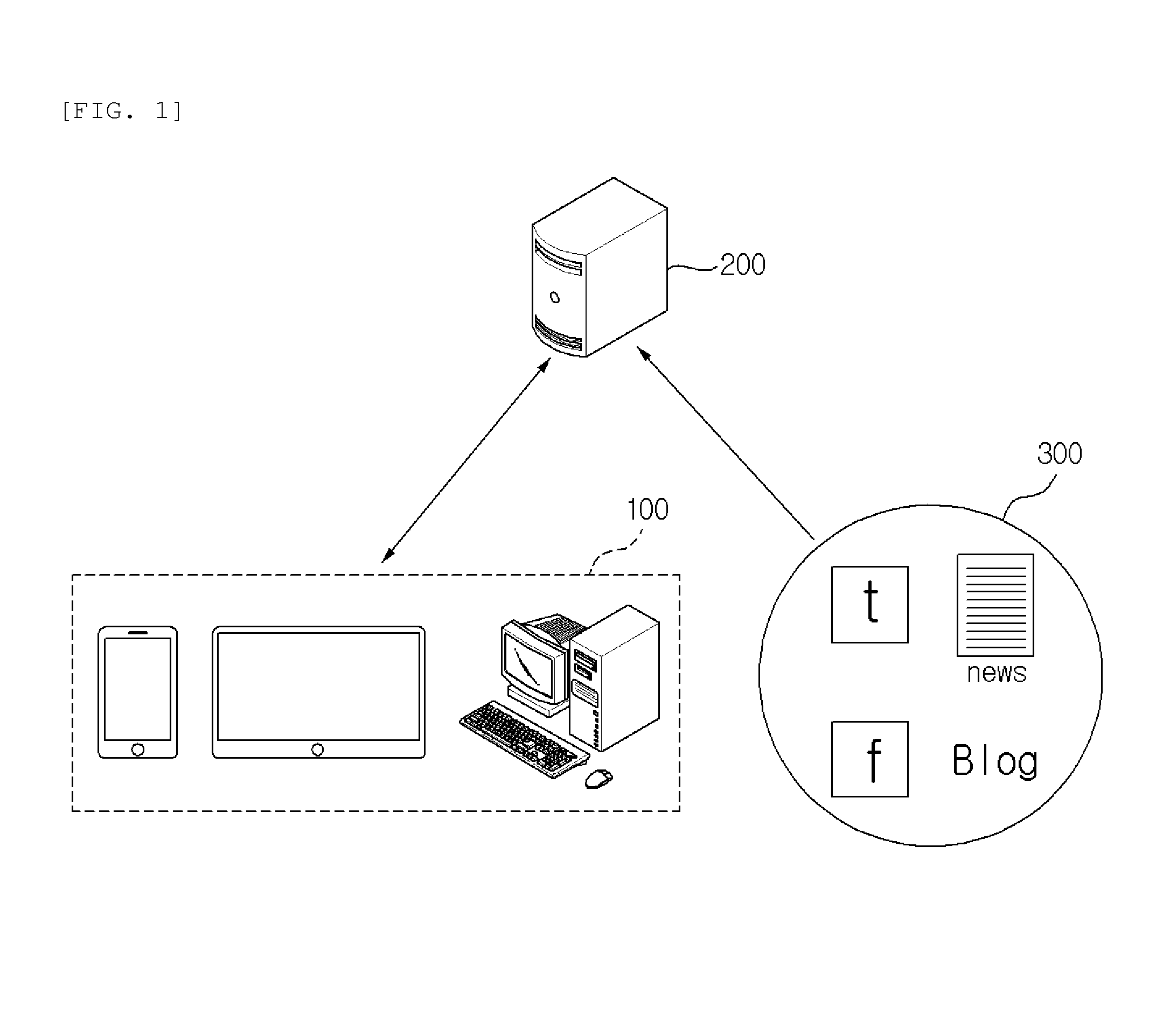

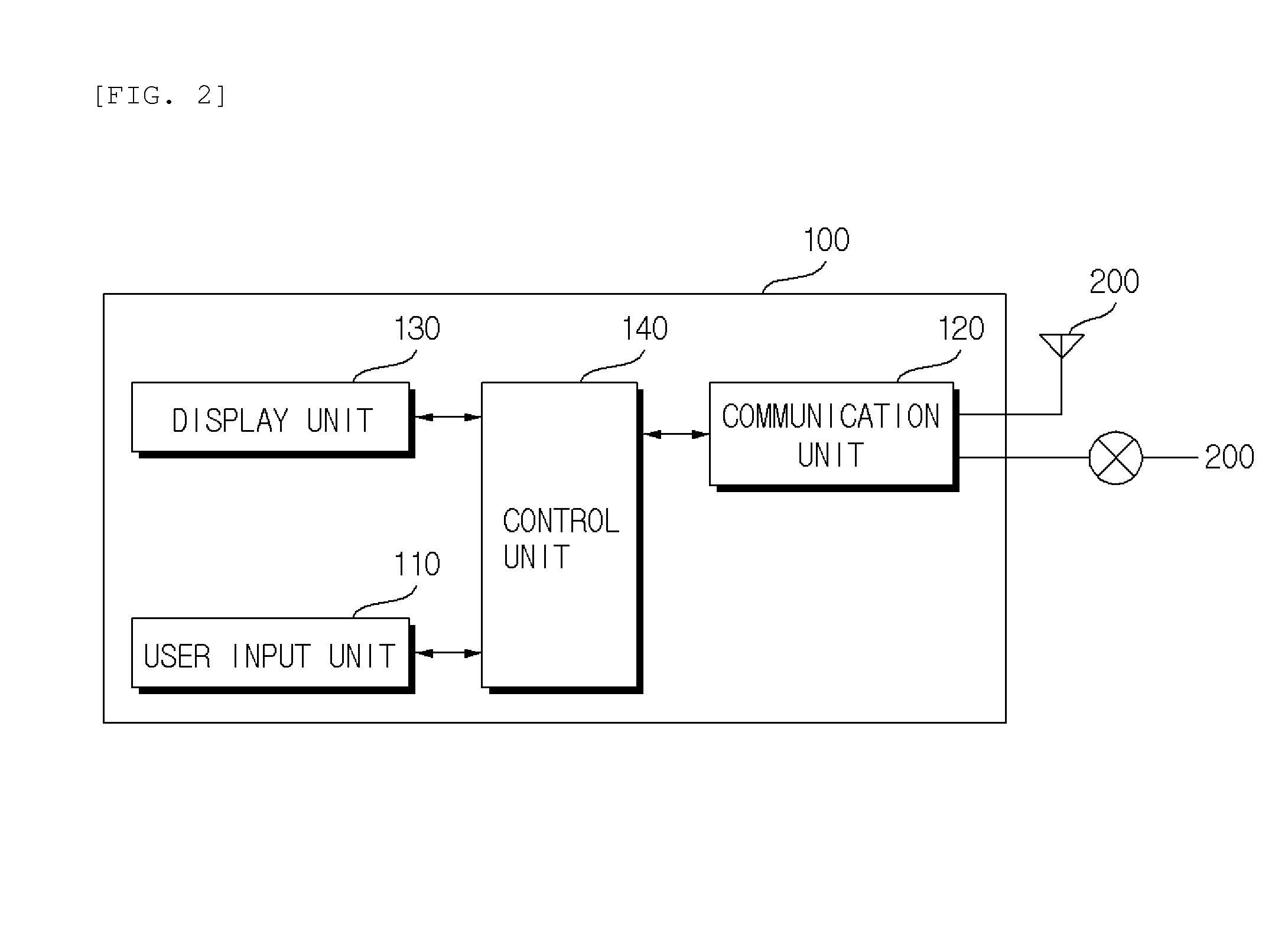

Apparatus and method for providing issue record, and generating issue record

InactiveUS20140101293A1Reliability issueAvoid mistakesData processing applicationsWeb data indexingWorld Wide WebSubject specific

Disclosed is a technology for extracting issue information having high interests to users by recognizing contents of a sentence within media (including news, Tweet, and a blog), and automatically detecting and presenting an issue subject related to the issue information. A method of providing issue information according to the present invention includes: extracting an issue by extracting issue information according to a predetermined condition or a condition received from the outside by using data expressed with a text on media or meta data defining additional information on the data; and displaying an issue history or hotness of the extracted issue information which has been issued in the media to a user.

Owner:ELECTRONICS & TELECOMM RES INST

Method of improving adhesion of bond pad over pad metallization with a neighboring passivation layer by depositing a palladium layer

ActiveUS8394713B2Reliability issueSemiconductor/solid-state device detailsSolid-state devicesPalladiumSemiconductor

A semiconductor device structure has a semiconductor die that has a bond pad with a passivation layer surrounding a portion of the bond pad. A nickel layer, which is deposited, is on the inner portion. A space is between a sidewall of the nickel layer and the passivation layer and extends to the bond pad. A palladium layer is over the nickel layer and fills the space. The space is initially quite small but is widened by an isotropic etch so that when the palladium layer is deposited, the space is sufficiently large so that the deposition of palladium is able to fill the space. Filling the space results in a structure in which the palladium contacts the nickel layer, the passivation layer and the bond pad.

Owner:NXP USA INC

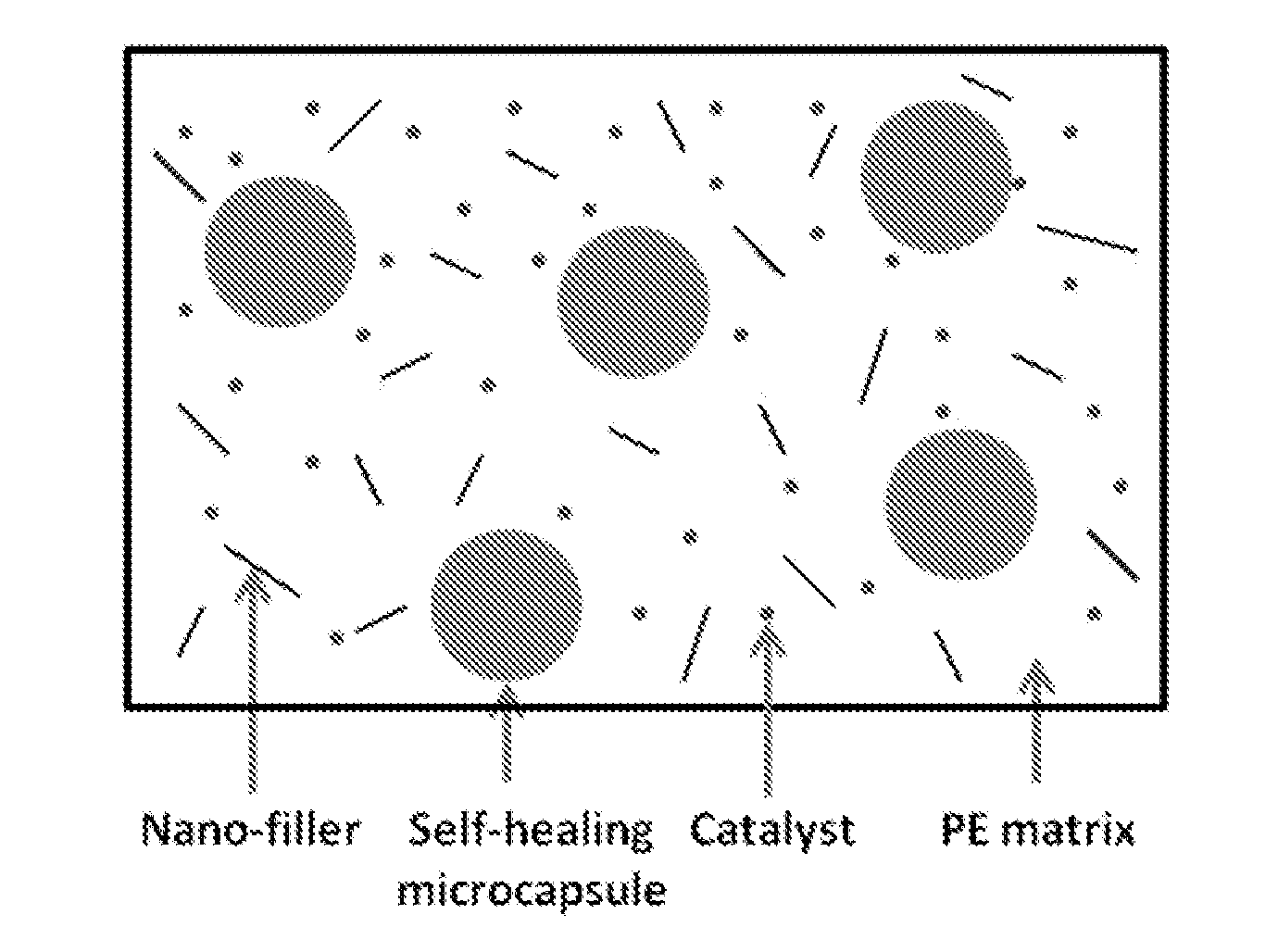

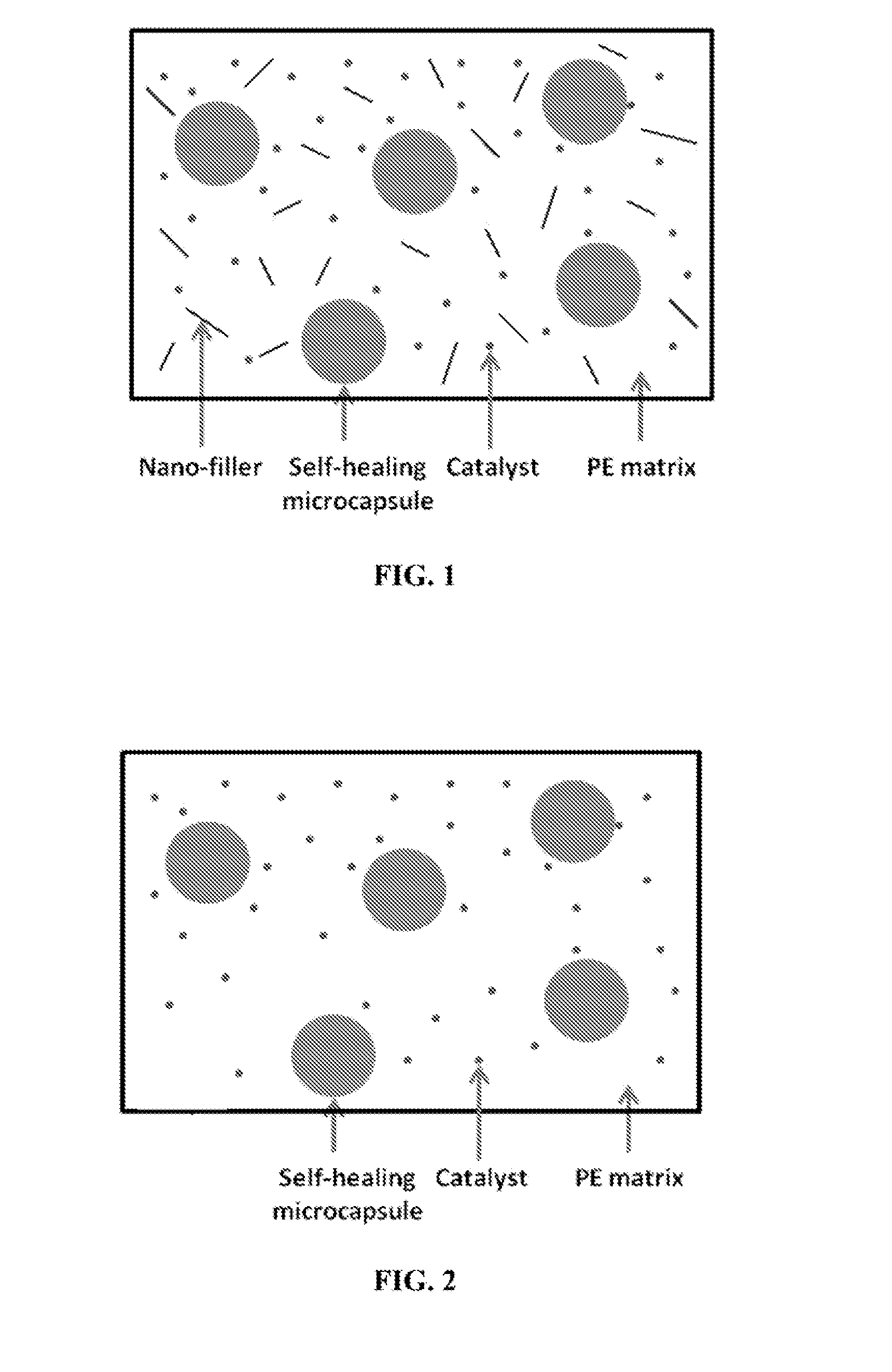

Self-Healing Polyethylene

InactiveUS20150291745A1Exceptional chemical resistance and long term durabilityReliability issueMaterial nanotechnologyAdhesivesSelf-healingThermoplastic matrix

A composite material implements self-healing microcapsules in thermoplastic matrices, such as polyethylene. A microencapsulated dicyclopentadiene monomer and a solid phase Grubbs's catalyst is embedded in a polyethylene matrix to achieve self-healing properties. Nanofillers may be added to improve the properties of the polyethylene matrix incorporating a self-healing system.

Owner:PEN

Intelligent, universal, reconfigurable electromechanical interface for modular systems assembly

InactiveUS7763995B2Reduce needReduce weightBus-bar/wiring layoutsCoupling device connectionsElectrical conductorElectrical connection

An electromechanical connection includes a first conductor disposed in a first non-conductive array and a second conductor disposed in a second non-conductive array capable of mating with the first non-conductive array. The second conductor is capable of mating with the first conductor when the first non-conductive array and the second non-conductive array are mated. A processor associated with the first non-conductive array determines if an electrical connection is formed between the first conductor and the second conductor. The processor can assign a function to the electrical connection.

Owner:PHYSICAL SCI

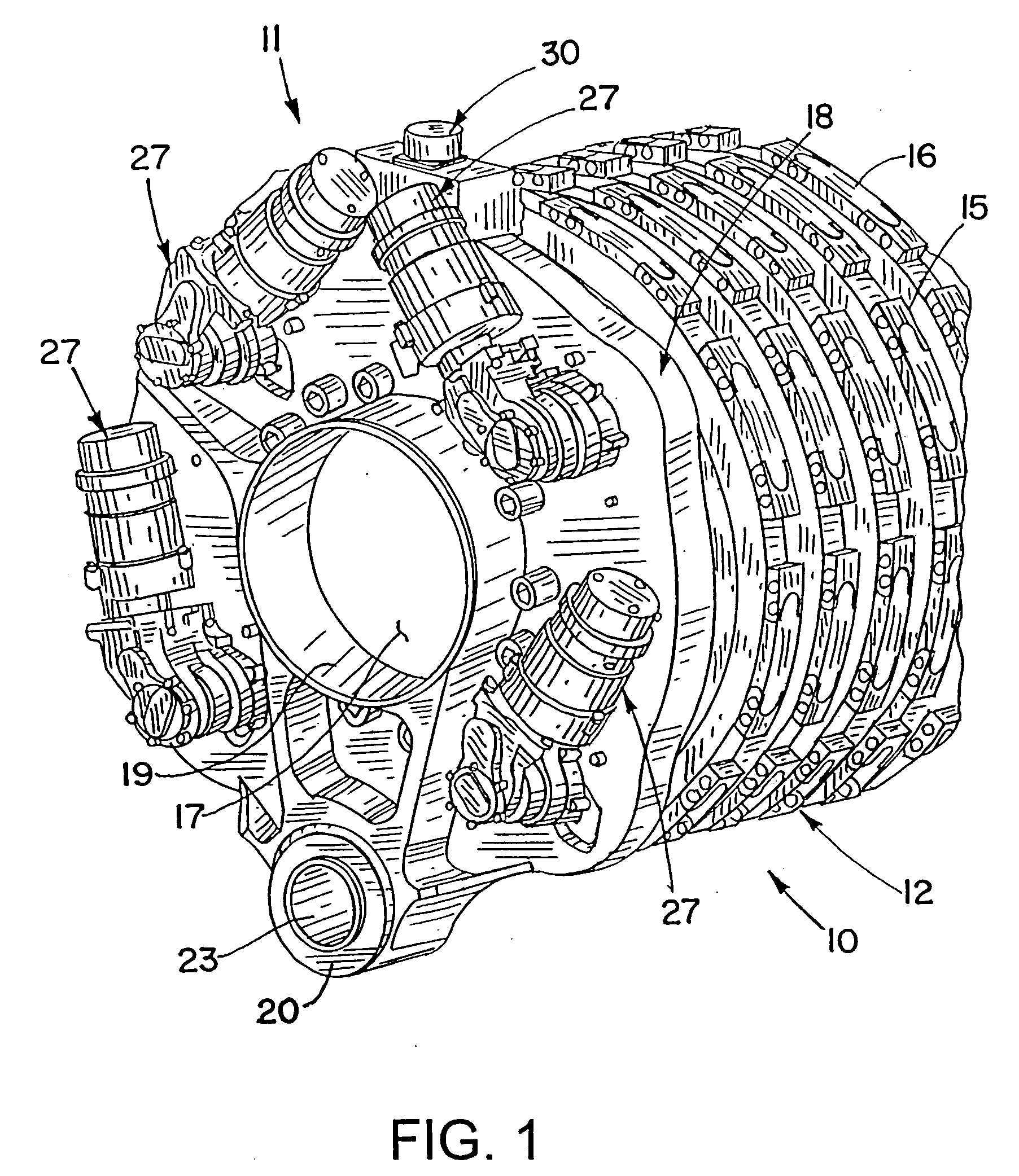

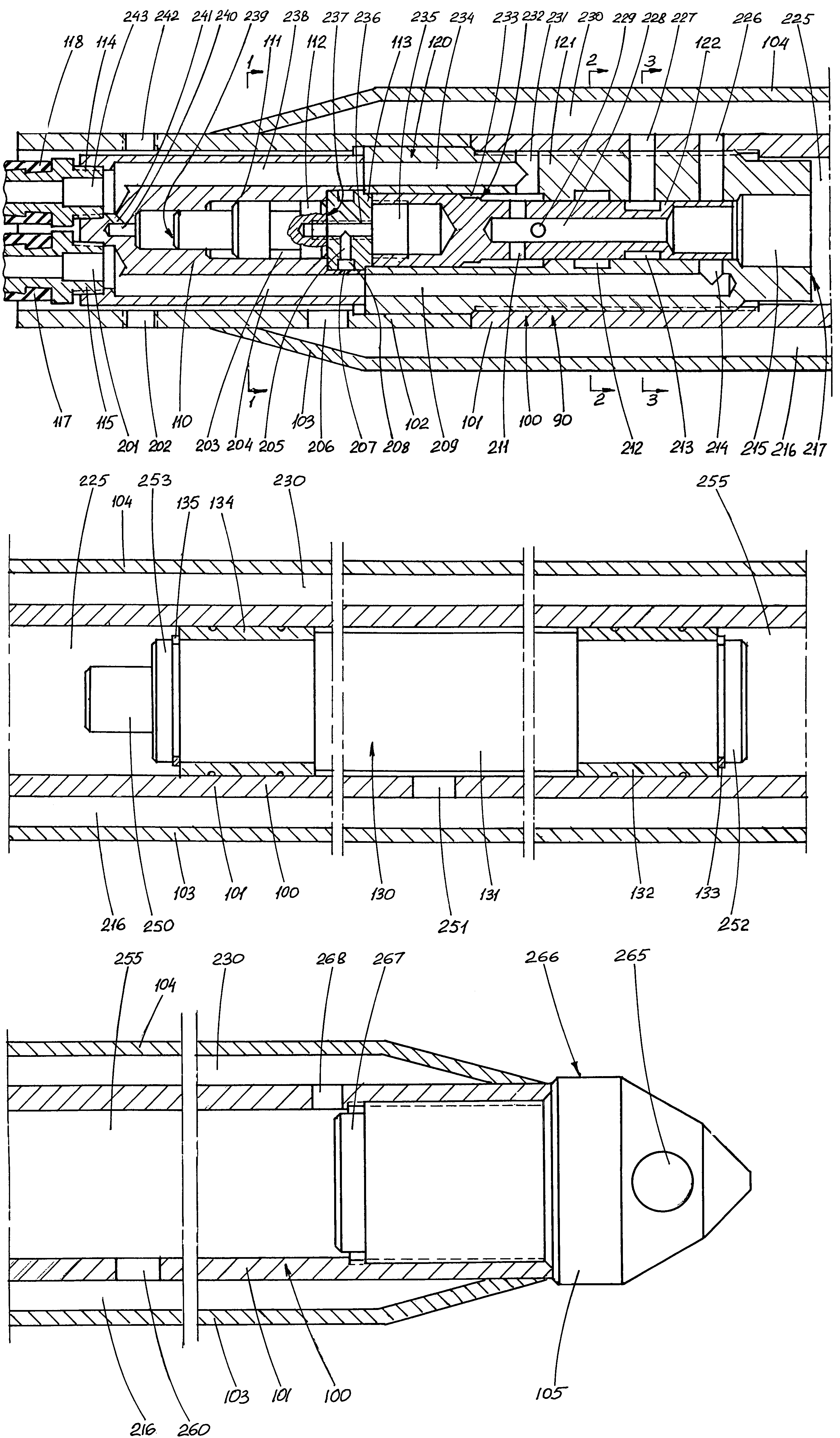

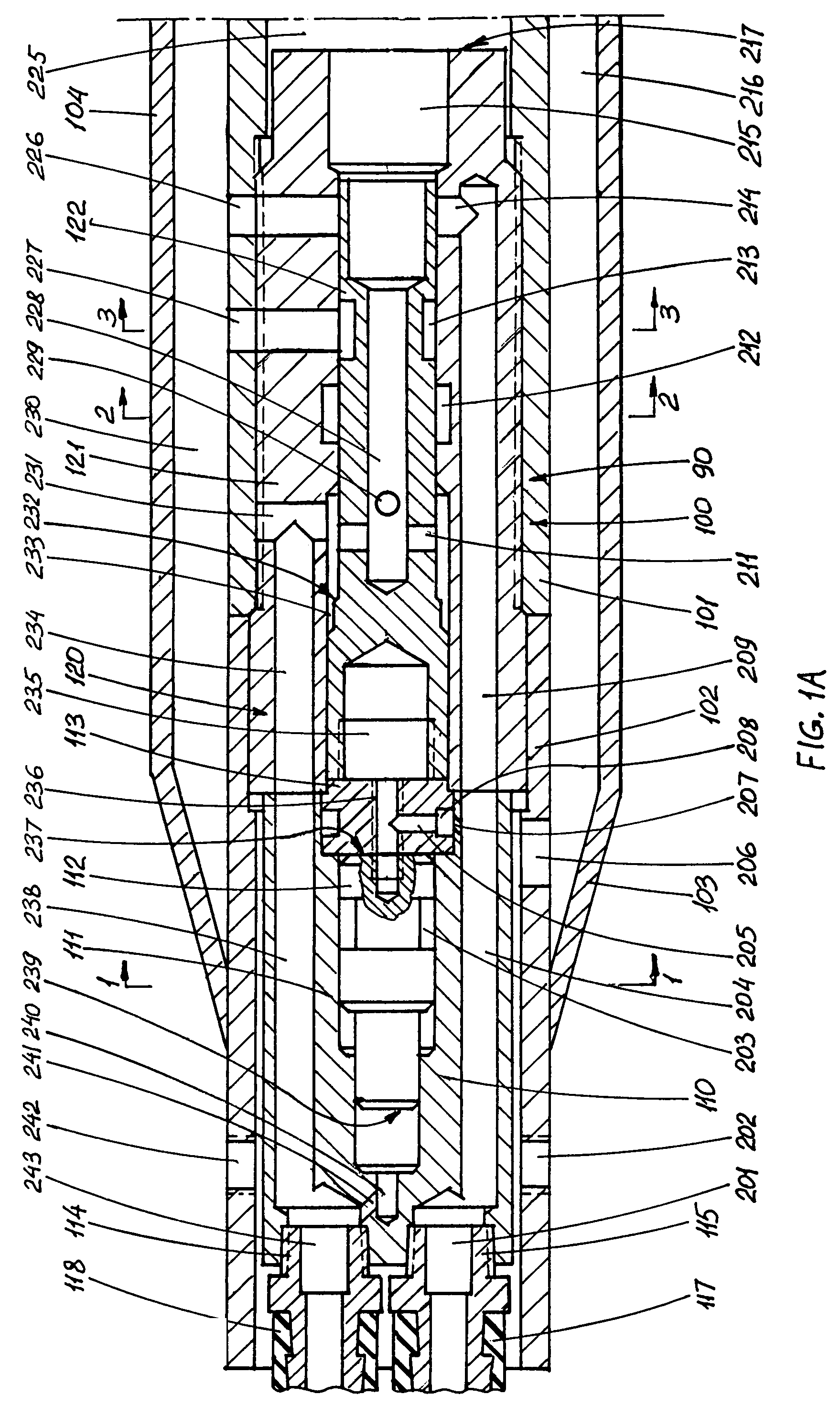

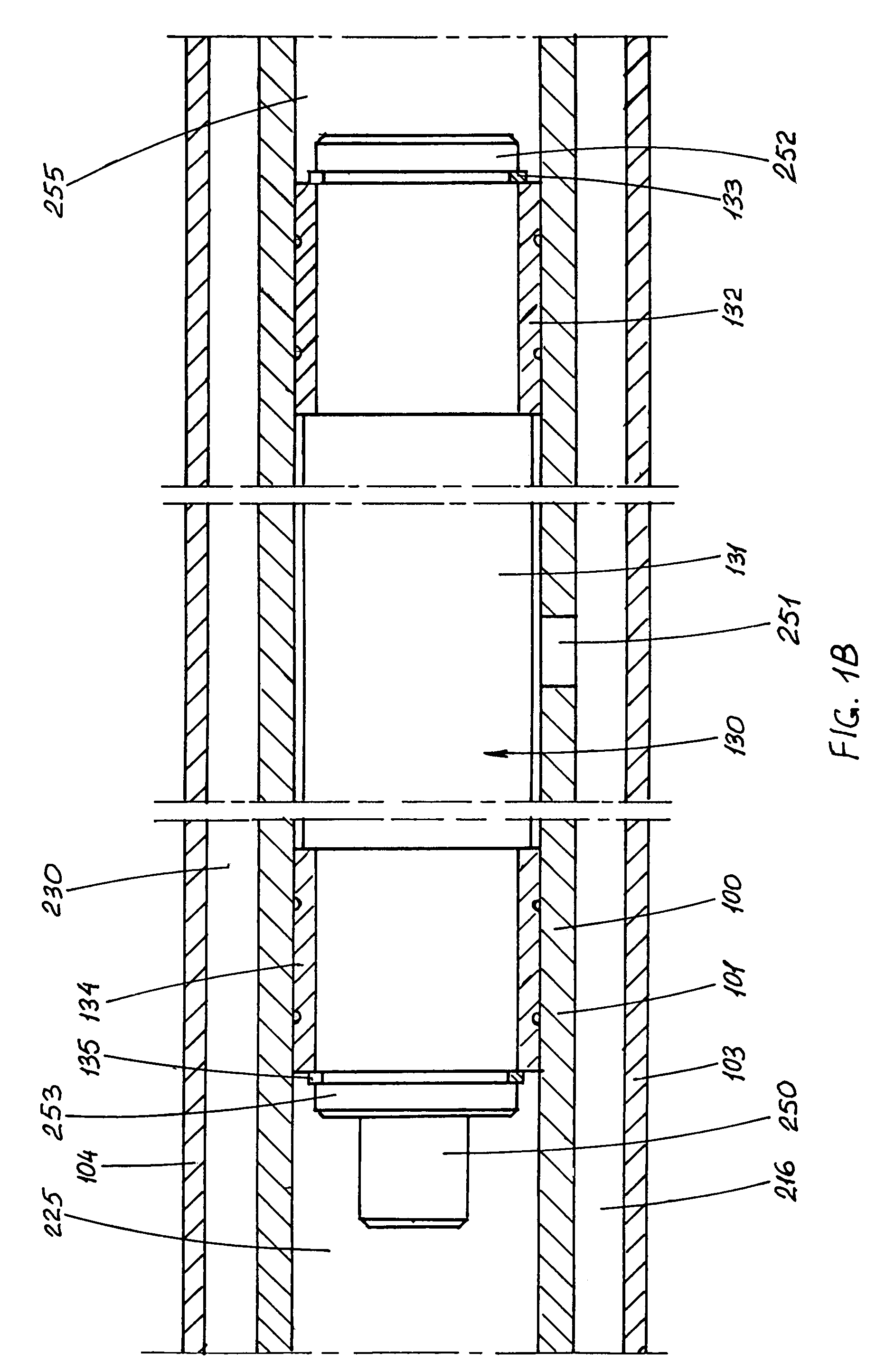

Reversible penetrating machine with a differential air distributing mechanism

InactiveUS7273113B2Reliability issueReduce the cost of the whole machineEarth drilling toolsConstructionsOperational costsEngineering

The invention represents a new design of a reversible penetrating machine (90) with a pneumatically controlled differential air distributing mechanism. This design eliminates the springs, the rear anvil assembly, and several other components found in the prior machine. The chisel and the tail of the machine are also redesigned to eliminate the need of a special attachment in case of retracting a failed machine. In addition, a simplified modification of the machine for special applications is disclosed in which the rear valve chest with associated parts is replaced by a single flange having appropriate air ducts. Finally, the new design of the chisel causes a reduction of the lateral friction between the body of the machine and soil. All this significantly increases the reliability and efficiency of the machine and results in decrease of the related manufacturing and operating cost.

Owner:SPEKTOR ENG

Parallel RIP with preamble caching

ActiveUS8077330B2Avoid overheadEliminate overheadVisual presentationDigital output to print unitsTelecommunicationsPreamble

A method and system is provided for splitting a print job into its preamble and at least one chunk. The splitter maintains a collection of RIP node addresses to which chunks of the job currently being split have already been sent. When a new chunk is about to be sent, the splitter checks whether each RIP node address has already received a chunk. If the RIP node has not already received a chunk, the splitter sends the preamble as well as the chunk to an available RIP associated with the RIP node. If, however, the RIP node address has already received a chunk, only the portion of the chunk after the preamble is sent to an available RIP associated with the RIP node and communicate the location of the preamble to the available RIP node. The preamble may contain common content for each job.

Owner:XEROX CORP

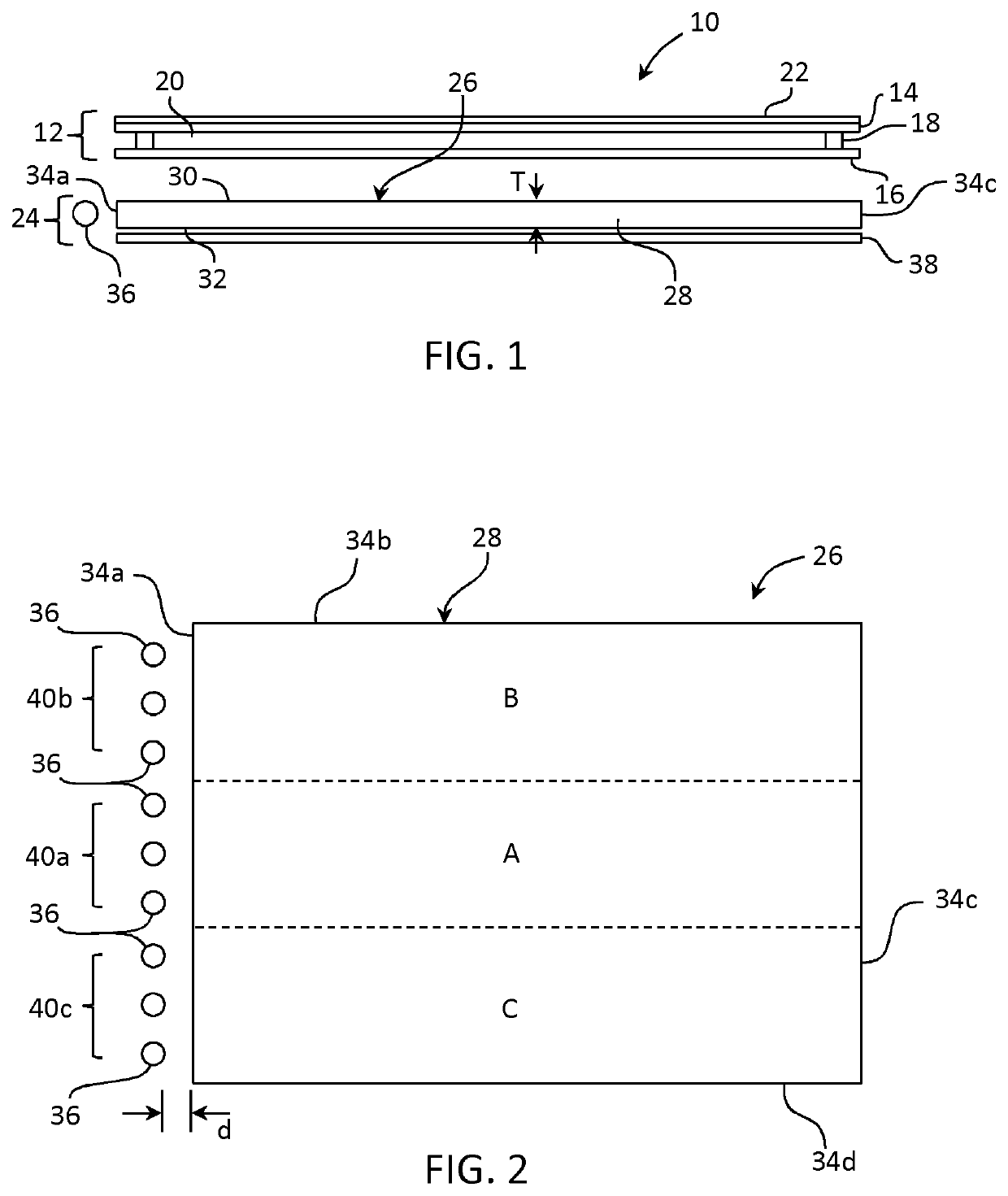

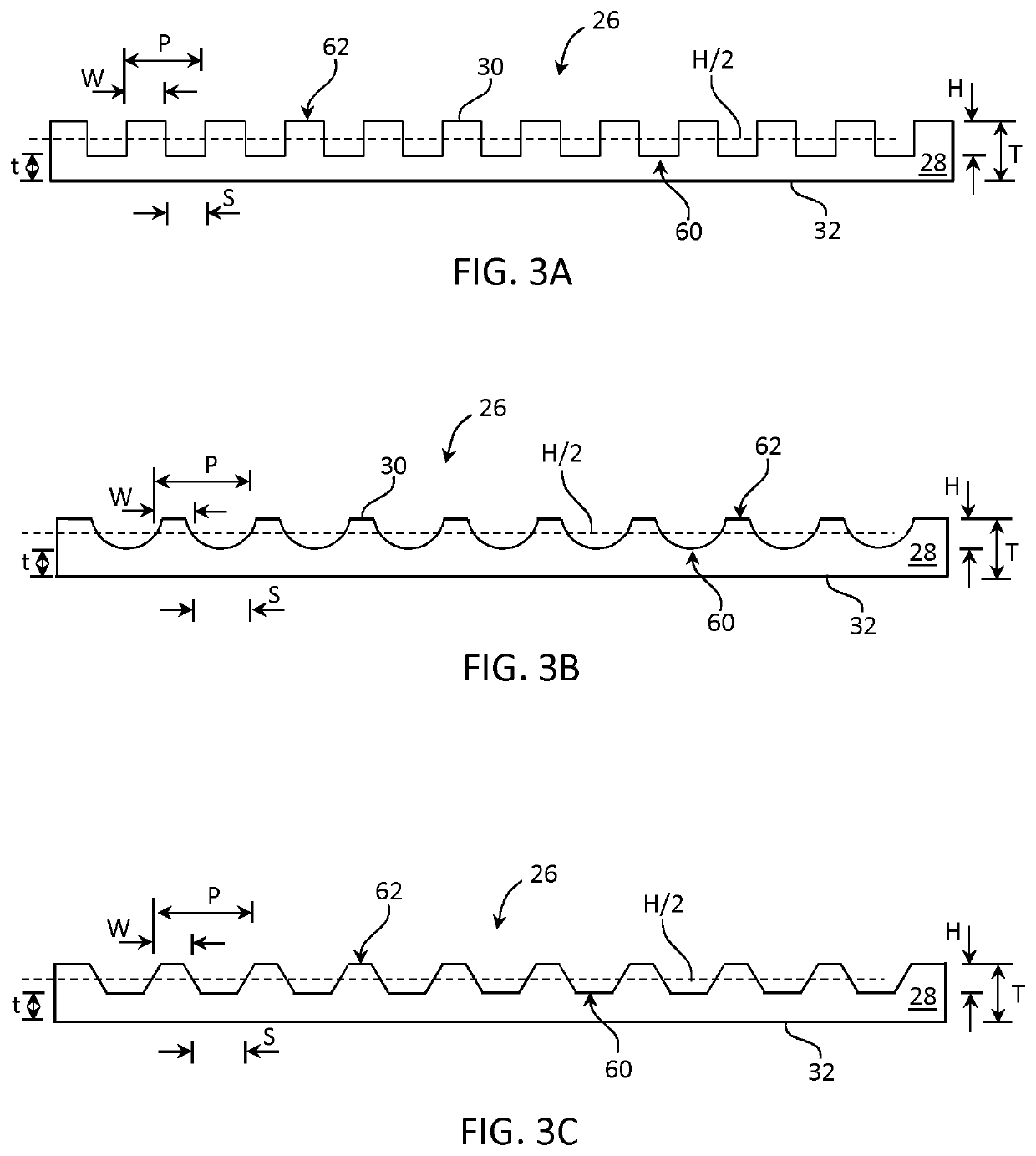

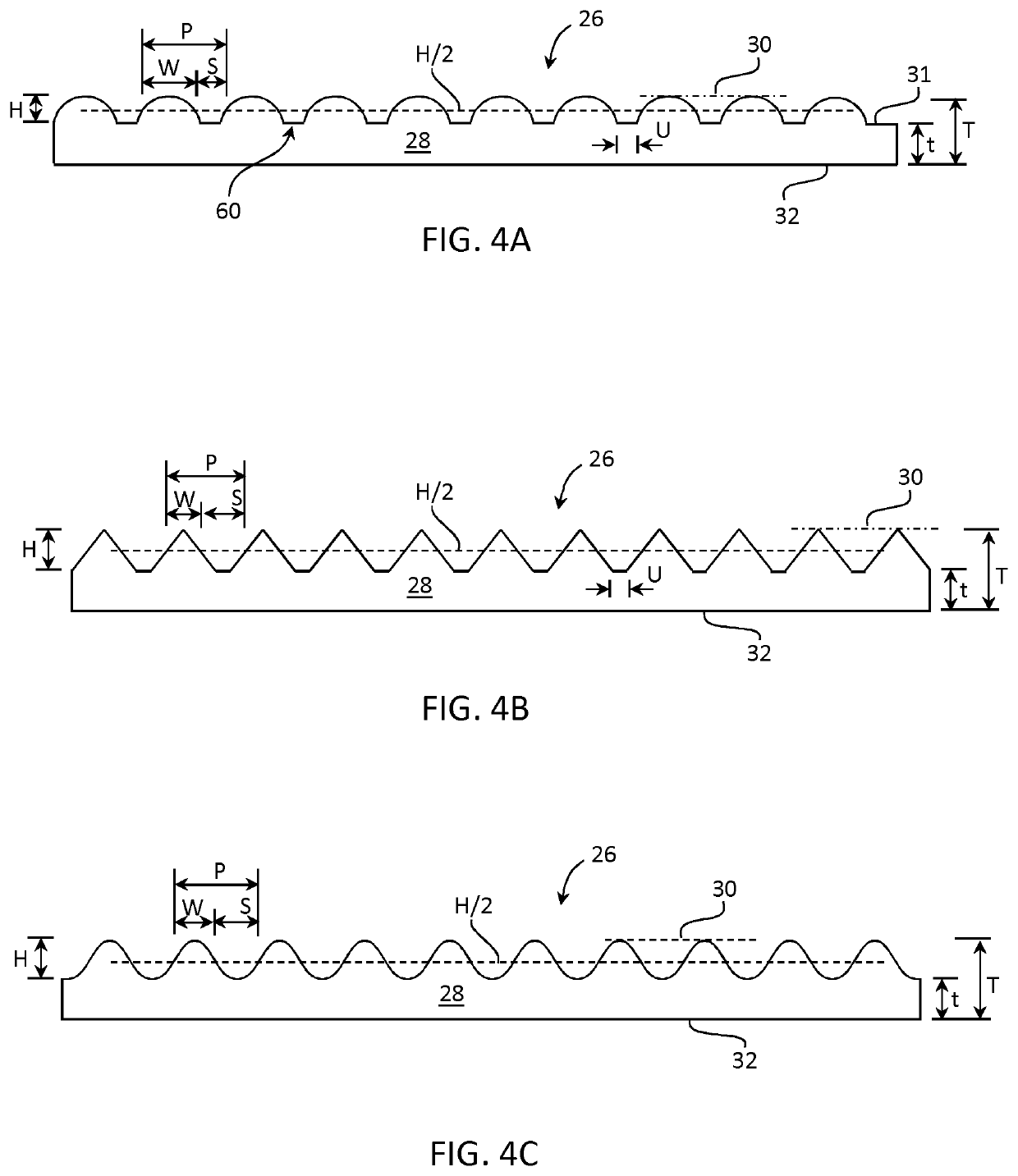

Methods of making a glass article with a structured surface

ActiveUS11186518B2Improve dynamic rangeIncrease refresh rateMechanical apparatusPlanar/plate-like light guidesLiquid-crystal displayLight guide

A method of making a glass article, for example a glass light guide plate comprising at least one structured surface including a plurality of channels and peaks. The glass article may be suitable for enabling one dimensional dimming when used in a backlight unit for use as an illuminator for liquid crystal display devices.

Owner:CORNING INC

Semiconductor device and method for manufacturing the same

PendingUS20210343839A1Improve reliabilityHot carrier electrons are reducedTransistorDevice materialCondensed matter physics

A semiconductor device includes first and second nitride semiconductor layers, a source, a drain, a gate structure, first and second p-type doped nitride semiconductor compound islands. The second nitride semiconductor layer is disposed on the first nitride semiconductor layer and has a bandgap greater than that of the first nitride semiconductor layer. The source, the drain, and the gate structure are disposed on the second nitride semiconductor layer. The drain viewed in a direction normal to the second nitride semiconductor layer extends longitudinally in an extending direction. The gate structure is between the source and the drain. The first p-type doped nitride semiconductor compound islands are disposed on the second nitride semiconductor layer and arranged adjacent to the drain along the extending direction. The second p-type doped nitride semiconductor compound island is disposed between the gate structure and the second nitride semiconductor layer.

Owner:INNOSCIENCE (SUZHOU) SEMICON CO LTD

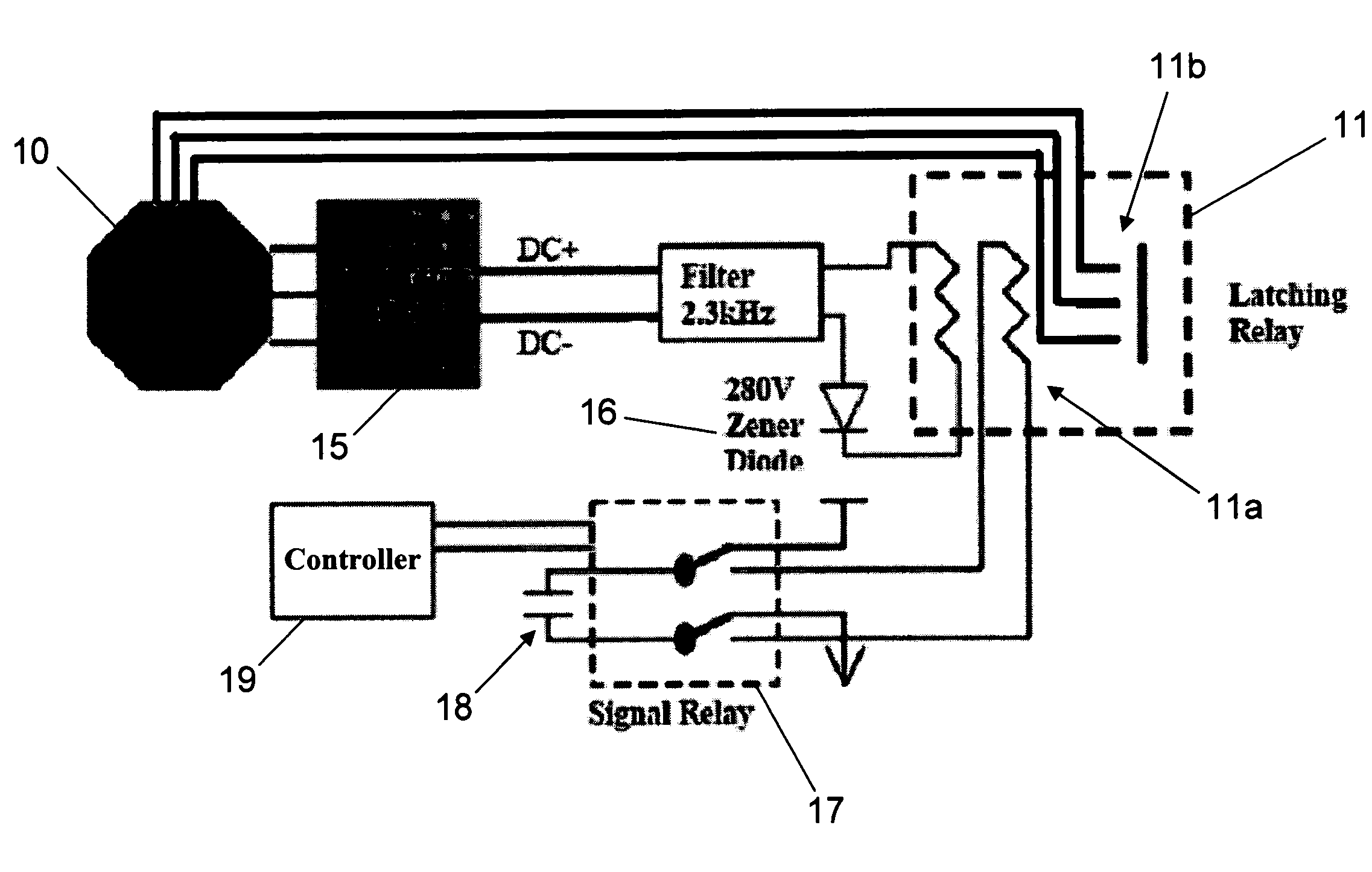

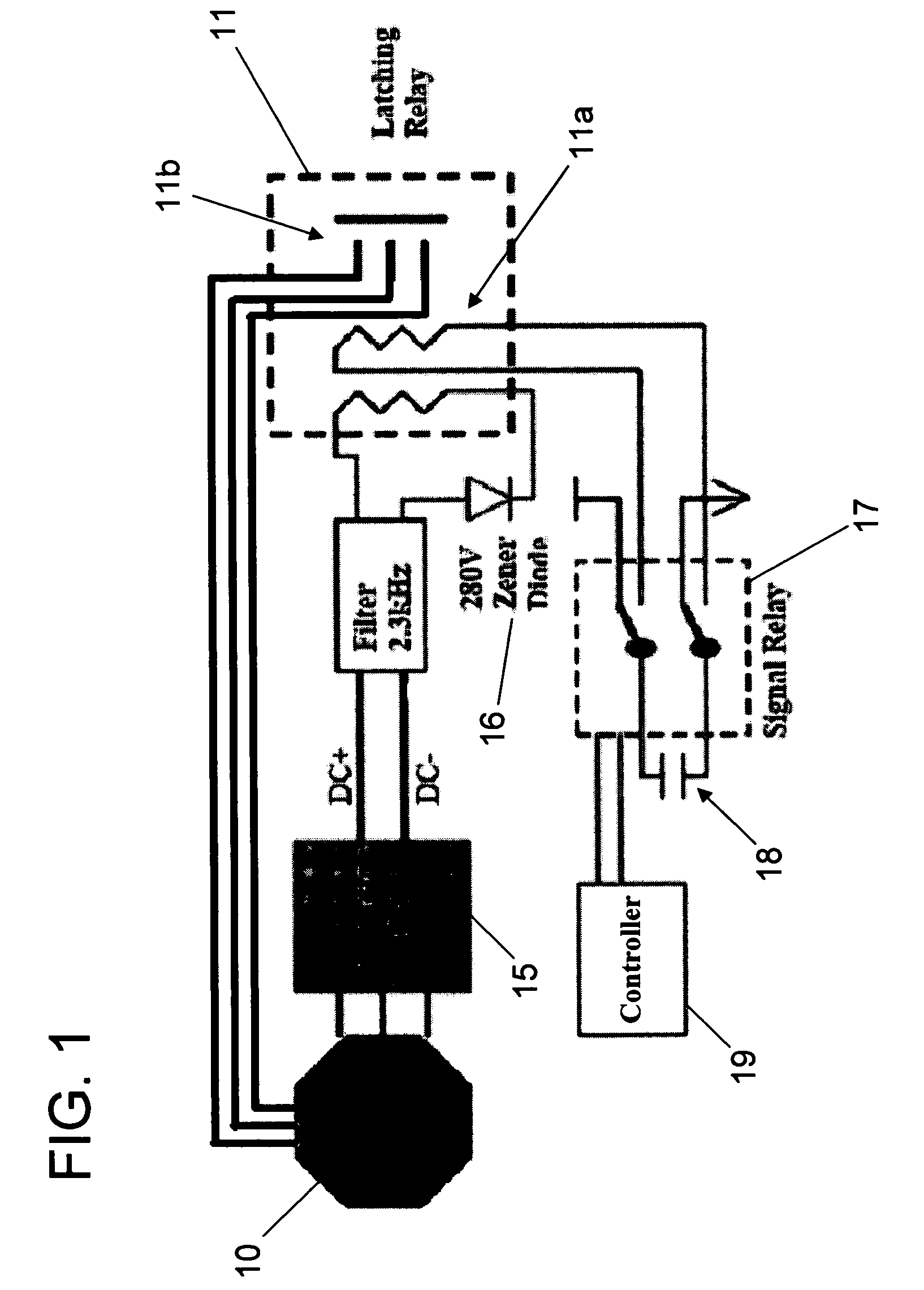

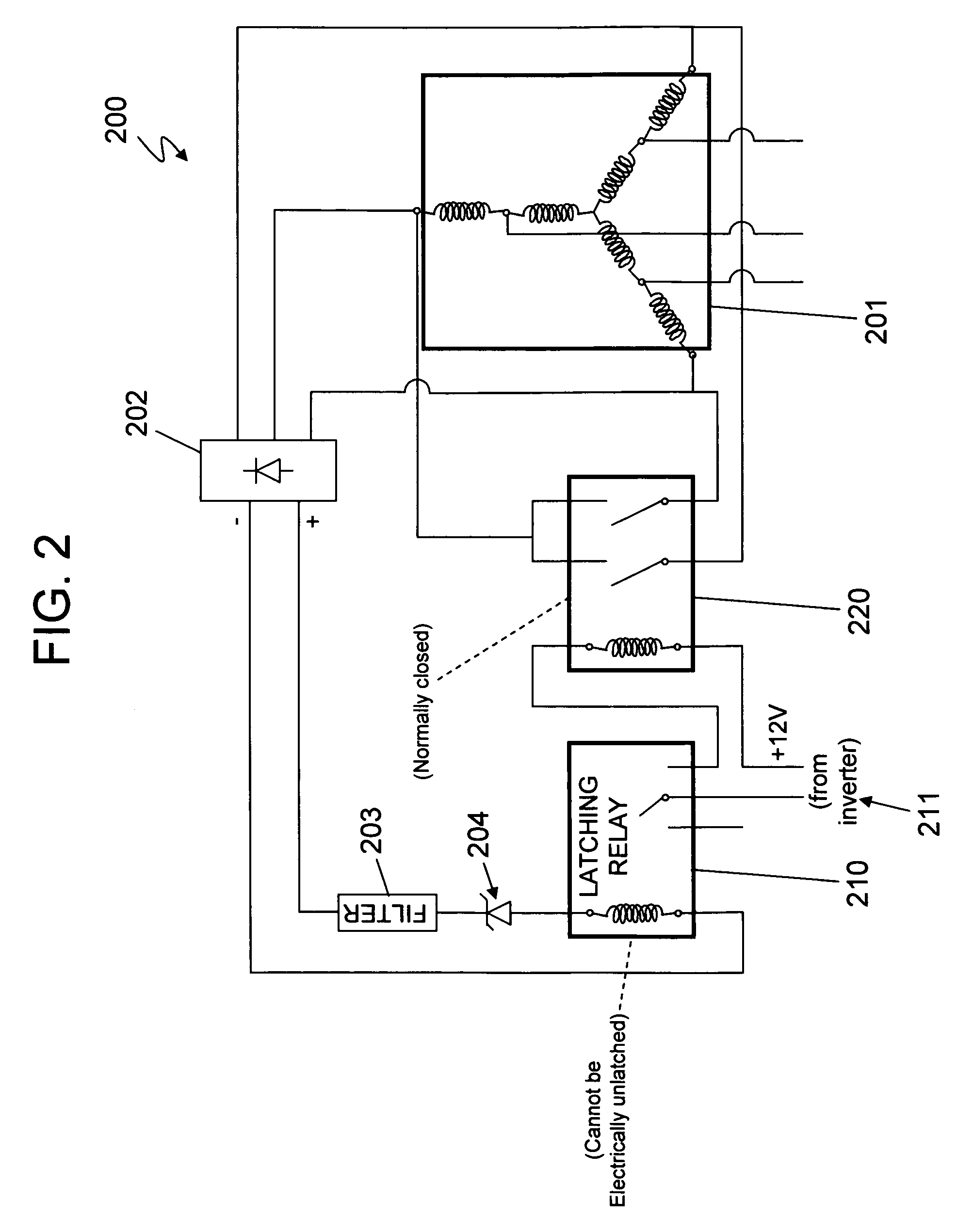

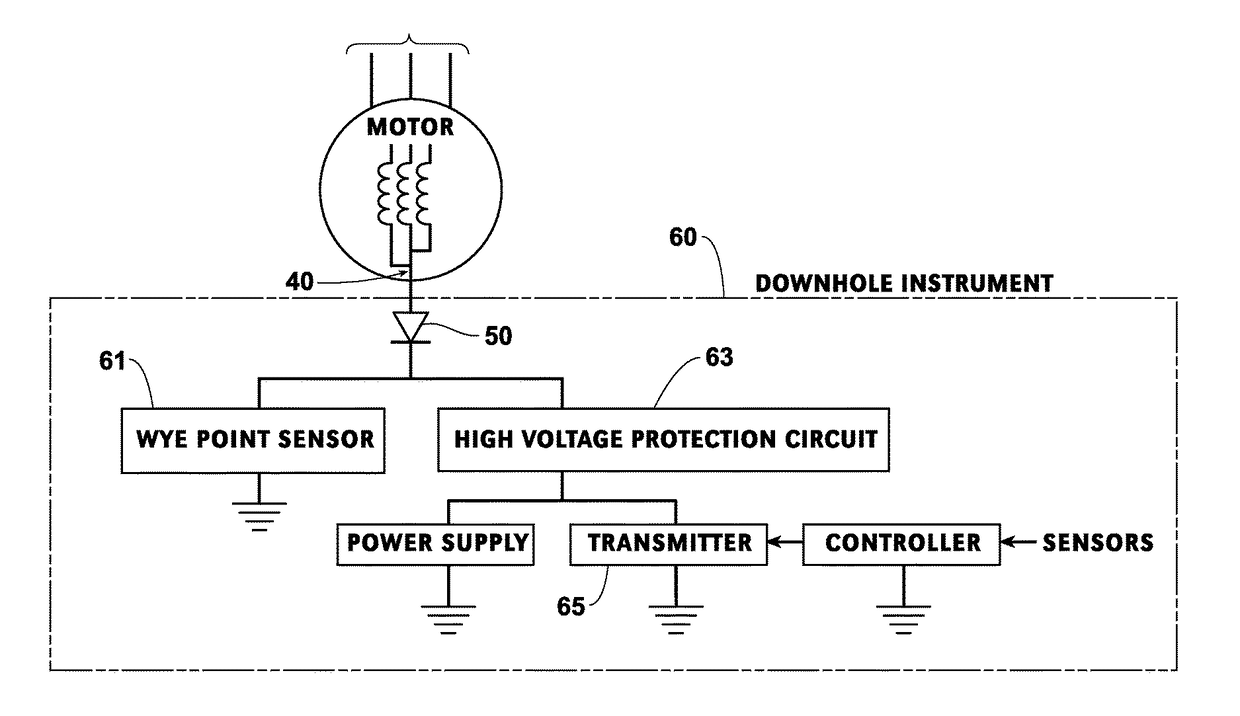

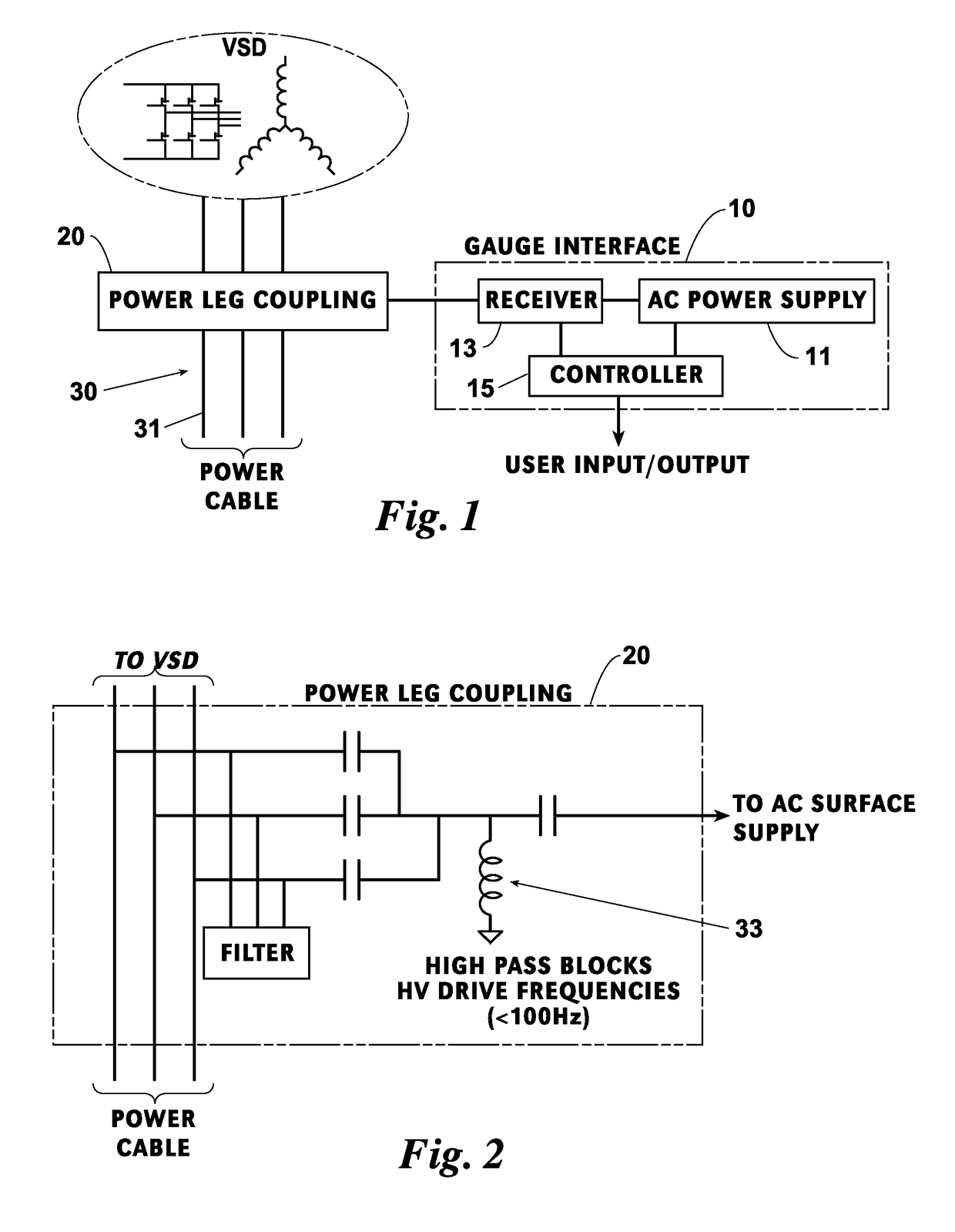

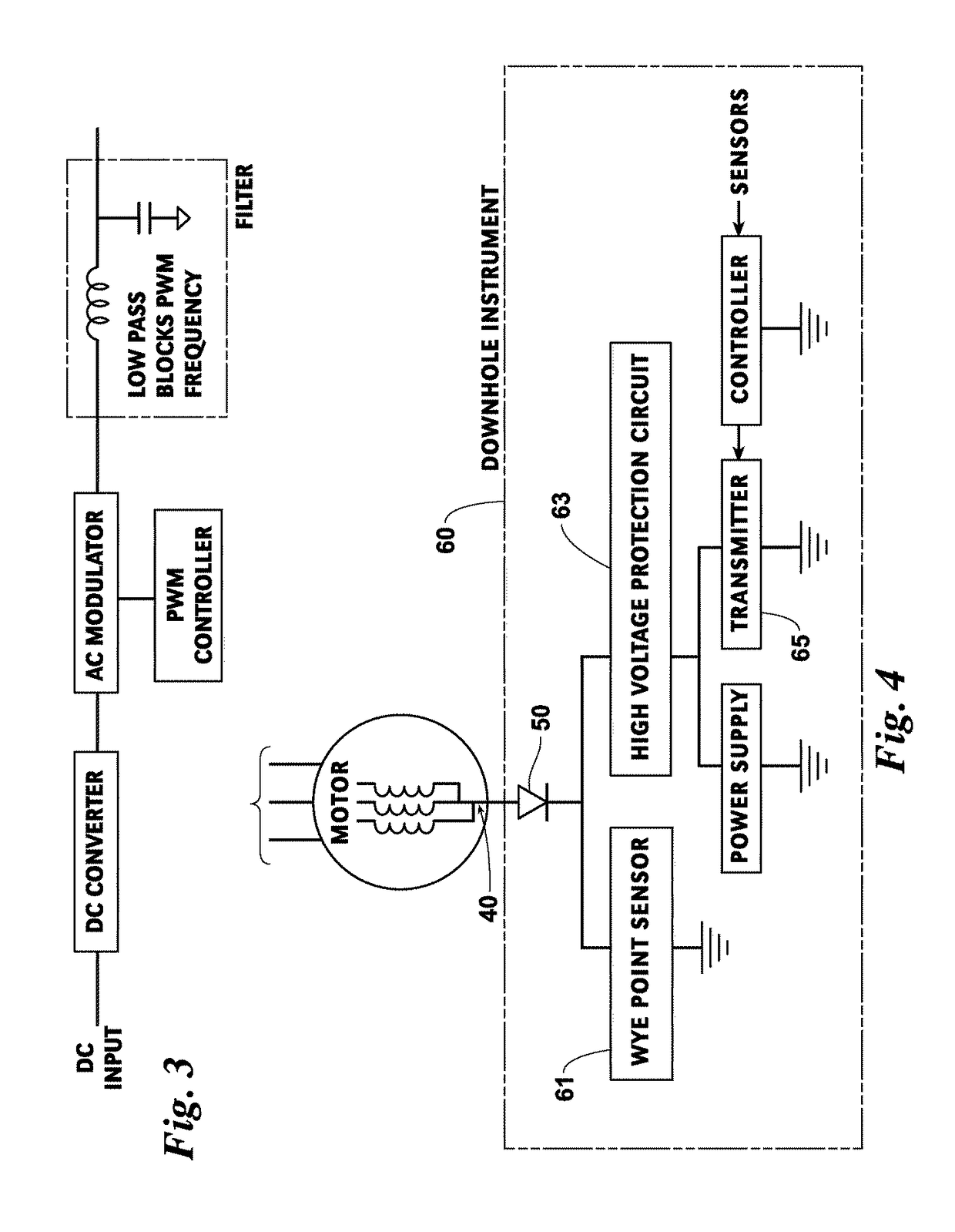

Ground fault tolerant data communication system for a downhole instrument

This invention relates to a data communication system / method for use in a downhole application wherein electrical energy is supplied over a multiple-conductor power cable to a motor assembly of a downhole tool such as an electric submersible pump. A power leg coupling interfaces a surface controller of a downhole instrument to the conductors of the tool's power cable. Uplink communication of telemetry data occurs via current modulation generated by the downhole instrument and interpreted by a surface controller. Downlink communication of downhole instrument data occurs over a different communication scheme supported by the downhole and surface controllers. Downlink communication scheme provides a supply of power to the downhole instrument. Protection of downhole electronics and continuity of communication is ensured in the event of a ground fault on the power cable. Both downlink and uplink communication frequencies are adaptive based on frequencies and voltages present on the power cable.

Owner:SERCEL INC

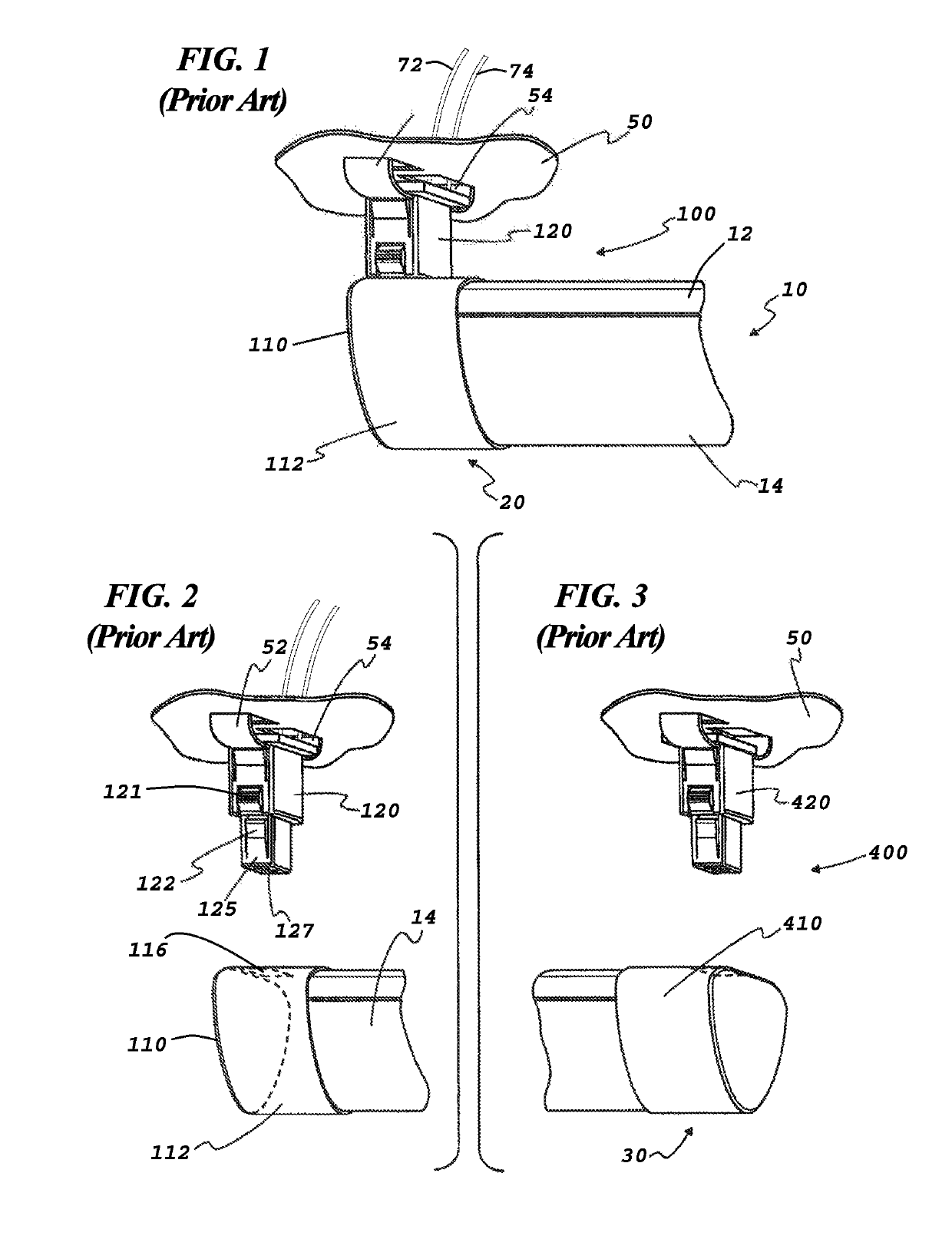

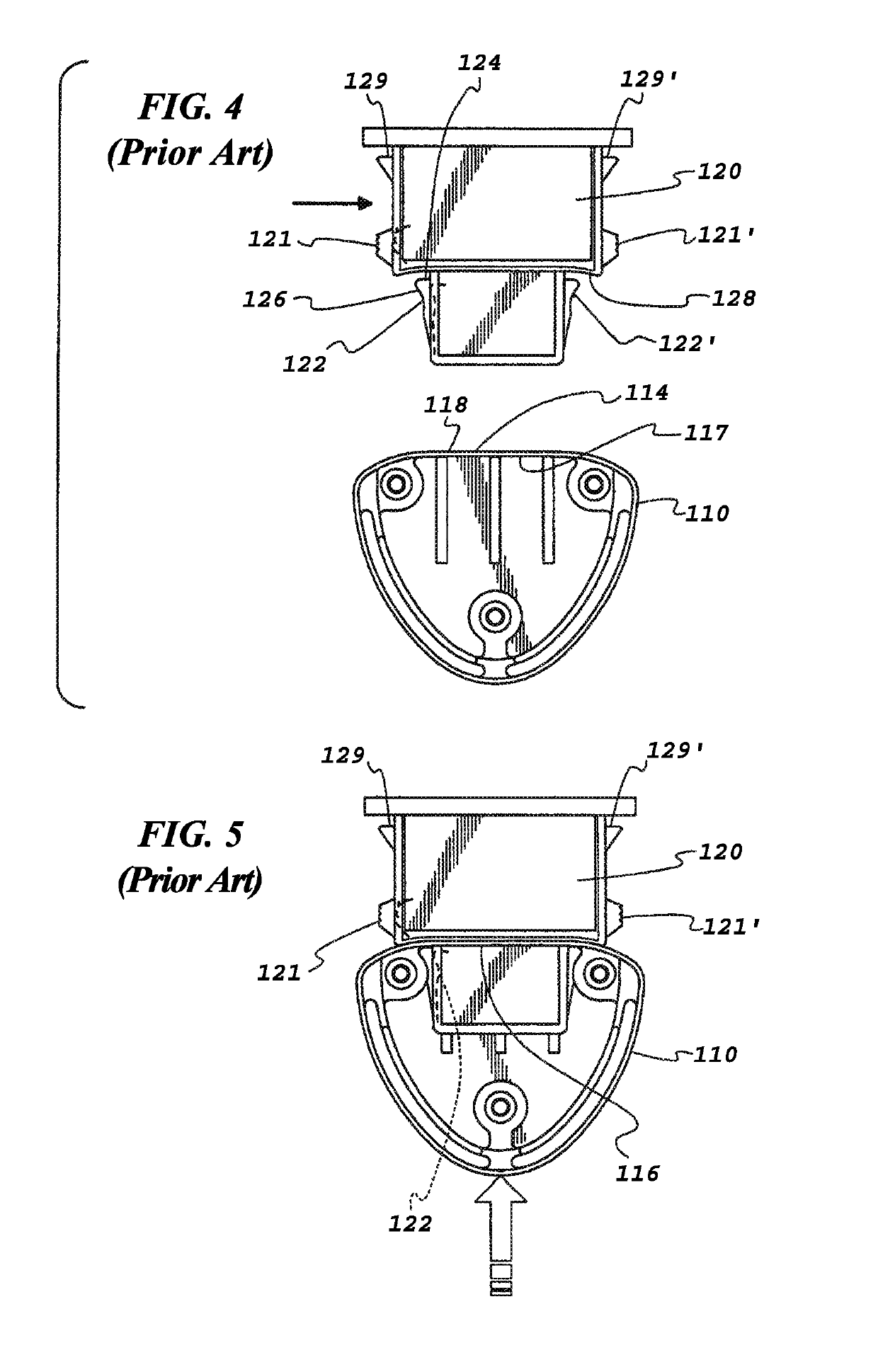

Connector system for lighting assembly

ActiveUS10488027B2Reliability issueEnsure safetyLighting support devicesElectric discharge tubesElectricityLED lamp

A support connector for maintaining an end of a linear LED lamp in an operative state on a support. The support connector comprises a nonconductive housing comprising a first portion including a mounting base at one end of the first portion configured to couple the support connector to the support. A second portion extends from the opposite end of the first portion and is configured to be insertable within an opening of a first end cap assembly of the linear LED lamp. First and second power electrical terminals are disposed within first and second receptacles of the support connector, and a grounding electrical terminal is disposed within a third receptacle, and the grounding electrical terminal is electrically isolated from the first and second power terminals. The first and second power electrical terminals mate with first and second conductive power pins of the end cap assembly, and the grounding electrical terminal is configured to mate with a grounding pin of the end cap assembly as the first end cap assembly is moved relative to the support connector from a position fully separated from the support connector in a path that is transverse to the length of the body into an engaged position.

Owner:DVA HLDG LLC

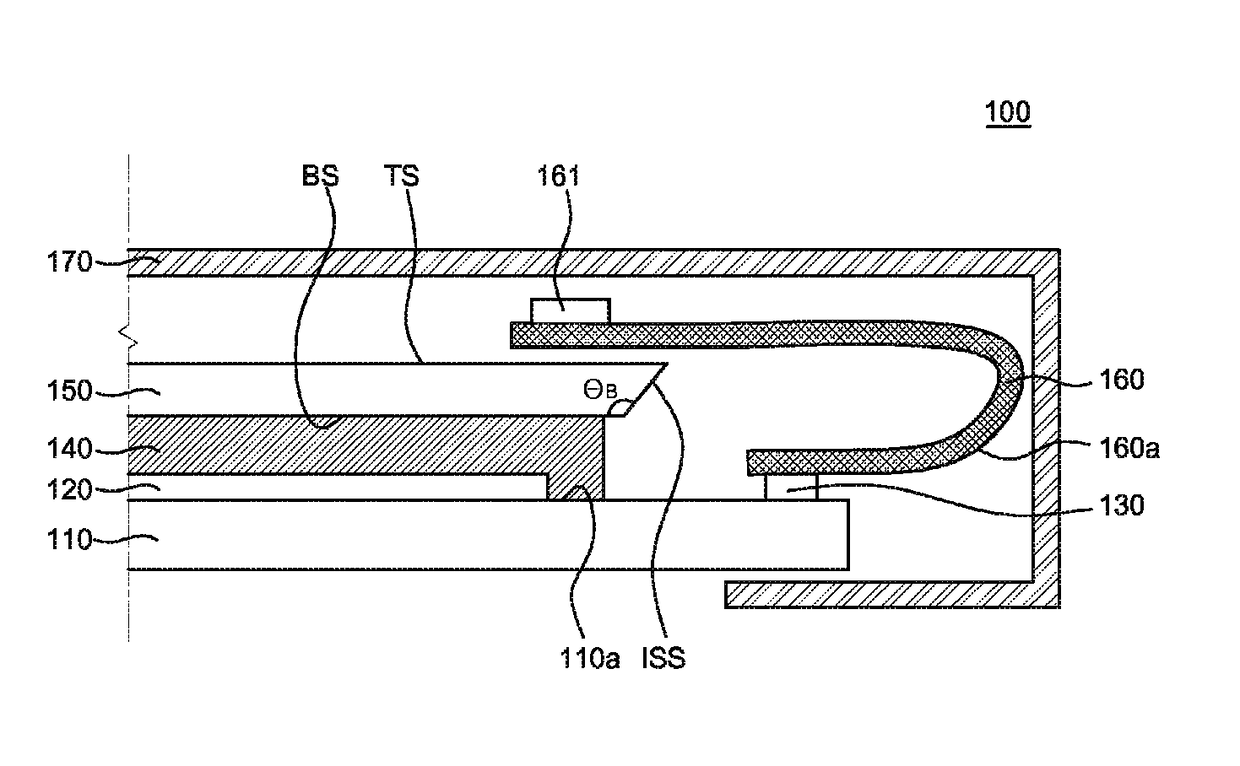

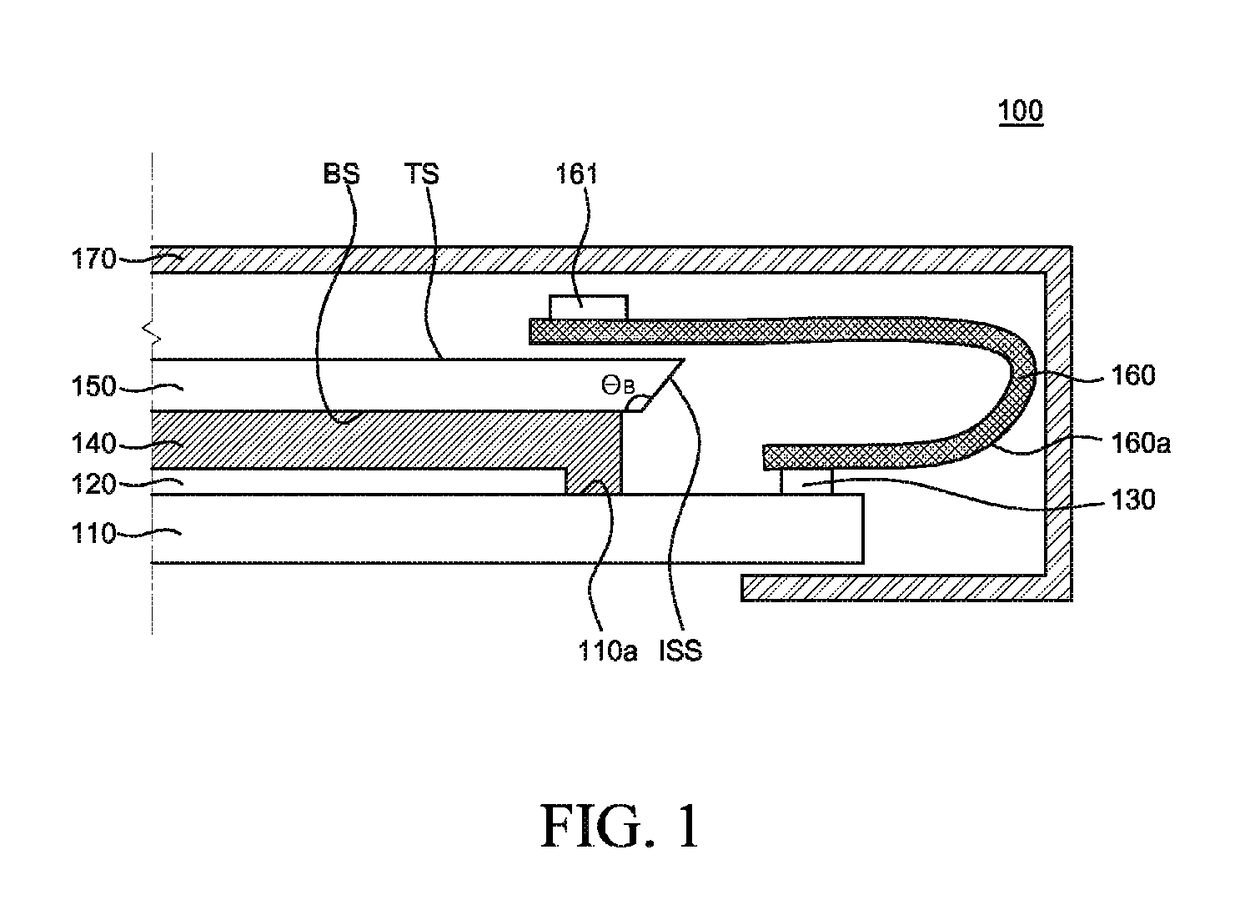

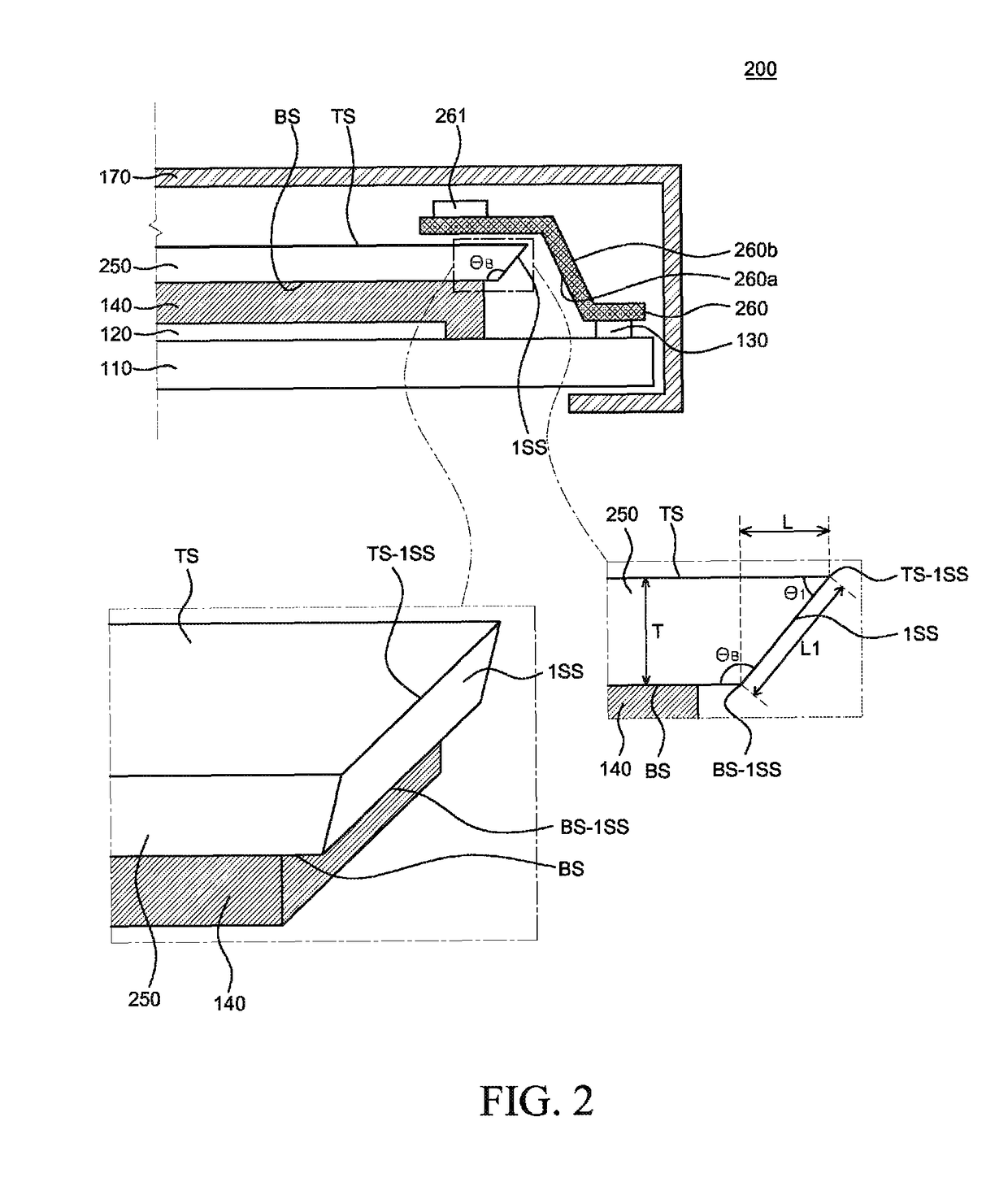

Organic light emitting display device

ActiveUS10021760B2Reliability issueImprove productivity and reliabilityElectroluminescent light sourcesSolid-state devicesDisplay deviceEngineering

An OLED device according to an example embodiment includes an organic light-emitting element between a lower substrate and an upper substrate. At least a part of a side surface of the upper substrate has a reverse-tapered shape configured to reduce damage to the lower substrate caused by deformation of the upper substrate due to an external impact. Accordingly, reliability issues resulting from a short circuit or burnt lines due to the deformation of the upper substrate may be resolved, improving overall reliability and productivity of an OLED device.

Owner:LG DISPLAY CO LTD

Structure and fabricating method with self-aligned bit line contact to word line in split gate flash

InactiveUS20050003622A1Reduce decreaseEliminates reliability issueSolid-state devicesSemiconductor/solid-state device manufacturingPolycrystalline siliconOxide

A new structure is disclosed for semiconductor devices in which contact regions are self-aligned to conductive lines. Openings to a gate oxide layer, in partially fabricated devices on a silicon substrate, have insulating sidewalls. First polysilicon lines disposed against the insulating sidewalls extend from below the top of the openings to the gate oxide layer. Oxide layers are grown over the top and exposed sides of the first polysilicon lines serving to insulate the first polysilicon lines. Polysilicon contact regions are disposed directly over and connect to silicon substrate regions through openings in the gate oxide layer and fill the available volume of the openings. Second polysilicon lines connect to the contact regions and are disposed over the oxide layers grown on the first polysilicon lines.

Owner:TAIWAN SEMICON MFG CO LTD

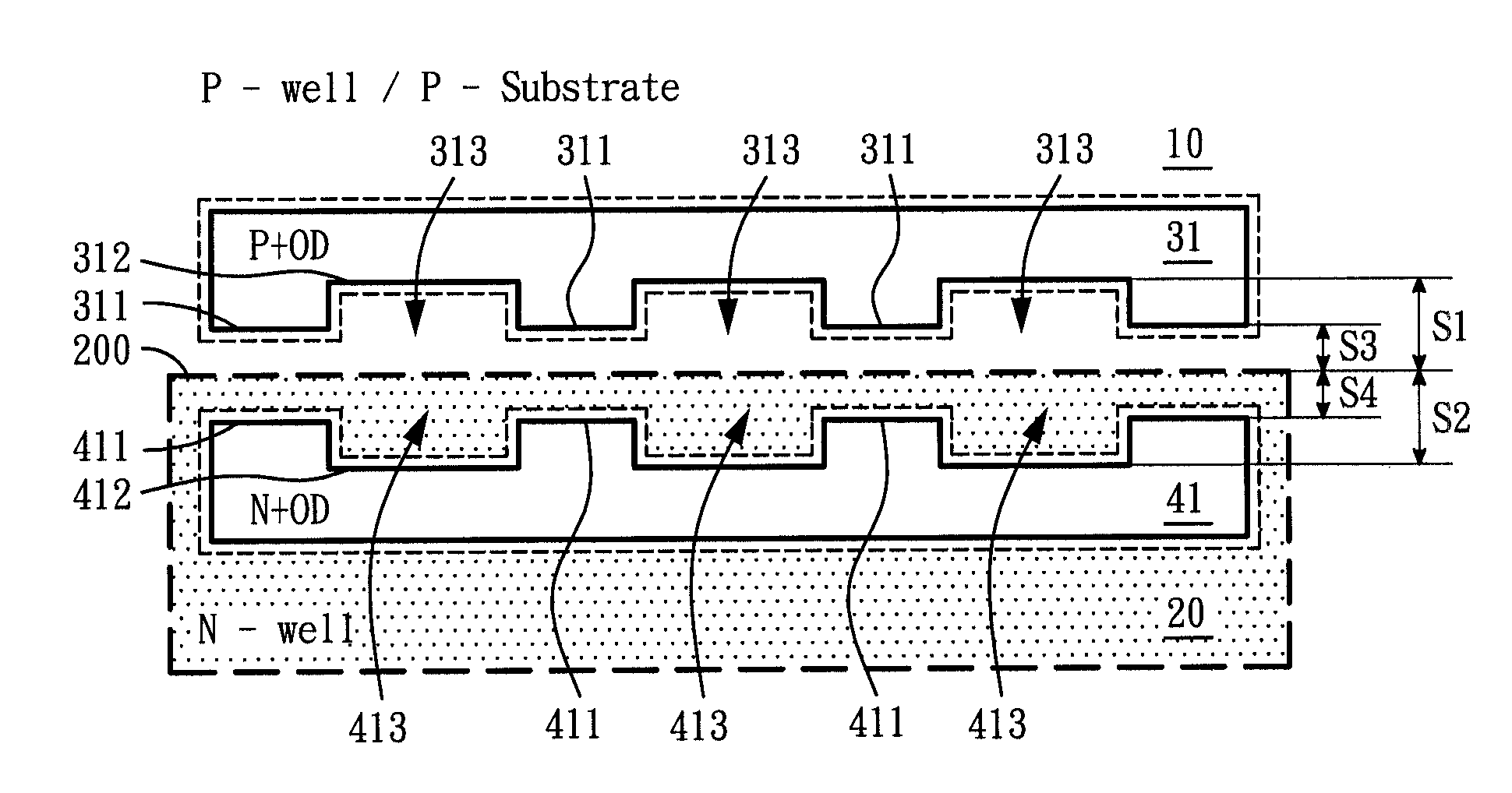

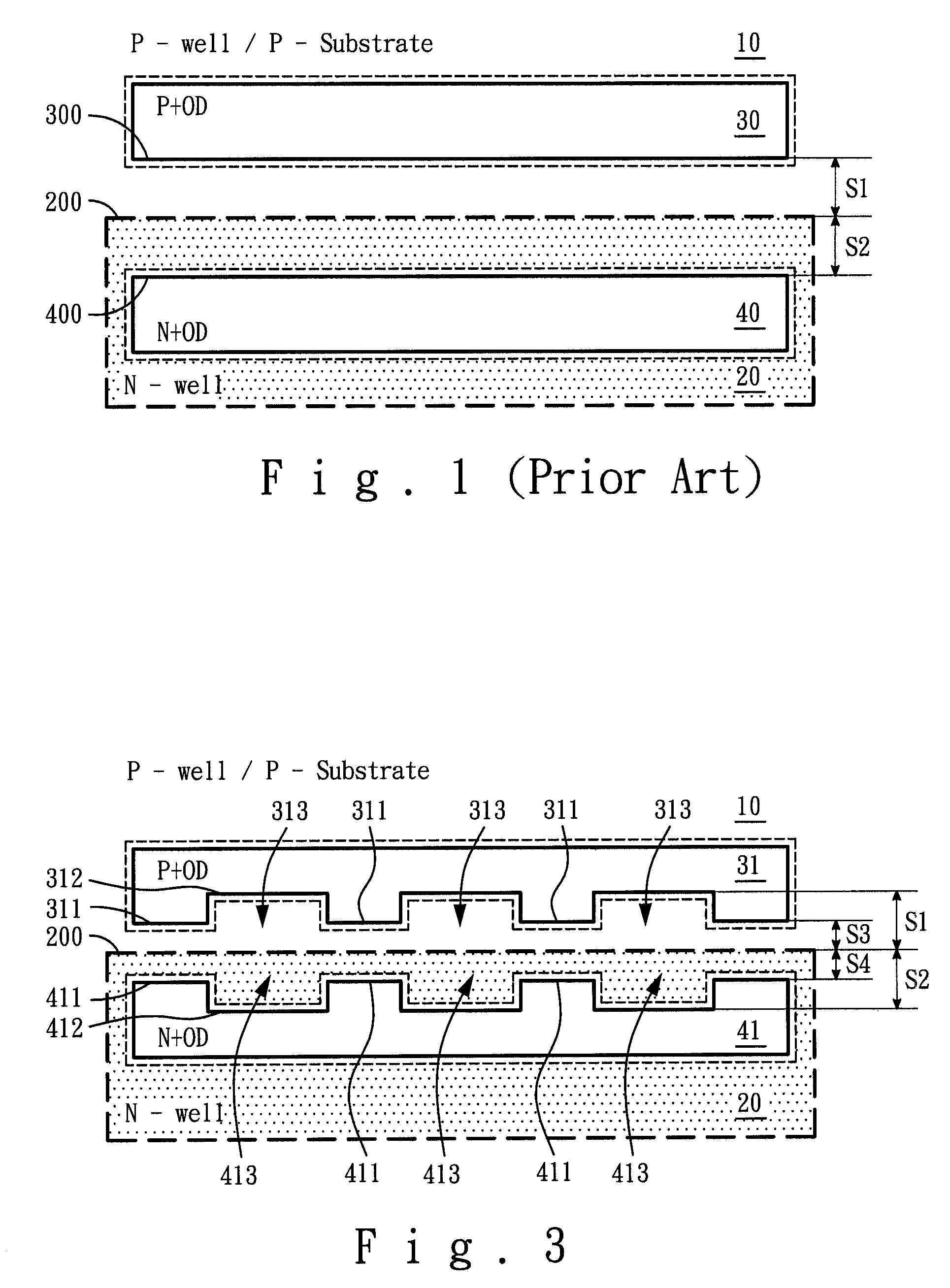

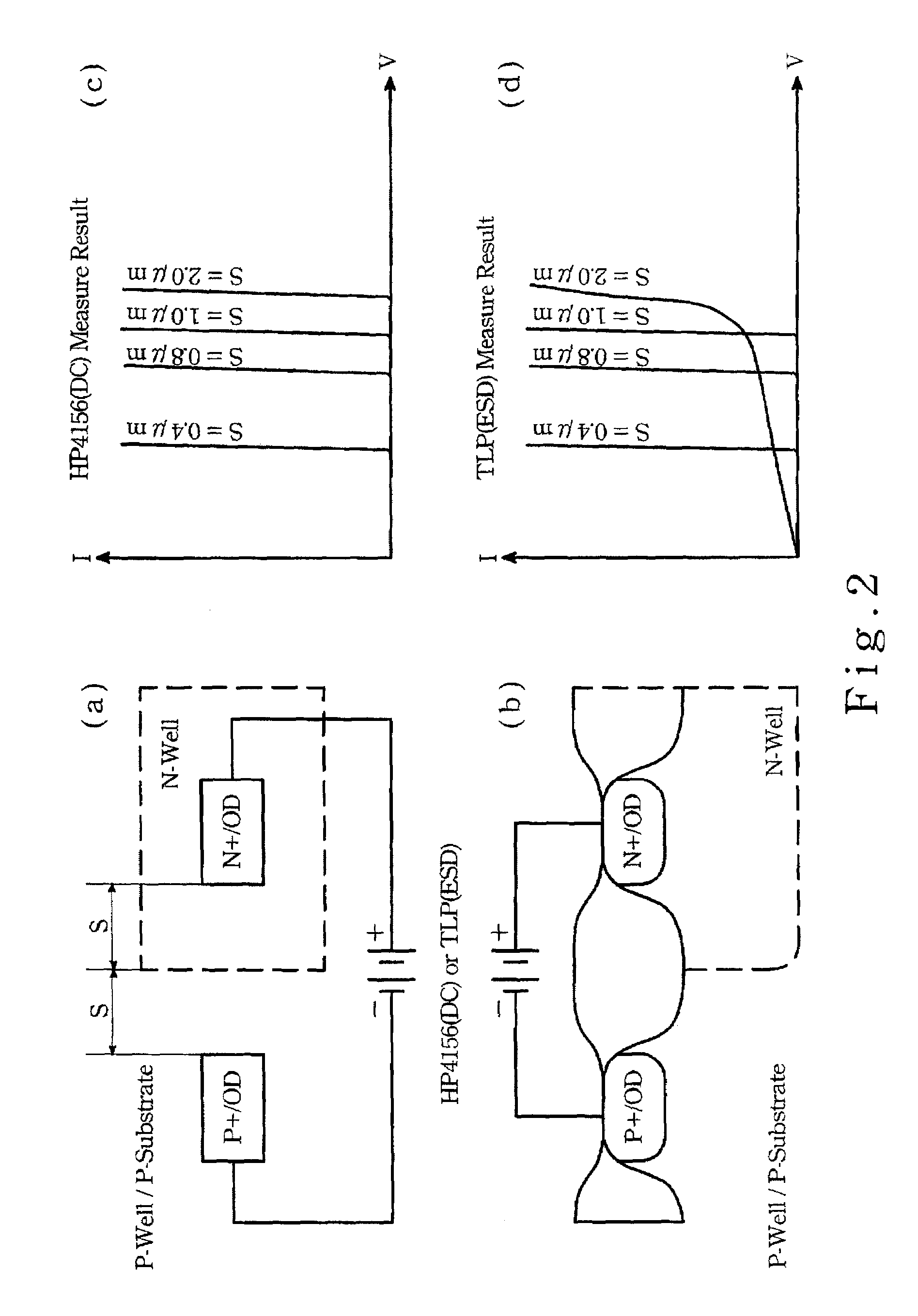

ESD device layout for effectively reducing internal circuit area and avoiding ESD and breakdown damage and effectively protecting high voltage IC

InactiveUS7855419B2Increased durabilityReduce chip areaTransistorSemiconductor/solid-state device detailsEngineeringHigh pressure

Owner:HIMAX TECH LTD

Organic light emitting display device

ActiveUS9967949B2Reliability issueImprove productivity and reliabilityElectroluminescent light sourcesSolid-state devicesProduction rateDisplay device

Owner:LG DISPLAY CO LTD