High-voltage tolerant power-rail ESD clamp circuit

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The present invention provides a high-voltage tolerant power-rail ESD clamp circuit, in which a substrate-triggered current is provided to drive different ESD protection elements under ESD stress. The substrate-triggered current has been reported to be beneficial to many ESD protection devices, such as the STNMOS (substrate-triggered NMOS) device, the SCR device, and the FOD (field oxide) device. The substrate-triggered current can improve ESD robustness of these ESD protection devices by increasing their turn-on speed and turn-on uniformity under ESD stress.

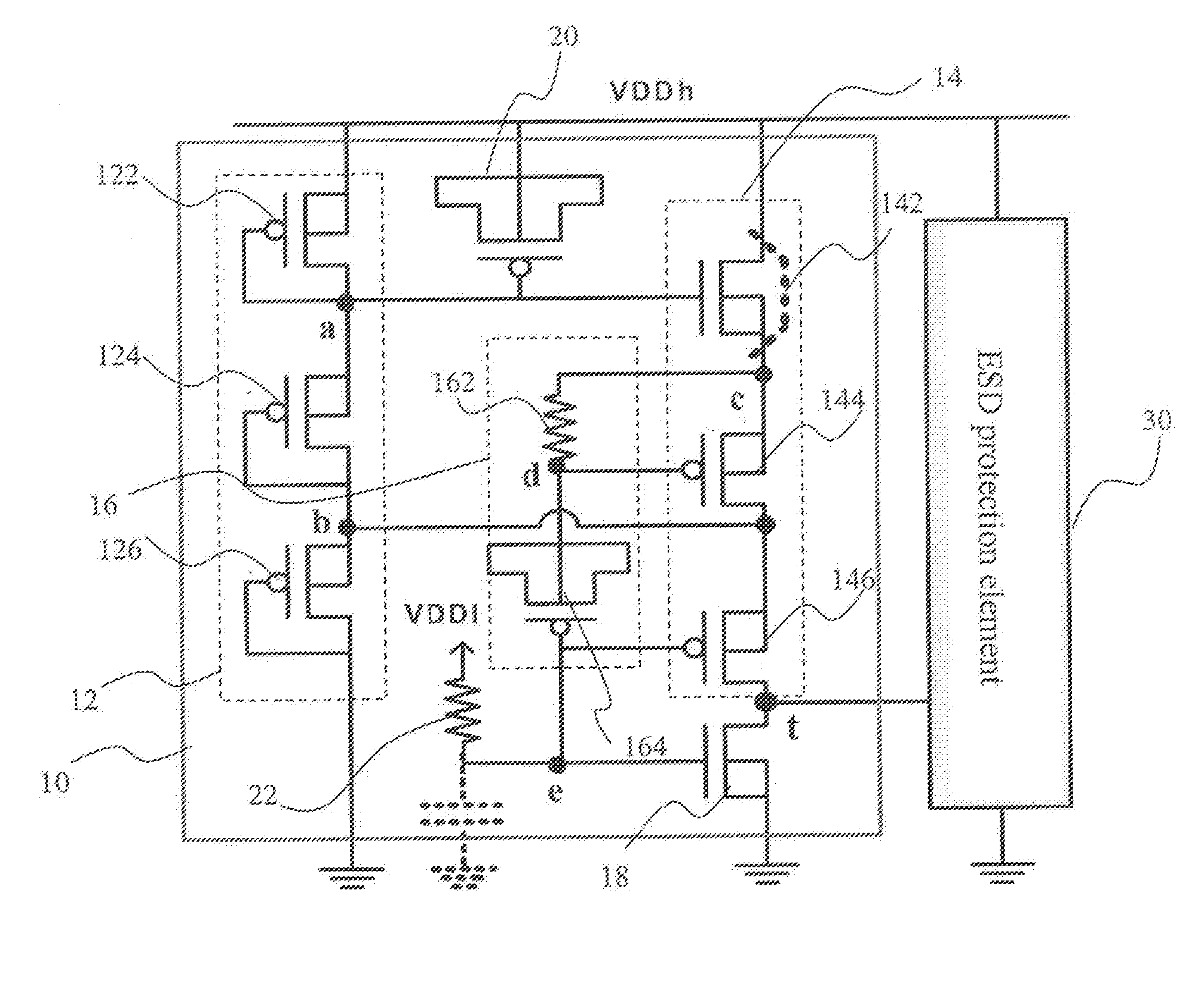

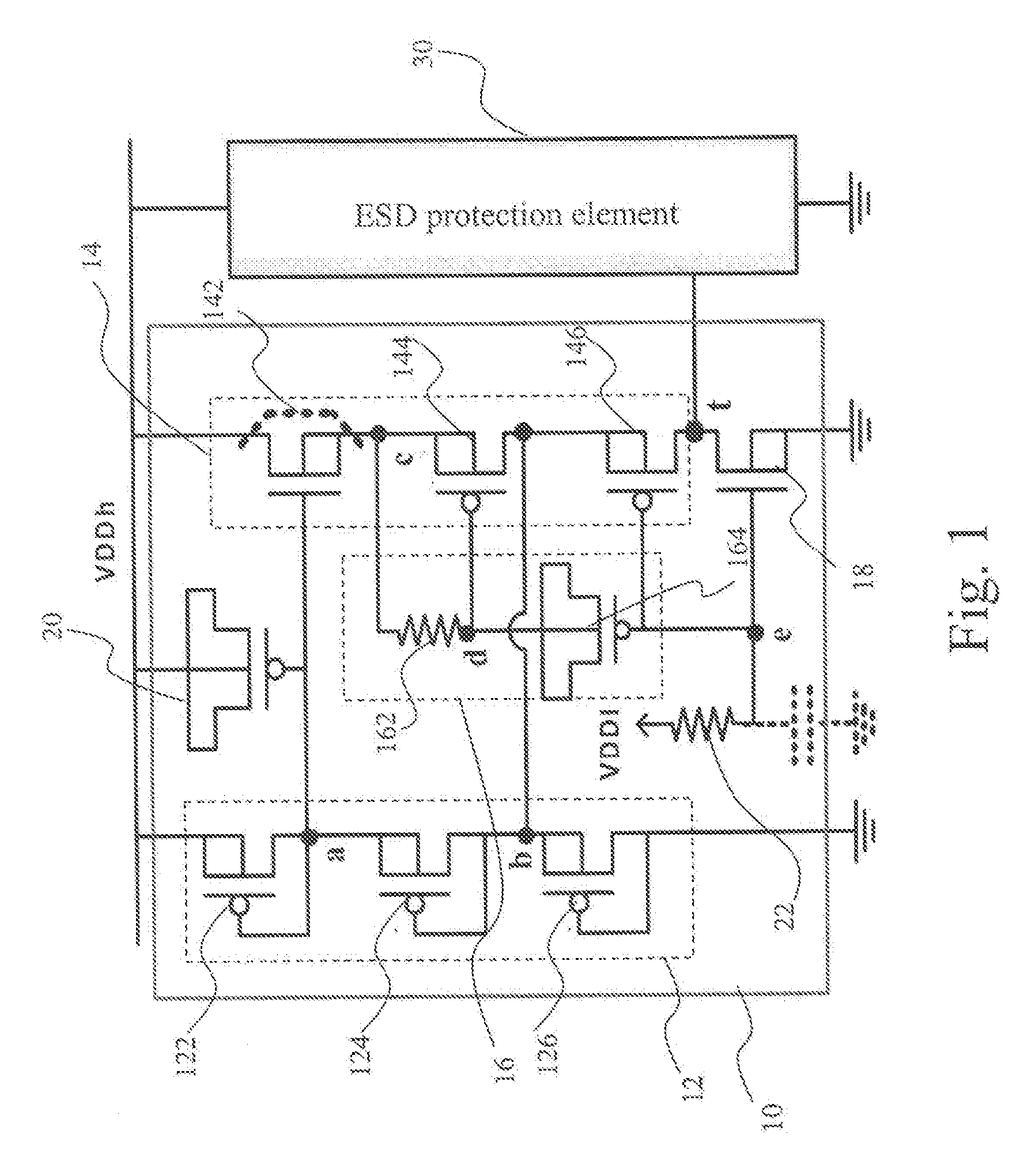

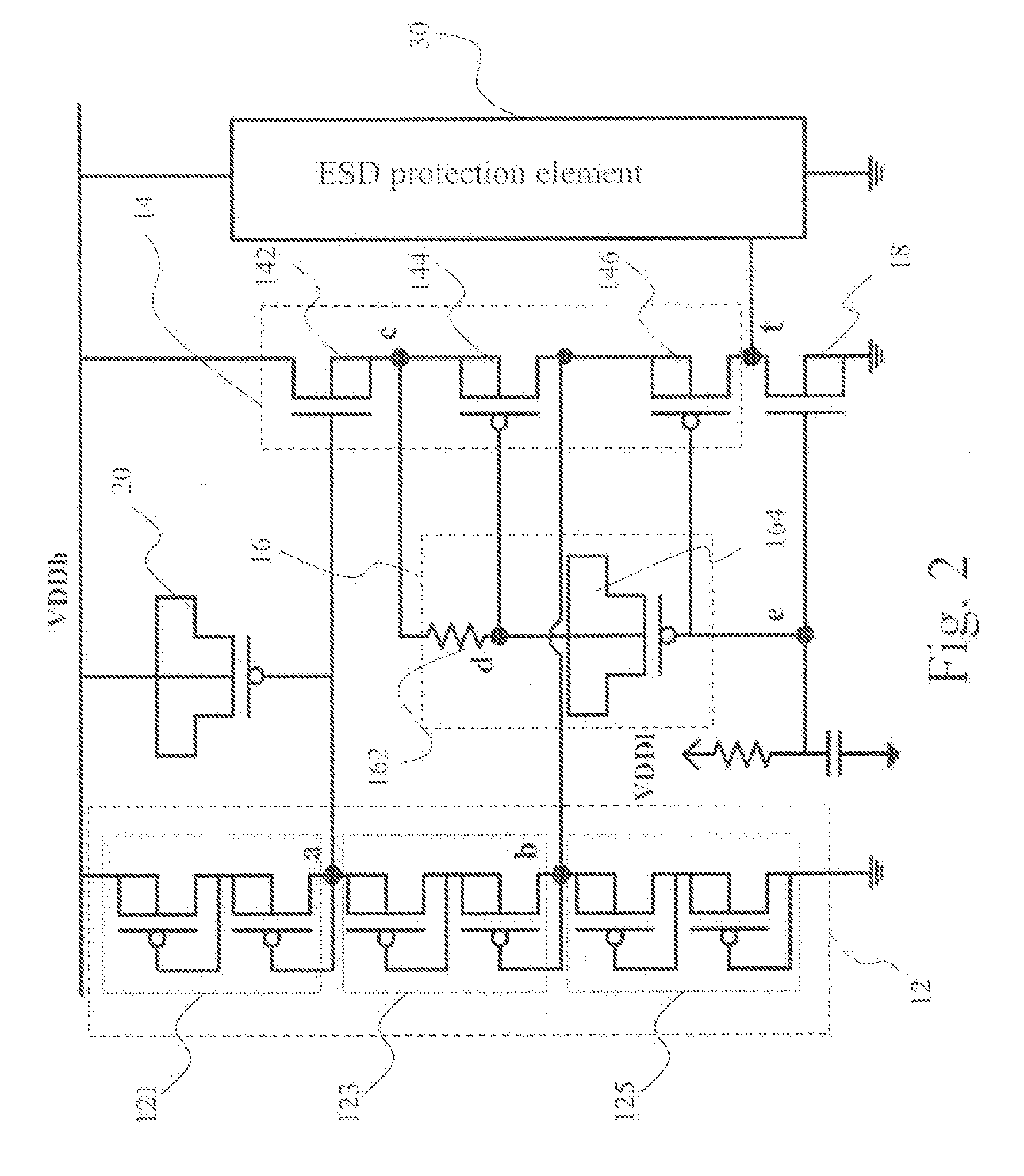

[0020] As shown in FIG. 1, a power-rail ESD clamp circuit of the present invention comprises two voltage sources VDDh and VDDl, an ESD detection circuit 10 and an ESD protection element 30. The ESD detection circuit 10 is composed of a voltage divider 12, a substrate driver 14, an RC distinguisher 16, a fourth transistor 18, a fifth transistor 20 and a second resistor 22. The voltage divider 12 includes three p-type tran...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More