SRAM cell with column select line

a column select line and sram technology, applied in the field of sram array structure, can solve the problems of increasing the difficulty of designing an sram cell, snm degradation, and cells generally suffering from much, so as to minimize data upset and power dissipation, increase read current, and optimize static noise margin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

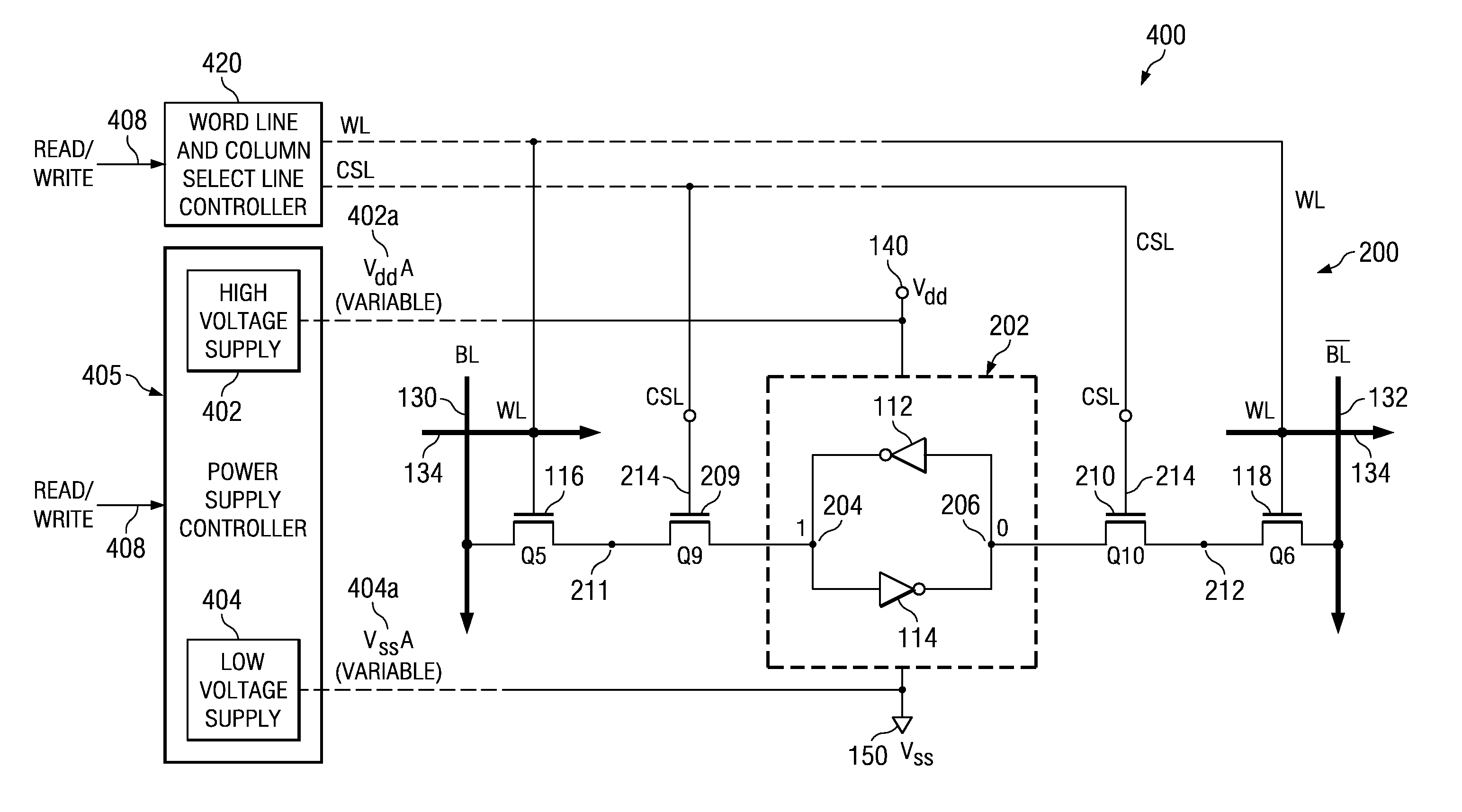

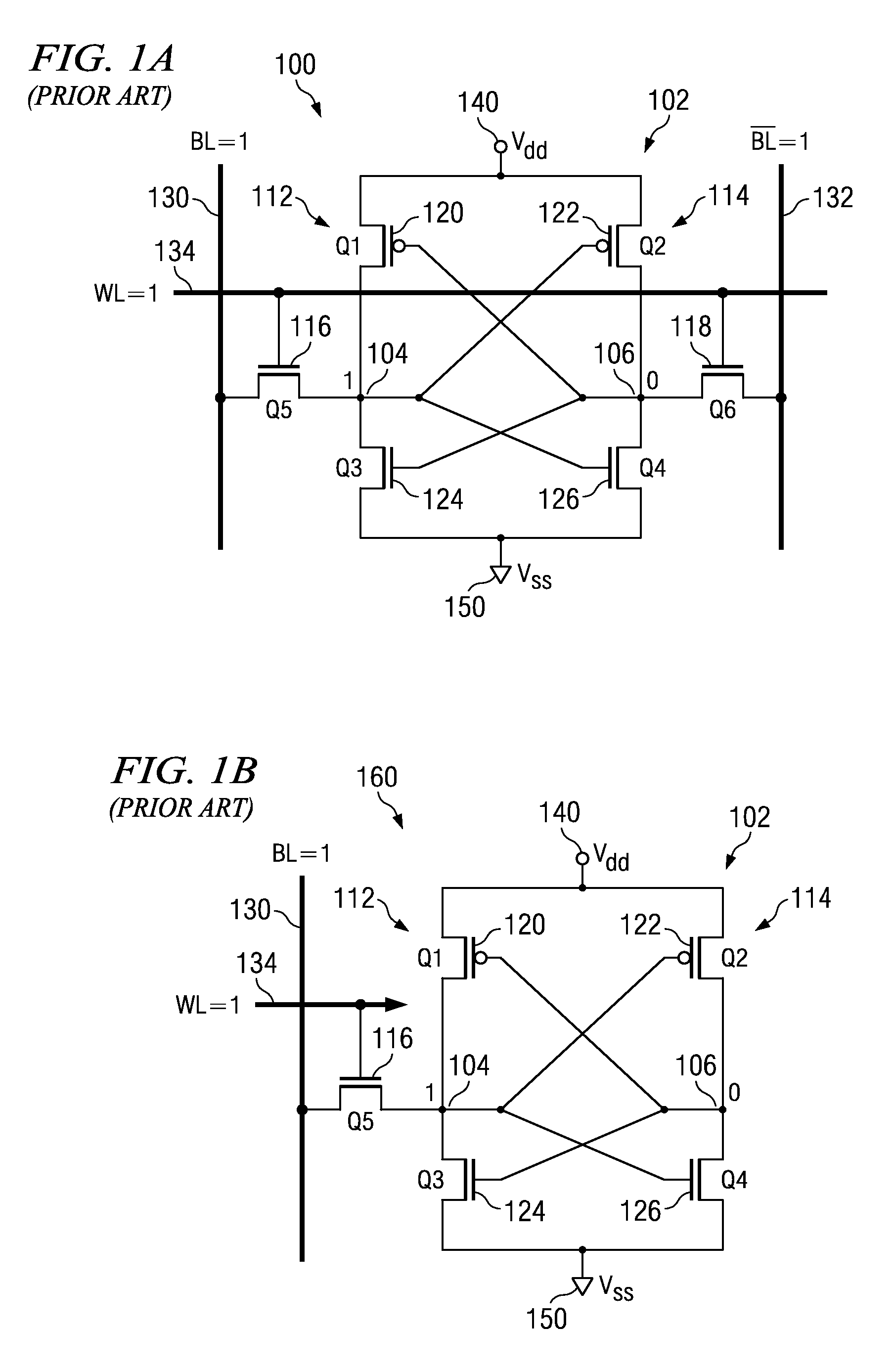

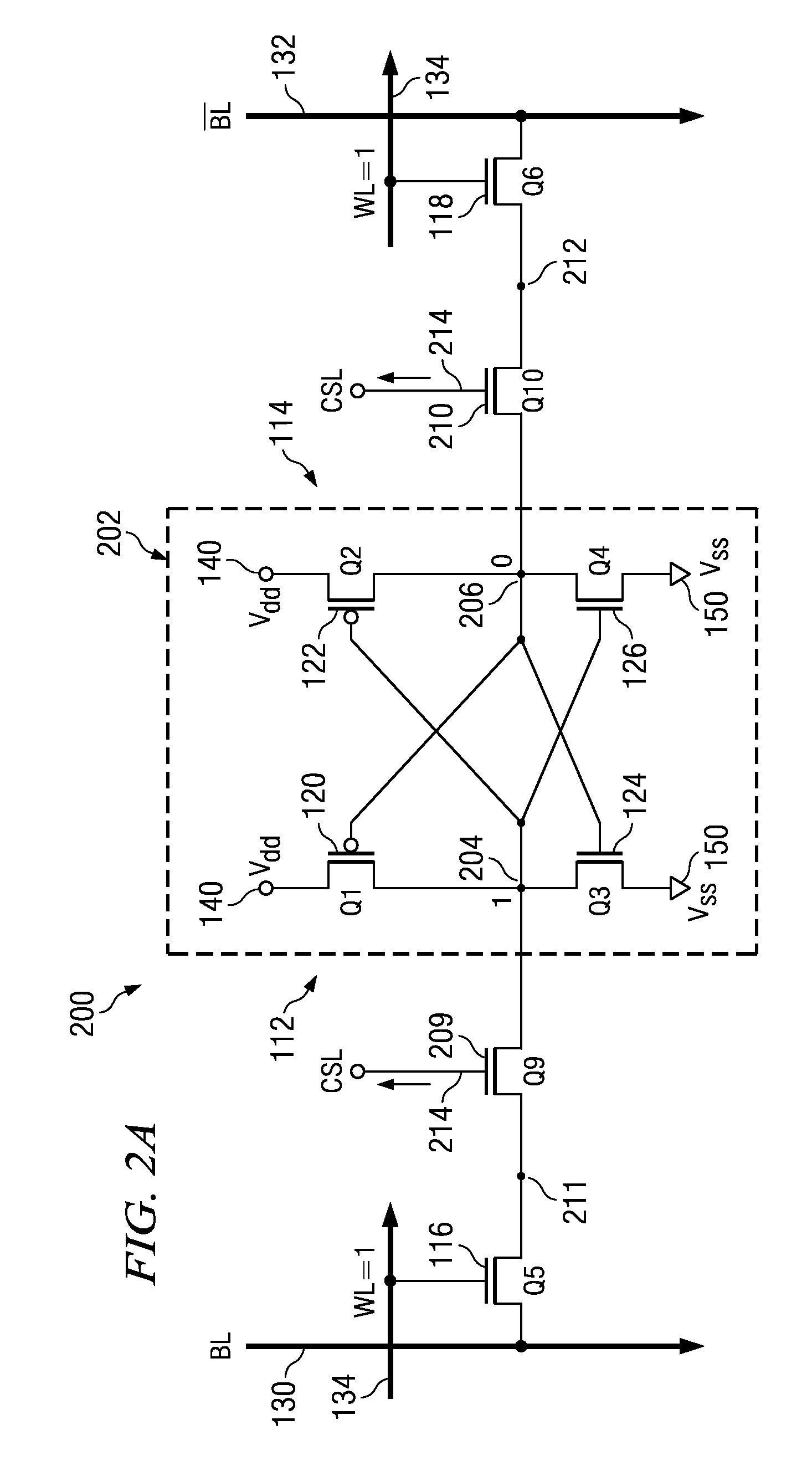

[0042] The present invention will now be described with reference to the attached drawings, wherein like reference numerals are used to refer to like elements throughout. The invention provides an improved SRAM array structure comprising SRAM cells (e.g., single sided 6T or differential 8T cells) having variable high and low voltage power supplies and a method of operating the SRAM array that provides a write bias condition during a write operation and a read bias condition during a read operation, wherein the read bias condition is different from the write bias condition.

[0043] The system and method provides optimum static noise margin while minimizing data upsets and power dissipation during read and write operations, by allowing the array supply voltage to be kept low during all but the read operation and then, enabled by a column select, only raising the supply to the selected columns to provide increased read current. In addition, by avoiding boosting the array supply and word...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More