Patents

Literature

334 results about "Test subject" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Systems and methods for monitoring behavior informatics

InactiveUS7269516B2Improve abilitiesIncrease powerDrug and medicationsCharacter and pattern recognitionBehavioral neurologyDiagnosis laboratory

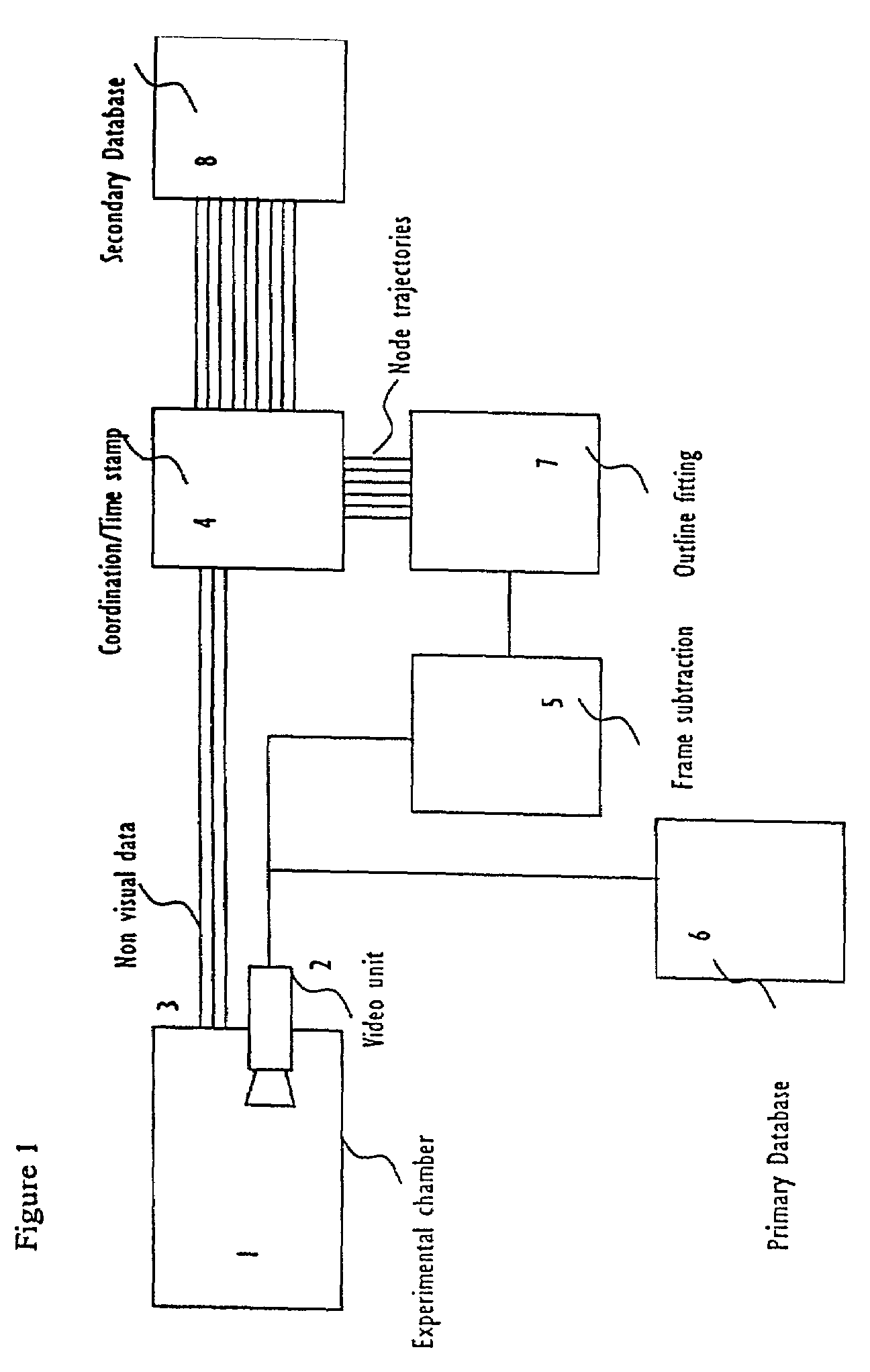

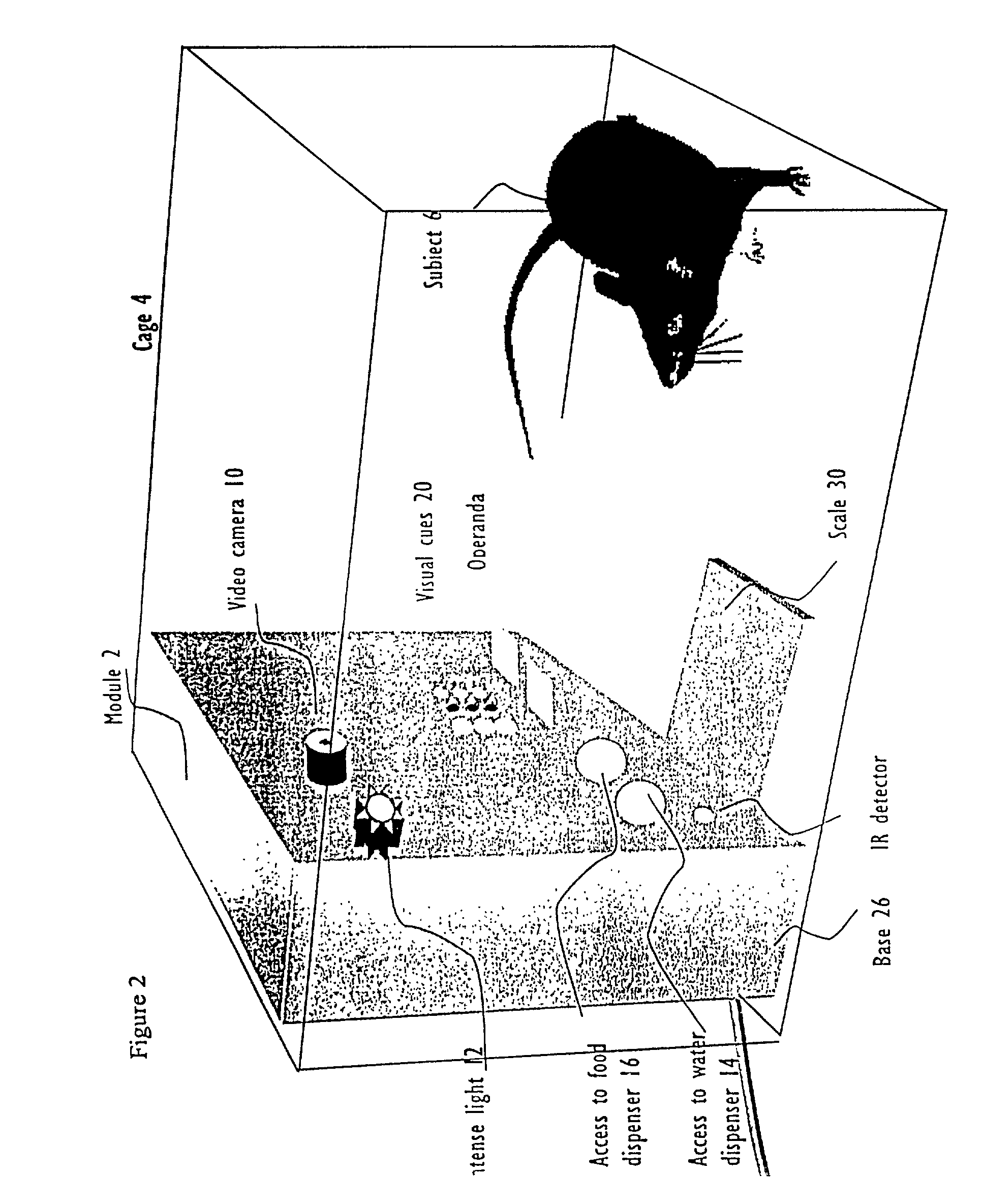

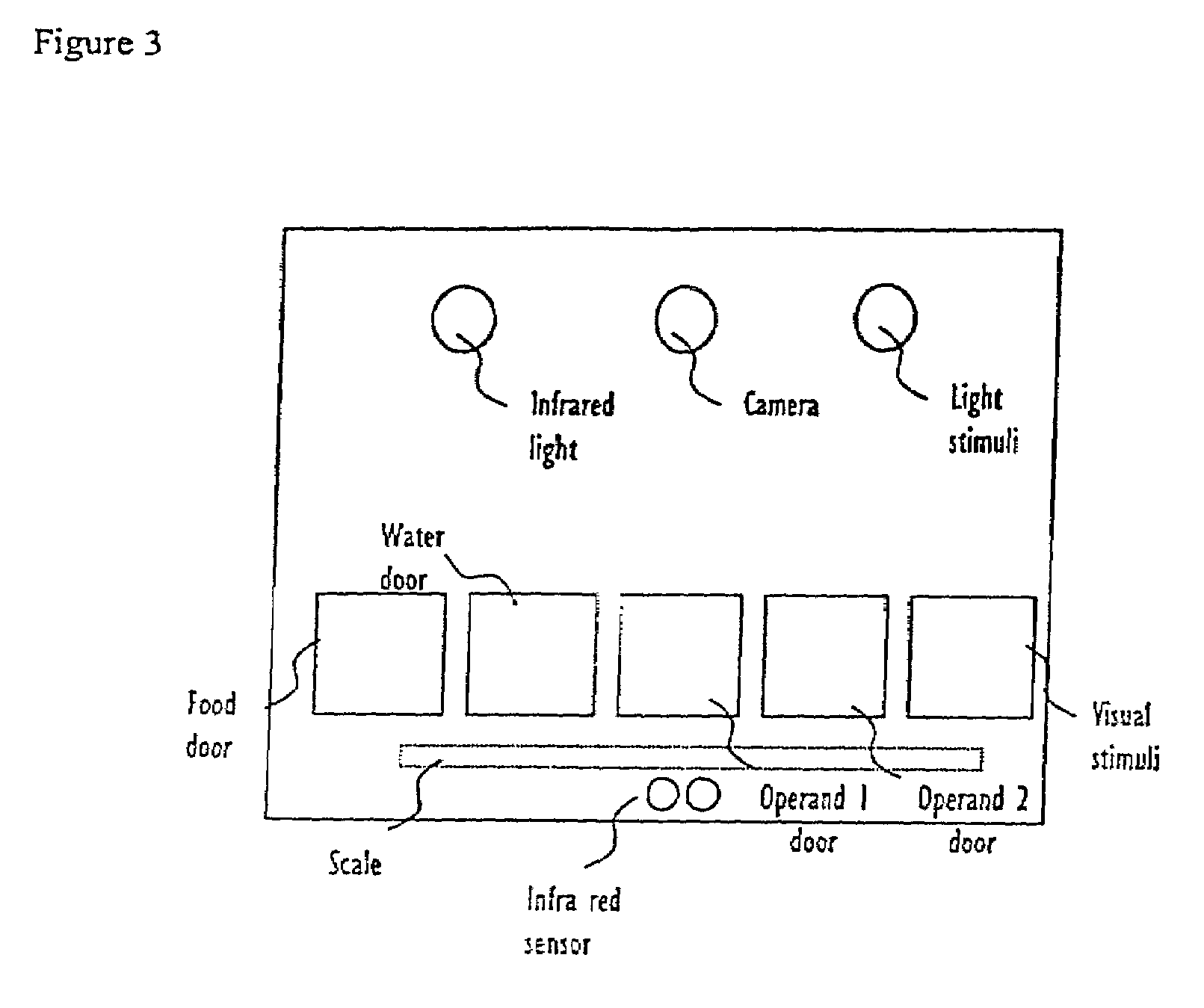

A system and method used to assess animal behavior includes a module having sensors that collects a variety of physical and biological data from a test subject. Interpretation of the data is provided to assess the test subject's behavior, neurology, biochemistry and physiology. The module is useful in observing the effects of a drug on the test animal and providing information on the drug's signature. Another advantage is the module's portability that allows it to be used in standard laboratory cages. This portability allows the animal to be tested in its own habitat, that can reduce any erroneous data due to stressing the animal when removed to a test cage. Additionally, the module's design allows for parallel data collection and interpretation from several laboratory animals undergoing different experiments. Multi-dimensional modeling of the test subject based the system's interpretation of the data allows pattern recognition of the drug signature, and predictive drug analysis.

Owner:CARNEGIE MELLON UNIV +1

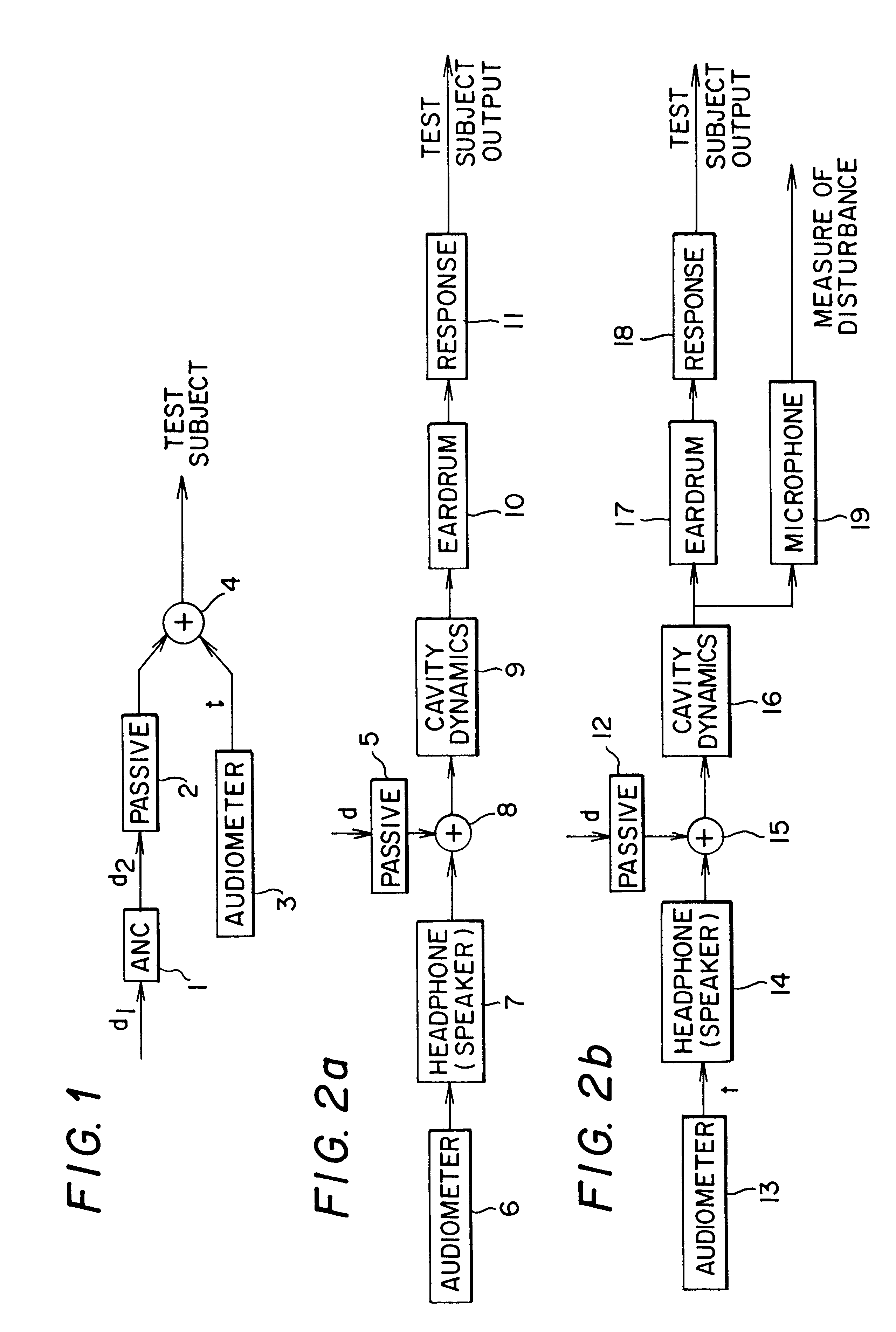

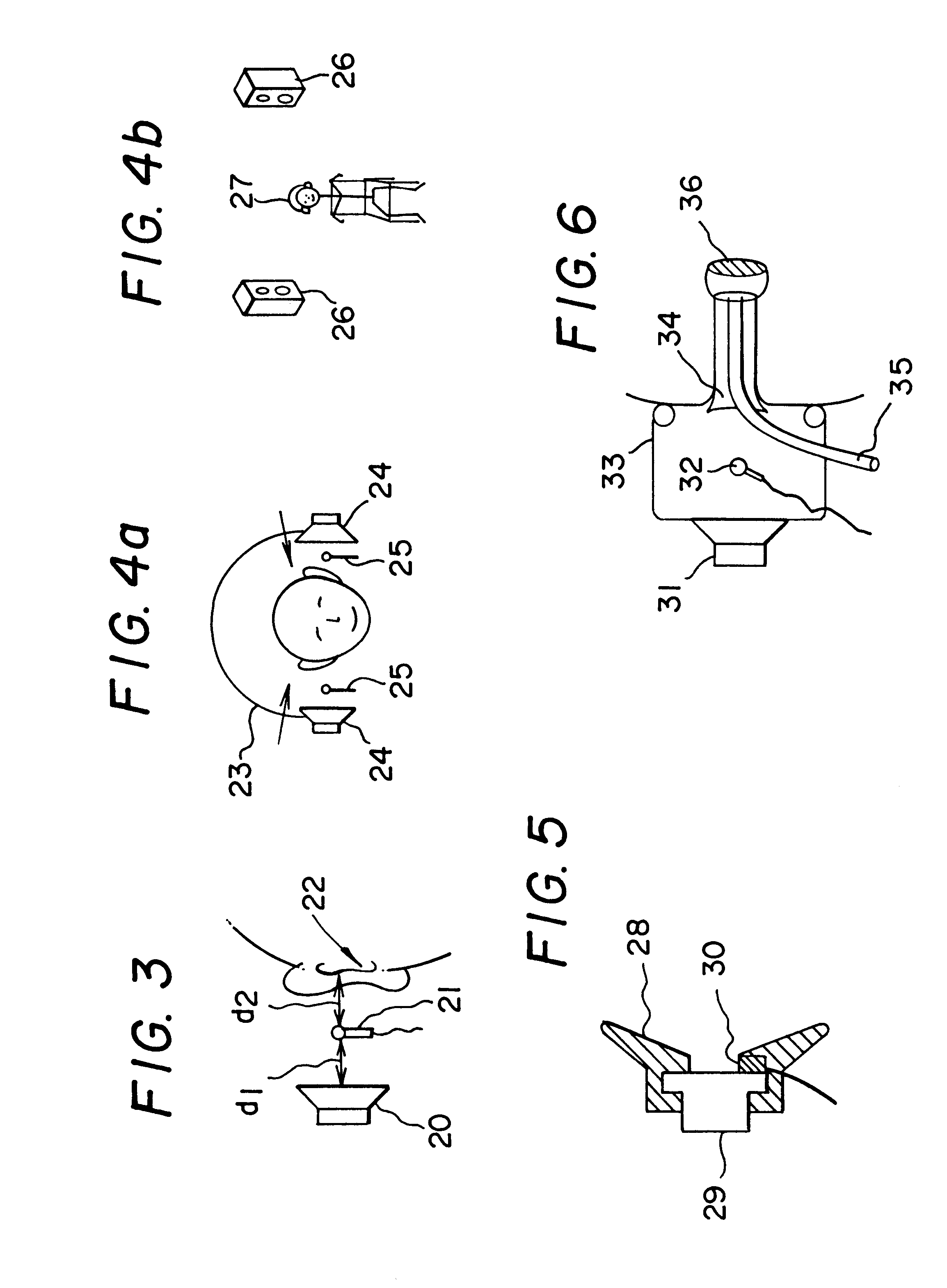

Active noise reduction for audiometry

InactiveUS6396930B1Maximize noise control performanceAccurate comparisonEar treatmentAudiometeringNoise controlNoise field

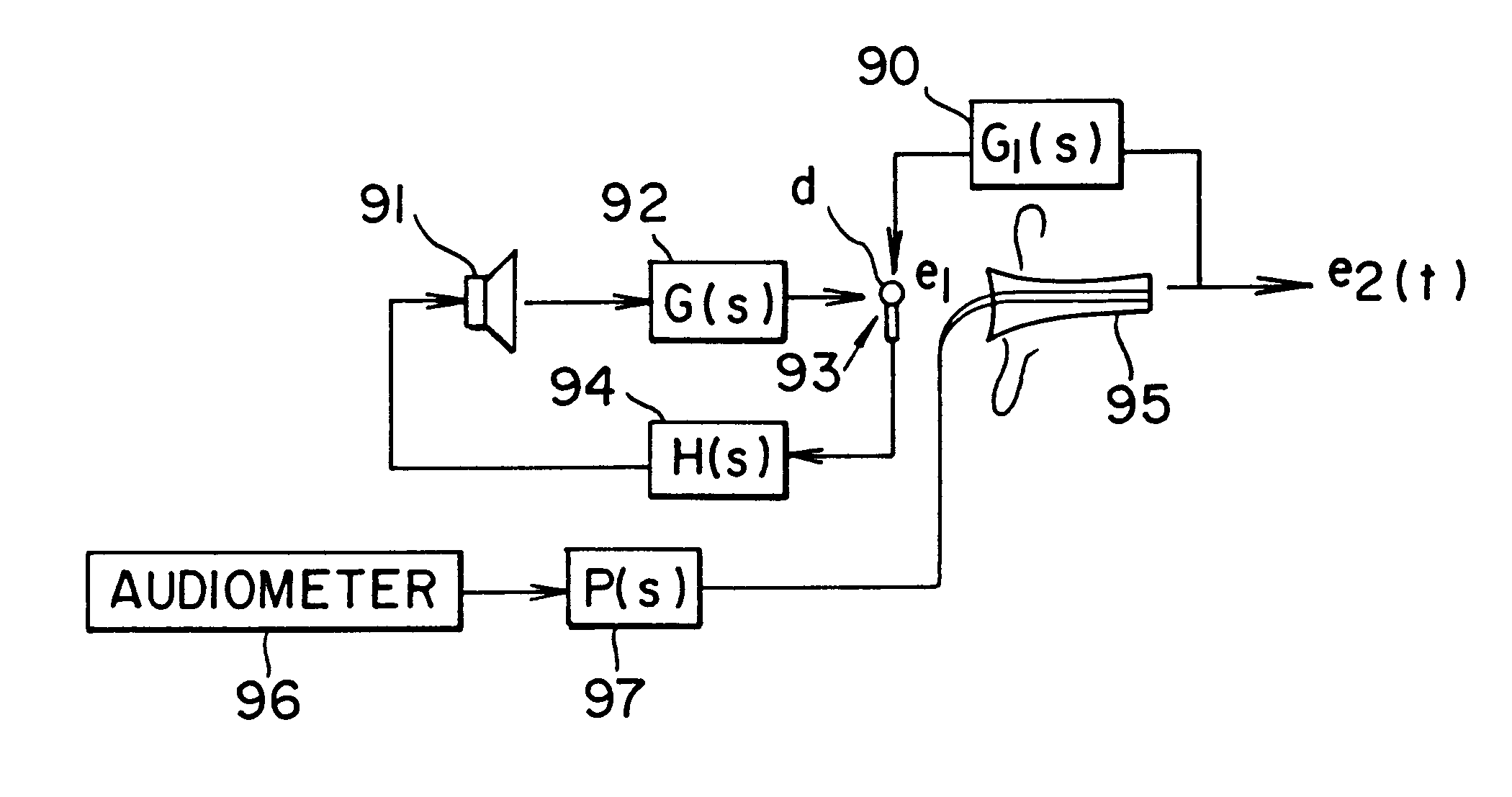

The technology of active noise reduction (ANR) is incorporated into audiometry testing in a variety of formats. Analog feedback, digital feedback, adaptive feedforward, and adaptive feedback noise control schemes are presented for use in audiometry to reduce the ambient noise heard by the test subject, allowing subject testing in higher ambient noise fields. Audiometer test signals are appropriately compensated so the test results are accurate and comply with existing calibration standards for audiometers. Existing audiometry headphone technologies are modified so that ANR can be accomplished while satisfying existing standards for audiometric testing. Embodiments are also defined for alternate headphone arrangements that may not conform to current (1997) audiometric testing standards but provide sufficient performance advantages to warrant new standards for audiometry testing in the future.

Owner:GENTEX CORP

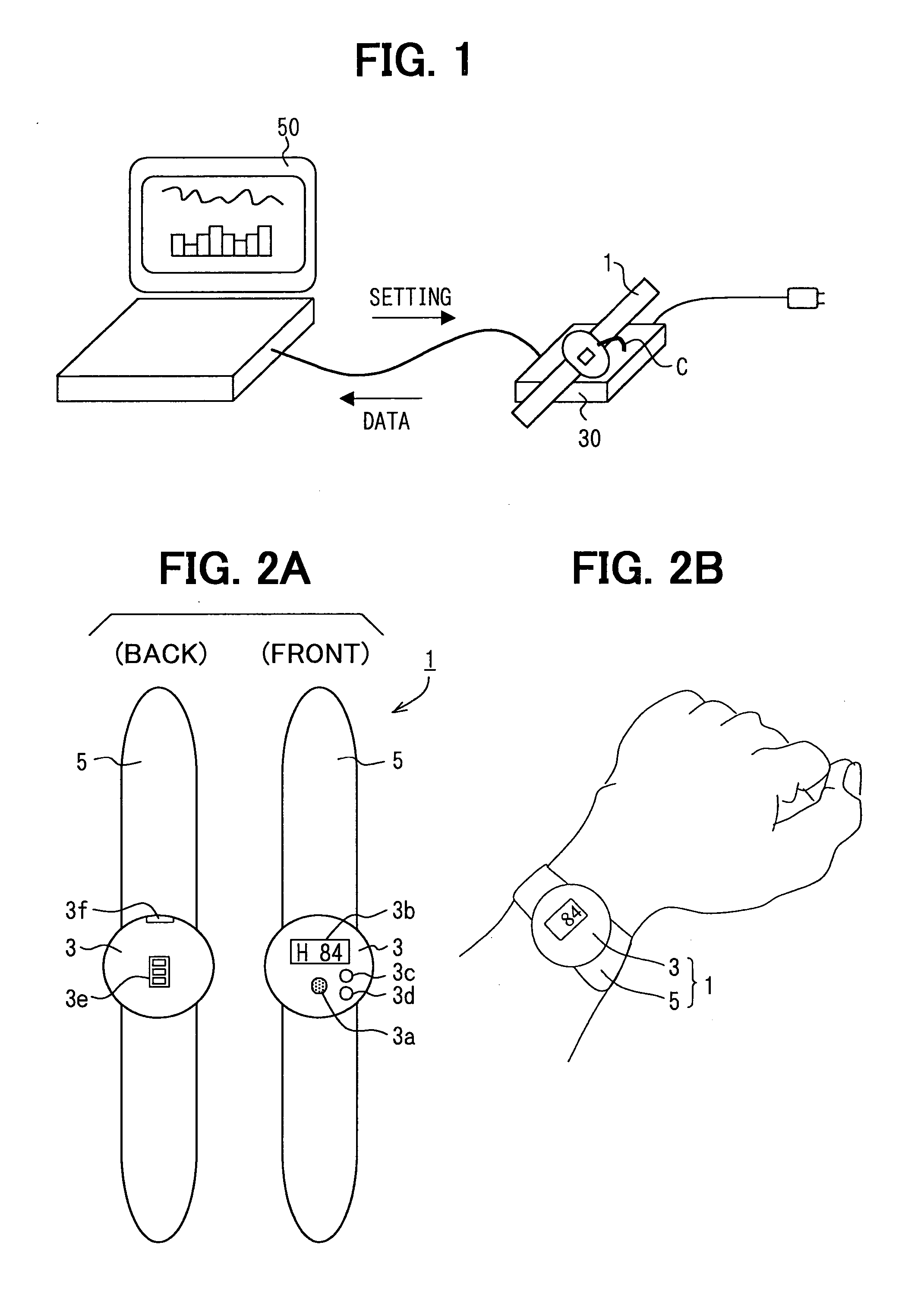

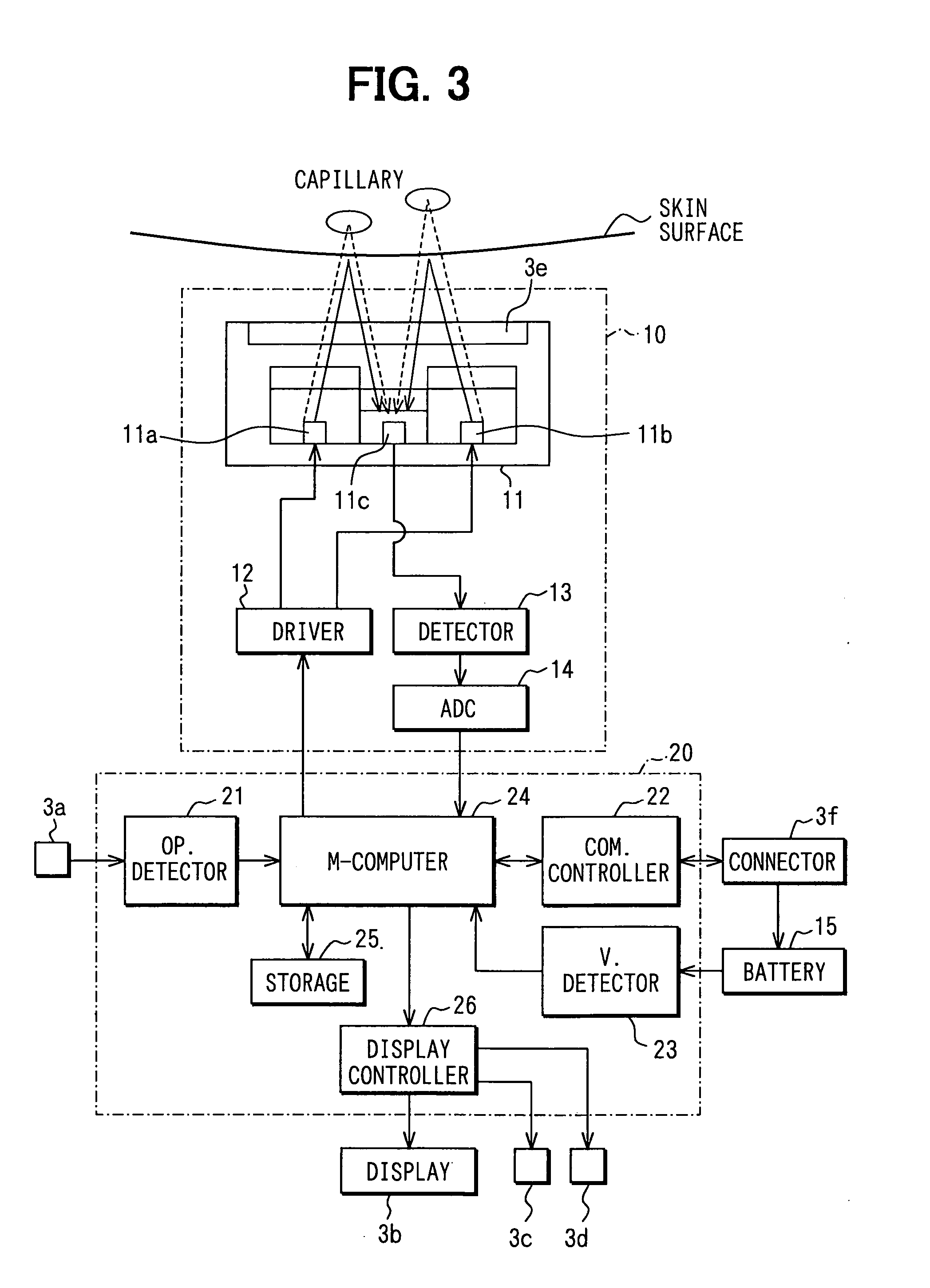

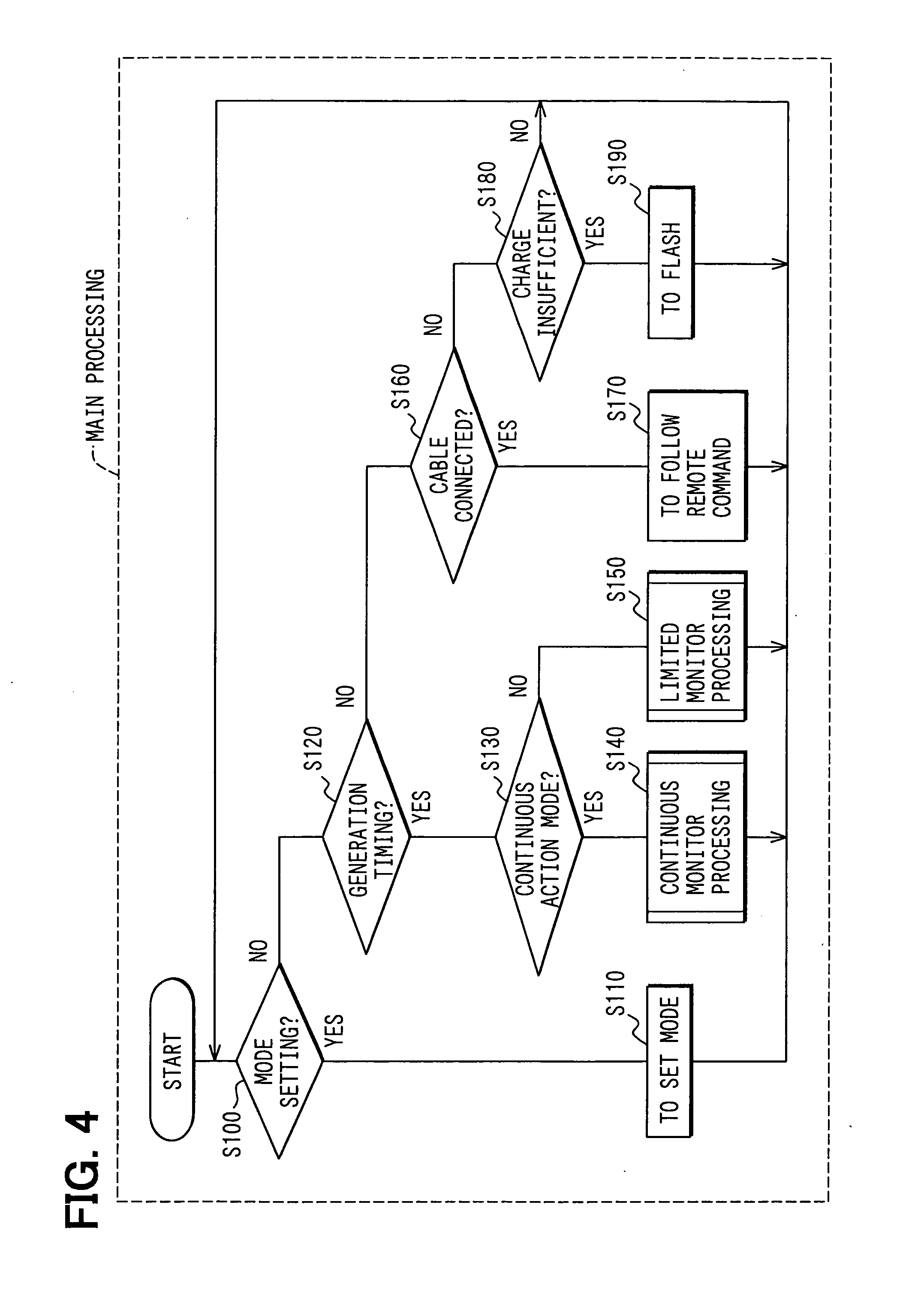

Portable biological information monitor apparatus and information management apparatus

In a portable biological information monitor apparatus, a pulse wave detection signal obtained by light emission from a green LED and a body motion detection signal obtained by light emission from an infrared LED are detected as biological information. This biological information is analyzed to compute various barometers. In a wake normal mode of a set generation mode, body motion and pulse are calculated as wake evaluation barometers for evaluation of a test subject's status in wake. In a wake steady state motion mode, body motion, pulse, and pitch are calculated as motion evaluation barometers for evaluation of the test subject's status in steady state motion. In a sleep mode, body motion, pulse, and autonomic nervous function are calculated as sleep evaluation barometers for evaluation of the test subject's status in sleep. Necessary barometers are thereby generated regardless of the test subject's action using the portable monitor apparatus alone.

Owner:DENSO CORP

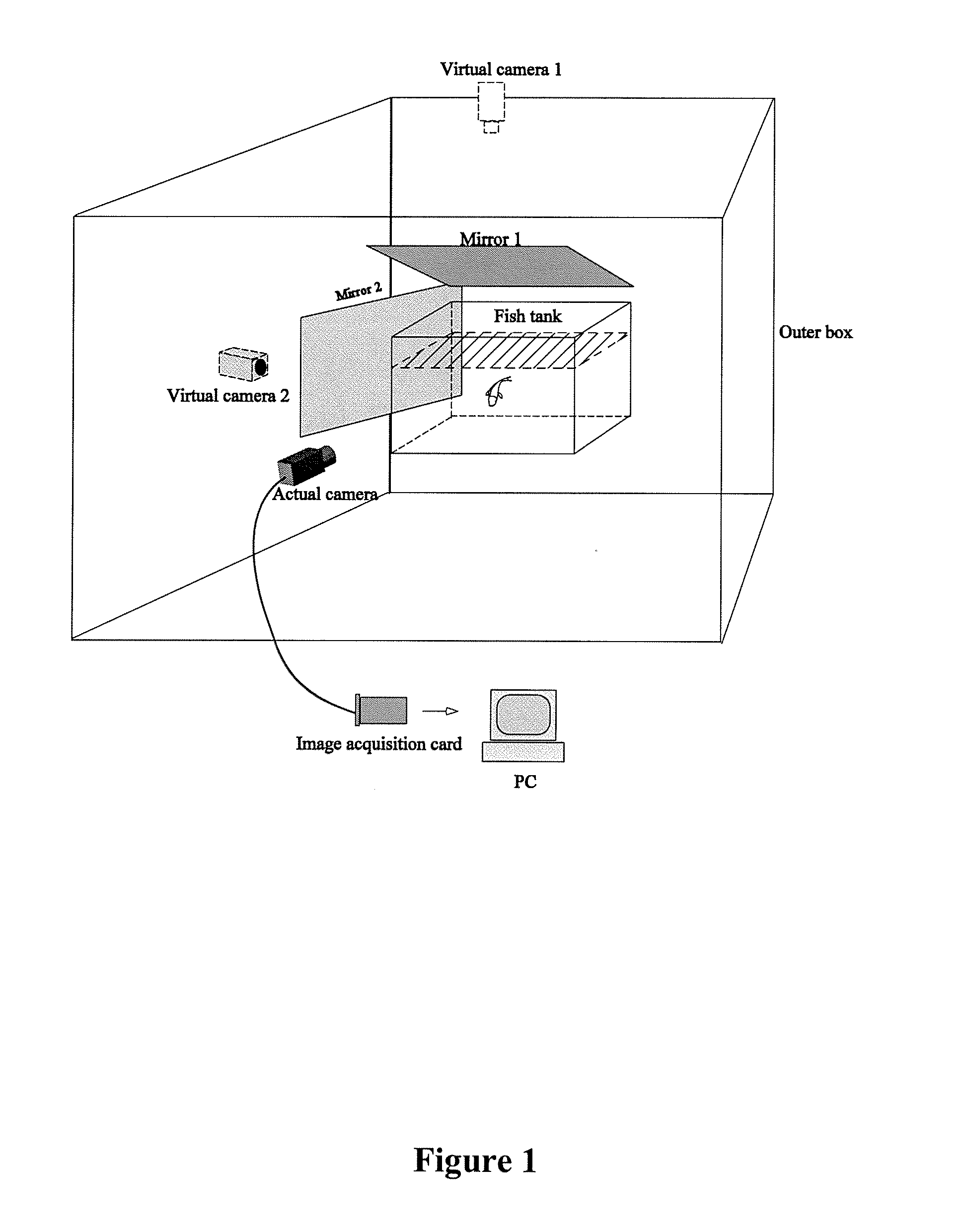

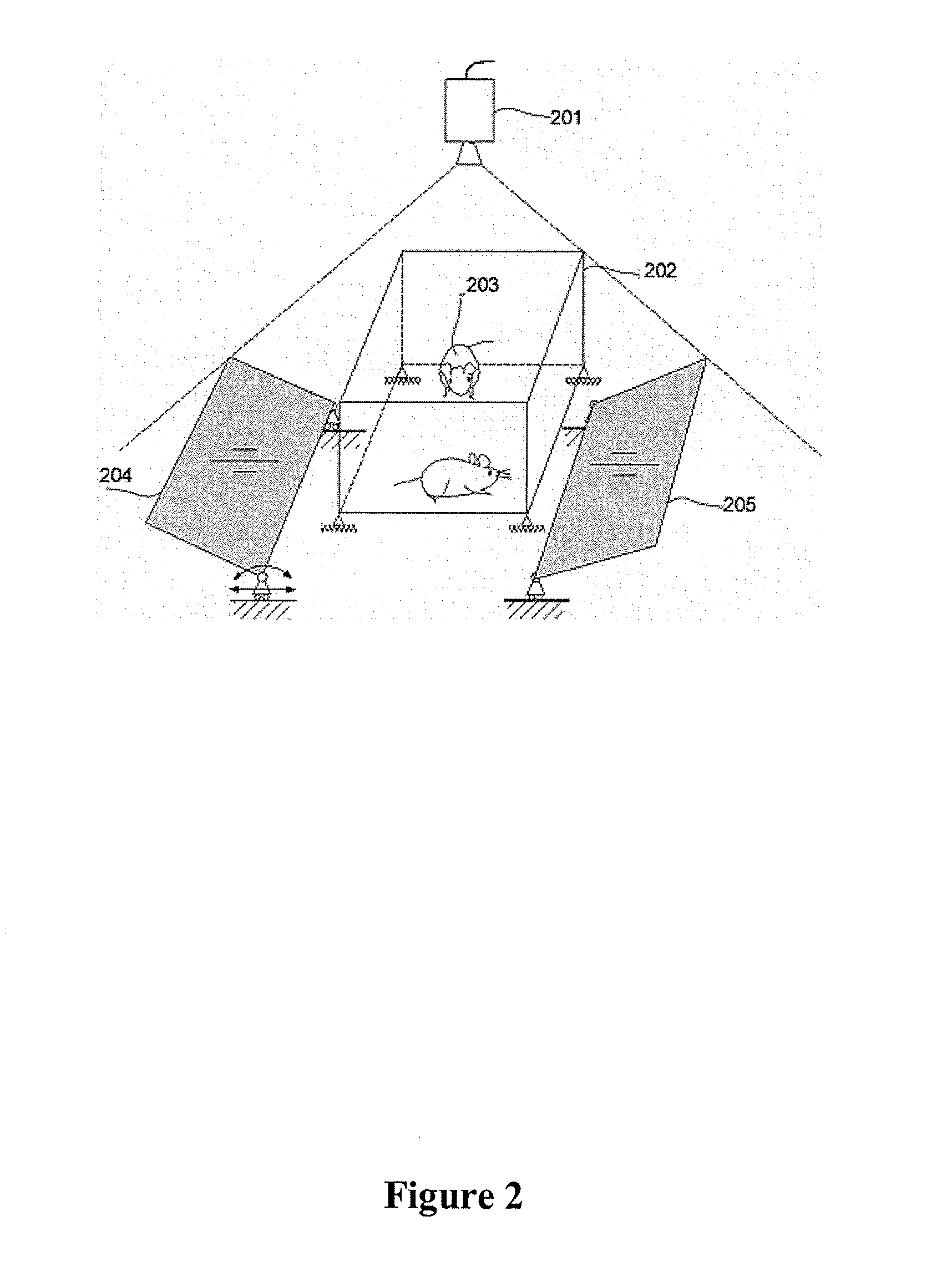

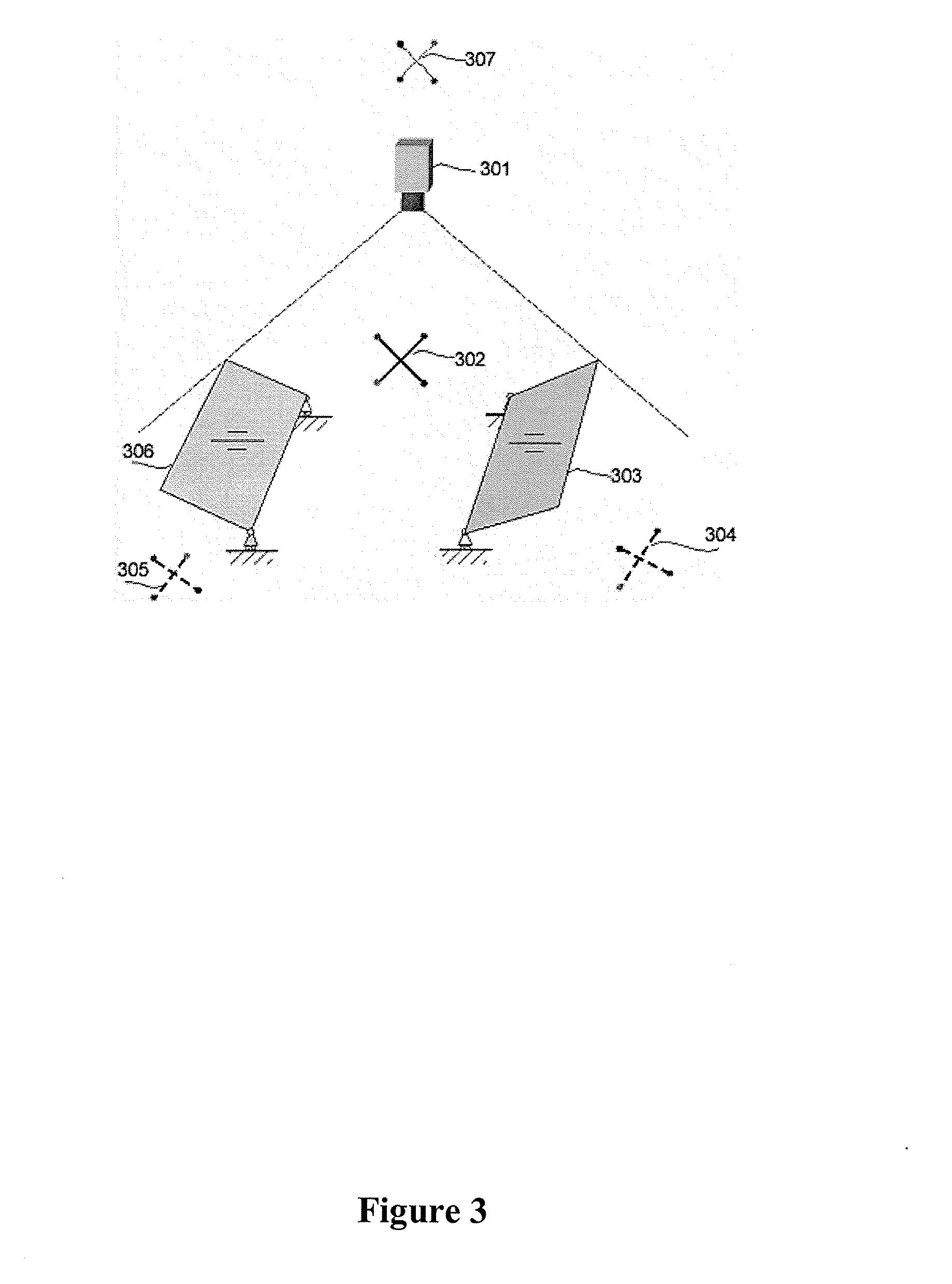

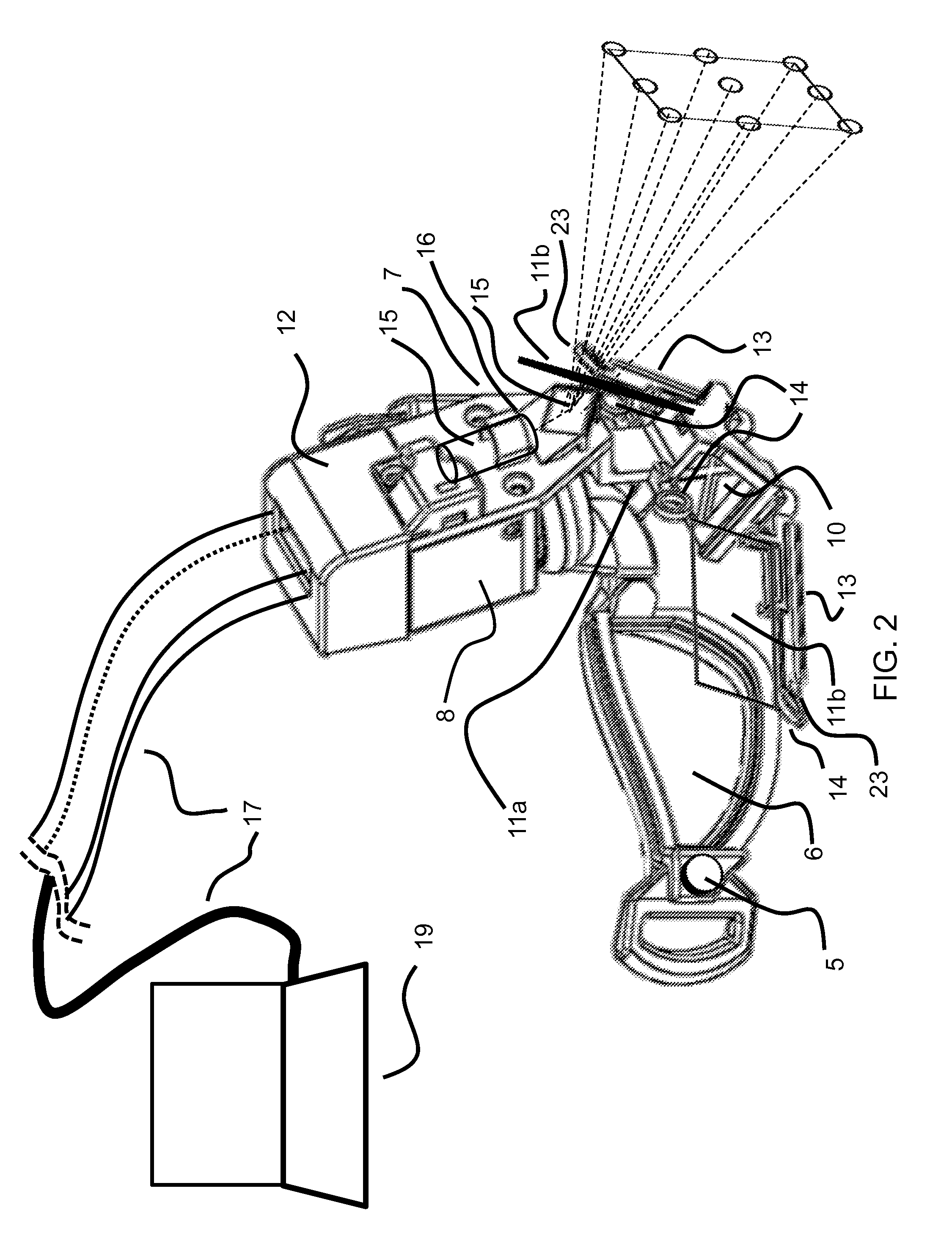

System For 3D Monitoring And Analysis Of Motion Behavior Of Targets

The present invention relates to a system for the 3-D monitoring and analysis of motion-related behavior of test subjects. The system comprises an actual camera, at least one virtual camera, a computer connected to the actual camera and the computer is preferably installed with software capable of capturing the stereo images associated with the 3-D motion-related behavior of test subjects as well as processing these acquired image frames for the 3-D motion parameters of the subjects. The system of the invention comprises hardware components as well as software components. The hardware components preferably comprise a hardware setup or configuration, a hardware-based noise elimination component, an automatic calibration device component, and a lab animal container component. The software components preferably comprise a software-based noise elimination component, a basic calibration component, an extended calibration component, a linear epipolar structure derivation component, a non-linear epipolar structure derivation component, an image segmentation component, an image correspondence detection component, a 3-D motion tracking component, a software-based target identification and tagging component, a 3-D reconstruction component, and a data post-processing component In a particularly preferred embodiment, the actual camera is a digital video camera, the virtual camera is the reflection of the actual camera in a planar reflective mirror. Therefore, the preferred system is a catadioptric stereo computer vision system.

Owner:INGENIOUS TARGETING LAB

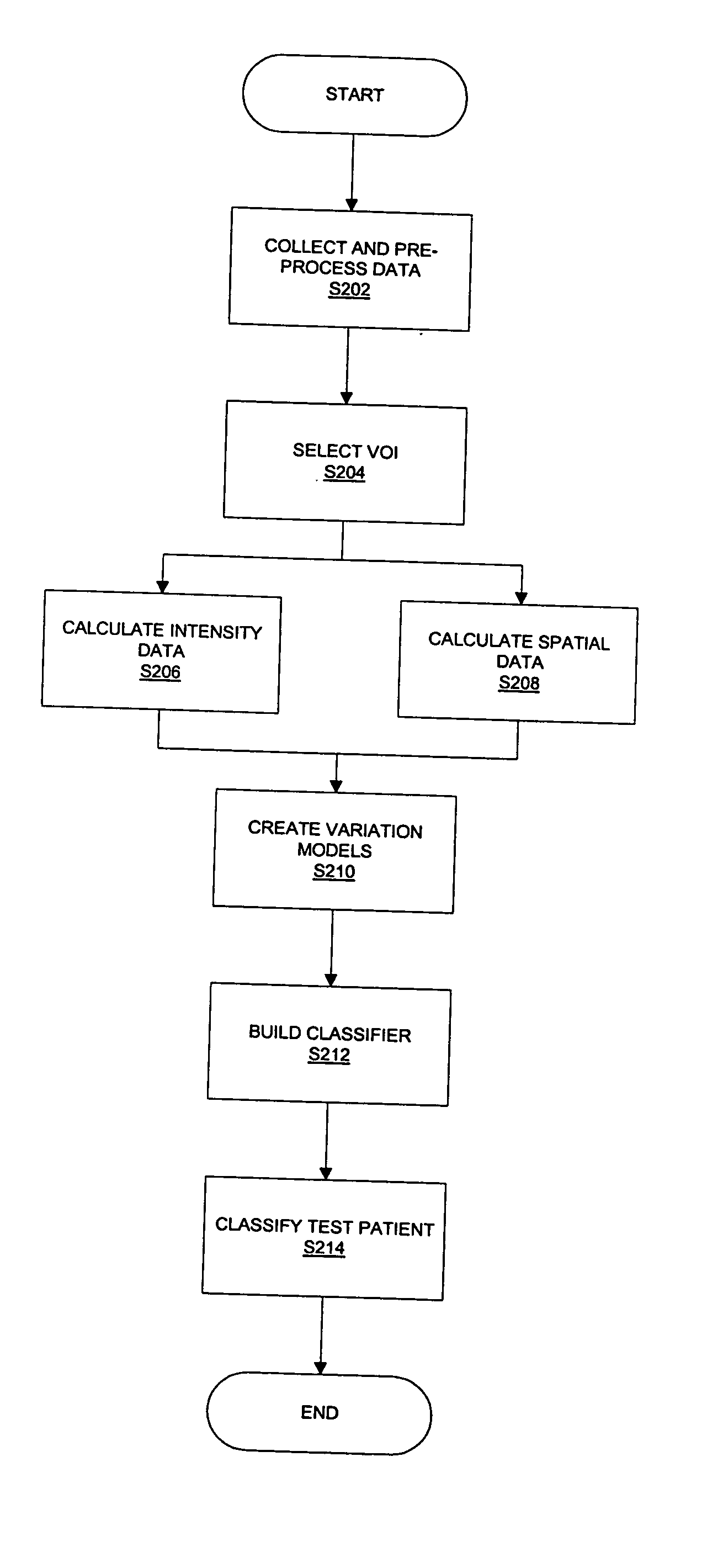

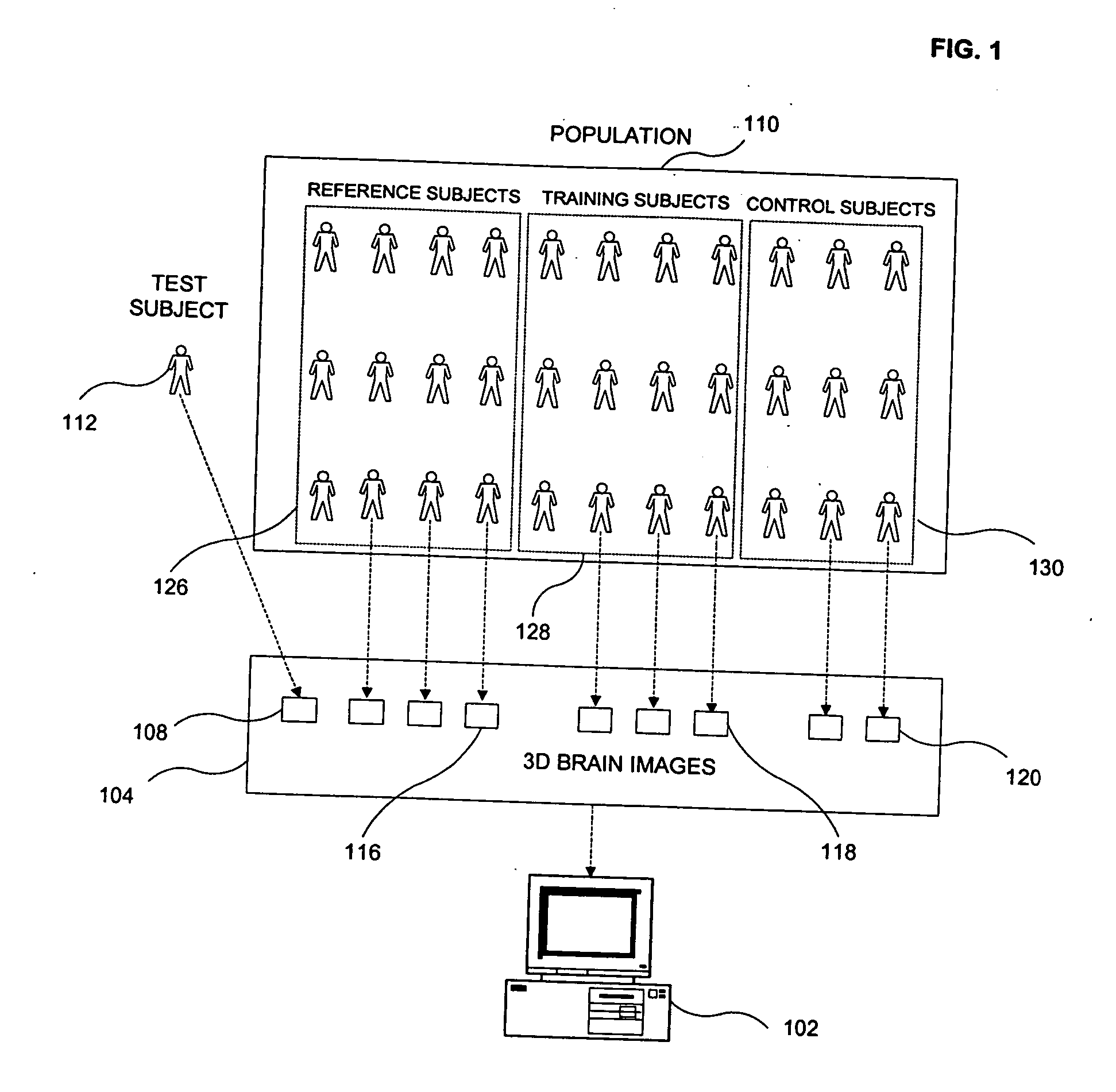

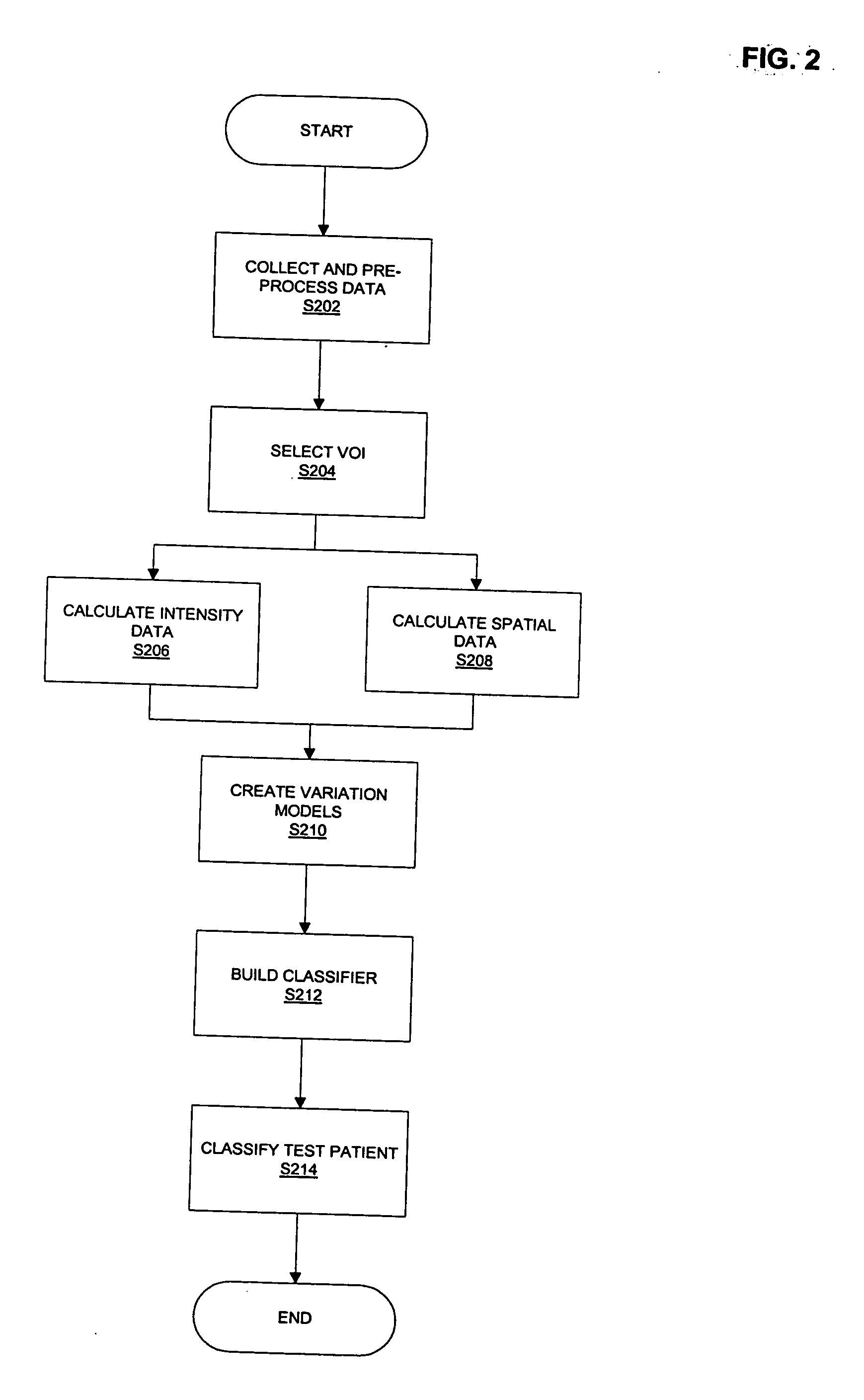

Systems and methods of classification utilizing intensity and spatial data

ActiveUS20060104494A1Effective classificationImage enhancementMedical data miningTest objectEpileptic disorder

A method of classifying a test subject comprises collecting imaging data for a plurality of training subjects, control subjects and a test subject. An intensity volume of interest (VOI) and a spatial VOI are selected from said imaging data. Training intensity data and spatial data are calculated for the intensity and spatial VOI. A statistical model can then be created based on the training intensity data and training spatial data to provide a universe of subjects. Control intensity data and spatial data are also calculated for the intensity and spatial VOI. A classifier can then be built dividing the universe into at least two regions. The test subject data can then be applied to the classifier to provide a determination of whether said test subject falls within the first region or the second region. The condition can be a neurological disease state such as temporal lobe epilepsy or Alzheimer's dementia.

Owner:MCGILL UNIV

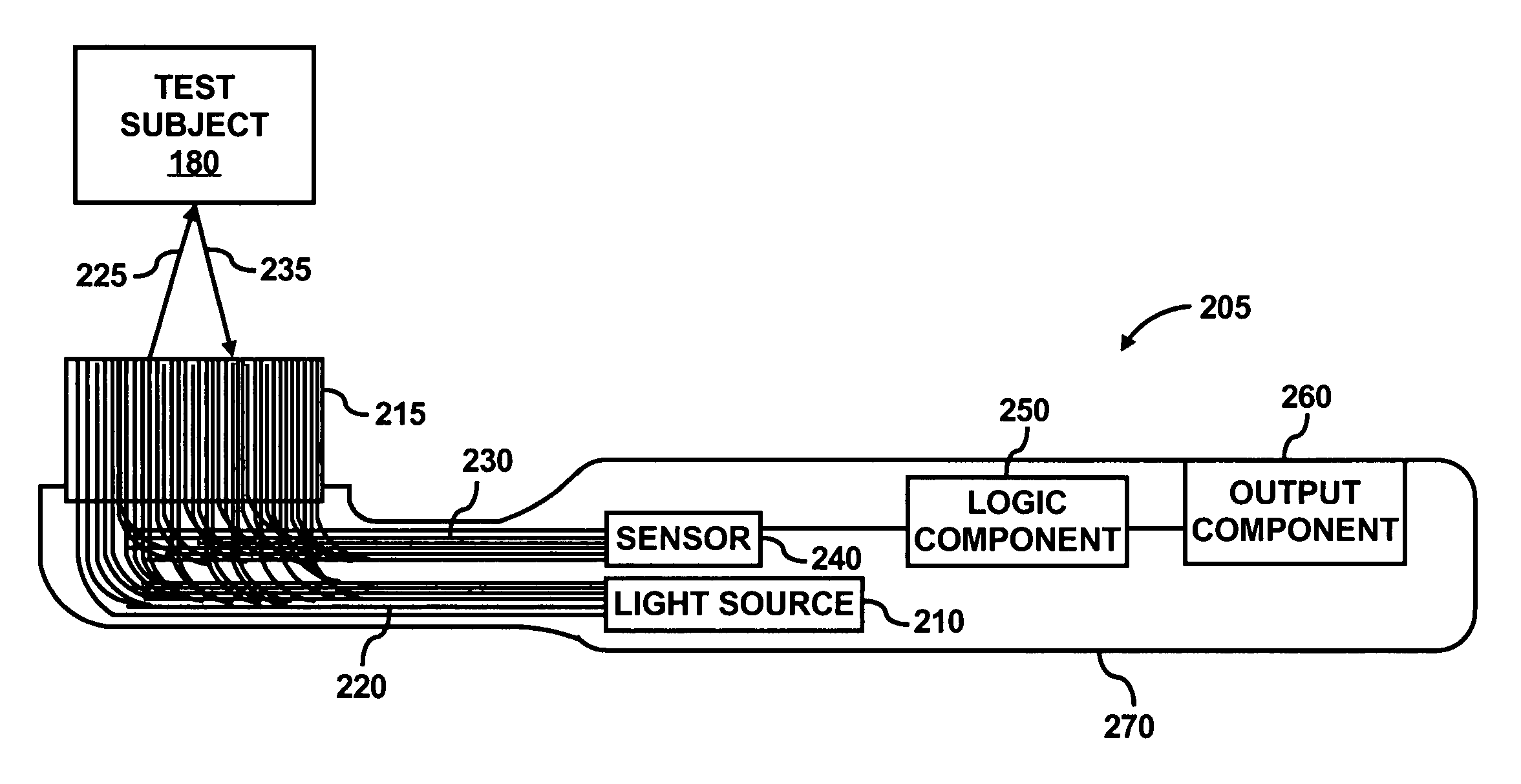

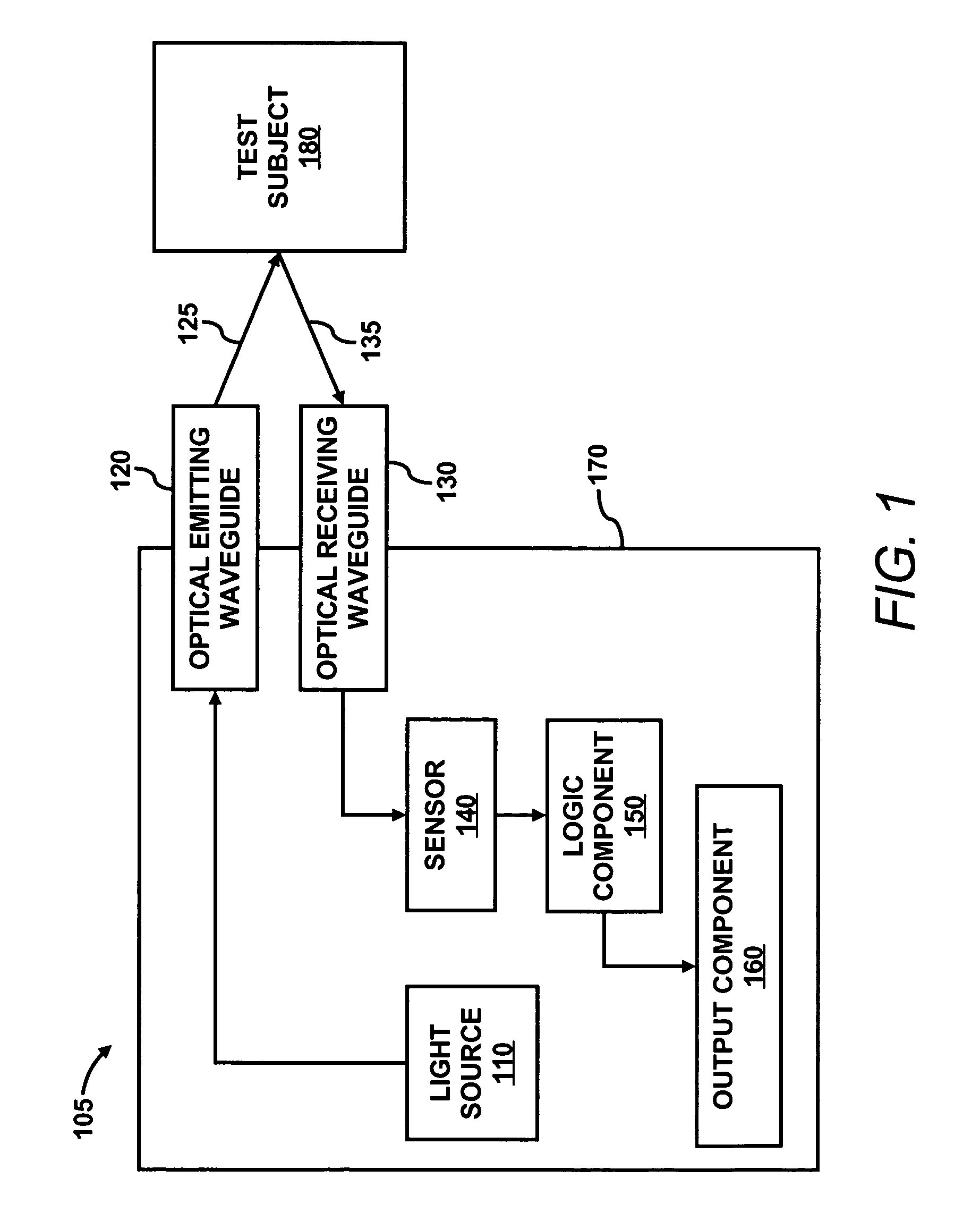

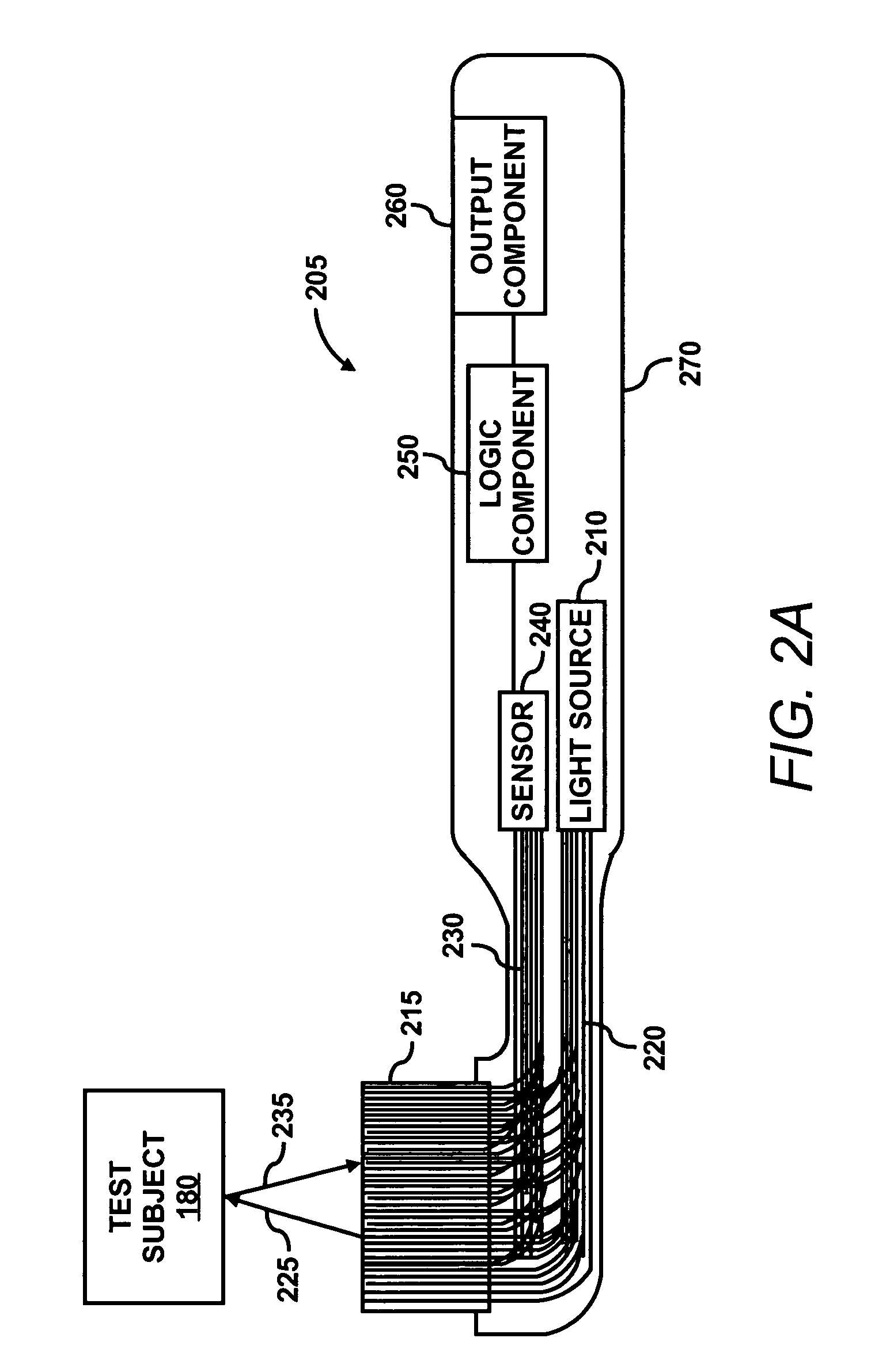

Test subject monitoring device

A device for monitoring a test subject includes a light source and at least one optical waveguide configured for at least one of directing light from the light source onto a biological substrate and receiving the light directed onto the biological substrate. The device also includes a sensor operable to detect the light received, a logic component operable to analyze the light detected by the sensor, an output component operable to convey information from the logic component to a user of the device, and a housing containing the light source, the sensor, the logic component, and the output component, where the at least one optical waveguide forms at least one bristle extending outside of the housing.

Owner:SAMSUNG ELECTRONICS CO LTD

System and method for evaluating ocular health

InactiveUS20130176534A1Quick implementationImprove accuracyRefractometersSkiascopesStimulus patternDisplay device

A method for adaptively determining a model of visual performance of a test subject comprising the step of exposing a test subject to a plurality of trials. Each trial comprises the steps of identifying the stimulus pattern to test, generating a stimulus pattern on a display, determining whether the stimulus pattern generated an OKR, updating the model to incorporate the OKR results, and determining whether the updated model is acceptable. The trials can be iteratively repeated until the model for visual performance is acceptable.

Owner:BAYLOR COLLEGE OF MEDICINE

Enzyme method for detecting lysophospholipids and phospholipids and for detecting and correlating conditions associated with altered levels of lysophospholipids

InactiveUS6248553B1Enhanced signalMicrobiological testing/measurementBiological material analysisBody fluidBiology

The present invention is an enzymatic method and diagnostic kits for detecting and quantifying the presence of one or more lysophospholids in a sample of bodily fluid taken from a test subject. The method uses enzymes in a two step assay and may be used to detect disease conditions associated with altered levels of lysophospholipids and to correlate such conditions with altered levels of lysophospholipids.

Owner:APOLLO ENDOSURGERY INC

Multiparameteric method for assessing immune system status

ActiveUS20060275752A1Risk minimizationMicrobiological testing/measurementBiological testingMedicineTest sample

The invention provides a multiparametric method of assessing the reaction of a patient's immune system to a test subject. The invention compares a patient sample reacted with a test sample and a third party sample and combines the assessments of the multiple parameters to correlate the test reaction with a clinical event.

Owner:UNIVERSITY OF PITTSBURGH

Cough/sneeze analyzer and method

ActiveUS7104962B2Improve analysis accuracyImprove accuracyAuscultation instrumentsRespiratory organ evaluationAir compressionMedicine

A cough event is differentiated from a sneeze event of a test subject enclosed within a plethysmograph test chamber by measuring air pressure changes during the event, and comparing the pressure changes against criteria indicative of a cough to determine the likelihood that the event is a cough. Air pressure changes are recorded as pressure and / or sound values. A graphical record of a waveform of changes in the air pressure during an event relative to a baseline value is recorded, and a value is calculated that is indicative of the likelihood that the event is a cough based on the sizes of areas between the waveform and baseline during the event, said areas including a first area indicative of the change in air pressure during air inspiration, a second area indicative of the change in air pressure during air compression, and a third area indicative of the change in air pressure during expiration.

Owner:DATA SCI INT

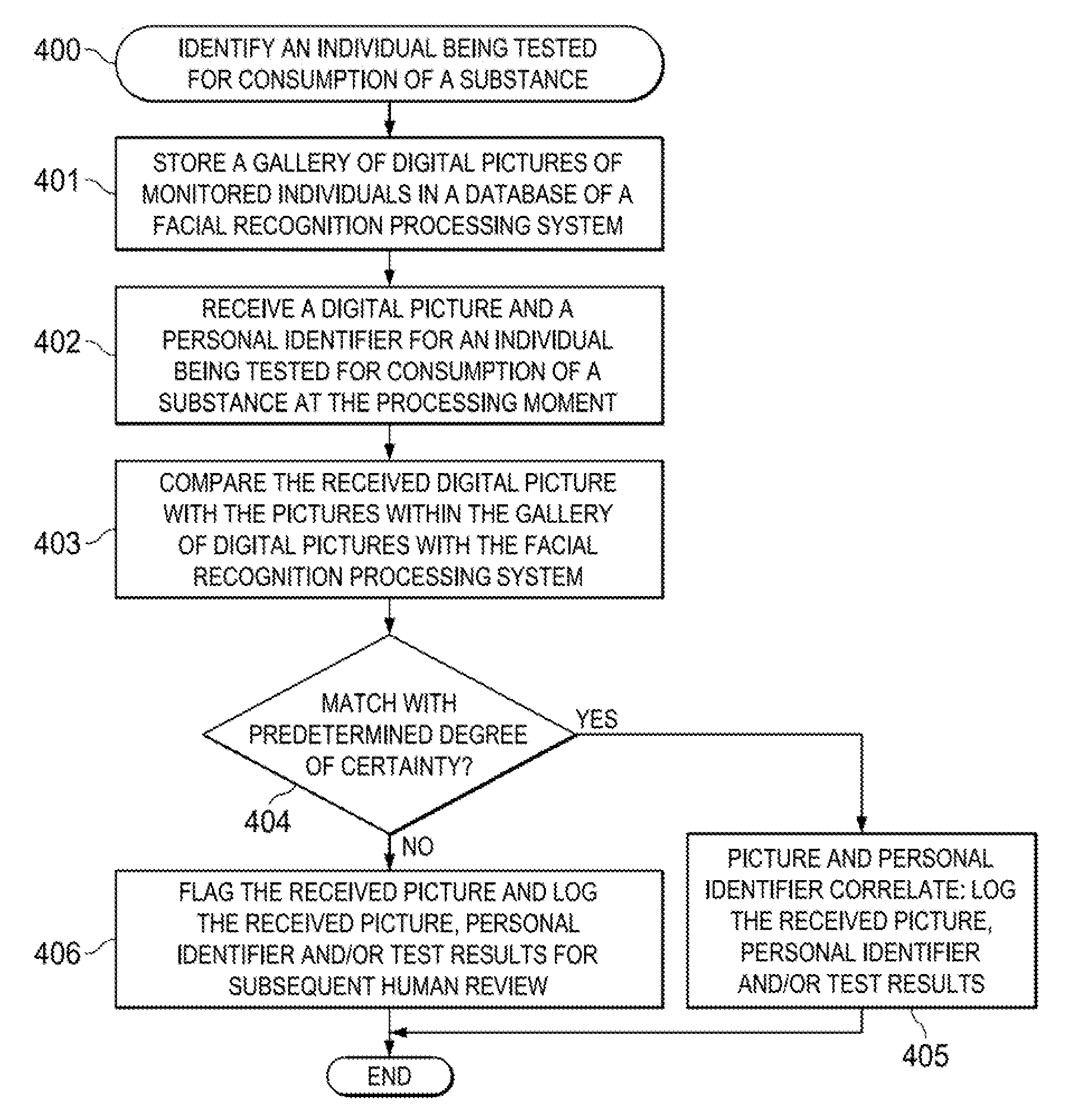

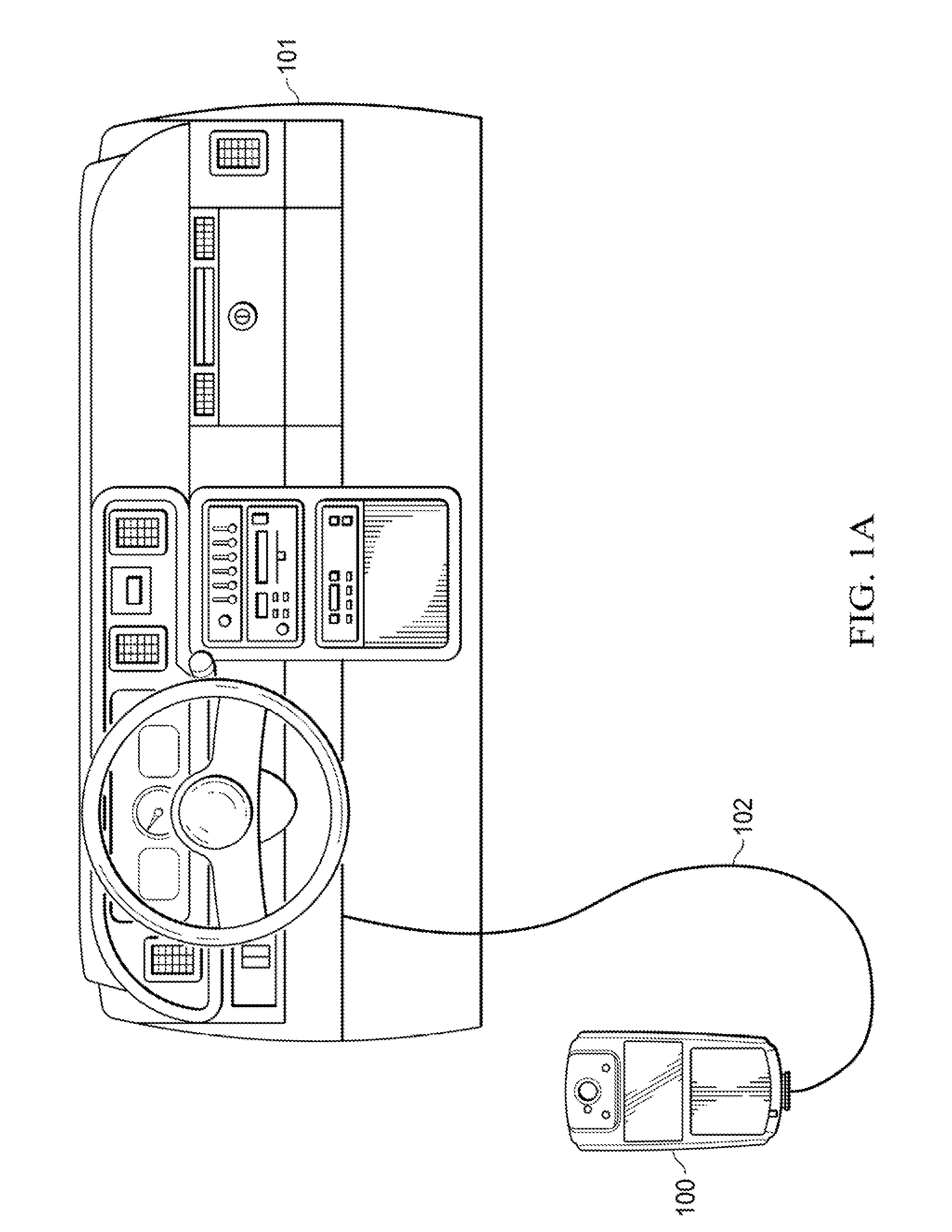

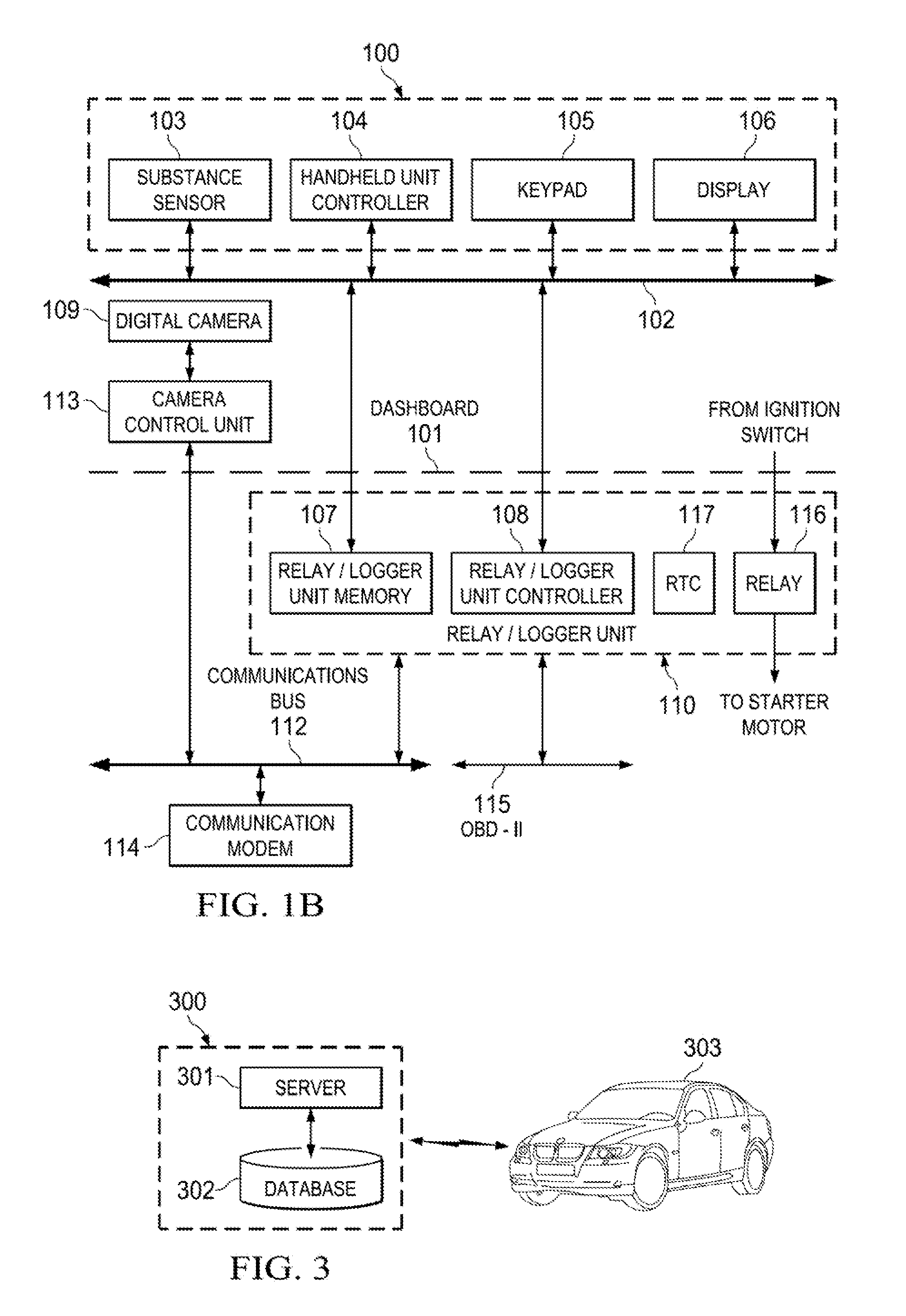

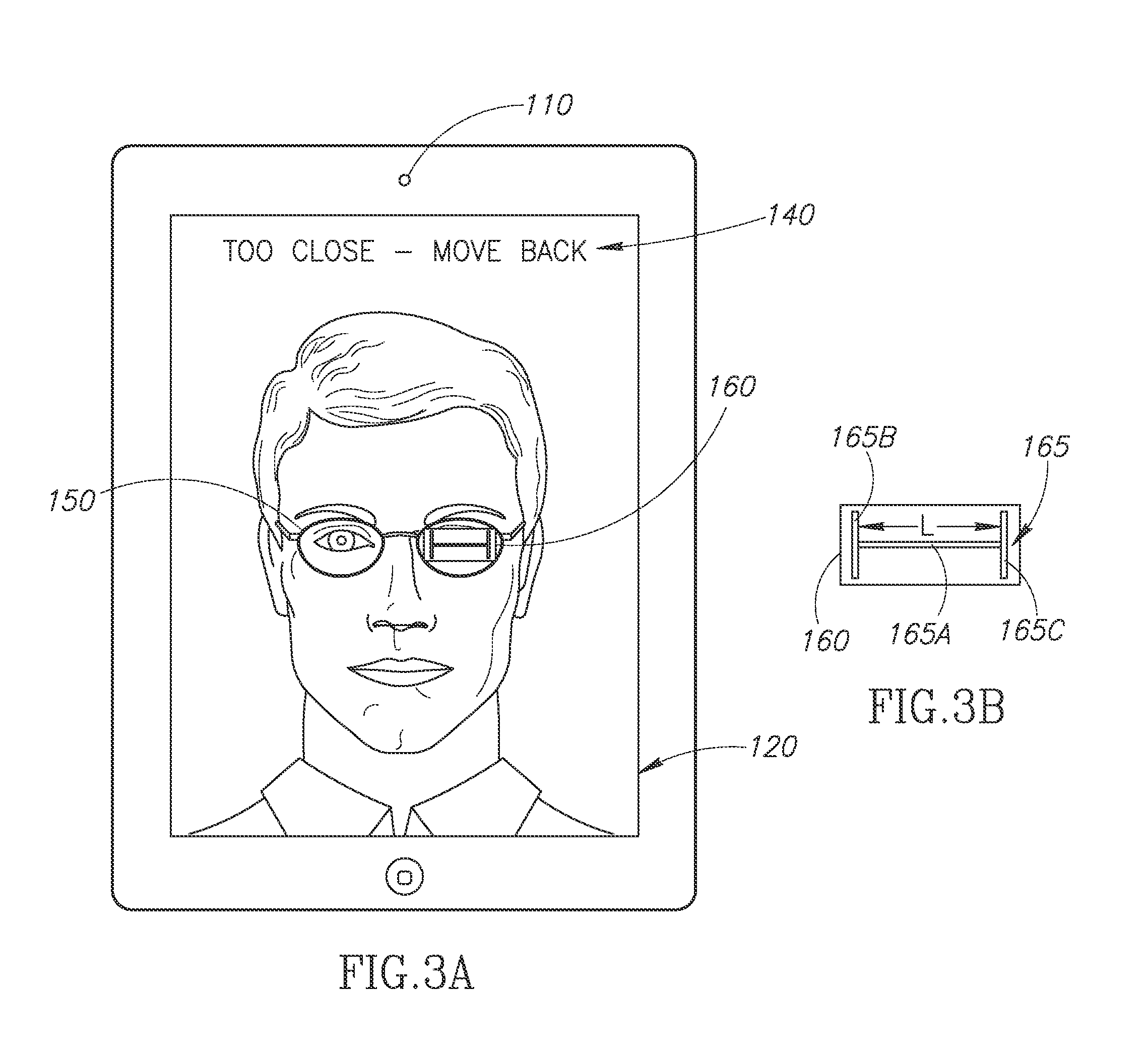

Substance Testing Systems and Methods with Test Subject Identification Using Electronic Facial Recognition Techniques

InactiveUS20160086021A1Minimize undetected misuse or circumventionStill image data retrievalDigital data processing detailsRecognition algorithmSystem identification

A method for identifying a test subject being tested for consumption of a selected substance includes storing in a database of a facial recognition processing system a gallery of facial images of a set of individuals. The facial recognition processing system receives a facial image of a test subject being tested for consumption of the selected substance and compares the received facial image with at least some of the facial images in the stored gallery by executing a facial recognition algorithm. In response to a match between a facial image in the stored gallery and the received facial image having a predetermined level of match certainty; the facial recognition processing system identifies the test subject. In response to a failure to obtain a match between a facial image in the stored gallery and the received facial image having a predetermined level of match certainty, the facial recognition processing system flags the received facial image for subsequent manual analysis.

Owner:1A SMART START LLC

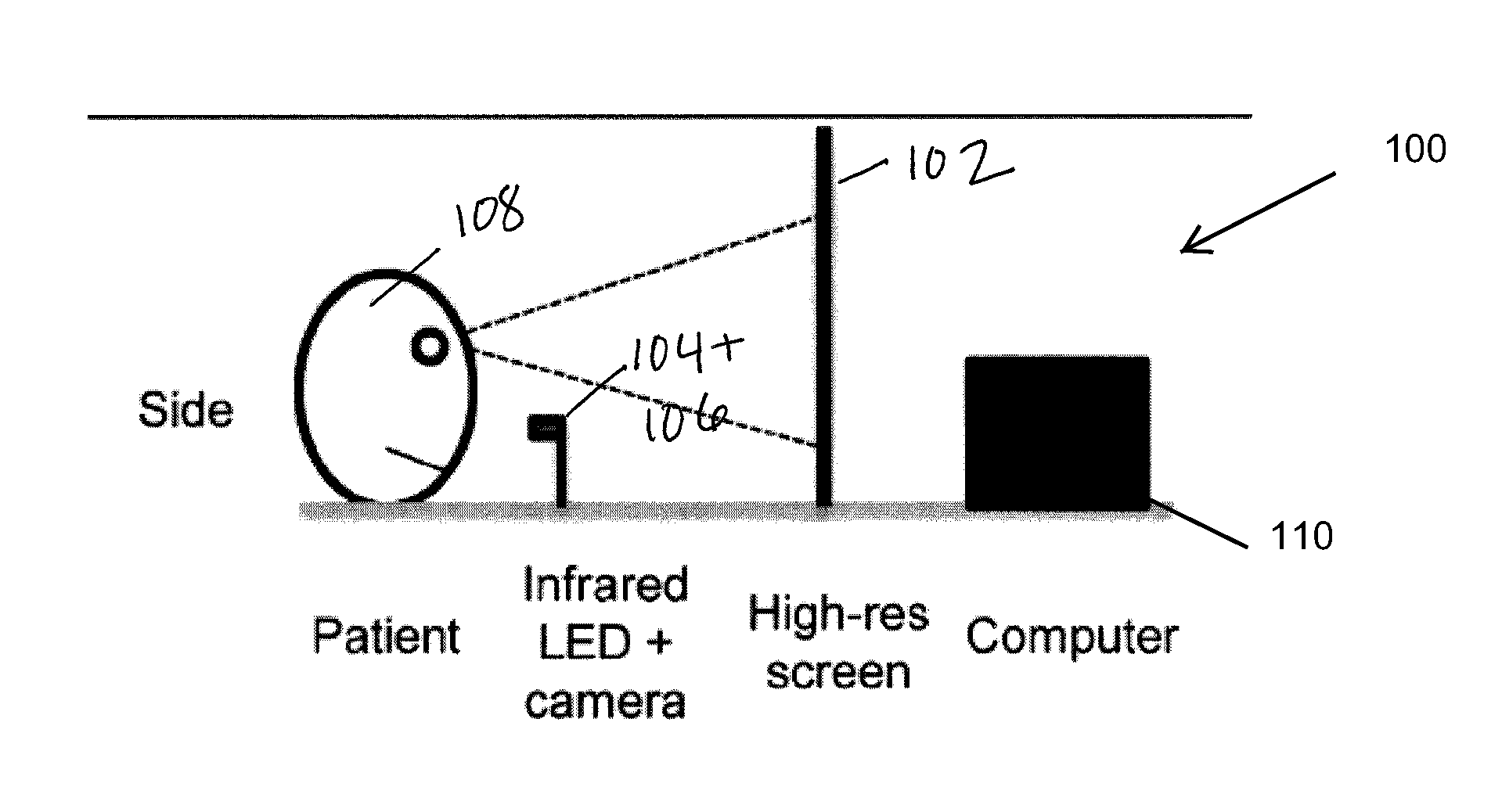

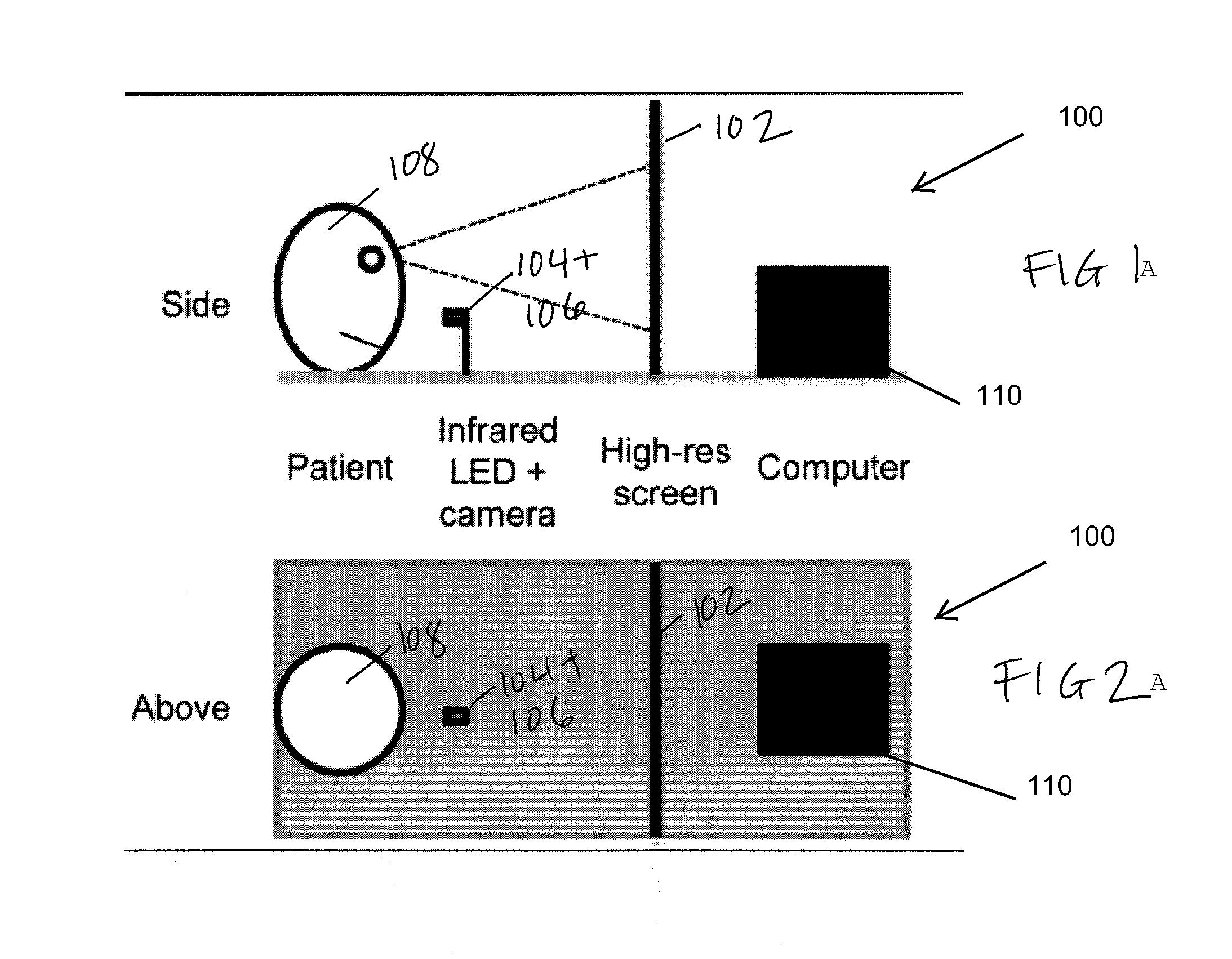

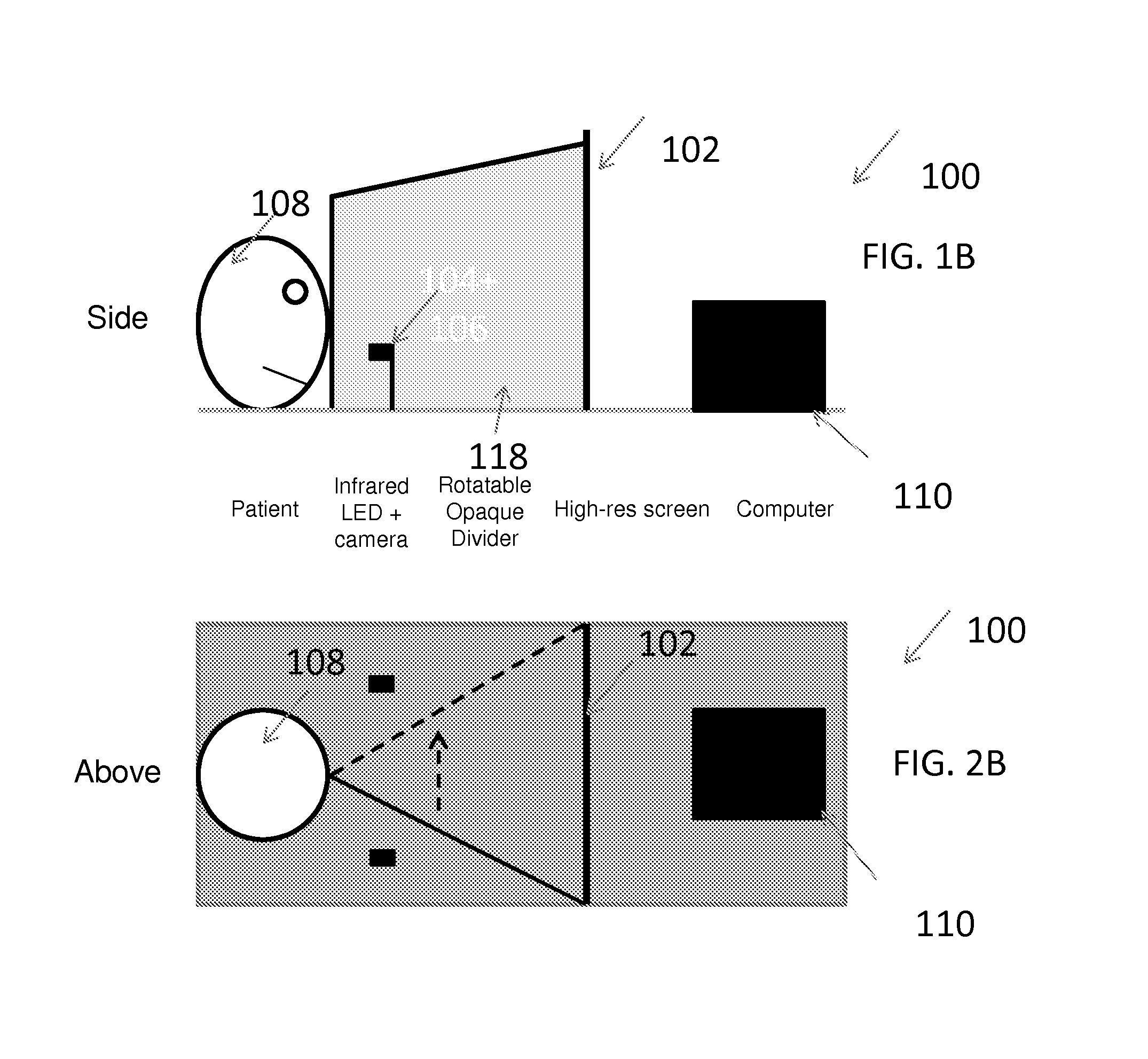

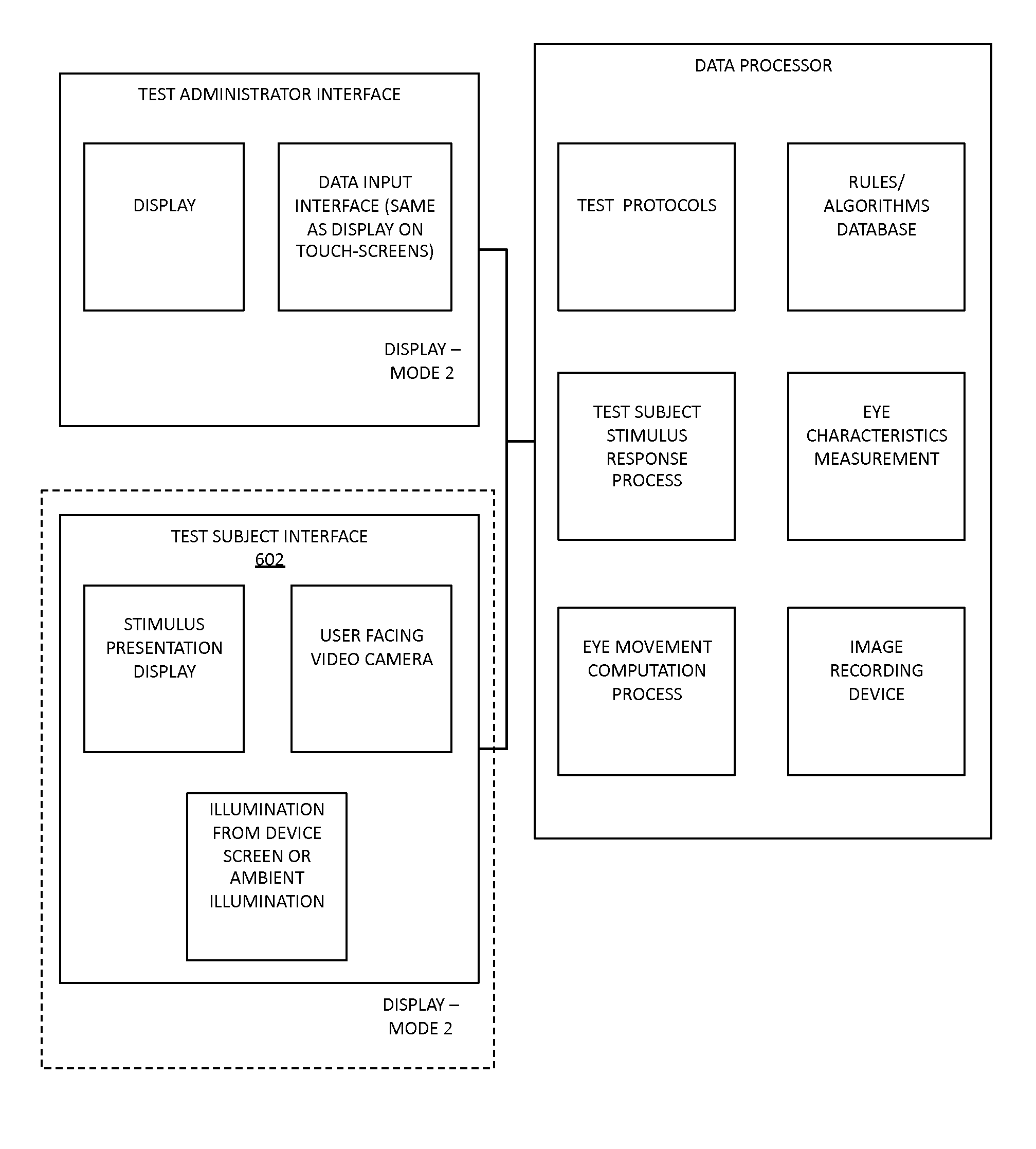

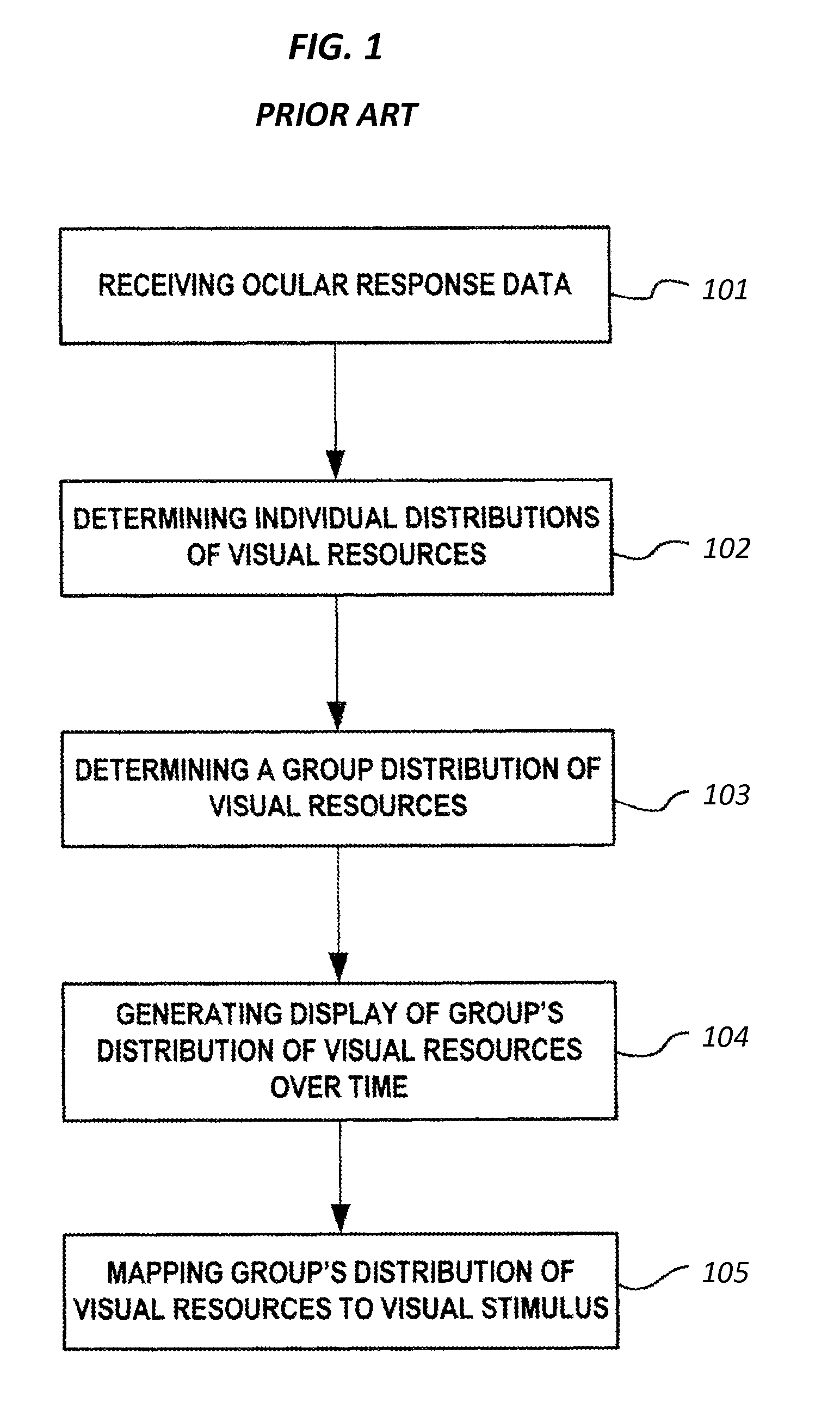

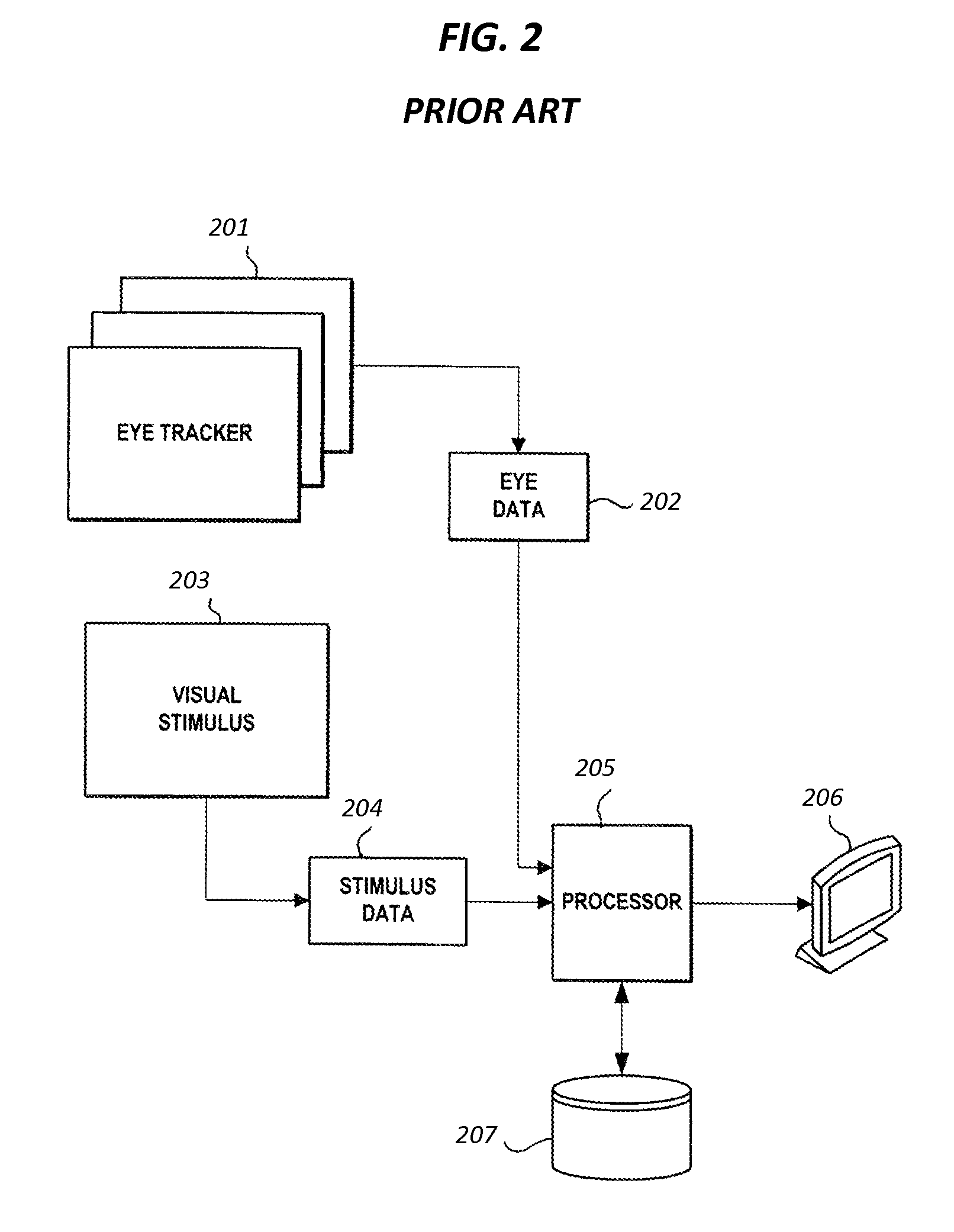

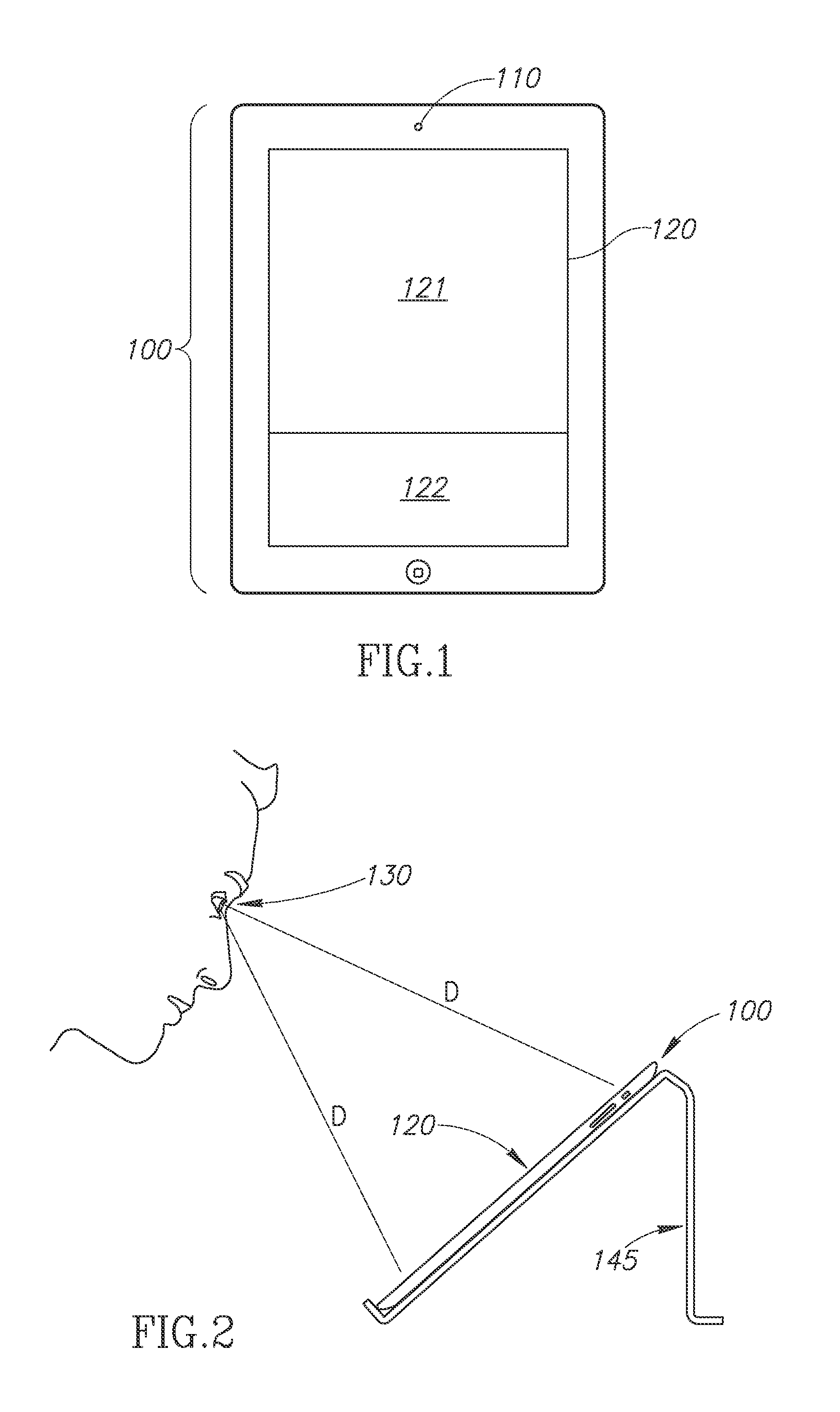

Method and System of Using Eye Tracking to Evaluate Subjects

InactiveUS20150282705A1ElectroencephalographyUltrasonic/sonic/infrasonic diagnosticsTablet computerOff the shelf

A method and system of organizing salient, aversive, and neutral stimuli in a visual display, deliberately separated by space and / or time, to better reveal attractors and aversions for a test subject observing the display, whose reactions are tracked using eye and gaze tracking, as well as other optional body parameters, all captured as data. The data is analyzed using rules and algorithms to characterize or diagnose the subject based on single test results, or comparison to prior test results, and comparisons to norms. The method and system may be employed on stand-alone, off-the-shelf electronic devices, including smartphones, tablets, laptops, and desktops, as well as on higher-end computers systems, specialized equipment, and cloud-based set-ups, allowing mobile or setting-based usage. Optional sensor inputs may be utilized for the optional inputs described above.

Owner:AVITAL OFER

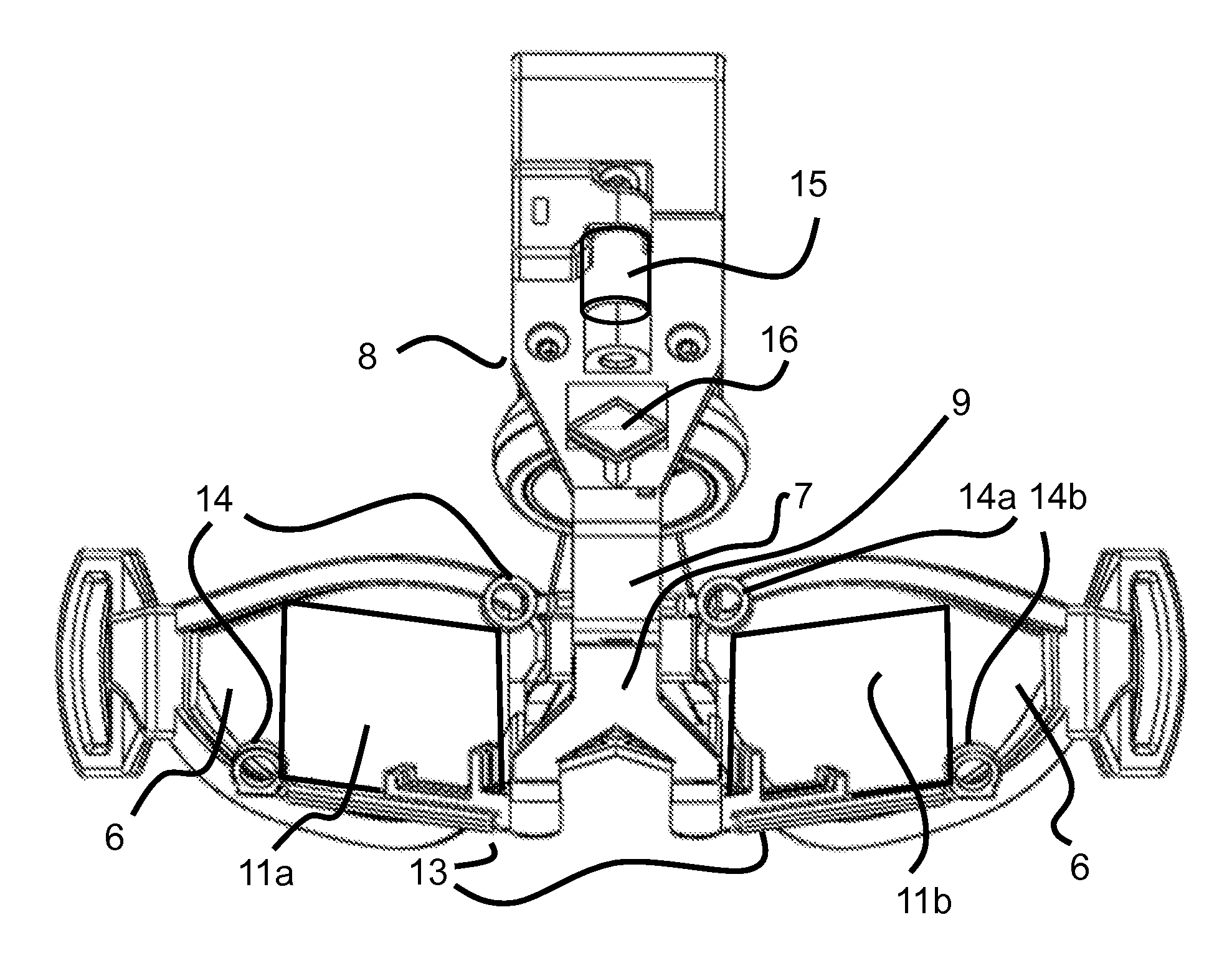

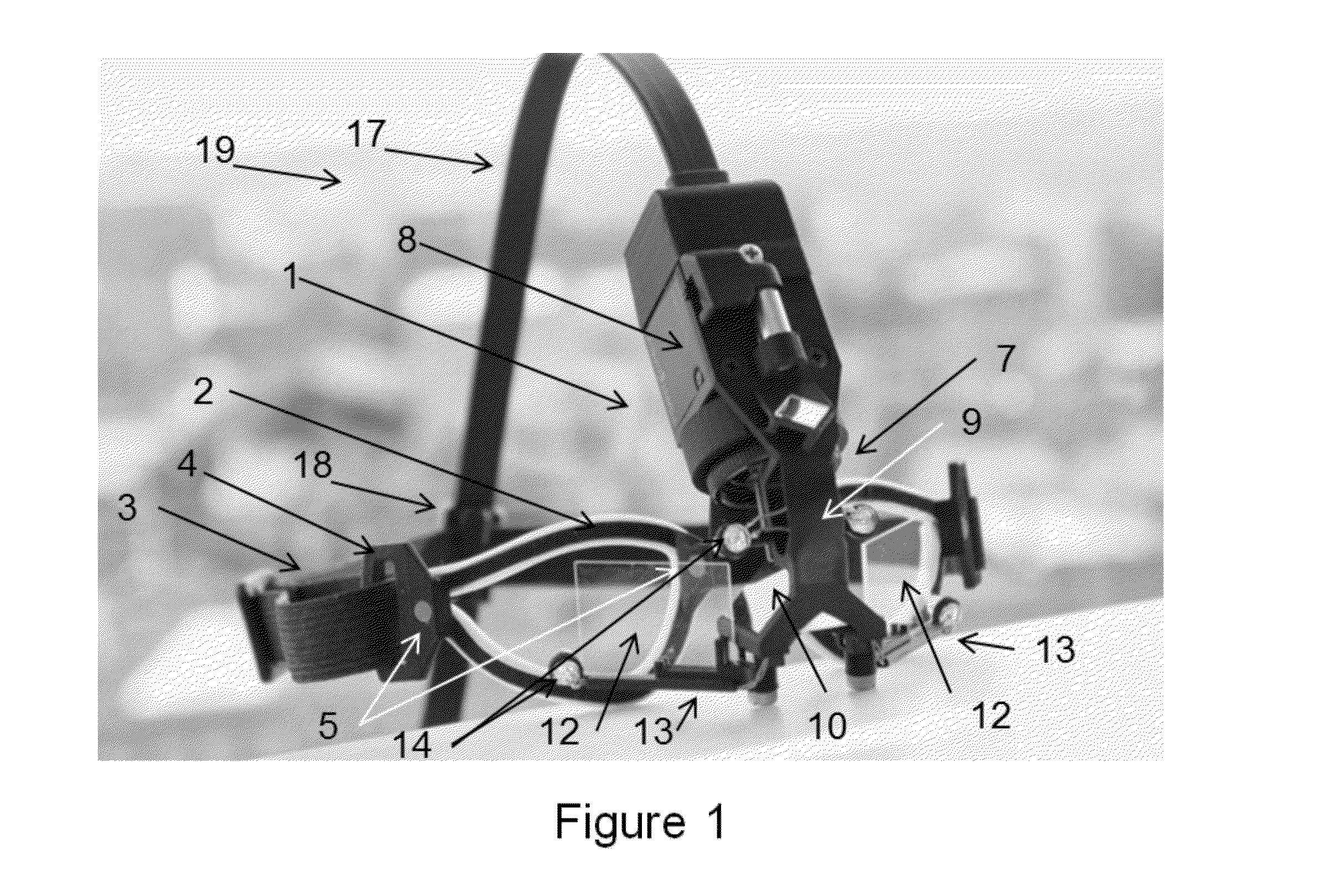

System For Synchronously Sampled Binocular Video-Oculography Using A Single Head-Mounted Camera

A one-camera, binocular, video-oculography (1CBVOG) system for measuring the movement of both of the eyes of a test subject, while the head of the test subject is undergoing a period of vestibular or oculomotor stimulation, includes: (a) a base frame, (b) a binocular imaging component, including a video camera adapted to capture a sequence of images containing both of the eyes of the test subject, (c) an optical component, (d) an illumination source, (e) a sensor module that senses translational and rotational motion of the head along and about three, mutually orthogonal axes that approximately align with the axes of the inner ears' semicircular canals, and (f) a computing device configured to quantify and measure the movement of the test subject's eyes from the sequence of captured images.

Owner:LABYRINTH DEVICES

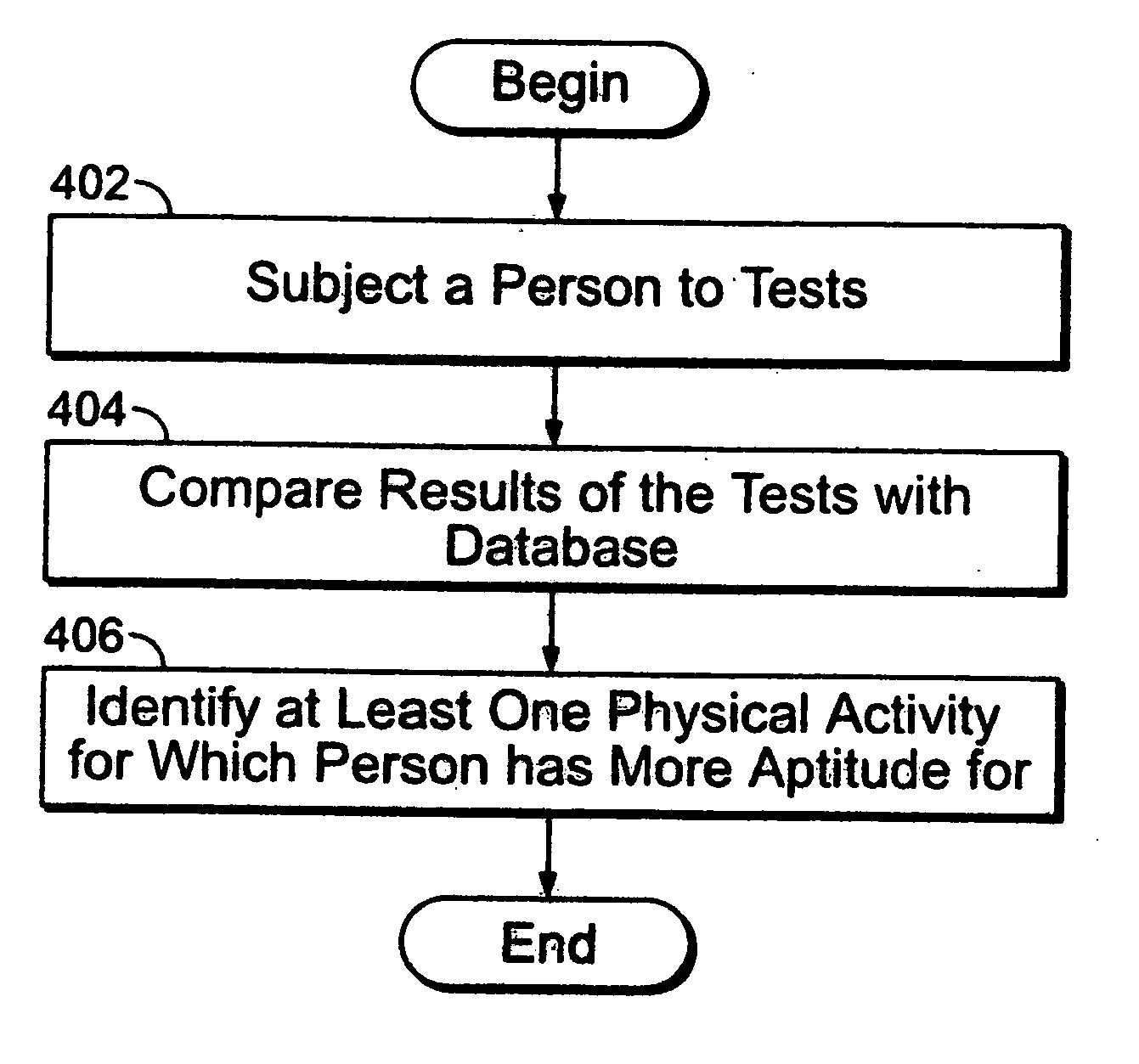

System, method and apparatus for evaluating military personnel

InactiveUS20060084850A1Cosmonautic condition simulationsHealth-index calculationMental testingComputer compatibility

A participant is evaluated to determine compatibility among different military disciplines. The participant is first subjected to physical, physiological, and psychological tests. The results of tests are compared with a database that contains the results of the same tests subjected to a set of elite military members from different military disciplines. At least one specific military discipline compatible with the participant based on the comparison is identified. A list of identified specific disciplines from most compatible to least compatible associated with a corresponding match score is then generated.

Owner:SPORTS POTENTIAL

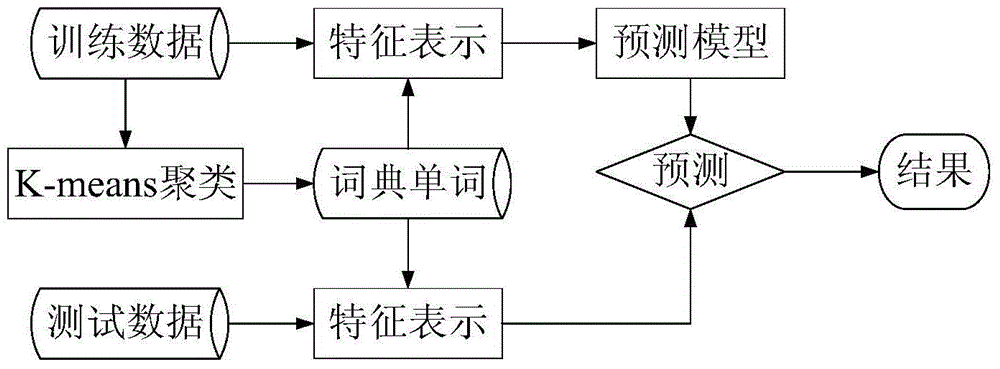

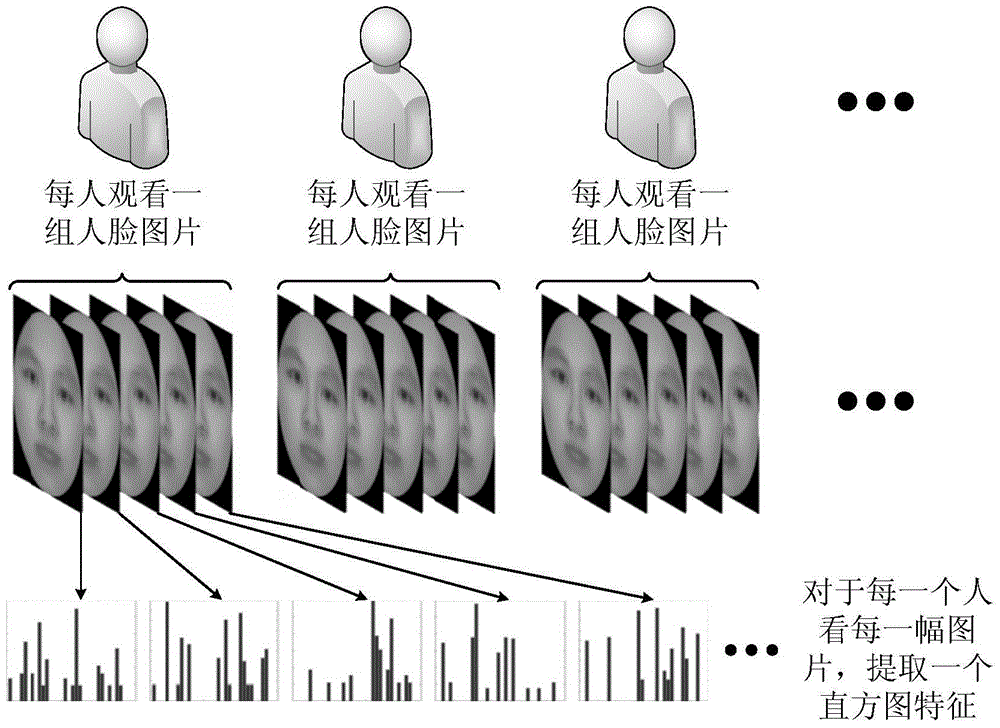

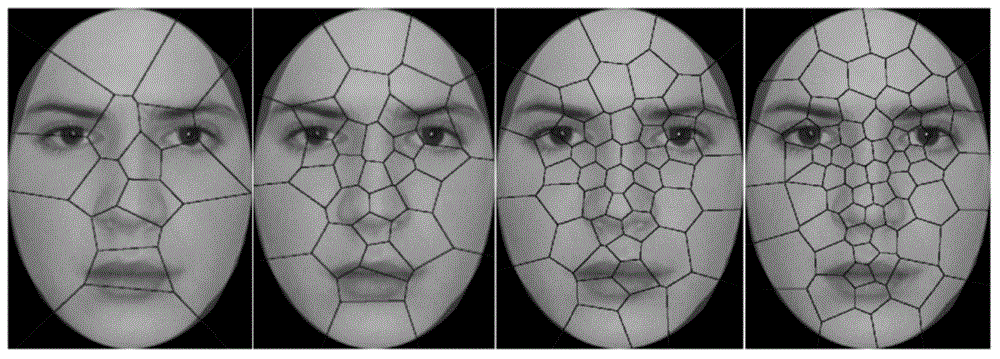

Machine learning-based method for evaluating and predicting ASD

ActiveCN105069304AAccurate and convenient assessmentImportantCharacter and pattern recognitionSpecial data processing applicationsLearning basedFeature extraction

The present invention discloses a machine learning-based method for evaluating and predicting ASD, comprising the following steps: S1. data collection: using an eye tracker to separately collect eye movement data that an eye ball scans a human face when persons participating in a test watch a human face image, wherein the persons participating in the test comprise individuals who have ASD and normal individuals; S2. feature extraction: dividing the human face image into different areas according to collected eye movement coordinate data, extracting a feature from the original data collected by the eye tracker, and making a mark; S3. classifier training: training a classifier by using a marked feature, to obtain a classifier model for predicting ASD; and S4. prediction: testing on a test subject by using the classifier model for predicting ASD acquired in step S3, to evaluate and predict severity of autism of the test subject. The present invention may be considered as a supplementary method of ASD evaluation, so that ASD evaluation and prediction in an early stage is more accurate and convenient.

Owner:SYSU CMU SHUNDE INT JOINT RES INST

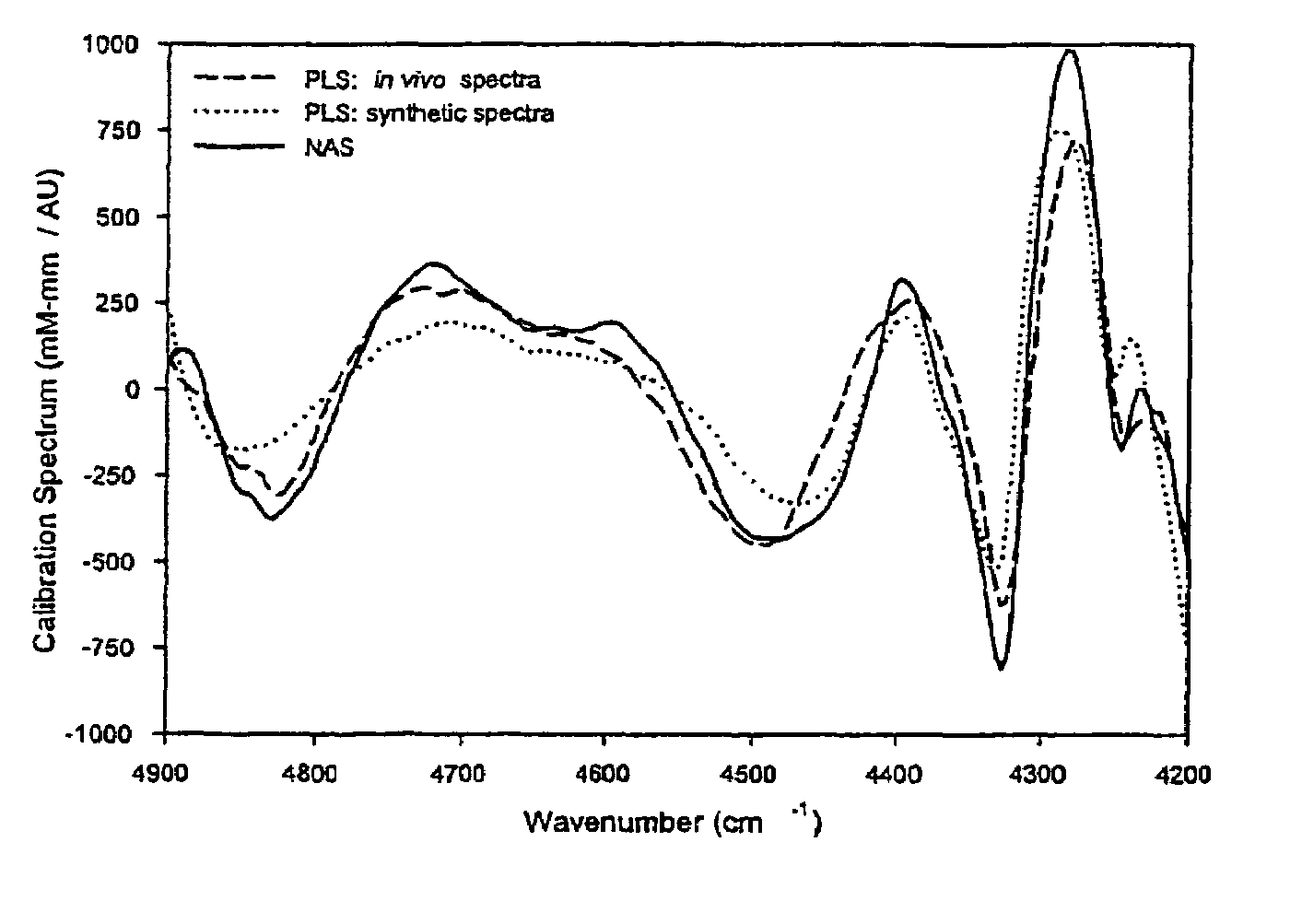

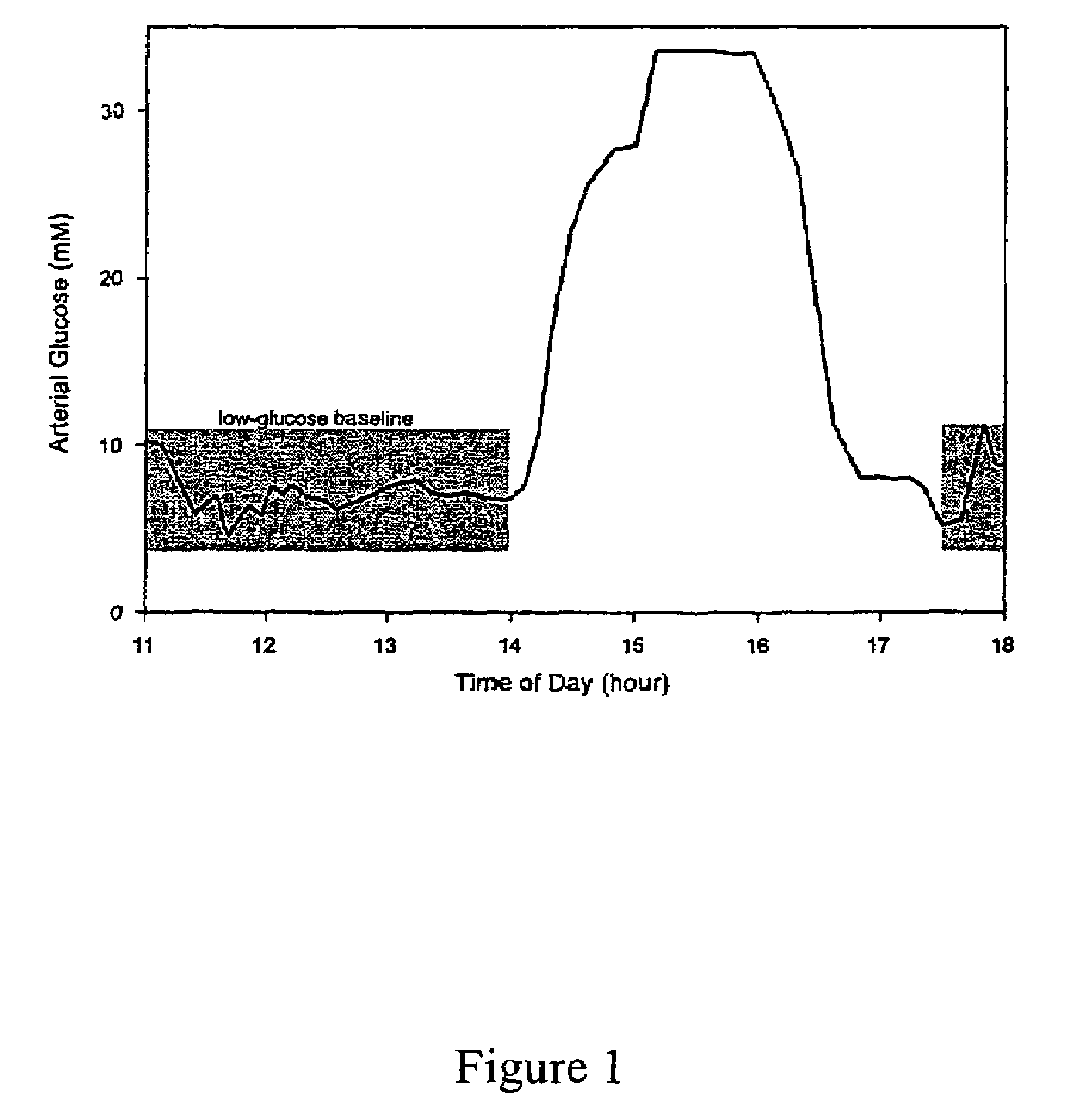

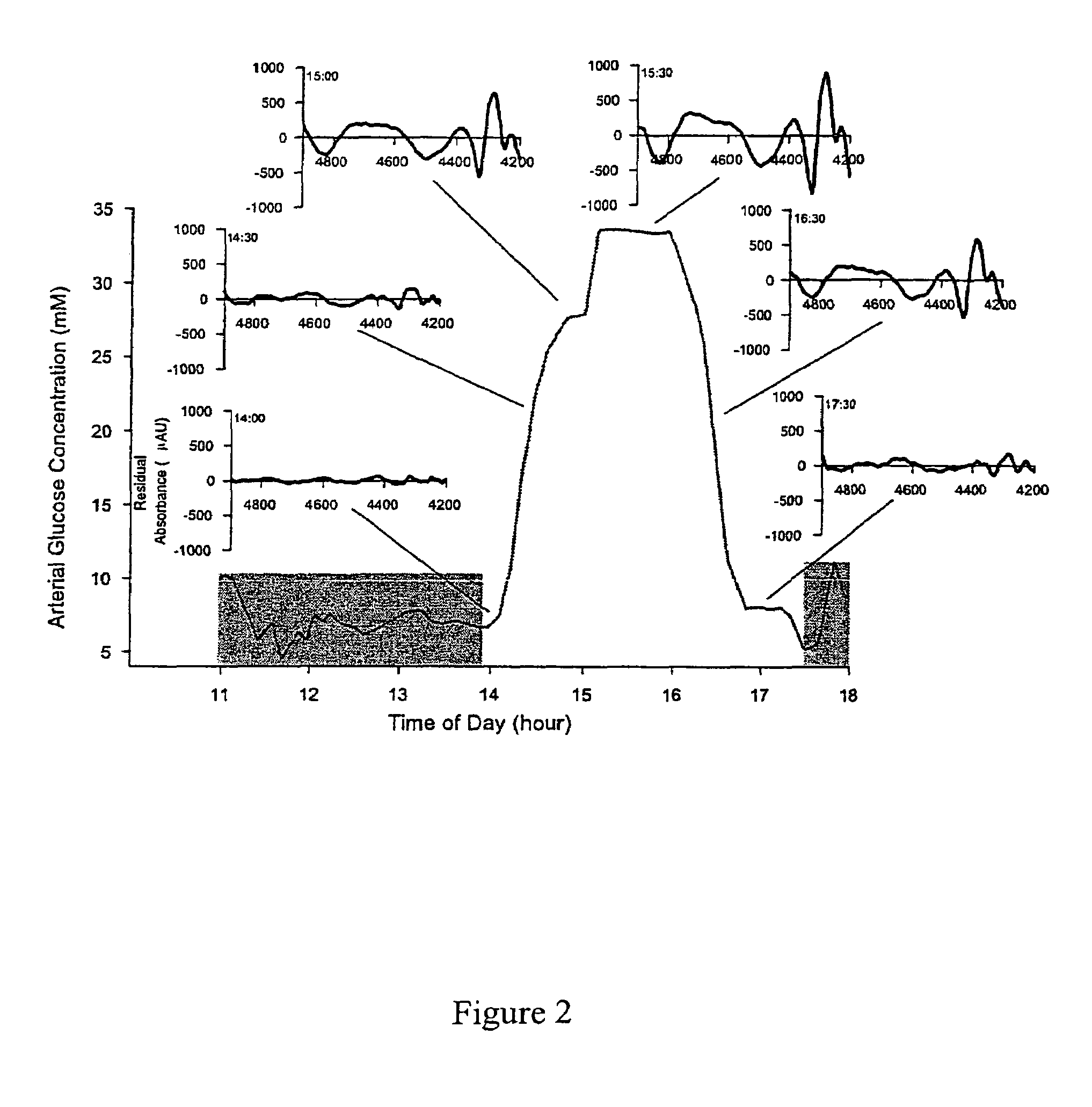

Method for generating a net analyte signal calibration model and uses thereof

Owner:IOWA RES FOUND UNIV OF

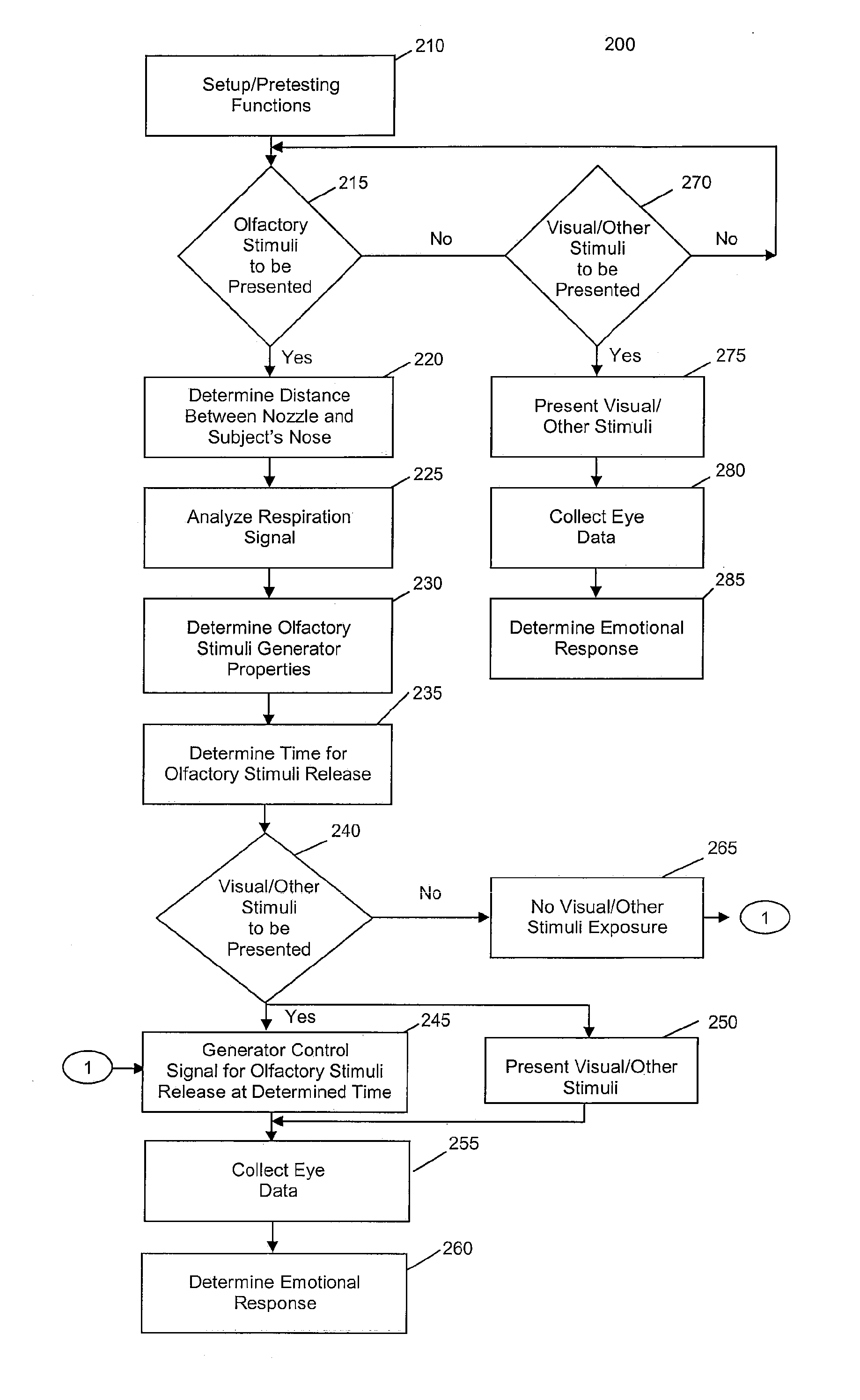

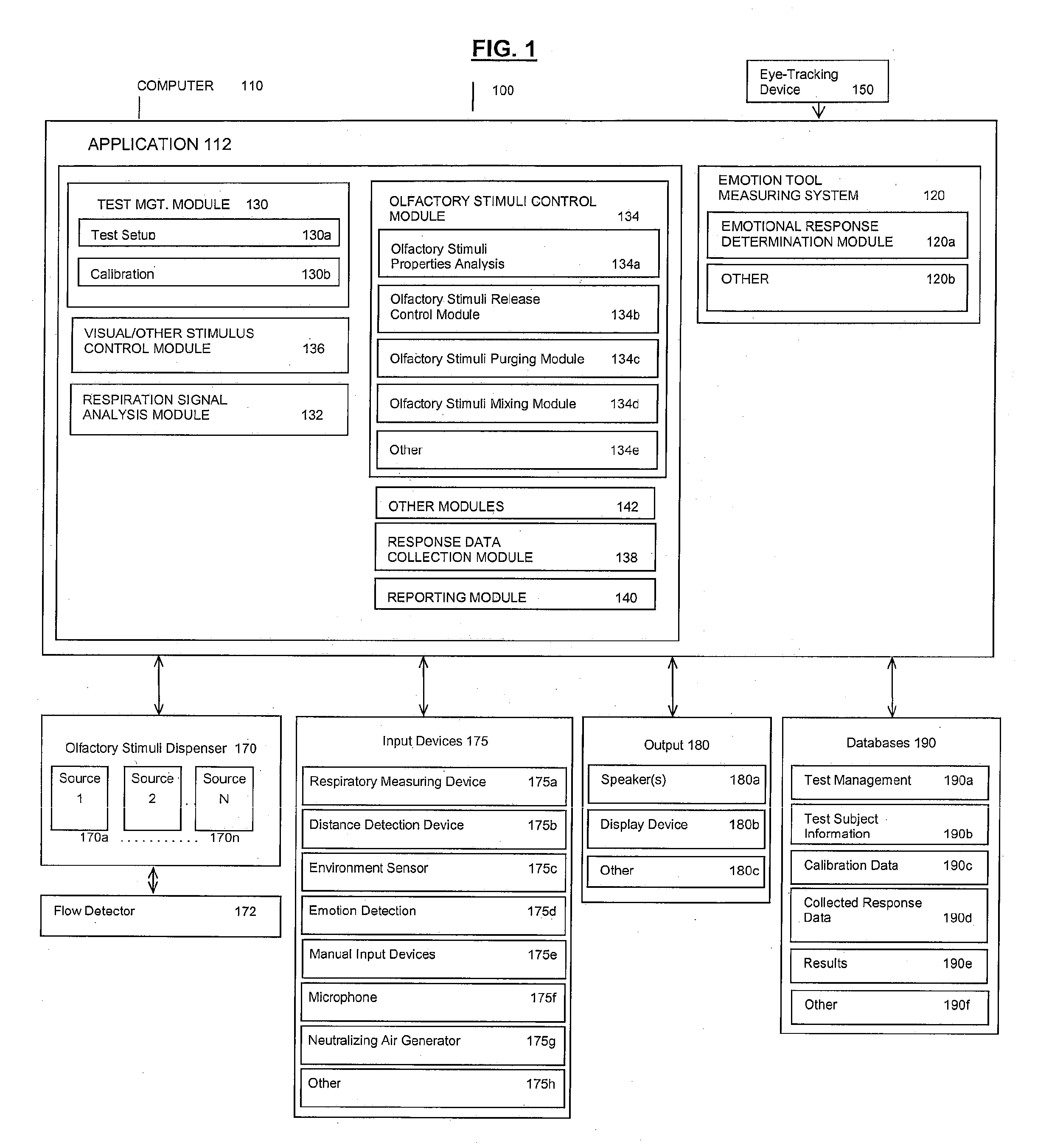

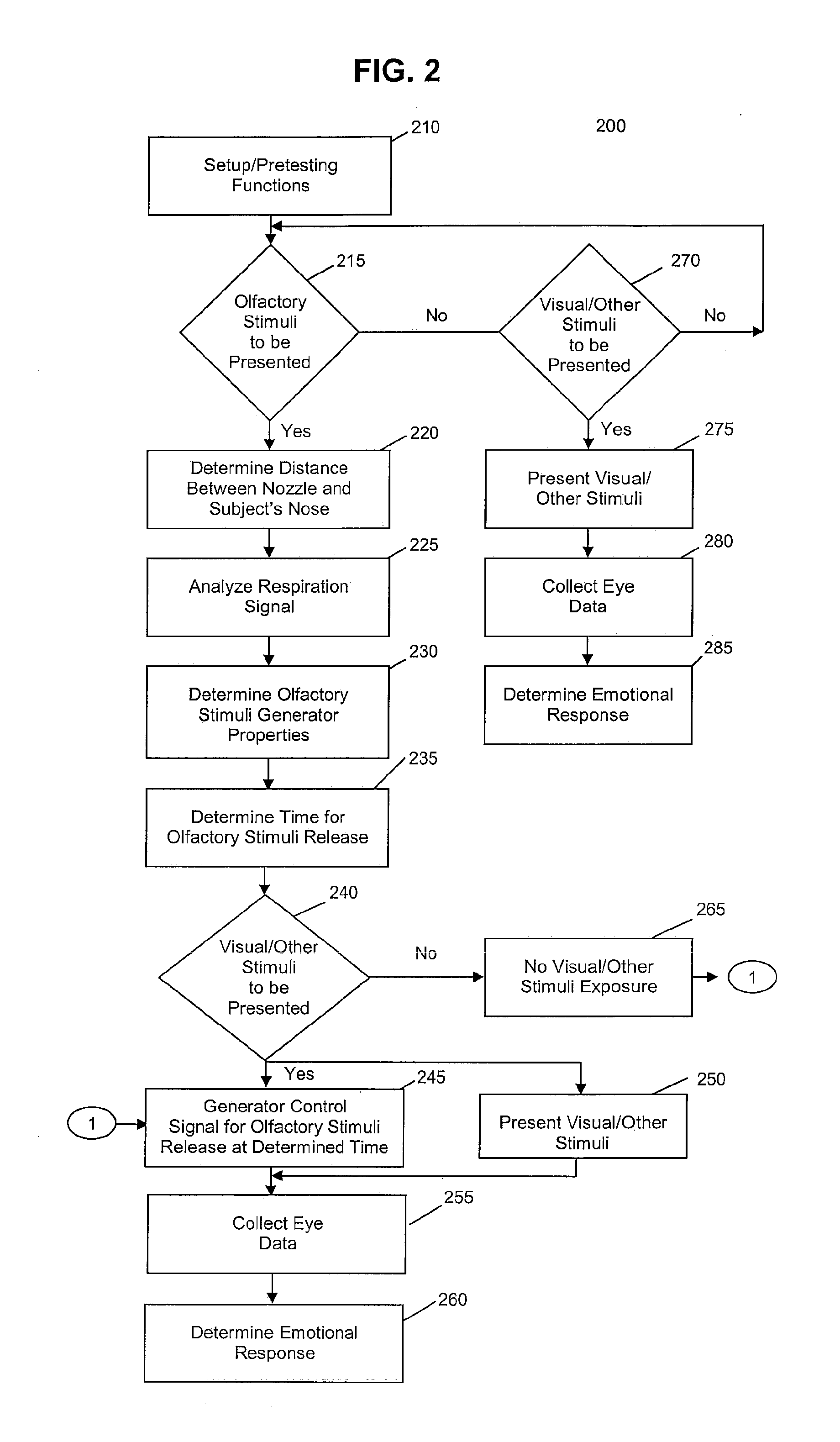

System and method for determining emotional response to olfactory stimuli

ActiveUS20120078065A1Reduce the impactReduce impactRespiratorsMedical devicesMeasurement testingNose

Systems and methods are provided for determining pre-cognitive and / or cognitive emotional response to predetermined olfactory stimuli. Among other things, the invention may include exposing a test subject to a controlled flow of a predetermined olfactory stimulus, measuring eye data (e.g., using an eye tracking device) corresponding to when the olfactory stimulus reached the subject's nose, and analyzing and processing the eye data for determining the subject's emotional response to the olfactory stimulus. In some implementations, the invention may include measuring the test subject's respiratory parameters so as to deliver the predetermined olfactory stimulus at a certain point in the test subjects respiratory cycle.

Owner:IMOTIONS

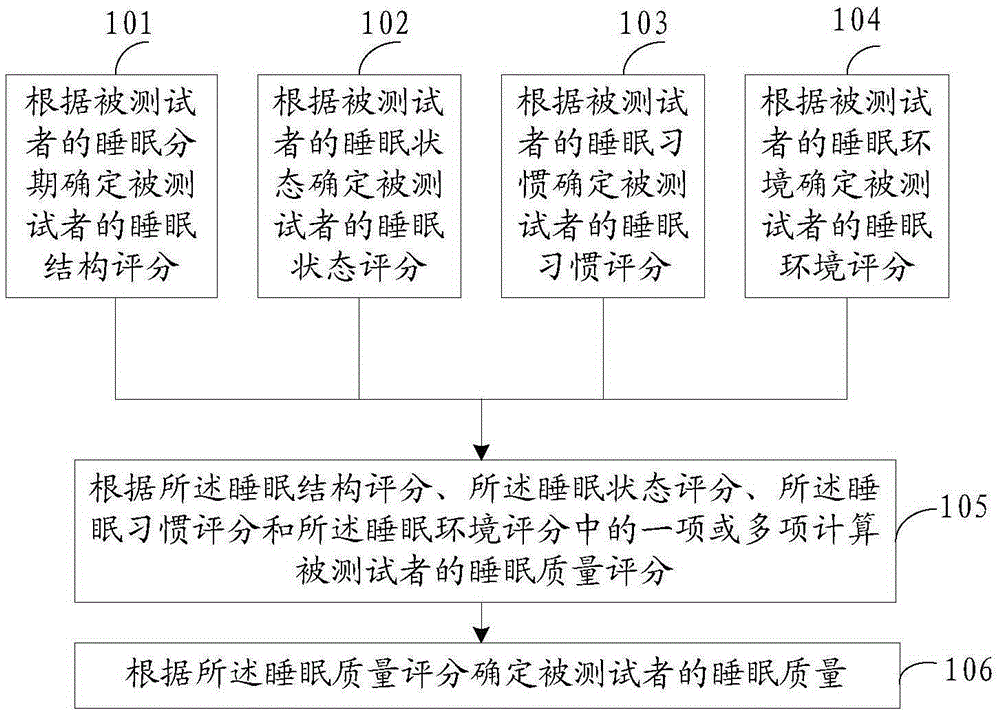

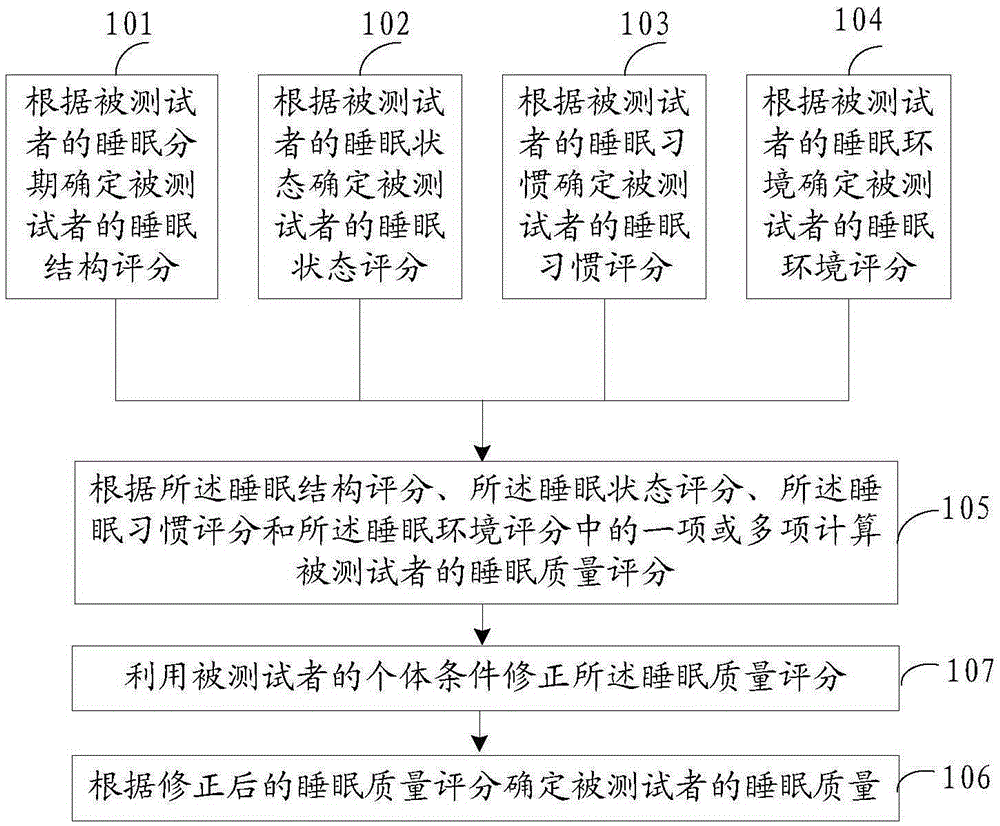

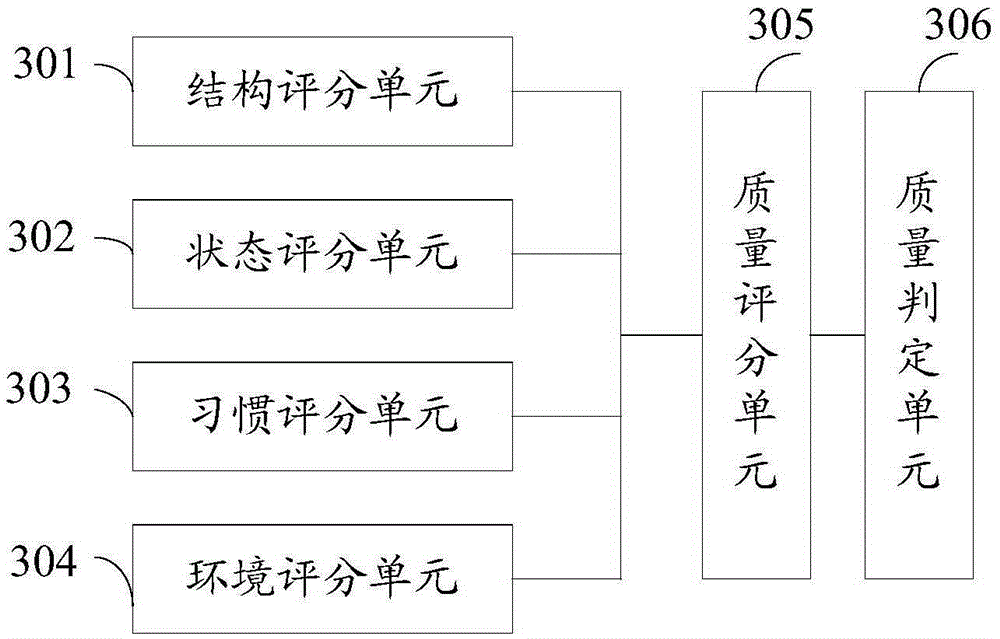

Sleep quality judging method and sleep instrument

InactiveCN105231997AImprove accuracyComprehensive decision factorsDiagnostic recording/measuringSensorsSleep stagingSleep state

The invention discloses a sleep quality judging method and a sleep instrument. The method comprises the following steps: according to the sleep stage of a tested subject, determining a sleep structure score of the tested subject; according to the sleep state of the tested subject, determining a sleep state score of the tested subject; according to the sleep habit of the tested subject, determining a sleep habit score of the tested subject; according to the sleep environment of the tested subject, determining a sleep environment score of the tested subject; according to one or more of the sleep structure score, the sleep state score, the sleep habit score and the sleep environment score, calculating a sleep quality score of the tested subject; and according to the sleep quality score, determining the sleep quality of the tested subject.

Owner:NEUSOFT XIKANG ALPS (SHENYANG) TECH CO LTD

Biomarkers

InactiveUS20080220530A1Minimal sample preparationSuppress water NMR resonanceMagnetic measurementsMicrobiological testing/measurementDiseaseBipolar mood disorder

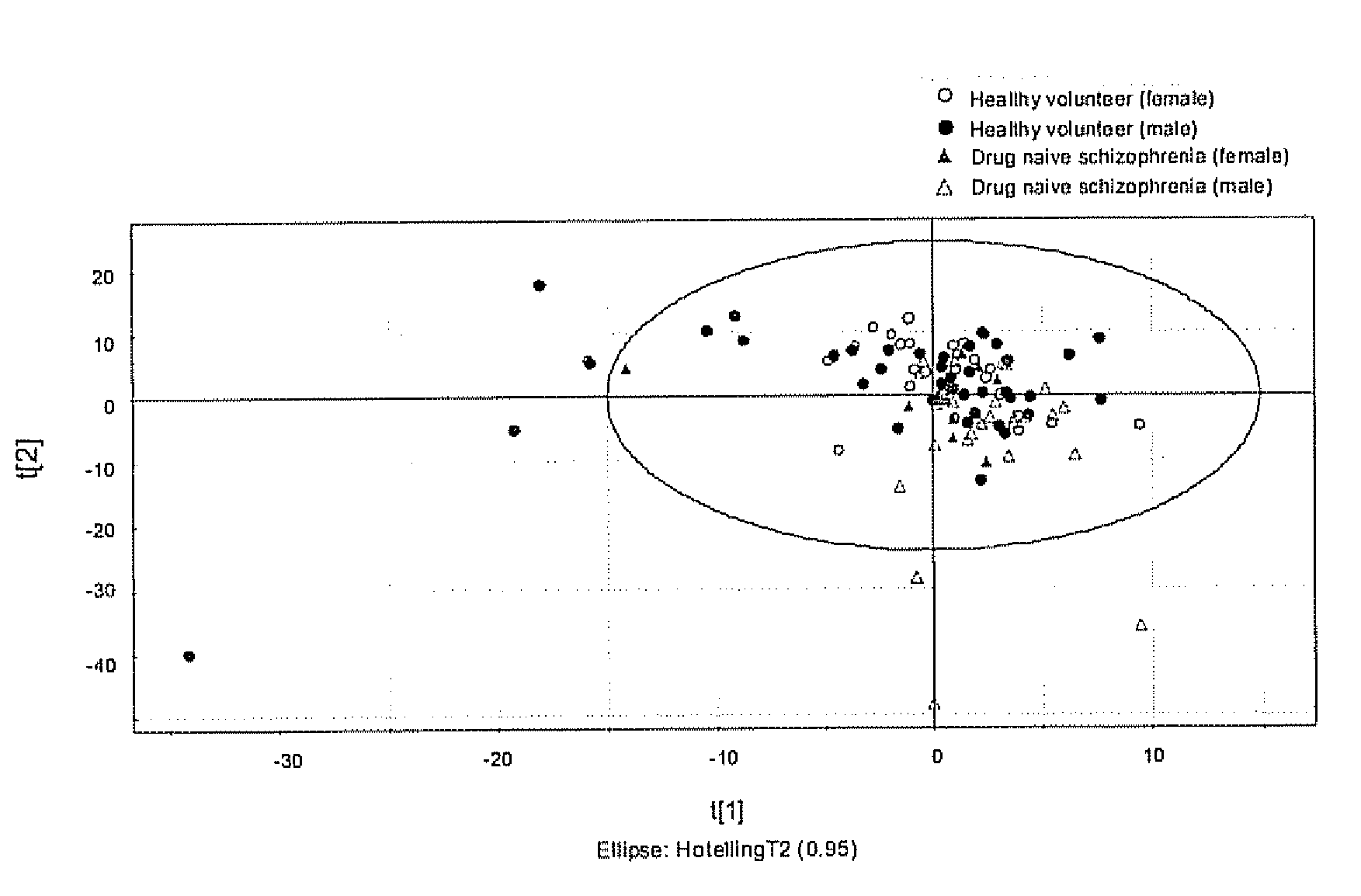

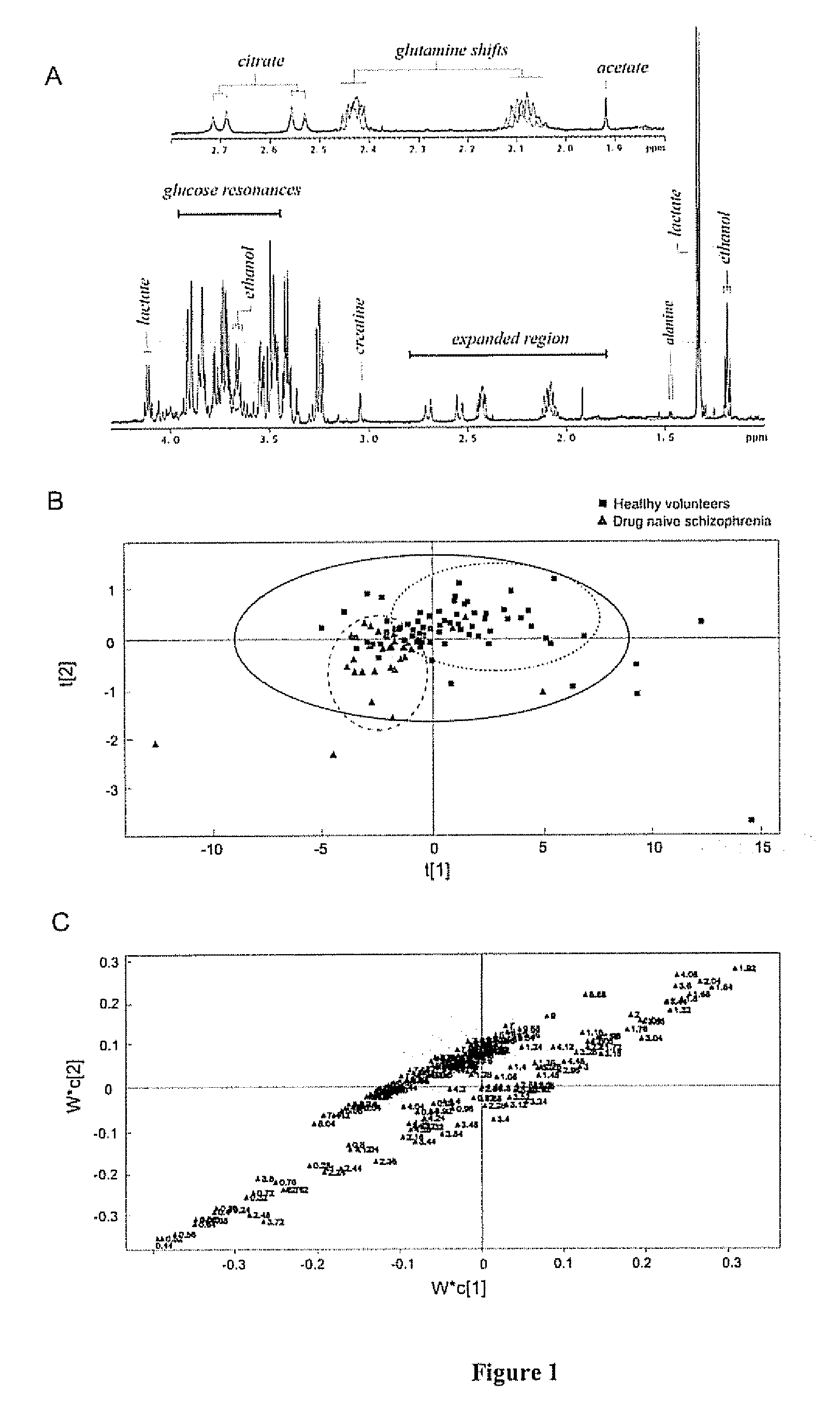

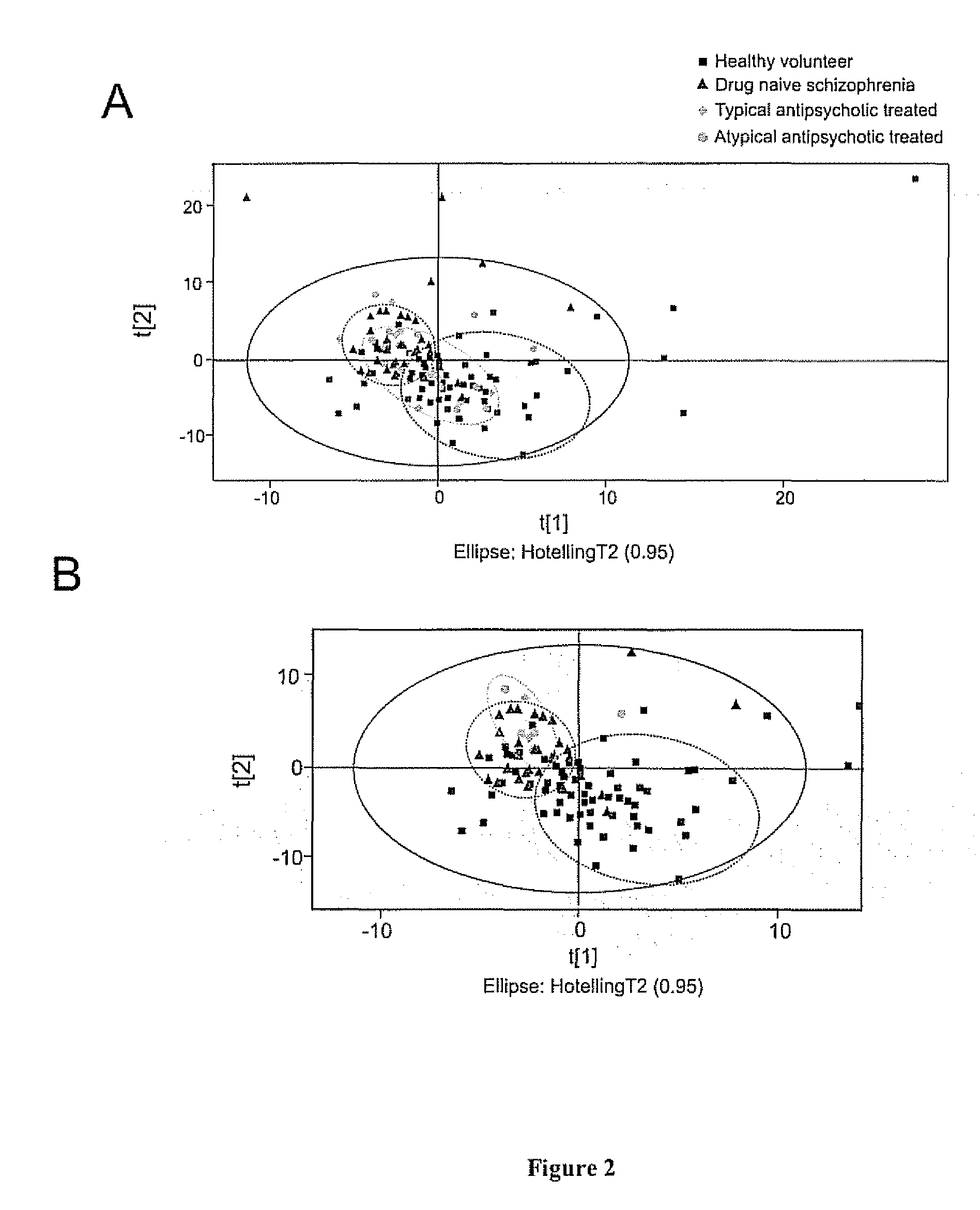

The invention relates to methods for diagnosing or monitoring psychotic disorders such as schizophrenic or bipolar disorders, comprising measuring the level of one or more biomarker(s) present in a cerebrospinal fluid sample taken from a test subject, said biomarker(s) being selected from the group consisting of: glucose, lactate, acetate species and pH. The invention also relates to methods of diagnosing or monitoring a psychotic disorder in a subject comprising providing a test sample of CSF from the subject, performing spectral analysis on said CSF test sample to provide one or more spectra, and, comparing the one or more spectra with one or more control spectra. The invention also relates to sensors, biosensors, multi-analyte panels, arrays, assays and kits for performing methods of the invention.

Owner:PSYNOVA NEUROTECH LTD

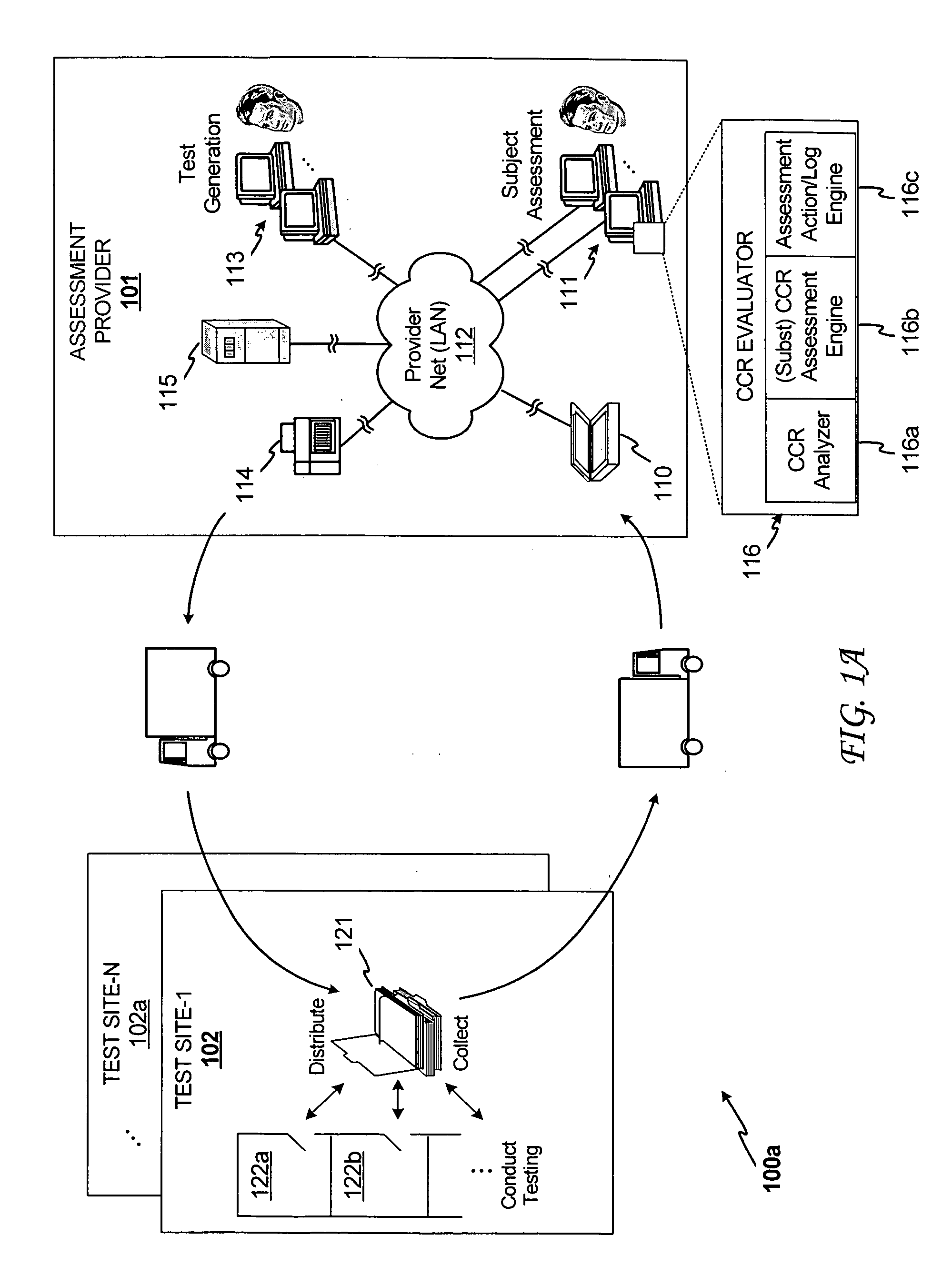

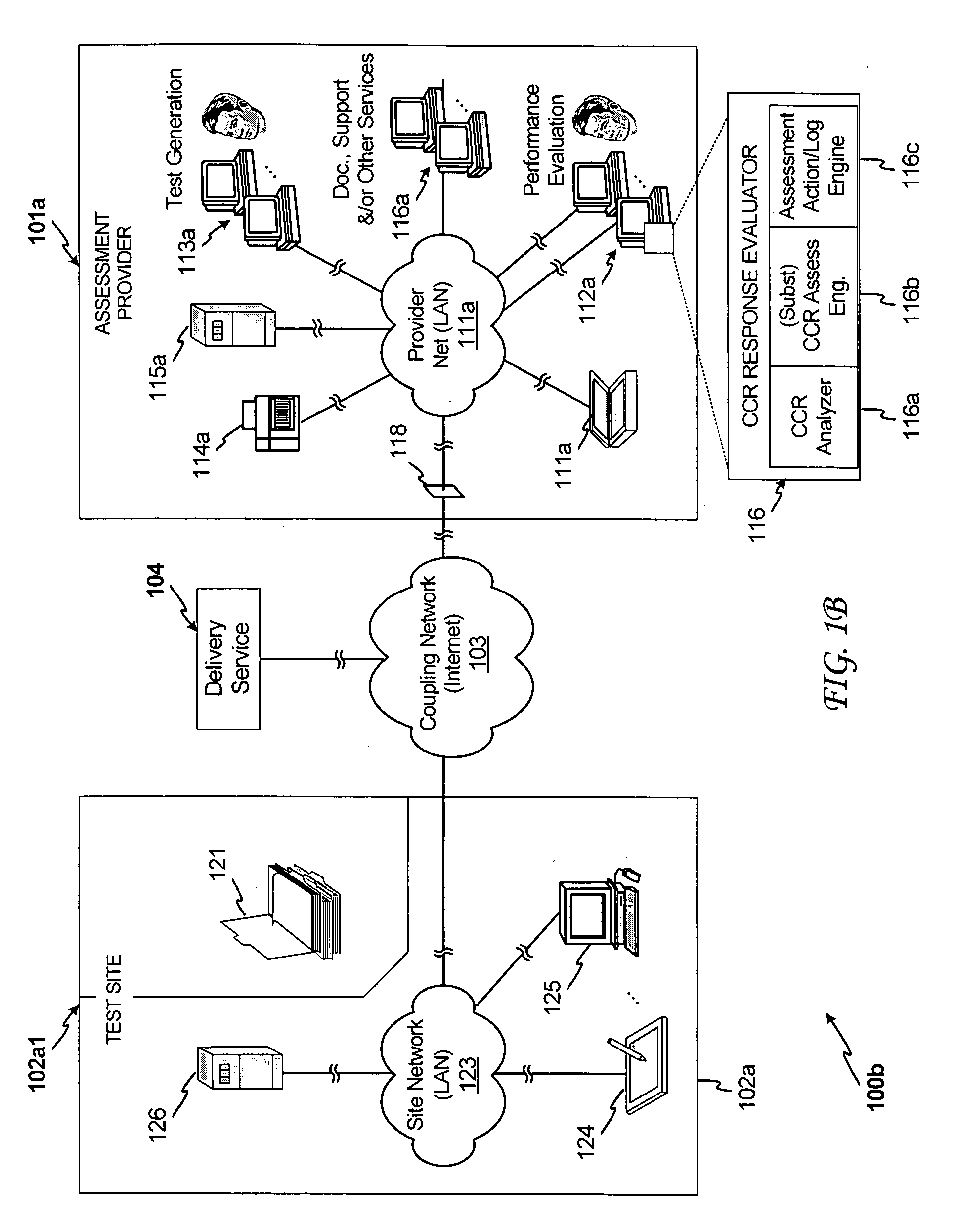

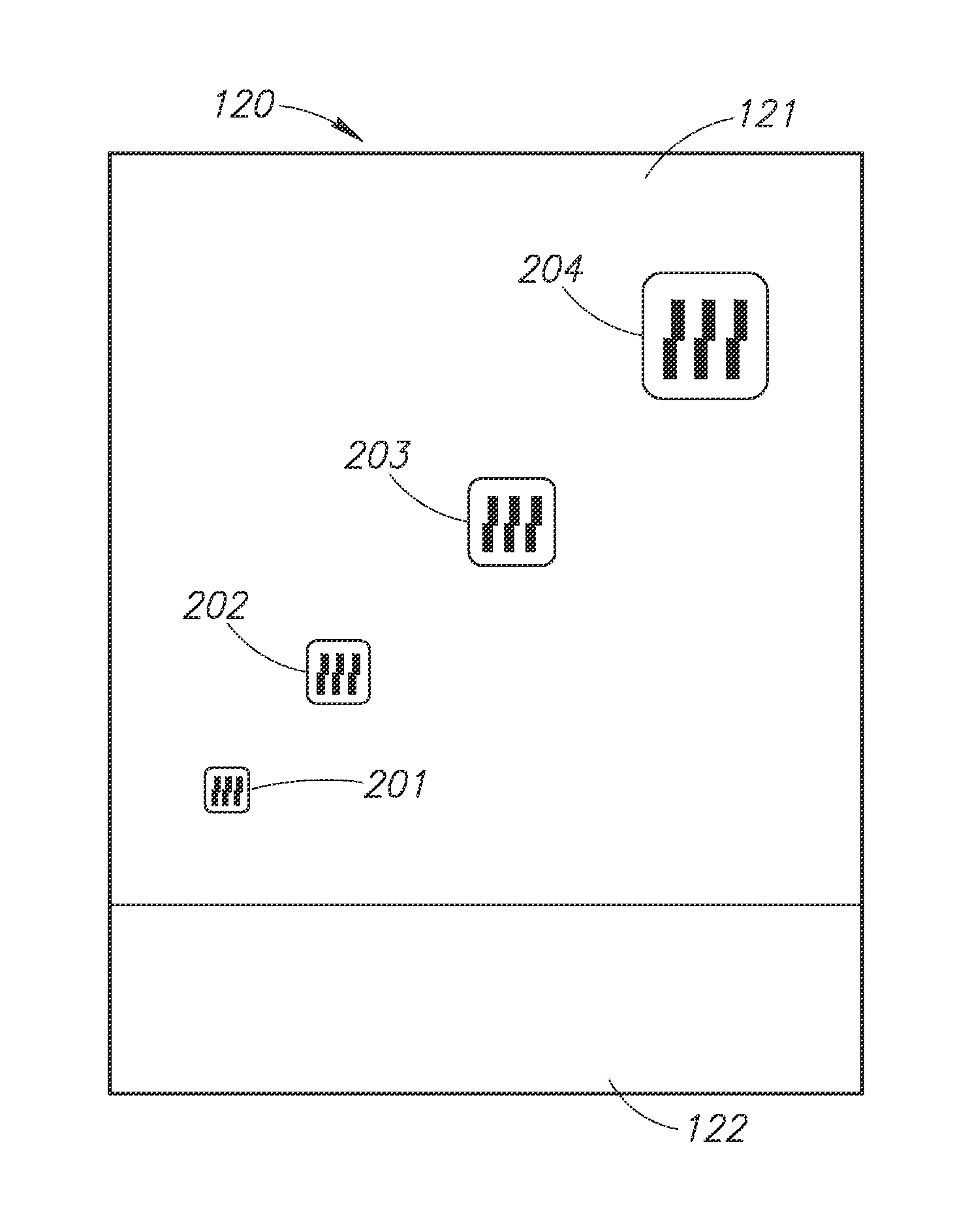

System and method for automated assessment of constrained constructed responses

ActiveUS20060286539A1Efficient and robustAvoid problemsElectrical appliancesMechanical appliancesGraphicsElectronic form

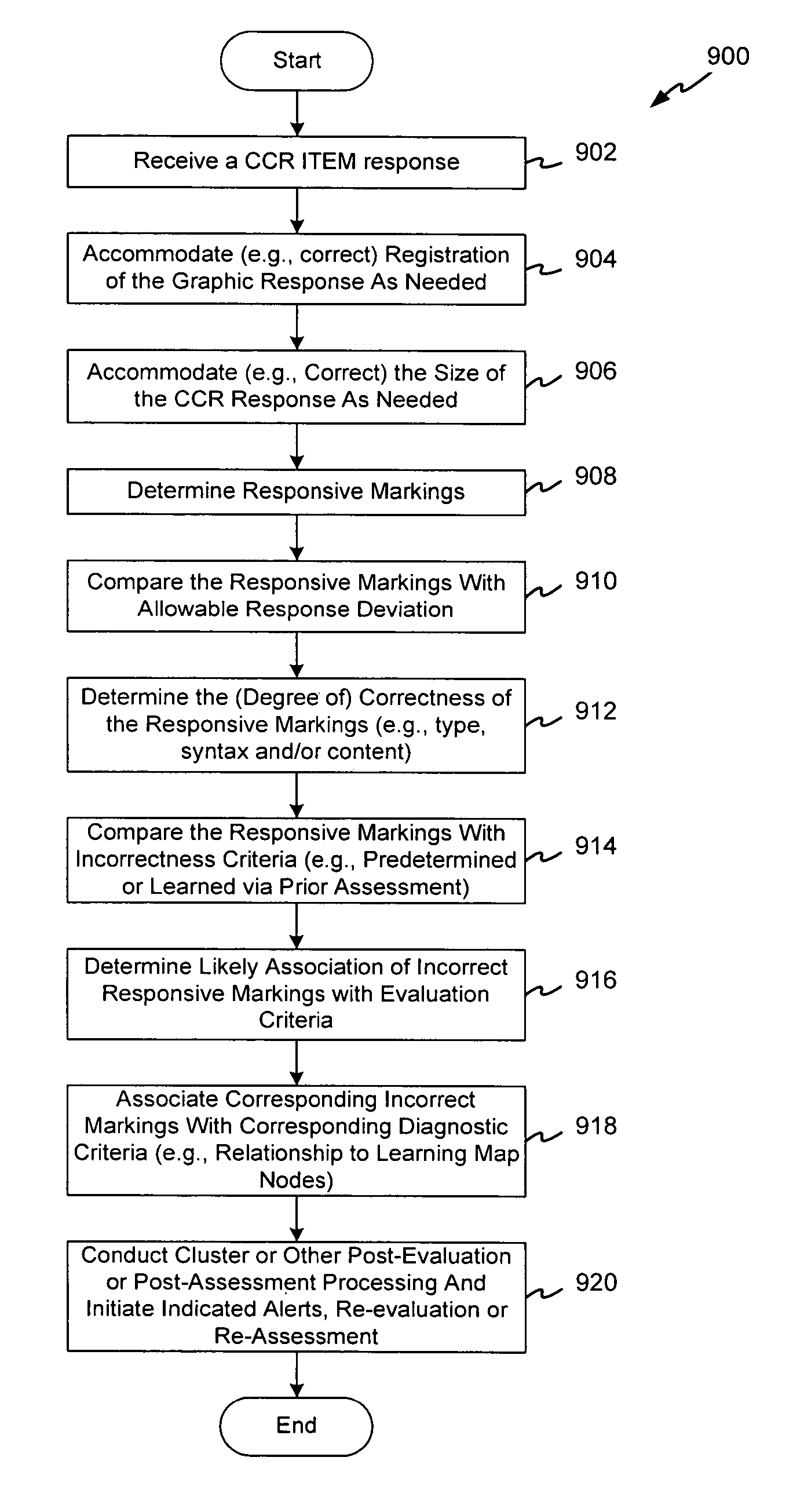

A system and method for automated assessment of constrained constructed responses provides for automatic, e.g., programmatic, assessing of a test subject response to a constrained constructed response item or question. In one embodiment, paper test materials with test subject markings thereon are converted to electronic form. Test subject markings are further isolated, for example, by registration, sizing and removal of markings other than a graphic response. The subject markings are further compared with a baseline response, correctness deviation criteria and incorrectness deviation criteria (e.g., correctness, incorrectness, substantial correctness, substantial incorrectness, and so on) from which one or more of a score, further learning or other assessment results may be determined. Cluster analysis or other post-evaluation or post-assessment processing may also be conducted, or re-evaluation or re-assessment may also be conducted.

Owner:DATA RECOGNITION

Circular preferential hyperacuity perimetry video game to monitor macular and retinal diseases

Systems and methods for providing a video game to map macular visual acuity comprising a test where a fixation point is ensured by brief simultaneous presentation of central and pericentral targets. The game may be implemented on a hardware platform including a video display, a user input device, and a video camera. The camera is used to monitor ambient light level and the distance between the device and the eyes of the test subject. The game serves as a macular acuity perimeter that produces a map of the acuity of an eye that may be compared with normative data. The type of acuity tested is preferably Vernier acuity, but resolution acuity can also be tested. The test results are transmitted to a health care professional by telecommunications means to facilitate the diagnosis or monitoring of age-related macular degeneration or other relevant eye diseases.

Owner:GOBIQUITY INC

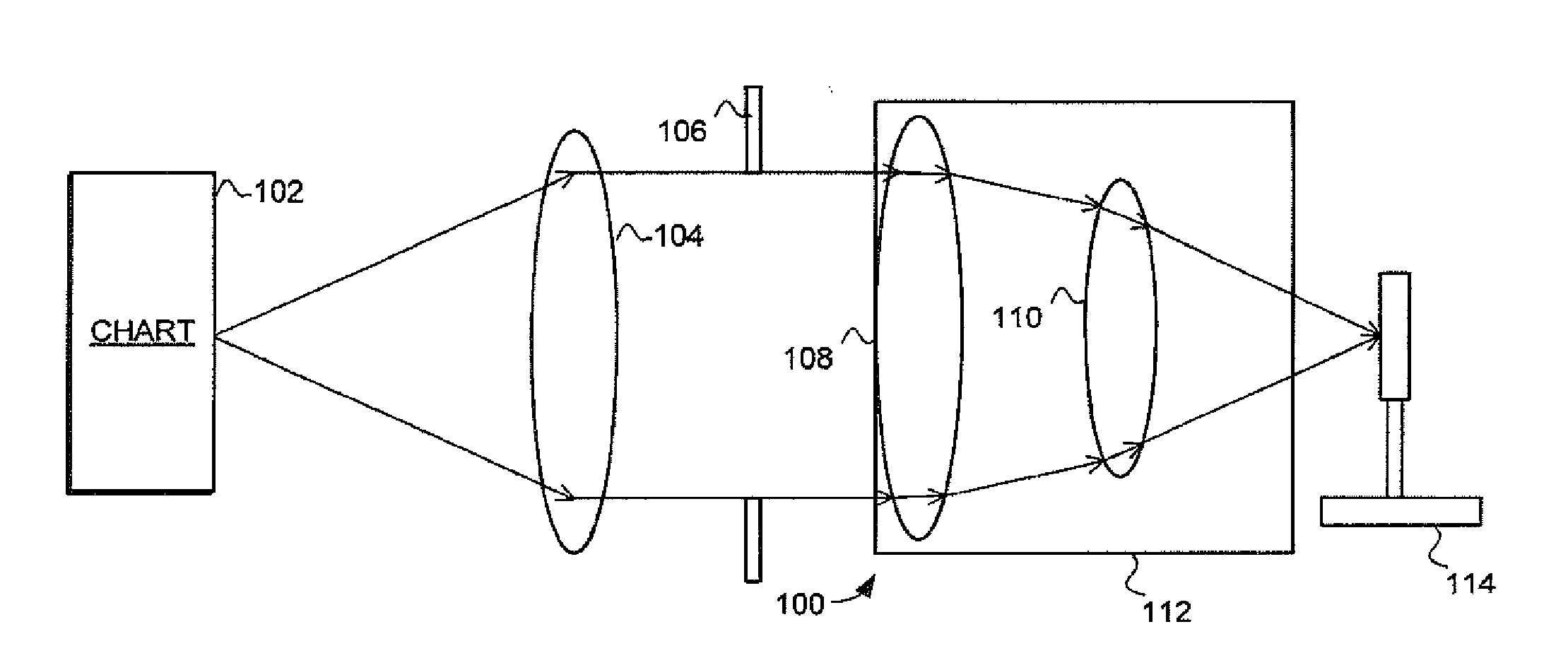

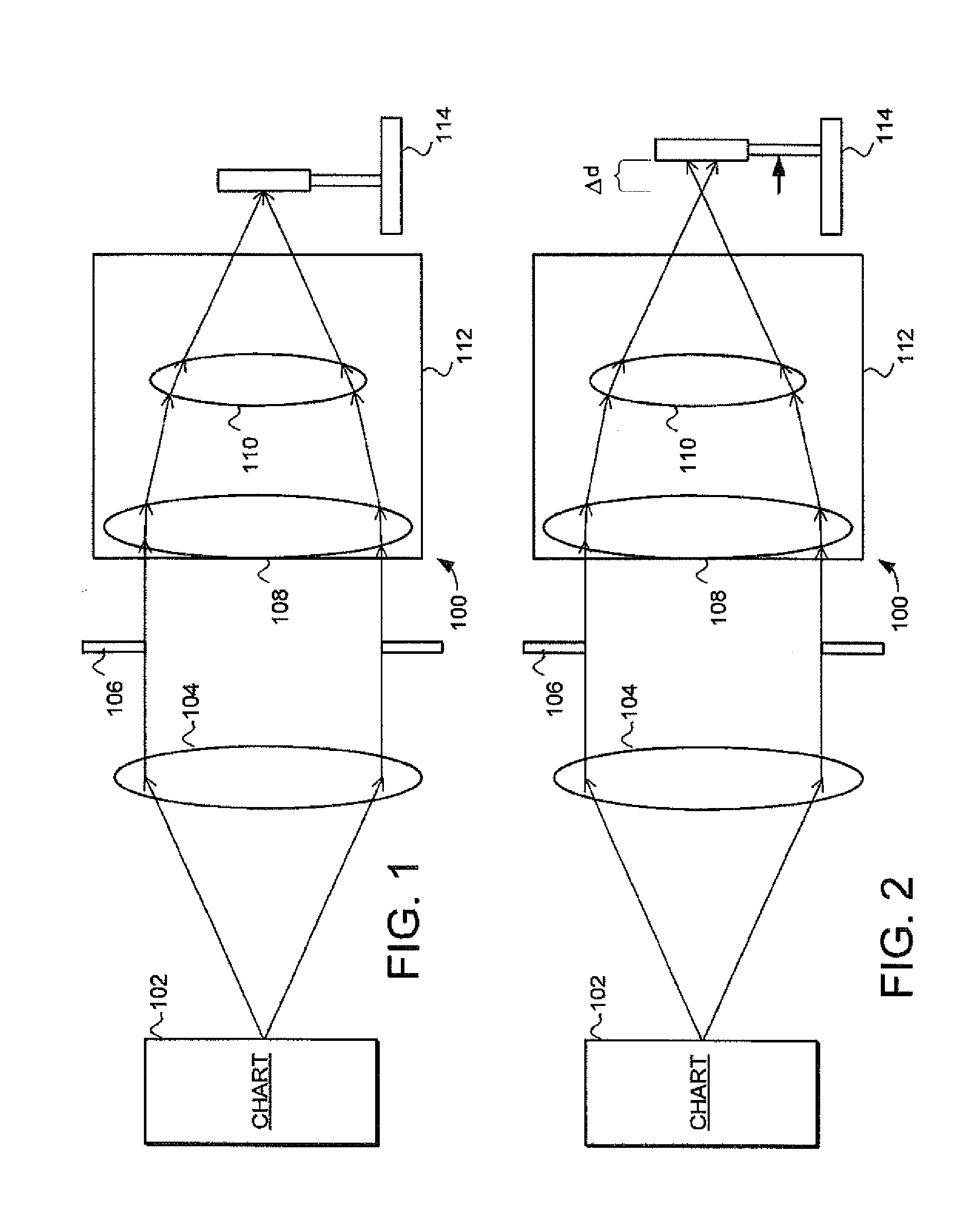

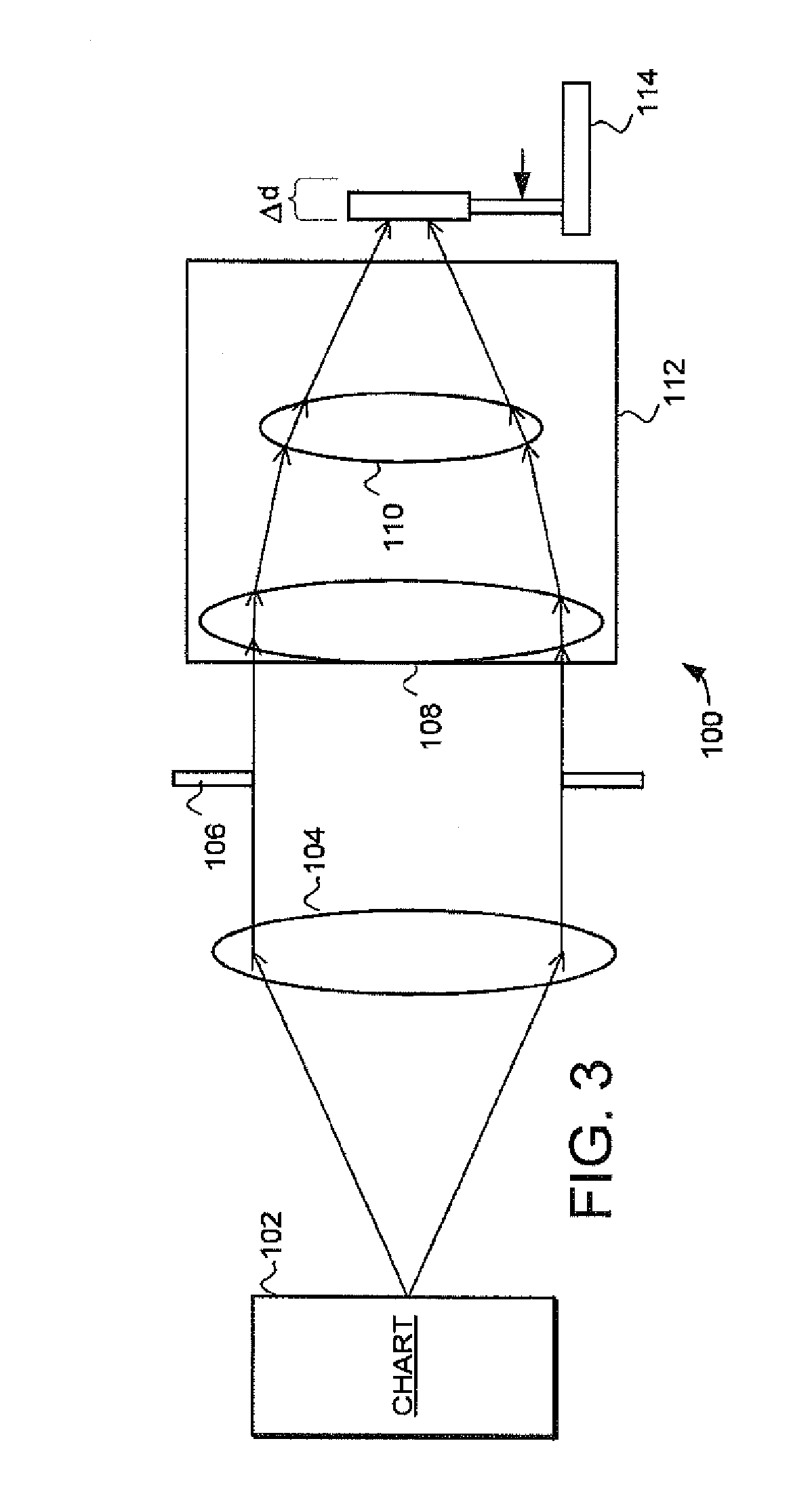

System and method for evaluating intraocular lens performance

Systems and methods for providing improved techniques for evaluating performance of intraocular lenses. Such techniques can be used to evaluate lens designs and can help reduce the need for multiple clinical trials that may otherwise be needed to evaluate multiple design iterations. In one embodiment, a method is provided for method for evaluating performance of an intraocular lens, where the method comprises capturing a plurality of images through the intraocular lens at different focus positions; displaying at least one selected image from the plurality of images to a test subject; receiving input from the test subject indicative of perceived acuity of the at least one selected image; and determining a measure of intraocular lens performance from the received input.

Owner:JOHNSON & JOHNSON SURGICAL VISION INC

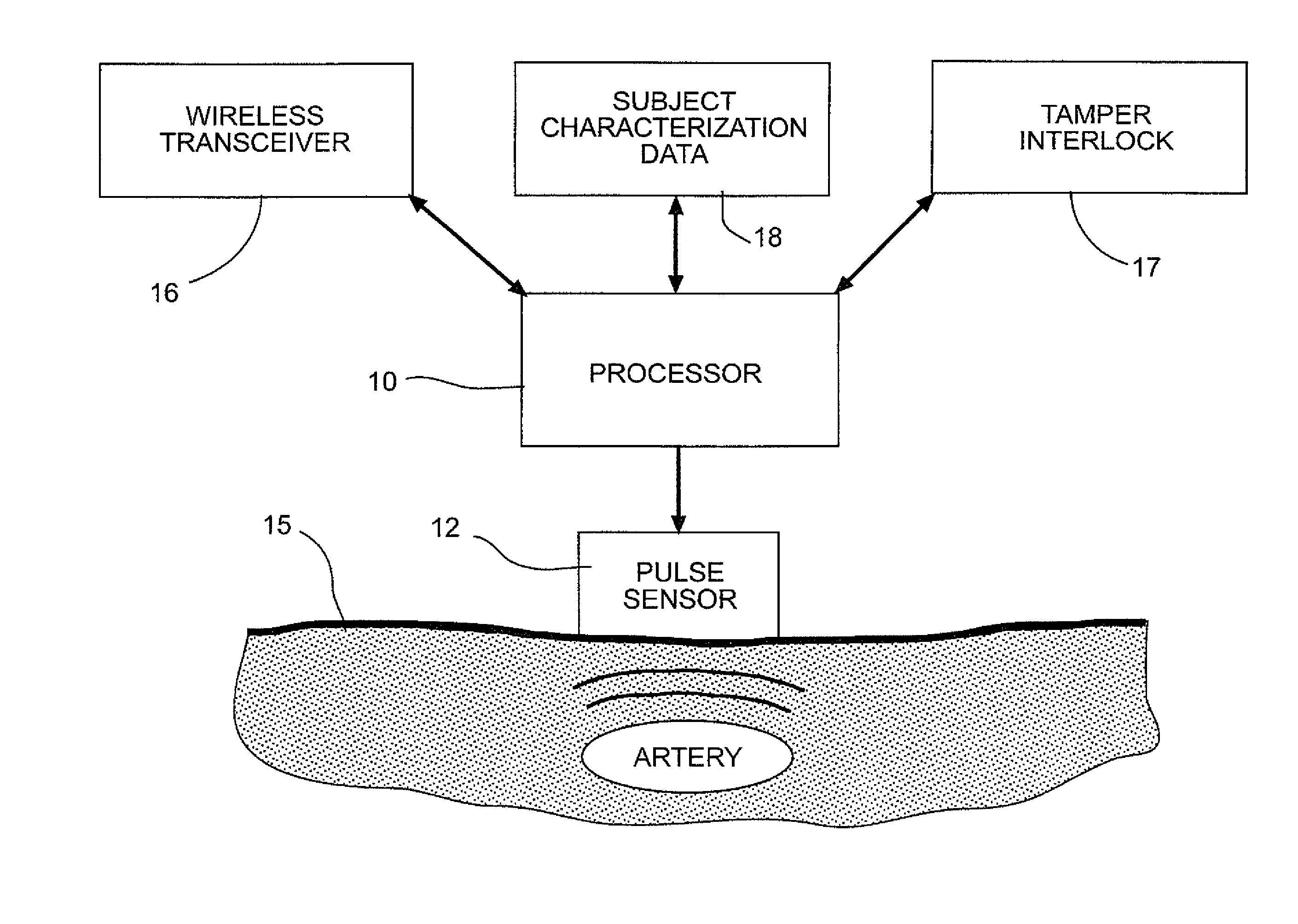

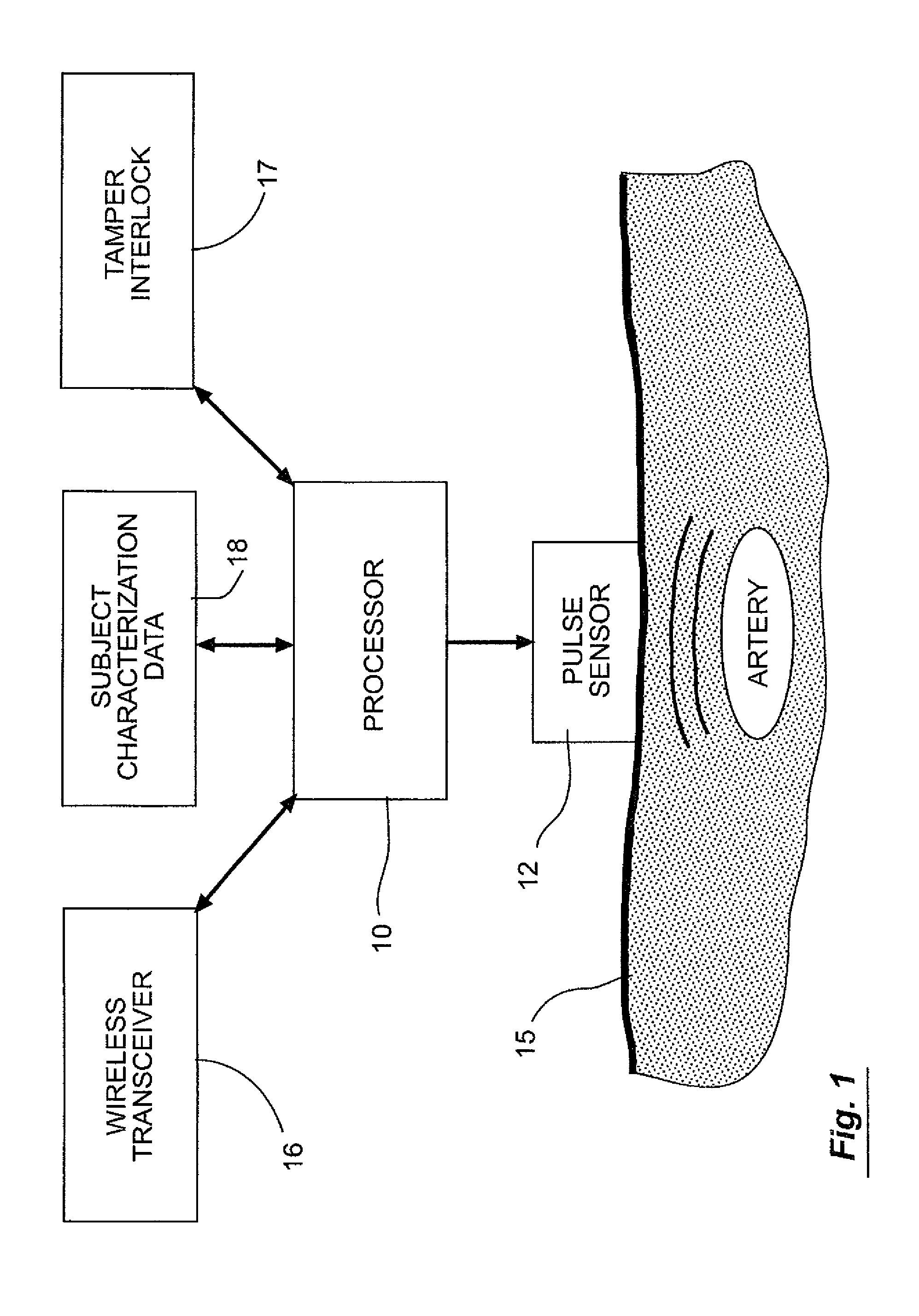

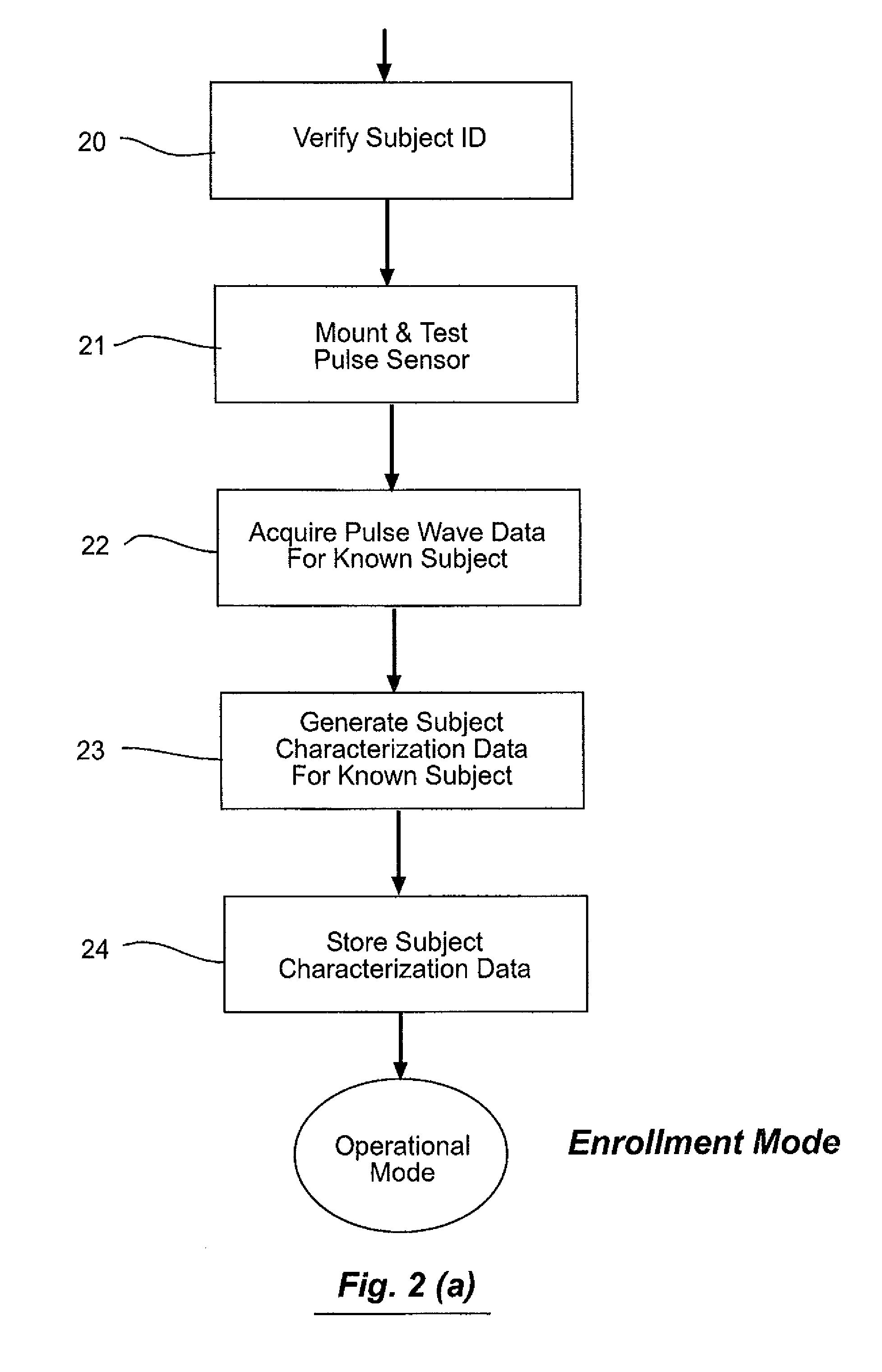

Biometric identification system using pulse waveform

ActiveUS8773239B2Electric signal transmission systemsDigital data processing detailsPhase spaceBlood pressure

A method and system for biometric identity confirmation is based on the pulse wave of a subject. During an initial enrollment mode, pulse wave data for a known subject are used to generate subject characterization data for the known subject. During a subsequent operational mode, pulse wave data for a test subject are analyzed using the subject characterization data to confirm whether the identity of the test subject matches the known subject. The subject characterization data can be a probability density in a phase space in which at least two quasi-periodic variables based on the pulse wave (e.g., blood pressure and volume time-series data) are correlated.

Owner:LIFELOC TECH

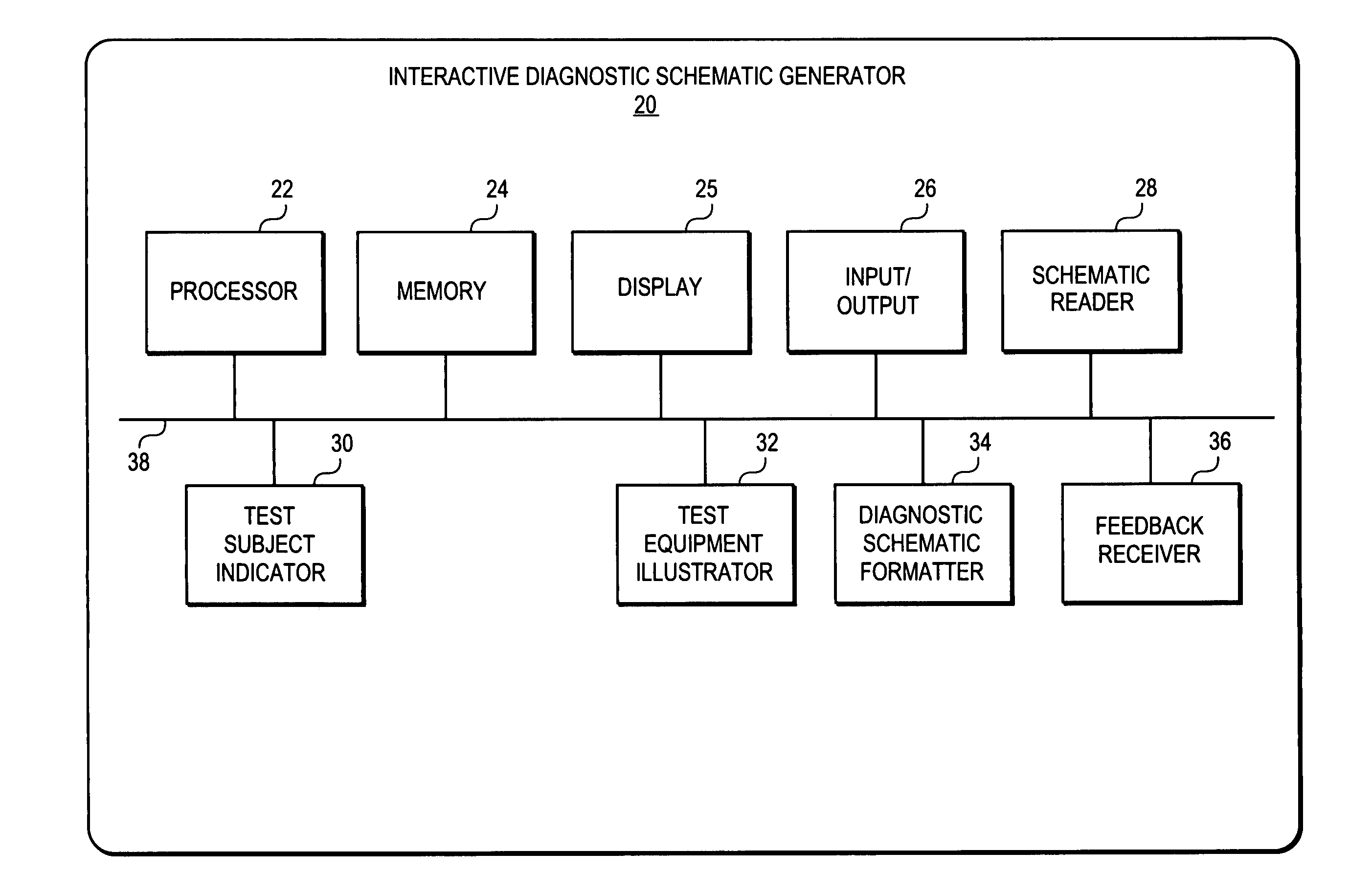

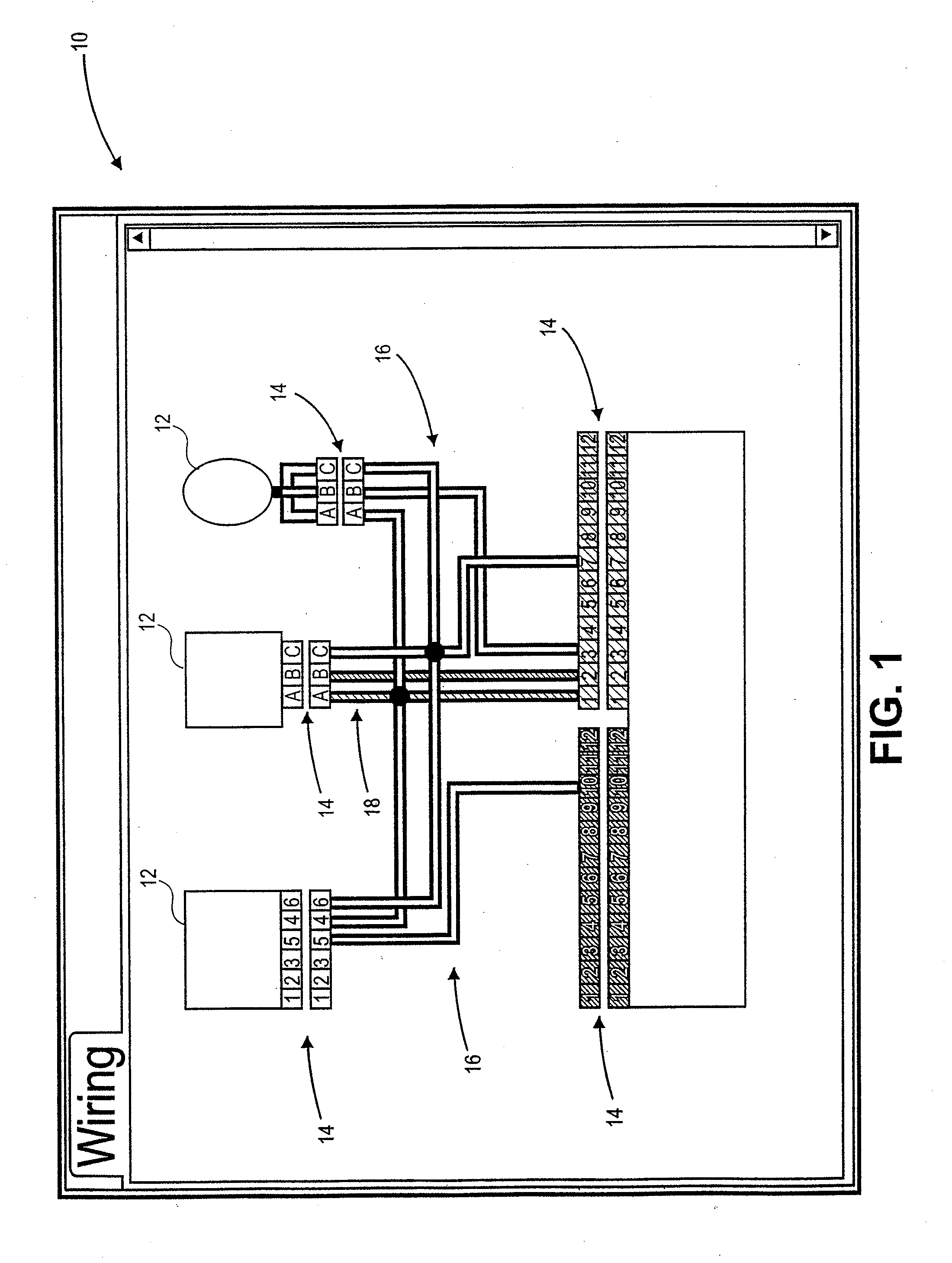

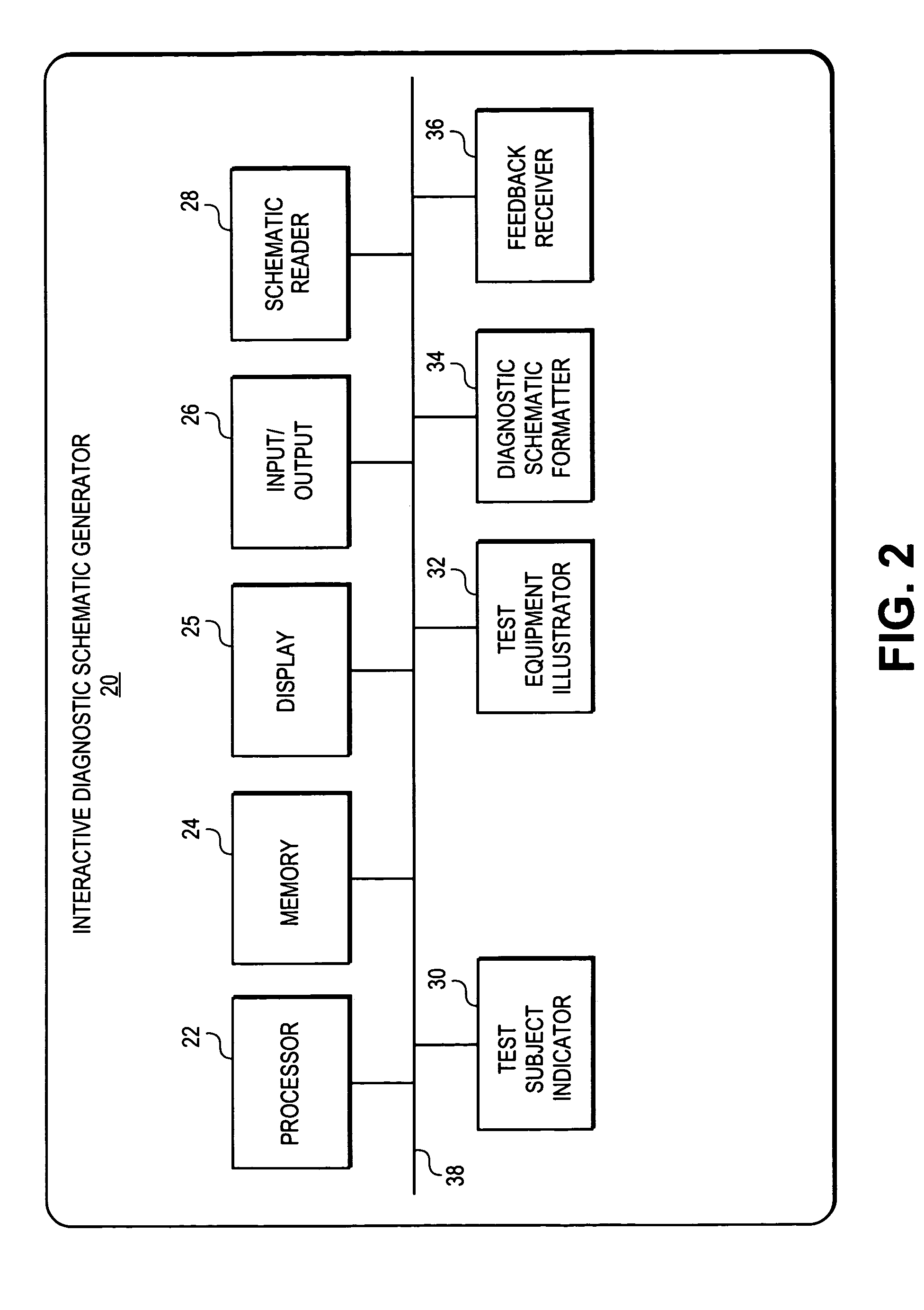

Interactive schematic generating method and apparatus for a vehicle diagnostic procedure

InactiveUS20070294002A1Vehicle testingRegistering/indicating working of vehiclesDiagnostic programUser input

An interactive diagnostic schematic generator illustrates diagnostic test procedures for diagnosing failure modes of a vehicle. The schematic generator reads a schematic data file such as a wiring diagram from a computer memory, indicates a test subject in the schematic or illustrates a location where test equipment is to be connected, and formats the schematic for display on a display device. The schematic generator also receives feedback from a vehicle onboard computer, test equipment or user input indicating that the action has been performed, and removes the indication of the test subject in the schematic. The schematic generator further marks the test subject to indicate that the action has been performed with a marking style that is visually distinct from the indicating style, optionally indicating that the result has validated or invalidated the test subject.

Owner:SPX CORP

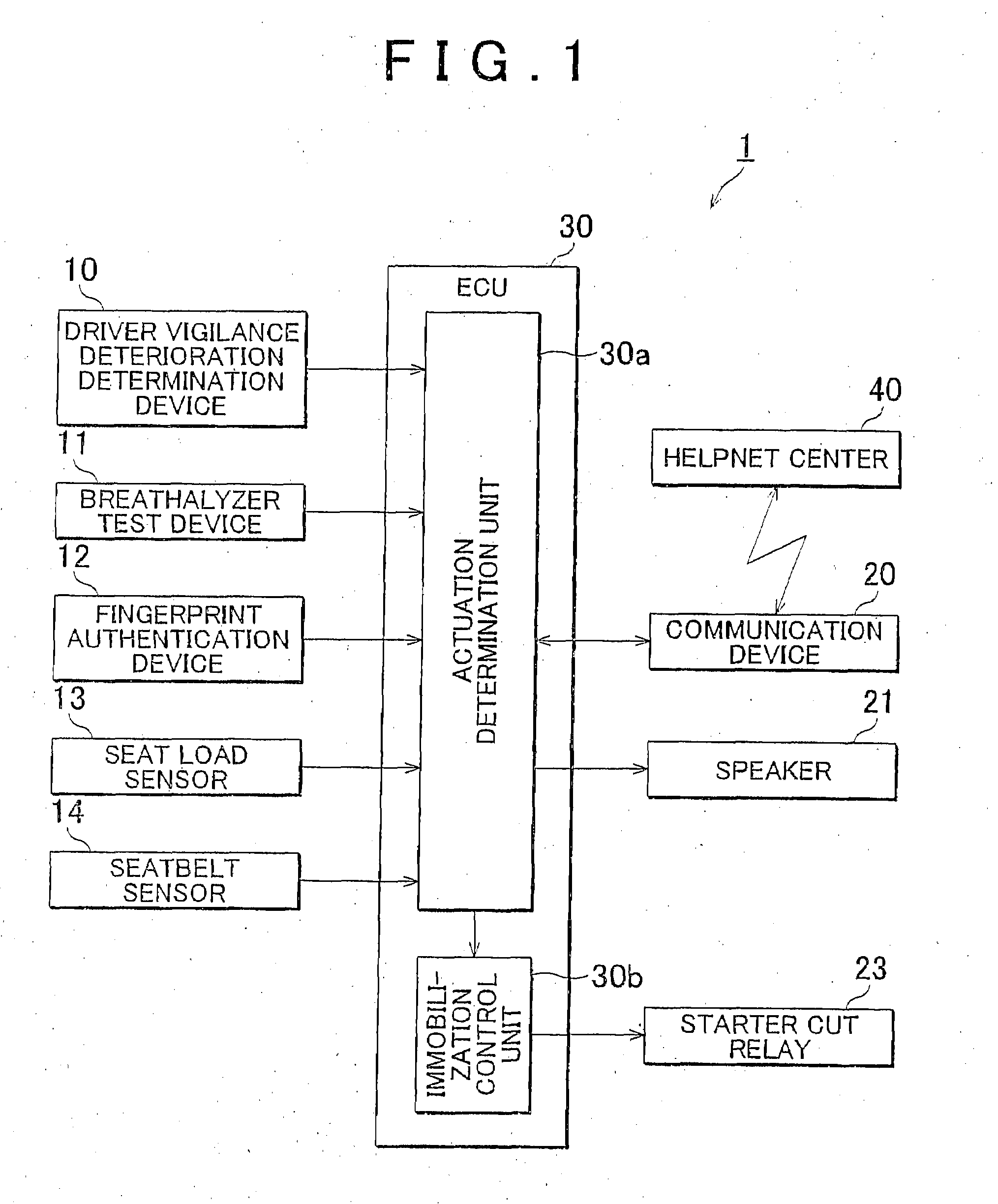

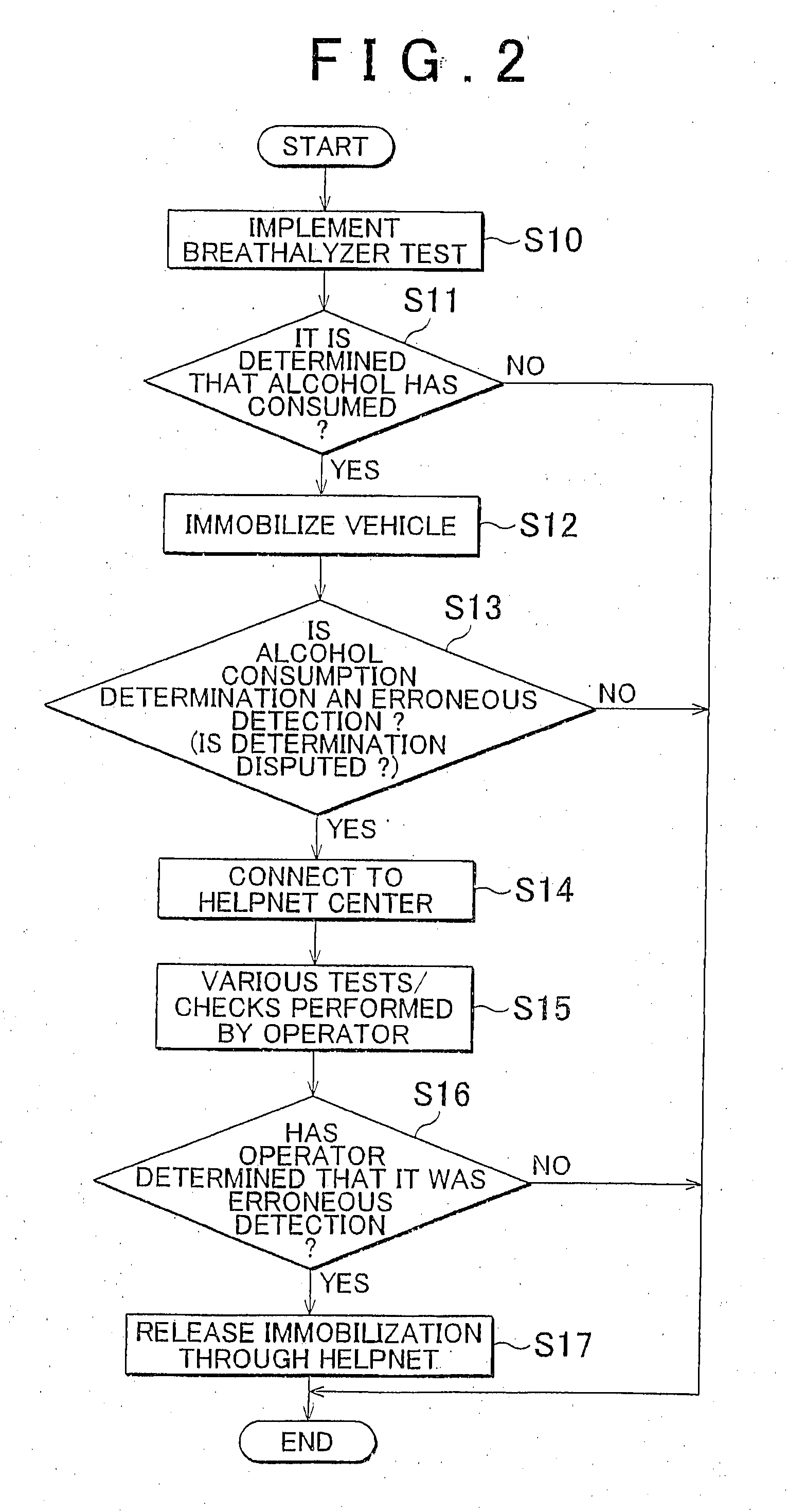

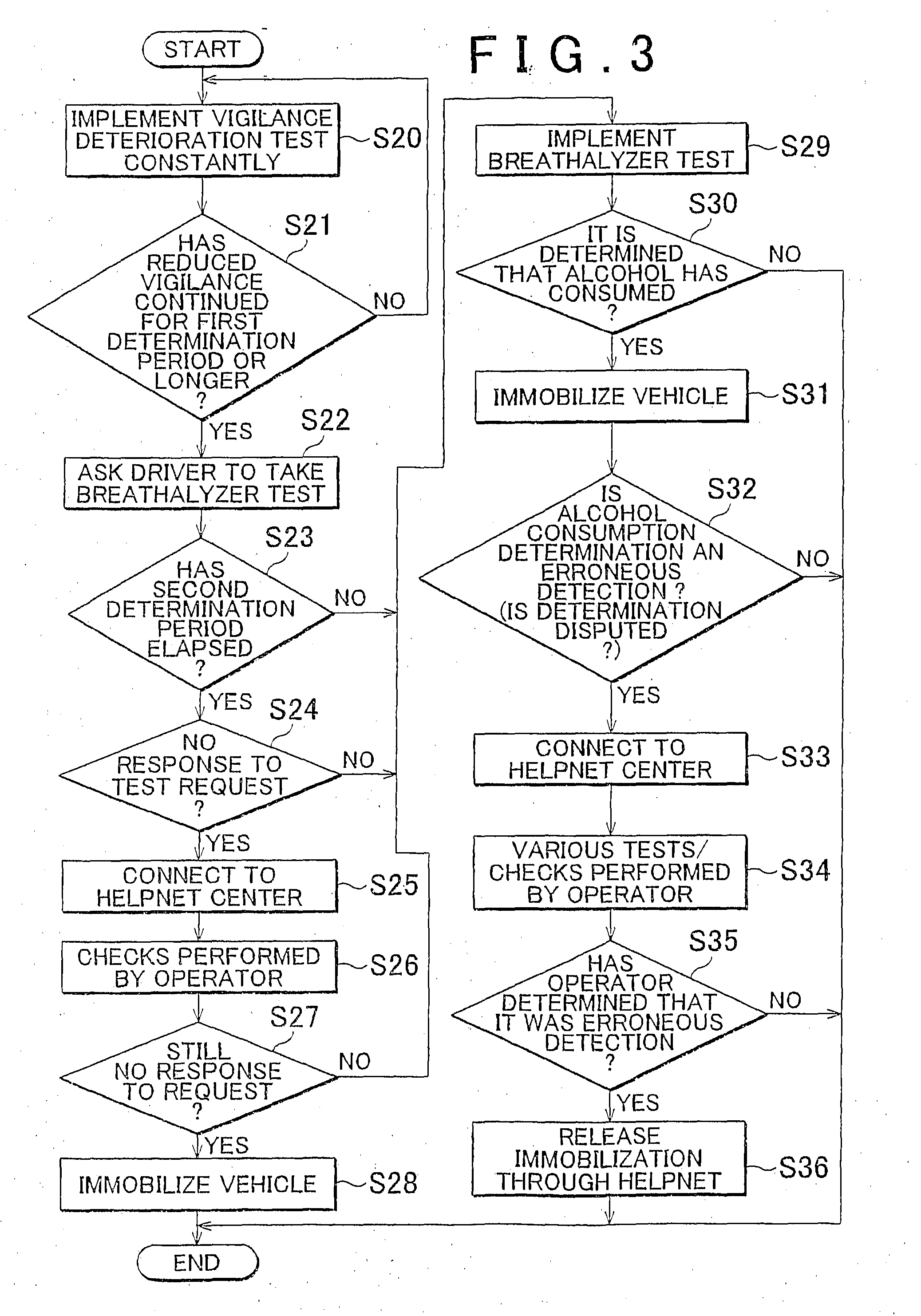

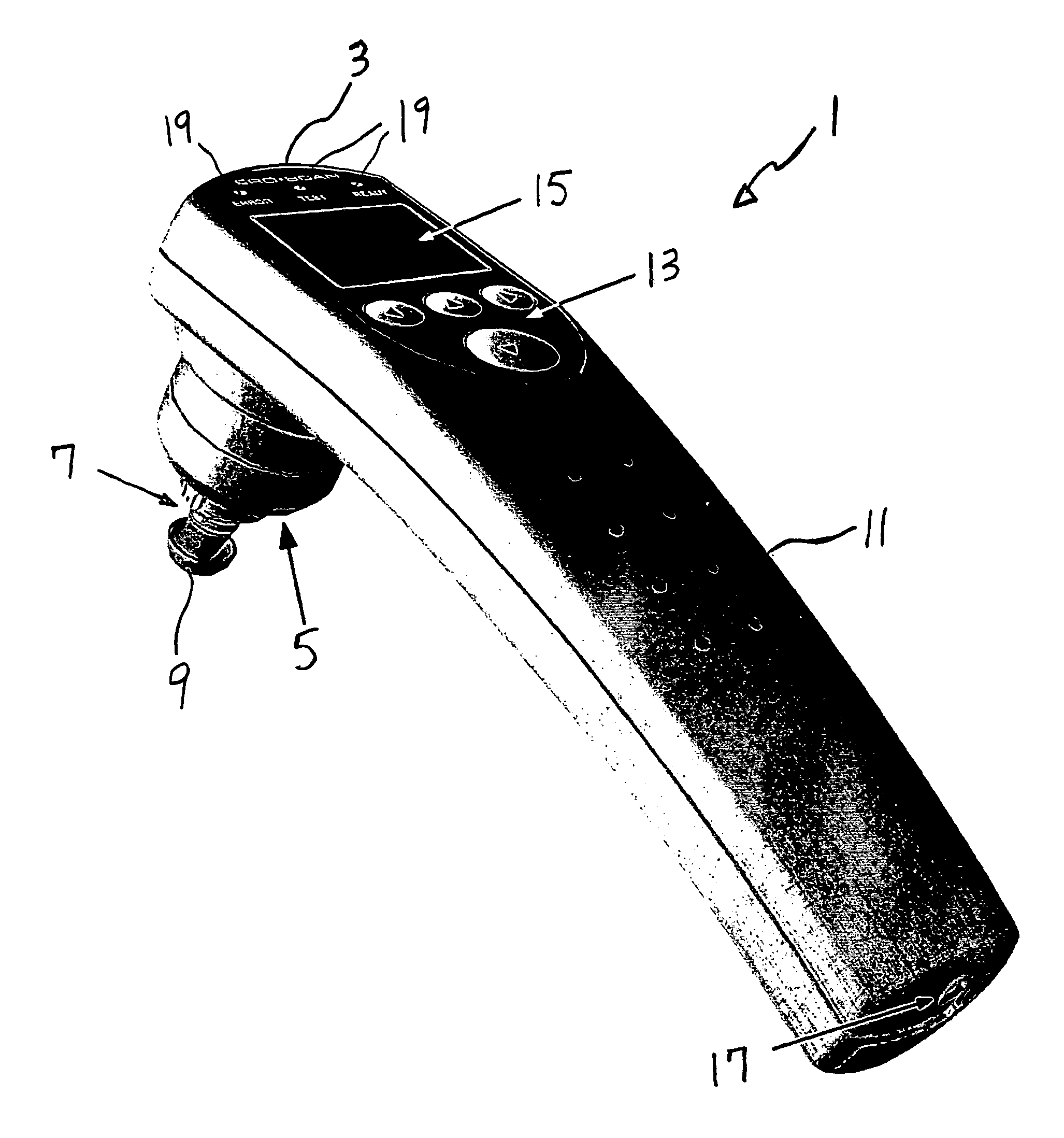

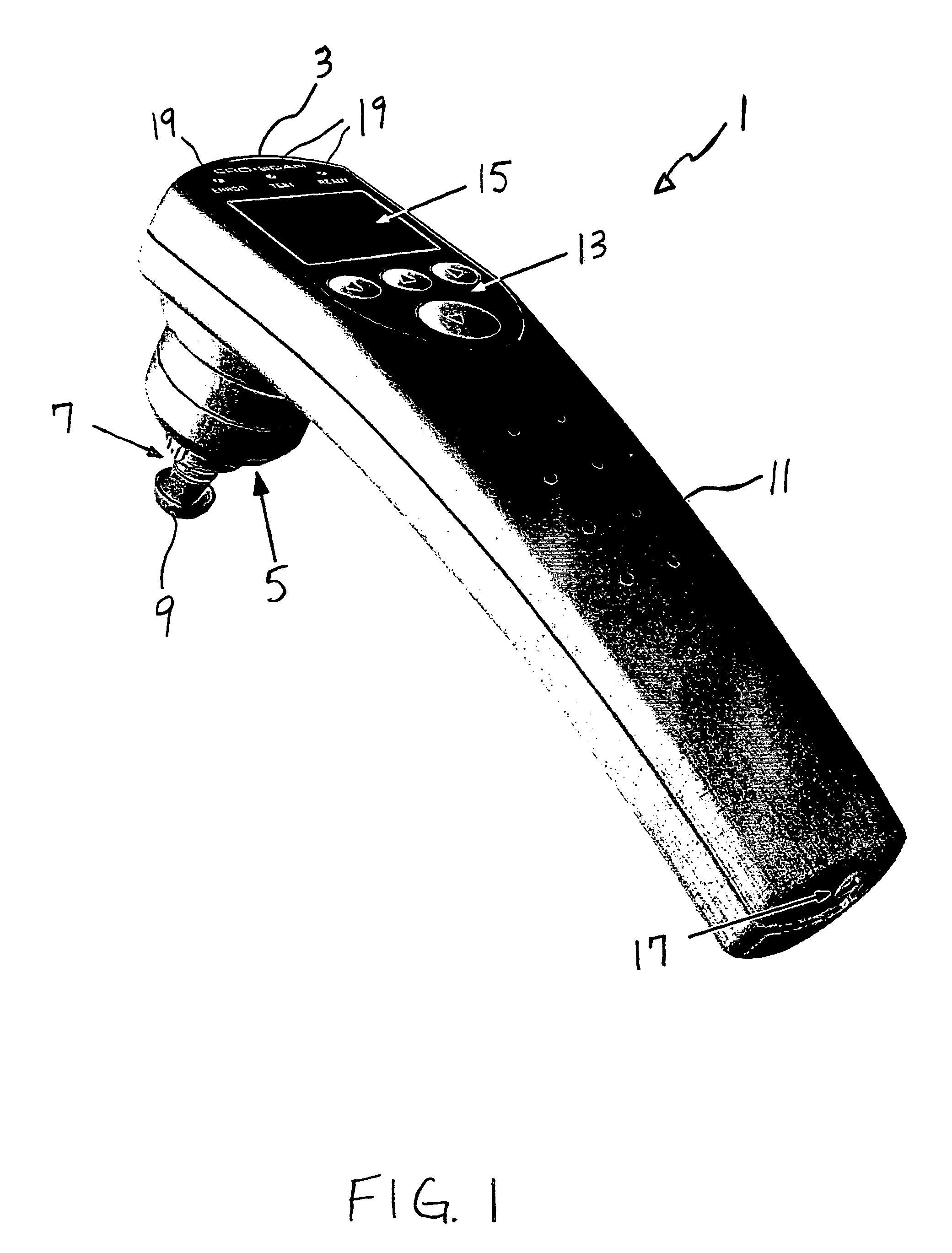

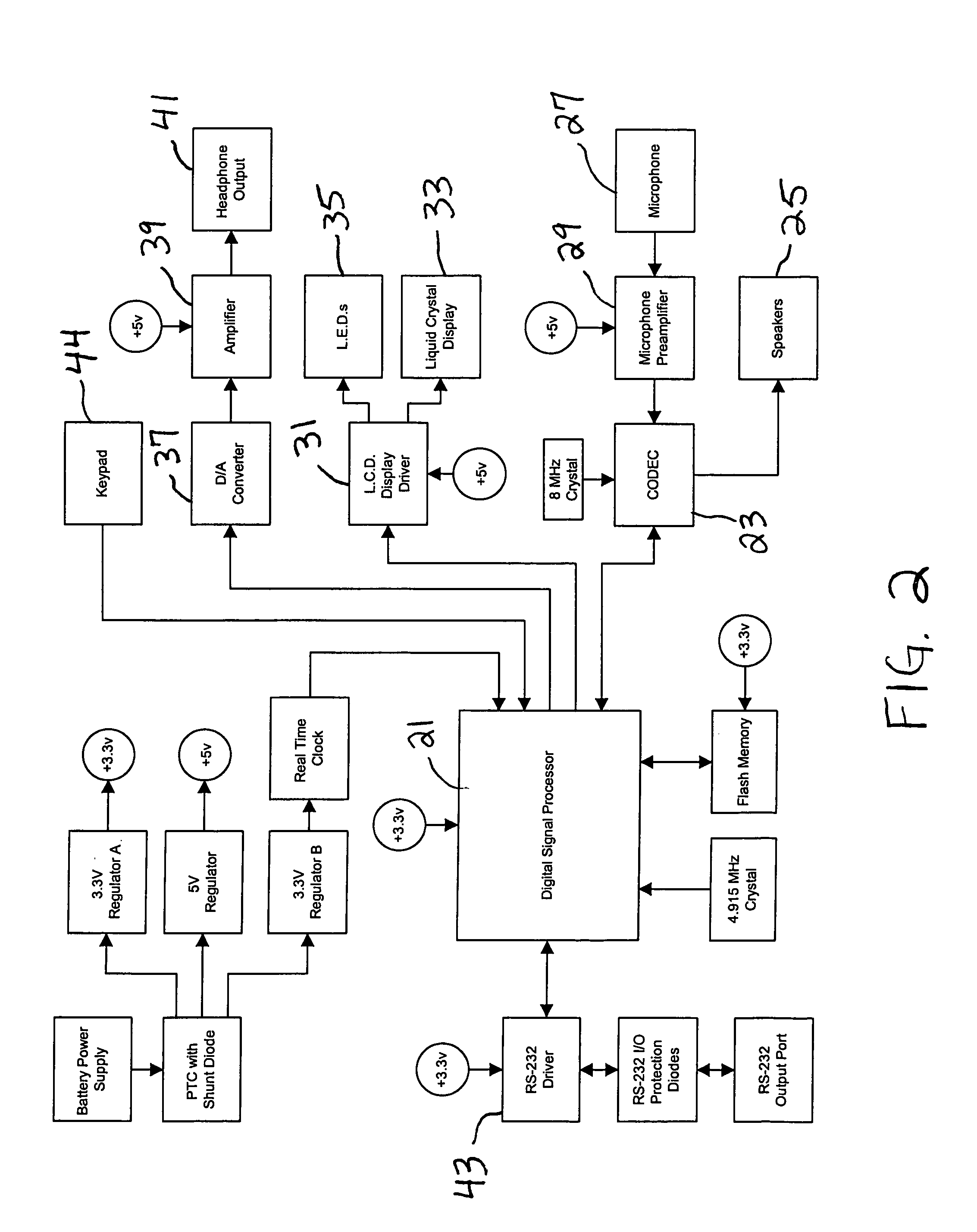

Breathalyzer test device

InactiveUS20100028210A1Reduce troubleReduce testingWithdrawing sample devicesDriver input parametersMedicineTest fixture

A breathalyzer test device includes vigilance detecting means for detecting the vigilance of a test subject, and breathalyzer test means for performing a breathalyzer test on the subject based on the vigilance detected by the vigilance detecting means.

Owner:TOYOTA JIDOSHA KK

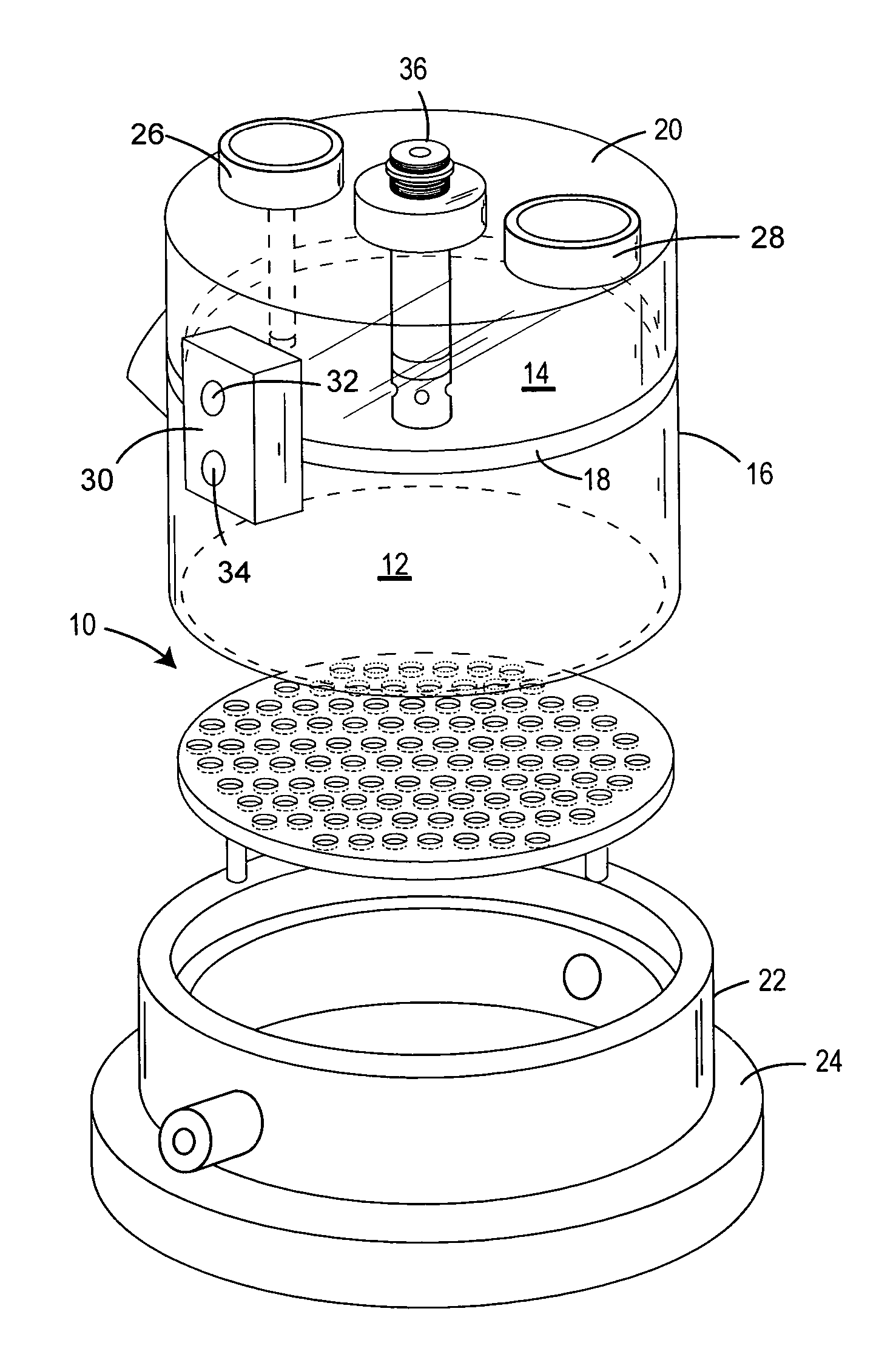

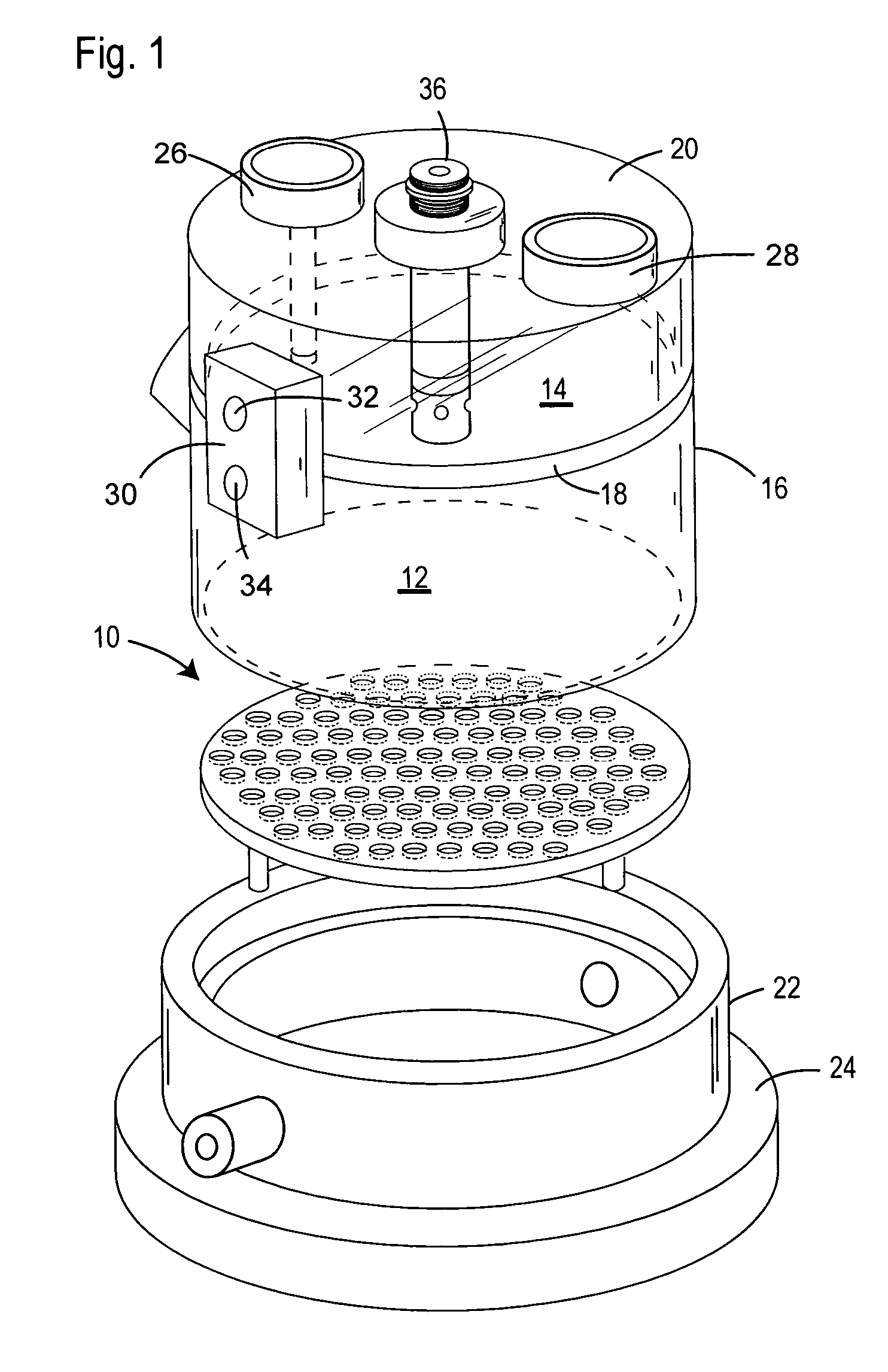

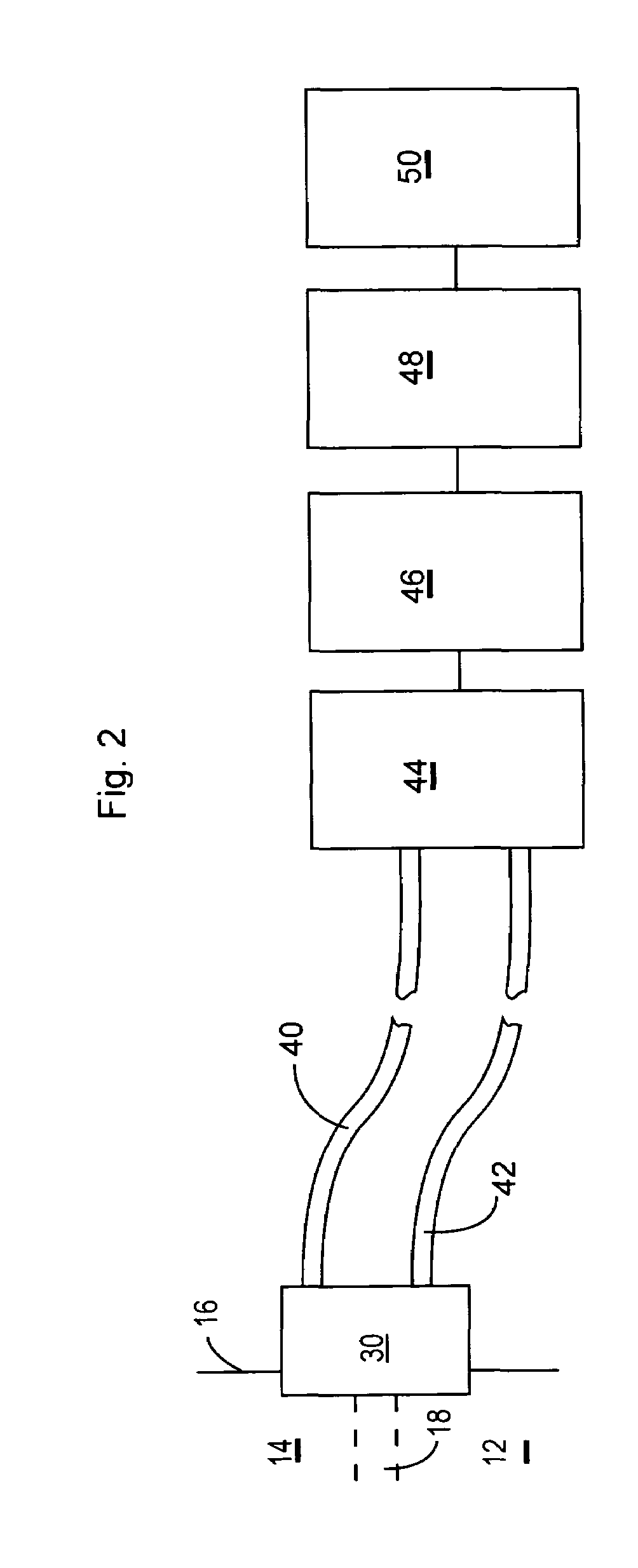

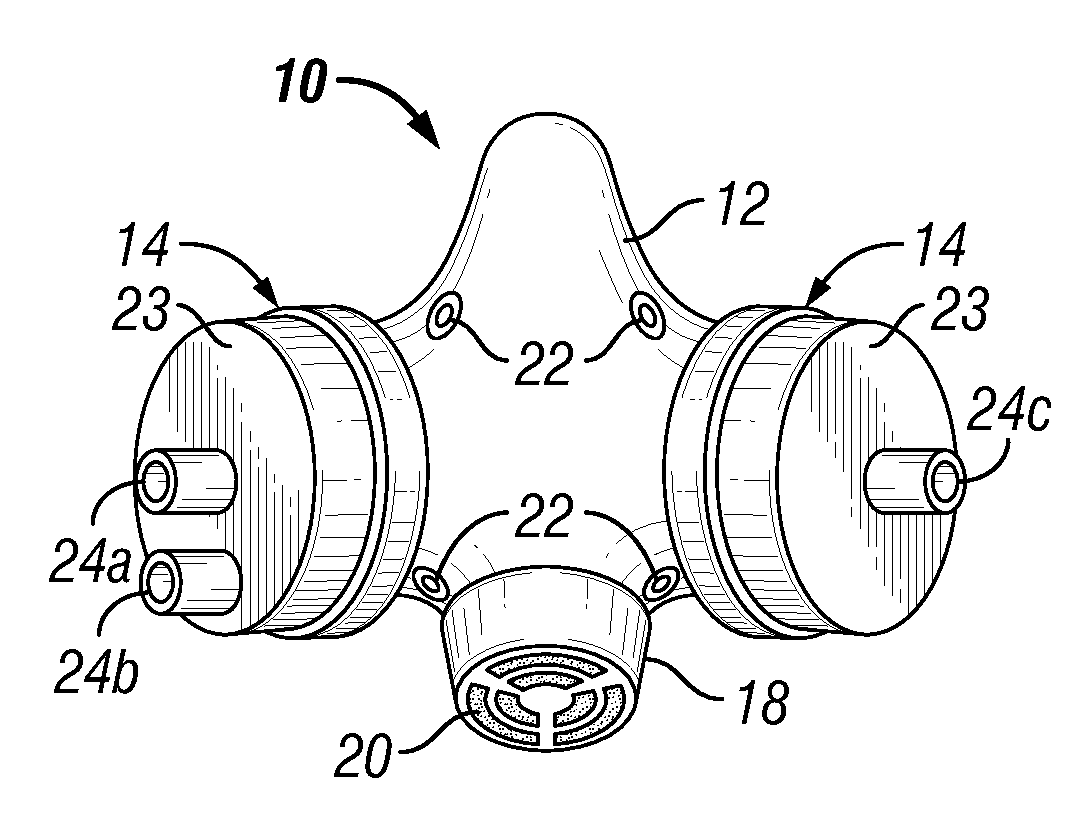

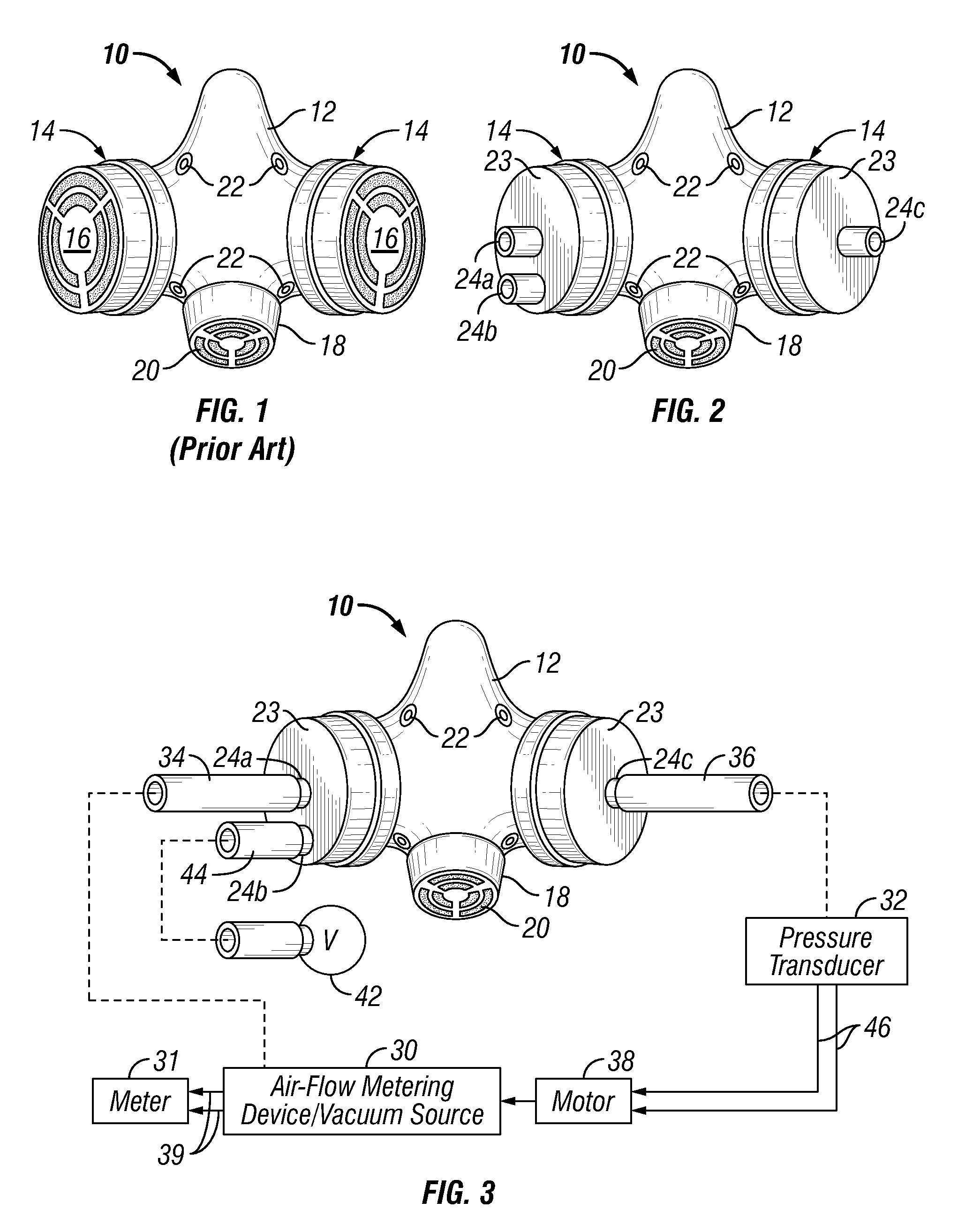

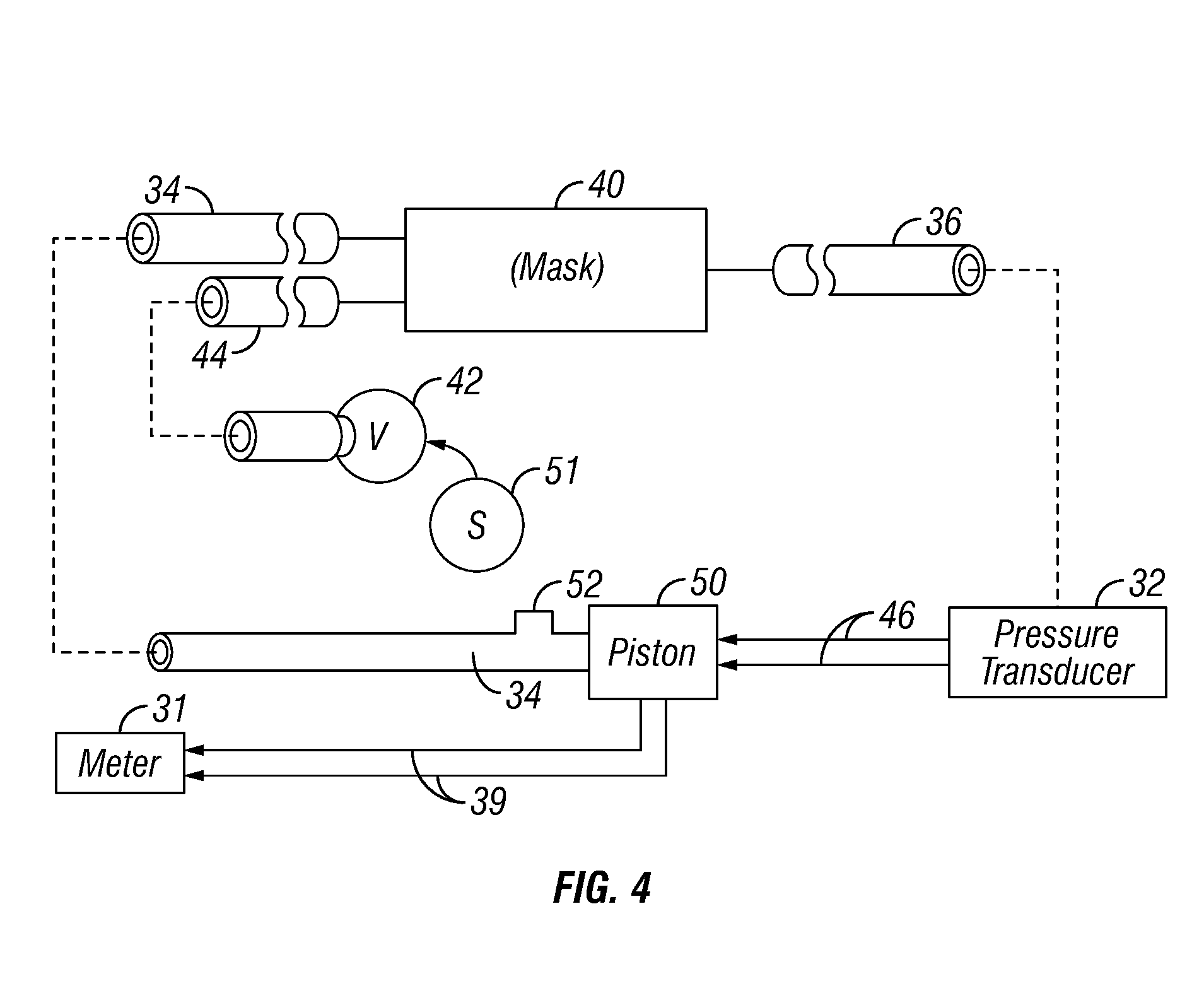

Respirator fit-testing apparatus and method

ActiveUS8011368B2Improve accuracyBetter assessmentRespiratorsDetection of fluid at leakage pointElectricityElectrical connection

Improved respirator fit-test methods and apparatus featuring an automated, respirator wearer-controlled, air-leak measurement system. For fit testing of a respirator positioned on a test subject's face and connected to a controlled negative pressure testing apparatus, the test subject simply holds his breath and then activates a switch in electrical connection with said apparatus, which results in the automatic closure of the breathing port on the respirator and the initiation of a complete fit-testing protocol. The fit-testing apparatus includes a single, self-contained, automated unit that includes a vacuum source (30), an air-flow measuring device, and an air-pressure transducer (32) for connection to a respirator (10) being tested. By measuring the rate of air exhausted from the respirator in order to maintain a constant challenge pressure, an air leakage rate is determined.

Owner:CRUTCHFIELD CELEVATORON D

Hearing test apparatus and method having automatic starting functionality

A hearing test device and method are disclosed which involve the placement of a testing probe in the ear canal of a test subject. The device analyzes responses to stimuli applied to the ear canal to determine whether the testing probe has been properly placed in the ear canal. The device may determine, for example, whether the probe is stable, whether it is sealed in the ear canal, whether the resulting volume of the ear canal is acceptable, and / or whether the stimuli delivery system is blocked in any way. If the device determines that the testing probe has been properly placed in the ear canal, the device automatically starts a hearing test without requiring any operator input.

Owner:INTERACOUSTICS

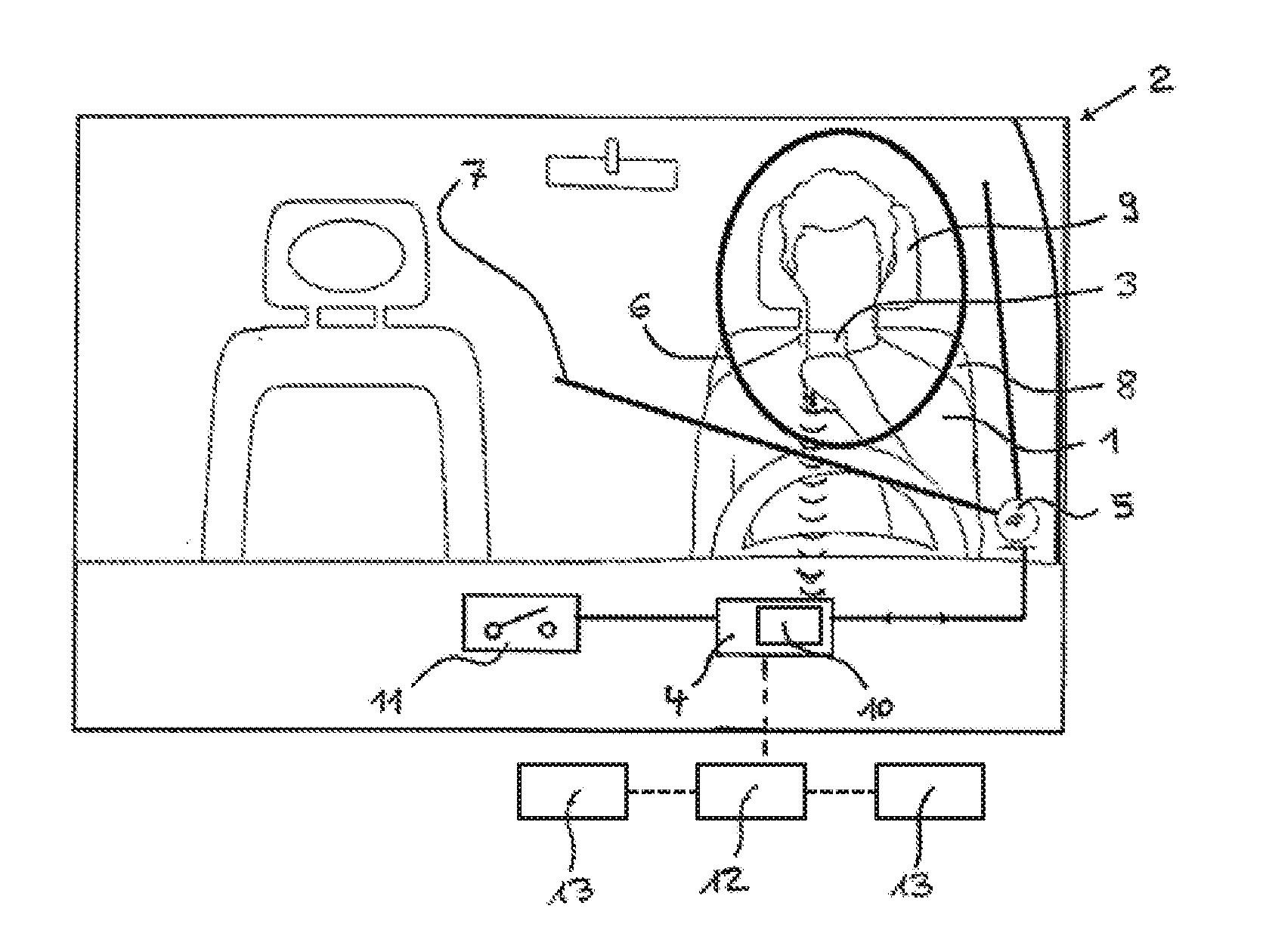

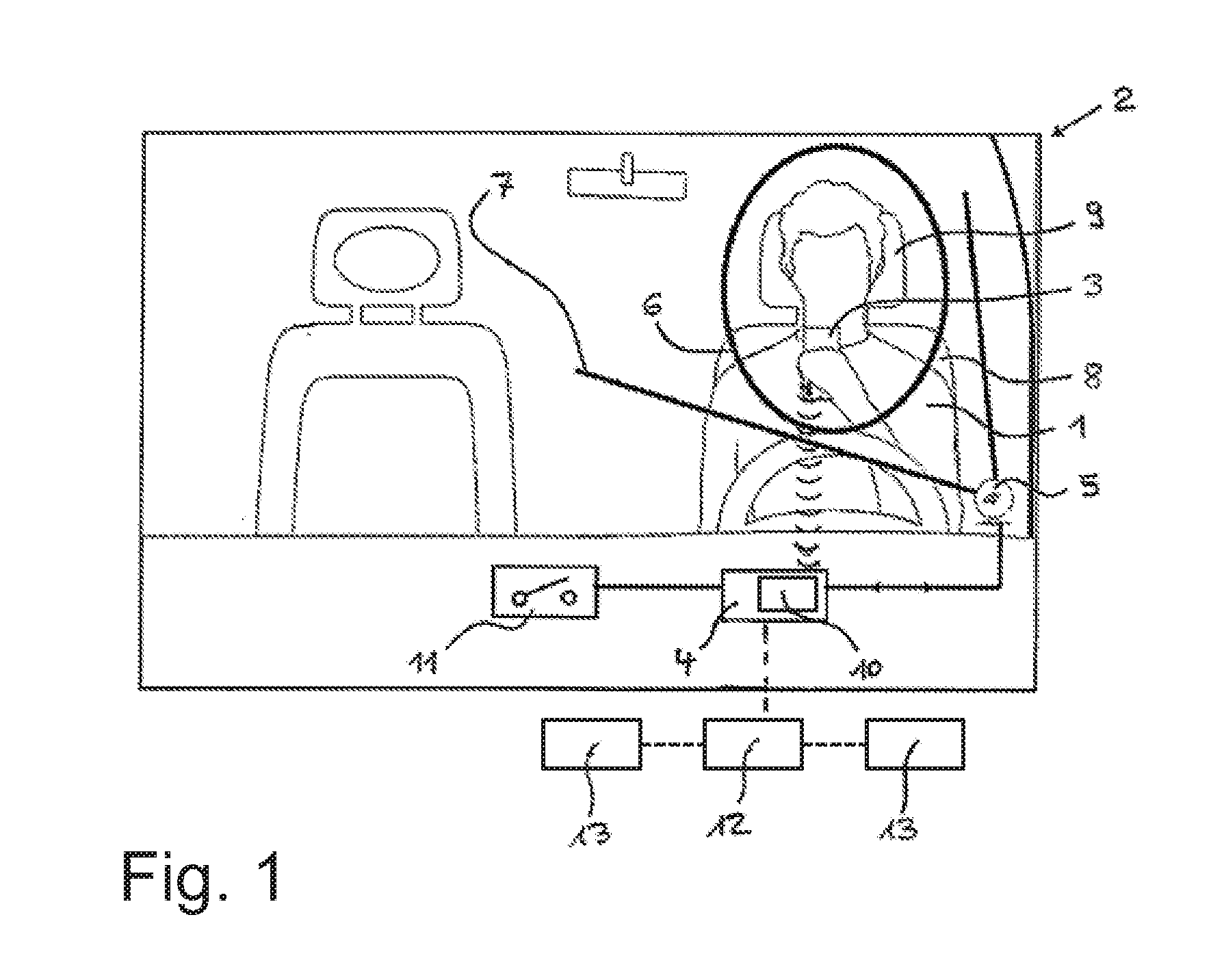

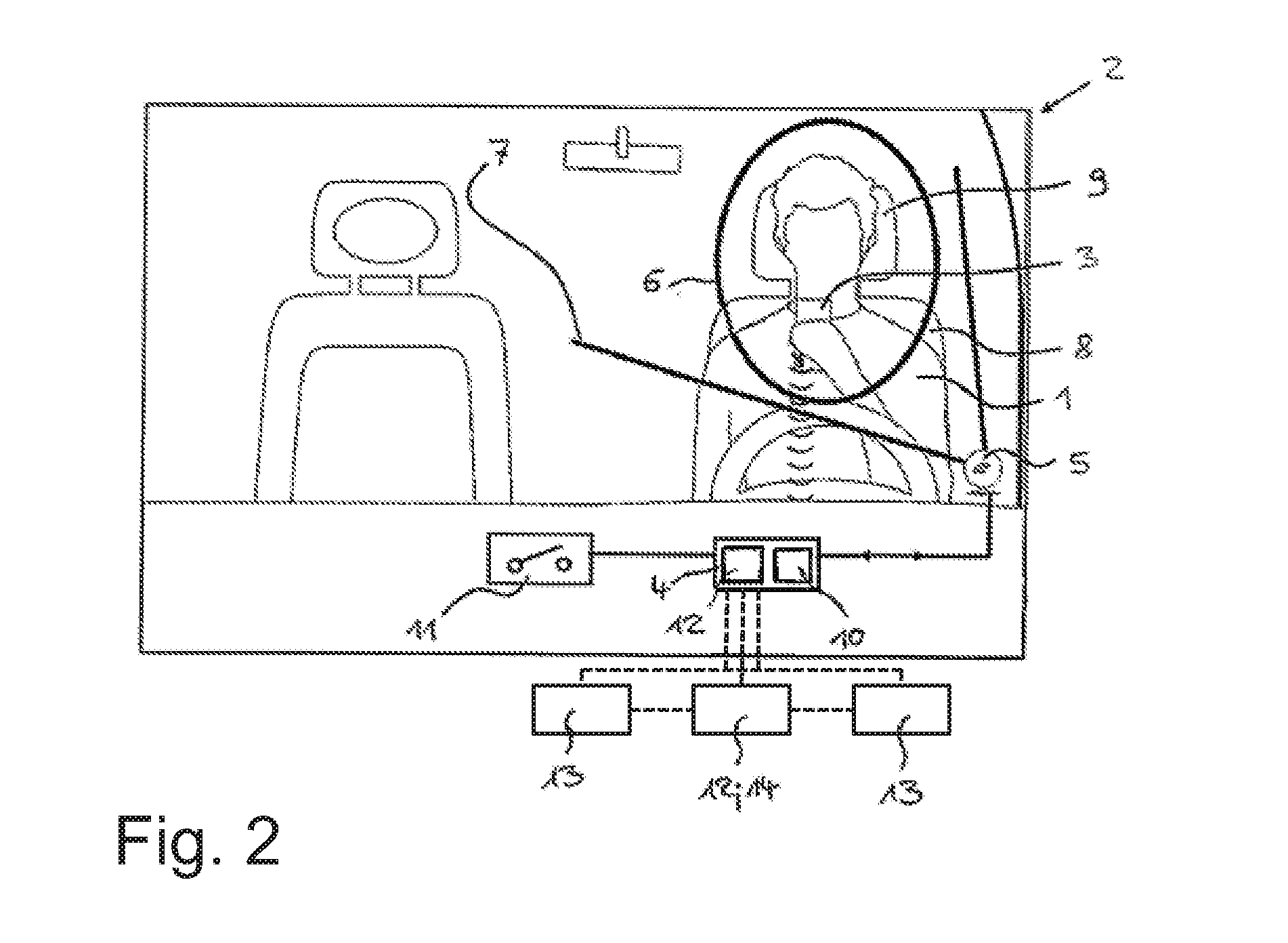

Device for measuring the state of intoxication of a test subject

ActiveUS20160229413A1Improve usabilityReduce the amount requiredCharacter and pattern recognitionTelevision systemsMeasurement deviceAlcohol

A device has a measuring device, in particular an alcohol-measuring device (3), for measuring the state of intoxication of a test subject and for generating a corresponding measured value. A camera (5) is provided for recording an image with the face of the test subject. A control unit (4) is configured to store the measured value together with the image in a memory unit (10). An analyzer (12) is configured such that the analyzer can identify a face and / or a defined, fixed pattern in the image. A follow-up action is triggered by the analyzer (12) when a face and / or pattern could not be identified.

Owner:DRAGER SAFETY

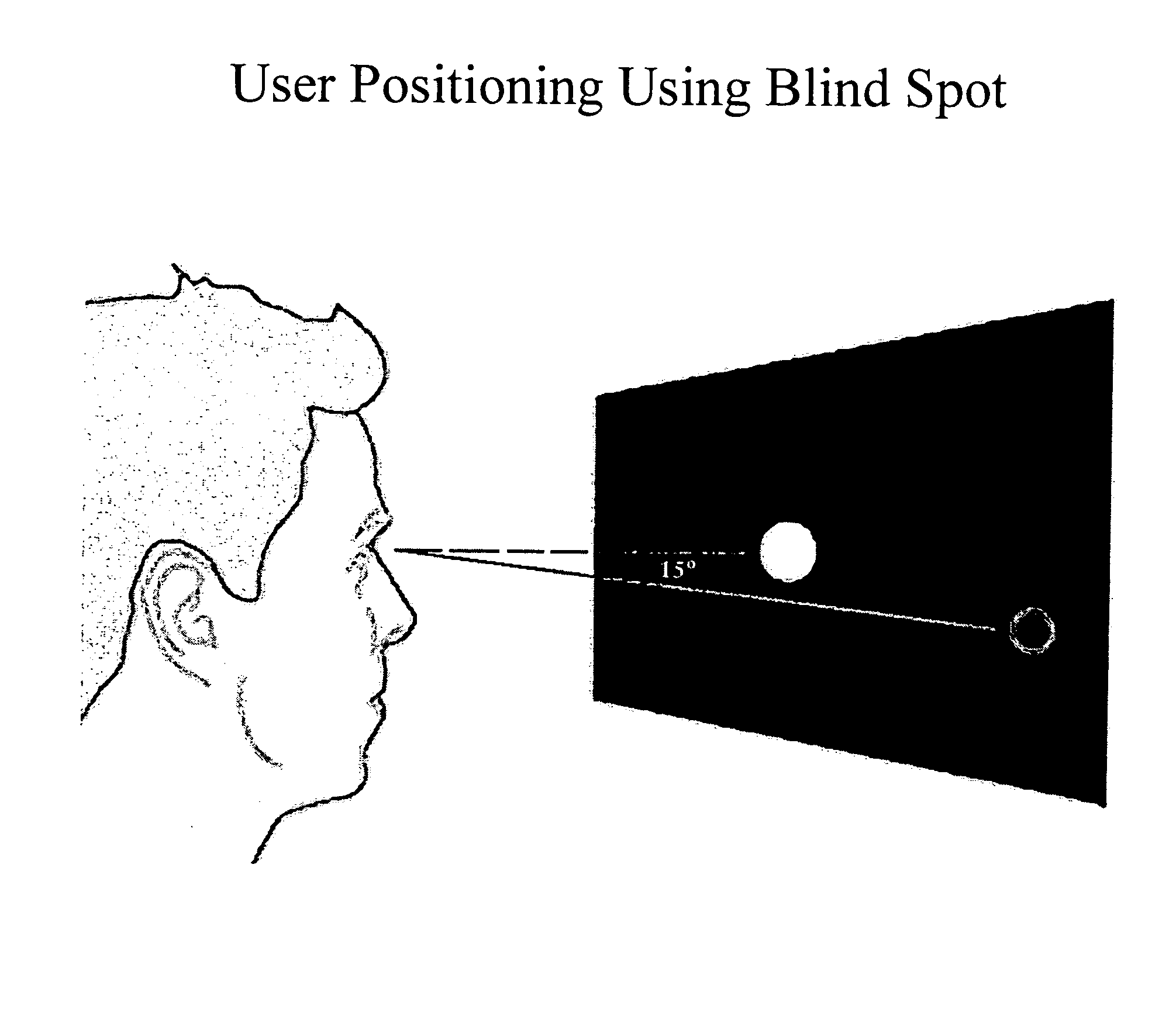

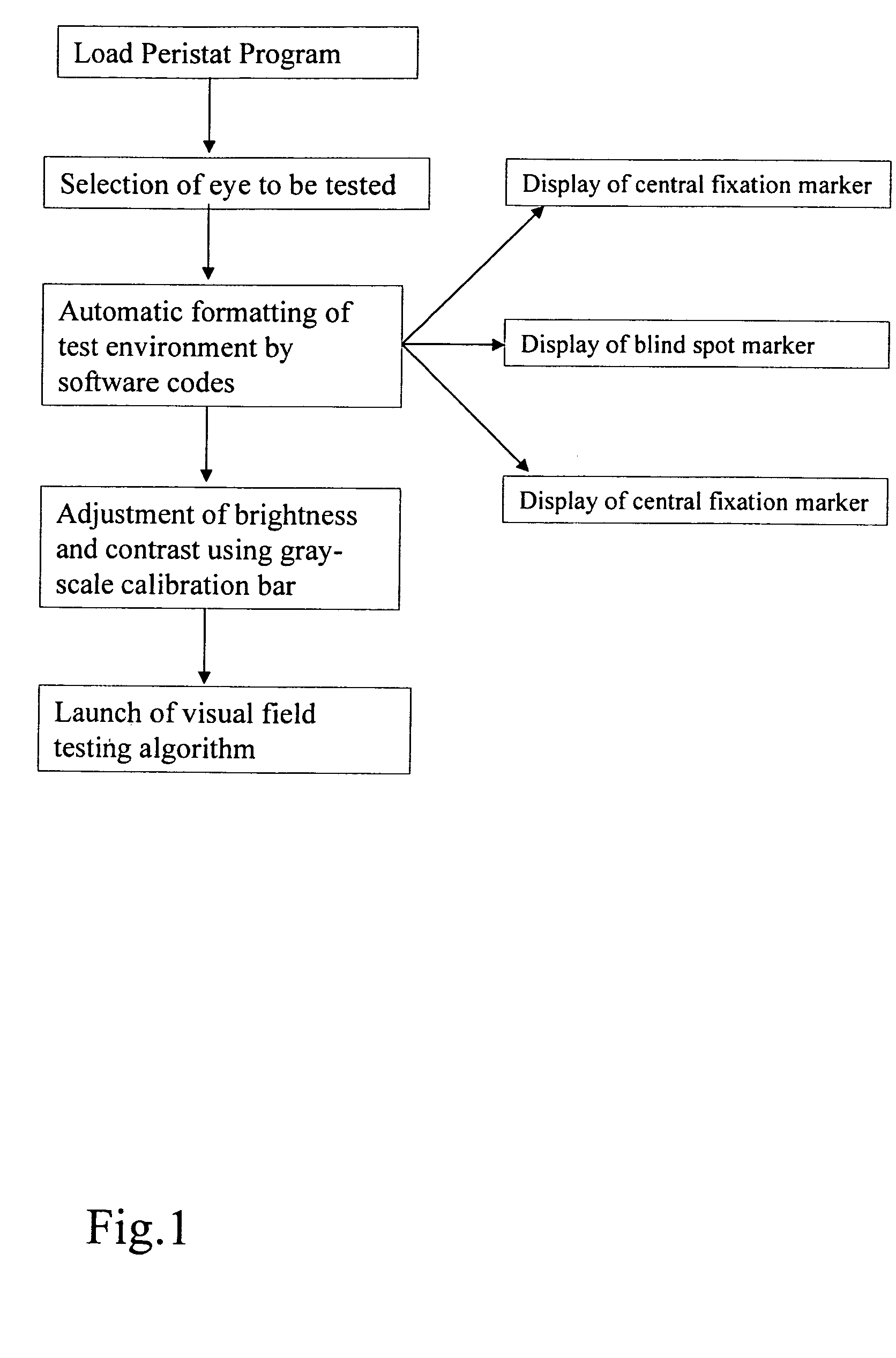

Computerized virtual reflex perimetry

InactiveUS20050128434A1Simple and easily achievable specification parameterImprove standardizationEye diagnosticsReflexRight visual field

An automated unaided virtual perimetry system and underlying method for relative-threshold contrast sensitivity interrogation of the visual field via algorithmic presentation of visual stimuli on a screen and subsequent analysis of test response data for the detection of pathophysiologic scotomas as well response time registration and analysis for visual motor reflex testing. Launch of system via access from a remote server or direct installation of systems technology allows seamless capability at the local computer system to instruct, administer, and analyze output of stimuli and input of responses of test subjects or subjects independent of external input or control. Specific algorithmic test environment is designed to achieve comparable clinical efficacy and diagnostic utility to office-based perimetry system.

Owner:IANCHULEV TSONTCHO +2

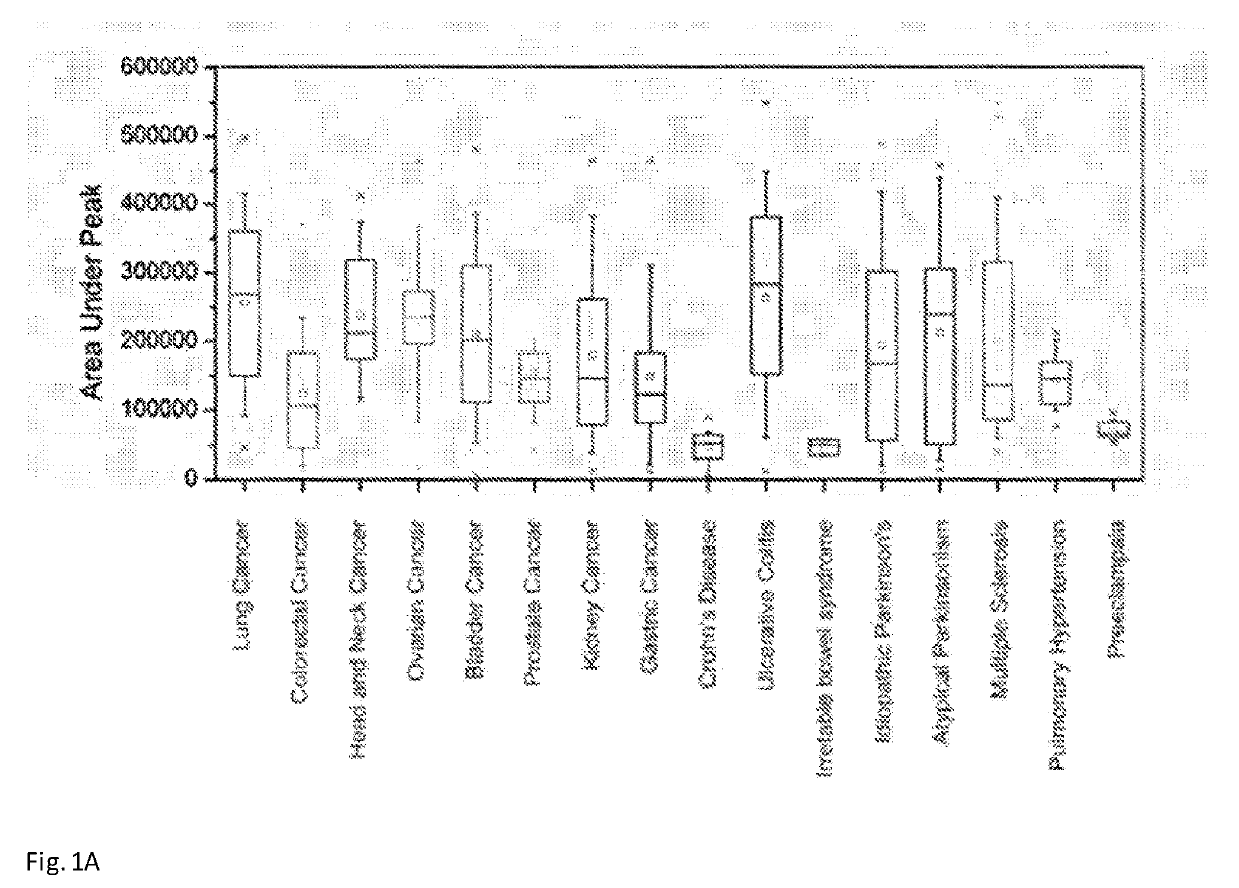

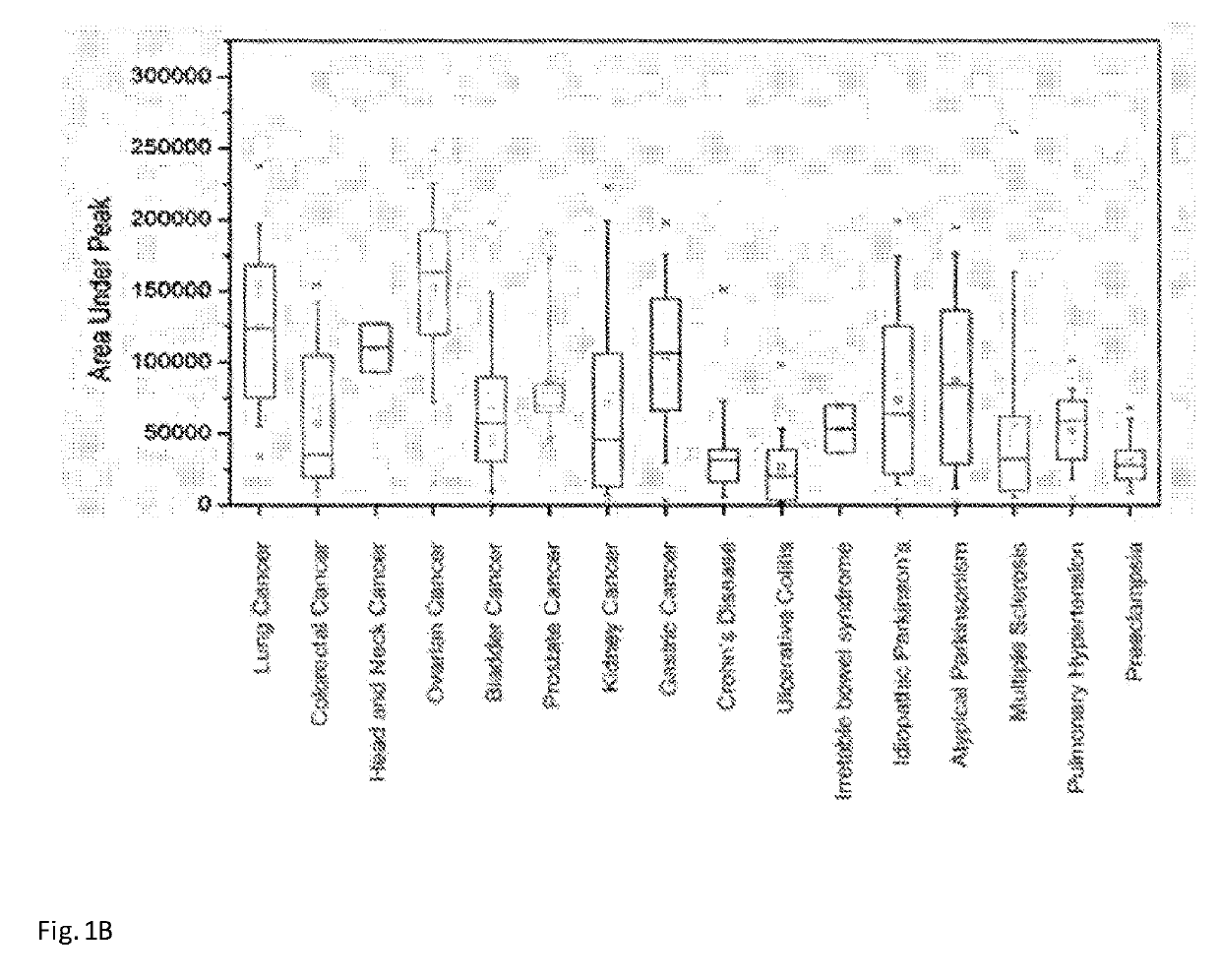

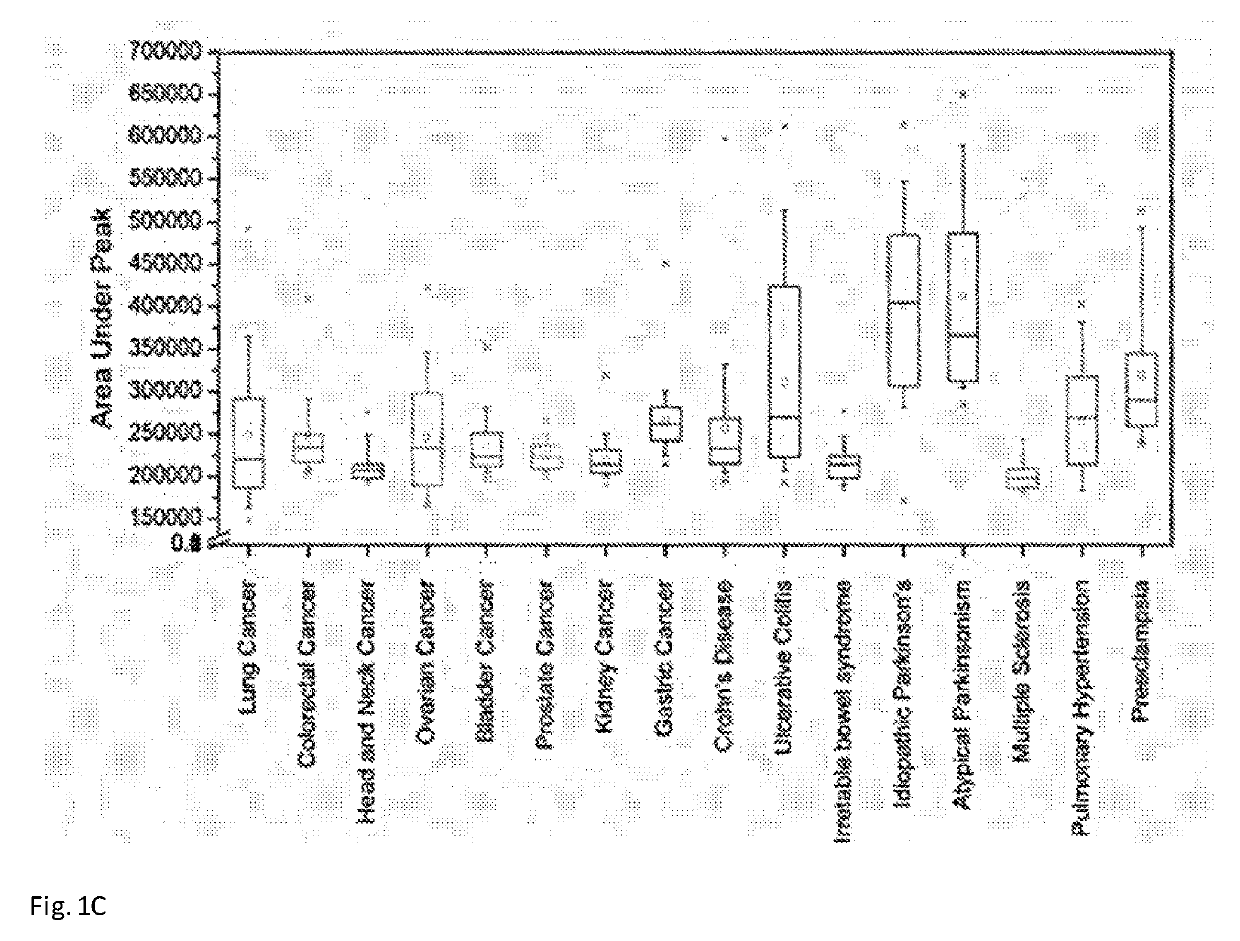

System and method for differential diagnosis of diseases

ActiveUS20190271685A1Adequate efficiencySolve the lack of reliabilityMedical automated diagnosisDisease diagnosisEthyl acetateBiomarker (petroleum)

The present invention provides a system and method for diagnosing, screening or monitoring a disease by analyzing the breath of a test subject using a selected definitive sensor set in conjunction with a pattern recognition analyzer, wherein the pattern recognition analyzer receives output signals of the sensor set, compares them to disease-specific patterns derived from a database of response patterns of the sensor set to exhaled breath of subjects with known diseases, wherein each of the disease-specific patterns is characteristic of a particular disease, and selects a closest match between the output signals of the sensor set and the disease-specific pattern. The present invention further provides a method of diagnosing, screening or monitoring a disease based on the determination of levels of volatile organic compounds (VOCs) from a universal biomarker set, including 2-ethylhexanol, 3-methylhexane, 5-ethyl-3-methyl-octane, acetone, ethanol, ethyl acetate, ethylbenzene, isononane, isoprene, nonanal, styrene, toluene and undecane.

Owner:TECHNION RES & DEV FOUND LTD