High-speed high-voltage level conversion circuit applied to GaN gate drive

A conversion circuit and gate drive technology, applied in the direction of logic circuit interface device, logic circuit connection/interface layout, etc., can solve the problems of ground current consumption, consumption of ground current, high current power consumption, etc. Current consumption, size reduction, cost saving effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

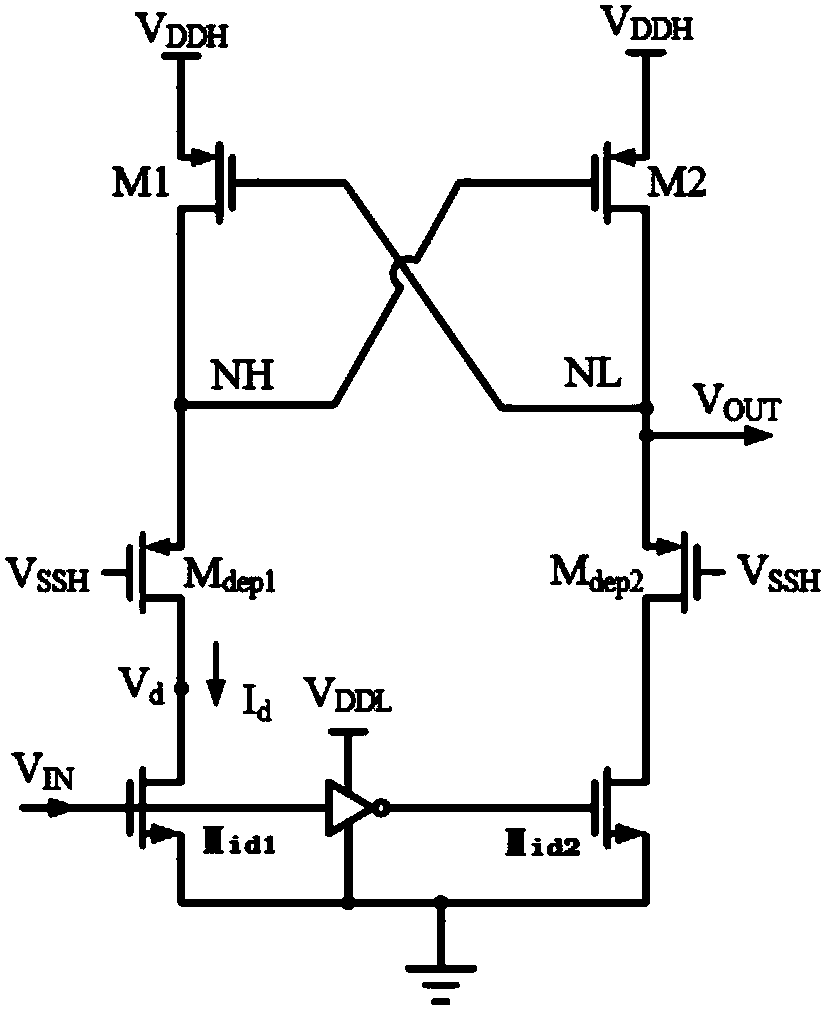

[0051] Image 6 A high-speed high-voltage level conversion circuit applied to GaN driving according to the first embodiment of the present invention is shown.

[0052] Such as Image 6 As shown, the present invention provides a high-speed high-voltage level conversion circuit applied to GaN gate drive, including: an input circuit 601, a first PMOS transistor 602 (that is, Image 6 MP1 in), the level conversion circuit 603 and the shaping circuit 604; the first end of the input circuit 601 is connected to the first end of the level conversion circuit 603 at the first node NH, and the second end is connected to the first PMOS at the second node A The drain of the transistor 602, the gate of the first PMOS transistor 602 is connected to the first power supply line, the source of the first PMOS transistor 602 is connected to the second terminal of the level conversion circuit 603 at the third node NL, and the level conversion circuit 603 Connected to the second power line, the s...

Embodiment 2

[0082] Figure 8 A high-speed high-voltage level conversion circuit applied to GaN driving according to the second embodiment of the present invention is shown.

[0083] Such as Figure 8 As shown, the present invention provides a high-speed high-voltage level conversion circuit 803 applied to GaN gate drive, including: an input circuit 801, a first PMOS transistor 802 (that is, Figure 8 MP1 in), the level conversion circuit 803 and the shaping circuit 804; the first end of the input circuit 801 is connected to the first end of the level conversion circuit 803 at the first node NH, and the second end is connected to the first PMOS at the first node A The drain of the transistor 802, the gate of the first PMOS transistor 802 is connected to the first power supply line, the source of the first PMOS transistor 802 is connected to the second terminal of the level conversion circuit 803 at the third node NL, and the level conversion circuit 803 Connected to the second power line...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More