Delay stage circuitry for a ring oscillator

a delay stage and oscillator technology, applied in the field of clock synchronization circuitry, can solve the problems of difficult to minimize, limited number of phase signals that can be generated, and offset and deadband problems

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

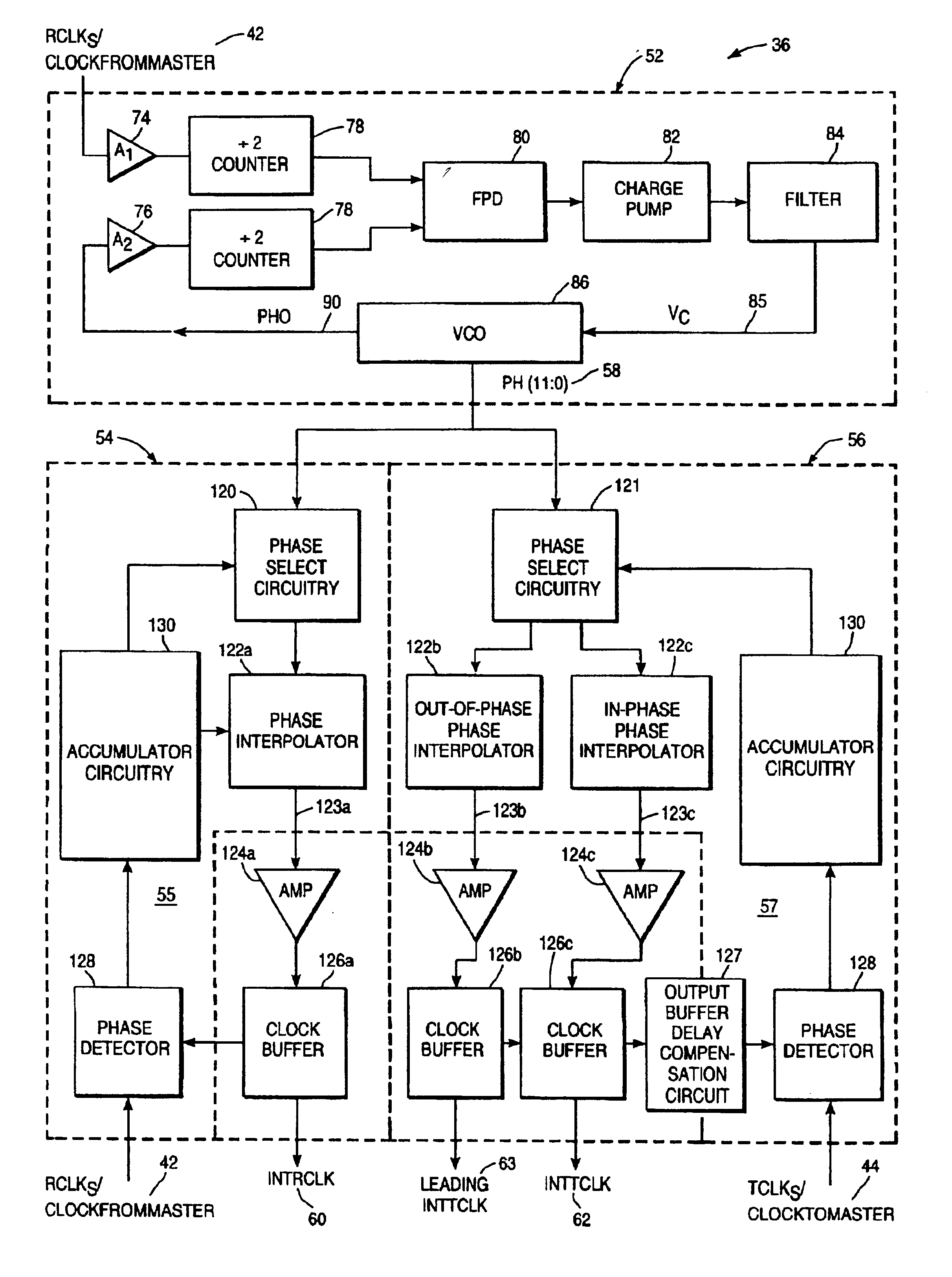

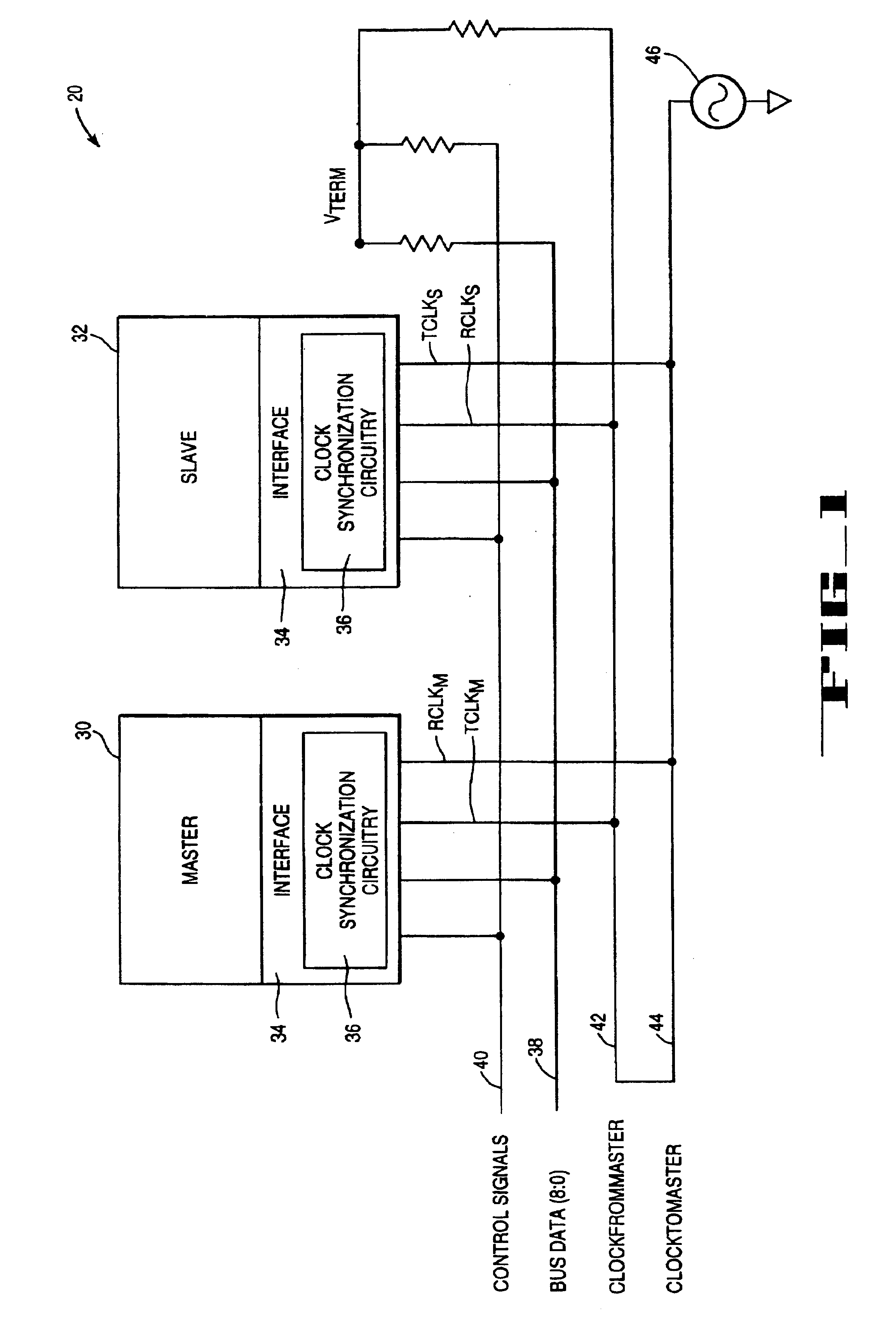

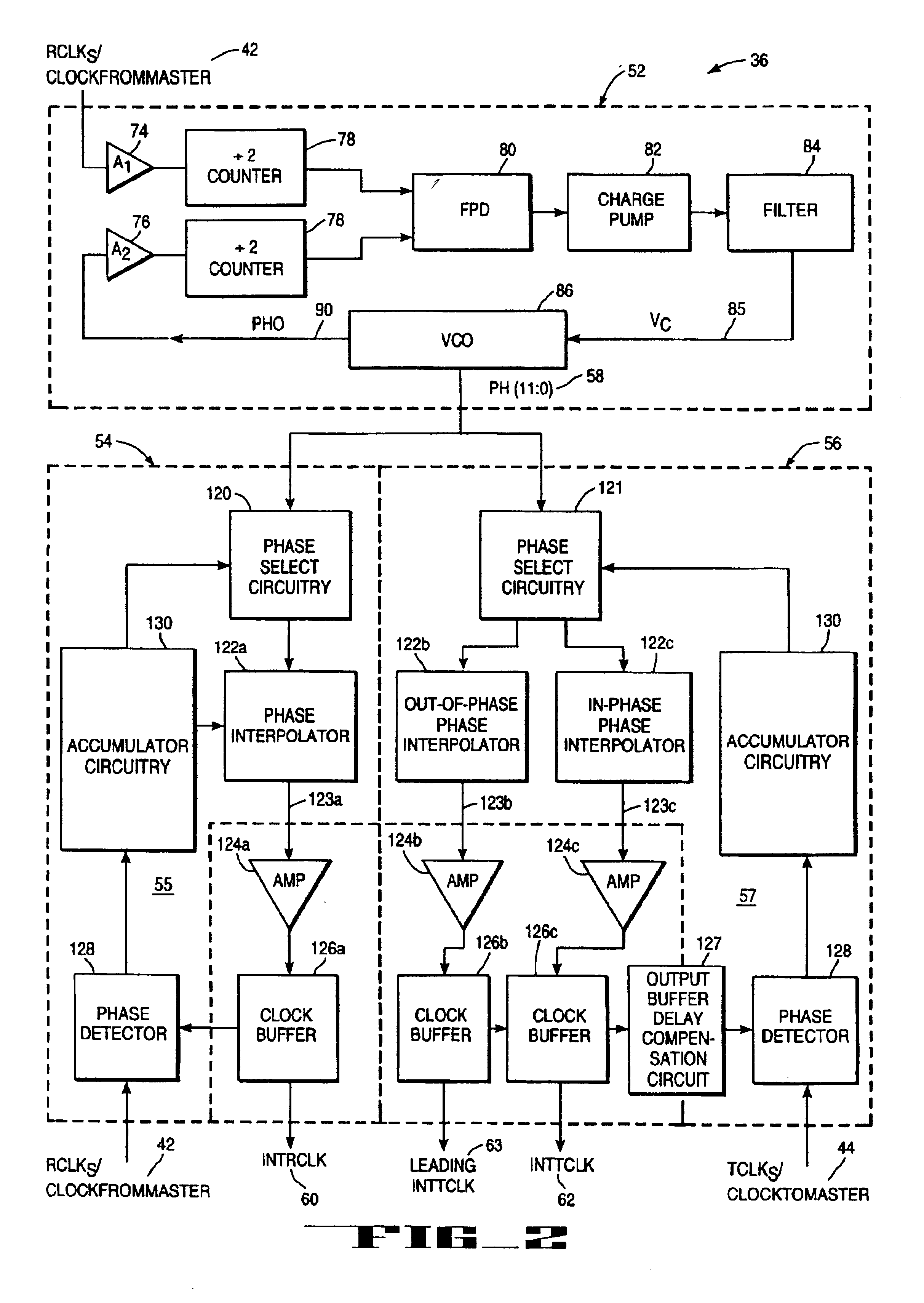

FIG. 1 is a block diagram of a high speed digital computer bus system 20. Devices 30 and 32 use clock synchronization circuitry 36 to synchronize the transfer of data between data bus 38. Clock synchronization circuitry 36 is a cascaded phase locked loop (PLL) 36. The main loop of PLL 36 utilizes a ring voltage controlled oscillator (VCO), which includes an even number of cascaded delay stages of the present invention. Two subloops coupled to the main loop perform fine phase tuning according to the method and circuitry of the present invention to generate two internal clock signals.

As will be described in more detail below, each delay stage of the present invention generates two complementary output signals using a differential amplifier. Coupled between the two complementary output signals, two clamping devices limit the peak-to-peak voltage swing of the complementary output signals. When the delay stages are cascaded together, they provide twelve different phase signals that are u...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More