SPI verification platform based on UVM

A verification platform and verification environment technology, applied in the field of IP verification, can solve the problems of low verification efficiency, poor portability, difficult convergence of coverage, etc., and achieve the effect of accelerating coverage convergence, accelerating convergence, and easy reuse

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

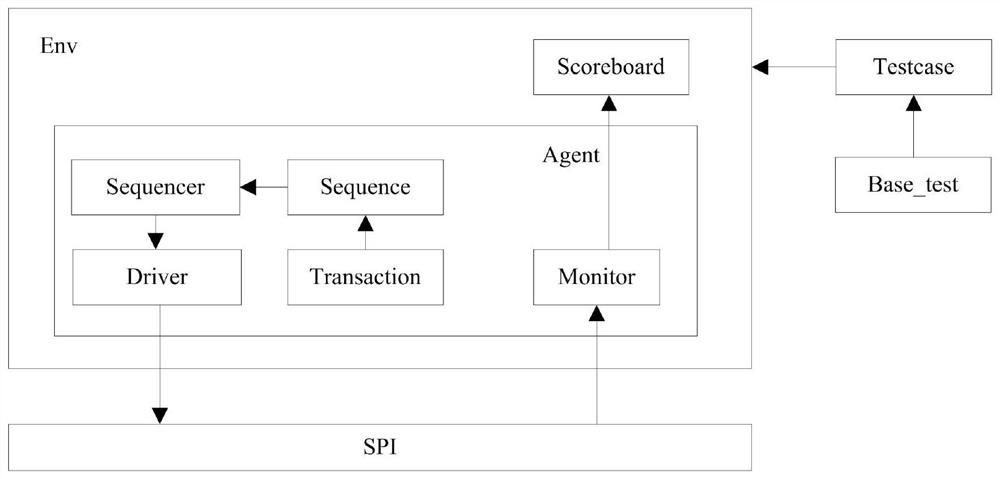

[0029] In the present invention, a UVM-based SPI verification platform is proposed, and the UVM is used to build a module-level verification environment. Systemverilog is an excellent verification language, but it is obviously not enough to only use Systemverilog for verification, and the UVM verification methodology provides a basic class library and a basic verification structure, so as to quickly and efficiently build a verification platform. The verification platform proposed by the present invention is built based on UVM verification methodology and Systemverilog language, and constrained random excitation is applied to the SPI interface module, which can be reused in different environments and improves design verification efficiency.

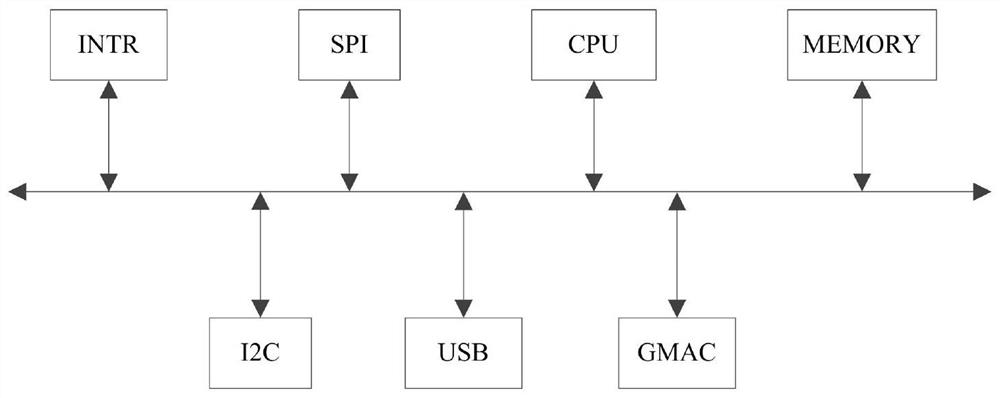

[0030] The present invention uses the UVM verification methodology to build a function verification environment for the SPI module. SPI is the abbreviation of Serial Peripheral Interface (Serial Peripheral Interface), which has the charact...

test Embodiment t

[0031] Test case testcase: test stimulus for the entire verification platform.

[0032] Basic test base_test: start the test, all testcases in the platform inherit from base_test.

[0033] Authentication environment env: used for the instantiation and management of various components.

[0034] Driver driver: used to apply excitation and data conversion to the dut port of the design under test.

[0035] Monitor monitor: used to collect the data of the dut port and perform data conversion.

[0036] Transaction transaction: used to define the basic item data package.

[0037] Sequence generator sequence: used to generate transaction transaction.

[0038] Sequence management sequencer: used to manage the sequence and generate a valid sequence sequence.

[0039]Agent agent: used for encapsulation and instantiation of driver, monitor and sequencer.

[0040] Scoreboard scoreboard: used to compare the output data of the dut port with the expected value after the stimulus is appli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More