Method and device for automatically generating assertion

An automatic generation and template technology, applied in the field of verification, can solve problems such as project delay and long development cycle, and achieve the effect of reducing the difficulty of use and ensuring the progress of the project

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

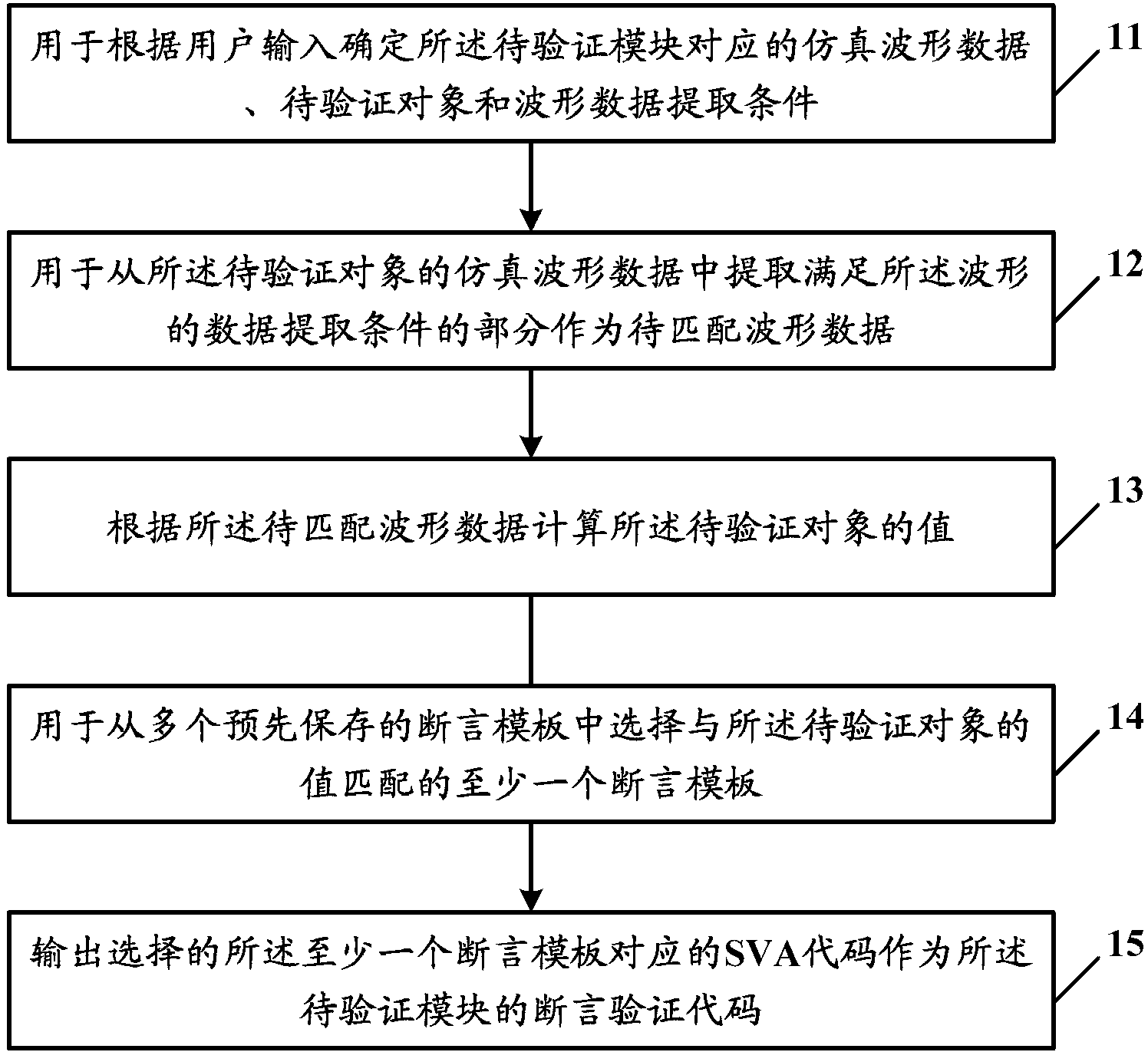

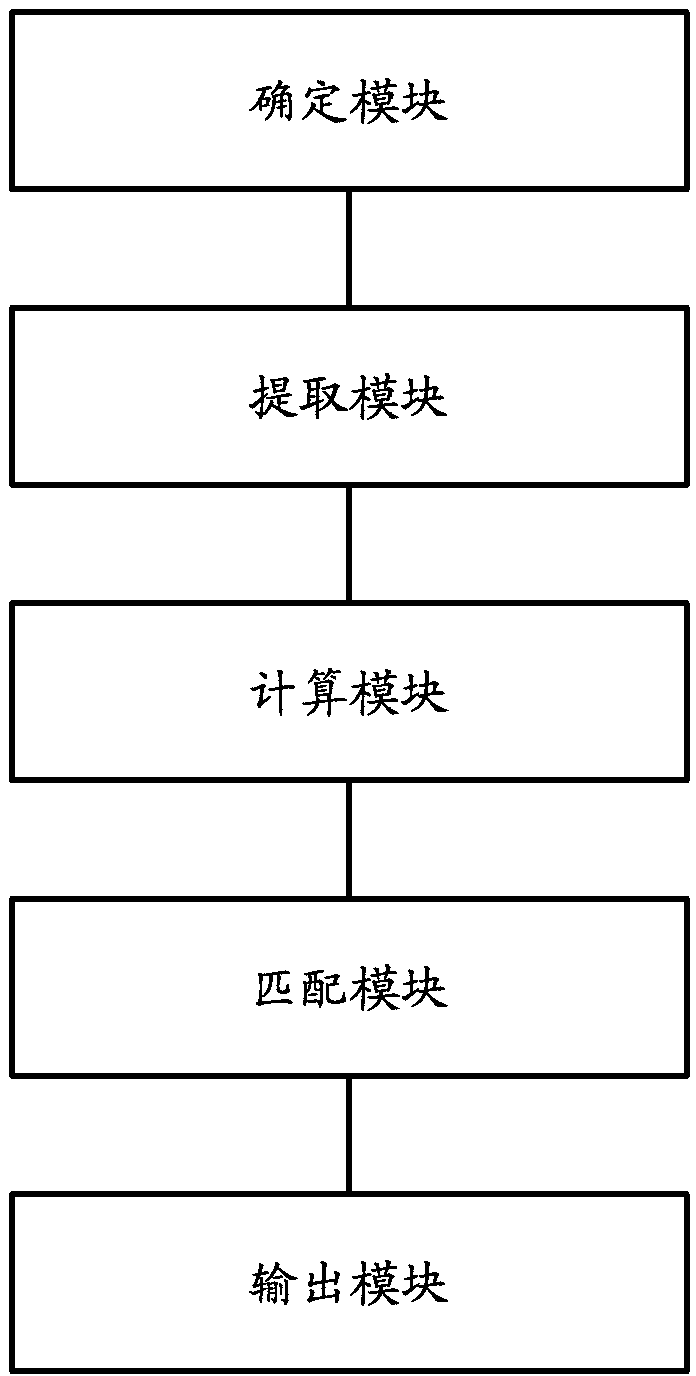

[0049] In the method and device for automatically generating an assertion in the embodiment of the present invention, a plurality of assertion templates and corresponding assertion verification codes are set in advance, and then the waveform information of the object to be verified is extracted from the simulation waveform data, and the waveform information that matches the waveform information The assertion verification code corresponding to the assertion template is used as the assertion verification code of the module to be verified, which reduces the difficulty of using the Assertion (assertion) code in the project development process and ensures the progress of the project.

[0050] A method for automatically generating assertions in an embodiment of the present invention is used to generate assertion verification codes for a module to be verified, such as figure 1 Shown include:

[0051] The determining step 11 is used to determine the simulation waveform data correspond...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More