Efficient digital circuit algorithm verification device

A digital circuit and algorithm verification technology, which is applied in the fields of electrical digital data processing, CAD circuit design, calculation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

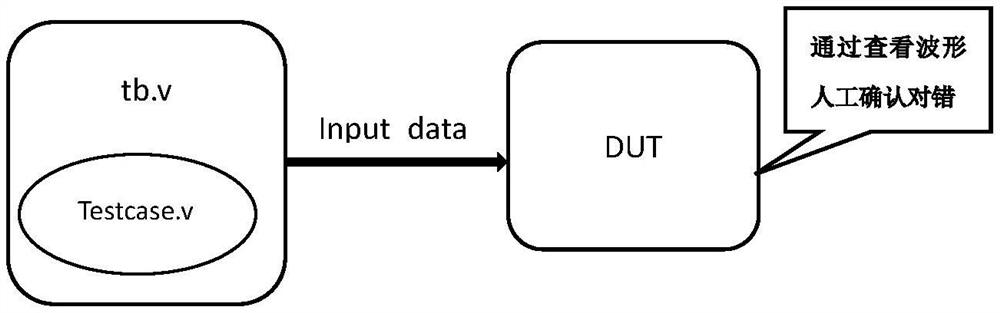

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

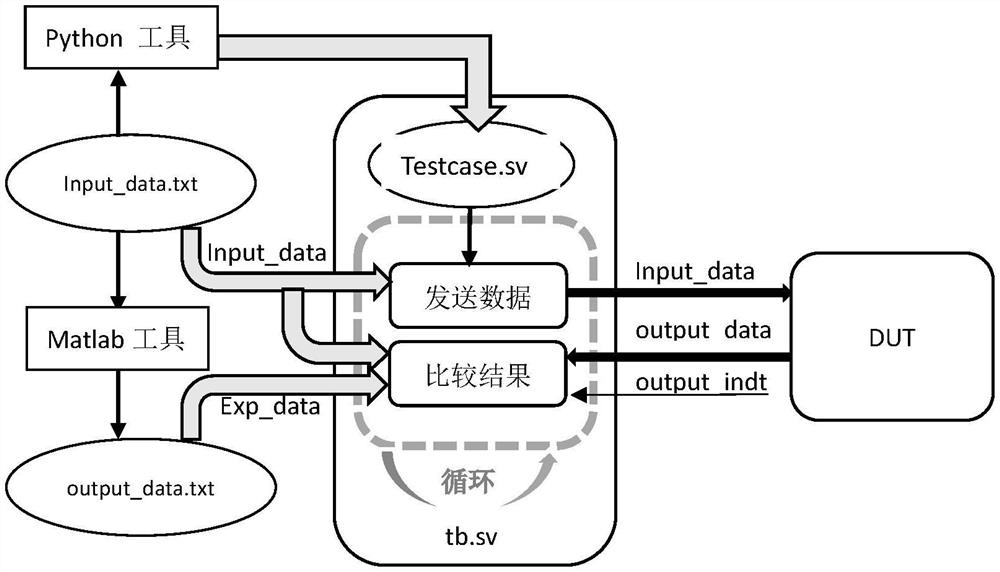

[0021] In order to make the purpose, technical solution and advantages of the present invention more clear, the present invention will be further described in detail below in conjunction with the accompanying drawings and examples. The specific examples described here are only used to explain the present invention, not to limit the present invention.

[0022] A kind of efficient digital circuit algorithm verification device circuit provided by the present invention mainly comprises:

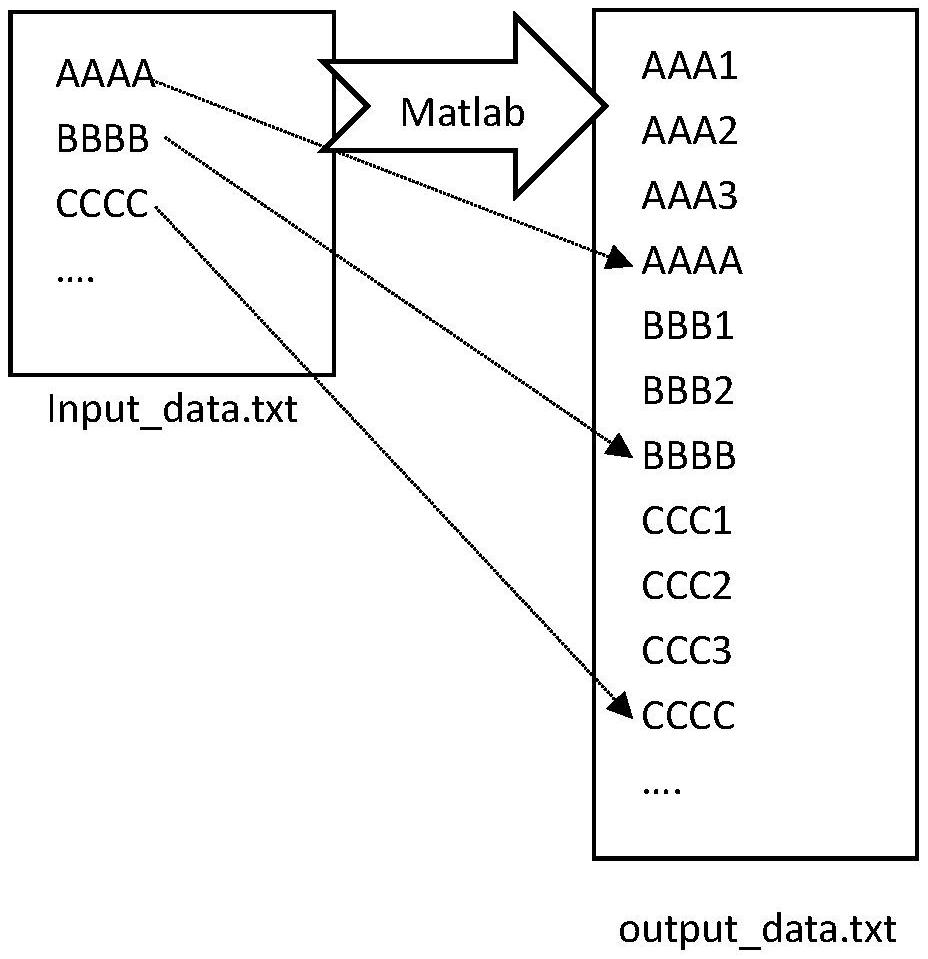

[0023] As shown in Figure 3 and Figure 6, the verified data source Input_data.txt, in order to simplify scripting, does not add "0x" in front of the value, and the 4-digit data is a hexadecimal number. After reading the Input_data.txt with the Matlab tool, because a large number of calculations cannot be based on string operations, it is necessary to convert this string into a hexadecimal number. The specific algorithm is written and debugged according to the design of the chip. In Chart 3, the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More