BFM (Bus Function Model)-based method for SystemVerilog to build protocol verification platform

A verification platform and protocol technology, applied in the computer field, can solve problems such as difficult protocol conversion verification, long time-consuming, difficult debugging, etc., and achieve the effect of simplifying the protocol processing process and increasing throughput

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

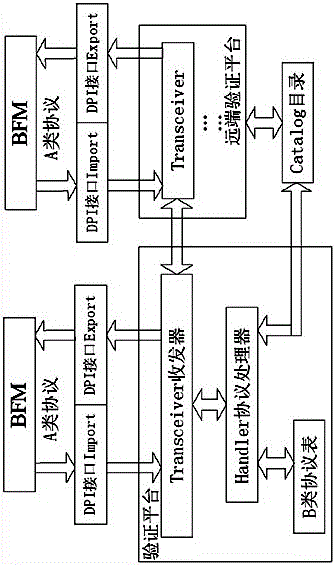

[0025] Such as figure 1 As shown, a method of building a protocol verification platform based on SystemVerilog of BFM, the method utilizes the support characteristics of SystemVerilog for verification, and perfectly supports the realization of protocol conversion and consistency. The implementation process is as follows:

[0026] (1) Build a Transceiver, responsible for sending and receiving, dismantling / assembling Class A protocol messages;

[0027] (2) Build the Catalog directory structure and be responsible for the recording of consistent information;

[0028] (3) Realize the protocol table model, responsible for realizing protocol conversion;

[0029] (4) Build Handler, responsible for protocol processing.

Embodiment 2

[0031] On the basis of Embodiment 1, the method described in this embodiment simulates multi-Clumps communication through BFM, and sends a type A protocol message.

Embodiment 3

[0033] On the basis of Embodiment 1 or 2, the Transceiver described in this embodiment receives and sends the Class A protocol message through the DPI interface, completes the splitting of the protocol message packet, sends it to the Handler for processing, and receives the Handler processing result to assemble into a The type A message packet is sent out.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More