Verification method and platform based on SystemVerilog language

A verification method and verification platform technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of difficult chip verification, unguaranteed verification quality, low efficiency, etc., and achieve easy reuse and maintenance. And the effect of modification and improvement of verification efficiency

Inactive Publication Date: 2016-09-28

SICHUAN DOUQI TECH

View PDF2 Cites 15 Cited by

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

However, due to the diversity and complexity of each module inside the flash memory chip, such as the coexistence of digital circuits and analog circuits, and the interweaving of digital circuits and analog circuits, it will cost a lot of money to verify the flash memory chip

Method used

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

View moreImage

Smart Image Click on the blue labels to locate them in the text.

Smart ImageViewing Examples

Examples

Experimental program

Comparison scheme

Effect test

Login to View More

Login to View More PUM

Login to View More

Login to View More Abstract

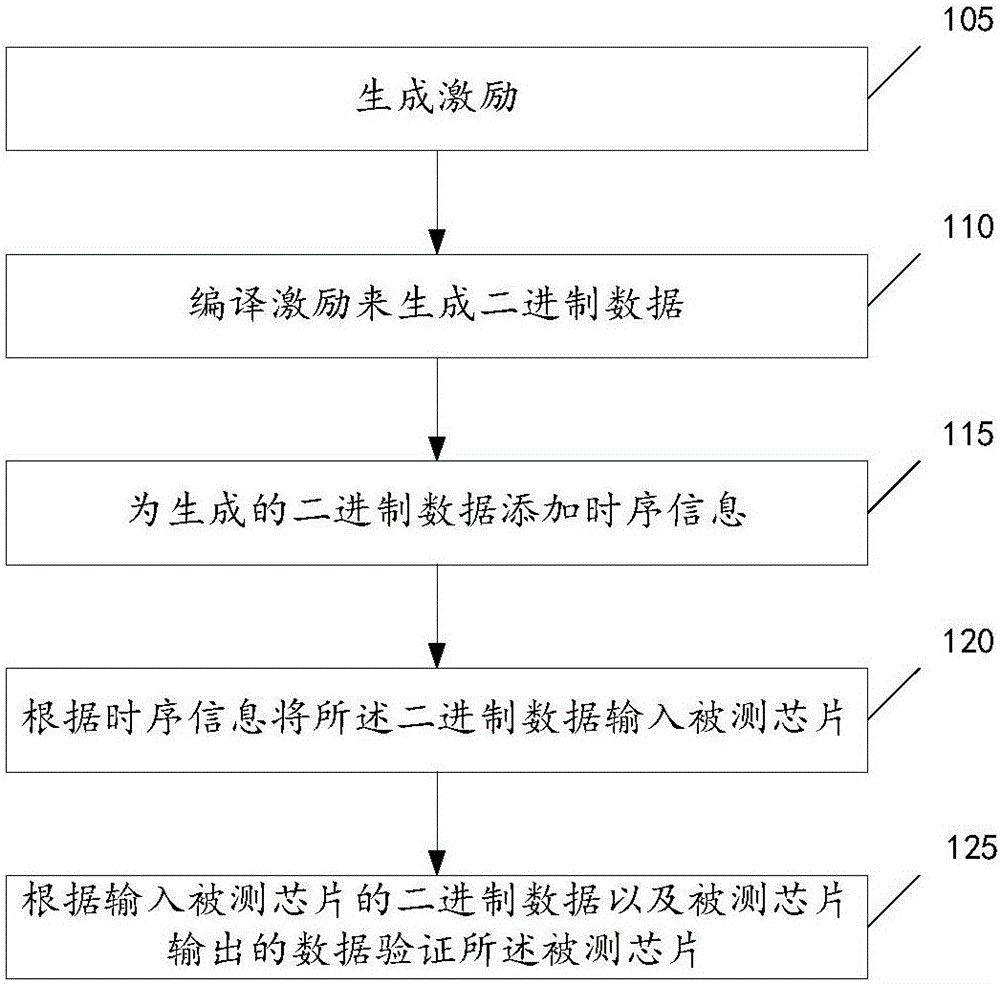

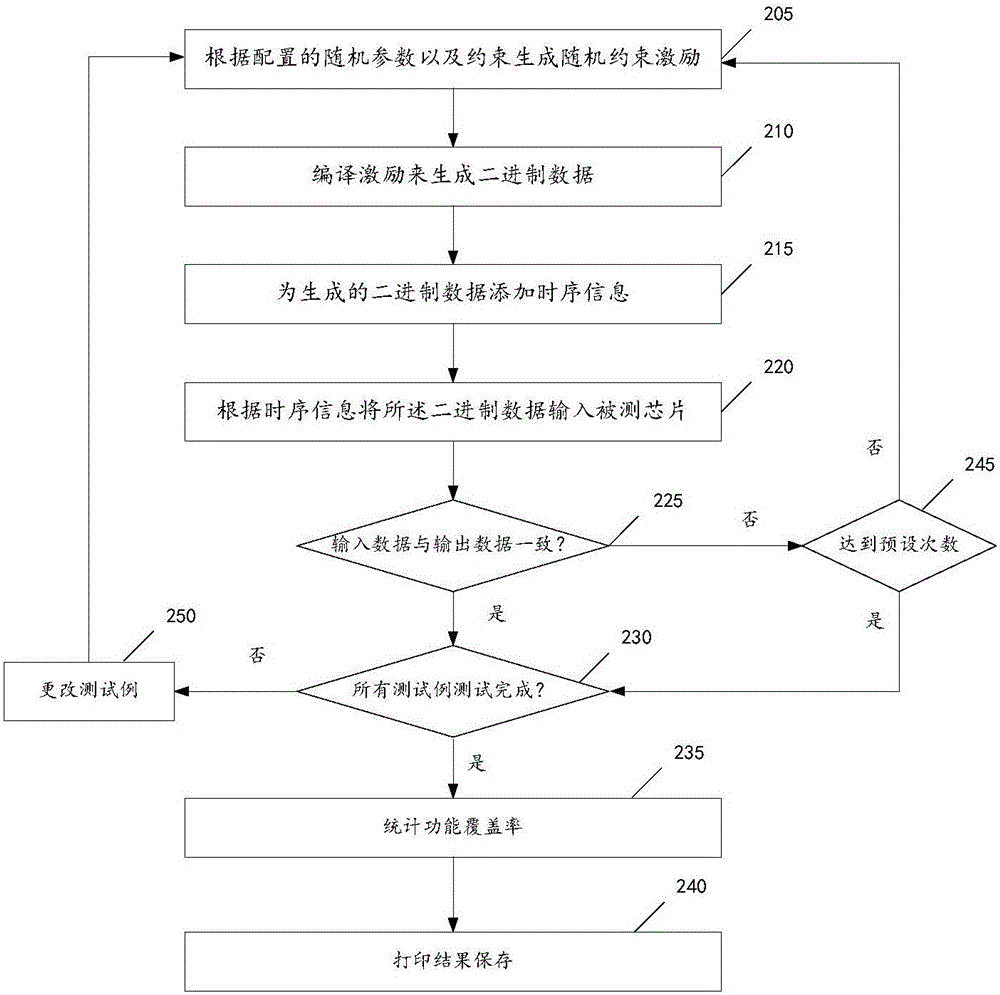

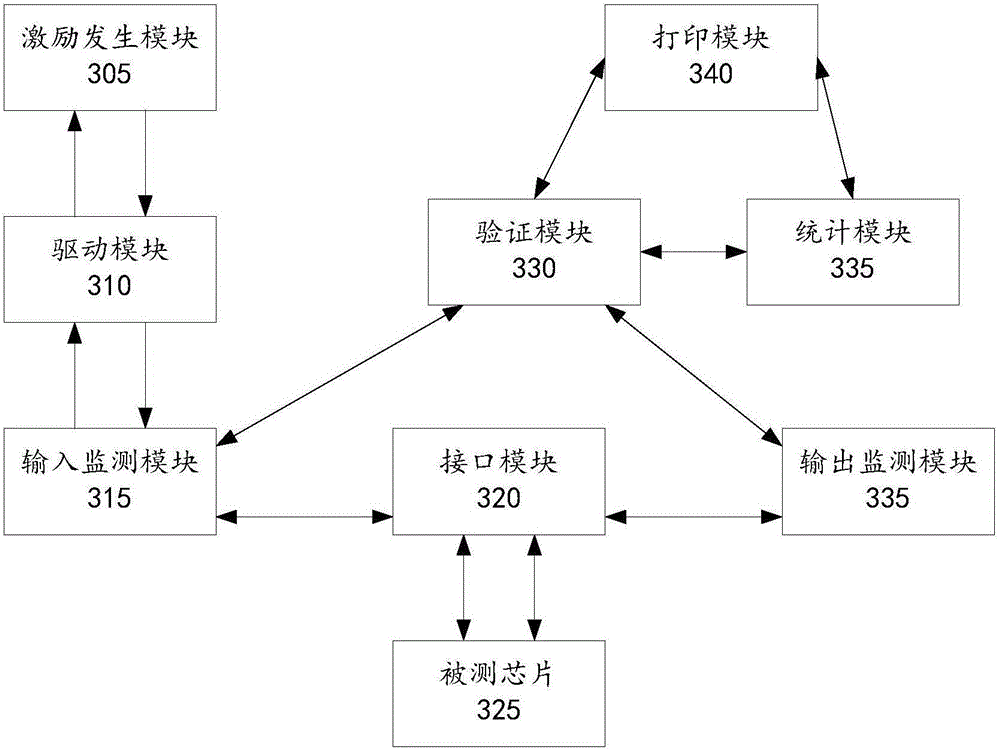

The invention discloses a verification method and platform based on a systemVerilog language. The method comprises the steps of generating excitation, compiling the excitation to generate binary data, adding timing sequence information for the generated binary data, inputting the binary data into a chip to be tested according to the timing sequence information, and verifying the chip to be tested according to the binary data input to the chip to be tested and data output by the chip to be tested, wherein the verification environment is achieved through the systemVerilog language. According to the verification method and platform based on the systemVerilog language, a simulation control platform and a self-verification control platform are separated, reutilization is easy; the verification method and platform based on the systemVerilog language have good compatibility, and therefore the verification platform compiled through SystemVerilog can be conveniently transplanted to various kinds of simulation environments; a hierarchical structure is adopted, modules are relatively independent, the complexity of the verification platform is lowered, and the platform can be conveniently maintained and modified in the verification process; the verification accuracy degree is improved, the verification efficiency is greatly improved, the verification time is saved, and verification tasks are finished more quickly.

Description

technical field [0001] The invention relates to the field of integrated circuits, in particular to a verification method and platform based on SystemVerilog language. Background technique [0002] In the field of integrated circuits, the design and verification of integrated circuits are two important contents for realizing mass production of chips. Chips with excellent performance need to be based on advanced design solutions, but in order to reduce the risk of mass production, verification is required before chip tape-out to ensure that the chip design meets the expected requirements. [0003] The flash memory chip is a commonly used chip in the fields of computer, communication and consumer electronics. It is a kind of non-volatile random access memory (Non-Volatile Random Access Memory, NVRAM). The program can be directly executed in the flash memory chip. won't go away. Flash memory chips are widely used due to their small size and low power consumption. [0004] At ...

Claims

the structure of the environmentally friendly knitted fabric provided by the present invention; figure 2 Flow chart of the yarn wrapping machine for environmentally friendly knitted fabrics and storage devices; image 3 Is the parameter map of the yarn covering machine

Login to View More Application Information

Patent Timeline

Login to View More

Login to View More IPC IPC(8): G06F17/50

CPCG06F30/398G06F2115/06

Inventor 陈锴

Owner SICHUAN DOUQI TECH