SystemVerilog based random verification platform and method

A random verification and platform technology, applied in special data processing applications, instruments, electrical and digital data processing, etc., can solve problems such as increasing the complexity of verification platforms, meet the needs of simulation verification, facilitate error checking, and improve versatility. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

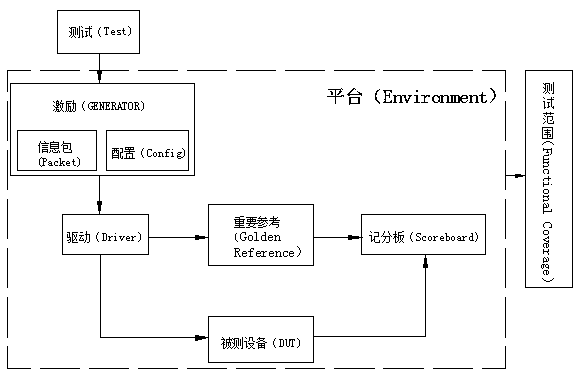

[0017] The random verification platform based on SystemVerilog described in this embodiment, as attached figure 1 As shown, the random verification platform includes a Test module, a Generator module, a Driver module, a DUT module, a Golden Reference module, a Scoreboard module, a Coverage module and an Environment module;

[0018] Among them, the Test module is used to instantiate the environment to start the test; the default values of many options can be set in the Test module, including dcb_arb_priority (simulation corresponds to PRIORITY), dcb_dir_any (simulation corresponds to DIR), flush_dcb_bank (simulation corresponds to FLUSH), Initialization (Simulation corresponds to INI);

[0019] Described Generator module: this module produces all test excitations, and test excitation is delivered to Driver module; Described Driver module: this module receives the test excitation of generator module, and drives to DUT and Golden Reference two modules; Described Scoreboard modu...

Embodiment 2

[0023] In the random verification platform based on SystemVerilog described in this embodiment, on the basis of Embodiment 1, the Generator module also includes two modules, Config and Packet, wherein the Config module: namely Configuration, can randomly generate configuration data according to configuration requirements ; Described Packet module: randomly generate the input of the design to be tested, the value of the address can repeat the previous address, can also be equal to the previous address of the previous address, can also be equal to the next address of the previous address, or can be equal to other random value; the Packet module will also randomly generate the input of the Golden Reference module.

[0024] In this embodiment 2, described Driver module receives the test excitation of generator module, and drives to DUT and Golden Reference two modules; By wait_cycles provided in Packet module, the transmission interval of input excitation can be randomized, and the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More