A random verification method of ahb kernel based on systemverilog

A random verification, host technology, applied in the direction of instrumentation, error detection/correction, calculation, etc., can solve problems such as bloat, test items are not closely related, and cannot take into account the mixing of multiple emergencies, so as to improve speed and Completeness, the effect of a complete testing process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] In order to make the content of the present invention clearer and easier to understand, the content of the present invention will be described in detail below in conjunction with specific embodiments and accompanying drawings.

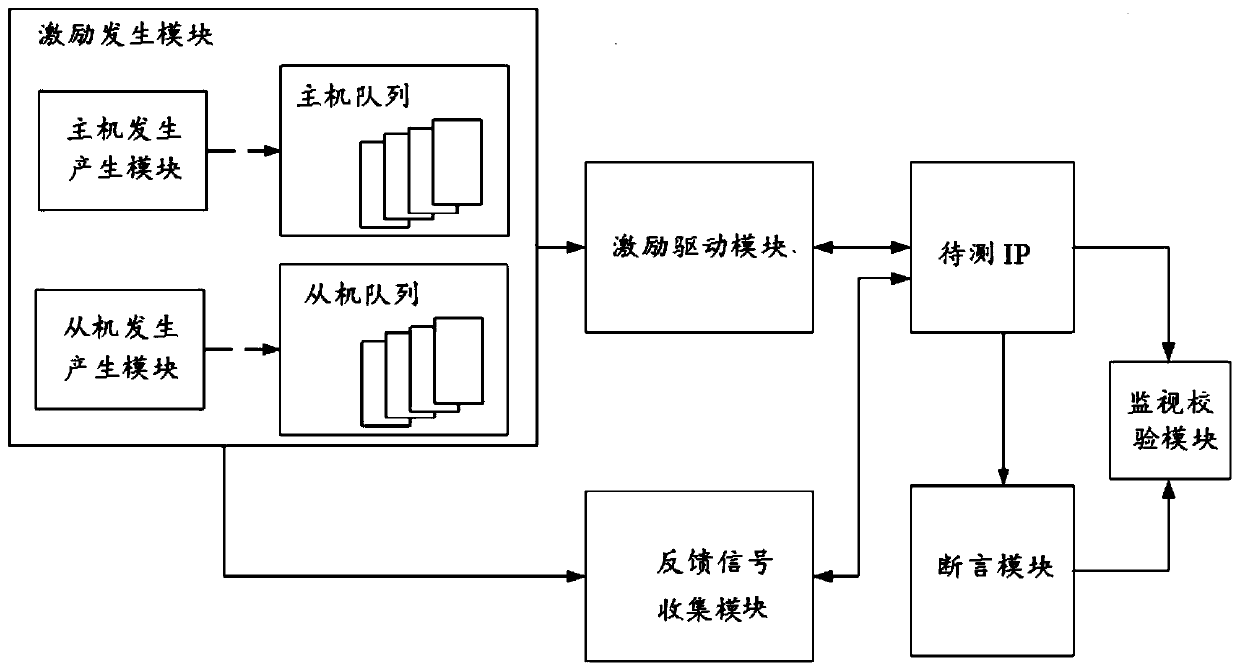

[0026] The IP to be detected is the AHB bus IP, so the verification method must be able to generate a feedback signal and update the input according to the feedback signal. Therefore, the required verification environment needs to be able to process these feedback signals and adjust the verification conditions in real time to check whether these feedbacks and the changes in the input conditions caused by the feedback are in compliance with the protocol.

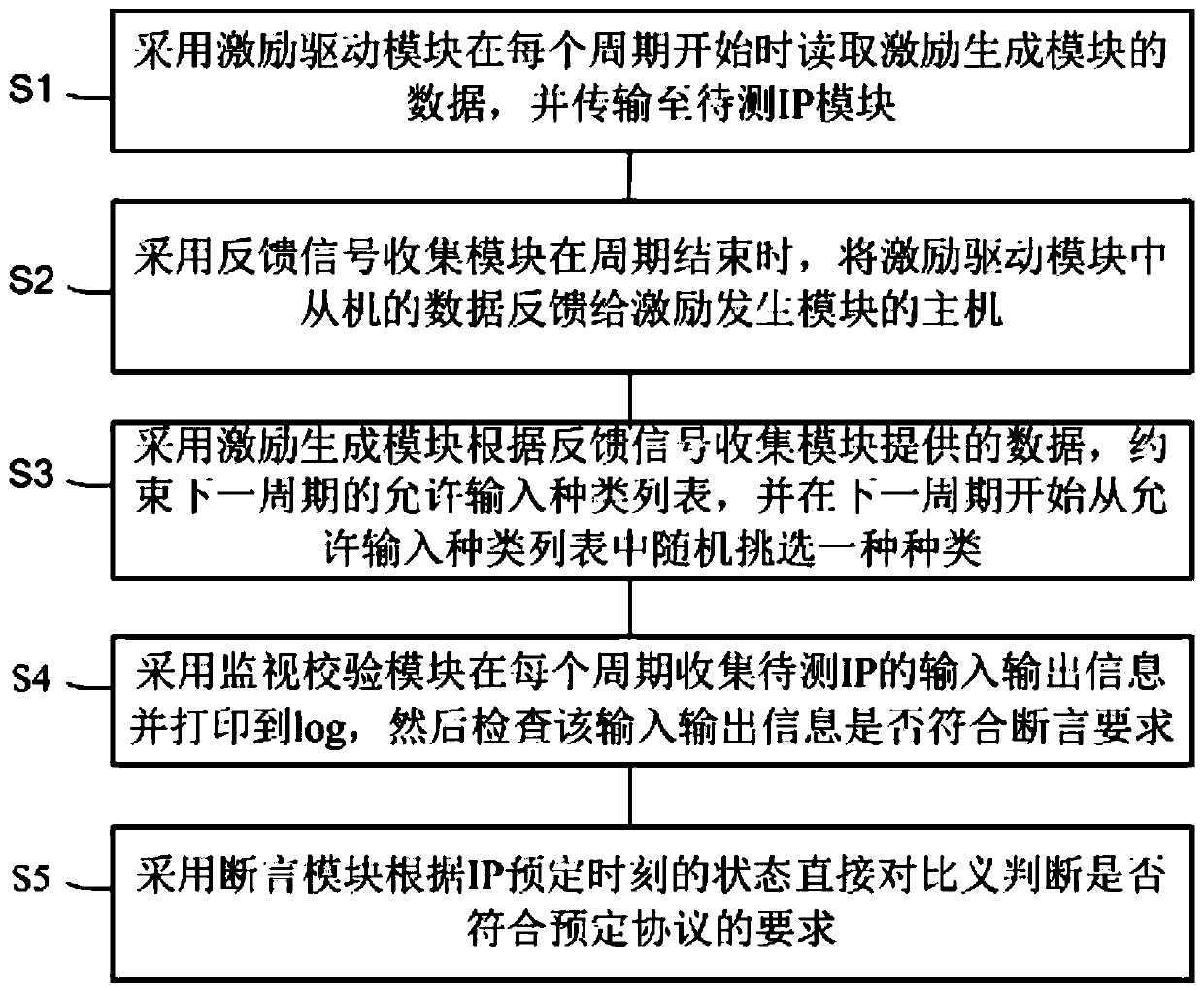

[0027] figure 1 It schematically shows the flowchart of the AHB core random verification method based on systemverilog according to a preferred embodiment of the present invention. figure 2 It schematically shows a block diagram of a systemverilog-based AHB core random verification method acc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More