Method for improving automatic verification platform efficiency through building reference model by using Python

An automatic verification and reference model technology, applied in the field of chip verification, to achieve the effect of improving development efficiency, improving verification efficiency, and developing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0048] The present invention will be further described below in conjunction with the drawings and specific embodiments.

[0049] The following describes the specific implementation steps in conjunction with the verification of the PKE (Public Key Engine) coprocessor.

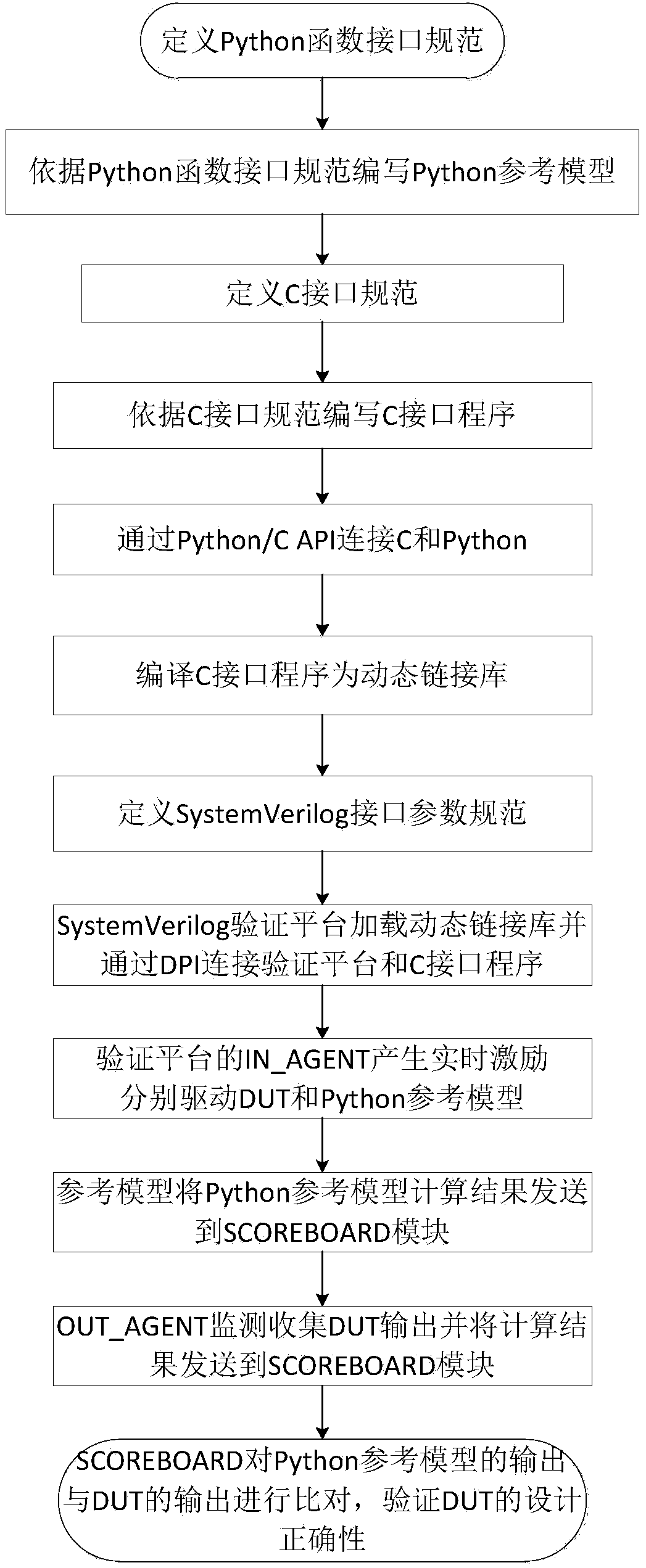

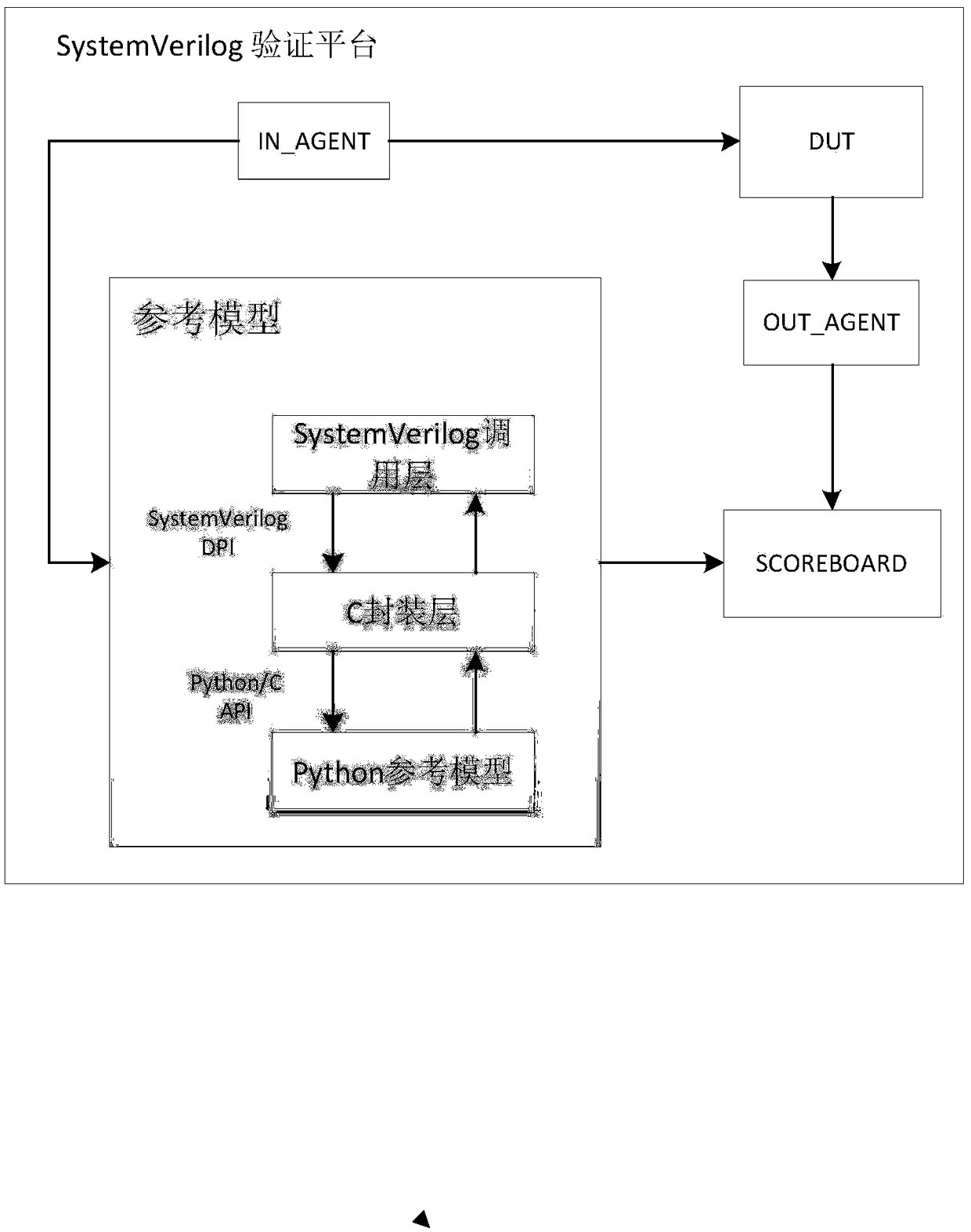

[0050] figure 1 Is the specific implementation flow chart. The first and third steps are to define the interface specification of the Python function and the definition of the C interface specification respectively. Since PKE designs 2048-bit long integer operations, the basic variables of C programs are only 64 bits long (unsigned long integer), so For transmission parameters larger than 64 bits, the input variables from C to Python and the output variables from Python to C can only be composite types composed of 64-bit long variables. Specifically, it is a tuple type consisting of multiple 64-bit integers on the Python side, and a PyTuple type on the C side.

[0051] The seventh step is to define the SystemVerilog ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More