Method and device for measuring temperature rising and heat resistance of Schottky grid field effect transistor

A Schottky gate, temperature rise technology, applied in the direction of single semiconductor device testing, material thermal development, etc., can solve problems such as affecting the acquisition temperature accuracy, gate voltage damage, burning devices, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

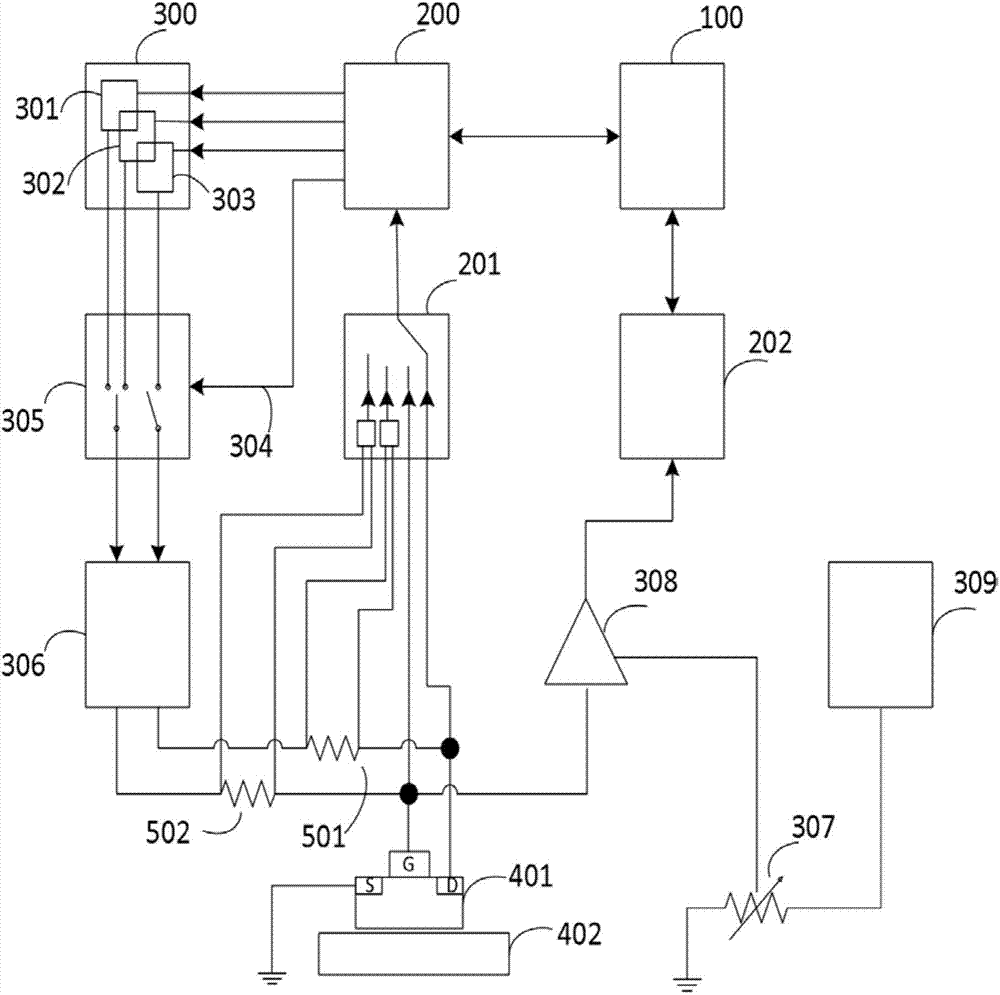

[0039] Firstly, the device under test 401 is placed on a temperature-adjustable constant temperature platform 402, and the constant temperature platform can be formed by using a semiconductor refrigerator. The computer 100 is the center of the measurement, and the sending of measurement instructions, transmission and storage of measurement data are all controlled by the computer 100 . The computer 100 is connected to the FPGA unit 200 via USB. The FPGA unit 200 can use Altera Cyclone II EP2C8Q208C8N. The FPGA unit 200 is connected to the power module 300 . The power module 300 includes a gate voltage source 301 , a test current source 302 and a drain voltage source 303 .

[0040] The gate voltage source 301 can be constructed using OP07 and TIP42C. One terminal of the gate voltage source 301 is connected to the FPGA unit 200 and receives a gate voltage command set by the computer 100 . The other end of the gate voltage source 301 is connected to a state control switch 305 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More