Patents

Literature

73 results about "Fpga field programmable gate array" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

FPGA Includes: FPGA basics. The Field Programmable Gate Array, or FPGA is a programmable logic device that can have its internal configuration set by software or as it is termed, “firmware.” This enables the FPGA functionality to be updated or even totally changed as required, because the FPGA firmware is updated when it is in circuit.

On-line upgrading method and device of configuration file of field-programmable gate array (FPGA)

InactiveCN102360302APower on to achieveProgram loading/initiatingFpga field programmable gate arrayElectricity

The invention discloses an on-line upgrading method and an on-line upgrading device of a configuration file of a field-programmable gate array (FPGA) and is used for accomplishing the on-line upgrading of the configuration file of the FPGA on the premise of no arrangement of an additional logic device and fulfilling the aim that the FPGA can be used after being energized. The on-line upgrading method of the configuration file of the FPGA comprises the following steps that: during the upgrading of the configuration file of the FPGA, a central processing unit (CPU) controls a bus changeover switch to switch off a first data channel between the FPGA and a memory and switch on a second data channel between the CPU and the memory; the CPU updates the configuration file, which is memorized in the memory, of the FPGA; after the configuration file of the FPGA is updated, the CPU controls the bus changeover switch to switch on the first data channel and switch off the second data channel; and the CPU triggers the FPGA to re-load the updated configuration file of the FPGA from the memory, and the FPGA performs configuration.

Owner:RUIJIE NETWORKS CO LTD

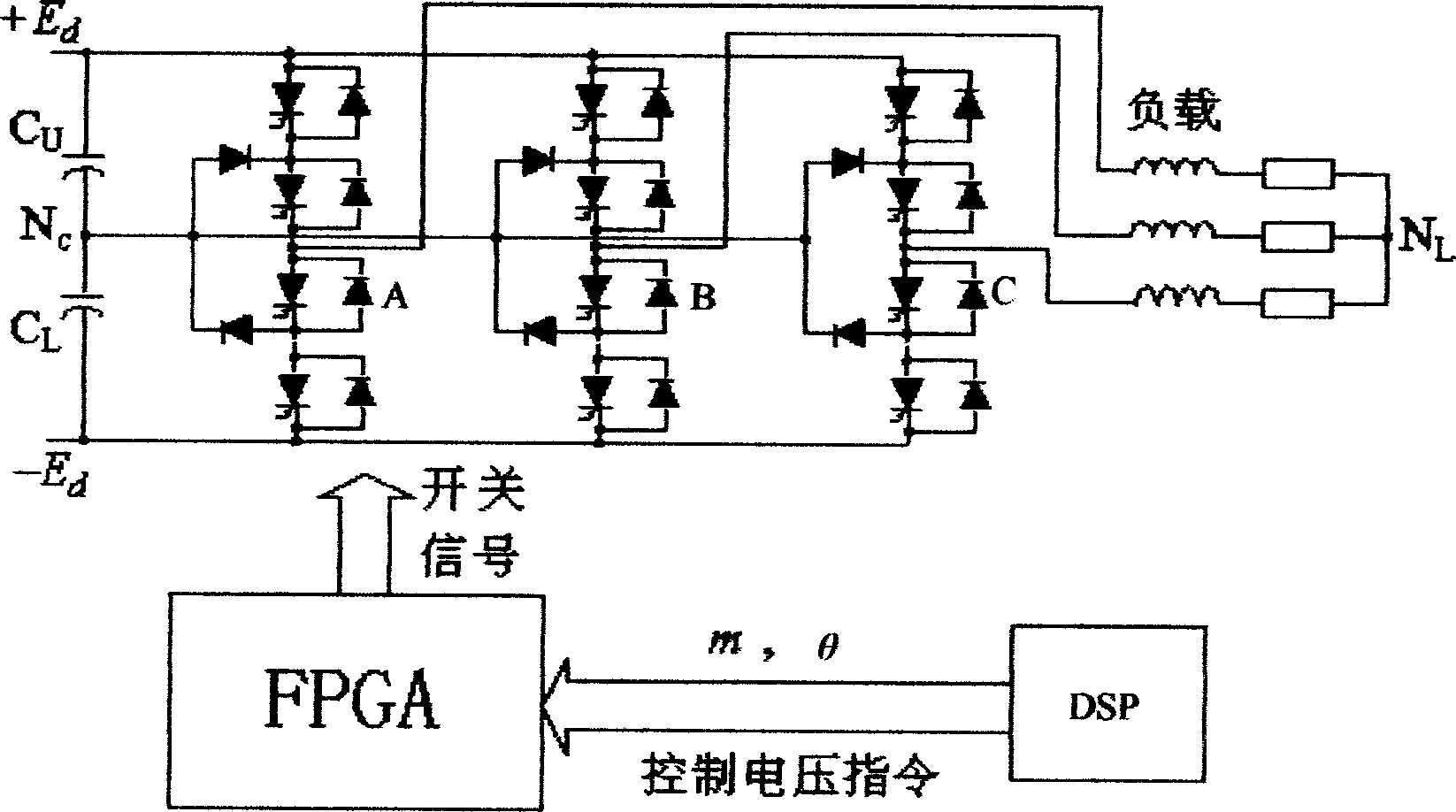

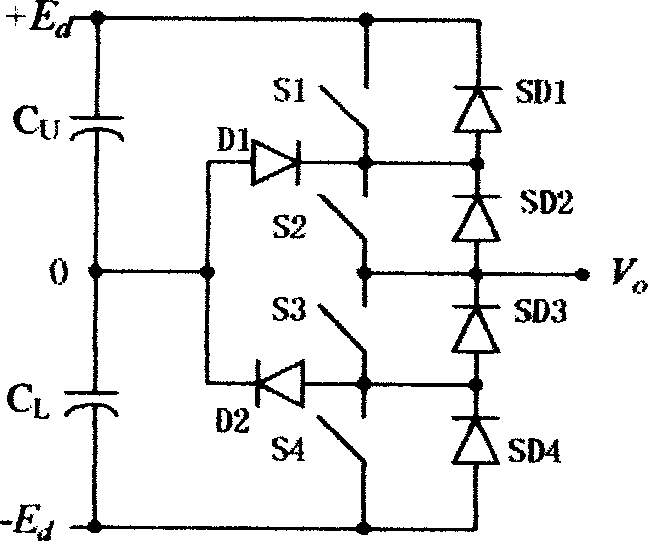

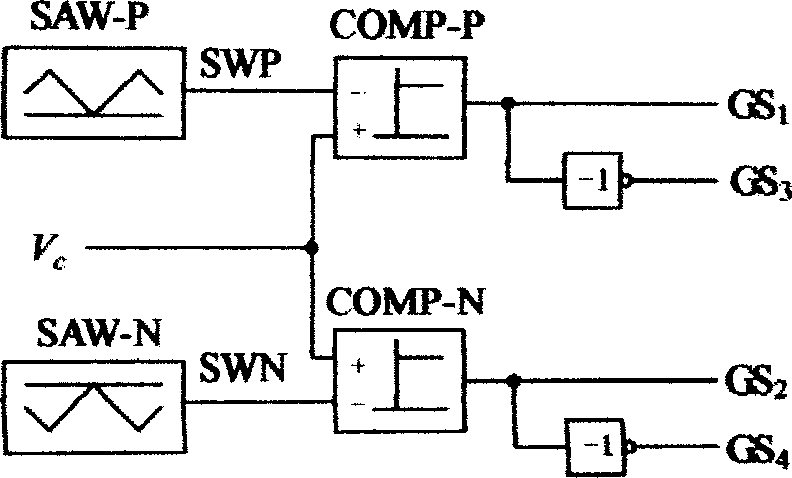

Three level inverter control system and method

InactiveCN1829061AFulfil requirementsImprove real-time performanceDc-ac conversion without reversalFpga field programmable gate arrayVoltage vector

The present invention discloses a three electric level inverter control system. It contains three electric level voltage source inverter (NPC), field programmable gate array (FPGA), digital signal processor (DSP), wherein FPGA field programmable gate array (FPGA) receiving digital signal processor (DSP) sent control voltage instruction generating three electric level voltage source inverter (NPC) control signal. The present invention also discloses three level inverter control method, featuring 1, digital signal processor (DSP) transmitting space voltage vector amplitude value m and argument for controlling three level inverter triphase reference voltage, 2, field programmable gate array (FPGA) receiving DSP sent space voltage vector amplitude value m and argument, generating signal Vca, Vcb, Vcc, through direct current biasing and dead zone compensation techniques processing to generate three-phase voltage modulation signal Vca **, Vcb **, Vcc **, 3, finally respectively comparing with positive triangular wave, negative triangular wave to generate control pulse. The present invention overcomes the insufficiency of current pulse width modulation method (SVPWM) and special harmonic cancellation method (SHE-PWM), provides a fine rapidity, simple controlling, and practical three level inverter control system and method.

Owner:GUANGDONG MINGYANG LONGYUAN POWER ELECTRONICS

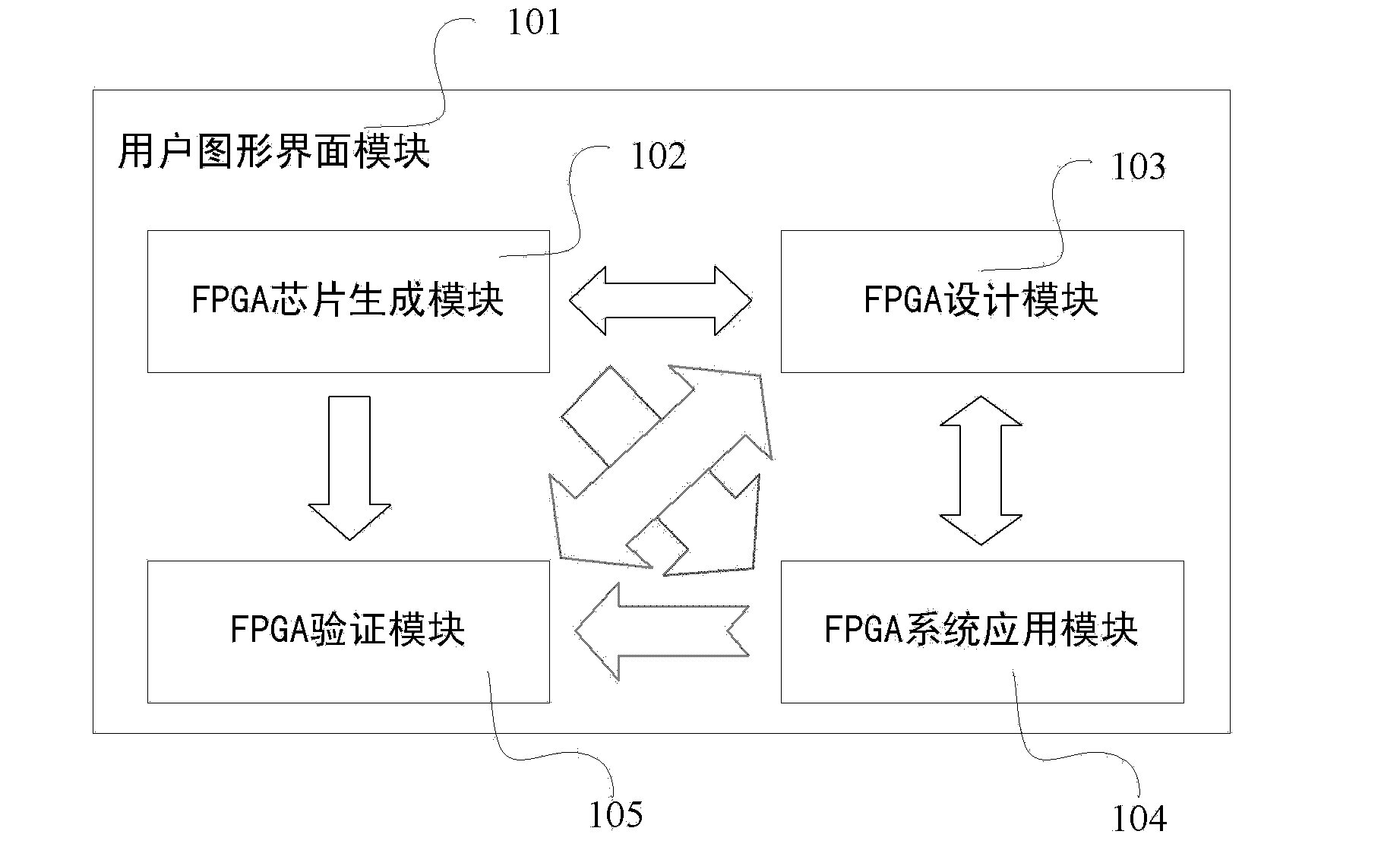

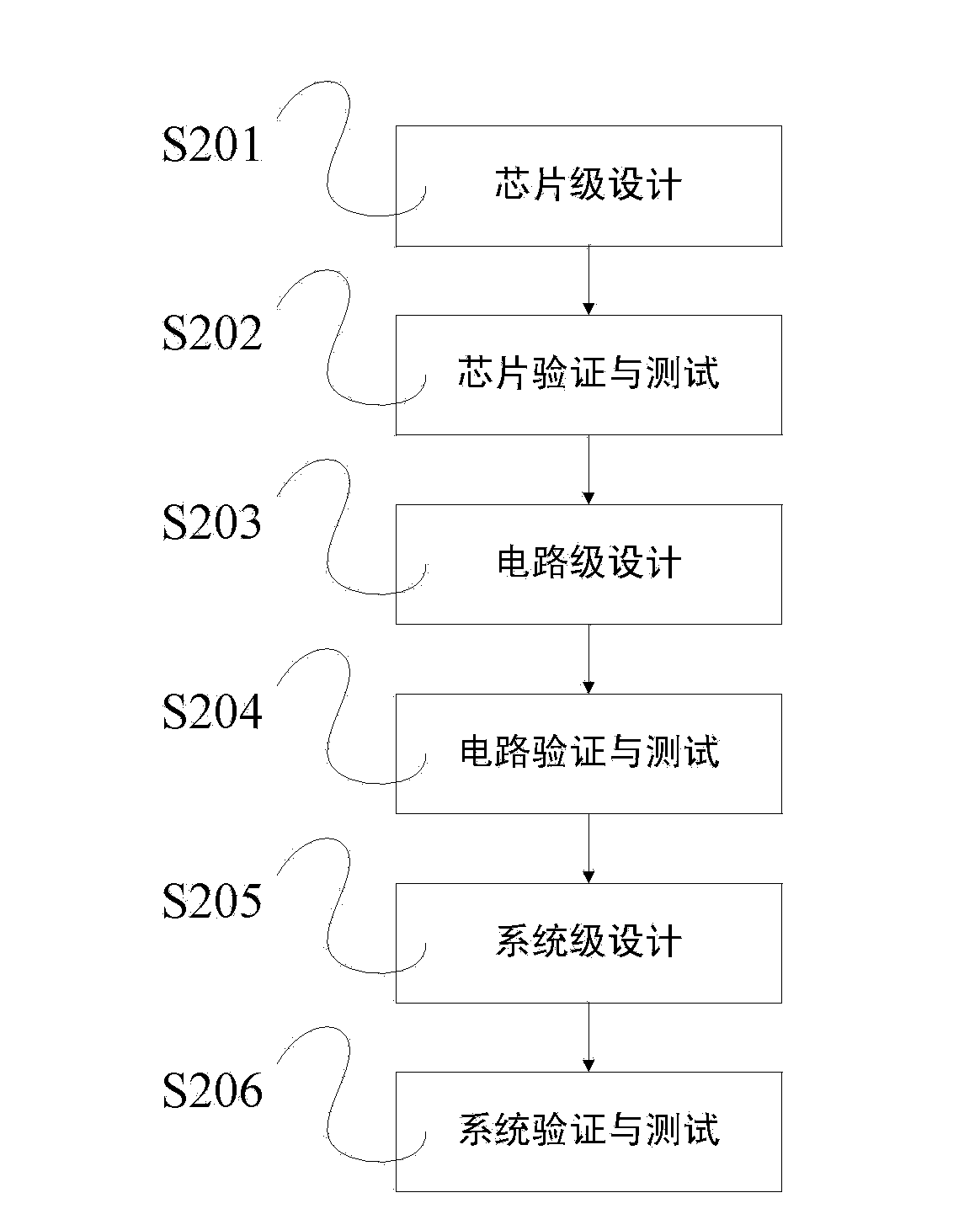

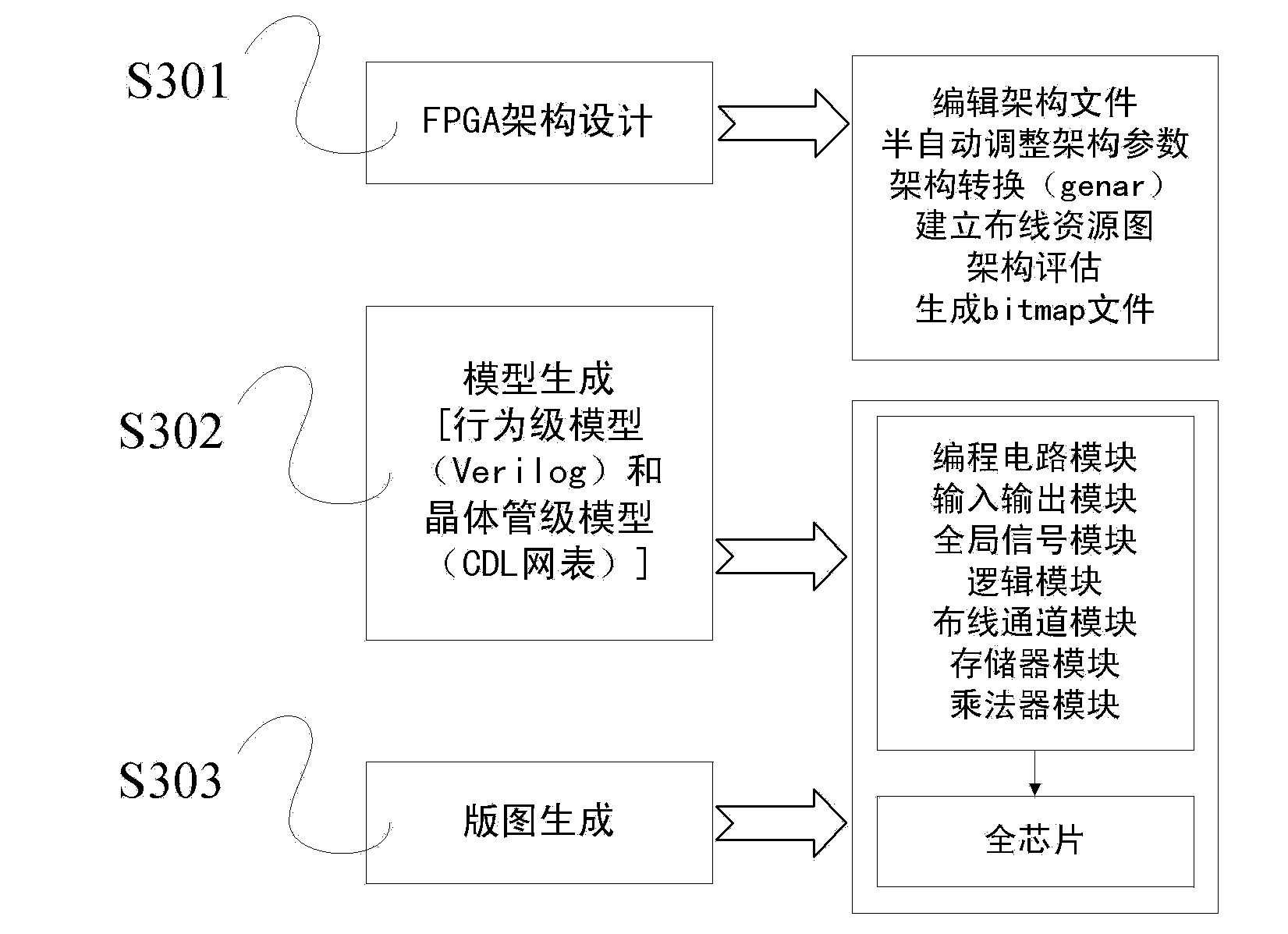

Cross-platform multilevel integrated design system for FPGA (field programmable gate array)

InactiveCN103678745AResolve does not provide quick designSolve functionSpecial data processing applicationsFpga field programmable gate arrayGNU/Linux

The invention discloses a cross-platform multilevel integrated design system for an FPGA (field programmable gate array). The cross-platform multilevel integrated design system comprises a user graphical interface module, an FPGA chip generating module, an FPGA design module, an FPGA system application module and an FPGA verification module, wherein the user graphic interface module is used for packaging the FPGA chip generating module, the FPGA design module, the FPGA system application module and the FPGA verification module. Switching among the FPGA chip generating module, the FPGA design module, the FPGA system application module and the FPGA verification module is realized by Tap page switching, so that the FPGA chip generating module, the FPGA design module, the FPGA system application module and the FPGA verification module can be called in a friendly and uniform user graphic interface, and cross-platform operating of Windows, Linux, Mac OS systems can be realized.

Owner:北京微纳星科技有限公司

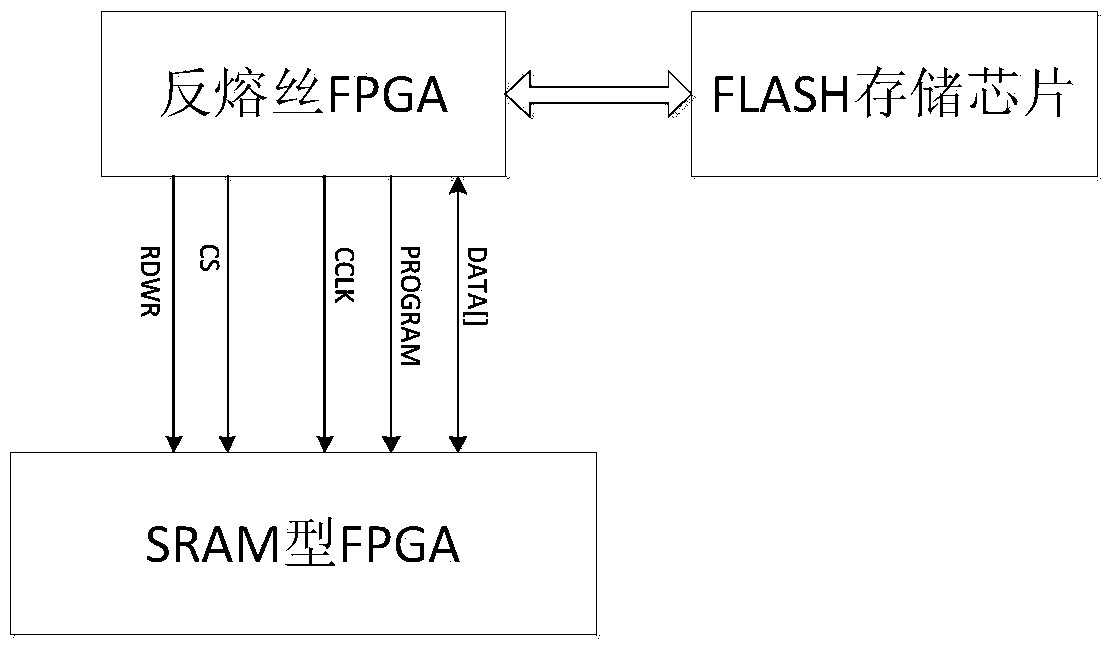

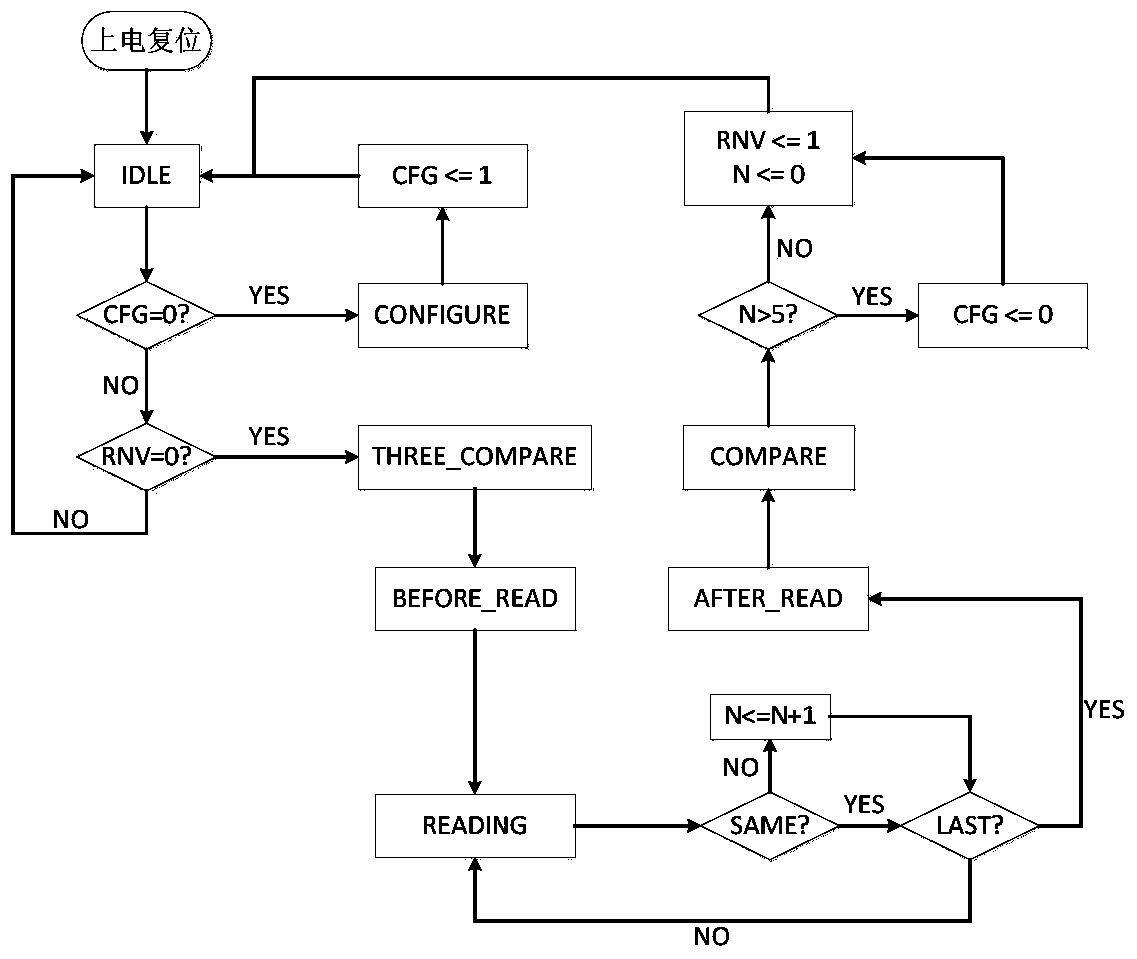

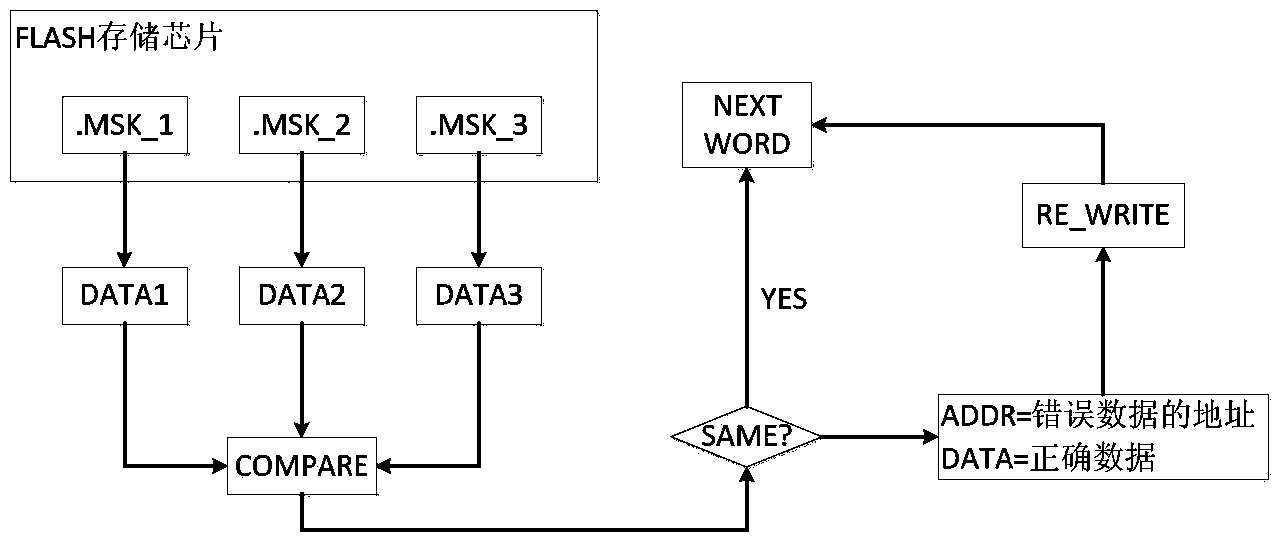

Method and system for monitoring single event upset effect of FPGA (field programmable gate array) and correcting reloading

InactiveCN103971732AReduce areaImproved ability to resist single event effectsDigital storageFpga field programmable gate arrayProgrammable read-only memory

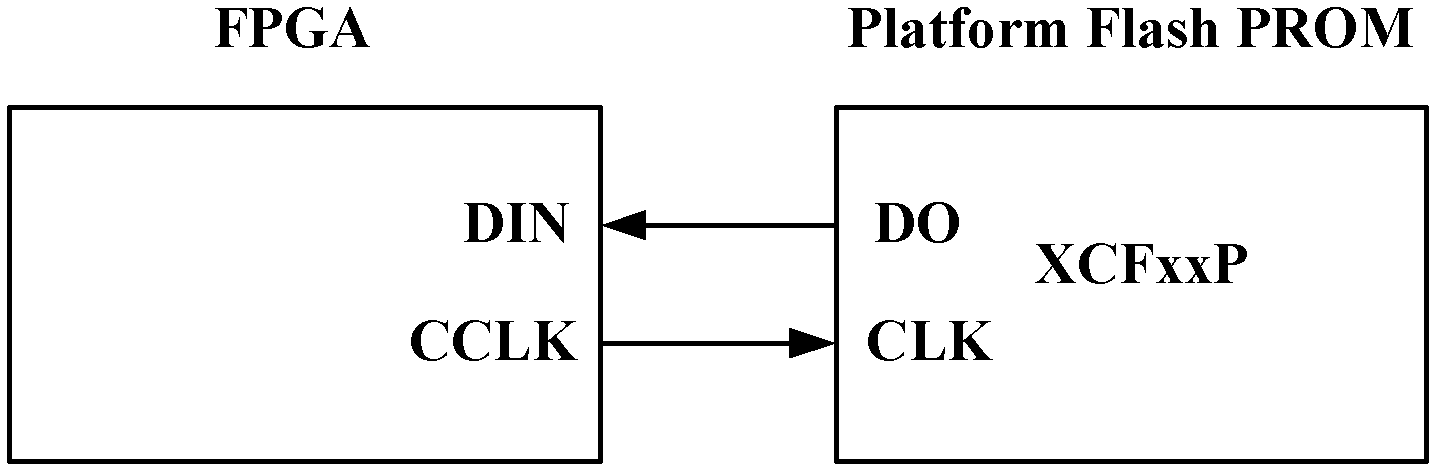

The invention discloses a method for monitoring a single event upset effect of an FPGA (field programmable gate array) and correcting reloading. The method comprises the steps: an antifuse FPGA reads back a configuration word through a configuration word readback function of an SRAM (static random access memory) type FPGA, compares the configuration word with a correct configuration word pre-stored in an FLASH storage chip, checks whether the SRAM type FPGA generates single event upset or not, and performs reloading through a loading program pre-stored in the FLASH storage chip if the SRAM type FPGA generates the single event upset. The invention also discloses a system for monitoring the single event upset effect of the FPGA and correcting the reloading. The system comprises the FLASH storage chip, the antifuse FPGA and the SRAM type FPGA which are connected in sequence. The method and the system which are disclosed by the invention simulate a time sequence of a PROM (programmable read-only memory) to load the SRAM type FPGA through a loading file pre-stored in the FLASH storage chip; compared with the system adopting a preliminary writing PROM, the system disclosed by the invention has the advantages that the distribution area of a PCB (printed circuit board) is reduced, and equipment minimization is facilitated.

Owner:ZHEJIANG UNIV

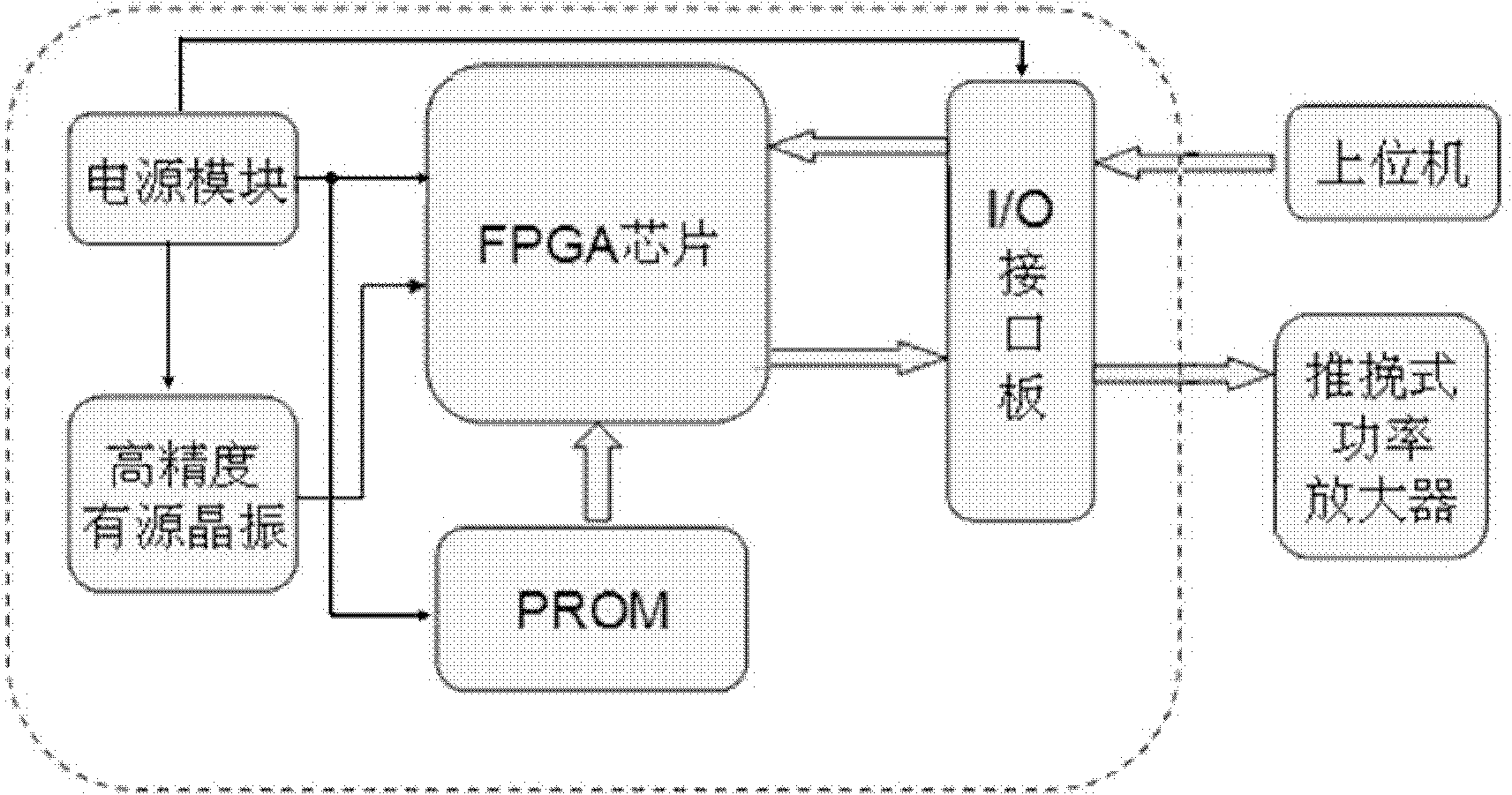

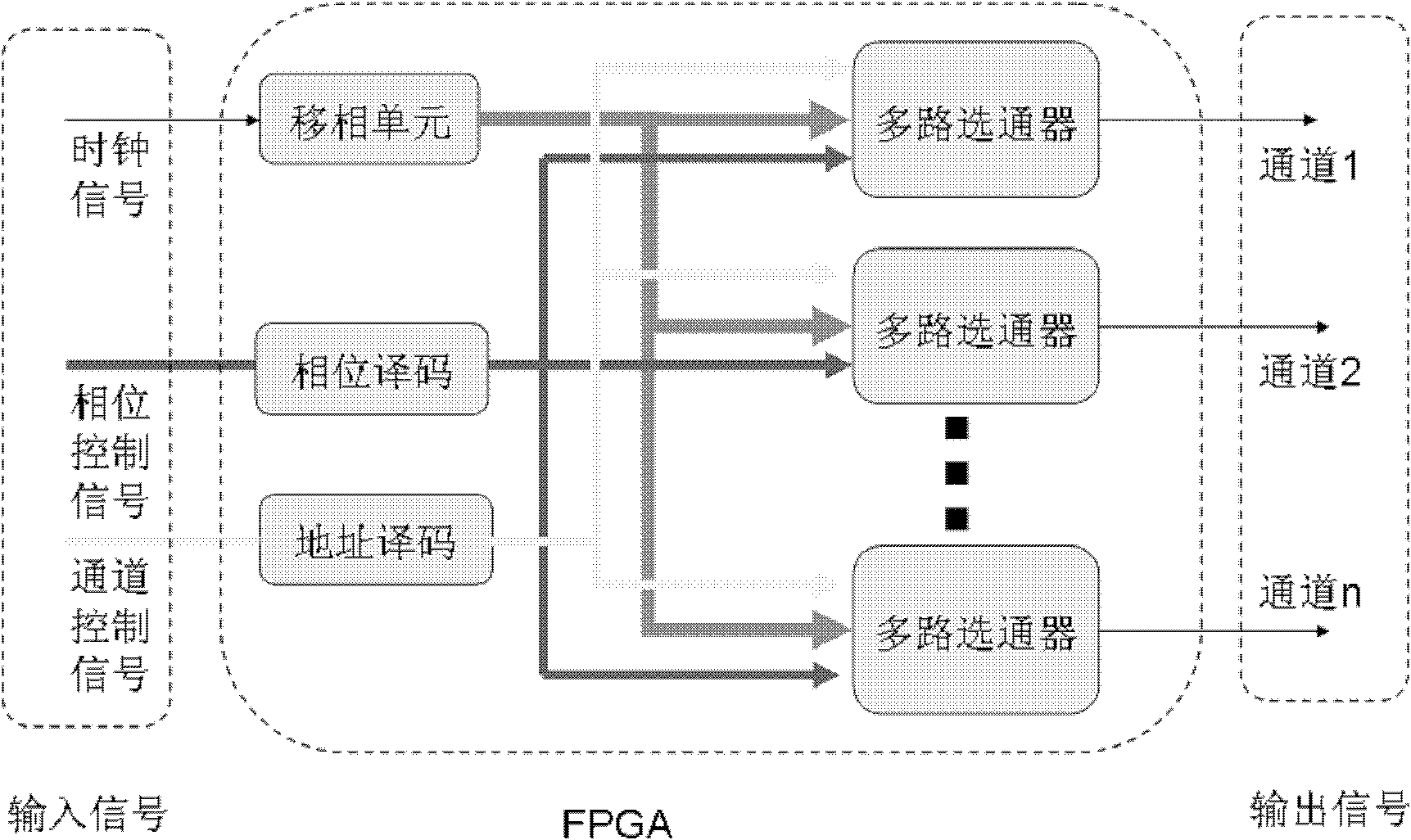

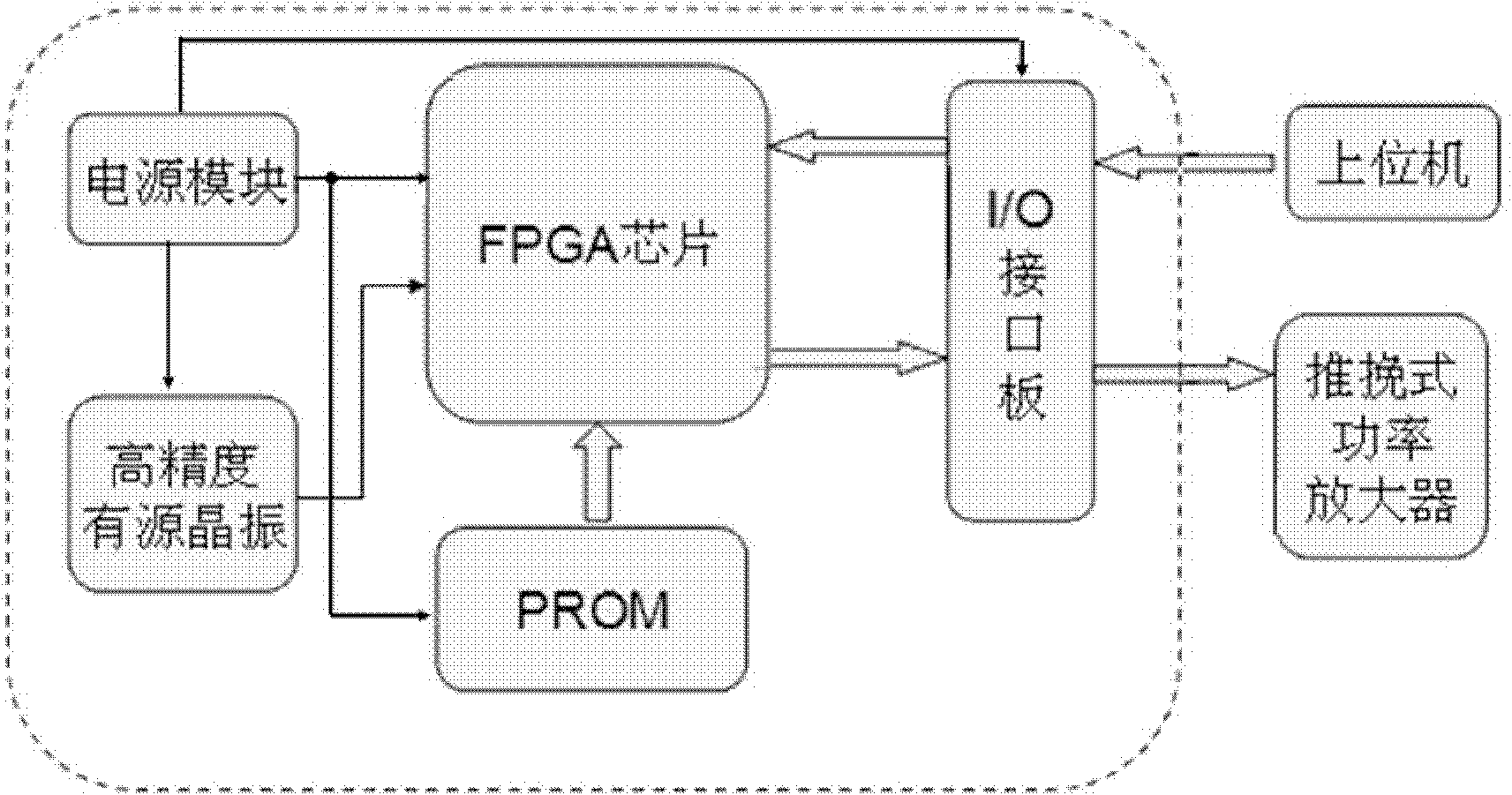

Multi-channel high precision phase control signal generation device

ActiveCN101862511AIncrease the number of channelsHigh precisionUltrasonic/sonic/infrasonic diagnosticsUltrasound therapyFpga field programmable gate arrayProgrammable read-only memory

The invention relates to a multi-channel high precision phase control signal generation device which utilizes a programmable read-only memory to generate a customized special circuit in an FPGA (Filed Programmable Gate Array) circuit through a VHDL (Very High Speed Integrated Circuit Hardware Description Language) language programming. The multi-channel high precision phase control signal generation device comprises a phase shift module, a phase coding module, an address coding module and a plurality of multi-channel gates. By taking a high precision active crystal oscillator as an information source, all multi-channel gates works in parallel to receive phase control signals of a host computer and output square wave signals of a multi-channel special phase. The output square wave signals access resonance of a power amplifier to generate sine wave signals with the same frequency and phase with the traditional output signals and the sine wave signals are used for excitation signals of an ultrasonic transducer array element in a phase control type high intensity focusing ultrasonic treatment system; and the frequency of the crystal oscillator is determined by the resonance frequency and the phase control precision requirements of the ultrasonic transducer array element. The invention dramatically increases the channel amount of the phase control signals and enhances the precision of the phase control signals, thereby satisfying the needs of the high intensity focusing ultrasonic treatment system.

Owner:SHANGHAI SHENDE MEDICAL TECH CO LTD

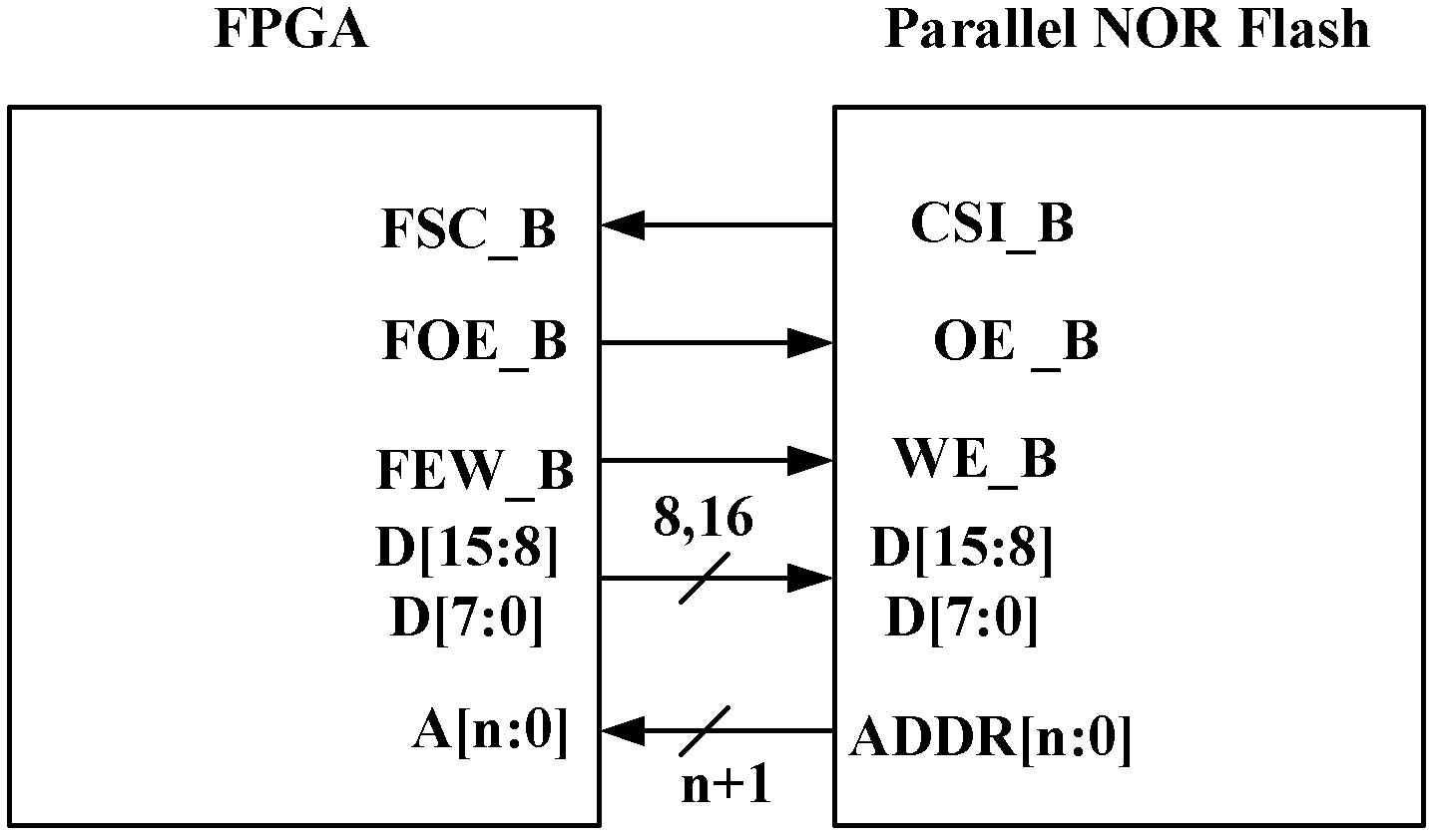

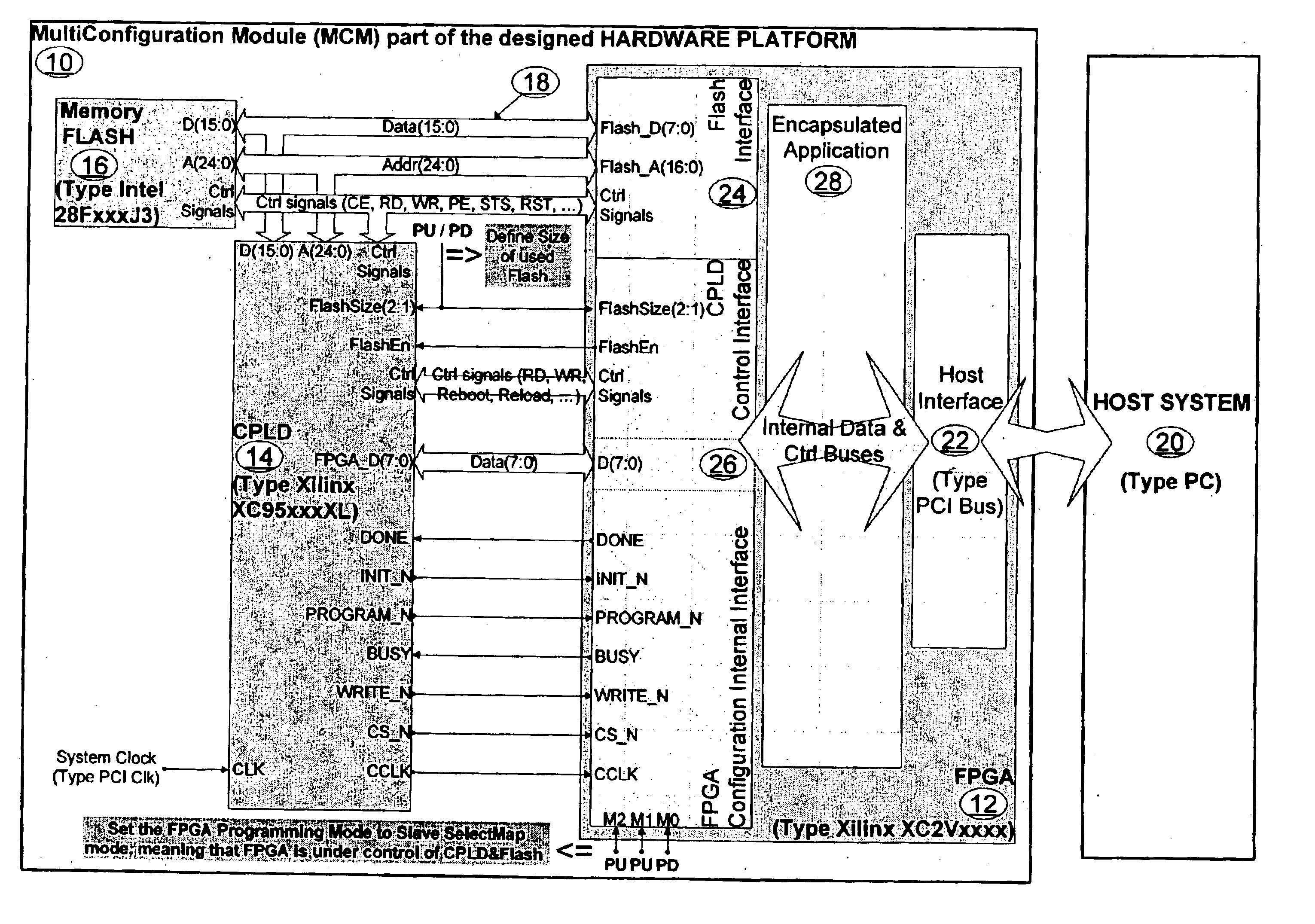

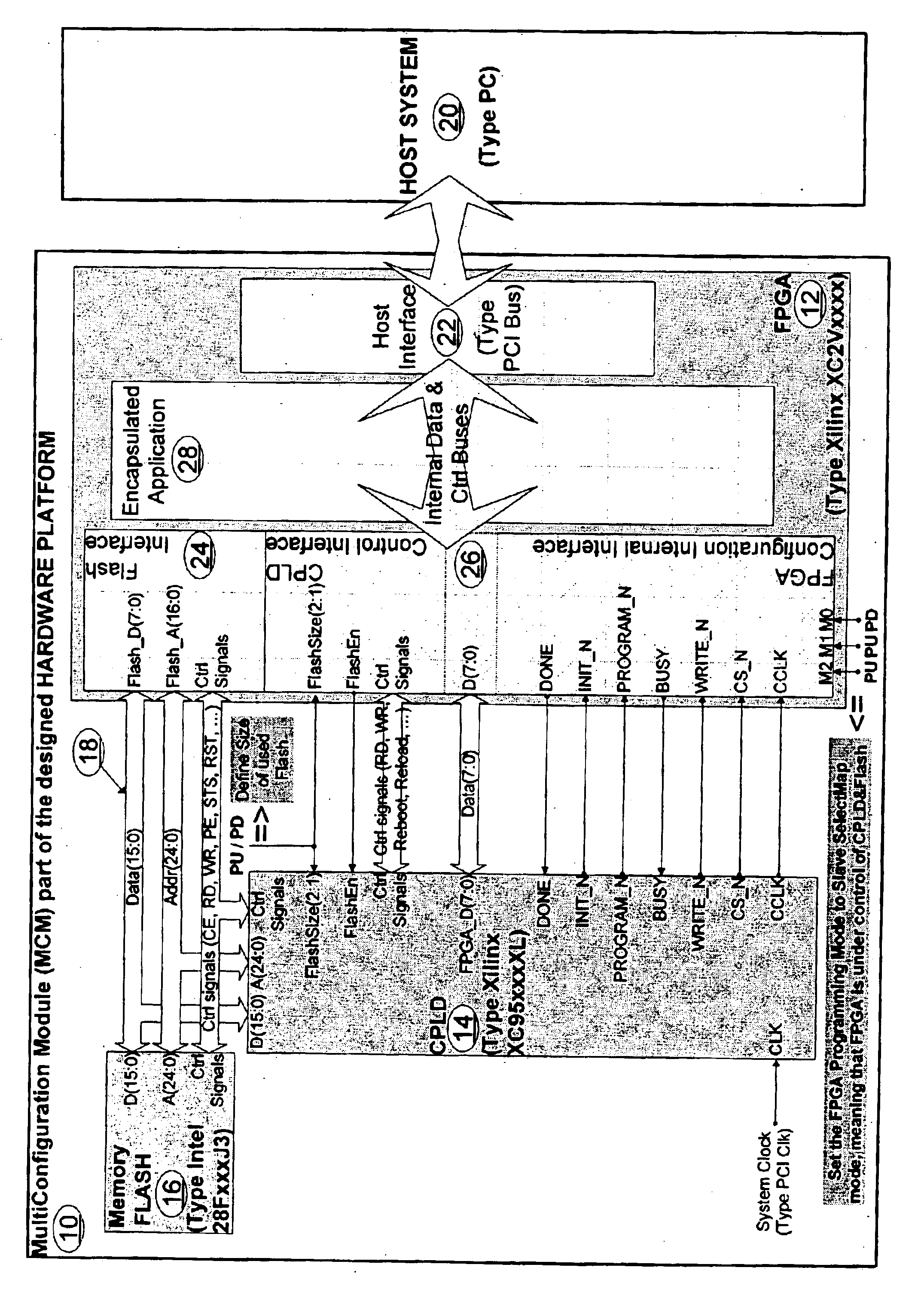

Multiconfiguration module for hardware platforms

InactiveUS6867614B1CAD circuit designSpecial data processing applicationsFpga field programmable gate arrayProgrammable logic device

A multiconfiguration module (MCM) includes a field-programmable gate array (FPGA), a memory flash, and a complex programmable logic device (CPLD). Hardware interfaces between the concerned components and the use of a raw FPGA configuration data stream (representing a part of FPGA code which should be common to all streams) are discussed. The raw configuration data stream handles communications between a user application running on the host system and the hardware platform components. The user application has the capability to load a new configuration data stream into the memory flash and request a full or partial reconfiguration of the FPGA with the available configuration data stream. This results in an FPGA that is re-programmable on-demand and that is useable in a variety of hardware platforms such as, for example, RAIT.

Owner:ORACLE INT CORP

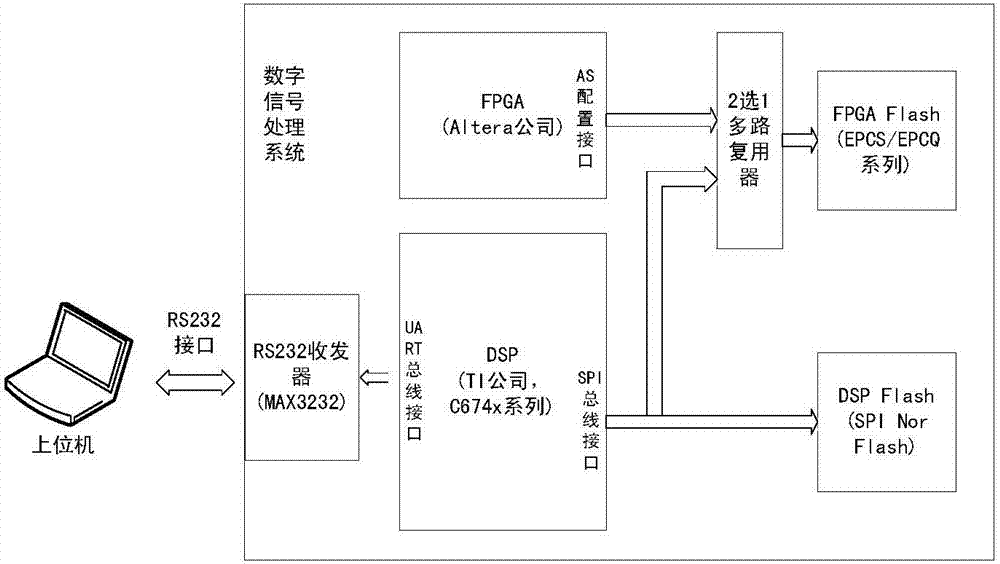

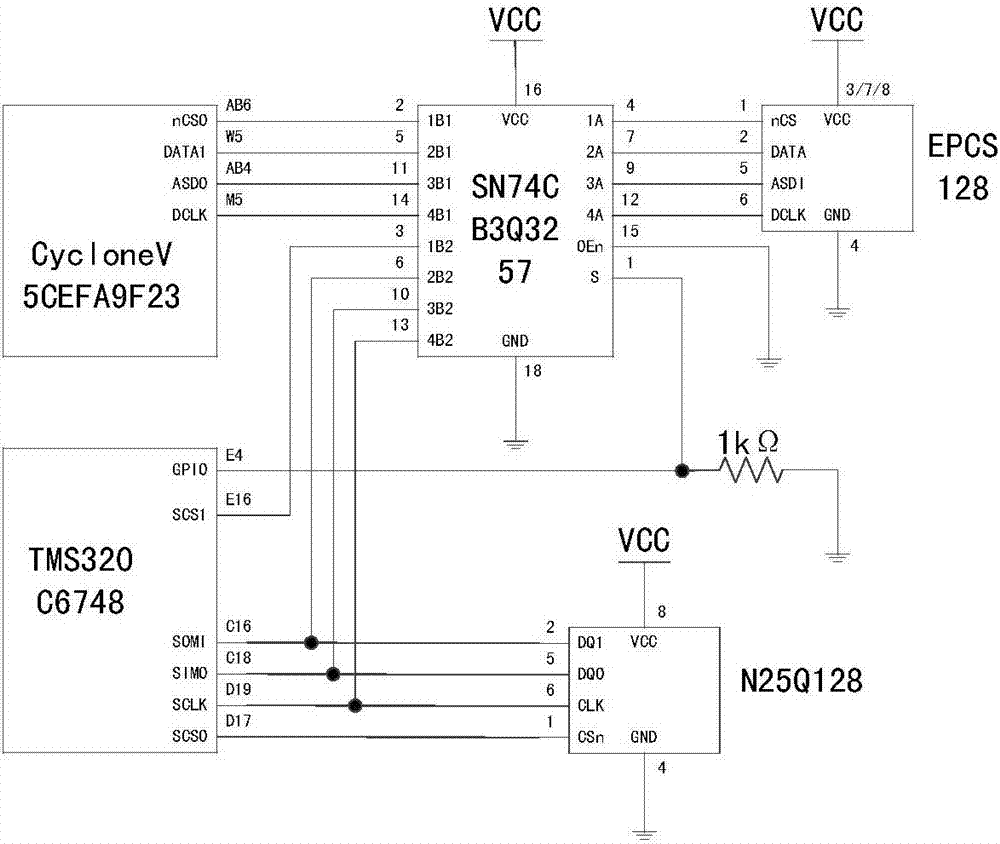

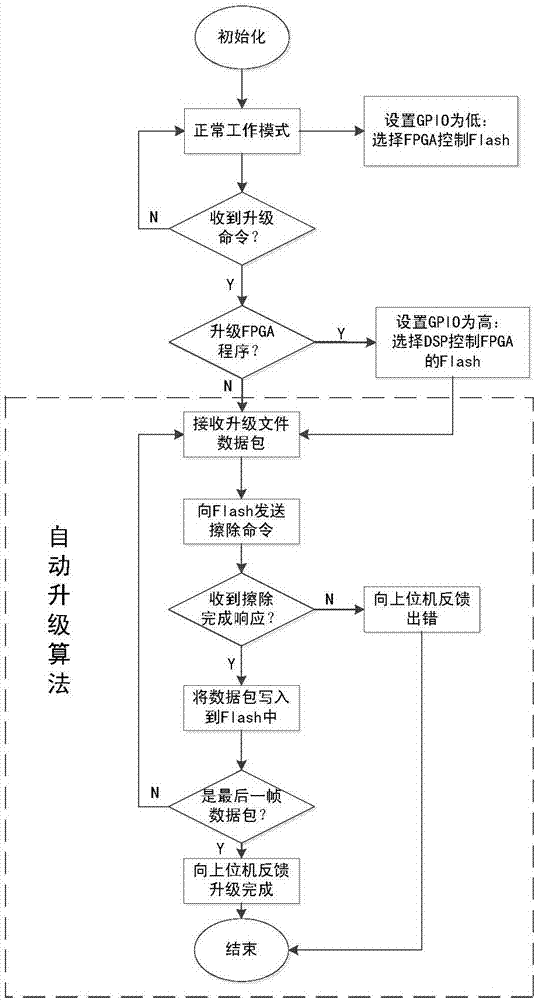

DSP (digital signal processor) and FPGA (field programmable gate array) system on-line updating method

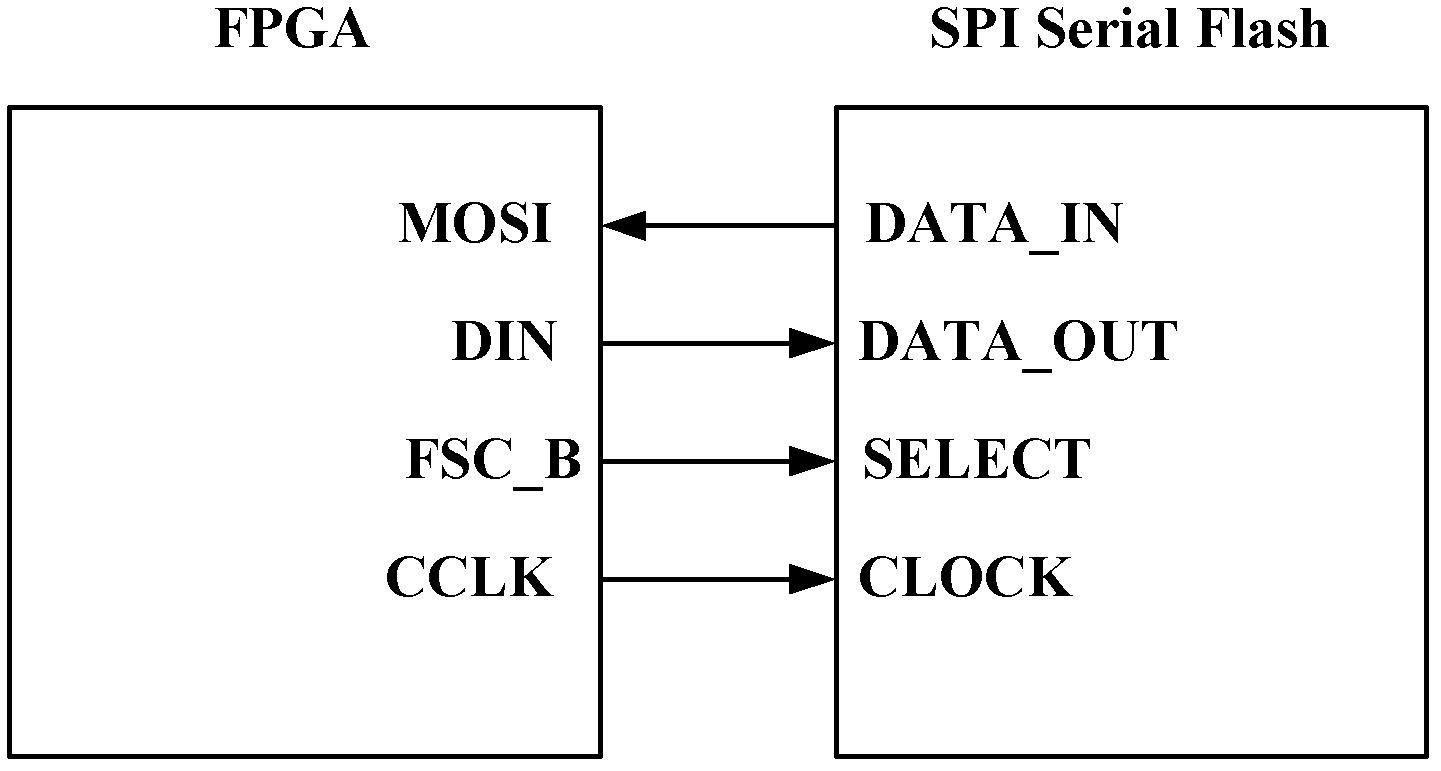

ActiveCN106909425AReduce Design ComplexitySimple interfaceSoftware engineeringProgram loading/initiatingFpga field programmable gate arrayMultiplexer

The invention discloses a DSP (digital signal processor) and FPGA (field programmable gate array) system on-line updating method, which is used for solving the problem of program online updating of a DSP and FPGA digital signal processing system. The method has the technical scheme that through a universal serial bus interface, the interconnection between a host computer and a DSP is completed; a DSP and FPGA program file to be updated is transmitted to the DSP; a Flash memory of the DSP or the FPGA is controlled to be updated by a DSP automatic updating algorithm; one group of SPI interface bus of the DSP is used for completing the hardware connection and erasing and writing of two Flashes; the bus address coding is completed through a multiplexer; the bus conflict is avoided. The program updating of the two chips of DSP and FPGA is simultaneously completed under the condition without dismounting the equipment; the interface is simple; the software and hardware design complexity is low; a simple and effective method is provided for the online updating of the digital signal processing system.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

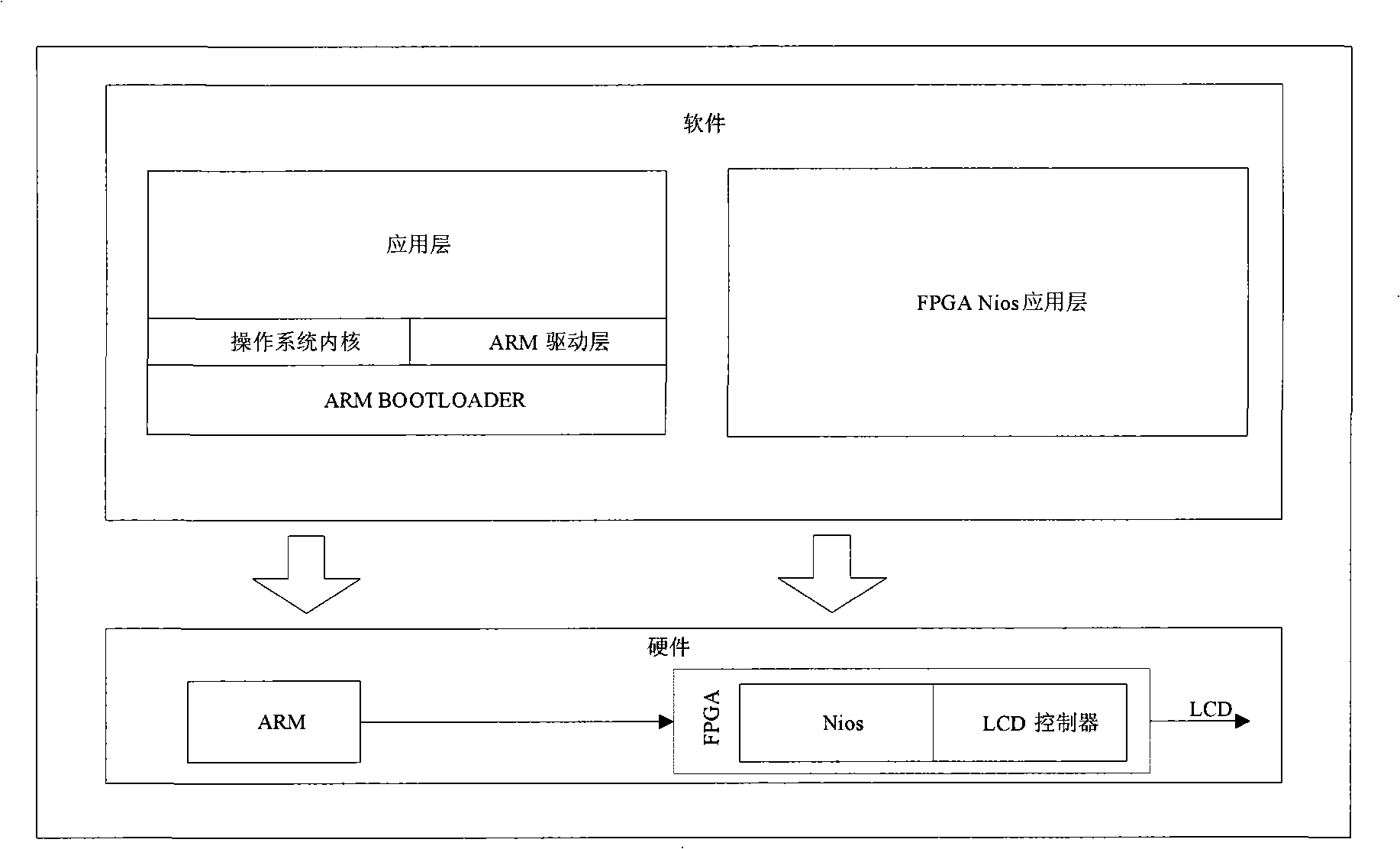

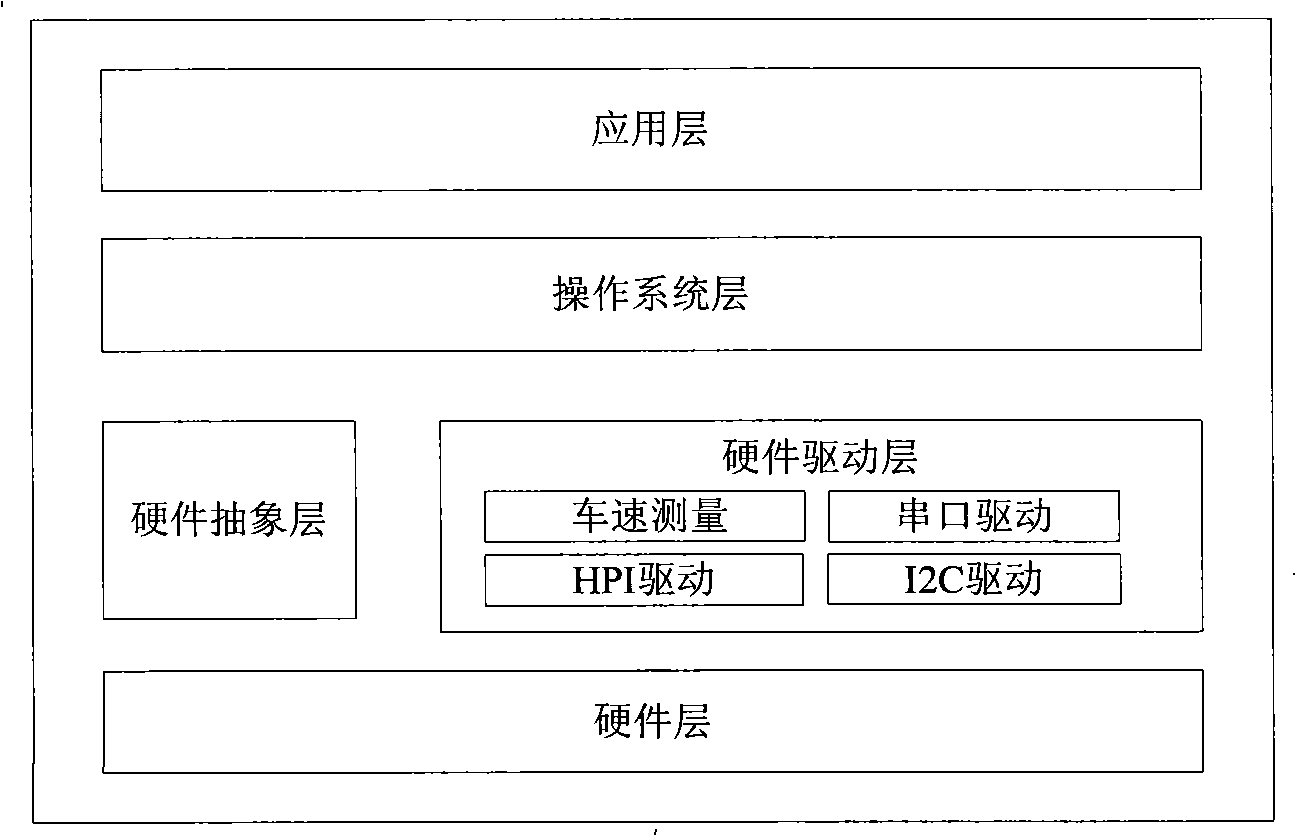

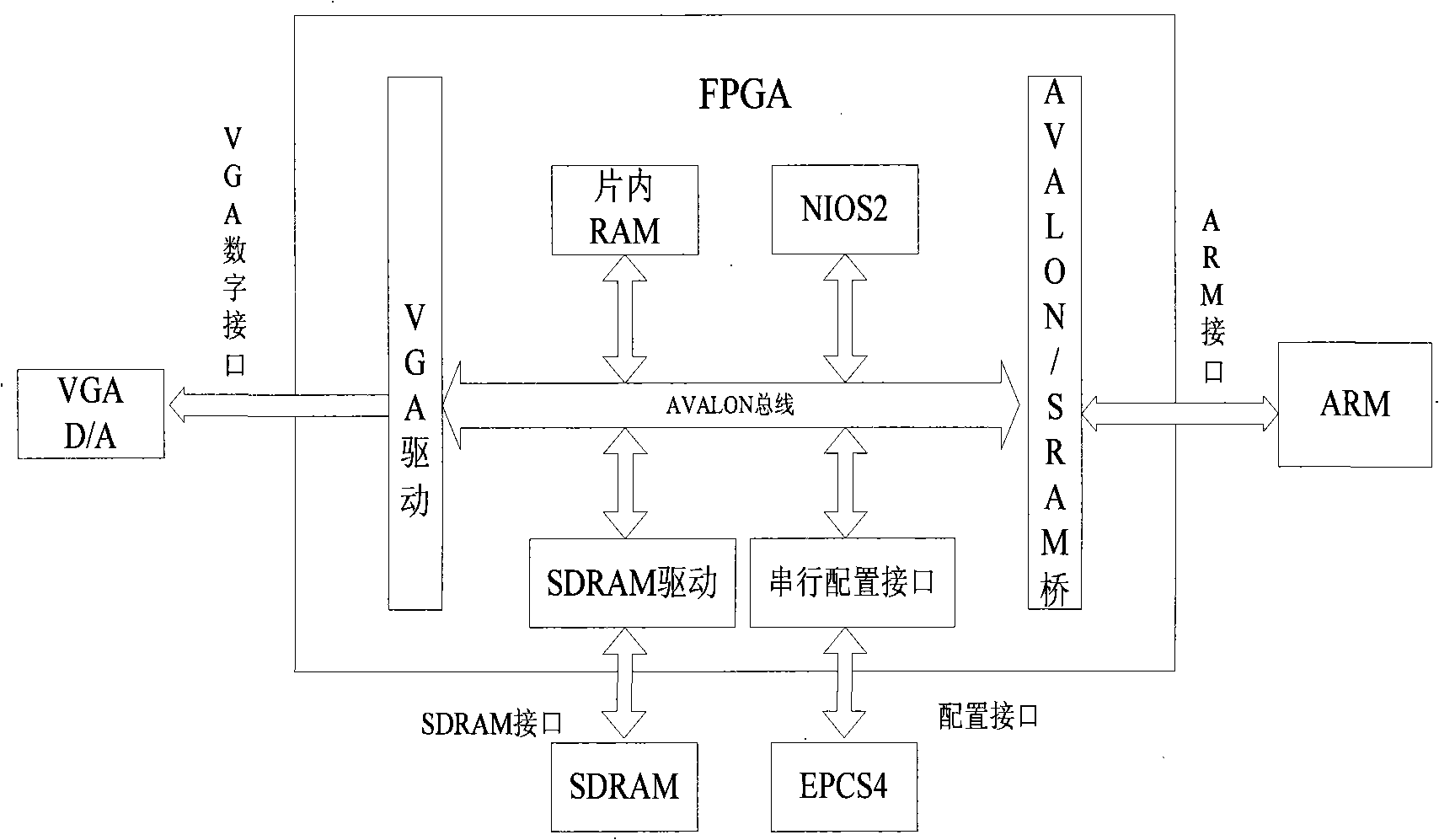

Hardware system structure of intellectualized full-graphics automobile instrument

InactiveCN101327785AExpansion layerBraking action transmissionElectrodynamic brake systemsFpga field programmable gate arrayStatic random-access memory

The present invention relates to a hardware system structure of intelligent wholly-graphic vehicle instrument, and consists of a microprocessor ARM and a field programmable gate array FPGA. The ARM is used for data acquisition and system control; the FPGA is used for video processing and graphic depiction display. The hardware system structure is characterized in that the FPGA and the ARM adopt an IIC mode or a shared memory for communication; the FPGA module is arranged outside, with an AVALON / SRAM serving as a static random access memory SRAM of the ARM processor; the graphic data transmitted from the ARM processor is stored in a synchronous dynamic random access memory SDRAM; the display and drawing array VGA display is driven according to the instructions of the ARM processor, so as to realize the functions of multilayer aliasing display, picture-in-picture display and point-line plotting. The hardware system adopts the highly efficient and flexible ARM+FPGA structure; the ARM is used for data collection, collation, analysis, storage and other functions; and the FPGA field programmable gate array is used for displaying the user interface.

Owner:WUHAN KOTEI TECH CORP

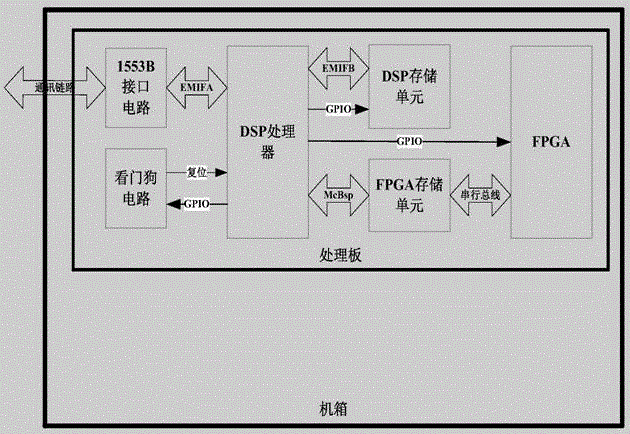

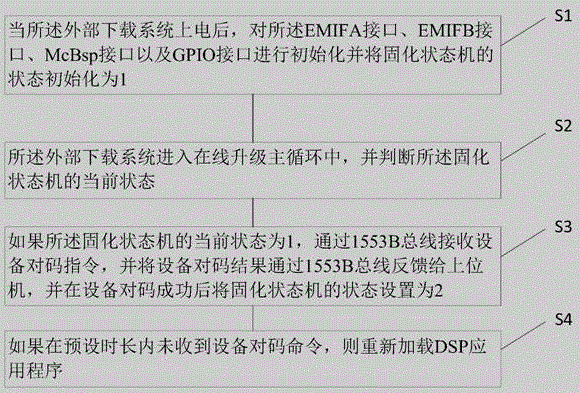

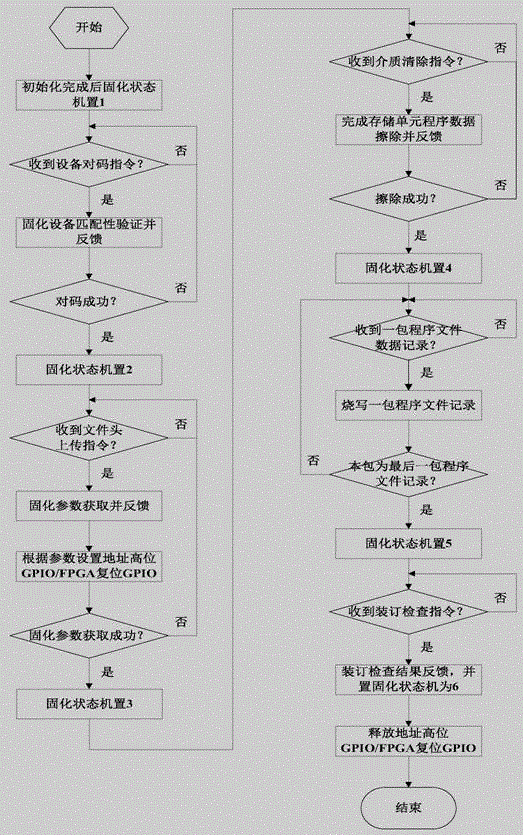

Method and system for external download of DSP (digital signal processor) program and FPGA (field programmable gate array) program

InactiveCN106547574AIncrease storage spaceImprove reliabilityVersion controlProgram documentationFpga field programmable gate arrayDsp processor

The invention provides a method and a system for external download of a DSP (digital signal processor) program and an FPGA (field programmable gate array) program. The system comprises a 1553B interface circuit, a DSP processor, a DSP storage unit, a watchdog circuit, an FPGA and an FPGA storage unit. The 1553B interface circuit is connected with the DSP processor through an EMIFA (external memory interface A), the watchdog circuit is connected with the DSP processor through a GPIO (general purpose input / output) interface, and the DSP storage unit is connected with the DSP processor through an EMIFB (external memory interface B) and a GPIO interface. The FPGA storage unit is connected with the DSP processor through a McBsp interface, the DSP processor is connected with the FPGA through a GPIO interface, and the FPGA storage unit is connected with the FPGA through a serial bus. The method and the system for external download of the DSP program and the FPGA program have the advantage that practicability, reliability and real-time performance of the system for external download can be improved.

Owner:SPACE STAR TECH CO LTD

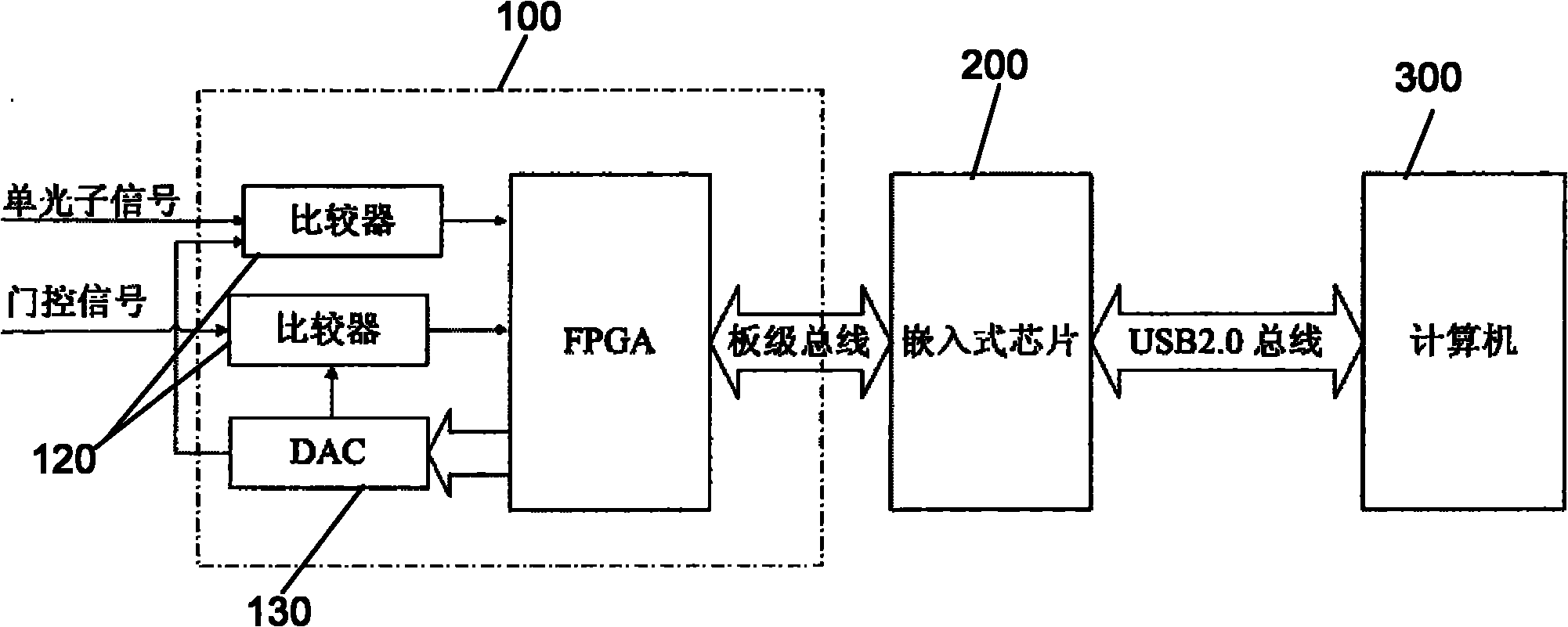

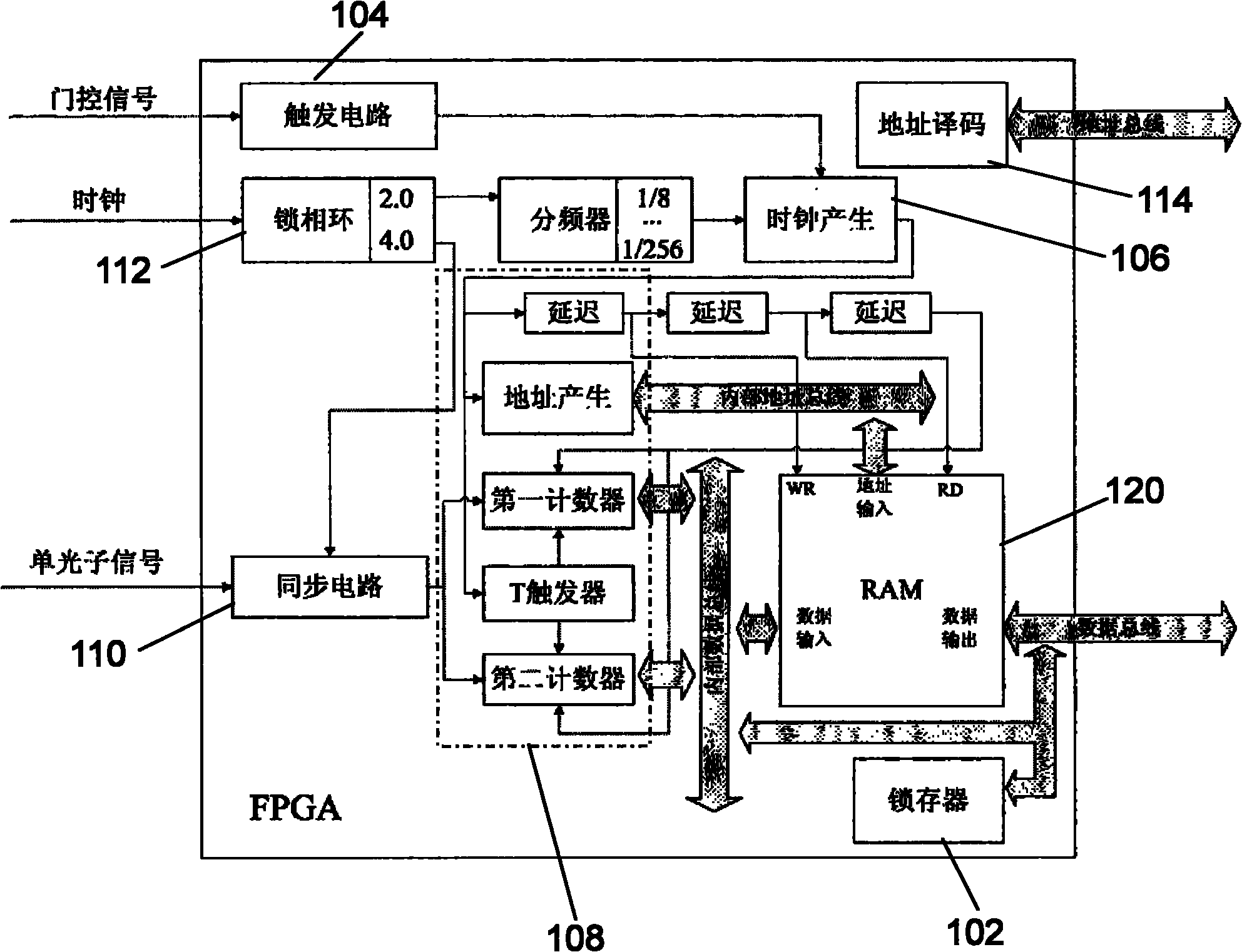

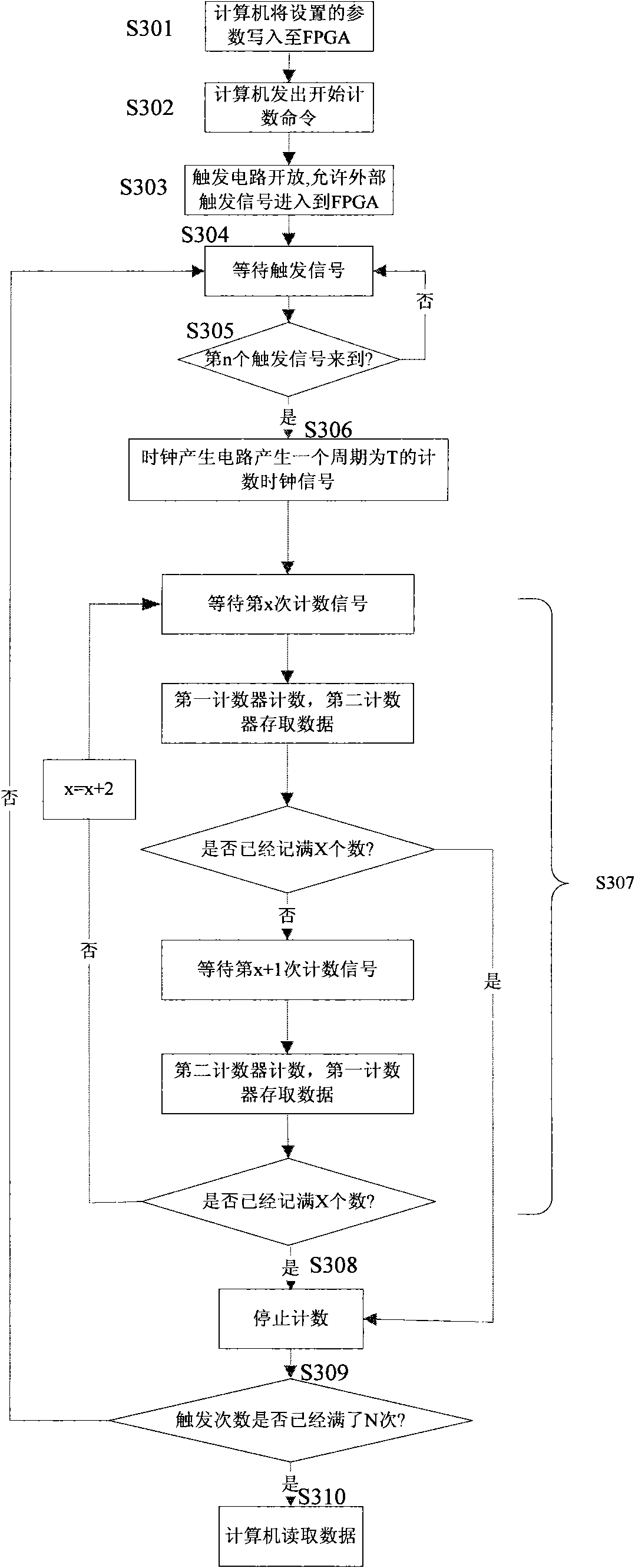

Single-photon counting system and counting method

InactiveCN101860358AReduce dead timeImprove counting efficiencyCounting chain synchronous pulse countersFpga field programmable gate arrayDead time

The invention discloses a single-photon counting system and a counting method. The system comprises a flip-latch, a triggering circuit, a clock generating circuit, a counting unit and a memory, wherein the counting unit comprises two counters, the ping-pong operation is adopted for carrying out the single-photon counting, the dead time is short, and the counting efficiency is high. The system can be realized through an FPGA field programmable gate array, and the hardware realization of the system has better flexibility and performance. In addition, the system can be connected with an external system through an embedded type chip and a USB bus, high-speed data transmission can be realized, and the invention has better real-time performance.

Owner:UNIV OF SCI & TECH OF CHINA

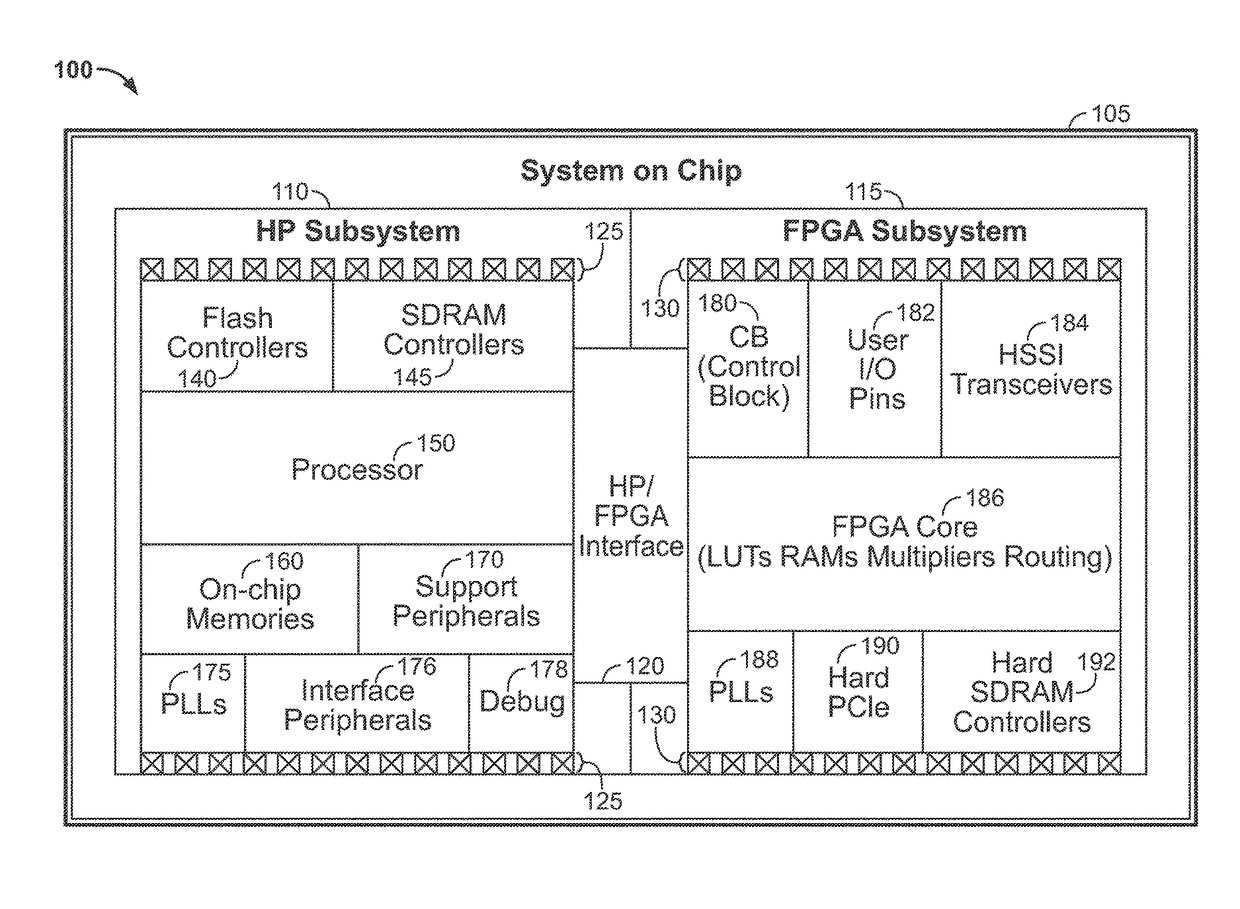

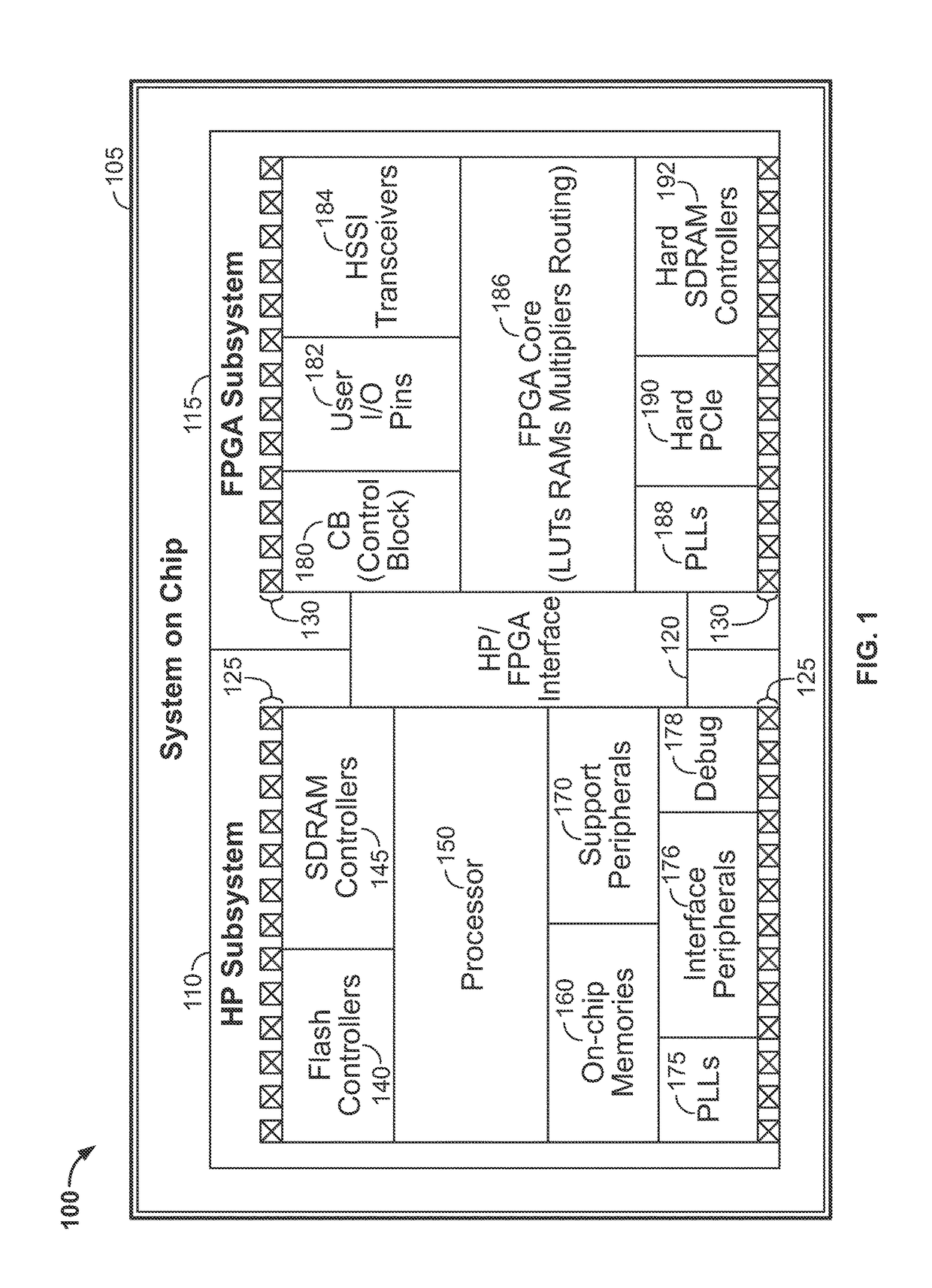

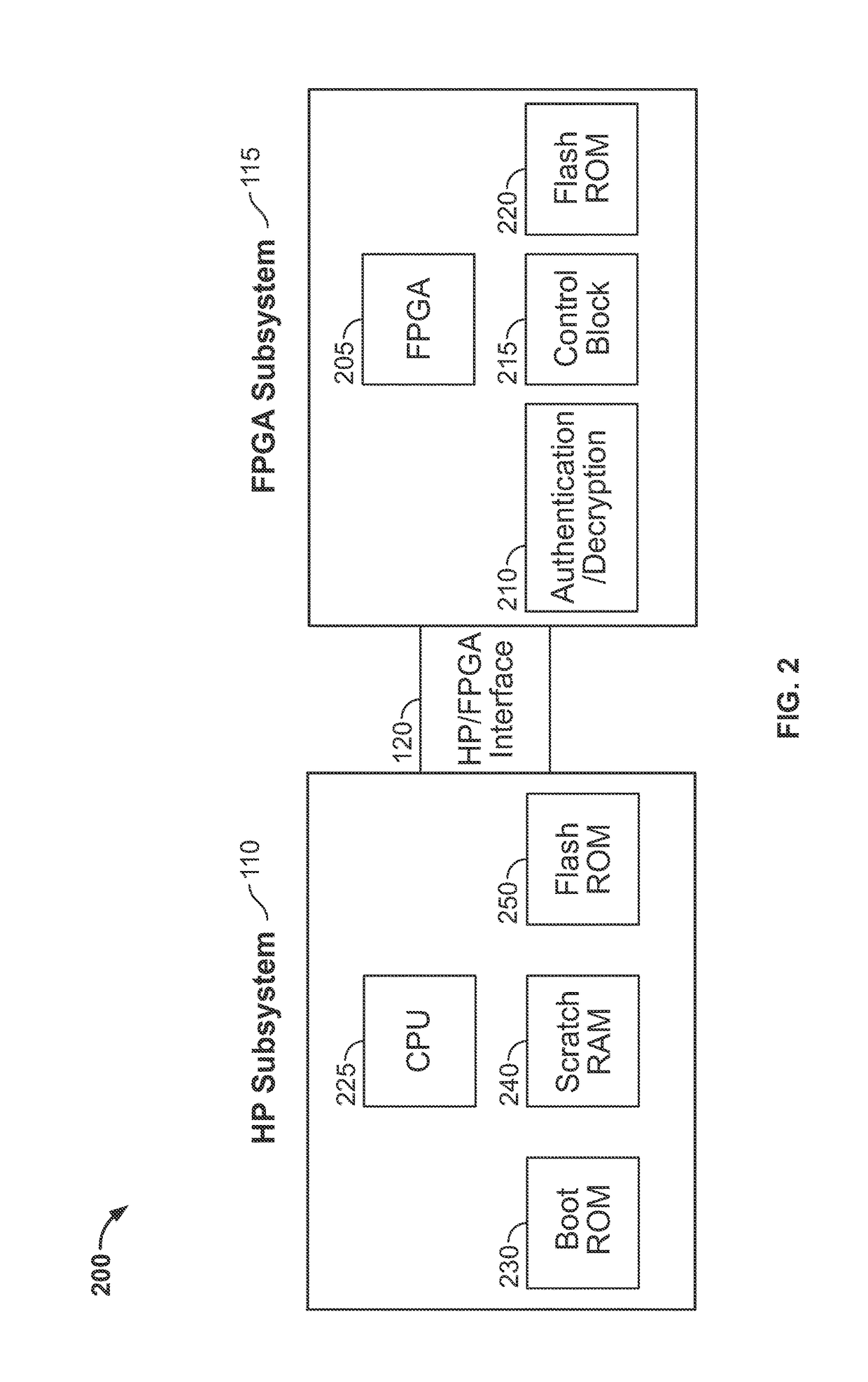

Secure boot using a field programmable gate array (FPGA)

ActiveUS9600291B1Ensure safetyUnauthorized memory use protectionDigital data protectionFpga field programmable gate arrayComputer science

This disclosure describes techniques for ensuring security in an integrated circuit system that includes a processor subsystem and a configurable-logic (e.g., FPGA) subsystem, which is capable of storing code executed by the processor. Techniques for utilizing the configurable-logic to control the process of booting a processor in the processor subsystem securely are described. Because the configurable-logic may be on the same die as the processor in the integrated circuit, the configurable-logic may securely boot the processor inside the security boundary of the package containing the die.

Owner:ALTERA CORP

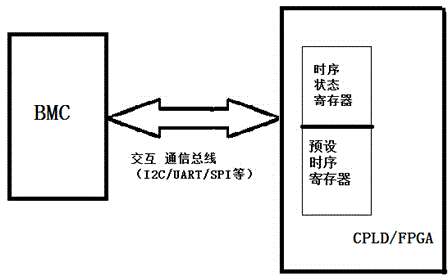

Method for using interaction of server motherboard BMC and CPLD for rapid diagnosis of motherboard timing

The invention provides a method for using interaction of a server motherboard BMC (baseboard management controller) and CPLD (complex programmable logic device) for rapid diagnosis of motherboard timing and relates to the field of server equipment. Through the use of the characteristics of customizable pins and internal registers of CPLD (FPGA-field programmable gate array), a communication bus is externally added on an existing motherboard CPLD (FPGA) to be used for communicating with BMC, and CPLD (FPGA) is internally added to record a timing state of the motherboard. Monitor and record of the timing state of the motherboard are realized with no motherboard hardware to be added.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

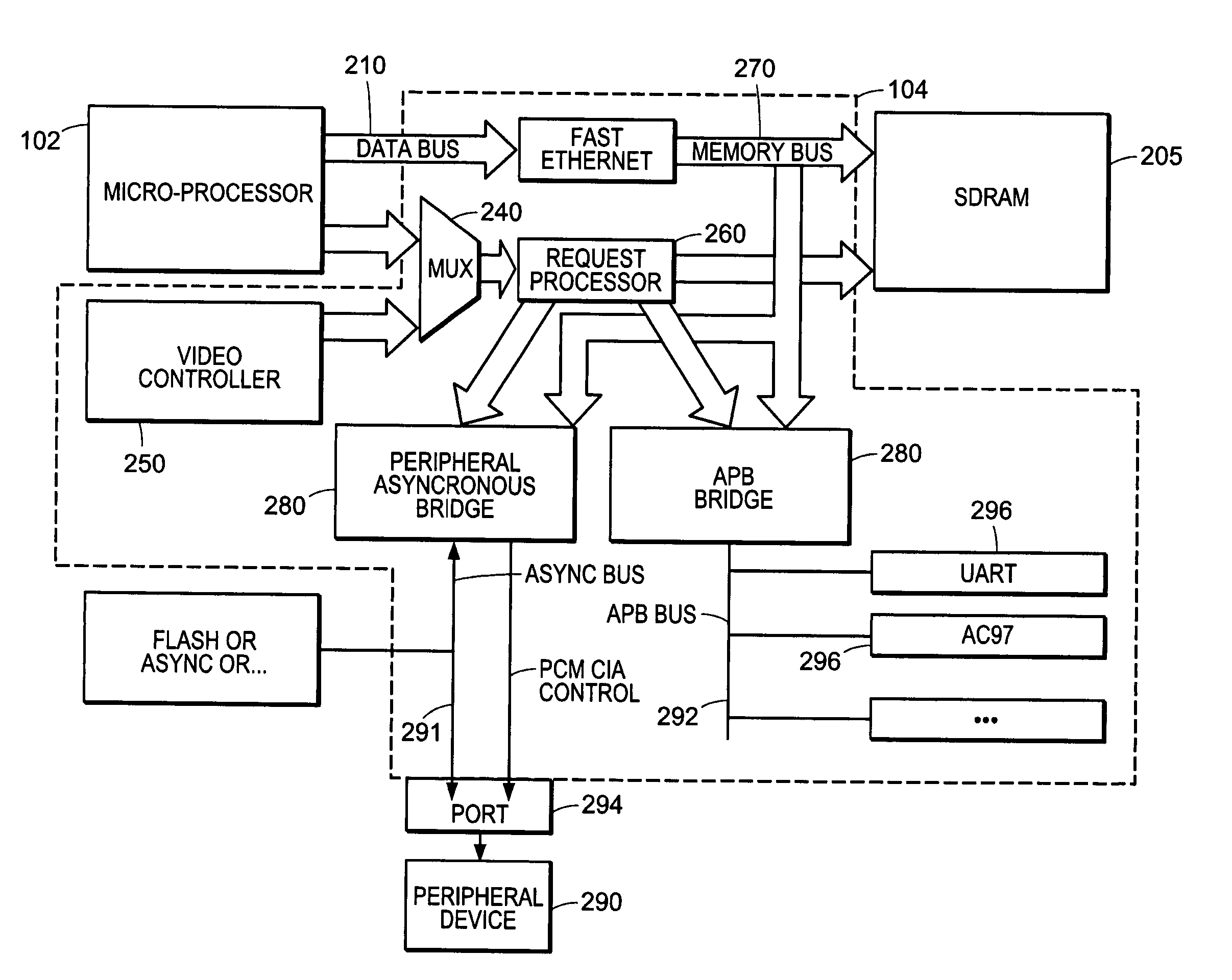

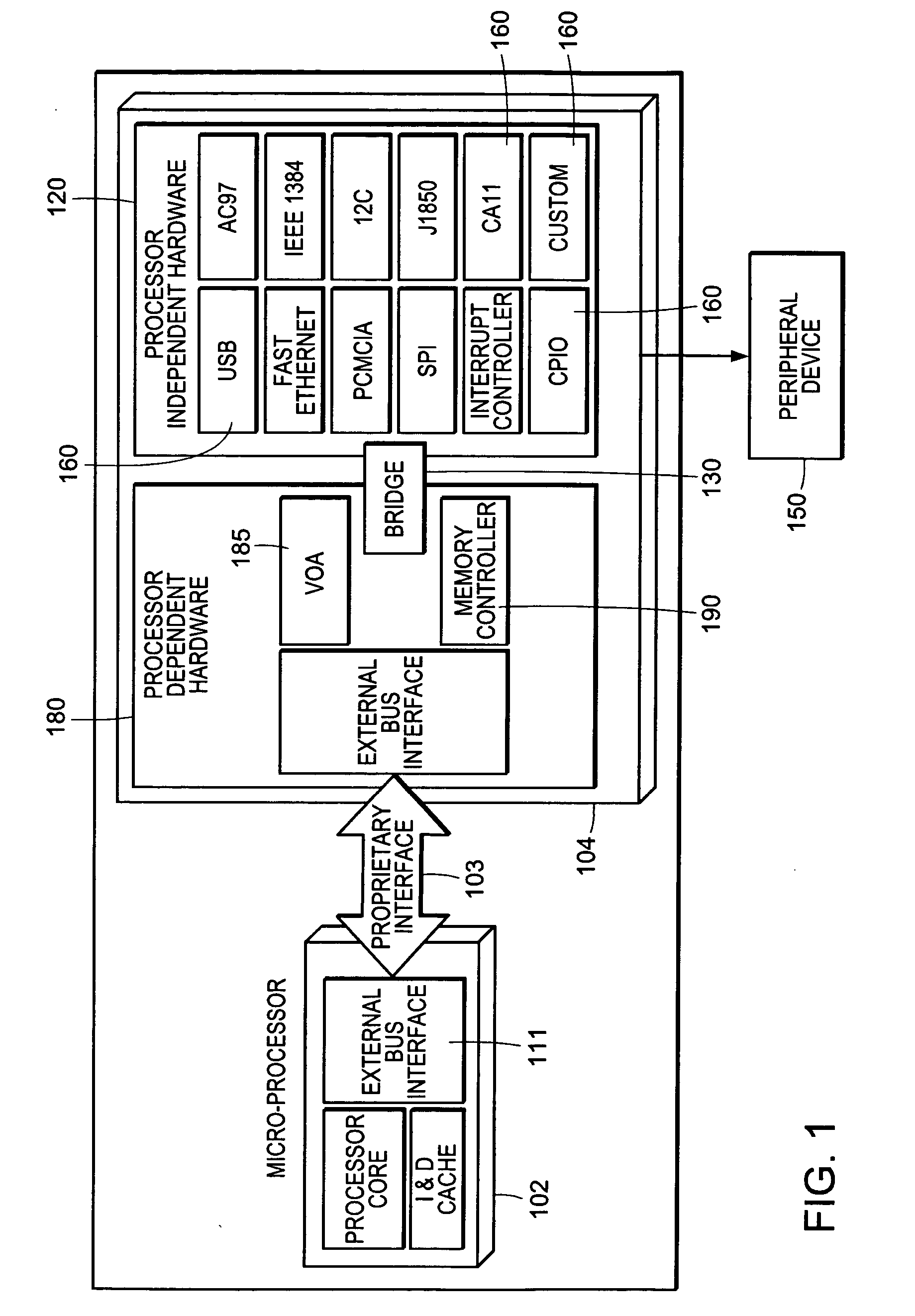

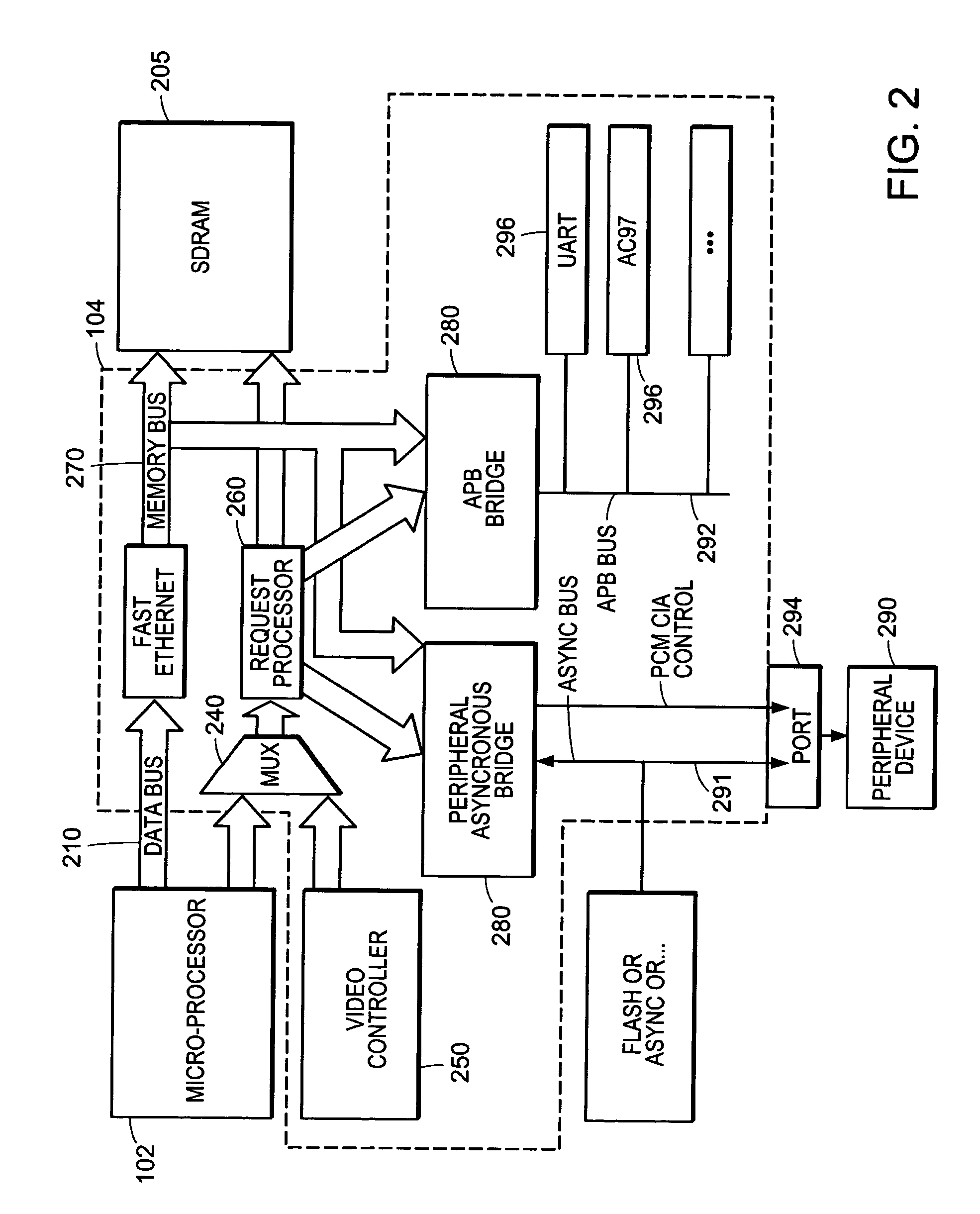

Customizable computer system

InactiveUS20040030861A1Architecture with single central processing unitElectric digital data processingFpga field programmable gate arrayProgrammable logic device

A customizable computing system, having a microprocessor and a programmable logic device coupled to the microprocessor via a dedicated bus. The programmable logic device includes a configuration to provide I / O functionality to the system and may be a field programmable gate array. The programmable logic device operates as both a north bridge and a south bridge as is understood by those of ordinary skill in the art. Requests are received from the microprocessor in the programmable logic device over the dedicated bus and are processor specific requests. The processor specific requests are translated into processor dependent commands by a bridge. After the processor specific requests are translated into processor dependent commands, the commands are forwarded to processor independent I / O structures which interface with both internal and external peripheral devices to the customizable computing system.

Owner:ACUNIA

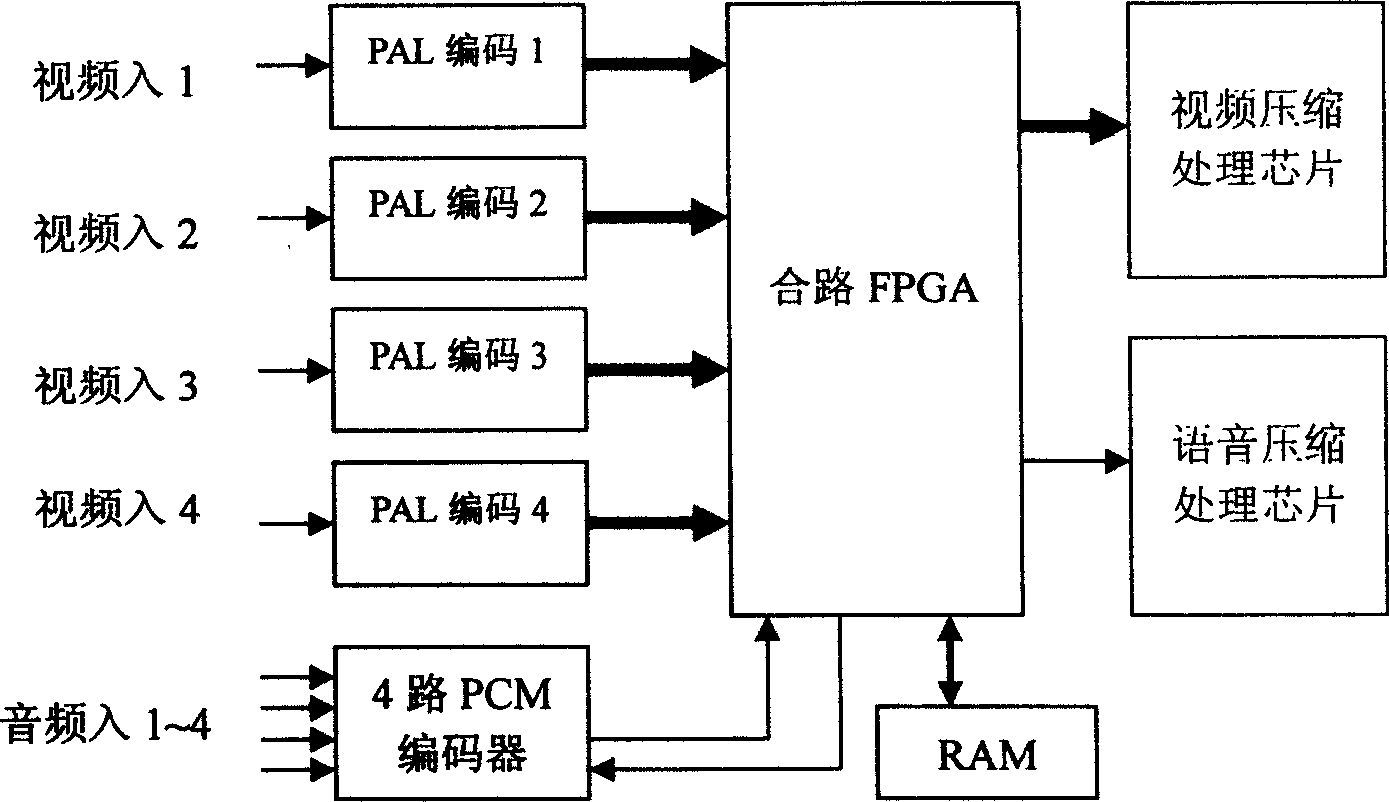

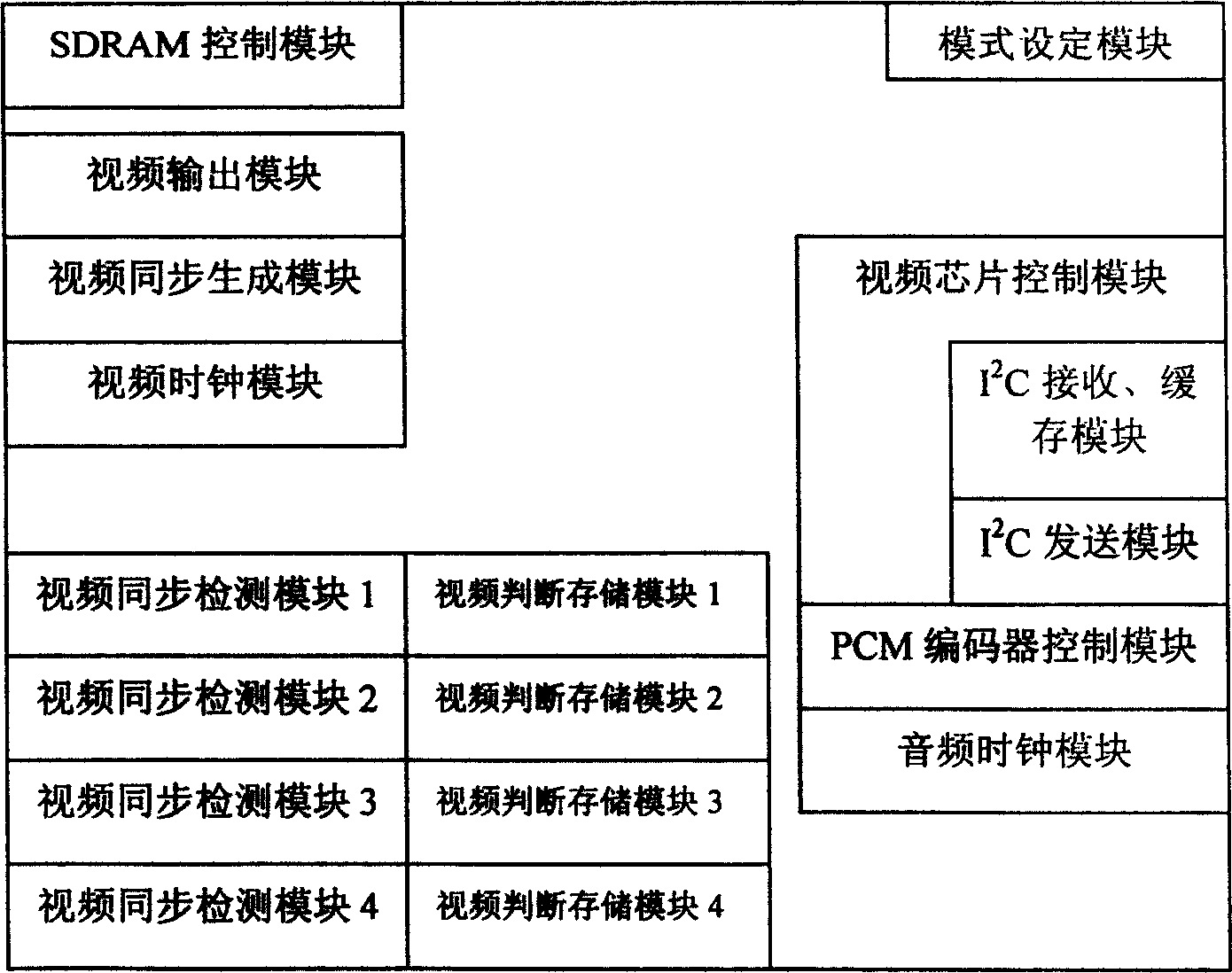

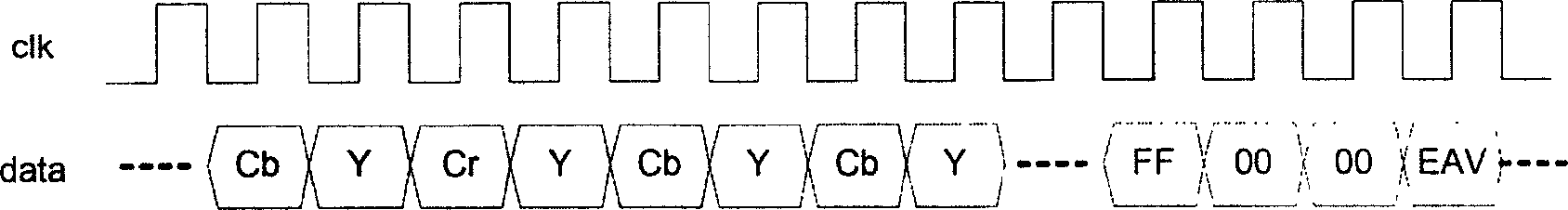

FPGA based four way audio-video multiplexing method

InactiveCN1645930ATroubleshoot input issuesIncrease profitTelevision systemsFpga field programmable gate arrayPAL

The method includes following steps: through PAL encode and decode chip and PCM speech coding chip, 4-ways video signals and 4-ways sound signals are inputted into FPGA chip for processing, and then implements 4-ways combination output of video and sound signal. The steps of signal processing are: the output format of video, input and output mode of clock and synchronous are set for 4-ways video and sound signals through mode setup module; then three branches are parallel processed; first branch is used in setting the register of video chip; second branch is used in combining 4-ways sound; third branch is used in combining 4-ways video.

Owner:JILIN UNIV

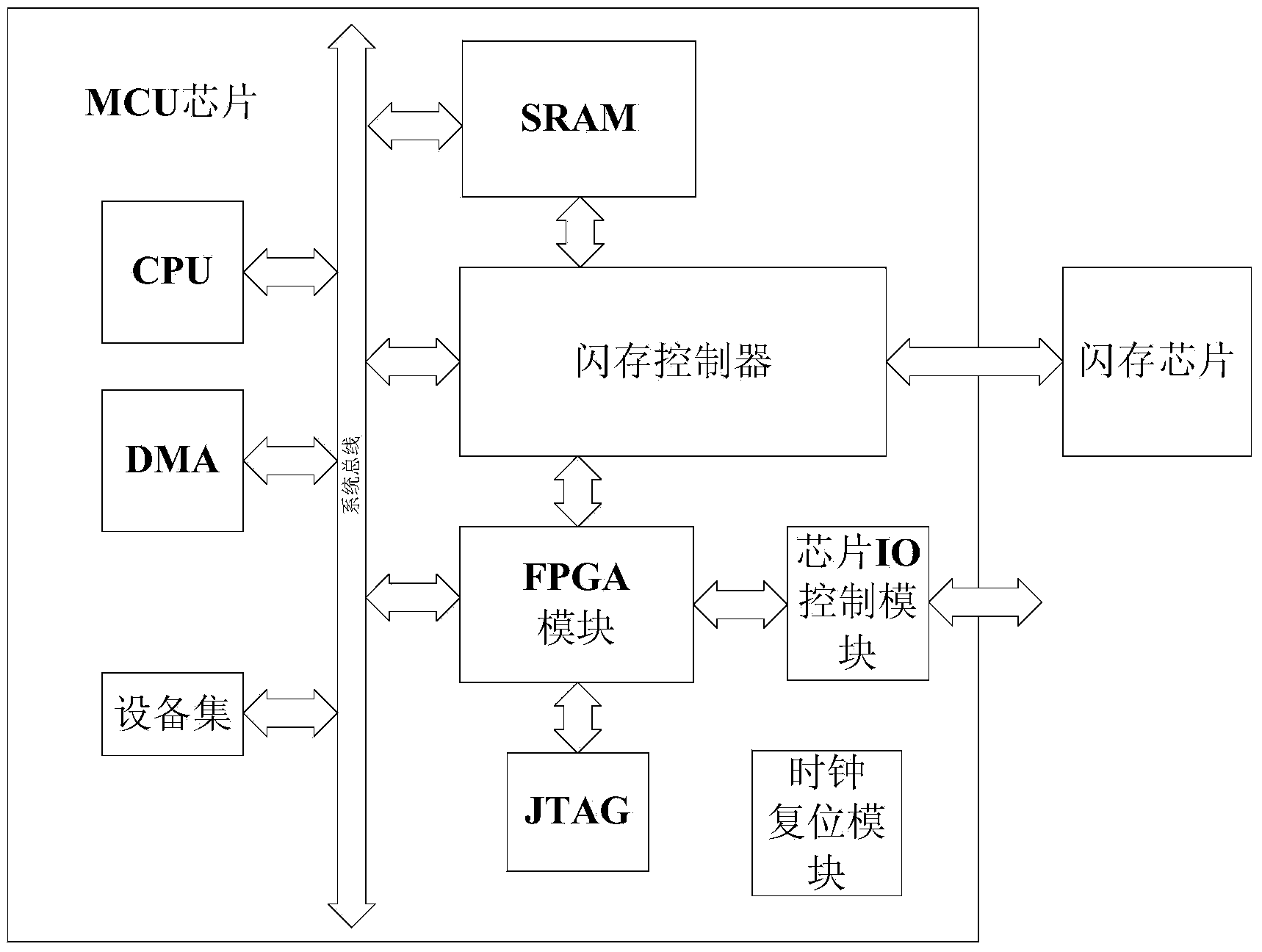

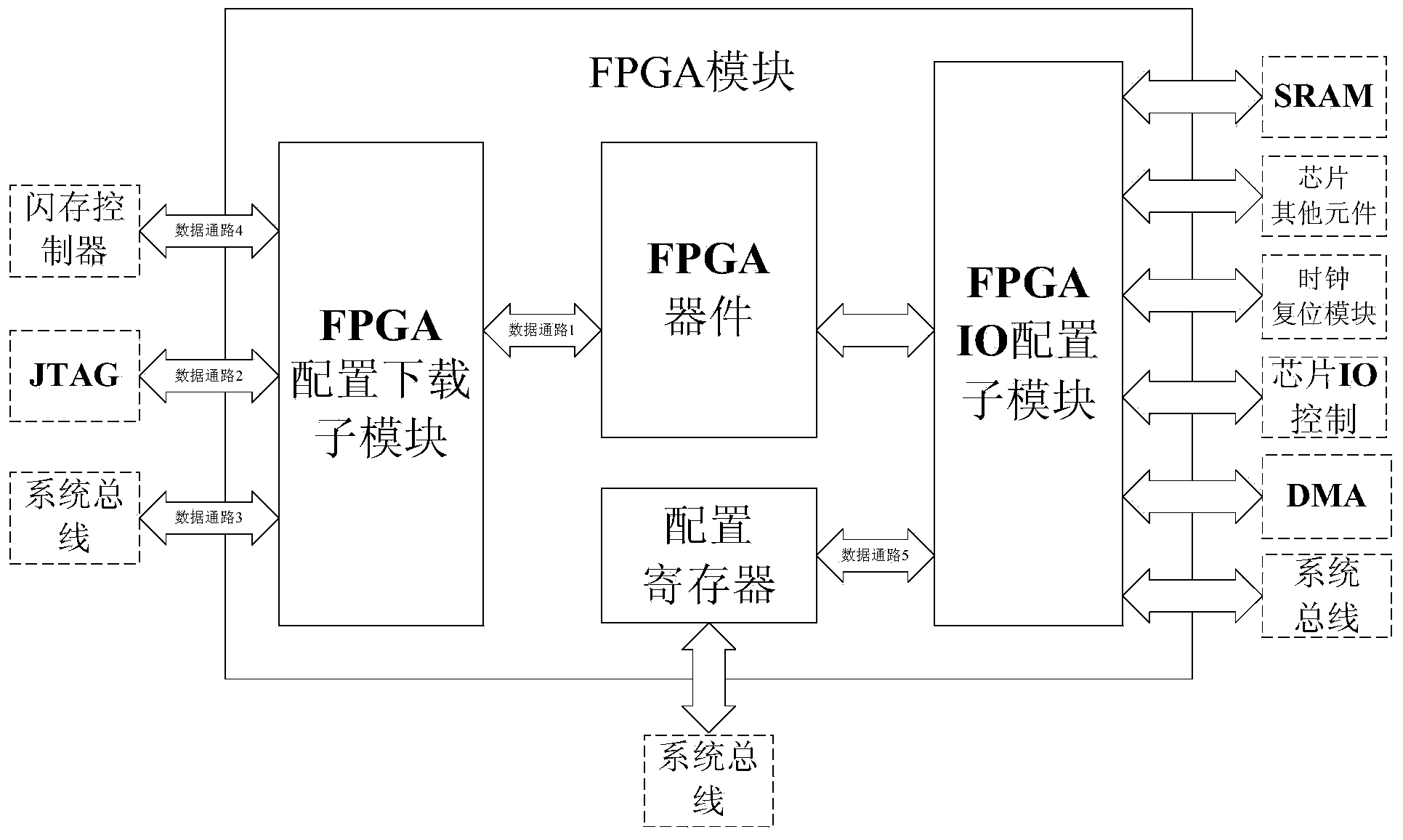

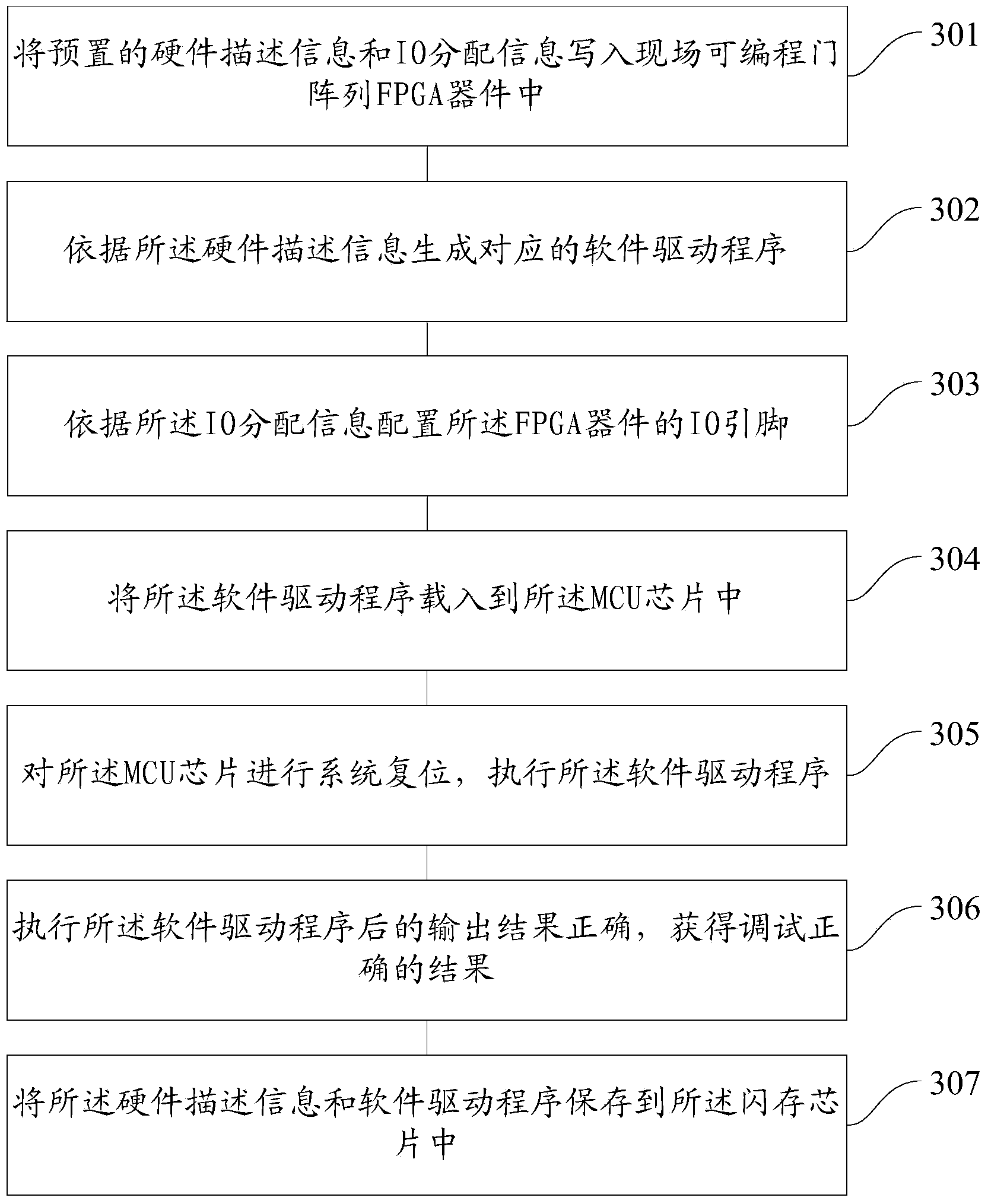

Method and device for debugging FPGA (field programmable gate array) in MCU (microprogrammed control unit) chip

ActiveCN104050068AReduce errorsGuaranteed accuracyFunctional testingFpga field programmable gate arrayData information

The embodiment of the invention provides a method and a device for debugging an FPGA (field programmable gate array) in an MCU (microprogrammed control unit) chip. The FPGA module is integrated into the MCU chip. The FPGA module comprises an FPGA device; the method comprises the steps of writing preset hardware description information and IO distribution information into the FPGA device; generating a corresponding software drive program according to the hardware description information; configuring IO pins of the FPGA device according to the IO distribution information; loading the software drive program into the MCU chip; performing system reset on the MCU chip and executing the software drive program. The right use of the FPGA in the MCU chip can be ensured, when data information has errors, the errors can be timely found and solved, so the FPGA can be normally used and the stability of the FPGA is improved.

Owner:GIGADEVICE SEMICON (BEIJING) INC

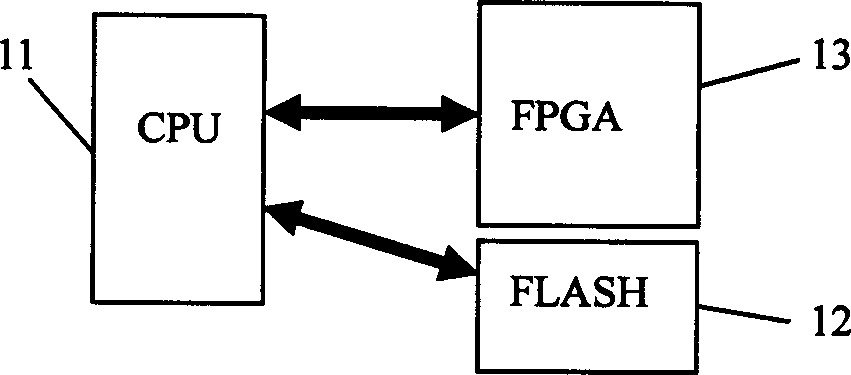

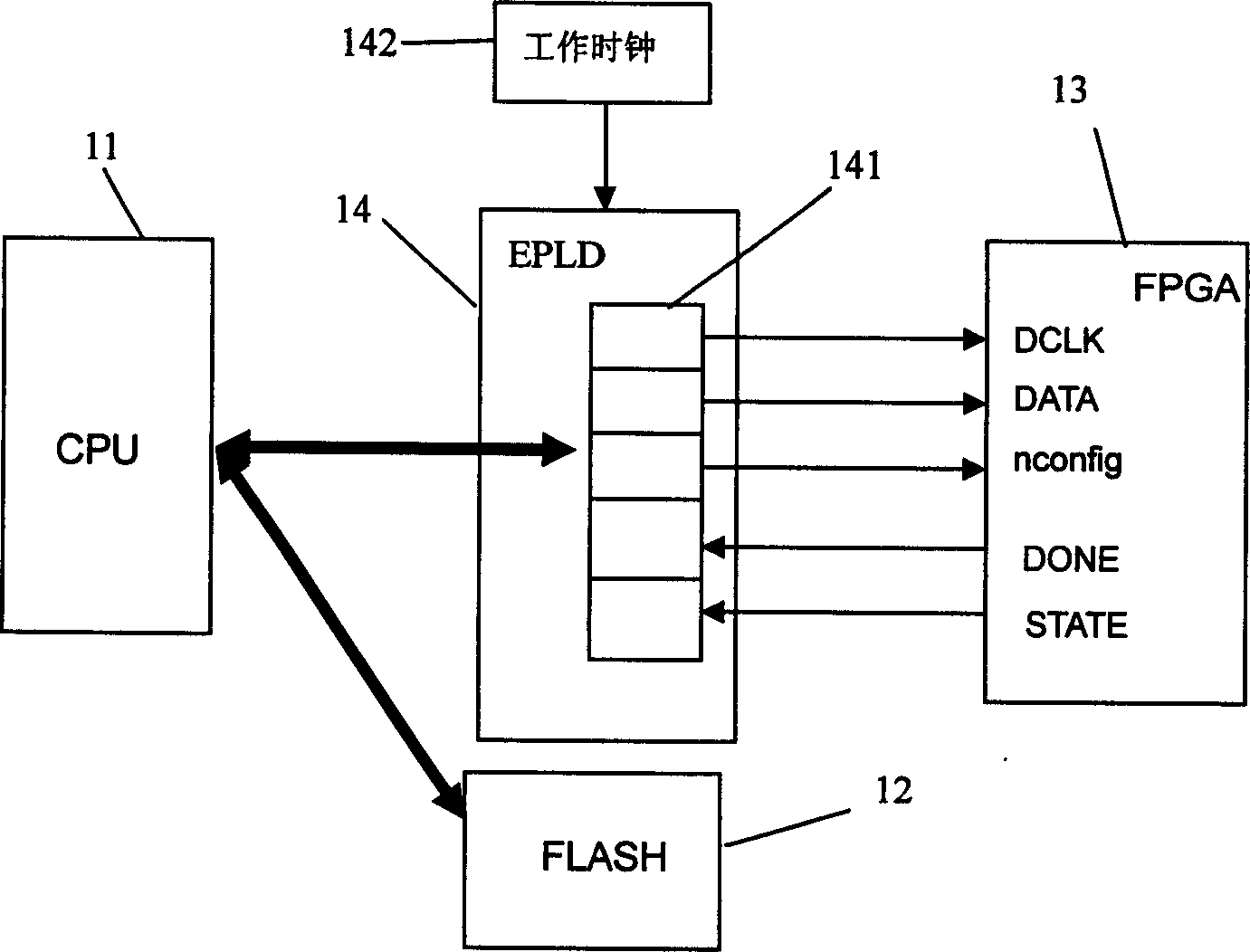

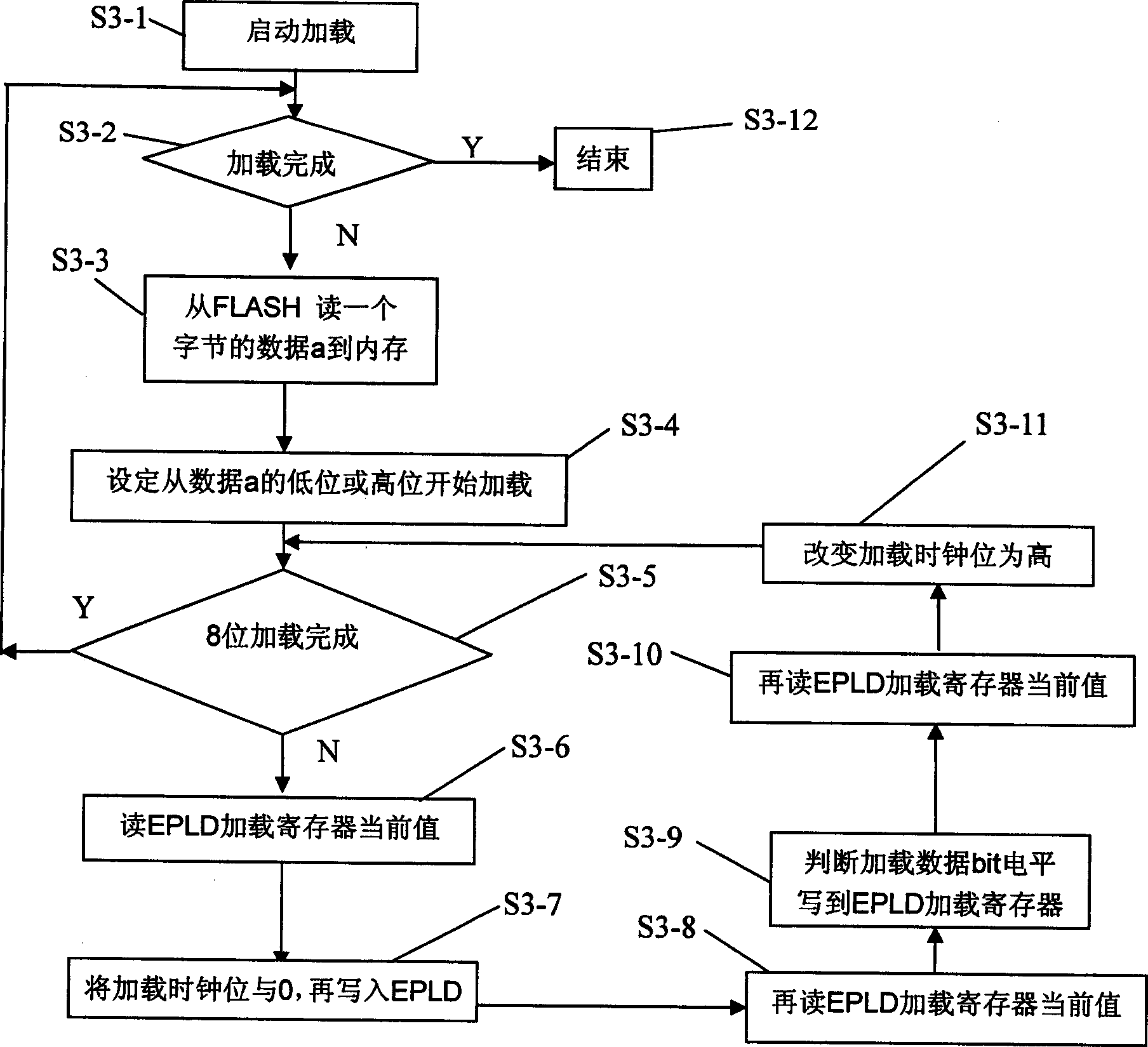

Field programmable gate array loading method

InactiveCN1808374AReduce the number of operationsImprove loading timeSpecific program execution arrangementsMemory systemsFpga field programmable gate arrayLoad time

Disclosed is a method for loading field programmable gate array, which comprises steps of: placing EPLD between CPU and FPGA; S5-1: starting to load; S5-2: detecting whether the loading is over or not, that is, stopping loading by judging the DONE signal of FPGA as end, and when judging the DONE signal of being not over, executing following steps: S5-3íóS5-4: Writing one byte data needed for loading into the loading data register of the EPLD once by CPU; S5-5: completing the loading of needed data to the FPGA by the internal logic of the EPLD; S5-6: delaying some time; repeating the S5-2 to S5-6 until finishing loading.

Owner:HUAWEI TECH CO LTD

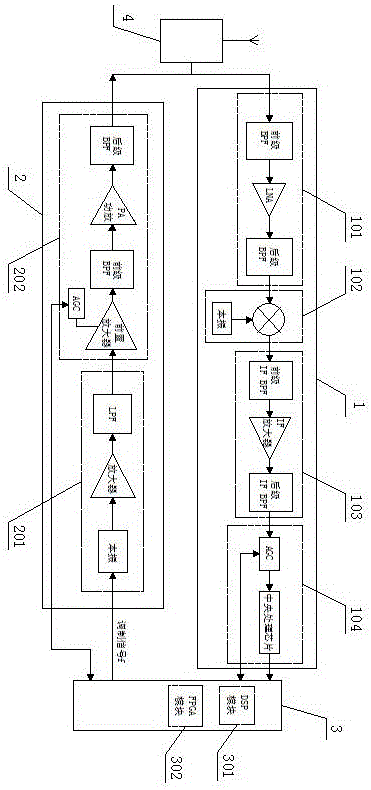

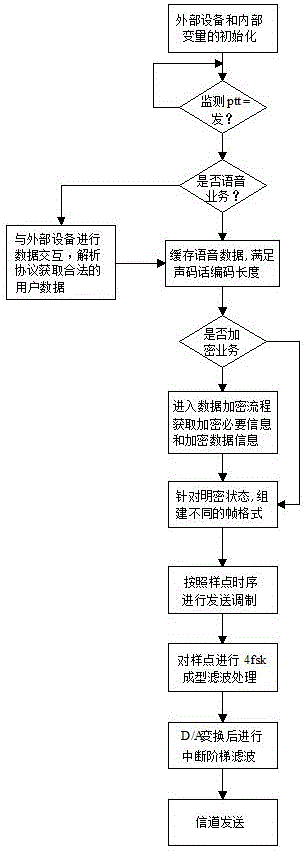

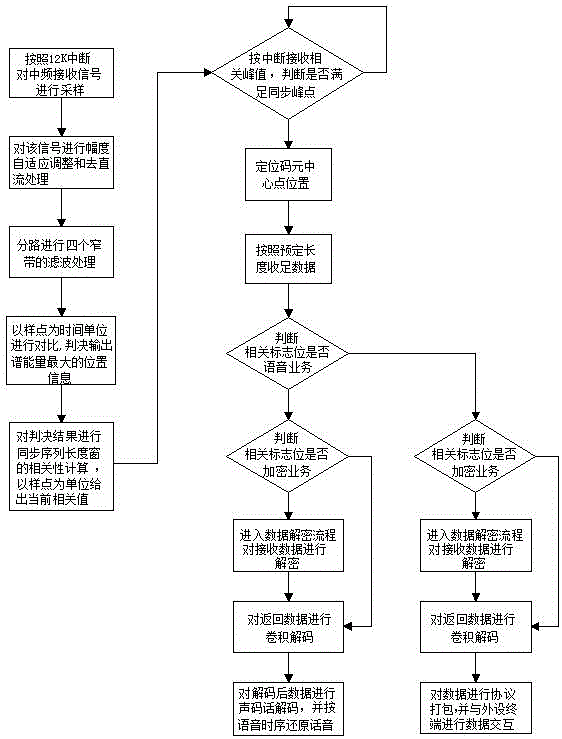

Maritime ultra-short wave beyond visual range communication device

InactiveCN106130595AImprove emission efficiencyReduce multipath interferenceTransmissionFpga field programmable gate arrayDigital signal processing

The invention relates to a maritime ultra-short wave beyond visual range communication device, and belongs to the technical field of the communication device. The device is composed of a radio frequency receiving unit, a radio frequency transmitting unit, a baseband unit and so on. The device is characterized in that an antenna is connected with the radio frequency transmitting unit and the radio frequency receiving unit through an electronic switch. The radio frequency transmitting unit and the radio frequency receiving unit are connected with the baseband unit. The radio frequency transmitting unit is composed of an excitation module and a power module. The radio frequency receiving unit is composed of a radio frequency front end module, a frequency conversion module, an intermediate frequency amplification unit and an intermediate processing module. The baseband unit is composed of a DSP digital signal processing unit, an FPGA field-programmable gate array module. The device has the advantages that the noise coefficient is low, the sensitivity is high, the dynamic range is wide, the low signal to noise ratio demodulation is accurate, the multi-path interference of remote communication can be reduced, the maritime beyond visual range communication distance is long, the communication quality is good, and the existing problems that the multi-path interference of the remote transmission is serious, the noise interference is high, the beyond visual range communication cannot be realized, and the maritime beyond visual range communication quality is influenced are solved.

Owner:湖北广兴通信科技有限公司

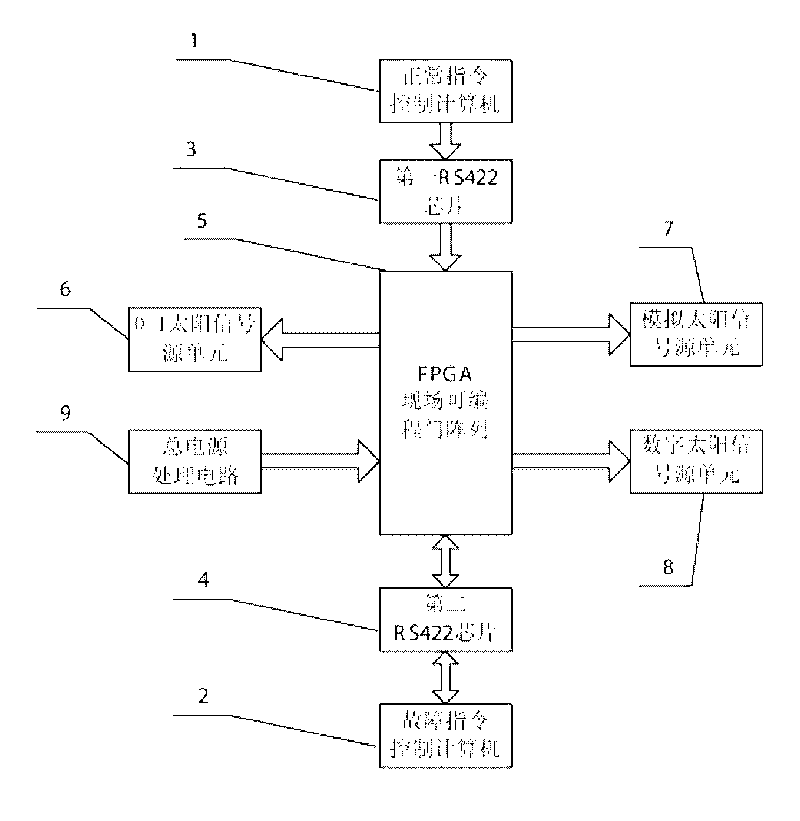

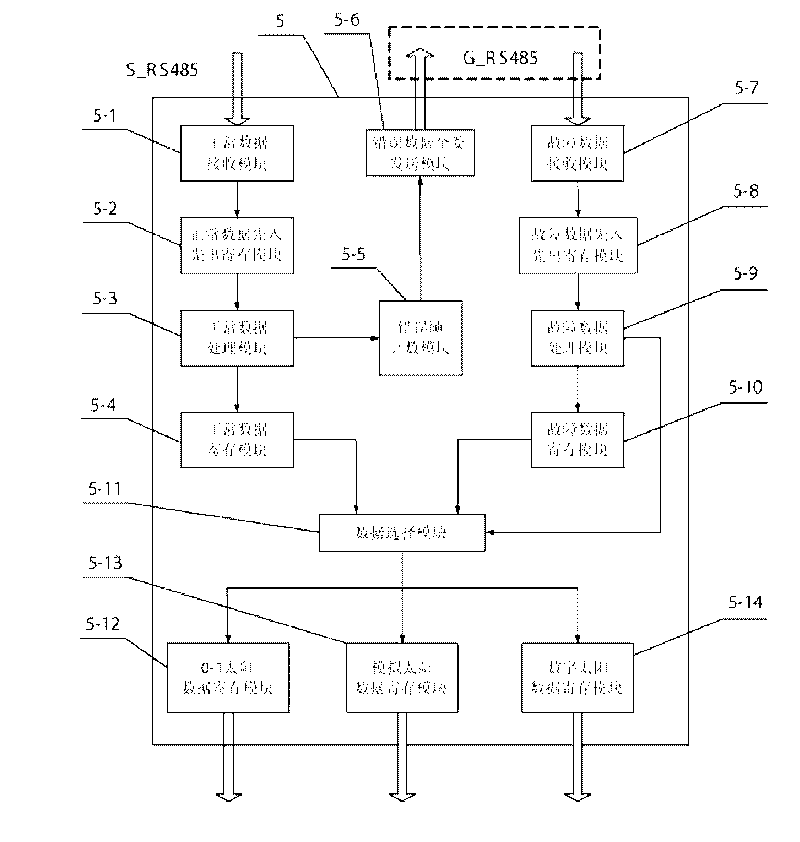

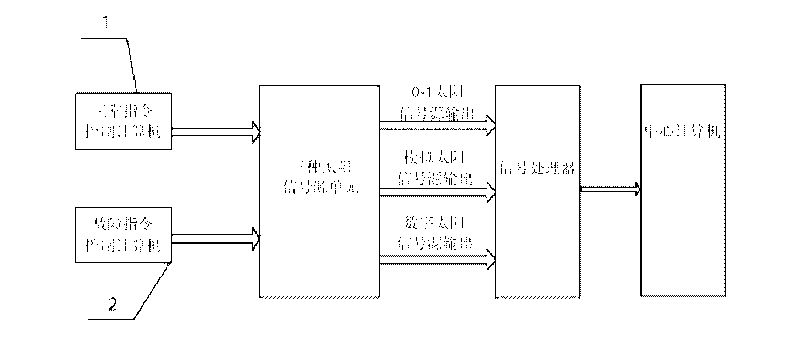

Sun sensor simulator for satellite closed cycle simulation test

InactiveCN101726299AShorten the development cycleReduce development costsInstruments for comonautical navigationFpga field programmable gate arrayData selection

The invention relates to a sun sensor simulator for satellite closed cycle simulation test, belonging to the field of satellite test; the sun sensor simulator simulates the signal output of three kinds of the sun sensors simultaneously; a normal instruction control computer and a fault instruction control computer transmit a normal work instruction and a fault work instruction to a FPGA field programmable gate array, a module in the FPGA field programmable gate array receives and processes the two instructions respectively, a data selection module ensures the preferential execution of the fault work instruction, and an error frame counting module counts the number of the fault work instructions in the normal work instruction and transmits to the fault instruction control computer, and the FPGA field programmable gate array outputs control data to a 0-1 sun signal source unit, a simulation signal source unit and a digital sun signal source unit respectively to lead the corresponding sun signal source unit to output the current. The sun sensor simulator is applied to the satellite closed cycle simulation test.

Owner:HARBIN INST OF TECH

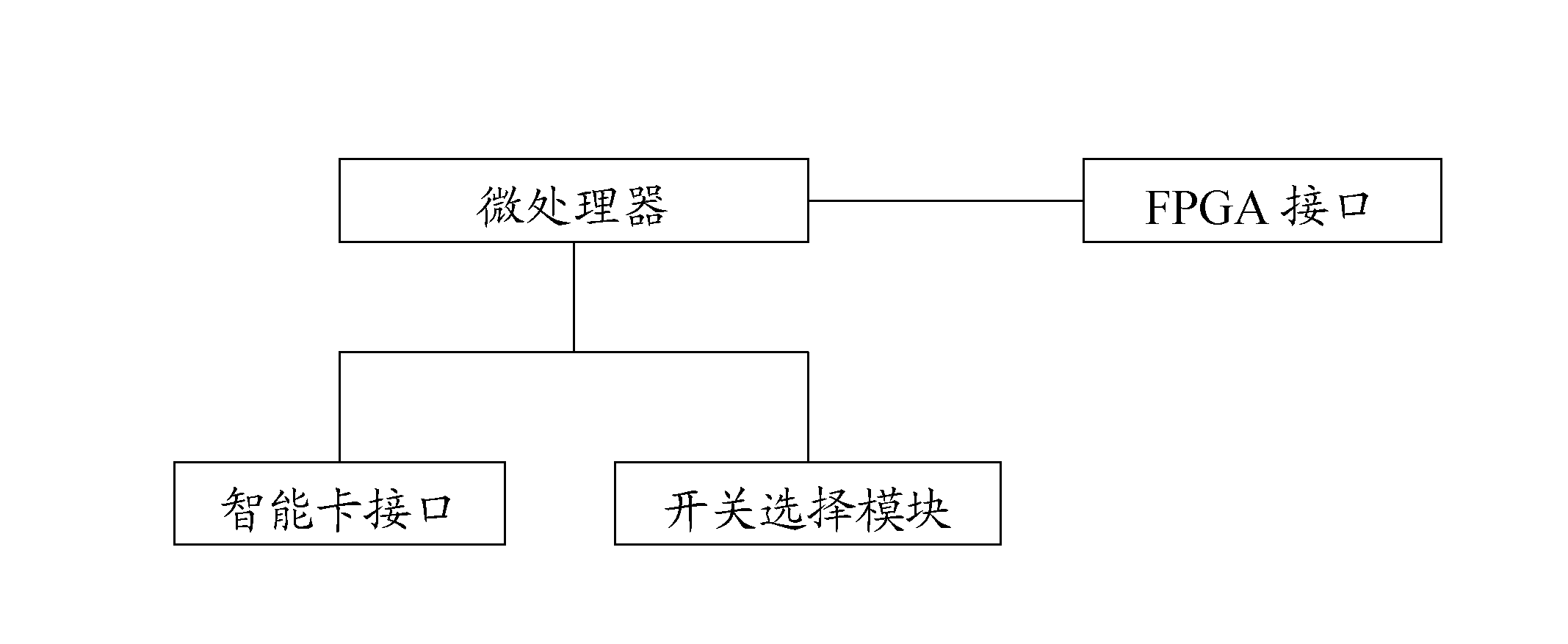

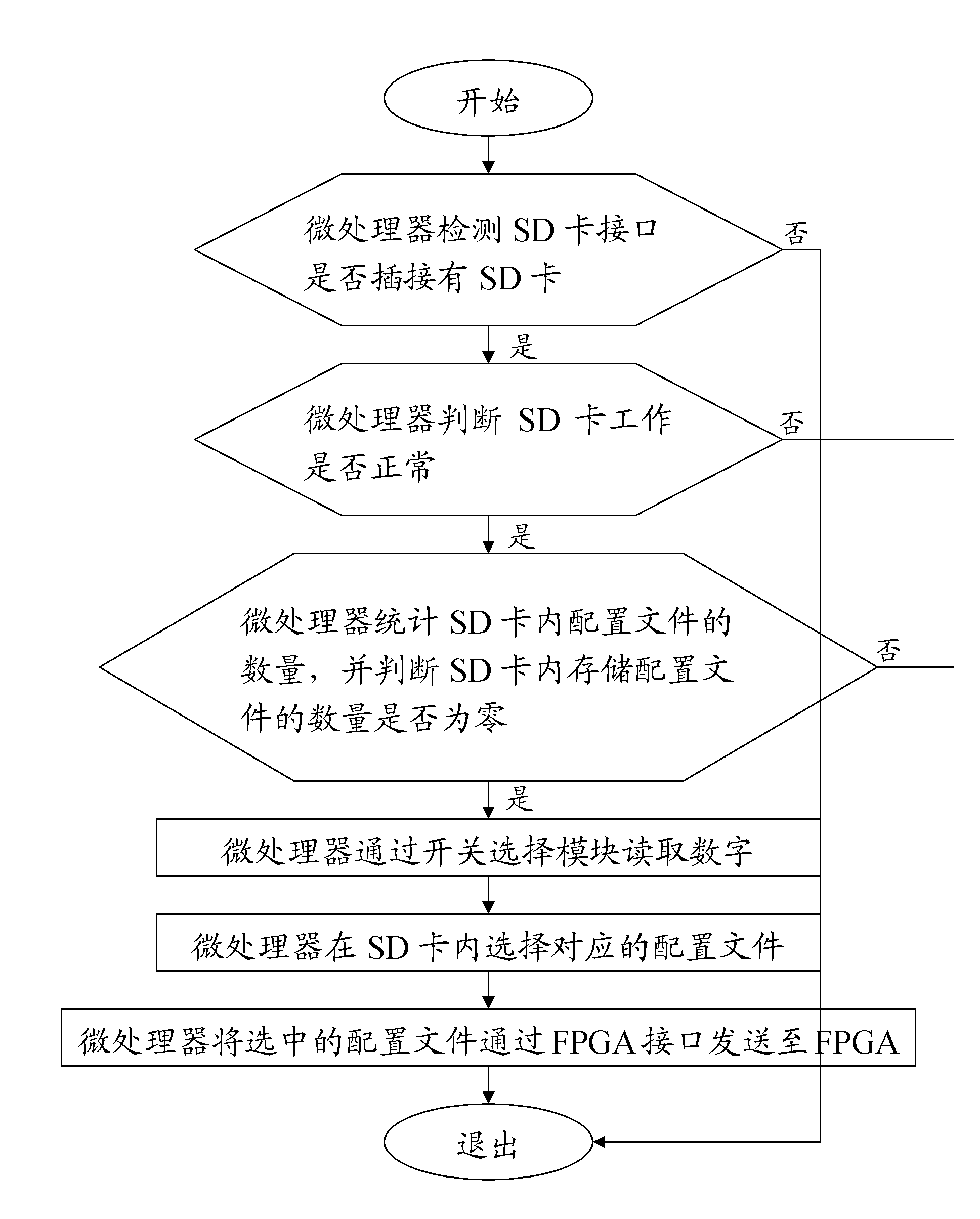

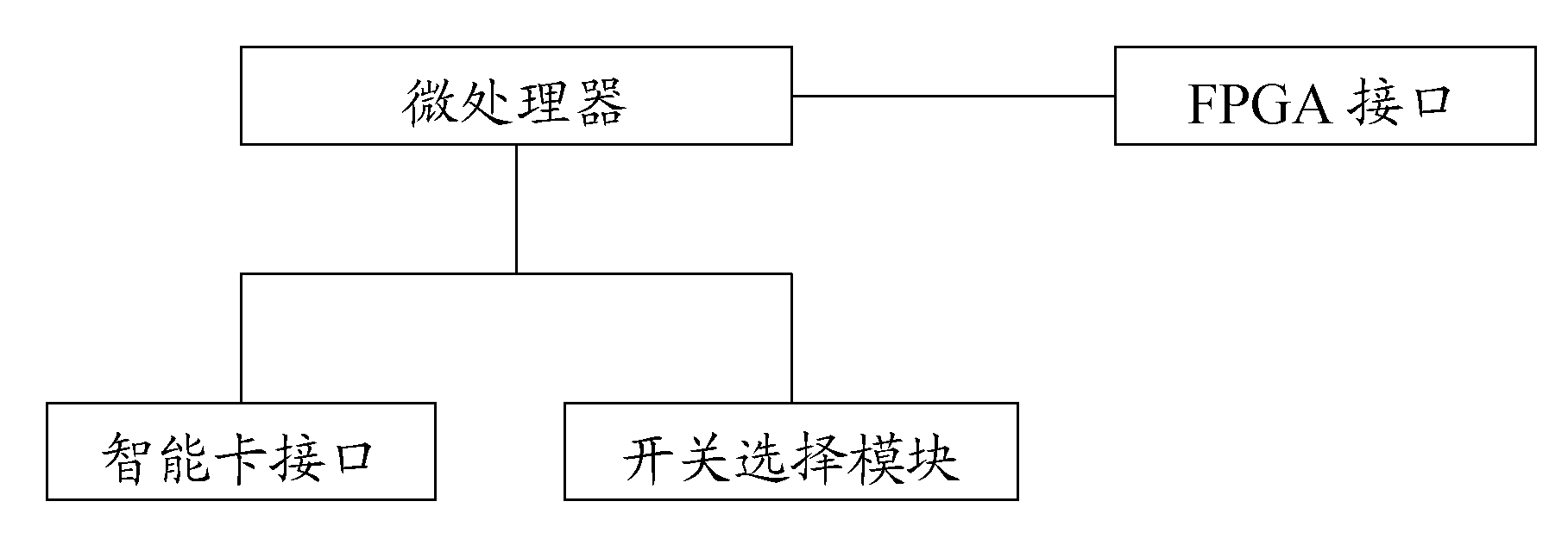

Field-programmable gate array (FPGA) configuration device and configuration method

InactiveCN102306107AEasy to replaceSolve development problemsCAD circuit designProgram loading/initiatingFpga field programmable gate arrayComputer module

The invention relates to a field-programmable gate array (FPGA) configuration device, which is used for sending a configuration file stored in an intelligent card to an FPGA. The FPGA configuration device comprises a microprocessor, an FPGA interface which is connected with the microprocessor, an intelligent card interface which is connected with the microprocessor and used for the intelligent card to insert, and a switch selection module which is connected with the microprocessor and used for reading an input number, wherein the microprocessor performs data transmission with the intelligent card through the intelligent card interface, selects the configuration file corresponding to the number in the intelligent card according to the number read by the switch selection module, and sends the selected configuration file to the FPGA through the FPGA interface. The invention also provides an FPGA configuration method. By the device and the method, cost is saved, and development and verification efficiency is improved.

Owner:IPGOAL MICROELECTRONICS (SICHUAN) CO LTD

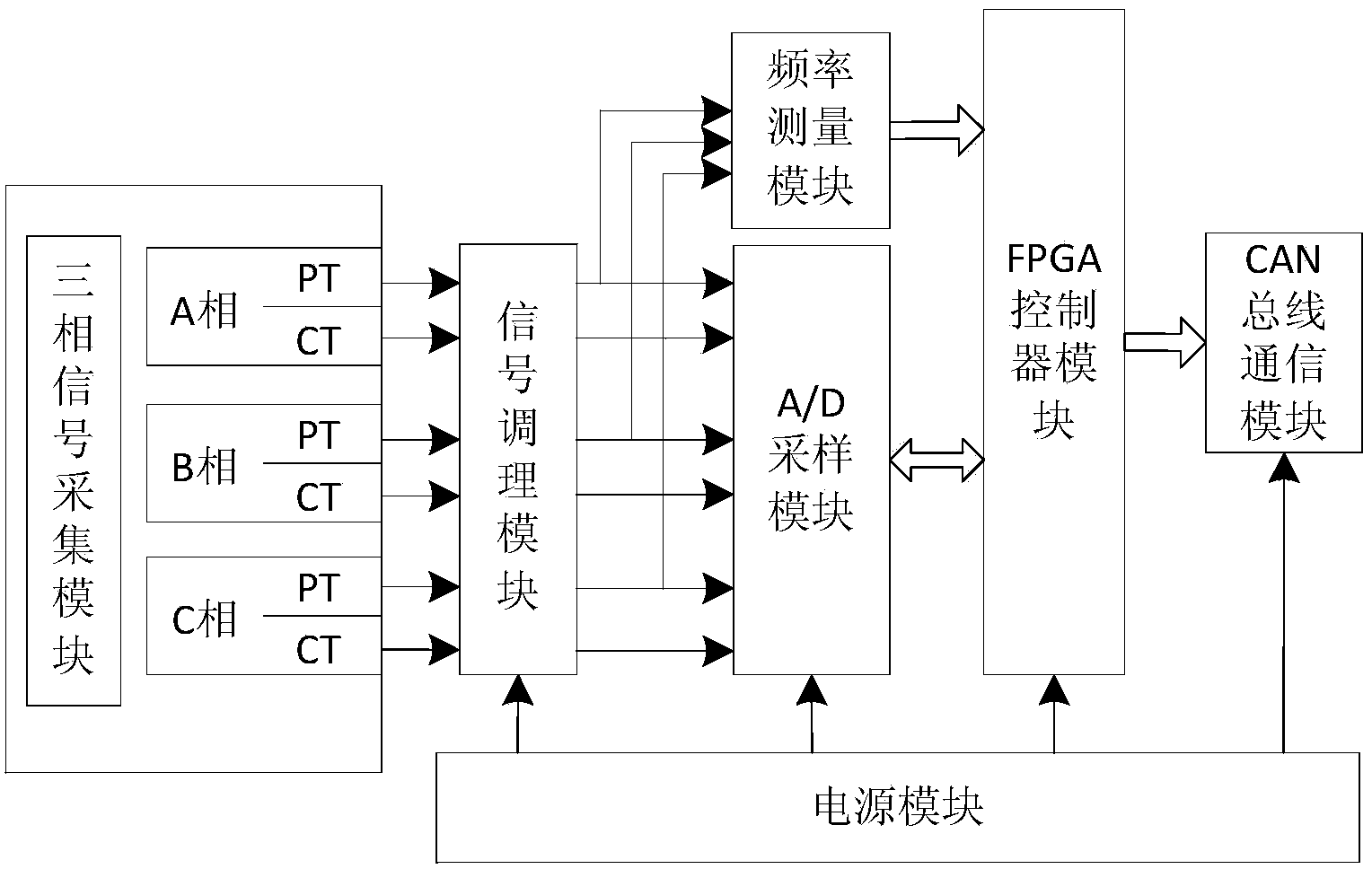

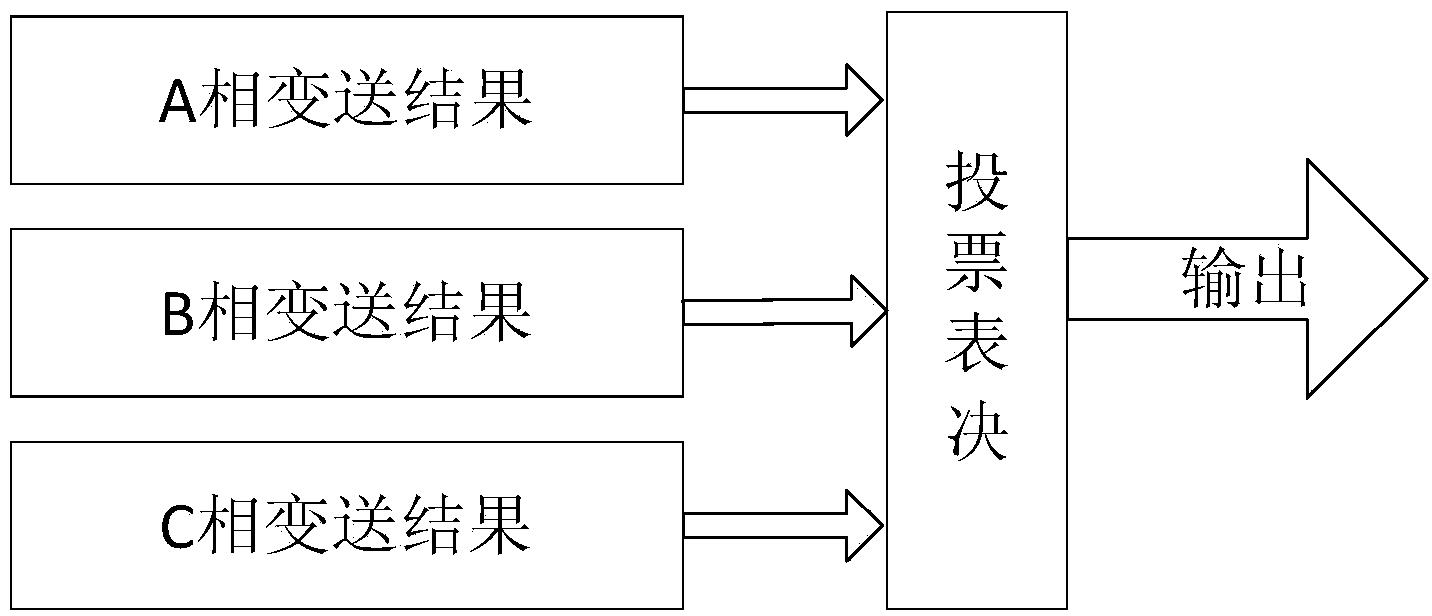

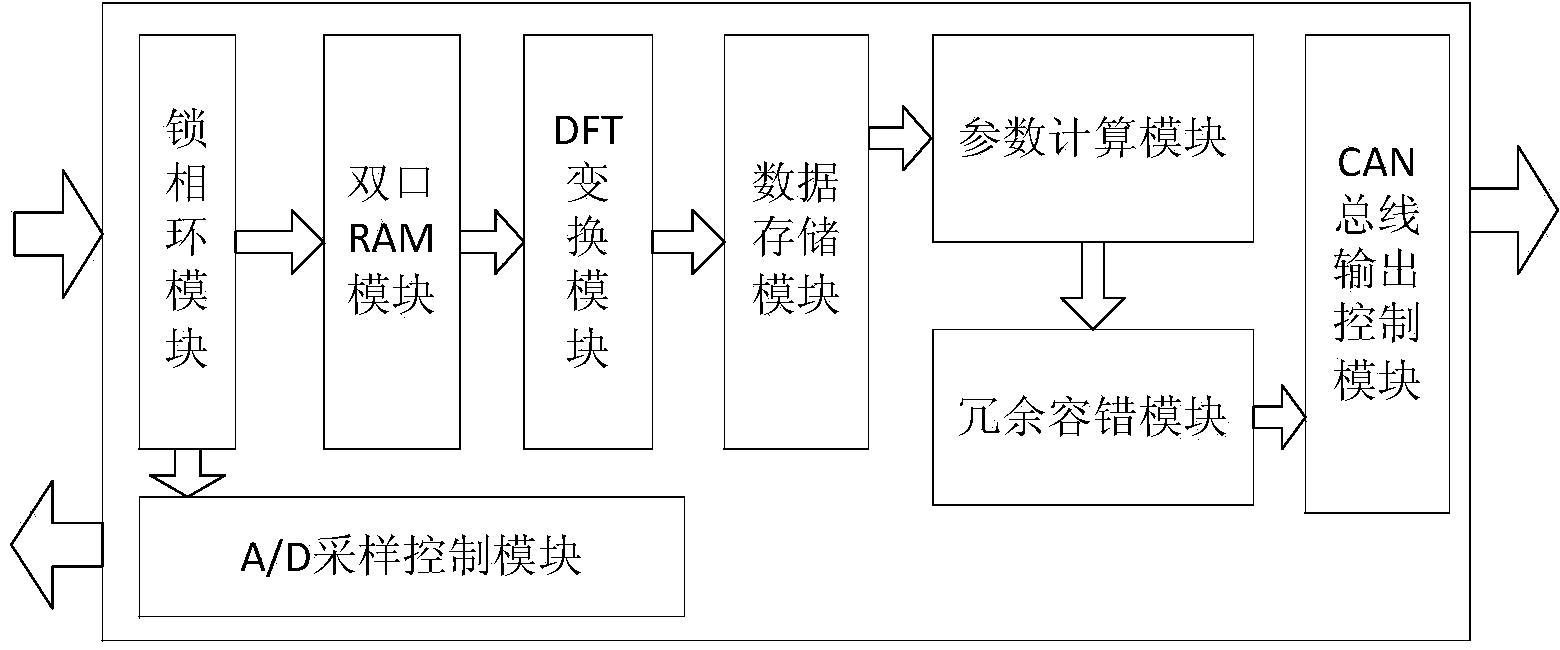

Electrical quantity transducer

ActiveCN103837738AHighlight substantive featuresAccurate outputElectrical measurementsFpga field programmable gate arrayFault tolerance

The invention discloses an electrical quantity transducer, and relates to a data processing device particularly suitable for achieving specific functions, in particular to an electrical quantity transducer with a fault tolerance function. The electrical quantity transducer is designed based on the FPGA according to the triple-module redundancy technology and comprises a three-phase signal acquisition module, a signal conditioning module, an A / D sampling module, a frequency measurement module, an FPGA controller module, a CAN bus communication module and a power module. The electrical quantity transducer overcomes the defect that an error in any single-phase transduction process of an existing electrical quantity transducer will directly result in inaccuracy of a final transduction result, open loops of a system or misoperation of equipment is caused and consequently breakdown of the whole system happens.

Owner:HEBEI UNIV OF TECH

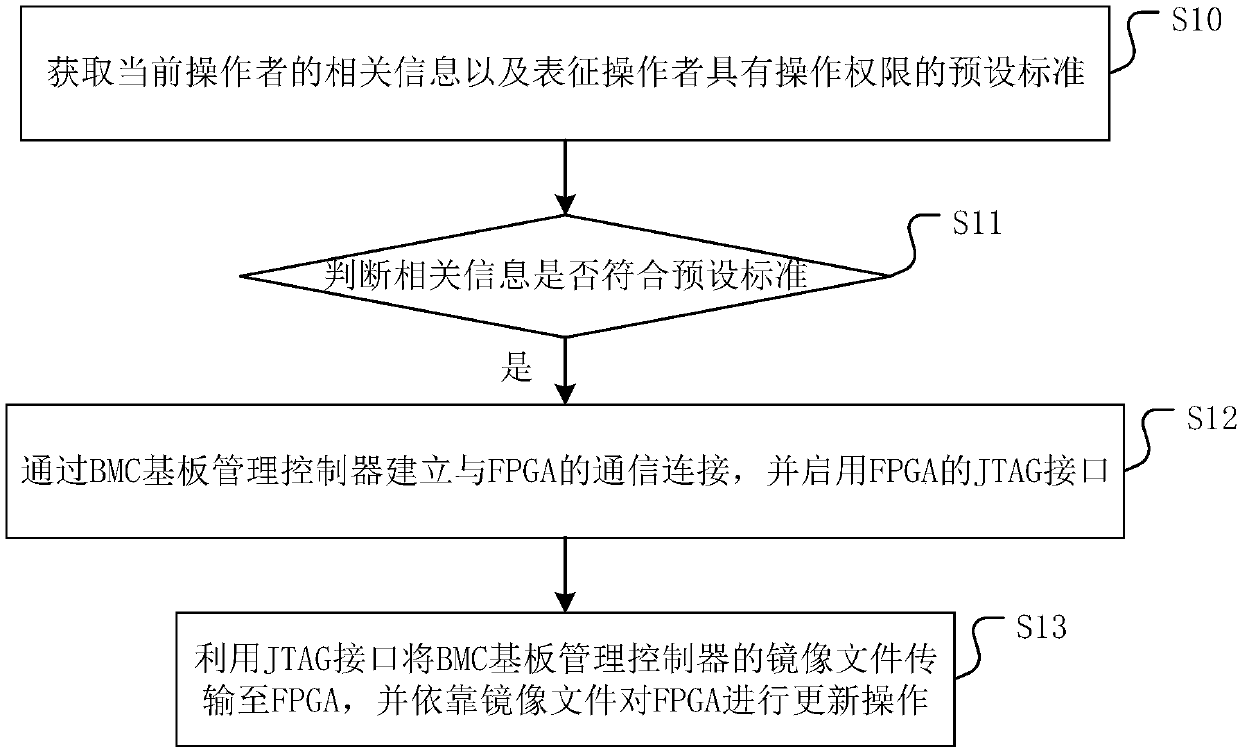

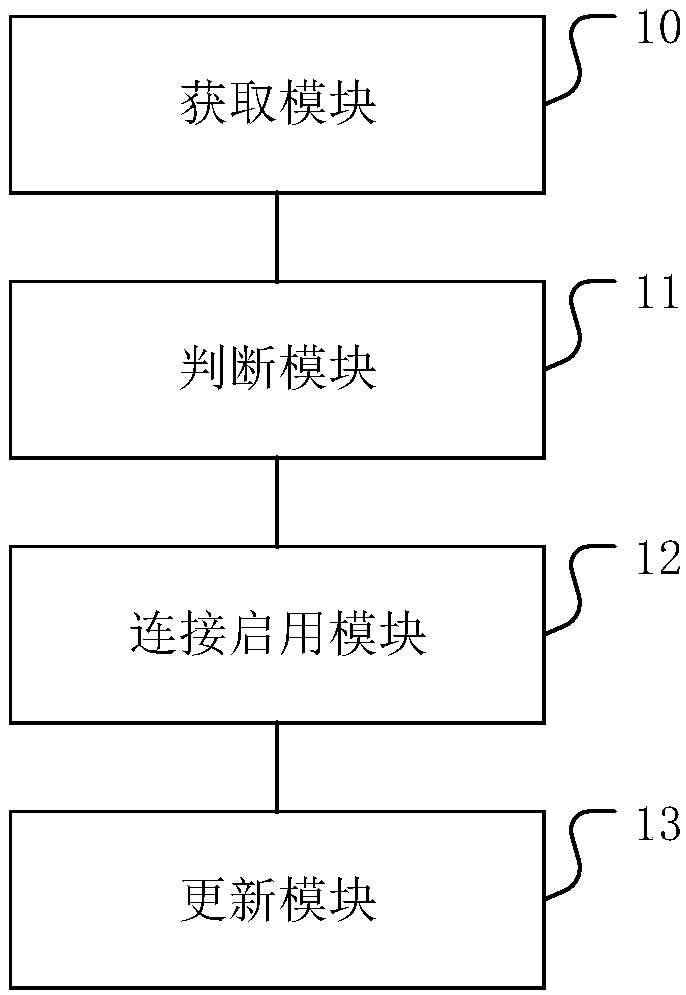

FPGA (field programmable gate array) firmware update method, FPGA firmware update device and medium

InactiveCN107608700AIncrease flexibilityEasy to operateVersion controlSoftware deploymentFpga field programmable gate arrayOperability

The invention discloses an FPGA (field programmable gate array) firmware update method, an FPGA firmware update device and a medium. The method includes acquiring related information of a current operator and preset standards representing the operator has operating authorization; judging whether or not the related information meets the preset standards; if yes, establishing communication connection with an FPGA by a BMC substrate management controller, and initiating a JTAG interface of the FPGA; transmitting mirror image documents of the BMC substrate management controller to the FPGA throughthe JTAG interface, and updating the FPGA by the mirror image documents. The FPGA firmware update method, the FPGA firmware update device and the medium have the advantages that flexibility and operability in FPGA firmware update are improved while FPGA firmware safety is improved.

Owner:INSPUR BEIJING ELECTRONICS INFORMATION IND

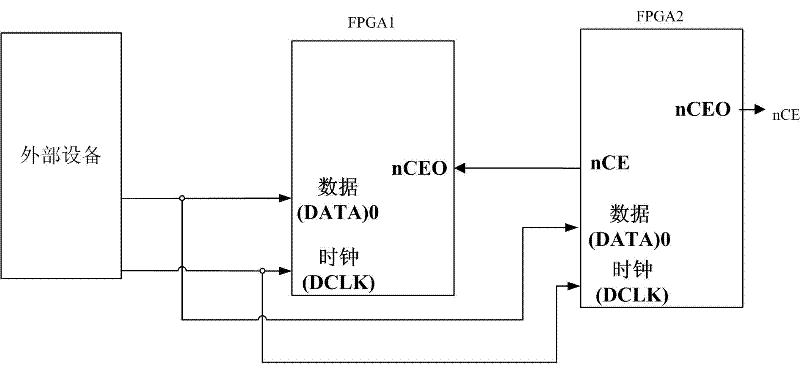

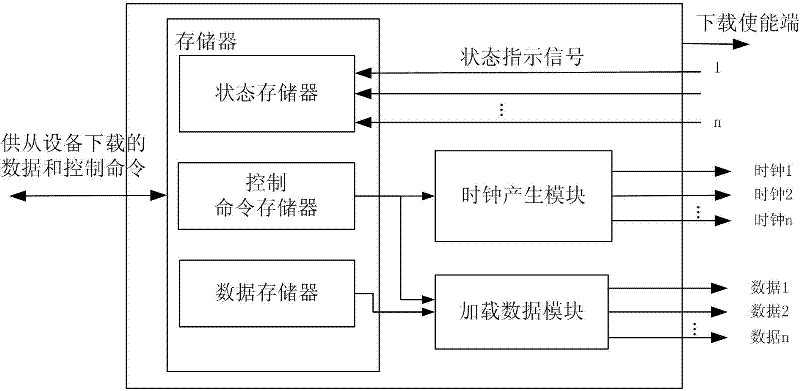

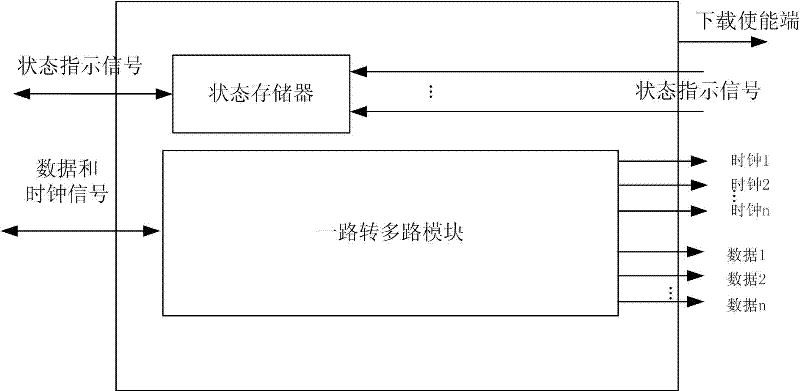

Method and device for supporting field programmable gate arrays (FPGA) to download data

ActiveCN102200955AAvoid the problem of incomplete signalSave download timeProgram loading/initiatingFpga field programmable gate arrayComputer science

The invention provides a method and a device for supporting a plurality of field programmable gate arrays (FPGA) to download data, and the FPGAs. The method comprises the following steps that: a master FPGA concurrently transmits clock signals and the data to n slave FPGAs, wherein n is an integer bigger than 1. By adoption of the technical scheme of the invention, the completeness of the signal can be guaranteed during the shortening of time required by data downloading of the plurality of slave FPGAs.

Owner:ZTE CORP

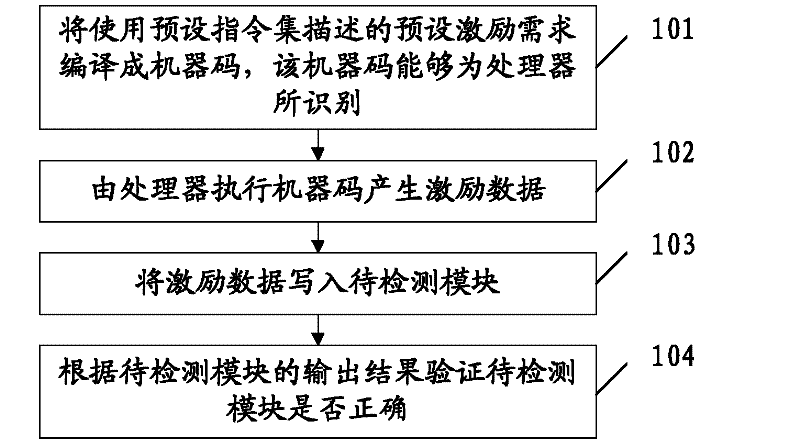

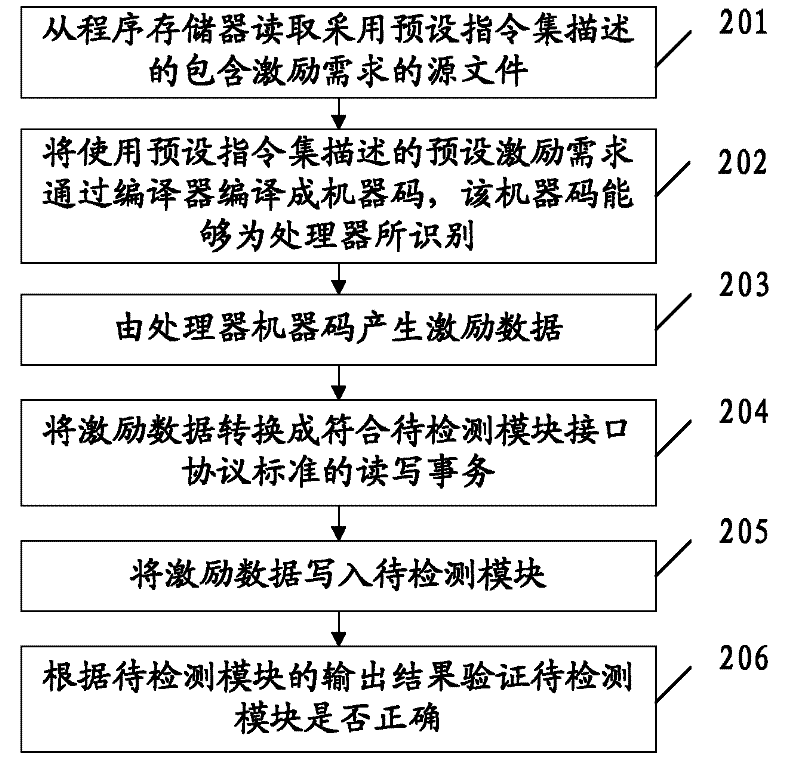

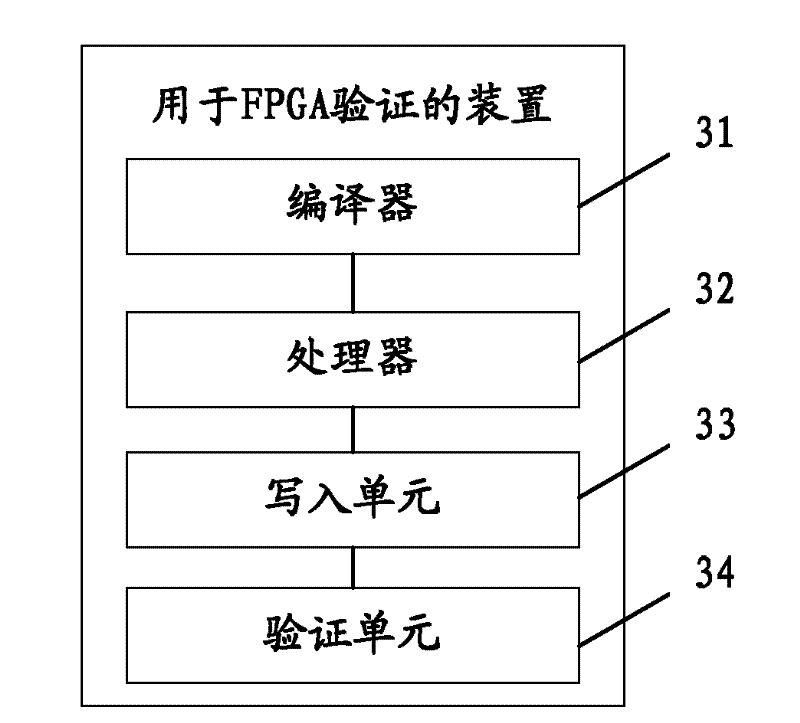

Method and device for checking field programmable gate array (FPGA)

InactiveCN102201022AOvercoming the need for incentives problemImprove versatilitySpecial data processing applicationsFpga field programmable gate arrayIntellectual property

The embodiment of the invention discloses a method and a device for checking a field programmable gate array (FPGA) and relates to the field of integrated circuit design. Various intellectual property (IP) core checking requirements can be met and the universality is high. The method comprises the following steps of: compiling a preset exciting demand into a machine code, wherein the preset exciting demand is described by using a preset instruction set and the machine code can be identified by a processor; executing the machine code by the processor and generating exciting data; inputting the exciting data into a module to be detected; and checking whether the module to be detected is correct according to an output result of the module to be detected. The invention is mainly applied to checking the FPGA.

Owner:HISENSE HIVIEW TECH CO LTD

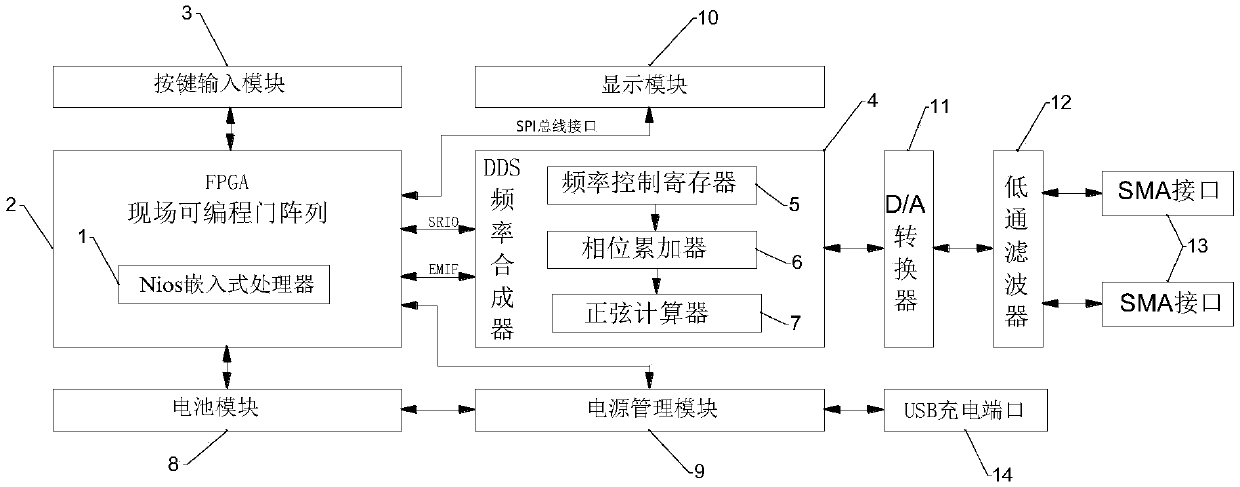

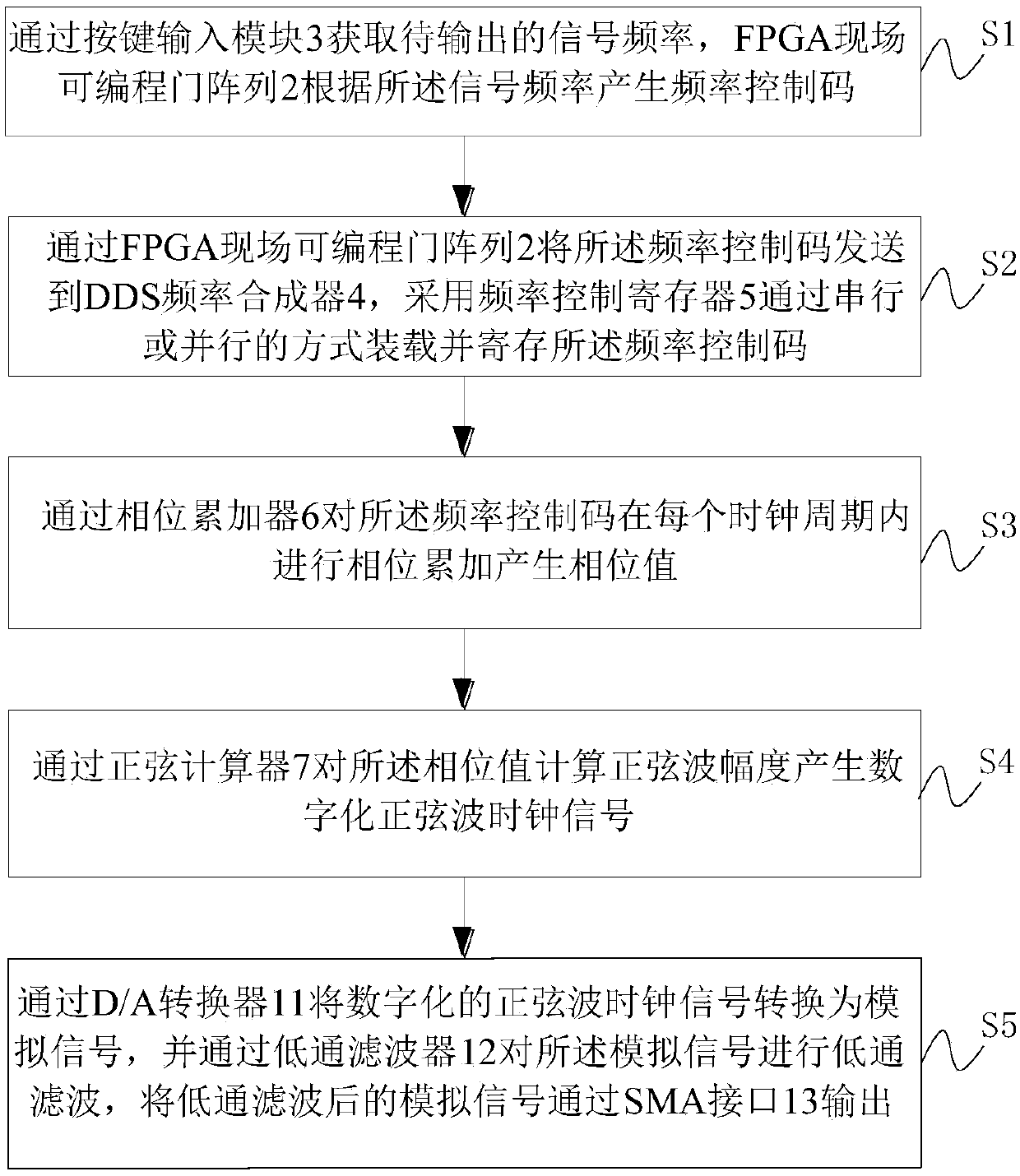

A clock signal generating apparatus and method

PendingCN109542161AGuaranteed power supply working hoursReduce volumeDigital function generatorsFpga field programmable gate arrayLow-pass filter

The invention relates to a clock signal generating device and method. The frequency of a signal to be output is obtained by a key input module. The FPGA field programmable gate array generates a frequency control code according to the frequency of the signal. The frequency control code is sent to the DDS frequency synthesizer through FPGA, and the frequency control code is loaded and stored in thefrequency control register in serial or parallel mode. A phase accumulator generates a phase value by accumulating the phase of the frequency control code in each clock cycle. A digital sine wave clock signal is generated by calculating the amplitude of the sine wave from the phase value by a sinusoidal calculator. The digitized sine wave clock signal is converted into analog signal by D / A converter, and the analog signal is low-pass filtered by low-pass filter, and the low-pass filtered analog signal is output through SMA interface. The method supports the generation of clock signal with arbitrary frequency in the range of 35MHz -4GHz, is flexible and suitable for testing, measuring or calibrating in the harsh environment in the field.

Owner:北京昊海雅正科技有限公司

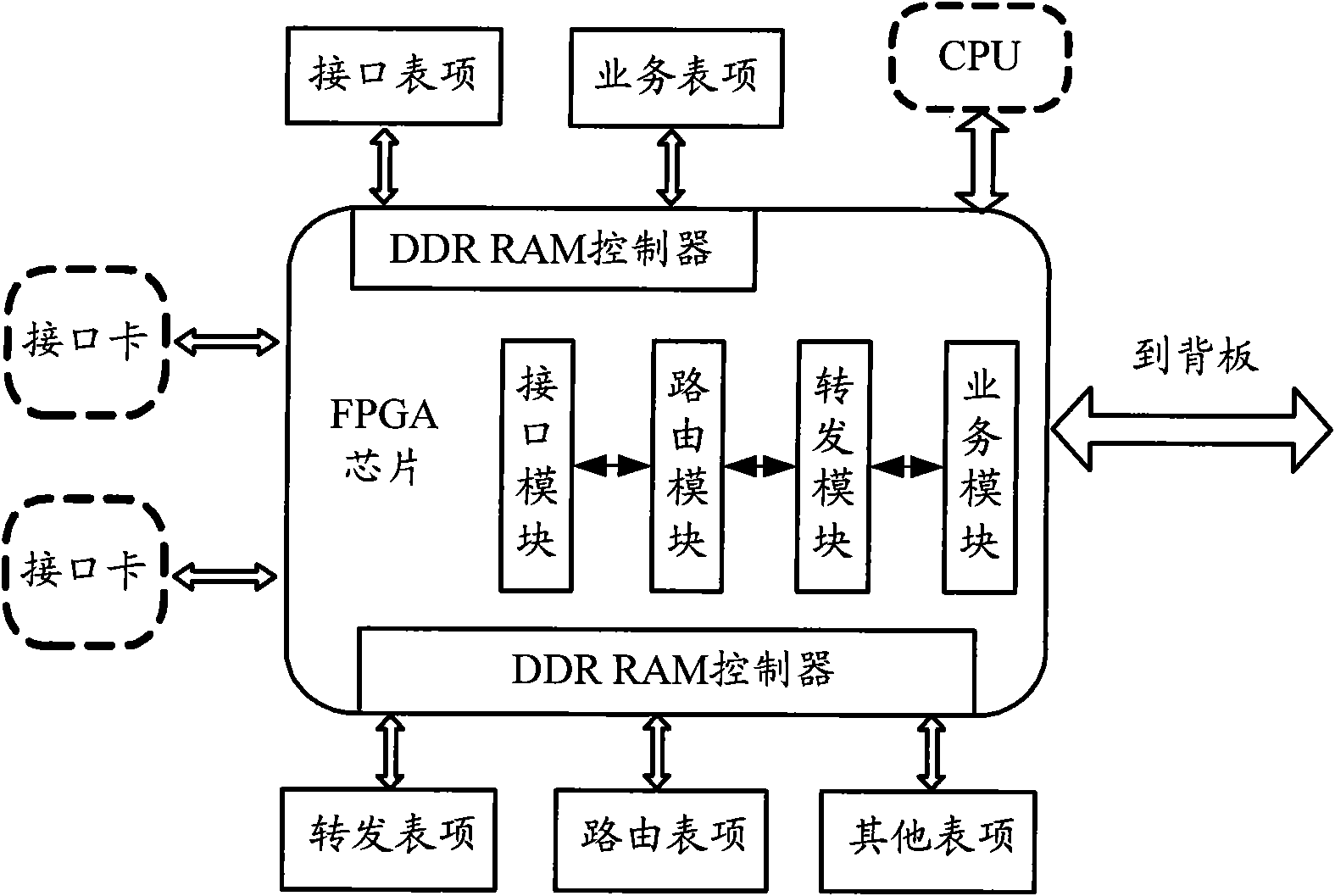

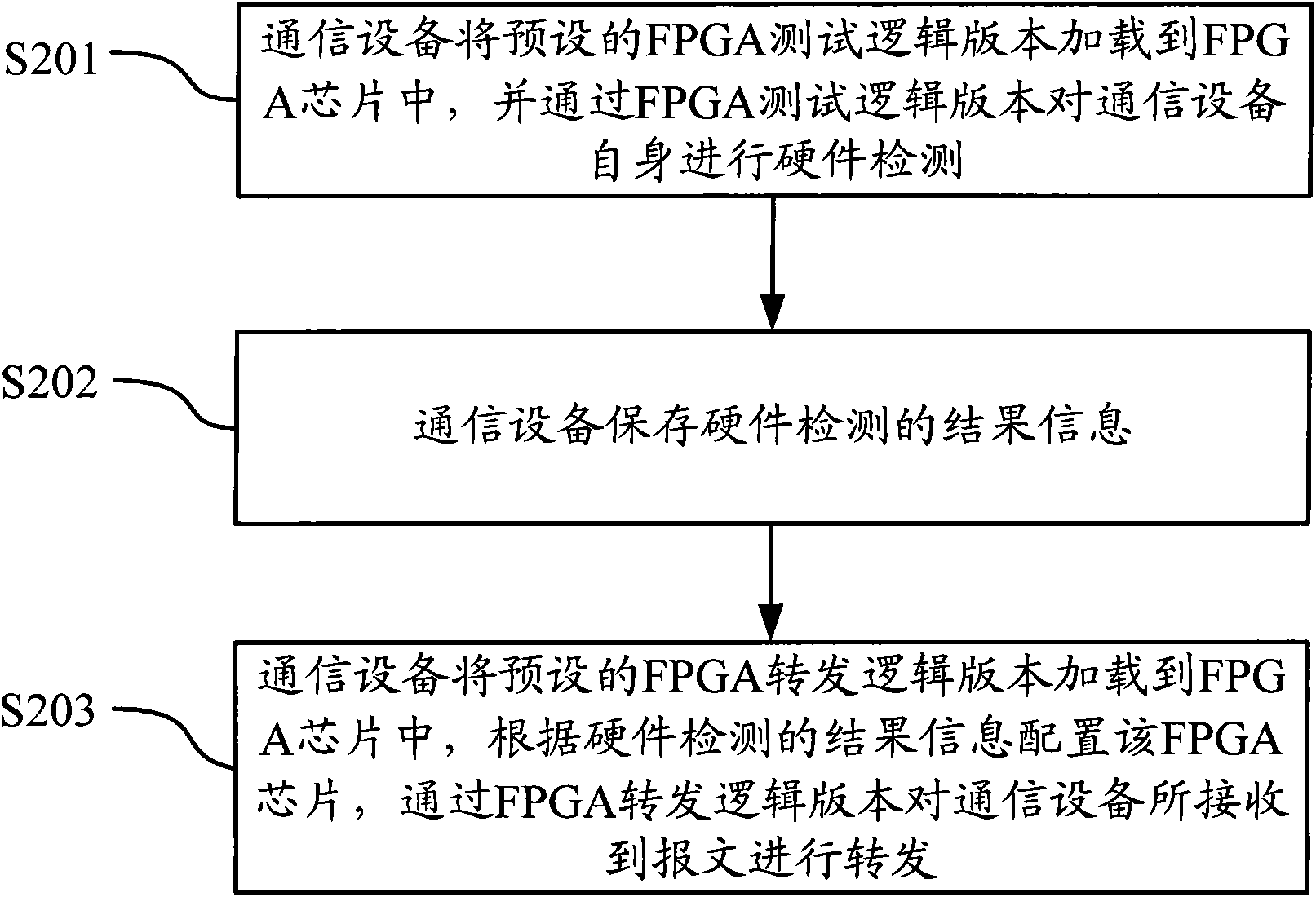

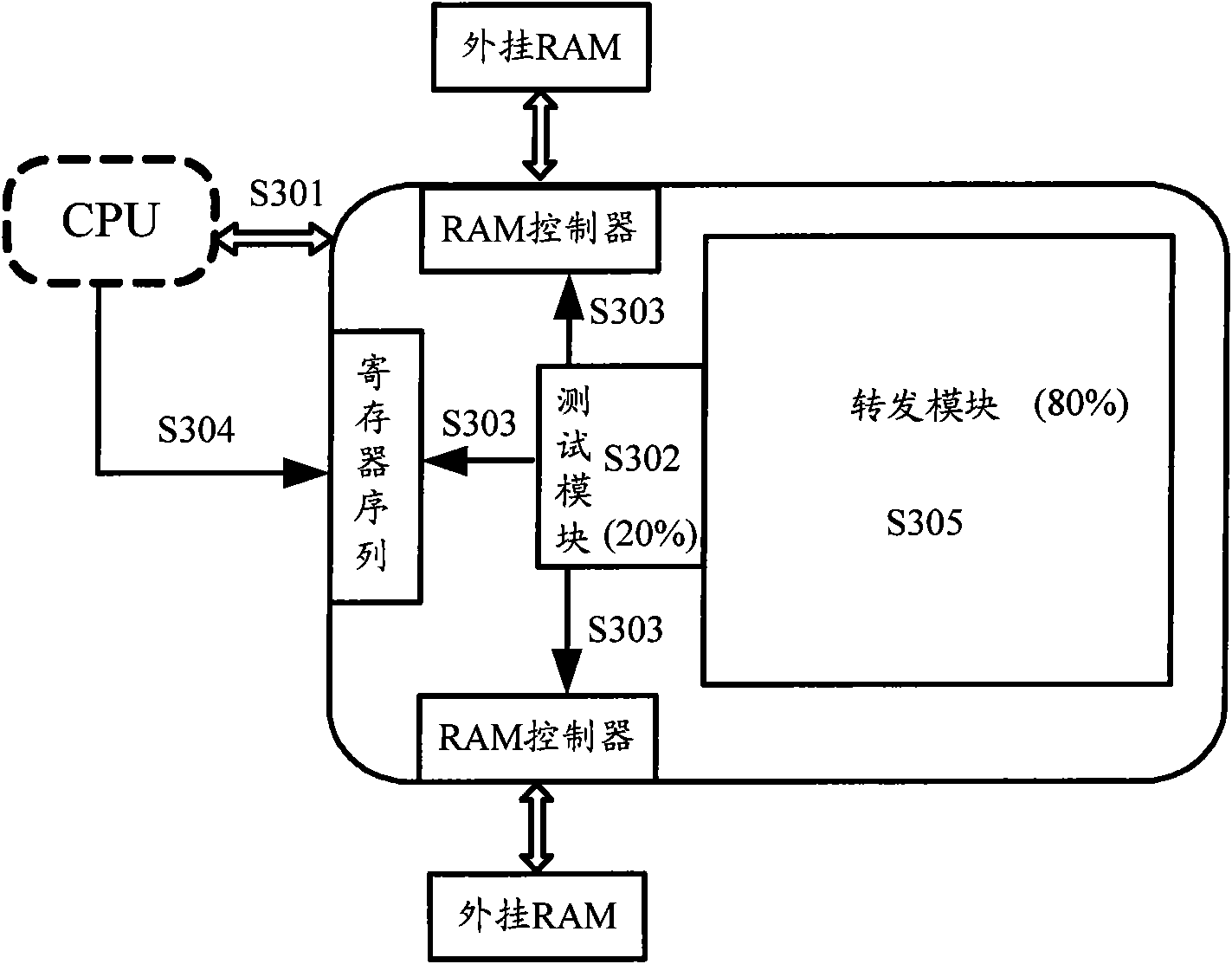

Loading method and device for FPGA (field programmable gate array) logic editions

ActiveCN102148754AImprove forwarding performanceImprove space resource utilizationData switching networksFpga field programmable gate arrayResource utilization

The invention discloses a loading method and a device for FPGA (field programmable gate array) logic editions. An FPGA (field programmable gate array) logic edition used for hardware detecting and an FPGA (field programmable gate array) logic edition used for message forwarding are split; the FPGA (field programmable gate array) logic edition used for hardware detecting is loaded preferentially; after the hardware detecting function of the FPGA (field programmable gate array) logic edition used for hardware detecting is completely actuated, the FPGA (field programmable gate array) logic edition used for message forwarding is loaded; therefore, the FPGA (field programmable gate array) logic edition used for message forwarding after being loaded on a FPGA chip can obtain more space resources, and realize the purposes of leading a communication device to support more service demands and improving the forwarding performance of the communication device as well as the space resource utilization rate of the FPGA chip under the premise that the space resources of the FPGA chip is fixed.

Owner:NEW H3C TECH CO LTD

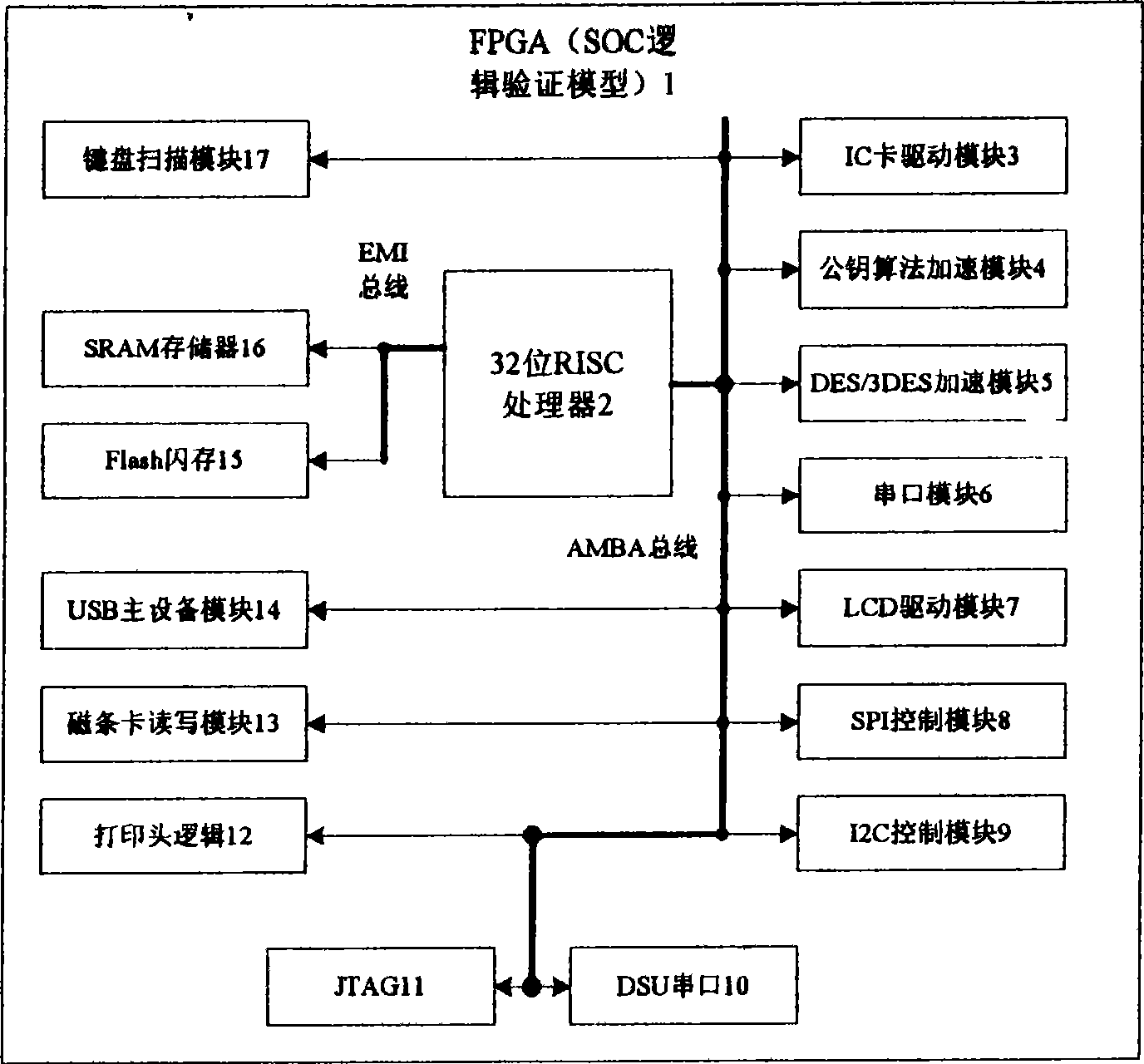

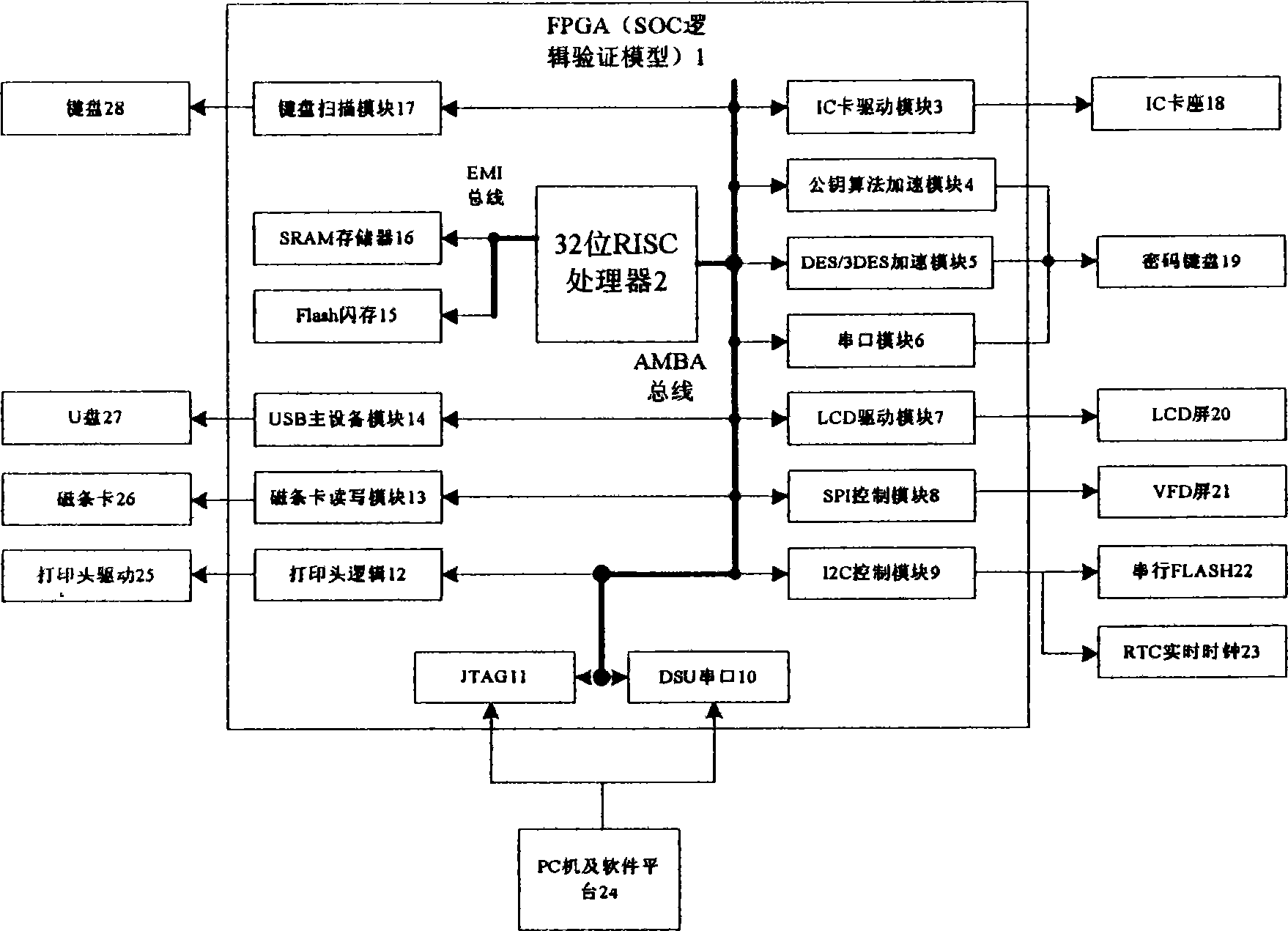

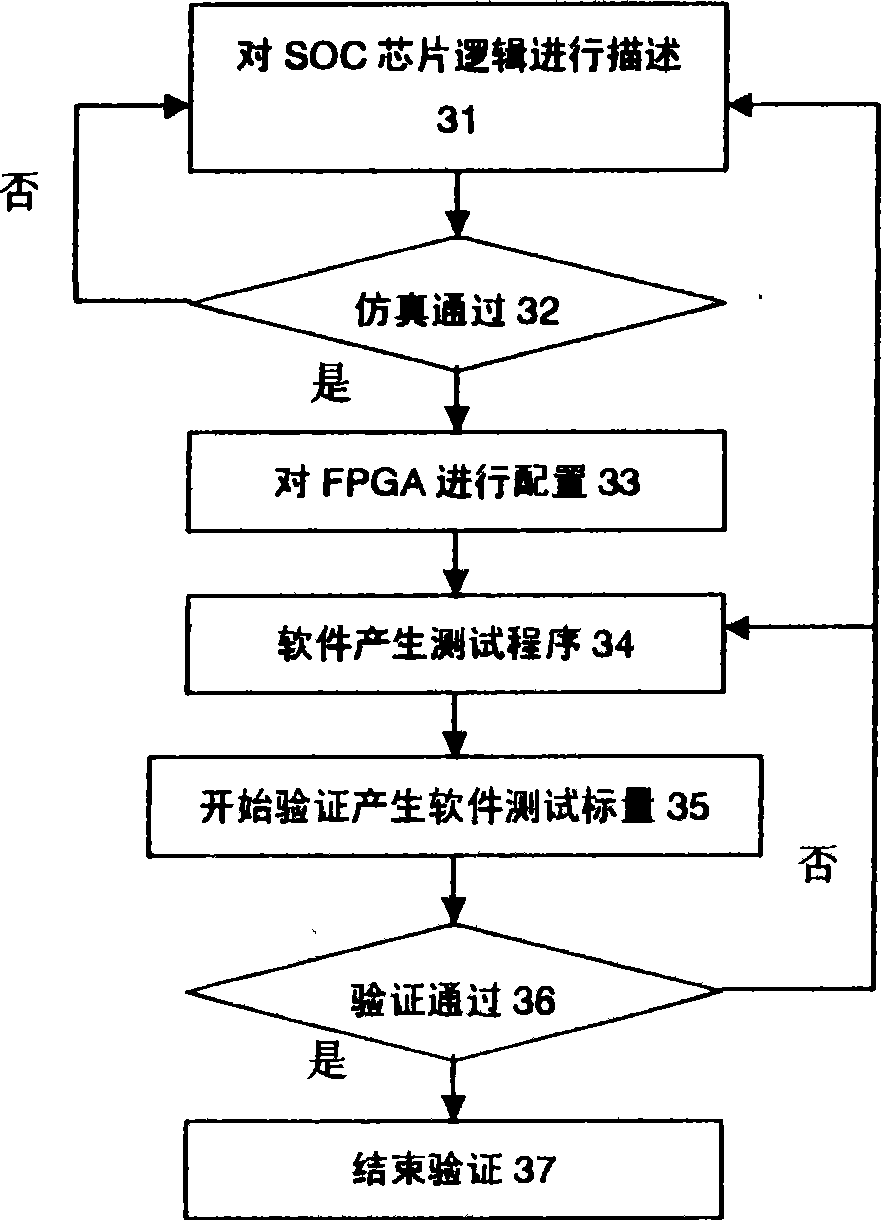

Financial tax control SOC chip logic checking system

InactiveCN101377794ASimple designShorten the development cycleSpecial data processing applicationsFpga field programmable gate arrayControl signal

The invention provides a financial tax control used SOC chip logic verification system. In the SOC chip logic verification system, a field programmable gate array FPGA is used for establishing a financial tax control SOC chip system. The system comprises a software platform and a hardware platform. The hardware platform comprises a chip logic verification model with the FPGA as the carrier of the model, various functional modules and interface modules thereof. The functional modules and the interface modules are connected with the chip logic verification model. The software platform is used for configuration of the chip logic verification model, the functional modules and the interface modules and processing related data, and inputting signals to the interface modules; the incoming signals of the chip logic verification model are generated through each functional module; control signals over software are generated through the chip logic verification model; the signals are converted into software display scalar quantities through each of the functional modules and the interface modules thereof.

Owner:LANGCHAO ELECTRONIC INFORMATION IND CO LTD

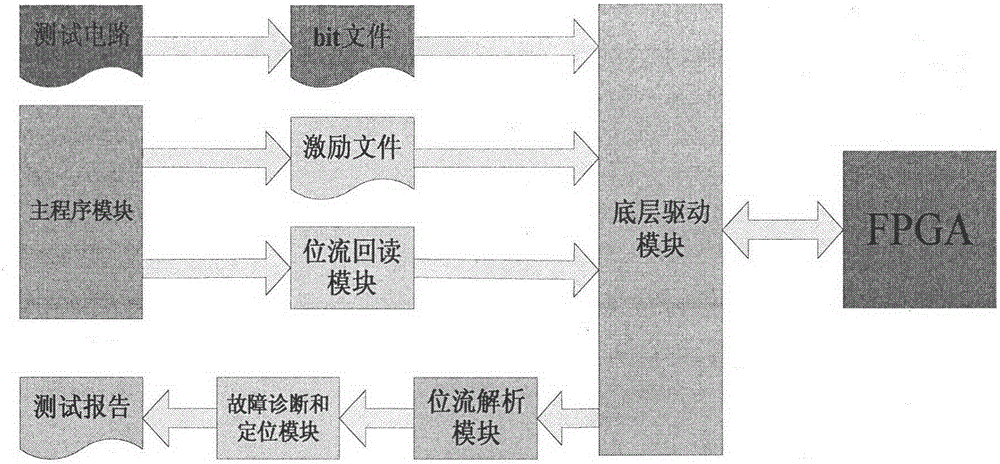

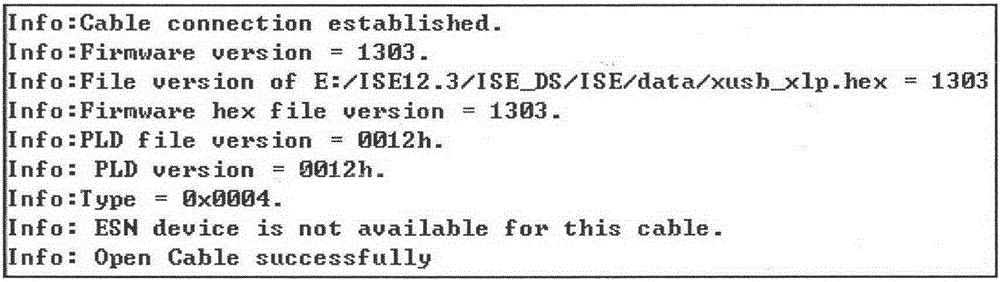

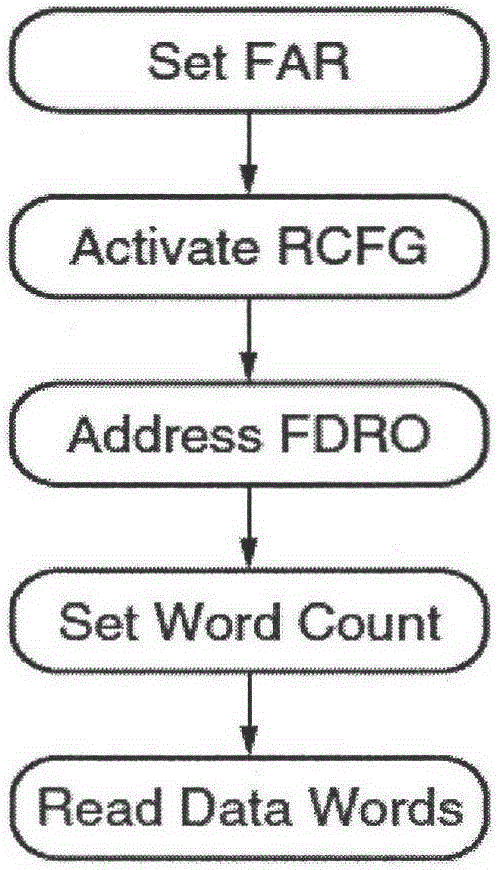

Bit stream readback-based FPGA (field programmable gate array) testing platform

The invention relates to a bit stream readback-based FPGA (field programmable gate array) testing platform. The testing platform has a bit stream analysis capability based on the boundary scanning function and bit stream readback function of an FPGA (field programmable gate array) manufactured by the Xilinx. A whole testing system, except a JTAG (joint test action group) interface, is completed in a computer. The testing system is not limited by the number of external IOB pins of the FPGA. Testing excitation can be applied directly through boundary scanning. A node for recovering test response is built into a D flip-flop and an LUT, so that the occupation of the resources of the FPGA and labor costs can be greatly decreased; and bit stream readback and bit stream analysis can achieve the detection and positioning of a fault more accurately.

Owner:张洪

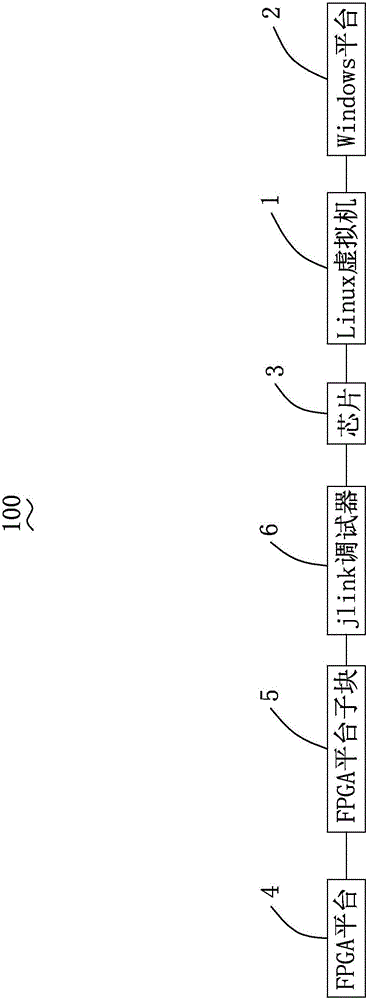

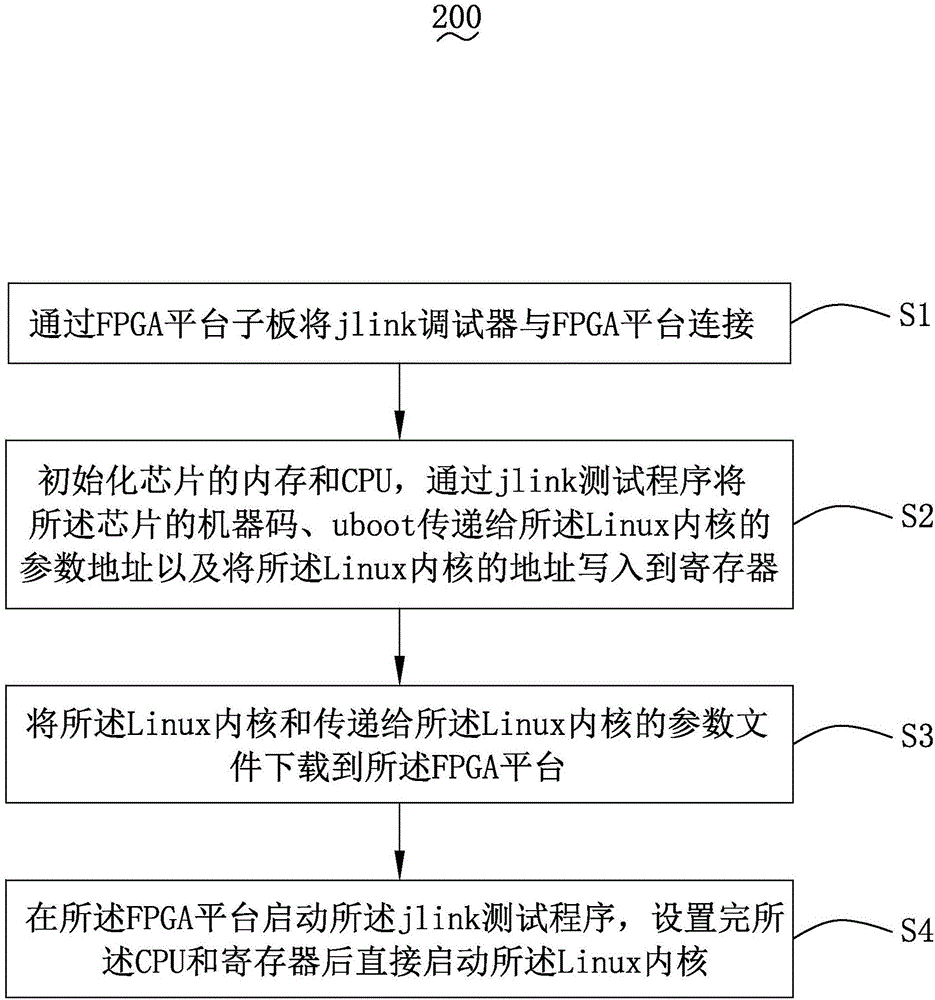

System for rapidly starting Linux core in field programmable gate array (FPGA) environment and starting method

ActiveCN106598652ASave build timeSave debugging timeProgram loading/initiatingSoftware simulation/interpretation/emulationFpga field programmable gate arrayFile system

The present invention provides a system for rapidly starting a Linux core in a field programmable gate array (FPGA) environment and a starting method. The system comprises a Linux virtual machine, a Windows platform, a function-to-be-verified chip, an FPGA platform, an FPGA platform sub-board, and a jlink debugger. The jlink debugger is connected with the chip. The jlink debugger is connected with the FPGA platform by using the FPGA platform sub-board. The Linux core is rapidly started by using the jlink debugger. Compared with related technologies, the system for rapidly starting the Linux core in the FPGA environment and the starting method have the following beneficial effects that complicate bootrom and uboot steps are omitted, a network file system is not mounted, a lot of time spent on platform building and debugging is saved, a process of connecting with Linux system driver debugging in chip development and verification is realized, reverse verification of the performance of the chip is realized, the chip development period is shortened, the chip quality is improved, and the development cost is saved.

Owner:HUNAN GOKE MICROELECTRONICS

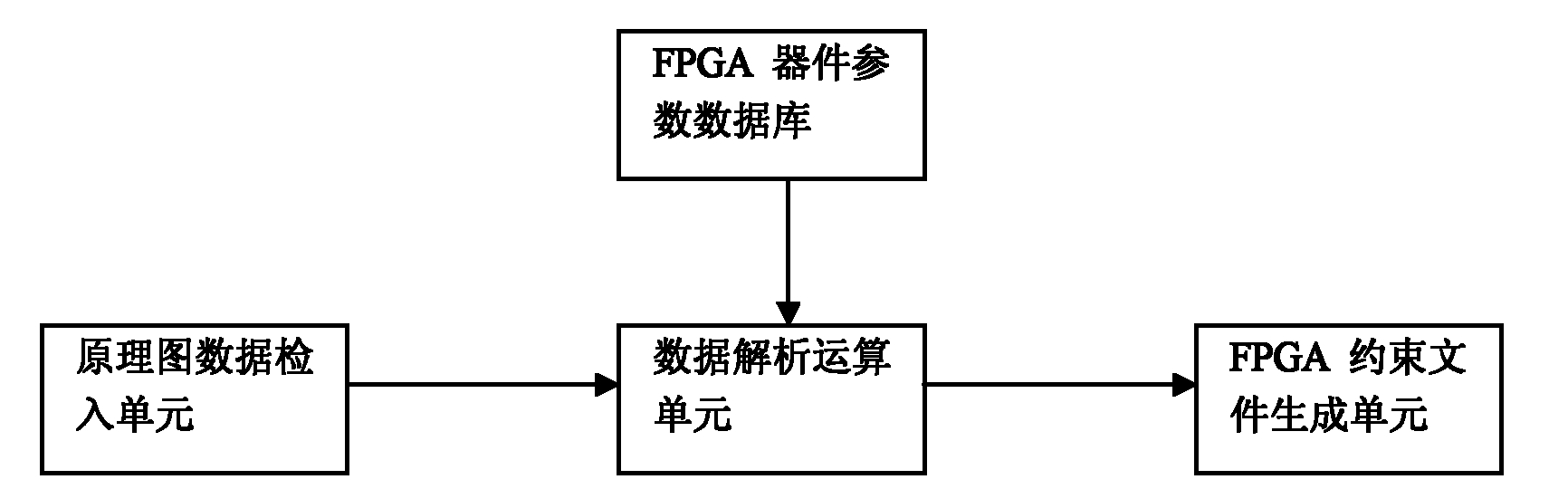

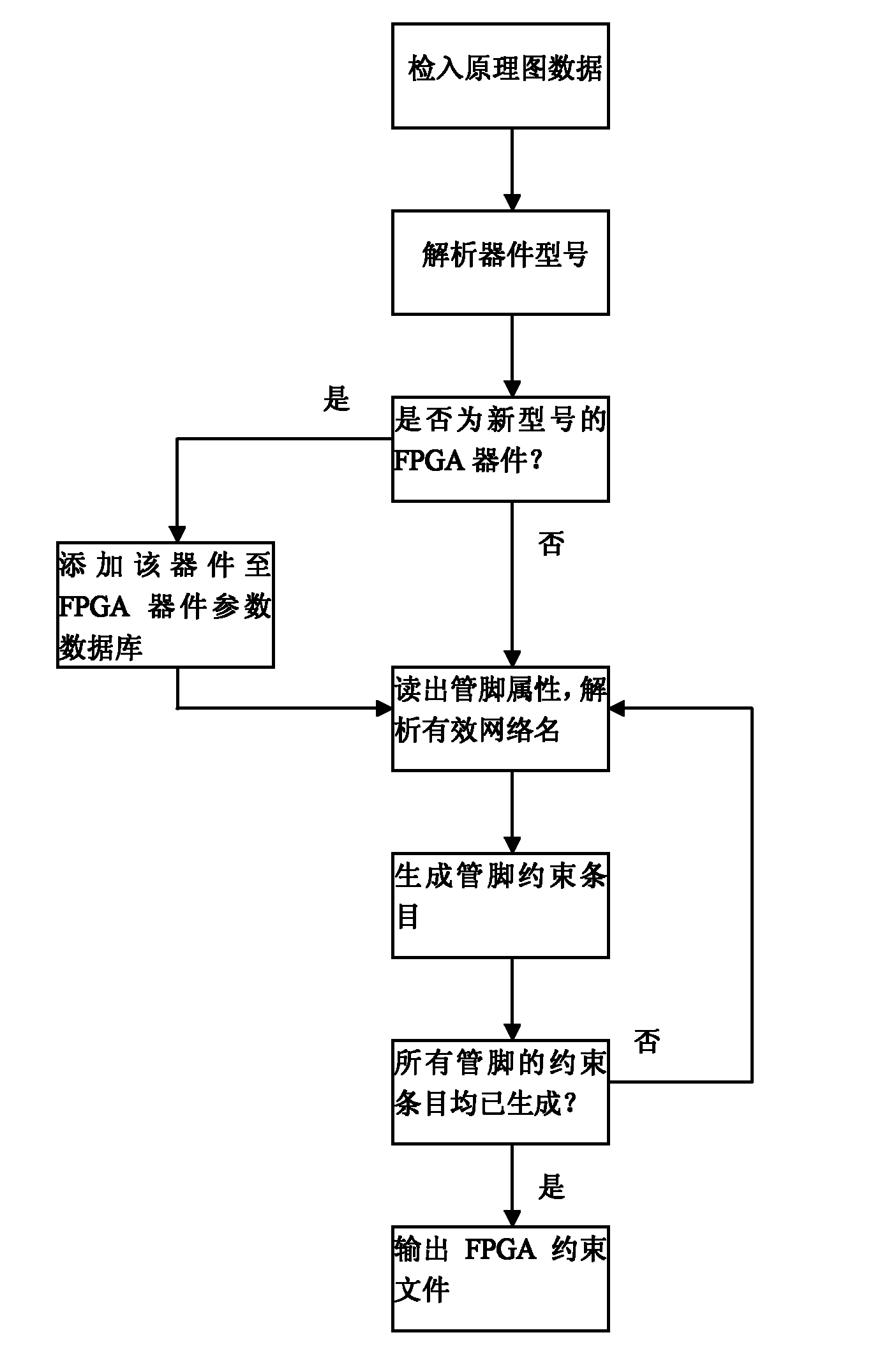

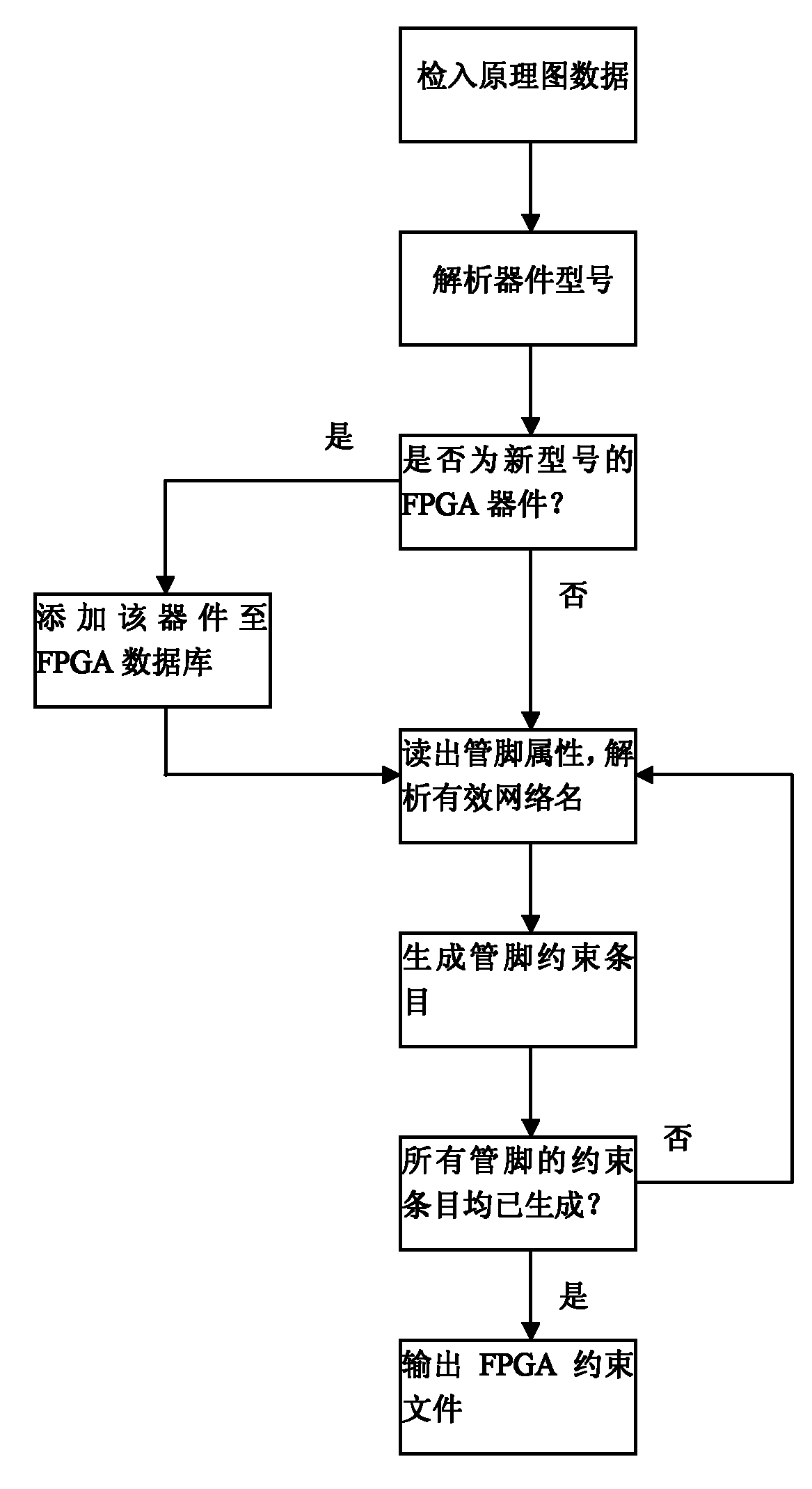

System and method for automatically generating constraint file of field programmable gate array (FPGA)

ActiveCN102156789AImprove design efficiencyGuaranteed accuracySpecial data processing applicationsFpga field programmable gate arrayBit numbering

Owner:MAIPU COMM TECH CO LTD

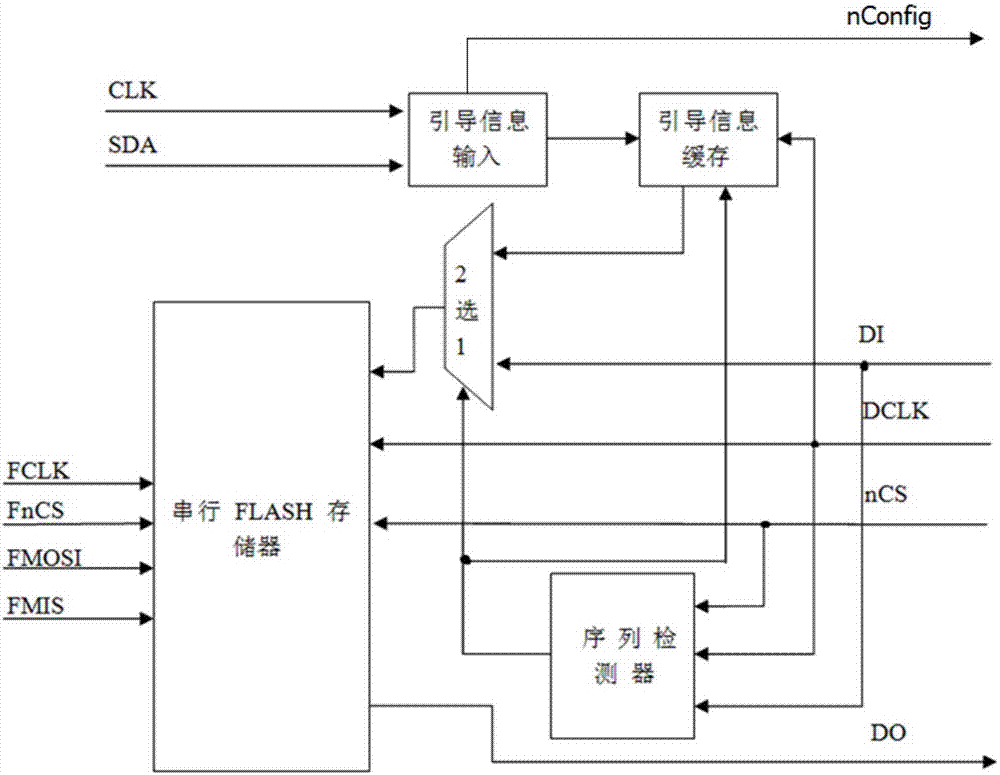

Guidable FPGA (field programmable gate array) configuration circuit

ActiveCN106940645AReduce in quantityRealize "hot switchingBootstrappingFpga field programmable gate arrayField-programmable object array

The invention belongs to the technical field of design and development of circuits, and discloses a guidable FPGA (field programmable gate array) configuration circuit. The guidable FPGA configuration circuit comprises a serial FLASH memory, wherein FCLK, FnCS, FMOSI and FMIS interfaces of the serial FLASH memory are connected with an external processor; the configuration information is written into the serial FLASH memory via the interfaces; CLK and SNA interfaces are connected with the external processor; the guiding information is set via the interfaces; nConfig, DI, DCLK, nCS and DO are connected with the FPGA. The guidable FPGA configuration circuit has the advantages that if the capacity of the FLASH memory is enough, multiple copies of FPGA configuration information can be stored in one FLASH chip, so that the number of chips can be reduced; the external processor can force the FPGA to reconfigure via CLK and SDA, so as to realize the heat exchange of the FPGA functions.

Owner:XIDIAN UNIV