Method and device for supporting field programmable gate arrays (FPGA) to download data

A gate array and data technology, applied in the field of field programmable gate array FPGA and FPGA, to shorten the download time and avoid incomplete signals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the purpose, technical solution and advantages of the present invention more clear, the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. It should be noted that, in the case of no conflict, the embodiments in the present application and the features in the embodiments can be combined arbitrarily with each other.

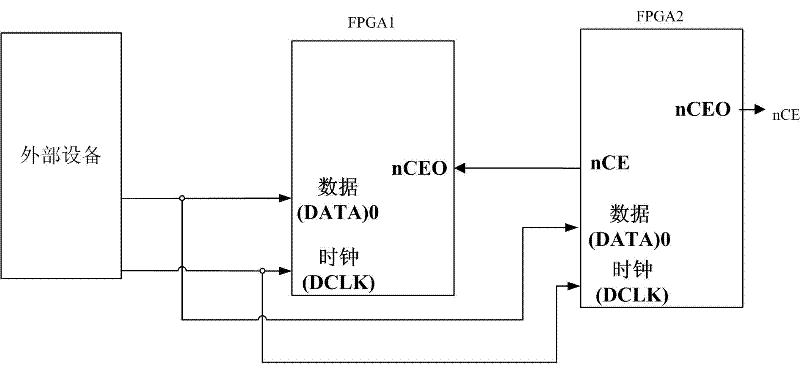

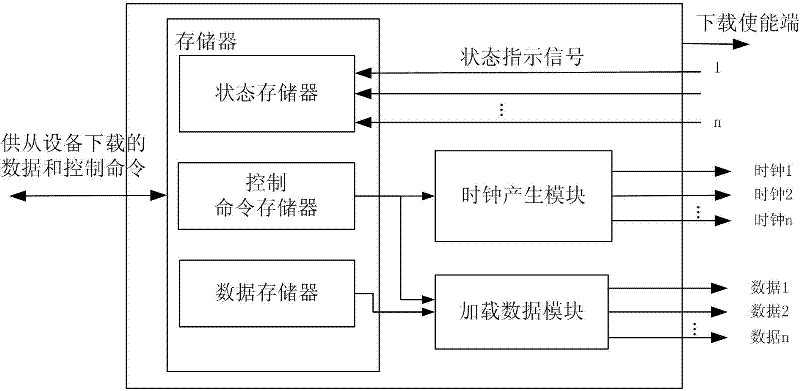

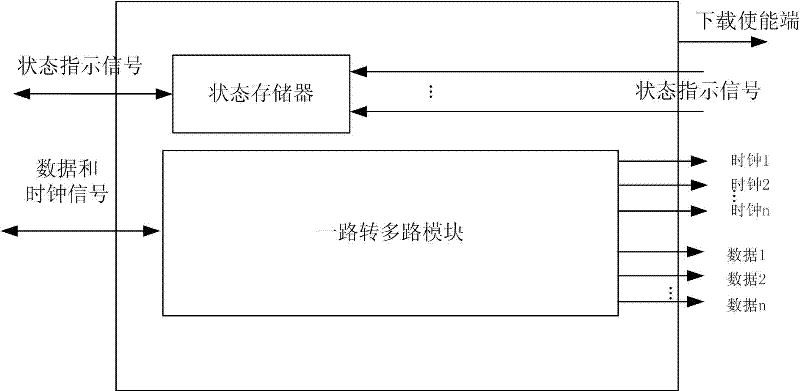

[0041] The present invention provides a kind of FPGA, and this FPGA can support a plurality of equipment Field Programmable Gate Arrays (FPGA) to download data, and this FPGA comprises: n are used to provide the first port of clock signal for described from FPGA, and n is greater than An integer of 1; n second ports for loading data from the FPGA; and a transmission module, used to use the n first ports to send the n data to the n through a dedicated clock signal transmission channel with each from the FPGA. transmitting the clock signal from the FPGAs; and transmitting the d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More