Method for using interaction of server motherboard BMC and CPLD for rapid diagnosis of motherboard timing

A rapid diagnosis and server technology, applied in the detection of faulty computer hardware, functional testing, etc., can solve problems such as time-consuming, labor-intensive, and ineffective

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

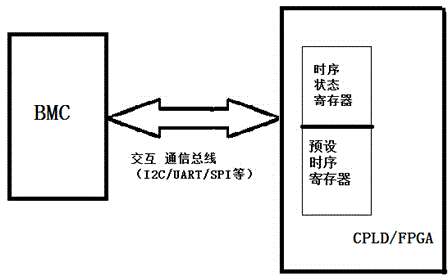

[0017] In order to describe the implementation process of the present invention more clearly, with the above figure 1 The interactive topology diagram is used for narrative explanation. The left side of the picture is the management unit BMC on the server motherboard, and the right side is the CPLD (FPGA) on the motherboard that controls timing.

[0018] 1) On the mainboard of the server, the current time is when the mainboard is in STBY state (power on but not on), BMC and CPLD (FPGA) are both in working state; but there is no communication between the two. After starting up, the timing of the motherboard is under the control of CPLD (FPGA), and it starts up according to the predetermined timing; except for the necessary timing interaction, there is no communication between the two. Therefore, to use BMC and CPLD (FPGA) to judge whether the timing is normal, there are two necessary conditions

[0019] a), BMC and CPLD (FPGA) need a communication bus;

[0020] b) The STBY s...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More